(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4956154号

(P4956154)

(45) 発行日 平成24年6月20日(2012.6.20)

(24) 登録日 平成24年3月23日(2012.3.23)

(51) Int.Cl.

H04B 3/06 (2006.01)

F 1

H04B 3/06

A

請求項の数 2 (全 19 頁)

(21) 出願番号 特願2006-318128 (P2006-318128)

(22) 出願日 平成18年11月27日 (2006.11.27)

(65) 公開番号 特開2007-174637 (P2007-174637A)

(43) 公開日 平成19年7月5日 (2007.7.5)

審査請求日 平成21年11月26日 (2009.11.26)

(31) 優先権主張番号 11/312,181

(32) 優先日 平成17年12月20日 (2005.12.20)

(33) 優先権主張国 米国(US)

早期審査対象出願

前置審査

(73) 特許権者 597154922

アルテラ コーポレイション

Altera Corporation

アメリカ合衆国 95134 カリフォルニア州 サンホセ イノベーション ドライヴ 101

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100062409

弁理士 安村 高明

(74) 代理人 100113413

弁理士 森下 夏樹

最終頁に続く

(54) 【発明の名称】信号調節受信器回路網

## (57) 【特許請求の範囲】

## 【請求項 1】

デジタル信号を調節するための受信器回路網であって、

周波数コンテンツ調節を提供する等化回路と、

該等化回路の出力に接続されている信号正規化回路であって、デジタル信号振幅を正規化された信号振幅に変換する信号正規化回路と、

フィードバックループを形成するように該等化回路および該信号正規化回路に接続されている制御回路であって、該等化回路の出力と該信号正規化回路の出力とを用いることにより、該周波数コンテンツ調節を制御し、該正規化された信号振幅を制御する制御回路とを備え、

該制御回路が、少なくとも、該信号正規化回路の出力に接続された可変抵抗を調節することによって、該正規化された信号振幅を制御し、該等化回路に対して、該制御回路が、境界周波数より低い周波数に対する周波数コンテンツ調節を制御せずに、該境界周波数より高い周波数に対する該周波数コンテンツ調節を制御し、

該制御回路が、該等化回路の出力に接続されている高域フィルタを含み、該境界周波数が、該高域フィルタのコナ周波数に対応し、

該高域フィルタの出力が、該信号正規化回路の出力に接続されている第2の高域フィルタの出力と実質的に均等になるように、該周波数コンテンツ調節の制御が行われ、

該信号正規化回路が、デジタル信号エッジスロープを正規化されたエッジスロープに変換し、該制御回路が、該正規化されたエッジスロープに基づいて該コナ周波数を制御す

る、受信器回路網。

【請求項 2】

デジタル信号を調節するための受信器回路網であって、

周波数コンテンツ調節を提供する等化回路と、

該等化回路の出力に接続されている信号正規化回路であって、デジタル信号振幅を正規化された信号振幅に変換する信号正規化回路と、

該等化回路および該信号正規化回路に接続されている制御回路と

を備え、

該制御回路が、該信号正規化回路の出力の低周波数コンテンツが、該等化回路の出力の低周波数コンテンツと実質的に均等になるように、該正規化された信号振幅を制御し、該制御回路が、少なくとも、該信号正規化回路の出力に接続された可変抵抗を調節することによって、該正規化された信号振幅を制御し、

該制御回路が、

該等化回路の出力に接続されている第1の低域フィルタと、

該信号正規化回路の出力に接続されている第2の低域フィルタと、

該第1の低域フィルタの出力を該第2の低域フィルタの出力と比較し、該低域フィルタ出力が実質的に均等になるように、該比較に基づいて該正規化された信号振幅を制御する比較器と

を備え、

該第1の低域フィルタおよび該第2の低域フィルタが、調節可能コーナ周波数を有し、

該制御回路が、該信号正規化回路の出力に少なくとも基づいて、該第1の低域フィルタおよび該第2の低域フィルタの調節可能コーナ周波数を制御する、受信器回路網。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、データ通信に関し、より詳細には、送信器回路網から受信器回路網に送信されるデータ信号の損失を補償するために、そのような通信に関与する回路網を自動的に調節する方法および装置に関する。

【背景技術】

【0002】

異なる信号送信媒体は、異なる信号送信特性を有する傾向がある。例えば、ケーブルは、プリント基板バックプレーンと異なる送信特性を有し得る。更に、任意の所定の種類の送信媒体の各段階は、その種類の送信媒体に対して典型的である範囲内において、何らかの異なる特性を有し得る。媒体の送信特性が時間とともに、もしくは環境または動作要因の結果として、変化することも可能である。

【0003】

送信媒体の性能に悪影響を及ぼし得る特性の中に、減衰および位相シフトがある。減衰および位相シフトの量が周波数依存であることは一般的である。典型的に、減衰および位相シフトの両方は、周波数が増加すると、増加する傾向がある。本明細書における便利性のために、減衰、位相シフト、および他の形の信号劣化は時々、「損失」として総称的に呼ばれる。

【0004】

デジタルデータ信号の満足な送信を行うために、高データレートまたは高周波数においては特に、送信される信号における損失を補償することが必要になり得る。更に、そのような損失が段階によって、かつ時間によって変化し得るため、そのような補償が少なくとも部分的に自動的または適応的になることが望まれ得る。そのような補償に対してよく使用される用語は等化である。プレエンファシスという用語も、時々、送信器にて実行される補償または等化、すなわち、生じるであろう損失を予期し、送信される前に信号を修正することによって損失を補償することに対して使用される。プレエンファシスという用語が使用される場合、等化という用語は、受信器にて実行される補償に対して使用され得る。

10

20

30

40

50

**【0005】**

プログラマブルロジックデバイス（「PLD」）のようなプログラマブル回路網は、適応性等化をサポートするのに有用になり得る能力を有する。例えば、PLDまたはPLD回路網は、適応性等化を必要とする信号を送信または受信することに関与する構成要素の1つになり得るか、またはそのような回路網は、そのような信号を送信および／または受信する回路網の所定の局面を制御するために使用され得る。プログラム可能であることが、生じ得る異なる送信損失特性に対処するための異なるパラメータおよび／または手順を提供することを助けるため、そのようなプログラマブル回路網（例えば、PLD回路網）は、本発明の実施において特に有用になり得る。

**【発明の開示】**

10

**【課題を解決するための手段】****【0006】**

開示される発明は、通信経路から受信されるデジタル信号を調節するための技術である。通信経路は、デジタル信号内的一部の周波数成分を減衰し得、受信器は、減衰を補償するための回路網を含み得る。

**【0007】**

受信器は、デジタル信号の周波数成分の少なくとも一部を調節する等化回路、信号振幅を正規化された信号振幅に変換し、信号エッジスロープを正規化されたエッジスロープに変換する信号正規化回路、および制御回路を含み得る。本明細書中に使用される場合、「スロープ」という用語は、一般に、「高」および「低」信号振幅領域間における上がりまた下がりのレートに関する。上がりおよび下がりは、線形または非線形になり得る。制御回路は、等化プロック内の周波数コンテンツ（frequency content）調節を制御でき、および／または信号正規化回路内の正規化された信号振幅または正規化されたエッジスロープを制御できる。

20

**【0008】**

等化回路および信号正規化回路を有する受信器構成は、順応性を提供する。信号正規化回路内の信号正規化パラメータは、受信器が異なるモードにて動作し、異なるデバイスとインターフェースすることを可能にするために変更され得る。信号正規化回路は、調節可能信号正規化パラメータを提供することによって、等化回路においてのように、周波数コンテンツを調節することもできる。従って、受信器は、等化回路と信号正規化回路との間に周波数調節動作を割り当てるための順応性をも有し得る。

30

**【0009】**

制御プロックは、コーナ周波数を有する高域フィルタおよび低域フィルタを含み得る。一実施形態においては、低域フィルタのコーナ周波数は、境界周波数より低い周波数が「低周波数」として特徴付けられるような周波数である境界周波数を規定できる。高域フィルタのコーナ周波数は、境界周波数より高い周波数が「高周波数」として特徴付けられるような周波数である境界周波数を規定できる。

**【0010】**

発明の一局面においては、信号正規化回路は、別々に制御可能である正規化された信号振幅および正規化されたエッジスロープを提供できる。信号振幅は、より低い周波数コンテンツの特定の範囲を表し得る。一実施形態においては、制御回路は、低周波数コンテンツ調節を制御するために信号正規化回路内の正規化された信号振幅を制御できる。更に、制御回路は、低周波数に対する等化回路内の周波数調節を制御しない場合もある。このようにして、受信された信号内の低周波数コンテンツの制御された調節は、等化プロック内ではなく、信号正規化プロック内にて実行され得る。

40

**【0011】**

本発明の一局面においては、制御回路は、等化回路の出力に基づいて信号正規化回路を制御できる。例えば、信号振幅は、低周波数コンテンツの特定の範囲を表し得る。信号正規化回路は、正規化された信号振幅を提供することによって、信号正規化回路の出力における低周波数コンテンツを調節できる。一実施形態においては、制御回路は、信号正規化

50

回路の出力における低周波数コンテンツが、等化回路の出力における低周波数コンテンツと実質的に均等になるように、信号正規化回路内の正規化された信号振幅を制御できる。

【0012】

本発明の一局面においては、制御回路は、信号正規化回路の出力に基づいて等化回路を制御できる。例えば、エッジスロープは、より高い周波数コンテンツの特定の範囲を表し得る。信号正規化ブロックは、信号エッジスロープを正規化されたエッジスロープに変換することによって、信号正規化ブロックの出力における特定の高周波数コンテンツを提供できる。一実施形態においては、制御回路は、等化回路の出力における高周波数コンテンツが、信号正規化回路の出力における高周波数コンテンツと実質的に均等になるように、等化回路を制御できる。

10

【0013】

開示された技術の一局面にしたがって、制御回路は、等化回路の出力を信号正規化回路の出力と比較することに基づいて、等化回路および信号正規化回路を制御できる。

【0014】

一実施形態においては、制御回路は、低域フィルタを使用して等化回路の出力における低周波数コンテンツおよび信号正規化回路の出力における低周波数コンテンツを計測できる。制御回路は、低周波数コンテンツが実質的に同じになるように、信号正規化回路内の正規化された信号振幅を制御できる。本明細書中に前述されたように、低周波数コンテンツは、制御回路内の低域フィルタのコーナ周波数に基づいて規定され得る。

【0015】

20

本発明の一局面においては、制御回路は、高域フィルタを使用して等化回路の出力における高周波数コンテンツおよび信号正規化回路の出力における高周波数コンテンツを計測できる。制御回路は、これらの周波数コンテンツが実質的に同等になるように、等化回路における周波数調節を制御できる。本明細書中に前述されたように、高周波数コンテンツは、制御回路内の高域フィルタのコーナ周波数に基づいて規定され得る。

【0016】

本発明の一局面においては、制御回路内の低域フィルタおよび高域フィルタのコーナ周波数は、予め決定され得るか、または調節可能になり得る。一実施形態においては、低域フィルタのコーナ周波数は、信号正規化回路の正規化された信号振幅に基づいておよび正規化された信号振幅によって表される周波数に基づいて調節され得る。一実施形態においては、高域フィルタのコーナ周波数は、信号正規化回路の正規化されたエッジスロープに基づいておよび正規化されたエッジスロープによって表される周波数に基づいて調節され得る。

30

【0017】

一実施形態においては、低域フィルタおよび高域フィルタは、調節可能キャパシタンスとの調節可能抵抗の直列接続によって形成され得る。調節可能抵抗は、抵抗およびスイッチの並列、直列および／または他の配置になり得、調節可能キャパシタンスは、キャパシタンスおよびスイッチの並列、直列および／または他の配置になり得る。スイッチは、コーナ周波数を調節するためにフィルタ内の抵抗およびキャパシタンスを調節するようにプログラマブルロジックデバイスによって制御され得る。

40

【0018】

本発明は、さらに以下の手段を提供する。

【0019】

(項目1)

デジタル信号を調節するための受信器回路網であって、

周波数コンテンツ調節を提供する等化回路と、

該等化回路の出力に接続されており、デジタル信号振幅を正規化された信号振幅に変換する信号正規化回路と、

該等化回路および該信号正規化回路に接続されており、該周波数コンテンツ調節および該正規化された信号振幅を制御する制御回路と

50

を備える、受信器回路網。

【0020】

(項目2)

上記等化回路に対して、上記制御回路が、境界周波数より低い周波数に対する周波数コンテンツ調節を制御せずに、該境界周波数より高い周波数に対する該周波数コンテンツ調節を制御する、項目1に記載の受信器回路網。

【0021】

(項目3)

上記制御回路が、上記等化回路の上記出力に接続される高域フィルタを含み、上記境界周波数が、該高域フィルタのコーナ周波数に対応する、項目2に記載の受信器回路網。 10

【0022】

(項目4)

上記信号正規化回路が、デジタル信号エッジスロープを正規化されたエッジスロープに変換し、上記制御回路が、該正規化されたエッジスロープに基づいて上記コーナ周波数を制御する、項目3に記載の受信器回路網。

【0023】

(項目5)

上記信号正規化回路の出力における周波数コンテンツの特定の範囲が、上記等化ブロックの出力における周波数コンテンツの該特定の範囲と実質的に均等になるように、上記制御回路が、上記正規化された信号振幅を制御する、項目1に記載の受信器回路網。 20

【0024】

(項目6)

上記制御回路が、

上記等化回路の出力に接続される第1の低域フィルタと、

上記信号正規化回路の出力に接続される第2の低域フィルタと、

該第1の低域フィルタの出力を該第2の低域フィルタの出力と比較し、該低域フィルタ出力が実質的に均等になるように、該比較に基づいて上記正規化された信号振幅を制御する比較器と

を備える、項目5に記載の受信器回路網。

【0025】

30

(項目7)

上記第1の低域フィルタおよび上記第2の低域フィルタが、調節可能コーナ周波数を有する、項目6に記載の受信器回路網。

【0026】

(項目8)

上記信号正規化回路が、デジタル信号エッジスロープを正規化されたエッジスロープに変換し、上記等化回路の出力における周波数コンテンツの特定の範囲が、上記信号正規化ブロックの出力における周波数コンテンツの該特定の範囲と実質的に均等になるように、上記制御回路が、上記周波数コンテンツ調節を制御する、項目1に記載の受信器回路網。

【0027】

40

(項目9)

上記制御回路が、

上記等化回路の出力に接続される第1の高域フィルタと、

上記信号正規化回路の出力に接続される第2の高域フィルタと、

該第1の高域フィルタの出力を該第2の高域フィルタの出力と比較し、該高域フィルタ出力が実質的に均等になるように、該比較に基づいて上記周波数コンテンツ調節を制御する比較器と

を備える、項目8に記載の受信器回路網。

【0028】

50

(項目10)

上記第1の高域フィルタおよび上記第2の高域フィルタが、調節可能コーナ周波数を有する、項目9に記載の受信器回路網。

**【0029】**

(項目11)

上記制御回路が、上記正規化されたエッジスロープに基づいて上記コーナ周波数を制御する、項目10に記載の受信器回路網。

**【0030】**

(項目12)

デジタル信号を調節するための受信器回路網であって、

周波数コンテンツ調節を提供する等化回路と、

10

該等化回路の出力に接続されており、正規化された信号振幅および正規化されたエッジスロープのうちの少なくとも1つを提供する信号正規化回路と、

該等化回路の出力に接続される第1の高域フィルタと、

該等化回路の出力に接続される第1の低域フィルタと、

該信号正規化回路の出力に接続される第2の高域フィルタと、

該信号正規化回路の出力に接続される第2の低域フィルタと

を備え、

該第1の高域フィルタ、該第1の低域フィルタ、該第2の高域フィルタ、および該第2の高域フィルタは調節可能コーナ周波数を有する、

受信器回路網。

20

**【0031】**

(項目13)

上記制御回路が、上記正規化された信号振幅に基づいて上記第1の低域フィルタおよび上記第2の低域フィルタの上記調節可能コーナ周波数を制御し、上記正規化されたエッジスロープに基づいて上記第1の高域フィルタおよび上記第2の高域フィルタの該調節可能コーナ周波数を制御する、項目12に記載の受信器回路網。

**【0032】**

(項目14)

上記第1の低域フィルタ、上記第1の高域フィルタ、上記第2の低域フィルタ、および上記第2の高域フィルタの各々が、可変キャパシタンスとの可変抵抗の直列接続を含む、項目12に記載の受信器回路網。

30

**【0033】**

(項目15)

上記可変抵抗が、抵抗および第1のスイッチの配置を含み、上記可変キャパシタンスが、キャパシタンスおよび第2のスイッチの配置を含む、項目14に記載の受信器回路網。

**【0034】**

(項目16)

上記第1のスイッチおよび上記第2のスイッチに接続されるプログラマブルロジックデバイスをさらに備えており、該プログラマブルロジックデバイスが、上記コーナ周波数を提供するために該第1のスイッチおよび該第2のスイッチを構成するようにプログラムされる、項目15に記載の受信器回路網。

40

**【0035】**

(項目17)

正規化された信号振幅および正規化されたエッジスロープを提供するための信号正規化回路であって、

調節可能電流源；

該調節可能電流源に結合されるソースノード、入力信号を受信するためのゲートノード、およびドレインノードを有する第1の電界効果トランジスタ；

該調節可能電流源に結合されるソースノード、ゲートノード、およびドレインノードを有する第2の電界効果トランジスタであって、該ゲートノードは該入力信号および基準

50

電圧のうちの 1 つに結合される、第 2 の電界効果トランジスタ；

該第 1 の電界効果トランジスタの該ドレインノードに接続される第 1 の可変抵抗；および、

該第 2 の電界効果トランジスタの該ドレインノードに接続される第 2 の可変抵抗；を備える、第 1 のステージ回路と、

該第 1 の電界効果トランジスタの該ドレインノードに接続されるゲートノードを有する第 3 の電界効果トランジスタ；および、

該第 2 の電界効果トランジスタの該ドレインノードに接続されるゲートノードを有する第 4 の電界効果トランジスタ；

を備える、第 2 のステージ回路と

を備える、信号正規化回路。

#### 【0036】

(項目18)

上記第 1 の可変抵抗および上記第 2 の可変抵抗の各々が、スイッチおよび抵抗の配置を含む、項目 17 に記載の信号正規化回路。

#### 【0037】

(項目19)

上記スイッチに結合されるプログラマブルロジックデバイスをさらに備えており、該プログラマブルロジックデバイスが、正規化されたエッジスロープを提供するために該スイッチを構成するようにプログラムされる、項目 18 に記載の信号正規化回路。

#### 【0038】

(項目20)

上記調節可能電流源が、調節可能電流を提供するための可変抵抗を有する電流ミラー回路を含む、項目 17 に記載の信号正規化回路。

#### 【0039】

(項目21)

上記電流ミラー回路の上記可変抵抗が、スイッチおよび抵抗の配置を含む、項目 20 に記載の信号正規化回路。

#### 【0040】

(項目22)

上記スイッチに接続されるプログラマブルロジックデバイスをさらに備えており、該プログラマブルロジックデバイスが、正規化された信号振幅を提供するために該スイッチを構成するようにプログラムされる、項目 21 に記載の信号正規化回路。

#### 【発明を実施するための最良の形態】

#### 【0041】

本発明の更なる特徴、その本質および様々な利点は、添付の図面および以下の詳細な説明からより明らかになる。

#### 【0042】

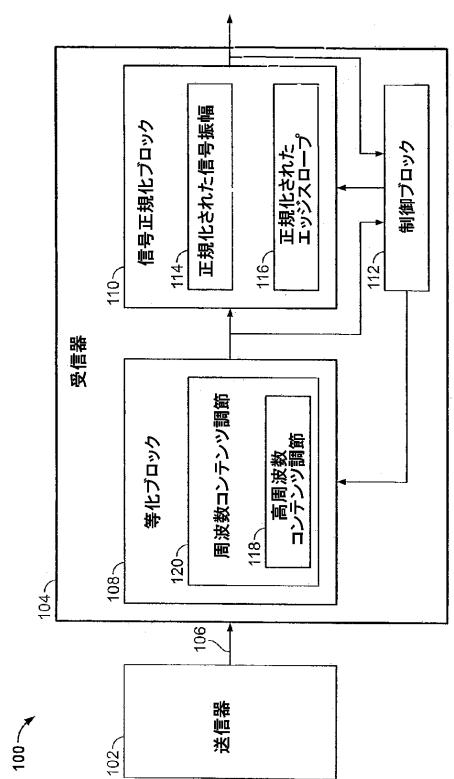

開示された技術は、受信器における送信信号を調節するための発明である。図 1 を参照すると、送信器 102 と受信器 104 との間において信号を通信するためのシステム 100 が示される。送信器 102 と受信器 104 との間の通信経路 106 は、1 つ以上の通信媒体（例えば、ワイヤ、大気、光ファイバ）および / または 1 つ以上の通信デバイス（例えば、ルータ、ハブ、スイッチ）を含み得る。通信経路 106 に沿う様々な地点において、通信経路は、デジタルまたはアナログ信号を含み得る。本明細書において使用される場合、「デジタル信号」は、「高」および「低」信号振幅領域および 2 つの振幅領域間ににおけるエッジ遷移を使用することによって情報を表す信号に関する。通信経路 106 は、経路内の様々な地点におけるデジタルまたはアナログ信号を含み得るが、開示された技術の受信器 104 は、デジタル信号を受信する。

#### 【0043】

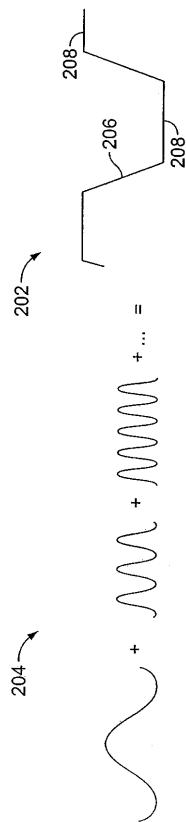

図 2 は、高および低振幅レベルならびに 2 つの振幅レベル間ににおけるエッジ遷移を有す

10

20

30

40

50

るデジタル信号 202 を示す。フーリエ変換に基づいて、デジタル信号 202 が異なる周波数および振幅を有するいくつかの成分信号 204 を含み得ることが当業者に理解されるであろう。デジタル信号内のエッジ遷移 206 のスロープは、高周波数コンテンツを示し得る。本明細書において使用される場合、「スロープ」という用語は、一般に、「高」および「低」信号振幅領域間ににおける上がりまたは下がりのレートに関する。上がりまたは下がりは、線形または非線形になり得る。より大きいスロープを有するエッジ遷移 206 は、より小さいスロープを有するエッジ遷移より多いコンテンツの高周波数成分を示し得る。デジタル信号の振幅レベル 208 は、より大きい振幅レベルがより低い振幅レベルより多いコンテンツの低周波数成分を示し得るように、低周波数コンテンツを示し得る。一実施形態においては、「高周波数」または「低周波数」として分類される周波数の範囲は、境界周波数に基づき得る。ここにおいて、高周波数は、境界周波数の上の周波数を含み、低周波数は、境界周波数の下の周波数を含む。他の実施形態においては、1つ以上の境界周波数があり得る。例えば、一実施形態においては、高周波数は、第1の境界周波数より上の周波数を含み得、低周波数は、第2の境界周波数より下の周波数を含み得る。境界周波数（単数または複数）は、一定または調節可能になり得る。境界周波数は、図7に関連して、本明細書中により詳細に説明される。

#### 【0044】

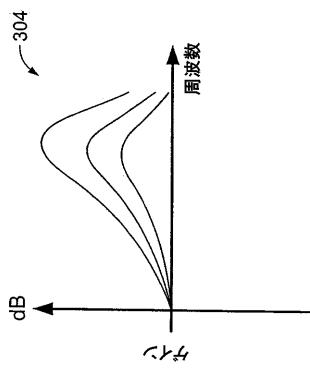

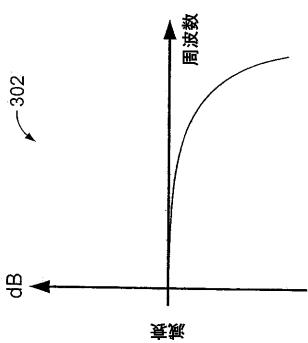

図3を参照し、図1を引き続き参照すると、減衰およびゲインの例示的グラフが示される。本明細書において使用される場合、減衰は、通信システムにおける現象または通信システムに影響を与える様々な現象によって、もしくはフィルタまたは他の回路網またはそれ以外によって生じ得る信号エネルギーにおける減少に関する。ゲインは、逆に、信号エネルギーにおける増加に関する。通信システムにおける信号は、通信経路 106（図1）における減衰を受け得る。図3の例示的減衰グラフ 302 に示されるように、高周波数を有する成分信号（例えば、204、図2）が、典型的に、より低い周波数を有する成分信号より大きな減衰を受けることが当業者に理解されるであろう。信号内のより高い周波数成分が減衰されると、信号のエッジ遷移（例えば、206、図2）のスロープは減少し得、回路タイミングおよび／または他の回路動作に悪影響を与え得る。

#### 【0045】

受信器における等化ブロック 108（図1の）の目的は、通信経路 106 に存在し得るオフセット減衰に対してゲインを提供することである。通信経路 106 の減衰効果が時間とともに変化し得るため、等化ブロック 108 は、変化に適応するための調節を行う必要があり得る。図3内のゲイングラフ 304 は、等化ブロック 108 が提供し得る例示的ゲインカーブを示す。図6に関連して本明細書中に後で説明されるように、どのゲインカーブが通信経路 106 における減衰を最も良くオフセットするかについての決定は、制御ブロック 112（図1）によって行われ得る。図3は例示的であり、本発明の範囲内における減衰およびゲインカーブの数、形、および／または大きさを制限しない。

#### 【0046】

再度図1を参照し、開示された発明の一局面に従うと、示された受信器 104 は、等化ブロック 108、信号正規化ブロック 110、および制御ブロック 112 を含む。等化ブロック 108 および信号正規化ブロック 110 を有する受信器は、順応性を提供する。信号正規化ブロック 110 内の信号正規化パラメータは、受信器 104 が異なるモードおよび異なるデータレートにて動作し、異なるデバイスとインターフェースすることを可能にするために変更され得る。信号正規化ブロック 110 は、調節可能信号正規化パラメータを提供することによって、等化ブロック 108 においてのように、周波数コンテンツを調節することもできる。従って、受信器 104 は、等化ブロック 108 と信号正規化ブロック 110との間に周波数調節動作を割り当てるための順応性をも有し得る。

#### 【0047】

一般に、等化ブロック 108 は、ゲインおよび／または減衰を提供でき、特に 118 の高周波数コンテンツを調節でき、および／または 120 の全般的な周波数コンテンツを調節できる。等化ブロックは、必要に応じて、低周波数コンテンツ調節を別々に提供し得る

10

20

30

40

50

(図示せず)。図6に関連してより詳細に説明されるように、周波数は、1つ以上の境界周波数に基づいて「高周波数」または「低周波数」として特徴付けられ得る。一実施形態において、等化ブロック108は、結果として生じる等化後信号を提供するために、ゲインカーブ(例えば、304、図3)に従って通信経路106から受信されるデジタル信号の周波数コンテンツを調節できる。当業者は、周波数コンテンツを調節するための様々な既存の技術が、等化ブロック108に使用され得ることを認識するであろう。図6に関連して本明細書中に後で説明されるように、等化ブロック108は、制御ブロック112によって制御され得る。

#### 【0048】

本発明の一局面に従うと、等化後信号は、等化後信号における振幅および/またはエッジスロープを、それぞれ正規化された振幅および/または正規化されたエッジスロープに変換し得る信号正規化ブロック110に通信される。一実施形態においては、信号正規化ブロック110は、産業規格、政治規制、および/または他の要件に基づいて正規化された信号振幅114および/または正規化されたエッジスロープ116を提供できる。一般に、受信器104および送信器102は一緒に作動するように設計されるため、受信器104は、送信器102によって使用される信号振幅(例えば、208、図2)およびエッジ遷移のスロープ(例えば、206、図2)を認識できる。したがって、受信器104における信号正規化ブロック110は、デジタル送信信号を提供するために送信器102によって使用されるものと同じである正規化された信号振幅114および/または正規化されたエッジスロープ116を提供できる。

10

#### 【0049】

一実施形態においては、信号正規化ブロック110は、特定のアプリケーションの動作要件に基づいて、正規化された信号振幅114および正規化された信号エッジスロープ116を提供できる。例えば、受信器104によって受信されるデジタル信号は、異なる電圧要件を有する複数のデバイスによる使用を意図し得る。1つのデバイスは、例えば、600mVの正規化された信号振幅を要求し得、別のデバイスは、例えば、1200mVの正規化された信号振幅を要求し得る。どのデバイスが受信器104と相互作用しているかによって、制御回路112は、それに応じて正規化された信号振幅114を変更し得る。他の例として、送信器102および受信器104は、異なる送信周波数を使用する異なるモードの動作を有し得る。送信器102と受信器104との間で通信されるデジタル信号が1メガビット/秒の信号周波数を有する場合、1ナノ秒の正規化されたエッジスロープが適切であり得る。しかしながら、デジタル信号が10ギガビット/秒の信号周波数を有する場合、1ナノ秒の正規化されたエッジスロープでは遅すぎる場合があり、制御回路112は、正規化されたエッジスロープ116を増加させる必要があり得る。したがって、一部の実施形態においては、信号正規化ブロック110内の正規化された信号振幅114および/または正規化されたエッジスロープ116は、調節可能になり得、制御ブロック112によって制御され得る。

20

30

#### 【0050】

図4は、図1の信号正規化ブロックの回路実施形態を示す。示された信号正規化回路400は、少なくとも2つのステージ402、404を含む。第1のステージ402は、等化後信号を受信するために接続INP1 406およびINN1 408を有する。等化後信号が差動信号であった場合、INP1接続406およびINN1接続408の両方は、等化後信号を受信するために使用され得る。等化後がシングルエンディッド信号であった場合、INN1接続408が基準電圧に接続され得る一方、INP1接続406は等化後信号を受信するために使用され得、その逆も同様にあり得る。説明を容易にするために、等化後信号が「高」値および「低」値を有し得る差動信号であることが想定される。等化後信号が「高」であった場合、INP1信号406はINN1信号408より大きい。等化後信号が「低」であった場合、INP1信号406はINN1信号408より小さい。

40

#### 【0051】

INP1接続406は、INP1電界効果トランジスタ(FET)410のゲートに接

50

続され、INN1接続408は、INN1 FET 412のゲートに接続される。差動信号が「高」であった場合、INP1 FET 410がONになり、INN1 FET 412がOFFになることが本明細書中に想定される。差動信号が「低」であった場合、INP1 FET 410がOFFになり、INN1 FET 412がONになることも本明細書中に想定される。INP1 FETのソースノードおよびINN1 FETのソースノードは、414において接続され、その両方は可変電流源416の内の1つのノードに接続される。可変電流源のもう一方のノードは、低基準電圧418に接続される。INP1 FET 410のドレインノードは、INP1可変抵抗420の内の1つのノードに接続され、INP1可変抵抗420のもう一方のノードは、高基準電圧422に接続される。同様に、INN1 FET 412のドレインノードは、INN1可変抵抗424の内の1つのノードに接続され、INN1可変抵抗424のもう一方のノードは、高基準電圧422に接続される。10

#### 【0052】

INP1 FET 410のドレインノードは、本明細書中にOUTP1 426として呼ばれ、INN1 FET 412のドレインノードは、本明細書中にOUTN1 428として呼ばれる。OUTP1ノード426およびOUTN1ノード428の電圧差は、第1のステージ402の出力である差動信号である。出力差動信号は、(OUTP1 - OUTN1)または(OUTN1 - OUTP1)のいずれかによって規定され得る。説明を容易にするために、この時点から、第1のステージの出力が(OUTP1 - OUTN1)によって規定されることが想定される。更に、OUTP1 426は、第2のステージ404において、INP2 FET 430のゲートノードに接続され、OUTN1 428は、第2のステージ404において、INN2 FET 432のゲートノードに接続される。20

#### 【0053】

第1のステージ402を参照すると、等化後信号が「高」値である場合、INP1 FET 410はONであり、INN1 FET 412はOFFである。INN1 FET 412がOFFである場合、OUTN1 428は、高基準電圧V<sub>H</sub> 422と同じ電圧を有する。INP1 FET 410がONであり、INN1 FET 412がOFFである場合、可変電流源416によって確立される電流Iは、INP1 FET 410およびINP1可変抵抗R<sub>INP1</sub> 420を介して流れる。したがって、OUTP1 426における電圧は、(V<sub>H</sub> - I \* R<sub>INP1</sub>)である。したがって、等化後が「高」値を有する場合、第1のステージの出力は、(OUTP1 - OUTN1) = (V<sub>H</sub> - I \* R<sub>INP1</sub>) - V<sub>H</sub> = - I \* R<sub>INP1</sub>である。等化後が「低」値を有する場合、INP1 FET 410はOFFであり、INN1 FET 412はONである。INP1 FET 410がOFFである場合、OUTP1 426は、高基準電圧V<sub>H</sub> 422と同じ電圧を有する。INN1 FET 412がONであり、INP1 FET 410がOFFである場合、可変電流源416によって確立される電流Iは、INN1 FET 412およびINN1可変抵抗R<sub>INN1</sub> 424を介して流れる。したがって、OUTN1 428における電圧は、(V<sub>H</sub> - I \* R<sub>INN1</sub>)である。したがって、等化後が「低」値を有する場合、第1のステージの出力は、(OUTP1 - OUTN1) = V<sub>H</sub> - (V<sub>H</sub> - I \* R<sub>INN1</sub>) = + I \* R<sub>INN1</sub>である。この動作によって、等化後信号が「高」と「低」の値の間ににおいて変化すると、第1のステージ420の出力は、正規化された信号振幅である-I \* R<sub>INP1</sub>と+I \* R<sub>INN1</sub>との間で変化する。したがって、図4の示された実施形態において、信号正規化回路400は、可変電流源416によって確立される電流Iの量を変化させることによって、および/または可変抵抗420、424の抵抗R<sub>INP1</sub>およびR<sub>INN1</sub>を変化させることによって、正規化された信号振幅(114、図1)を調節できる。3040

#### 【0054】

出力ノードOUTP1 426およびOUTN1 428は、第2のステージ404におけるFET 430、432のゲートノードに接続される。これらのFET 430、50

432のゲートノードがゲートキャパシタンスを有するため、第1のステージ402における可変抵抗420、424および第2のステージ404におけるゲートキャパシタンスは、RC時定数を有するRC回路を全体として形成する。RC回路は、ノードOUTP1 426およびOUTN1 428における電圧がRC時定数に基づいて指数関数的に上がり下がりすることを引き起こし、それによって、出力信号(OUTP1 - OUTN1)における正規化されたエッジスロープを規定する。RC時定数は、抵抗 $R_{INP1} 420$ および $R_{INN1} 424$ を変化させることによって調節され得る。この調節は、OUTP1 426およびOUTN1 428におけるエッジ遷移のスロープを変化させ、結果的に、出力信号(OUTP1 - OUTN1)におけるエッジ遷移のスロープも調節される。したがって、図4の示された実施形態において、信号正規化回路400は、可変抵抗420、424の抵抗 $R_{INP1}$ および $R_{INN1}$ を調節することによって特定の正規化されたエッジスロープ(116、図1)を提供できる。

10

#### 【0055】

図4の示された実施形態において、第2のステージ404は、第1のステージ402と同じである。第2のステージ404は、入力ノードINP2 426およびINN2 428を介して差動信号を受信し、差動出力信号(OUTP2 - OUTN2)を提供する。第2のステージ404の出力は、更なる他のステージの入力に接続され得るか、または信号正規化回路の出力に接続され得る。

#### 【0056】

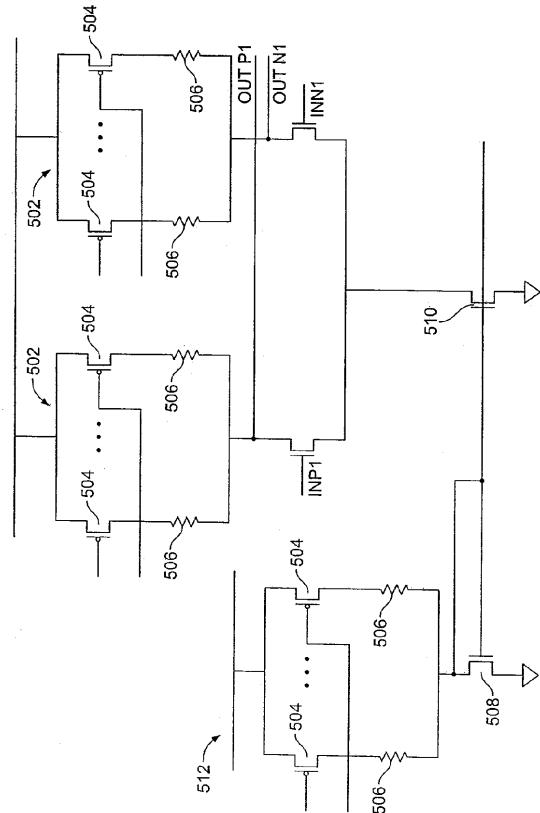

図5は、可変抵抗および可変電流源の回路インプリメンテーションが示される図4の信号正規化回路の第1のステージの実施形態を示す。一般に、可変抵抗は、スイッチおよび抵抗の直列、並列、および/または他の配置によってインプリメントされ得る。図5は、並列配置の各ブランチがスイッチ504の開閉によって、除外または含まれ得る抵抗502の並列配置を示す。一実施形態において、各ブランチにおける抵抗506は、実質的に同等の値を有し得る。他の実施形態においては、配置502内の2つ以上の抵抗506は、実質的に異なる値を有し得る。スイッチ504はpチャネル電界効果トランジスタとして示されるが、他の種類のデバイスまたは回路は、スイッチング能力を提供するために使用され得る。示された可変抵抗回路502は、本発明の範囲を限定せず、他の配置および/または種類のスイッチおよび抵抗が使用され得る。図9に関連して本明細書中に後で説明されるように、スイッチ504は、プログラマブルロジックデバイス(「PLD」)によって動作され得る。

20

30

#### 【0057】

図5の示された実施形態において、図4の可変電流源416は、電流ミラー回路を使用してインプリメントされる。電流ミラー回路およびその動作は当業者に理解されるが、簡単な説明がここに提供される。電流ミラー回路において、基準電流は、基準側FET 508を介して流れるために確立され得る。基準側FET 508のゲートおよびドレインノードは接続され得、基準側FET 508のゲートノードは、「ミラーリング」FET 510のゲートノードにも接続される。この構成によって、ミラー電流は、ミラーリングFET 510を介して流れるため確立され得る。ミラーリングFET 510を介して流れるミラー電流の量は、基準側FET 508を介して流れる基準電流の量と同じである場合も同じでない場合もある。ミラー電流と基準電流との間の関係は、特に、基準側FET 508およびミラーリングFET 510のサイズにより得る。基準電流が変化した場合、ミラー電流は、関係に基づいてそれ相応に変化する。図4の信号正規化回路400の各ステージ(例えば、402、404、図4)は、ミラーリングFETのゲートノードが基準側FET 508のゲートノードに接続される、ミラーリングFETを含み得る。各ミラーリングFET(例えば、510)のサイズは、基準電流に対する、各ステージにおけるミラー電流の関係を決定できる。

40

#### 【0058】

図5の示された実施形態において、基準電流は、可変抵抗512を使用することによって確立され得る。本明細書中に前述されたように、可変抵抗512は、抵抗506および

50

スイッチ 504 の配置によってインプリメントされ得る。可変抵抗 512 内のスイッチ 504 は、プログラマブルロジックデバイス（図示されない）によって制御され得る。可変電流源の示されたインプリメンテーションは例示的であり、本発明の範囲を限定しない。電流ミラー回路は、電界効果トランジスタよりむしろ複接合（bi-junction）トランジスタを含み得る。他の実施形態において、電流ミラー以外の回路は、電流源を提供するために使用され得る。

#### 【0059】

図 1 を再度参照し、受信器 104 内の制御ブロック 112 の動作が説明される。受信器 104 内の制御ブロック 112 は、等化ブロック 108 および信号正規化ブロック 110 における様々な動作を制御できる。一般に、等化ブロック 108 は、ゲインおよび／または減衰を提供でき、特に 118 の高周波数コンテンツを調節でき、および／または 120 の全般的な周波数コンテンツを調節できる。制御ブロック 112 は、等化ブロック 108 によって提供されるゲインまたは減衰の量を制御できる。一実施形態においては、制御ブロック 112 は、等化ブロック 108 内の周波数コンテンツ 120 の全般的な調整を制御できる。一実施形態においては、制御ブロック 112 は、等化ブロック 108 内の高周波数調節 118 のみを制御できる。等化ブロックは、必要に応じて、低周波数コンテンツ調節を別々に提供できる（図示されない）。制御ブロック 112 は、この低周波数コンテンツ調節を制御する場合もしない場合もある。信号正規化ブロック 110 は、一般に、正規化された信号振幅 114 および／または正規化されたエッジスロープ 116 を提供できる。一実施形態においては、制御ブロック 112 は、正規化された信号振幅 114 および正規化されたエッジスロープ 116 の両方を制御できる。一実施形態においては、制御ブロック 112 は、正規化された信号振幅 114 のみまたは正規化されたエッジスロープ 116 のみを制御できるが、両方ともを制御できない。

#### 【0060】

図 1 に示されるように、制御ブロック 112 は、等化ブロック 108 の出力において等化後信号および信号正規化ブロック 110 の出力において正規化された信号を受信できる。制御ブロック 112 は、これらの出力信号に基づいて、等化ブロック 108 および信号正規化ブロック 110 における動作を制御できる。このようにして、等化ブロック 108 、信号正規化ブロック 110 、および制御ブロック 112 は、フィードバックループを全体として形成する。フィードバックループの動作は、受信器 104 が使用される特定のデバイスまたはアプリケーションによって変化し得る。一例が図 6 に示される。

#### 【0061】

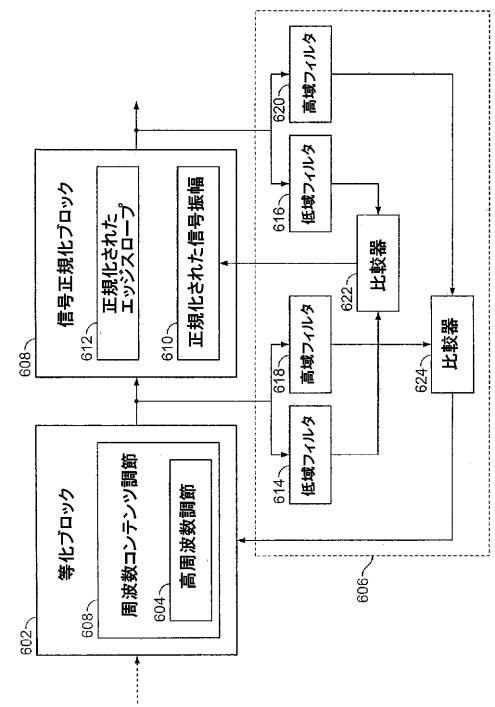

図 6 は、制御された低周波数調節が信号正規化ブロックに提供される、図 1 の受信器 104 の一実施形態を示す。等化ブロック 602 において、高周波数調節 604 および／または全般周波数コンテンツ調節 608 は、制御ブロック 606 によって制御され得る。等化ブロック 602 が別々の低周波数調節（図示されない）を提供した場合、別々の低周波数調節は、制御ブロック 606 によって制御されない。信号正規化ブロック 608 においては、正規化された信号振幅 610 は、制御ブロック 606 によって制御される。信号正規化ブロック 608 は、制御ブロック 606 によって制御される場合もされない場合もある正規化されたエッジスロープ 612 を提供できる。この構成において、制御された低周波数調節は、信号正規化ブロック 608 において提供され（正規化された信号振幅 610 を介して）、等化ブロックにおける別々の低周波数調節がある場合、それらは制御されない。この構成を使用することに対する利益として、等化ブロック 602 の動作を簡単にし、および／または等化ブロック 602 において低周波数成分信号と比べて高周波数成分信号に対してより多いゲインを得ることが挙げられるが、それらに限定されない。

#### 【0062】

示された実施形態において、制御ブロック 606 は、高域および低域フィルタ 614 ~ 620 を含む。一実施形態においては、低域フィルタ 614 、 616 に対するコーナ周波数は、その周波数より低い周波数では、低域フィルタが実質的に減衰を与えず、その周波数より高い周波数では、低域フィルタが減衰を与えるような周波数になり得る。同様に、

高域フィルタ 618、620に対するコーナ周波数は、その周波数よりも高い周波数では、高域フィルタが実質的に減衰を与えず、その周波数より低い周波数では、高域フィルタが減衰を与えるような周波数になり得る。減衰は、例えば、20 dB / デカードの下がりレートまたは20 dB / デカードより高い下がりレートのように、異なるレートにおいて生じ得る。高域フィルタ 618、620および低域フィルタ 614、616に対するコーナ周波数は、同じになり得、もしくは実質的に同じ周波数または実質的に異なる周波数になり得る。高域および低域フィルタ 614～620のコーナ周波数は、一定または調節可能になり得る。

#### 【0063】

一実施形態において、コーナ周波数は、「高周波数」としてカテゴライズされる周波数および「低周波数」としてカテゴライズされる周波数を規定する境界周波数に対応し得る。例えば、低域フィルタ 614、616に対するコーナ周波数は、その周波数より低い周波数が「低周波数」として特徴付けられるような周波数になり得る。同様に、高域フィルタ 618、620に対するコーナ周波数は、その周波数よりも高い周波数が「高周波数」として特徴付けられるような周波数になり得る。

10

#### 【0064】

一実施形態において、高域および低域フィルタ 614～620に対するコーナ周波数は、予め決定され得、変化または調節可能でない場合もある。一実施形態において、高域および低域フィルタ 614～620に対するコーナ周波数は調節可能になり得、例えば、正規化された信号振幅 610または正規化されたエッジスロープ 612に基づいて調節され得る。本明細書中に前述されたように、正規化された信号振幅 610は、低周波数の特定の範囲の代表であり得、信号正規化ブロック 608の正規化されたエッジスロープ 612は、高周波数の特定範囲を表し得る。一実施形態においては、低域フィルタ 614、616に対するコーナ周波数は、正規化された信号振幅 610に基づいて調節され得る。低域フィルタ 614、616のコーナ周波数は、正規化された信号振幅 610によって表される周波数コンテンツのかなりの部分が、コーナ周波数より低くなるように選ばれ得る。このようにして、正規化された信号振幅 610は、「低周波数」としてカテゴライズされる周波数の範囲を決定できる。一実施形態において、高域フィルタ 618、620に対するコーナ周波数は、正規化されたエッジスロープ 612に基づき得る。例えば、高域フィルタ 618、620のコーナ周波数は、正規化されたエッジスロープ 612によって表される周波数コンテンツのかなりの部分が、コーナ周波数より高くなるように調節され得る。このようにして、正規化されたエッジスロープ 612は、「高周波数」としてカテゴライズされる周波数の範囲を決定できる。調節可能コーナ周波数は、図 7～図 9に関連して本明細書中により詳細において説明される。

20

30

40

#### 【0065】

図 6 の示された実施形態において、制御ブロック 606は、等化後信号の低周波数コンテンツを提供する第 1 の低域フィルタ 614 および正規化された信号の低周波数コンテンツを提供する第 2 の低域フィルタ 616 を含む。低周波数コンテンツ比較器 622 は、2つの低域フィルタ 614、616 の出力を比較する。一実施形態においては、低周波数コンテンツ比較器 622 は、低域フィルタ 614、616 の出力のエネルギーレベルを計測でき、かつエネルギーレベルを実質的に均等化するように、信号正規化ブロック 608 内の正規化された信号振幅 610 を調節できる。この動作によって、信号正規化ブロック 608 の正規化された信号振幅 610 は、正規化された信号の低周波数コンテンツおよび等化後信号の低周波数コンテンツを実質的に均等化するように制御され得る。したがって、この動作は、低周波数コンテンツが通信経路（106、図 1）によって減衰されないこと、または補償を必要としないようにのみ減衰されることを想定し得る。

#### 【0066】

示された制御ブロック 606 は、等化後信号の高周波数コンテンツを提供する第 1 の高域フィルタ 618 および正規化された信号の高周波数コンテンツを提供する第 2 の高域フ

50

イルタ 620 をも含む。高周波数コンテンツ比較器 624 は、2つの高域フィルタ 618、620 の出力を比較する。一実施形態において、高周波数コンテンツ比較器 624 は、高域フィルタ 618、620 の出力のエネルギーレベルを計測でき、かつエネルギーレベルを実質的に均等化するように等化ブロック 602 を制御できる。この動作によって、等化ブロック 602 における周波数コンテンツ調節 608 および / または高周波数調節 604 は、等化後信号内の高周波数コンテンツおよび正規化された信号内の高周波数コンテンツを実質的に均等化するように調節され得る。

#### 【0067】

制御ブロック 606 内の比較器 622、624 は、様々な方法においてインプリメントされ得る。一実施形態において、比較器 622、624 は、信号のエネルギーレベルを計測するための回路網を含み得る。比較器 622、624 は、フィルタの出力を整流するための回路網を含み得る。整流された信号は、演算増幅器回路のようなエラー増幅器によって比較され得、エラー増幅器は比較に基づいて制御信号を生成できる。一実施形態においては、エラー増幅器は、アナログ制御信号を生成できる。一実施形態においては、アナログ制御信号は、アナログ - デジタル変換器によってデジタル信号に変換され得るか、またはエラー増幅器は、デジタル制御信号を生成できる。一実施形態においては、デジタル信号は、プログラマブルロジックデバイス (PLD) に通信され得る。制御動作に対する PLD の使用は、図 9 に関連して本明細書中に説明される。本明細書中に説明される実施形態は、例示的であり、限定するものではない。当業者は、本明細書において説明される比較器能力をインプリメントするために様々な回路が存在することを認識するであろう。

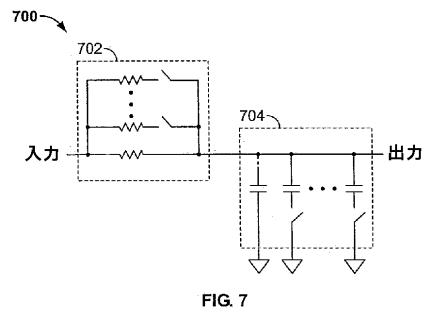

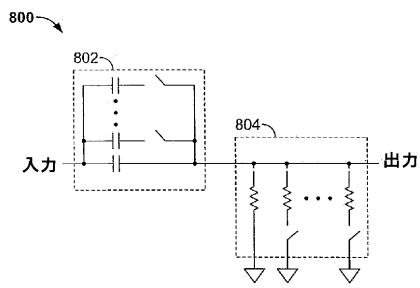

#### 【0068】

図 7 を参照すると、調節可能キャパシタンス 704 に接続される調節可能抵抗 702 を含む低域フィルタ 700 の一実施形態が示される。同様に、図 8 は、調節可能抵抗 804 に接続される調節可能キャパシタンス 802 を含む高域フィルタ 800 の一実施形態を示す。調節可能抵抗 702、804 は、抵抗およびスイッチの並列、直列、および / または他の配置を使用してインプリメントされ得る。調節可能キャパシタンス 704、802 は、キャパシタンスおよびスイッチの並列、直列、および / または他の配置を使用してインプリメントされ得る。スイッチは、所望の抵抗および / または所望のキャパシタンスを提供するためにプログラマブルロジックデバイス (図示されない) によって開けられ得るか、または閉じられ得る。抵抗および / またはキャパシタンスを調節することによって、図 7 ~ 図 8 におけるフィルタ 700、800 のコーナ周波数は変更され得る。

#### 【0069】

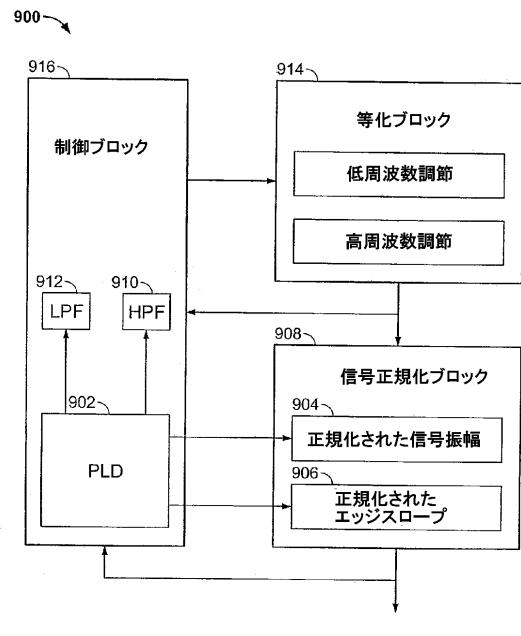

図 9 は、プログラマブルロジックデバイス (PLD) 902 が制御動作を実行するために使用され得る、図 1 の制御ブロック 112 (図 6 の制御ブロック 606 も) の一実施形態を示す。図 5 および図 7 ~ 図 8 に示されるもののように、PLD 902 は、調節可能抵抗または調節可能キャパシタンスにおけるスイッチに接続され得る。更に、PLD 902 は、抵抗および / またはキャパシタンスを調節するようにプログラムされ得る。例えば、図 5 に関連して、PLD 902 は、正規化されたエッジスロープを提供するために出力ノード OUTP1 および OUTN1 に接続される抵抗 502 を調節するようにプログラムされ得る。PLD は、正規化された信号振幅を提供するために電流ミラー内の抵抗 512 を調節するようにもプログラムされ得る。他の例としては、図 7 ~ 図 8 に関連して、PLD 802 は、所望のコーナ周波数を提供するためにフィルタ 700、800 内の抵抗 702、804 および / またはキャパシタンス 704、802 を調節するようにプログラムされ得る。一実施形態においては、PLD 902 が信号正規化ブロック 908 内の正規化されたエッジスロープ 904 および / または正規化された信号振幅 906 を変化させた場合、PLD 902 は、それに応じて、制御ブロック内の高域および低域フィルタ 910、912 のコーナ周波数も変更できる。制御ブロック 916 内の PLD 902 または他の構成要素は、制御ブロック 916 内のフィルタ 910、912 のコーナ周波数に基づいて、等化ブロック 914 における周波数コンテンツ調節を制御できる。

#### 【0070】

10

20

30

40

50

図9のPLD902は制御ブロック916の一部として示されるが、制御ブロック916は、PLD902が他の目的のためにも使用され得るように、PLDリソースの一部のみを使用し得る。したがって、PLD902は、物理的に、制御ブロック916の一部になる必要はない。図9は例示的であり、回路構成要素の他の配置および数は、本明細書中に説明される能力を提供するために使用され得る。

#### 【0071】

したがって、これまでに説明された事項は、通信経路から受信される信号を調節するためのシステムおよび方法である。受信器は、信号の周波数成分の少なくとも一部を減衰する通信経路から信号を受信できる。受信器は、受信された信号の周波数コンテンツの少なくとも一部を調節する等化ブロック、正規化された信号振幅および／または正規化されたエッジスロープを提供する信号正規化ブロック、および制御ブロックを含み得る。制御ブロックは、等化ブロック内の周波数コンテンツ調節および／または信号正規化ブロック内の正規化された信号振幅または正規化されたエッジスロープを制御できる。一実施形態においては、制御ブロックは、高周波数に対する等化ブロックにおける周波数調節を制御するが、低周波数に対しては制御しない。低周波数調節に対して、制御ブロックは、信号正規化ブロック内の正規化された信号振幅を制御する。このようにして、低周波数コンテンツに対する制御された調節は、信号正規化ブロックにおいて実行される。当業者は、本明細書中に説明および／または図示された任意の実施形態が例示的であり、上記の特許請求の範囲によって規定されるような発明の範囲を限定しないことを理解するであろう。

#### 【0072】

以上のように、本発明の好ましい実施形態を用いて本発明を例示してきたが、本発明は、この実施形態に限定して解釈されるべきものではない。本発明は、特許請求の範囲によってのみその範囲が解釈されるべきであることが理解される。当業者は、本発明の具体的な好ましい実施形態の記載から、本発明の記載および技術常識に基づいて等価な範囲を実施することができる事が理解される。

#### 【0073】

通信経路から受信される信号を調節するためのシステムおよび方法が開示される。受信器は、信号の周波数成分の少なくとも一部を減衰する通信経路から信号を受信できる。受信器は、受信される信号の周波数コンテンツの少なくとも一部を調節する等化ブロック、正規化された信号振幅および／または正規化されたエッジスロープを提供する信号正規化ブロック、および制御ブロックを含み得る。一実施形態においては、制御ブロックは、高周波数に対する等化ブロックにおける周波数調節を制御するが、低周波数に対しては制御しない。低周波数調節に対して、制御ブロックは、信号正規化ブロック内の正規化された信号振幅を制御する。このようにして、低周波数コンテンツに対する制御された調節は、信号正規化ブロックにおいて実行される。

#### 【図面の簡単な説明】

#### 【0074】

【図1】本発明の一局面に従う例示的通信システムのブロック図である。

【図2】デジタル信号内の例示的成分信号の図である。

【図3】例示的減衰およびゲインカーブのグラフ図である。

【図4】図1の信号正規化ブロックの一実施形態の回路図である。

【図5】図4の信号正規化回路におけるステージの一実施形態の回路図である。

【図6】図1の受信器内の一例示的制御配置のブロック図である。

【図7】例示的低域フィルタの回路図である。

【図8】例示的高域フィルタの回路図である。

【図9】プログラマブルロジックデバイスを含む受信器の一実施形態のブロック図である。

#### 【符号の説明】

#### 【0075】

- 1 0 4 受信器

1 0 6 通信経路

1 0 8 等化ブロック

1 1 0 信号正規化ブロック

1 1 2 制御ブロック

1 1 4 正規化された信号振幅

1 1 6 正規化されたエッジスロープ

【図 1】

【図 2】

FIG. 2

【図3】

FIG. 3

【図5】

FIG. 5

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 ウィルスン ウォン

アメリカ合衆国 カリフォルニア 94134, サンフランシスコ, フェルトン ストリート

301

(72)発明者 ラケシュ エイチ. パテル

アメリカ合衆国 カリフォルニア 95014, クバチーノ, ラス オンダス コート 20

087

(72)発明者 セルゲイ シューマレヴ

アメリカ合衆国 カリフォルニア 94579, サン リンド口, ロッキー ポイント コ

ート 2328

(72)発明者 ティン エイチ. レイ

アメリカ合衆国 カリフォルニア 95127, サン ノゼ, バーナイス アベニュー 33

36

審査官 東 昌秋

(56)参考文献 特表2005-503093(JP,A)

米国特許出願公開第2004/0022303(US,A1)

米国特許第6819166(US,B1)

米国特許第6584151(US,B1)

特開昭54-32049(JP,A)

特開昭62-210740(JP,A)

特開平4-310010(JP,A)

S.GONDI et al., A 10Gb/s CMOS adaptive equalizer for backplane applications, 2005 IEEE

International Solid-State Circuits Conference (ISSCC), Digest of Technical Papers, IE

EE, 2005年 2月, vol.1, pp.328,329,601

(58)調査した分野(Int.Cl., DB名)

H04B 3/04 - 3/18

H04B 7/005

H04L 25/00 - 25/66