(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-328900

(P2007-328900A)

(43) 公開日 平成19年12月20日(2007.12.20)

(51) Int.C1.

G 11 C 11/413 (2006.01)

F 1

G 11 C 11/34

335 A

テーマコード(参考)

5 B 015

審査請求 未請求 請求項の数 4 O L (全 10 頁)

(21) 出願番号 特願2007-28839 (P2007-28839)

(22) 出願日 平成19年2月8日 (2007.2.8)

(31) 優先権主張番号 特願2006-129832 (P2006-129832)

(32) 優先日 平成18年5月9日 (2006.5.9)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

(74) 代理人 100115691

弁理士 藤田 篤史

最終頁に続く

(54) 【発明の名称】スタティック型半導体記憶装置

## (57) 【要約】

【課題】スタティック型半導体記憶装置における書き込み動作の確実性を保証する電源及び基板電位の制御技術を提供する。

【解決手段】書き込み完了タイミング検出用のダミーメモリセル20をメモリセル10のレプリカとして設け、メモリセル10の電源制御及び基板電位制御により書き込み動作の補助を行う際に、ダミーメモリセル20の情報をもとに電圧制御回路30にて書き込み補助動作の終了タイミングを決定する。例えば、電圧制御回路30は、メモリセル10へのデータ書き込み動作時に、PチャネルMOS負荷トランジスタ用ソース電源101をプルダウントランジスタ37により降圧する書き込み補助動作を行った後、ダミーメモリセル20へのデータ書き込み動作の完了を検知した時点で書き込み補助動作を終了して前記ソース電源101の電圧をプルアップトランジスタ38により元に戻すように制御する。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

1対のPチャネルMOS負荷トランジスタと、1対のNチャネルMOS転送トランジスタと、1対のNチャネルMOS駆動トランジスタとを有するメモリセルと、

1対のPチャネルMOS負荷トランジスタと、1対のNチャネルMOS転送トランジスタと、1対のNチャネルMOS駆動トランジスタとを有するダミーメモリセルと、

前記メモリセルへのデータ書き込み動作時に、前記メモリセル及び前記ダミーメモリセルの双方の前記PチャネルMOS負荷トランジスタ用のソース電源を降圧する書き込み補助動作と、前記メモリセル及び前記ダミーメモリセルの双方の前記NチャネルMOS駆動トランジスタ用のソース電源を昇圧する書き込み補助動作と、前記メモリセル及び前記ダミーメモリセルの双方の前記PチャネルMOS負荷トランジスタの基板電位を上げる書き込み補助動作と、前記メモリセル及び前記ダミーメモリセルの双方の前記NチャネルMOS駆動トランジスタの基板電位を上げる書き込み補助動作と、前記メモリセル及び前記ダミーメモリセルの双方の前記NチャネルMOS駆動トランジスタの基板電位を下げる書き込み補助動作とのうち少なくとも1つの書き込み補助動作を行った後、前記ダミーメモリセルへのデータ書き込み動作の完了を検知した時点で前記書き込み補助動作を終了するよう<sup>10</sup>に制御する電圧制御回路とを備えたことを特徴とするスタティック型半導体記憶装置。

## 【請求項 2】

請求項1記載のスタティック型半導体記憶装置において、

1対のPチャネルMOS負荷トランジスタと、1対のNチャネルMOS転送トランジスタと、1対のNチャネルMOS駆動トランジスタとを有する他のダミーメモリセルを更に備え、

前記電圧制御回路は、前記複数のダミーメモリセルの各々へのデータ書き込み動作の完了を示す複数の信号の論理演算結果に基づいて前記書き込み補助動作の終了タイミングを決定することを特徴とするスタティック型半導体記憶装置。

## 【請求項 3】

請求項1記載のスタティック型半導体記憶装置において、

1対のPチャネルMOS負荷トランジスタと、1対のNチャネルMOS転送トランジスタと、1対のNチャネルMOS駆動トランジスタとを有し、かつ1本のワード線を前記メモリセルと共有する他のメモリセルを更に備え、

前記電圧制御回路は、前記ダミーメモリセルを利用して前記複数のメモリセルの各々に同じ書き込み補助動作を行うことを特徴とするスタティック型半導体記憶装置。

## 【請求項 4】

請求項1記載のスタティック型半導体記憶装置において、

1対のPチャネルMOS負荷トランジスタと、1対のNチャネルMOS転送トランジスタと、1対のNチャネルMOS駆動トランジスタとを有し、かつ1対のピット線を前記メモリセルと共有する他のメモリセルを更に備え、

前記電圧制御回路は、前記ダミーメモリセルを利用して前記複数のメモリセルの各々に同じ書き込み補助動作を行うことを特徴とするスタティック型半導体記憶装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、スタティック型半導体記憶装置の信頼性向上、高速化、低消費電力化の技術に関するものである。

## 【背景技術】

## 【0002】

各々6トランジスタ構成の多数のメモリセルを有するCMOS (complementary metal oxide semiconductor) 型のSRAM (static random access memory) が知られている。各メモリセルは、1対のPチャネルMOS負荷トランジスタと、1対のNチャネルMOS転送トランジスタと、1対のNチャネルMOS駆動トランジスタとで構成される。

10

20

30

40

50

**【 0 0 0 3 】**

近年、電源電圧の低下や、トランジスタサイズのシュリンクに伴い、メモリセルを構成する各トランジスタの能力が低下傾向にあり、書き込み速度が遅くなってしまっている。この対策として、メモリセルへのデータの書き込み動作時に、この書き込み動作の補助をする技術が種々提案されている。例えば、書き込みサイクルの間だけメモリセル中の1対のPチャネルMOS負荷トランジスタ用のソース電源を降圧するように、当該PチャネルMOS負荷トランジスタのソースをフローティングにするという書き込み補助技術が知られている（非特許文献1参照）。

【非特許文献1】M. Yamaoka et al., "Low-Power Embedded SRAM Modules with Expanded Margins for Writing," ISSCC Digest of Technical Papers, pp.480-481, Feb., 2005

10

**【発明の開示】****【発明が解決しようとする課題】****【 0 0 0 4 】**

従来のSRAMでは、ワースト条件で正常書き込みを保証するように、書き込み補助のために例えば負荷トランジスタ用ソース電源をどの程度降圧するのかや、書き込み補助動作を実行する期間の長さが、一定のマージンを見込んで予めシミュレーションにより決定されていた。このマージンが大きすぎると、電圧を通常状態に戻すのに要する充放電電流分の消費電力が無駄に必要になったり、電圧を通常状態に戻すためのドライバのサイズを余分に大きくすることが必要になったりする。また、書き込み補助動作がデータを書き込まないメモリセルのリテンションに影響する場合には、信頼性の低下に繋がる。

20

**【 0 0 0 5 】**

本発明の目的は、スタティック型半導体記憶装置における書き込み動作の確実性を保証する電源及び基板電位の制御技術を提供することにある。

**【課題を解決するための手段】****【 0 0 0 6 】**

上記課題を解決するため、本発明によれば、書き込み完了タイミング検出用のダミーメモリセルをメモリセルのレプリカとして設け、メモリセルの電源制御及び基板電位制御により書き込み動作の補助を行う際に、ダミーメモリセルの情報をもとに書き込み補助動作の終了タイミングを決定する。

30

**【 0 0 0 7 】**

具体的に説明すると、本発明によれば、メモリセルへのデータ書き込み動作時に、メモリセル及びダミーメモリセルの双方のPチャネルMOS負荷トランジスタ用のソース電源を降圧する書き込み補助動作と、メモリセル及びダミーメモリセルの双方のNチャネルMOS駆動トランジスタ用のソース電源を昇圧する書き込み補助動作と、メモリセル及びダミーメモリセルの双方のPチャネルMOS負荷トランジスタの基板電位を上げる書き込み補助動作と、メモリセル及びダミーメモリセルの双方のNチャネルMOS転送トランジスタの基板電位を上げる書き込み補助動作と、メモリセル及びダミーメモリセルの双方のNチャネルMOS駆動トランジスタの基板電位を下げる書き込み補助動作とのうち少なくとも1つの書き込み補助動作を行った後、ダミーメモリセルへのデータ書き込み動作の完了を検知した時点で書き込み補助動作を終了する。

40

**【 0 0 0 8 】**

PチャネルMOS負荷トランジスタ用ソース電源を降圧する動作、又はPチャネルMOS負荷トランジスタ基板電位を上げる動作を実行すれば、メモリセル中のPチャネルMOS負荷トランジスタの電流が減少するため、当該メモリセルの2つの記憶ノードを書き込み前の状態に保持する能力が低下する結果、書き込み動作の確実性が向上する。

**【 0 0 0 9 】**

NチャネルMOS転送トランジスタ基板電位を上げる動作を実行すれば、メモリセル中のNチャネルMOS転送トランジスタの電流が増加するため、当該メモリセルの2つの記憶ノードにデータを書き込む能力が向上する結果、書き込み動作の確実性が向上する。

50

## 【0010】

NチャネルMOS駆動トランジスタ用ソース電源を昇圧する動作、又はNチャネルMOS駆動トランジスタ基板電位を下げる動作を実行すれば、メモリセル中のNチャネルMOS駆動トランジスタの電流が減少するため、当該メモリセルの2つの記憶ノードを書き込み前の状態に保持する能力が低下する結果、書き込み動作の確実性が向上する。

## 【0011】

しかも、本発明によれば、ダミーメモリセルへのデータ書き込み動作の完了を検知した時点で書き込み補助動作を終了することとしたので、書き込み動作の補助に必要な最小限の電圧調整幅が得られる。

## 【発明の効果】

10

## 【0012】

本明によれば、書き込み動作の補助に必要な最小限の電圧調整幅が得られるため、書き込み動作の安定性を高め、かつ低消費電力化、データ保持特性の向上を実現できる。

## 【発明を実施するための最良の形態】

## 【0013】

以下、図1～図4を用いて、本発明の実施形態を詳細に説明する。

## 【0014】

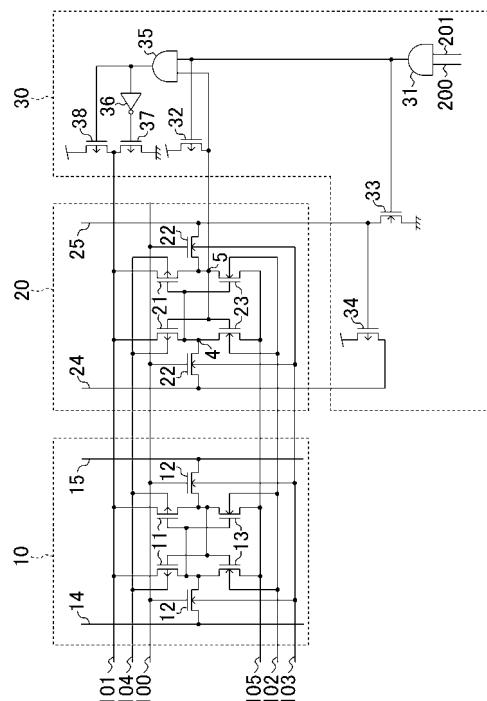

図1は、本発明に係るスタティック型半導体記憶装置の構成例を示している。図1において、10はメモリセル、20はダミーメモリセル、30は電圧制御回路である。

## 【0015】

メモリセル10は、6トランジスタ構成のSRAMメモリセルであって、1対のPチャネルMOS負荷トランジスタ11と、1対のNチャネルMOS転送トランジスタ12と、1対のNチャネルMOS駆動トランジスタ13とを有する。一方のPチャネルMOS負荷トランジスタ11のドレインと一方のNチャネルMOS駆動トランジスタ13のドレインとの接続点が第1の記憶ノードを、他方のPチャネルMOS負荷トランジスタ11のドレインと他方のNチャネルMOS駆動トランジスタ13のドレインとの接続点が第2の記憶ノードをそれぞれ構成する。第1の記憶ノードは一方のNチャネルMOS転送トランジスタ12を介して一方のビット線14に、第2の記憶ノードは他方のNチャネルMOS転送トランジスタ12を介して他方のビット線15にそれぞれ接続されている。両NチャネルMOS転送トランジスタ12の各々のゲートは、ワード線100に接続されている。両PチャネルMOS負荷トランジスタ11の各々のソースはPチャネルMOS負荷トランジスタ用ソース電源101に、両NチャネルMOS駆動トランジスタ13の各々のソースはNチャネルMOS駆動トランジスタ用ソース電源105にそれぞれ接続されている。また、両PチャネルMOS負荷トランジスタ11の各々のバックゲートはPチャネルMOS負荷トランジスタ基板電位104に、両NチャネルMOS転送トランジスタ12の各々のバックゲートはNチャネルMOS転送トランジスタ基板電位103に、両NチャネルMOS駆動トランジスタ13の各々のバックゲートはNチャネルMOS駆動トランジスタ基板電位102にそれぞれ接続されている。1対のビット線14、15に任意の相補データ信号を供給しつつ、ワード線100をHレベルに設定することにより両NチャネルMOS転送トランジスタ12を導通させれば、当該メモリセル10に任意のデータを書き込むことができる。

20

30

40

40

## 【0016】

ダミーメモリセル20は、メモリセル10のレプリカとして設けられたものであって、メモリセル10と同様に、1対のPチャネルMOS負荷トランジスタ21と、1対のNチャネルMOS転送トランジスタ22と、1対のNチャネルMOS駆動トランジスタ23とを有する。一方のPチャネルMOS負荷トランジスタ21のドレインと一方のNチャネルMOS駆動トランジスタ23のドレインとの接続点が第1の記憶ノード4を、他方のPチャネルMOS負荷トランジスタ21のドレインと他方のNチャネルMOS駆動トランジスタ23のドレインとの接続点が第2の記憶ノード5をそれぞれ構成する。第1の記憶ノード4は一方のNチャネルMOS転送トランジスタ22を介して一方のダミービット線24

50

に、第2の記憶ノード5は他方のNチャネルMOS転送トランジスタ22を介して他方のダミービット線25にそれぞれ接続されている。両NチャネルMOS転送トランジスタ22の各々のゲートは、前記ワード線100に接続されている。両PチャネルMOS負荷トランジスタ21の各々のソースは前記PチャネルMOS負荷トランジスタ用ソース電源101に、両NチャネルMOS駆動トランジスタ23の各々のソースは前記NチャネルMOS駆動トランジスタ用ソース電源105にそれぞれ接続されている。また、両PチャネルMOS負荷トランジスタ21の各々のバックゲートは前記PチャネルMOS負荷トランジスタ基板電位104に、両NチャネルMOS転送トランジスタ22の各々のバックゲートは前記NチャネルMOS転送トランジスタ基板電位103に、両NチャネルMOS駆動トランジスタ23の各々のバックゲートは前記NチャネルMOS駆動トランジスタ基板電位102にそれぞれ接続されている。

10

#### 【0017】

電圧制御回路30は、メモリセル10へのデータ書き込み動作時に、PチャネルMOS負荷トランジスタ用ソース電源101を降圧する書き込み補助動作を行った後、ダミーメモリセル20へのデータ書き込み動作の完了を検知した時点で書き込み補助動作を終了するように制御する回路であって、第1のANDゲート31と、PチャネルMOSリセットトランジスタ32と、NチャネルMOS電位設定トランジスタ33と、PチャネルMOS電位設定トランジスタ34と、第2のANDゲート35と、インバータ回路36と、PチャネルMOSプルダウントランジスタ37と、PチャネルMOSプルアップトランジスタ38とを有する。

20

#### 【0018】

第1のANDゲート31は、クロック信号200と書き込みイネーブル信号201とを受け取り、その出力をPチャネルMOSリセットトランジスタ32のゲートと、NチャネルMOS電位設定トランジスタ33のゲートと、第2のANDゲート35の第1入力とに供給する。

#### 【0019】

PチャネルMOSリセットトランジスタ32は、メモリセル10へのデータ書き込み前に、すなわち第1のANDゲート31の出力がLレベルである間に導通して、ダミーメモリセル20の第2の記憶ノード5をHレベルにリセットするためのトランジスタである。この際、当該ダミーメモリセル20の第1の記憶ノード4は自動的にLレベルにリセットされる。

30

#### 【0020】

NチャネルMOS電位設定トランジスタ33は、メモリセル10へのデータ書き込み動作が開始した時点から、すなわち第1のANDゲート31の出力がLレベルからHレベルへ遷移した時点から導通して、一方のダミービット線25の電位をLレベルに設定する。PチャネルMOS電位設定トランジスタ34は、当該ダミービット線25の電位がLレベルに設定された時点から導通して、他方のダミービット線24の電位をHレベルに設定する。つまり、これらの電位設定トランジスタ33, 34は、第1及び第2の記憶ノード4, 5のリセットされた電位を各々反転させるように、ダミーメモリセル20に書き込むべき所定のダミーデータを供給するものである。

40

#### 【0021】

第2のANDゲート35は、ダミーメモリセル20の第2の記憶ノード5の電位を第2入力として受け取り、その出力をインバータ回路36の入力と、PチャネルMOSプルアップトランジスタ38のゲートとに供給する。インバータ回路36は、第2のANDゲート35の出力を反転した信号をPチャネルMOSプルダウントランジスタ37のゲートに供給する。

#### 【0022】

この結果、電圧制御回路30は、通常はPチャネルMOSプルアップトランジスタ38が導通してPチャネルMOS負荷トランジスタ用ソース電源101を高い電圧に保持し、メモリセル10へのデータ書き込み動作が開始して第2のANDゲート35の出力がHレ

50

ベルになるとPチャネルMOSプルダウントランジスタ37が導通してPチャネルMOS負荷トランジスタ用ソース電源101を降圧する書き込み補助動作を開始し、ダミーメモリセル20へのデータ書き込み動作が完了して第2の記憶ノード5の電位がLレベルになると書き込み補助動作を終了してPチャネルMOSプルアップトランジスタ38が再度導通することによりPチャネルMOS負荷トランジスタ用ソース電源101を元の電圧に戻すように動作する。

#### 【0023】

以上のとおり、図1のスタティック型半導体記憶装置によれば、書き込み完了タイミング検出用のダミーメモリセル20をメモリセル10のレプリカとして設け、PチャネルMOS負荷トランジスタ用ソース電源101を降圧する書き込み補助動作を行う際に、ダミーメモリセル20の第2の記憶ノード5の電位をもとに書き込み補助動作の終了タイミングを決定することとしたので、書き込み動作の補助に必要な最小限の電圧調整幅が得られる。この結果、書き込み動作の安定性を高め、かつ低消費電力化、データ保持特性の向上を実現できる。

#### 【0024】

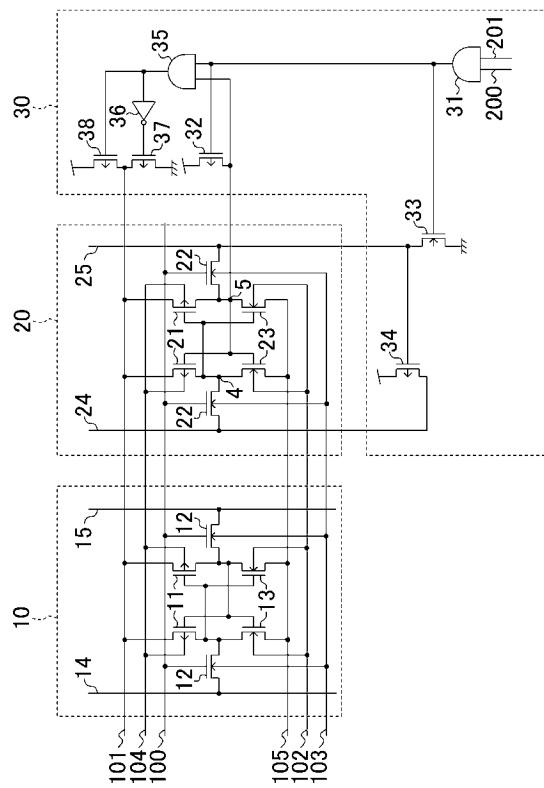

図2は、本発明に係るスタティック型半導体記憶装置の他の構成例を示している。図2によれば、第1及び第2のダミーメモリセル20a, 20bがそれぞれメモリセル10のレプリカとして設けられる。24a及び25aは第1のダミーメモリセル20aの1対のダミービット線であり、24b及び25bは第2のダミーメモリセル20bの1対のダミービット線である。電圧制御回路30は、第1及び第2のダミーメモリセル20a, 20bへのデータ書き込み動作の完了を示す2つの信号に応答して、PチャネルMOS負荷トランジスタ用ソース電源101を降圧する書き込み補助動作の終了タイミングを決定するように構成されている。具体的に説明すると、32a及び32bはPチャネルMOSリセットトランジスタ、33a及び33bはNチャネルMOS電位設定トランジスタ、34a及び34bはPチャネルMOS電位設定トランジスタであり、第2のANDゲート35は、第1のANDゲート31の出力と、第1のダミーメモリセル20aへのデータ書き込み動作の完了を示す信号と、第2のダミーメモリセル20bへのデータ書き込み動作の完了を示す信号とを受け取る3入力ゲートである。

#### 【0025】

図2のスタティック型半導体記憶装置では、第1及び第2のダミーメモリセル20a, 20bへのデータ書き込み動作の完了を示す2つの信号の論理積に基づいて、第2のANDゲート35にて書き込み補助動作の終了タイミングを決定する。メモリセル10並びに第1及び第2のダミーメモリセル20a, 20bの書き込み特性にはばらつきがあるが、第1及び第2のダミーメモリセル20a, 20bのうち遅くデータ書き込み動作が完了するダミーメモリセルの特性に従って書き込み補助動作の終了タイミングが決定されるので、メモリセル10の書き込み動作の確実性が向上する。

#### 【0026】

なお、第1及び第2のダミーメモリセル20a, 20bへのデータ書き込み動作の完了を示す2つの信号の論理和に基づいて書き込み補助動作の終了タイミングを決定することとしてもよい。また、3個以上のダミーメモリセルをメモリセル10のレプリカとして設けてもよい。使用するダミーメモリセルの数を動的に変更することも可能である。

#### 【0027】

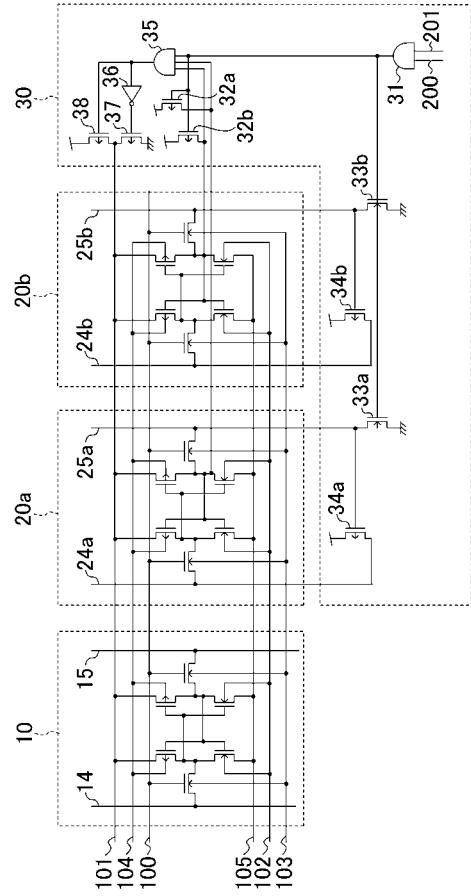

図3は、本発明に係るスタティック型半導体記憶装置の更に他の構成例を示している。図3によれば、1本のワード線100を共有する複数のメモリセル10が第1のワード300を構成し、他の1本のワード線100を共有する複数のメモリセル10が第2のワード301を構成する。第1のワード300と第2のワード301との間で電源系統が分離されており、ワード毎にダミーメモリセル20と電圧制御回路30とが設けられる。ワード毎の電圧制御回路30は、ダミーメモリセル20を利用して複数のメモリセル10の各々に同じ書き込み補助動作を行う。ここに、書き込み補助動作とは、PチャネルMOS負荷トランジスタ用ソース電源101を降圧する動作と、NチャネルMOS駆動トランジ

10

20

30

40

50

タ用ソース電源 105 を昇圧する動作と、P チャネルMOS 負荷トランジスタ基板電位 104 を上げる動作と、N チャネルMOS 転送トランジスタ基板電位 103 を上げる動作と、N チャネルMOS 駆動トランジスタ基板電位 102 を下げる動作とのうち少なくとも 1 つの動作をいう。電圧制御回路 30 は、メモリセル 10 へのデータ書き込み動作時に、ダミーメモリセル 20 へのデータ書き込み動作の完了を検知した時点で書き込み補助動作を終了するように制御する。

#### 【0028】

図 3 によれば、ワード毎に独立した電圧制御回路 30 を設けたので、書き込み補助動作がデータを書き込まないワード（非選択ワード）中のメモリセル 10 のリテンションに悪影響を及ぼすことがない。複数のダミーメモリセルをワード毎に設けてもよい。

10

#### 【0029】

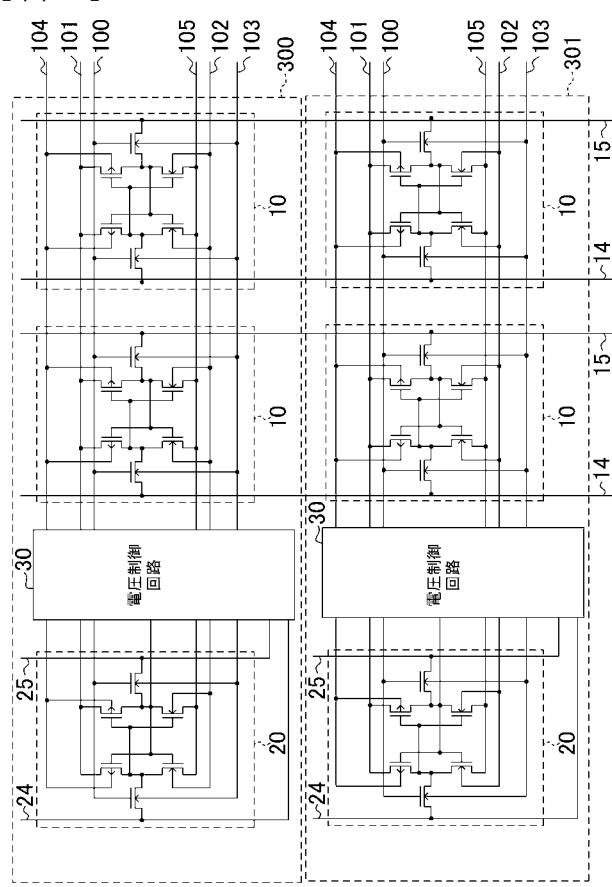

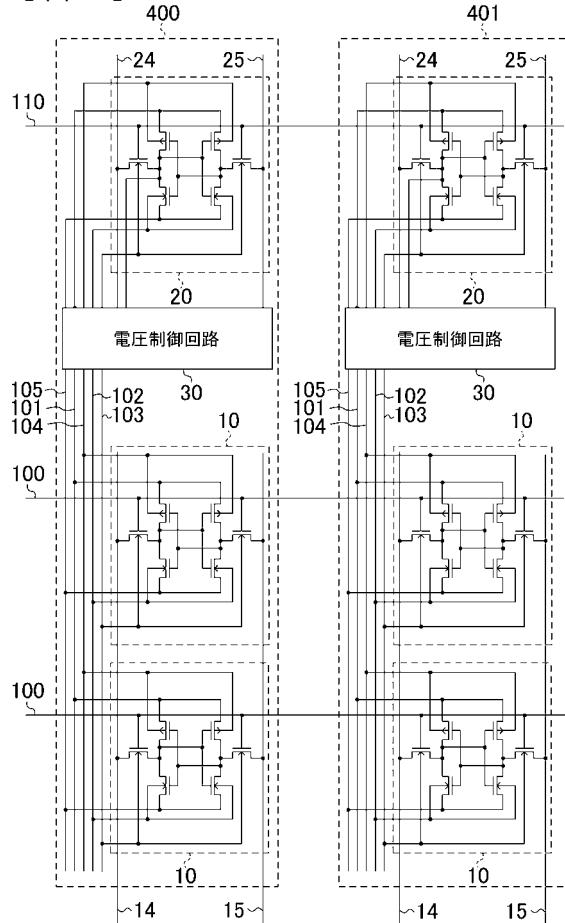

図 4 は、本発明に係るスタティック型半導体記憶装置の更に他の構成例を示している。図 4 によれば、1 対のビット線 14, 15 を共有する複数のメモリセル 10 が第 1 のビット 400 を構成し、他の 1 対のビット線 14, 15 を共有する複数のメモリセル 10 が第 2 のビット 401 を構成する。第 1 のビット 400 と第 2 のビット 401 との間で電源系統が分離されており、ビット毎にダミーメモリセル 20 と電圧制御回路 30 とが設けられる。110 はダミーワード線である。ビット毎の電圧制御回路 30 は、複数のメモリセル 10 の各々に同じ書き込み補助動作を行い、ダミーメモリセル 20 へのデータ書き込み動作の完了を検知した時点で書き込み補助動作を終了するように制御する。

#### 【0030】

図 4 によれば、ビット毎に独立した電圧制御回路 30 を設けたので、書き込み補助動作がデータを書き込まないビット（非選択ビット）中のメモリセル 10 のリテンションに悪影響を及ぼすことがない。複数のダミーメモリセルをビット毎に設けてもよい。複数ビットからなるブロック毎に 1 つの電圧制御回路 30 と、1 又は複数のダミーメモリセルとを設けてもよい。

20

#### 【0031】

以上、図 1 ~ 図 4 を用いて本発明の実施形態を説明したが、種々の変形が可能である。例えば、図 1 中のダミーメモリセル 20 の 1 対の N チャネルMOS 駆動トランジスタ 23 の各々のソース電源を別々に制御することにより、ダミーメモリセル 20 の第 1 及び第 2 の記憶ノード 4, 5 をリセットすることも可能である。メモリセル 10 中の N チャネルMOS 転送トランジスタ 12 のゲートに与える選択信号に先んじて、ダミーメモリセル 20 中の N チャネルMOS 転送トランジスタ 22 のゲートにダミー選択信号を与えるようにしてもよい。ダミーメモリセル 20 中に流れる電流をもとに当該ダミーメモリセル 20 へのデータ書き込み動作の完了を検知することもできる。

30

#### 【0032】

また、ダミーメモリセル 20 において、P チャネルMOS 負荷トランジスタ 21 のソース電源、N チャネルMOS 駆動トランジスタ 23 のソース電源、P チャネルMOS 負荷トランジスタ 21 の閾値、N チャネルMOS 転送トランジスタ 22 の閾値、N チャネルMOS 駆動トランジスタ 23 の閾値のうちいずれかを調整することにより、電圧制御回路 30 の動作タイミングを調整することも可能である。

40

#### 【0033】

また、電圧制御回路 30 における書き込み補助動作の開始タイミング及び終了タイミングを外部信号に応じて調整できるようにしてもよい。電圧制御回路 30 による書き込み補助動作を外部信号に応じて禁止することも可能である。

#### 【産業上の利用可能性】

#### 【0034】

以上説明してきたとおり、本発明に係るスタティック型半導体記憶装置は、書き込み完了タイミング検出用のダミーメモリセルをメモリセルのレプリカとして設け、ダミーメモリセルの情報をもとにメモリセルの書き込み補助動作の終了タイミングを決定することとしたので、書き込み動作の安定性を高め、かつ低消費電力化、データ保持特性の向上を実

50

現でき、いわゆる S R A M 等として有用である。

【図面の簡単な説明】

【0 0 3 5】

【図 1】本発明に係るスタティック型半導体記憶装置の構成例を示す回路図である。

【図 2】本発明に係るスタティック型半導体記憶装置の他の構成例を示す回路図である。

【図 3】本発明に係るスタティック型半導体記憶装置の更に他の構成例を示す回路図である。

【図 4】本発明に係るスタティック型半導体記憶装置の更に他の構成例を示す回路図である。

【符号の説明】

10

【0 0 3 6】

20

30

40

4, 5 ダミーメモリセルの記憶ノード

1 0 メモリセル

1 1 P チャネルM O S 負荷トランジスタ

1 2 N チャネルM O S 転送トランジスタ

1 3 N チャネルM O S 駆動トランジスタ

1 4, 1 5 ビット線

2 0, 2 0 a, 2 0 b ダミーメモリセル

2 1 P チャネルM O S 負荷トランジスタ

2 2 N チャネルM O S 転送トランジスタ

2 3 N チャネルM O S 駆動トランジスタ

2 4, 2 5 ダミービット線

2 4 a, 2 5 a ダミービット線

2 4 b, 2 5 b ダミービット線

3 0 電圧制御回路

3 1, 3 5 A N D ゲート

3 2, 3 2 a, 3 2 b P チャネルM O S リセットトランジスタ

3 3, 3 3 a, 3 3 b N チャネルM O S 電位設定トランジスタ

3 4, 3 4 a, 3 4 b P チャネルM O S 電位設定トランジスタ

3 6 インバータ回路

3 7 P チャネルM O S プルダウントランジスタ

3 8 P チャネルM O S プルアップトランジスタ

1 0 0 ワード線

1 0 1 P チャネルM O S 負荷トランジスタ用ソース電源

1 0 2 N チャネルM O S 駆動トランジスタ基板電位

1 0 3 N チャネルM O S 転送トランジスタ基板電位

1 0 4 P チャネルM O S 負荷トランジスタ基板電位

1 0 5 N チャネルM O S 駆動トランジスタ用ソース電源

1 1 0 ダミーワード線

2 0 0 クロック信号

2 0 1 書き込みイネーブル信号

3 0 0, 3 0 1 ワード

4 0 0, 4 0 1 ビット

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 小池 剛

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 金原 旭成

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ターム(参考) 5B015 HH03 JJ03 JJ24 KA06 KB64 KB66 KB72 KB88