(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4265865号

(P4265865)

(45) 発行日 平成21年5月20日(2009.5.20)

(24) 登録日 平成21年2月27日(2009.2.27)

(51) Int.Cl.

F 1

H03F 3/34 (2006.01)

H03F 3/45 (2006.01)H03F 3/34

H03F 3/45A

A

請求項の数 4 (全 14 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2000-279474 (P2000-279474) |

| (22) 出願日  | 平成12年9月14日 (2000.9.14)       |

| (65) 公開番号 | 特開2002-94341 (P2002-94341A)  |

| (43) 公開日  | 平成14年3月29日 (2002.3.29)       |

| 審査請求日     | 平成18年8月22日 (2006.8.22)       |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 308014341<br>富士通マイクロエレクトロニクス株式会社<br>東京都新宿区西新宿二丁目7番1号 |

| (74) 代理人  | 100117385<br>弁理士 田中 裕人                               |

| (72) 発明者  | 安河内 克之<br>愛知県春日井市高蔵寺町二丁目1844番<br>2 富士通ヴィエルエスアイ株式会社内  |

審査官 儀同 孝信

最終頁に続く

(54) 【発明の名称】能動負荷回路

## (57) 【特許請求の範囲】

## 【請求項 1】

電流入力側トランジスタにおける第1入力端子に差動入力電流の一方の入力電流を入力し、電流出力側トランジスタにおける第1出力端子から差動出力電流の一方の出力電流を出力する第1カレントミラー回路と、

電流入力側トランジスタにおける第2入力端子に差動入力電流の他方の入力電流を入力し、電流出力側トランジスタにおける第2出力端子から差動出力電流の他方の出力電流を出力する第2カレントミラー回路と、

前記第1カレントミラー回路の電流入力側トランジスタにおける基準電位接続端子と前記第2カレントミラー回路の電流出力側トランジスタにおける基準電位接続端子とに一端を接続し、他端を基準電位に接続する第1インピーダンス回路と、

前記第2カレントミラー回路の電流入力側トランジスタにおける基準電位接続端子と前記第1カレントミラー回路の電流出力側トランジスタにおける基準電位接続端子とに一端を接続し、他端を基準電位に接続する第2インピーダンス回路とを備え、

前記第1インピーダンス回路は第1MOSトランジスタを有し、前記第2インピーダンス回路は第2MOSトランジスタを有し、

前記第1MOSトランジスタのゲート端子が前記第2カレントミラー回路の第2入力端子に、前記第2MOSトランジスタのゲート端子が前記第1カレントミラー回路の第1入力端子に接続されている

ことを特徴とする能動負荷回路。

10

20

**【請求項 2】**

電流入力側トランジスタにおける第1入力端子に差動入力電流の一方の入力電流を入力し、電流出力側トランジスタにおける第1出力端子から差動出力電流の一方の出力電流を出力する第1カレントミラー回路と、

電流入力側トランジスタにおける第2入力端子に差動入力電流の他方の入力電流を入力し、電流出力側トランジスタにおける第2出力端子から差動出力電流の他方の出力電流を出力する第2カレントミラー回路と、

前記第1カレントミラー回路の電流入力側トランジスタにおける基準電位接続端子と前記第2カレントミラー回路の電流出力側トランジスタにおける基準電位接続端子とに一端を接続し、他端を基準電位に接続する第1インピーダンス回路と、

10

前記第2カレントミラー回路の電流入力側トランジスタにおける基準電位接続端子と前記第1カレントミラー回路の電流出力側トランジスタにおける基準電位接続端子とに一端を接続し、他端を基準電位に接続する第2インピーダンス回路とを備え、

前記第1インピーダンス回路は第1ジャンクションFETを有し、前記第2インピーダンス回路は第2ジャンクションFETを有し、

前記第1ジャンクションFETのゲート端子が前記第2カレントミラー回路の第2入力端子に、前記第2ジャンクションFETのゲート端子が前記第1カレントミラー回路の第1入力端子に接続されていることを特徴とする能動負荷回路。

**【請求項 3】**

前記第1インピーダンス回路は第1抵抗素子を有し、前記第2インピーダンス回路は第2抵抗素子を有することを特徴とする請求項1または2に記載の能動負荷回路。

20

**【請求項 4】**

前記第1MOSトランジスタまたは前記第1ジャンクションFETは前記第2カレントミラー回路に入力される入力電流の増減に従いインピーダンスが増減し、前記第2MOSトランジスタまたは前記第2ジャンクションFETは前記第1カレントミラー回路に入力される入力電流の増減に従いインピーダンスが増減するようにインピーダンス制御されることを特徴とする請求項1または2に記載の能動負荷回路。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

30

本発明は、差動増幅器等に使用する能動負荷回路に関するものであり、特に、演算増幅器等の入力段における差動増幅器の能動負荷回路に関するものである。

**【0002】**

**【従来の技術】**

従来より演算増幅器において、出力振幅を電源電圧VDD範囲にまで広げて出力電流能力を確保しながら回路の電流消費を抑える方策として、出力段のソース・シンク側と共にMOSトランジスタで構成した演算増幅器が提案されている。これにより、出力段トランジスタをバイポーラトランジスタで構成した場合の出力振幅の制限を排除しながら、ソース・シンク側の何れか一方を定電流源回路で構成したりバイポーラトランジスタで構成した場合に必要とする多大なバイアス電流を不要として、出力電流能力と低消費電流との両立を図っている。

40

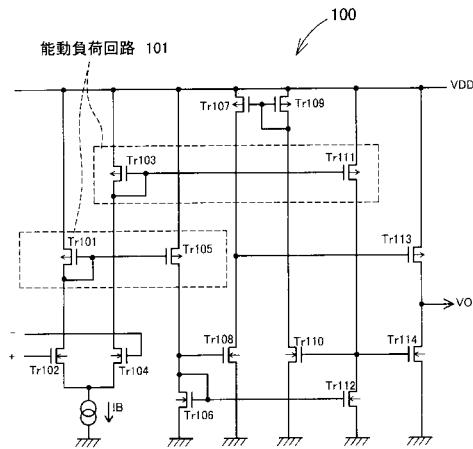

**【0003】**

図1が、従来技術による演算増幅器100である。本回路例はMOSトランジスタで構成されており、入力差動増幅段の能動負荷トランジスタTr101、Tr103に流れる差動電流は、カレントミラー回路にて、正入力の差動電流についてはトランジスタTr101からトランジスタTr105へ、更にトランジスタTr106を介してトランジスタTr108とトランジスタTr112に渡され、負入力の差動電流についてはトランジスタTr103からトランジスタTr111へ渡される。そして、トランジスタTr112とトランジスタTr111との電流差で作られる電圧が出力シンクトランジスタTr114のゲートに印加されると共に、トランジスタTr107乃至Tr110で構成される出

50

カアイドリング電流設定回路のトランジスタTr110のゲートにも印加される。出力アイドリング電流設定回路では、トランジスタTr107とトランジスタTr109、トランジスタTr108とトランジスタTr110とがそれぞれ同一のトランジスタで構成されており一種の差動回路としての動作をするので、演算増幅器100を含む系の帰還動作により定常状態では、トランジスタTr110とトランジスタTr108のゲート電圧同士、及びドレイン電圧同士は同電位となるように制御され、トランジスタTr108のドレイン、即ちトランジスタTr107のドレインと、トランジスタTr109のドレインは同電位となり、この電位が出力ソーストランジスタTr113のゲートに印加される。

#### 【0004】

これにより、出力ソーストランジスタTr113とトランジスタTr109とのゲート・ソース間電圧は等しくなり、トランジスタTr109に対する出力ソーストランジスタTr113の面積(ゲートサイズ)比に応じた電流が出力段のクロスオーバー歪み防止用の出力段バイアス電流として流れることとなる。出力アイドリング電流設定回路におけるトランジスタTr109の電流値は、トランジスタTr106に対するトランジスタTr108及びトランジスタTr110の電流比で設定されるが、この電流値を適當な値とすることにより出力段のバイアス電流を低く抑えて低消費電流を実現している。

#### 【0005】

##### 【発明が解決しようとする課題】

しかしながら、従来技術の演算増幅器100の構成においては、入力差動増幅段の能動負荷トランジスタTr101、Tr103に流れる差動電流をカレントミラー回路で切り替えることにより、MOSトランジスタで構成される出力段のソース・シンクトランジスタTr113、Tr114をバイアスしており、カレントミラー回路を多数必要とする。具体的には、正入力側差動入力電流についてのトランジスタTr101とトランジスタTr105、負入力側差動入力電流についてのトランジスタTr103とトランジスタTr111、出力シンクトランジスタTr114のバイアス設定のための、トランジスタTr106とトランジスタTr112等のカレントミラー回路を必要とする。これらの回路は、入力差動増幅段の差動対Tr102、Tr104及び能動負荷対Tr101、Tr103と共に、対となるトランジスタ間の同一性が演算増幅器100の精度を決定し、トランジスタ相互間の特性バラツキが演算増幅器100のオフセットバラツキを拡大する要因となる。即ち、バラツキ要因が3組のカレントミラー回路に入力差動増幅段における2組の要因を合わせ総計で5組ものバラツキ要因を含む構成となっており、演算増幅器100構成上、オフセットバラツキが大きくなり問題である。

#### 【0006】

また、カレントミラー回路による多段接続構成としているため、入出力応答に時間を要することとなり、応答の高速化が図れないという問題がある。

#### 【0007】

本発明は前記従来技術の問題点を解消するためになされたものであり、出力電流能力と低消費電流とを両立しながら、オフセットが少なく、過渡応答時において高速動作が可能な演算増幅器等を実現するために好適な能動負荷回路を提供することを目的とする。

#### 【0008】

##### 【課題を解決するための手段】

前記目的を達成するために、請求項1に係る能動負荷回路は、電流入力側トランジスタにおける第1入力端子に差動入力電流の一方の入力電流を入力し、電流出力側トランジスタにおける第1出力端子から差動出力電流の一方の出力電流を出力する第1カレントミラーレンジス

10

20

30

40

50

子と第1カレントミラー回路の電流出力側トランジスタにおける基準電位接続端子とに一端を接続し、他端を基準電位に接続する第2インピーダンス回路とを備え、第1インピーダンス回路は第1MOSトランジスタを有し、第2インピーダンス回路は第2MOSトランジスタを有し、第1MOSトランジスタのゲート端子が第2カレントミラー回路の第2入力端子に、第2MOSトランジスタのゲート端子が第1カレントミラー回路の第1入力端子に接続されていることを特徴とする。

また、請求項2に係る能動負荷回路は、第1インピーダンス回路は第1ジャンクションFETを有し、第2インピーダンス回路は第2ジャンクションFETを有し、第1ジャンクションFETのゲート端子が第2カレントミラー回路の第2入力端子に、第2ジャンクションFETのゲート端子が第1カレントミラー回路の第1入力端子に接続されていることを特徴とする。

#### 【0009】

前記請求項1、または請求項2の能動負荷回路では、第1及び第2カレントミラー回路の電流入力側トランジスタにおける第1及び第2入力端子に入力した差動入力電流に対して第1及び第2カレントミラー回路の電流出力側トランジスタにおける第1及び第2出力端子から差動出力電流を出力する際、差動入力電流が第1及び第2インピーダンス回路を流れるので、差動入力電流の差動成分に応じた電位降下の差が第1及び第2インピーダンス回路に現れ、この降下電圧が他方のカレントミラー回路の出力側トランジスタにおける基準電位接続端子に印加される。

#### 【0010】

これにより、差動入力電流が差動成分を有する場合にのみ、差動成分の大きい側に接続されているインピーダンス回路での電圧降下が他方のインピーダンス回路での電圧降下より大きくなり、このインピーダンス回路に接続されている他方の出力電流側トランジスタの基準電位接続端子の端子電圧は自身の出力電流側トランジスタの基準電位接続端子の端子電圧より低い電圧が印加されるため、自身の出力電流側トランジスタの電流駆動能力を増大させると共に他方の出力電流側トランジスタの電流駆動能力を低減させるので、カレントミラー回路のミラー比で規定される電流比以上に増幅された差動出力電流を、差動入力電流における差動成分の大きさに応じて得ることができ、この能動負荷回路を演算増幅器の能動負荷回路として使用した場合、演算増幅器が過渡状態となり差動入力電流が差動成分を有する場合にのみ差動出力電流を増幅することができ、過渡応答特性の高速性を実現することができる。

また、能動負荷回路の構成素子間に特性上のバラツキがある場合には、差動出力電流がバランスするために差動入力電流にオフセットが発生するが、インピーダンス回路を追加したことにより、差動入力電流の差動成分に応じた差動出力電流の増幅作用が働くので、インピーダンス回路がない場合のバランス点では差動出力電流はバランスするには至らず、更に差動入力電流のオフセットを狭めることができるので、本発明に係る能動負荷回路を演算増幅器に使用した場合に、オフセットバラツキを小さく抑えることができる。

#### 【0011】

また、差動入力電流を入力するカレントミラー回路の入力端子電圧は、差動入力電流の差動成分に応じて差動出力電流を増幅するように、MOSトランジスタまたはジャンクションFETのインピーダンスを増減制御する電圧となる。これにより、差動出力電流に増幅効果をもたらす能動素子を、従来から能動負荷回路において常用されているMOSトランジスタまたはジャンクションFETにより構成することができ、更にゲート端子を各カレントミラー回路の入力端子電圧で制御することができるので、レイアウト設計において特別な領域を確保する必要がなく従来のレイアウト資産等を有效地に利用することができると共に、ゲート端子制御信号も既存の信号を利用でき新たに生成する必要がなく簡易且つ確実に制御することができる。

#### 【0012】

また、請求項3に係る能動負荷回路は、請求項1または2に記載の能動負荷回路において、インピーダンス回路は、抵抗素子を有して構成されていることを特徴とする。

10

20

30

40

50

**【0013】**

前記請求項3の能動負荷回路では、インピーダンス回路の抵抗素子には、差動入力電流の差動成分に比例した電圧降下が現れ、この降下した電圧が他方のカレントミラー回路における出力側トランジスタの基準電位接続端子に印加される。

**【0014】**

これにより、差動出力電流に増幅効果をもたらすインピーダンス回路を、従来から能動負荷回路において常用されている抵抗素子を有して構成することができるので、レイアウト設計においても特別な領域を確保する必要がなく、従来のレイアウト資産等を有効に利用することができる。

**【0015】**

10

また、請求項4に係る能動負荷回路は、請求項1または2に記載の能動負荷回路において、インピーダンス回路は、能動素子を有して構成されており、カレントミラー回路に入力される入力電流の増減に従いインピーダンスが増減制御されることを特徴とする。

**【0016】**

前記請求項4の能動負荷回路では、差動入力電流における差動成分に応じて、差動電流が大きい側の能動素子のインピーダンスが大きく、差動電流が小さい側の能動素子のインピーダンスが小さくなるように能動素子のインピーダンスが増減制御される。

**【0017】**

20

これにより、増減制御されたインピーダンスと差動成分を有する差動入力電流の積により出力側トランジスタの基準電位接続端子に印加される電圧が決定され、両出力側トランジスタの基準電位接続端子間における電圧差により差動出力電流を増幅するので、より大きな増幅効果を得ることができる。

**【0018】****【発明の実施の形態】**

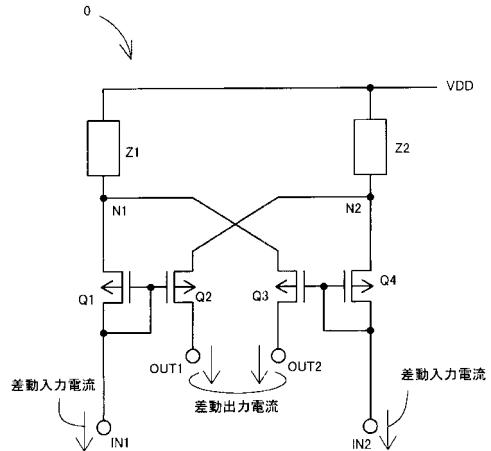

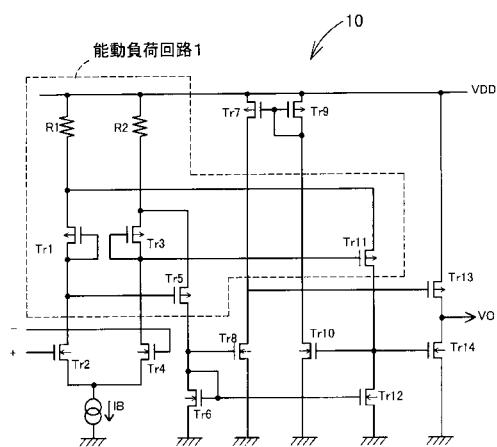

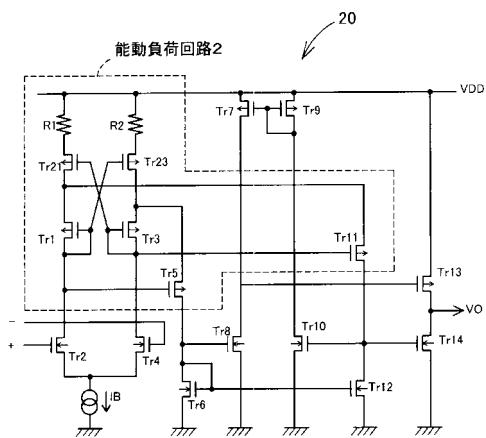

以下、本発明の能動負荷回路について具体化した第1及び第2実施形態を図2乃至図6に基づき図面を参照しつつ詳細に説明する。図2は、本発明における能動負荷回路の原理図である。図3は、第1実施形態の能動負荷回路を使用した演算増幅器の回路図である。図4は、第2実施形態の能動負荷回路を使用した演算増幅器の回路図である。図5は、第1実施形態の能動負荷回路についての動作説明図である。図6は、第2実施形態の能動負荷回路についての動作説明図である。

30

**【0019】**

図2の原理図は、P型MOSトランジスタを構成素子とした構成例である。P型MOSトランジスタQ1、Q2で構成された第1カレントミラー回路と、P型MOSトランジスタQ4、Q3で構成された第2カレントミラー回路とから構成されており、第1カレントミラー回路の入力側トランジスタであるQ1のソース端子と第2カレントミラー回路の出力側トランジスタであるQ3のソース端子とをインピーダンス回路Z1を介して電源電圧VDDに接続している。同様に、第2カレントミラー回路の入力側トランジスタQ4と第1カレントミラー回路の出力側トランジスタQ2とのソース端子をインピーダンス回路Z2から電源電圧VDDに接続して本発明に係る能動負荷回路Oを構成している。そして、第1及び第2カレントミラー回路の入力側トランジスタQ1、Q4のドレイン端子間を差動入力端子IN1、IN2として差動入力電流を入力し、両カレントミラー回路の出力側トランジスタQ2、Q3のドレイン端子間を差動出力端子OUT1、OUT2として差動出力電流を出力するものである。

40

**【0020】**

差動入力端子IN1、IN2に入力される差動入力電流の差動成分がない場合には、出力される差動出力電流の差動成分もなくなり両出力端子OUT1、OUT2からは同一電流値の同相成分が出力され、同時に各P型MOSトランジスタ(Q1及びQ3、Q4及びQ2)のソース端子と両インピーダンス回路Z1、Z2との接続点N1、N2も同電位となる。

**【0021】**

50

差動入力電流の差動成分が有限の場合には、差動入力電流がインピーダンス回路Z1、Z2に流れることによる電圧降下で接続点N1、N2に差動入力電流の差動成分に応じた電位差を生ずる。この電位差は差動出力電流の差動成分を増幅する方向に出力側トランジスタQ2、Q3のゲート・ソース間電圧を変調するので、差動出力端子OUT1、OUT2には差動入力電流の差動成分に応じて増幅された差動成分を有する差動出力電流が出力される。

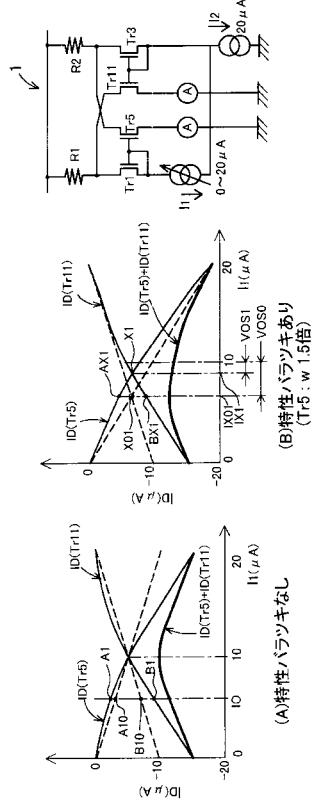

#### 【0022】

図3に示す演算増幅器10は、第1実施形態の能動負荷回路1を含んだものである。能動負荷回路1は、図2におけるP型MOSトランジスタQ1乃至Q4をP型MOSトランジスタTr1、Tr5、Tr11、Tr3で、インピーダンス回路Z1、Z2を抵抗素子R1、R2で置き換えた構成であり、それぞれのトランジスタは、図1に示す従来技術における能動負荷回路101を構成するP型MOSトランジスタTr101、Tr105、Tr111、Tr103に対応しており従来技術と同様の機能を行うものである。第1実施形態においては、上記4つのトランジスタに加えて抵抗素子R1、R2が追加されており、各カレントミラー回路の出力側トランジスタTr5、Tr11のソース端子が他方のカレントミラー回路における入力側トランジスタTr3、Tr1のソース端子に接続されており、演算増幅器10の過渡応答時に差動入力段の差動電流成分が大きくなった際に、演算増幅器10の次段以降のバイアス電流を増幅することができるので、演算増幅器10の過渡応答における高速応答特性を改善することができる。

#### 【0023】

更に、第1実施形態における能動負荷回路10は、構成素子間の特性バラツキに伴うオフセットの悪化を改善する効果を有している。この様子を図5を基に説明する。

#### 【0024】

図5の回路図は、第1実施形態における能動負荷回路1の場合を示しており、差動入力電流の総和電流I2のうちトランジスタTr1に入力される電流をI1として設定している。そして、図5(A)に各構成素子の特性バラツキがない場合の入出力特性図を示し、図5(B)にトランジスタTr5のチャネル幅Wが他方の出力トランジスタTr11に対して1.5倍にばらついた場合の入出力特性図を示す。入出力特性図中、トランジスタTr5の差動出力電流をID(Tr5)で、トランジスタTr11の差動出力電流をID(Tr11)で表し、差動出力電流の総和電流をID(Tr5)+ID(Tr11)で表している。また、図において抵抗素子R1、R2のない従来技術における能動負荷回路101の入出力特性を点線で表している。各カレントミラー回路における電流比は2対1に設定してあり、0μA乃至20μAの電流入力に対して0μA乃至10μAの電流出力が得られる構成である。

#### 【0025】

図5(A)に示す構成素子間に特性バラツキがない場合においては、差動出力電流がバランスして差動成分がなくなるポイントは、回路の対称性により従来技術による場合と同様に差動入力電流がバランスして差動成分がなくなる $I_1 = 10 \mu A$ であり差動出力電流も同一となる。即ち、演算増幅器10の能動負荷回路1として第1実施形態における能動負荷回路1を使用する場合、演算増幅器10の定常状態では従来技術による能動負荷回路101を使用する場合と同じ低消費電流性を維持することができる。

#### 【0026】

また、差動入力電流がバランス点( $I_1 = 10 \mu A$ )からはずれて差動成分を有する場合においては、差動出力電流も差動成分を有することとなるが、各出力トランジスタTr5、Tr11のソース端子が他方の入力トランジスタTr3、Tr1のソース端子と接続された上で抵抗素子R1、R2を介して電源電圧VDDに繋がれているので、差動入力電流が抵抗素子R1、R2を流れることによる電位降下で差動出力電流が増幅される方向に出力トランジスタTr5、Tr11のゲート・ソース間電圧が変調される。

#### 【0027】

図5(A)において $I_1 = I_0 < 10 \mu A$ の場合を例に具体的に示す。この場合トラン

10

20

30

40

50

ジスタ Tr 3 を介して抵抗素子 R 2 に流れる差動入力電流 ( $I_2 - I_1$ ) が他方のトランジスタ Tr 1 に入力される差動入力電流  $I_1$  に対してより大きな電流であり抵抗素子 R 2 の電位降下が抵抗素子 R 1 の電位降下より大きいので、トランジスタ Tr 1 1 より小さな差動出力電流が流れているトランジスタ Tr 5 のゲート・ソース間電圧はトランジスタ Tr 1 1 に比して小さくなり、出力電流  $I_D$  (Tr 5) は抵抗素子 R 1、R 2 のない従来技術より更に小さくなる（図 5 (A) 中、ポイント A 1 0 に対する A 1）。一方、出力トランジスタ Tr 1 1 の出力電流  $I_D$  (Tr 1 1) は逆に作用し、抵抗素子 R 1 の電位降下が抵抗素子 R 2 の電位降下より小さく、トランジスタ Tr 1 1 のゲート・ソース間電圧はトランジスタ Tr 5 に対して大きくなり、出力電流  $I_D$  (Tr 1 1) は抵抗素子 R 1、R 2 のない従来技術より更に大きくなる（図 5 (A) 中、ポイント B 1 0 に対する B 1）。以上の動作により、差動出力電流の増幅作用が行われ、演算增幅器 1 0 の能動負荷回路として第 1 実施形態における能動負荷回路 1 を使用する場合、演算增幅器 1 0 の過渡応答時には従来技術による能動負荷回路 1 0 1 を使用する場合より高速な応答特性を得ることができる。10

#### 【0028】

図 5 (B) に示す構成トランジスタ間に特性バラツキがある場合においては、差動出力電流がバランスして差動成分がなくなるポイント X 1 は、回路の対称性がずれているためオフセットを有することとなる。具体的には図 5 (B) に示すように、従来技術の場合では図 5 (B) 中の  $I_1 = I_{X01} < 10 \mu A$  でバランスするところ、第 1 実施形態によれば差動出力電流の増幅効果によりオフセット値を改善することができる。即ち、 $I_1 = I_{X01} < 10 \mu A$  が流れる抵抗素子 R 1 の電位降下が抵抗素子 R 2 の電位降下より小さいので、トランジスタ Tr 1 1 のゲート・ソース間電圧がトランジスタ Tr 5 のゲート・ソース間電圧より大きくなり、トランジスタ Tr 1 1 により大きな電流  $I_D$  (Tr 1 1) を流し（図 5 (B) 中、ポイント BX 1）、トランジスタ Tr 5 により小さな電流  $I_D$  (Tr 5) を流す（図 5 (B) 中、ポイント AX 1）。この結果、差動出力電流のバランスするポイント X 1 は、トランジスタ Tr 5 にはより大きな電流を流し、トランジスタ Tr 1 1 にはより小さな電流を流す必要から、差動入力電流  $I_1$  がより大きな電流  $I_1 = I_{X1}$  へとシフトし、オフセットを改善することができる。20

#### 【0029】

尚、過渡応答時における動作に関しては特性バラツキがない場合と同様の動作をし、演算增幅器 1 0 の能動負荷回路として第 1 実施形態における能動負荷回路 1 を使用する場合、演算增幅器 1 0 の過渡応答時において、従来技術による能動負荷回路 1 0 1 を使用する場合より高速な応答特性を得ることができる。30

#### 【0030】

また、図 5 における具体的説明においては、図 5 (A) では  $I_1 < 10 \mu A$  の領域を例にして説明し、また図 5 (B) ではトランジスタ Tr 5 のチャネル幅 W を大きくした上で  $I_1 < 10 \mu A$  の領域を例にして説明したが、 $I_1 > 10 \mu A$  の領域においても、また例示とは異なる特性バラツキについても第 1 実施形態に係る回路 1 の対称性から同様な動作を有することはいうまでもない。

#### 【0031】

従って、第 1 実施形態における能動負荷回路 1 では、出力振幅を電源電圧 VDD 範囲にまで広げて出力電流能力を確保しながら回路の電流消費を抑える構成の演算增幅器 1 0 において、従来の性能に加えて、過渡応答時に限りバイアス電流増幅作用を実現することができるので、過渡時の高速応答特性を実現することができると共に、構成素子間の特性バラツキに伴う演算增幅器 1 0 のオフセット性能の悪化を防止することができる。40

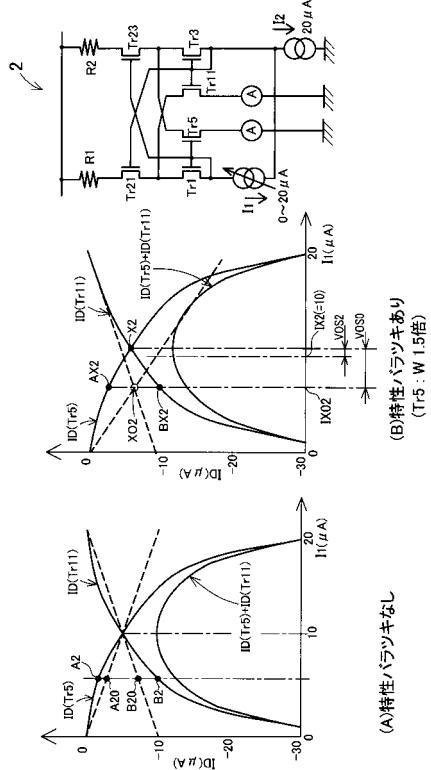

#### 【0032】

次に、図 4 に示す演算增幅器 2 0 は、第 2 実施形態の能動負荷回路 2 を含んだものである。能動負荷回路 2 の基本的構成は第 1 実施形態における構成と同様であるが、第 1 実施形態の抵抗素子 R 1、R 2 と P 型 MOS トランジスタ Tr 1、Tr 1 1、Tr 3、Tr 5 との間に、能動抵抗素子として P 型 MOS トランジスタ Tr 2 1、Tr 2 3 を挿入したこ50

とを特徴としている。即ち、MOSトランジスタTr21のソース端子を抵抗素子R1に接続し、ドレイン端子をMOSトランジスタTr1、Tr11のソース端子に接続すると共に、ゲート端子をMOSトランジスタTr3のゲート端子とドレイン端子に接続し、同様にMOSトランジスタTr23のソース端子を抵抗素子R2に、ドレイン端子をMOSトランジスタTr3、Tr5のソース端子に、ゲート端子をMOSトランジスタTr1のゲート端子とドレイン端子に接続して演算増幅器20の能動負荷回路2を構成している。

#### 【0033】

第2実施形態における能動負荷回路2を演算増幅器20に使用すれば、第1実施形態における能動負荷回路10を使用する場合と同様に、演算増幅器20の過渡応答時に差動入力段の差動電流成分が大きくなつた際、バイアス電流を増幅して過渡応答における高速応答特性を改善することができると共に、構成素子間の特性バラツキに伴うオフセットバラツキの悪化を改善することができる。

#### 【0034】

図6に具体例を示している。第2実施形態に係る回路2の素子定数、入力電流の与え方、出入力特性図は図5における第1実施形態と同様である。

#### 【0035】

図6(A)に示す構成素子間に特性バラツキがない場合においては、回路の対称性により差動出力電流がバランスして差動成分がなくなるポイントは、 $I_1 = 10 \mu A$ となり差動出力電流も同一となって、従来技術及び第1実施形態の場合と同様である。従って、演算増幅器20に第2実施形態における能動負荷回路2を使用すれば、定常状態では従来技術及び第1実施形態による能動負荷回路101、1を使用する場合と同じ低消費電流性を維持することができる。

#### 【0036】

また、差動入力電流がバランス点からずれて差動成分を有する場合においても第1実施形態で説明したのと同様の機構により、図5(A)における $I_1 = I_0 < 10 \mu A$ に具体的に示すように、トランジスタTr5の電流値 $I_D(Tr5)$ は、A20から減少したA2へ、トランジスタTr11の電流値 $I_D(Tr11)$ は、B20から増加したB2へ、それぞれシフトし差動出力電流は増幅されて出力される。

#### 【0037】

更に、図6(B)に示すトランジスタ間に特性バラツキがある場合においても、同様にオフセット値を改善することができ、図6(B)における $I_1 = I_{X02} < 10 \mu A$ のオフセットに対して、 $I_1 = I_{X2}$ まで、改善することができる。

#### 【0038】

第2実施形態では、増幅効果をもたらすトランジスタTr5、Tr11のゲート・ソース間電圧の変調は、第1実施形態における抵抗素子R2、R1に能動抵抗素子であるP型MOSトランジスタTr23、Tr21が直列接続されて強化されている。即ち、抵抗成分の追加に伴い電圧降下量が増加することに加え、追加した抵抗成分がMOSトランジスタTr23、Tr21のチャネル抵抗を利用してゲート端子が他方のカレントミラーリー回路の入力端子電圧で制御されているため、差動入力電流の差動成分に従いチャネル抵抗値の差が拡大する作用を有し、差動成分が大きくなるほど大きな抵抗差が生じ差動出力電流の増幅度を大きなものとすることができます。

#### 【0039】

能動負荷回路2を演算増幅器20の能動負荷回路として使用した場合、過渡応答時において、高速な応答特性を実現することができると共に、構成素子の特性バラツキに対してもオフセットのズレが少ない演算増幅器20を実現することができる。

#### 【0040】

尚、図6における $I_1 > 10 \mu A$ の領域や、他の構成素子における特性バラツキについても第2実施形態に係る回路の対称性から上記の具体的説明と同様な動作を有することは、第1実施形態における場合と同様である。

#### 【0041】

10

20

30

40

50

従って、出力振幅を電源電圧 V D D 範囲にまで広げて出力電流能力を確保しながら回路の電流消費を抑える構成の演算増幅器 2 0において、従来の性能に加えて、過渡応答時に限りバイアス電流増幅作用を実現することができるので、高速応答特性を実現することができると共に、構成素子間の特性バラツキに伴う演算増幅器 2 0のオフセット性能の悪化を防止することができる。

#### 【 0 0 4 2 】

加えて、第 1 実施形態における能動負荷回路 1 では、従来から能動負荷回路において常用されている抵抗素子 R 1、R 2 を付加するのみで構成することができ、第 2 実施形態における能動負荷回路 2 では、従来から能動負荷回路において常用されている M O S トランジスタ T r 2 1、T r 2 3 を能動抵抗素子として付加するのみで構成することができ、共にレイアウト設計において特別な領域を確保する必要がなく、しかも従来のレイアウト資産等を有効に利用することができる。また、M O S トランジスタ T r 2 1、T r 2 3 のゲート端子制御信号も既存の信号であり新たに生成する必要がなく簡易且つ確実に制御することができる。10

#### 【 0 0 4 3 】

以上詳細に説明したとおり、第 1 実施形態に係る能動負荷回路 1 では、P 型 M O S トランジスタ T r 1、T r 5 で構成された第 1 カレントミラー回路と、P 型 M O S トランジスタ T r 3、T r 1 1 で構成された第 2 カレントミラー回路とからなり、トランジスタ T r 1 とトランジスタ T r 1 1とのソース端子を抵抗素子 R 1 に、トランジスタ T r 3 とトランジスタ T r 5 とのソース端子を抵抗素子 R 2 に接続して能動負荷回路 1 を構成している。20 そして、トランジスタ T r 1、T r 3 のドレイン端子間を差動入力端子とし、トランジスタ T r 5、T r 1 1 のドレイン端子間を差動出力端子として、演算増幅器 1 0 の能動負荷回路 1 として接続した場合、図 1 に示す従来技術における能動負荷回路 1 0 1 と同様の機能に加え、過渡応答時に、抵抗素子 R 1、R 2 により次段以降のバイアス電流を増幅することができるので、演算増幅器 1 0 の過渡応答における高速応答特性を改善することができる。

#### 【 0 0 4 4 】

即ち、構成素子の特性バラツキがない図 5 ( A ) に示すように、トランジスタ T r 1 1 より小さな差動出力電流が流れているトランジスタ T r 5 のゲート・ソース間電圧がトランジスタ T r 1 1 に比して小さくなるため、出力電流 I D ( T r 5 ) は抵抗素子 R 1、R 2 のない従来技術より更に小さくなり ( 図 5 ( A ) 中、ポイント A 1 0 に対する A 1 ) 、出力トランジスタ T r 1 1 の出力電流 I D ( T r 1 1 ) は、トランジスタ T r 1 1 のゲート・ソース間電圧がトランジスタ T r 5 に対して大きくなるため、抵抗素子 R 1、R 2 のない従来技術より更に大きくなる ( 図 5 ( A ) 中、ポイント B 1 0 に対する B 1 ) ことにより、差動出力電流が増幅されて演算増幅器 1 0 の過渡応答特性を高速化することができる。尚、図 5 ( B ) における構成素子に特性ばらつきがある場合も、同様に過渡応答特性の高速化を図ることができる。30

#### 【 0 0 4 5 】

また、図 5 ( A ) に示すように、差動出力電流がバランスして差動成分がなくなるポイント ( I 1 = 1 0 μ A ) では、回路の対称性から差動入力電流がバランスして差動成分がなくなる I 1 = 1 0 μ A であり差動出力電流も同一となる。即ち、演算増幅器 1 0 の能動負荷回路として能動負荷回路 1 を使用すれば、定常状態において従来と同様に演算増幅器 1 0 の低消費電流性を維持することができる。40

#### 【 0 0 4 6 】

更に、トランジスタ T r 5 のチャネル幅が他のトランジスタに比して 1 . 5 倍であり特性バラツキを有する場合には図 5 ( B ) に示すように、従来技術におけるバランス点 X 0 1 である I 1 = I X 0 1 < 1 0 μ A に対して、差動出力電流の増幅効果により、トランジスタ T r 5 に流れる電流 I D ( T r 5 ) に対してトランジスタ T r 1 1 により大きな電流 I D ( T r 1 1 ) が流れるので ( 図 5 ( B ) 中、ポイント A X 1、B X 1 ) 、差動出力電流のバランスするポイント X 1 は、差動入力電流 I 1 がより大きくなる方向にシフトし、50

オフセットを改善することができる。

**【0047】**

上記の特性は、第1実施形態に係る回路1の対称性から、図5(A)(B)における $I_1 < 10 \mu A$ の領域のみならず $I_1 > 10 \mu A$ の領域においても同様に成立し、また例示とは異なる構成素子の特性バラツキについても同様な動作をするので、第1実施形態における能動負荷回路1では、出力振幅を電源電圧VDD範囲にまで広げて出力電流能力を確保しながら回路の電流消費を抑える構成の演算増幅器10において、過渡応答時に限りバイアス電流増幅作用を実現することができ、高速応答特性を実現することができると共に、構成素子間の特性バラツキに伴う演算増幅器10のオフセット性能の悪化を防止することができる。

10

**【0048】**

また、第2実施形態に係る能動負荷回路2では、第1実施形態に係る能動負荷回路1の構成に加えて、2つのカレントミラー回路と抵抗素子R1、R2との間に能動抵抗素子としてP型MOSトランジスタTr21、Tr23を、ソース端子を抵抗素子R1、R2に接続すると共に、ゲート端子をトランジスタTr3のゲート及びドレイン端子、及びトランジスタTr1のゲート及びドレイン端子に接続して構成されている。

**【0049】**

構成素子間に特性バラツキがない場合は図6(A)に示すように、回路の対称性により $I_1 = 10 \mu A$ で差動出力電流がバランスして差動成分がなくなり差動出力電流も同一なので、能動負荷回路2を演算増幅器20に使用すれば、定常状態では従来技術及び第1実施形態による能動負荷回路101、1を使用する場合と同じ低消費電流性を維持することができる。

20

**【0050】**

また、差動入力電流がバランス点からずれている場合も、第1実施形態で説明したのと同様の機構により、差動出力電流を増幅することができる。

**【0051】**

更に、特性バラツキがある場合においても図6(B)に示すように、第1実施形態と同様にオフセット値を改善することができ、 $I_1 = IX_02 < 10 \mu A$ のオフセットに対して、 $I_1 = IX_2$ まで改善することができる。

30

**【0052】**

ここで、増幅効果は、抵抗素子R1、R2に能動抵抗素子であるP型MOSトランジスタTr21、Tr23が直列接続されて強化されており、抵抗成分の追加に伴い電圧降下量が増加することに加え、MOSトランジスタTr21、Tr23のチャネル抵抗が他方のカレントミラー回路の入力端子電圧で制御されているため、差動入力電流の差動成分に従いチャネル抵抗値の差が拡大する作用を有し、差動成分が大きくなるほど大きな抵抗差が生じて差動出力電流の増幅度を大きなものとすることができます。

**【0053】**

能動負荷回路2を演算増幅器20の能動負荷回路として使用した場合、過渡応答時において、高速な応答特性を実現することができると共に、構成素子の特性バラツキに対してもオフセットのズレが少ない演算増幅器20を実現することができる。

40

**【0054】**

尚、第1実施形態の場合と同様、図6における $I_1 > 10 \mu A$ の領域や、他の特性バラツキについても能動負荷回路2の対称性から上記の具体的説明と同様な動作を有することはいうまでもない。

**【0055】**

従って、出力振幅を電源電圧VDD範囲にまで広げて出力電流能力を確保しながら回路の電流消費を抑える構成の演算増幅器20において、過渡応答時に限りバイアス電流増幅作用を実現することができ、高速応答特性を実現することができると共に、構成素子間の特性バラツキに伴う演算増幅器20のオフセット性能の悪化を防止することができる。

**【0056】**

50

加えて、第1及び第2実施形態における能動負荷回路1、2では、従来から能動負荷回路において常用されている抵抗素子R1、R2や、MOSトランジスタTr21、Tr23を付加するのみで構成することができ、レイアウト設計において特別な領域を確保する必要がなく、しかも従来のレイアウト資産等を有効に利用することができる。またMOSトランジスタTr21、Tr23のゲート端子制御信号も既存の信号であり新たに生成する必要がなく簡易且つ確実に制御することができる。

#### 【0057】

尚、本発明は前記実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲内で種々の改良、変形が可能であることは言うまでもない。

例えば、本実施形態においては、カレントミラー回路をP型MOSトランジスタで構成して説明したが、本発明に係る能動負荷回路はこれに限定されるものではなく、N型MOSトランジスタの他、NPNバイポーラトランジスタやPNPバイポーラトランジスタで構成することもできる。

インピーダンス回路についても、本実施形態の回路に限定されることはなく、MOSトランジスタ単独での構成とすることの他、MOSトランジスタに代えてジャンクションFETにて構成しても良く、また抵抗素子も含めたこれらの素子の任意の組み合わせで構成することもできる。

更に、本実施形態においては、演算増幅器を利用した場合について説明したが、これに限定されることではなく、コンパレータ等にも利用することができ、この場合にも差動入力に対して高速応答特性を実現することができる。

#### 【0058】

#### 【発明の効果】

本発明によれば、差動入力電流が差動成分を有する場合に、差動成分に応じて差動出力電流が増幅されるように出力側トランジスタの電流駆動能力が制御されるので、出力電流能力と低消費電流とを両立しながら、オフセットが少なく、過渡応答時において高速動作が可能な演算増幅器等を実現するために好適な能動負荷回路を提供することが可能となる。

#### 【図面の簡単な説明】

【図1】 従来技術における能動負荷回路を使用した演算増幅器の回路図である。

【図2】 本発明における能動負荷回路の原理図である。

【図3】 第1実施形態の能動負荷回路を使用した演算増幅器の回路図である。

【図4】 第2実施形態の能動負荷回路を使用した演算増幅器の回路図である。

【図5】 第1実施形態の能動負荷回路についての動作説明図である。

【図6】 第2実施形態の能動負荷回路についての動作説明図である。

#### 【符号の説明】

|           |                  |    |

|-----------|------------------|----|

| 0、1、2     | 能動負荷回路           |    |

| 101       | 従来の能動負荷回路        |    |

| 10、20     | 演算増幅器            |    |

| 100       | 従来の演算増幅器         |    |

| Z1、Z2     | インピーダンス回路        | 40 |

| R1、R2     | 抵抗素子             |    |

| Tr21、Tr23 | 能動抵抗素子用MOSトランジスタ |    |

【 図 1 】

### 従来技術における能動負荷回路を使用した演算増幅器の回路図

【 図 2 】

## 本発明における能動負荷回路の原理図

【 図 3 】

## 第1実施形態の能動負荷回路を使用した演算増幅器の回路図

【 図 4 】

## 第2実施形態の能動負荷回路を使用した演算増幅器の回路図

【図5】

第1実施形態の能動負荷回路についての動作説明図

【図6】

第2実施形態の能動負荷回路についての動作説明図

---

フロントページの続き

(56)参考文献 特開昭56-020315(JP,A)

特開平06-037558(JP,A)

特開昭62-048114(JP,A)

特開昭61-074406(JP,A)

特開2000-209047(JP,A)

特開平06-303050(JP,A)

特開昭53-098762(JP,A)

特開2000-040925(JP,A)

特開2000-151305(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03F 1/00- 3/45、 3/50- 3/52,

3/62- 3/64、 3/68- 3/72