(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6224994号

(P6224994)

(45) 発行日 平成29年11月1日(2017.11.1)

(24) 登録日 平成29年10月13日(2017.10.13)

(51) Int.Cl.

F 1

|             |             |                  |        |      |       |

|-------------|-------------|------------------|--------|------|-------|

| <b>G06F</b> | <b>1/32</b> | <b>(2006.01)</b> | G 06 F | 1/32 | Z     |

| <b>G06F</b> | <b>1/24</b> | <b>(2006.01)</b> | G 06 F | 1/24 | A     |

| <b>G06F</b> | <b>1/04</b> | <b>(2006.01)</b> | G 06 F | 1/04 | 5 7 5 |

請求項の数 16 (全 18 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2013-228754 (P2013-228754) |

| (22) 出願日  | 平成25年11月1日 (2013.11.1)       |

| (65) 公開番号 | 特開2015-88129 (P2015-88129A)  |

| (43) 公開日  | 平成27年5月7日 (2015.5.7)         |

| 審査請求日     | 平成28年7月26日 (2016.7.26)       |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】情報処理装置およびその制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

割り当てられた演算を行い、電力供給の遮断状態から復帰する際にリセット動作を行う複数の回路ブロックを有する情報処理装置であって、

少なくとも1つの回路ブロックを含む電源ドメインに対する電力供給を制御する電力制御手段と、

前記電力制御手段により電力供給が再開される回路ブロックのリセット動作を制御する初期化制御手段と、を有し、

前記初期化制御手段は、前記リセット動作による前記情報処理装置の消費電力が所定の消費電力以下となるように、前記回路ブロックが前記リセット動作に要するクロックサイクル数に基づき、前記回路ブロックのリセット動作時のリセット動作パラメータを設定し

10

前記リセット動作パラメータは動作周波数であることを特徴とする情報処理装置。

## 【請求項 2】

割り当てられた演算を行い、電力供給の遮断状態から復帰する際にリセット動作を行う複数の回路ブロックを有する情報処理装置であって、

少なくとも1つの回路ブロックを含む電源ドメインに対する電力供給を制御する電力制御手段と、

前記電力制御手段により電力供給が再開される回路ブロックのリセット動作を制御する初期化制御手段と、を有し、

20

前記初期化制御手段は、前記リセット動作による前記情報処理装置の消費電力が所定の消費電力以下となるように、前記回路ブロックが前記リセット動作に要するクロックサイクル数に基づき、前記回路ブロックのリセット動作時のリセット動作パラメータを設定し

前記リセット動作パラメータは動作電圧であることを特徴とする情報処理装置。

**【請求項 3】**

前記初期化制御手段は、前記リセット動作パラメータと回路ブロックのリセット動作時のダイナミック電力の関係を示すパラメーターテーブル情報に基づいて、前記リセット動作パラメータを設定することを特徴とする請求項 1 または 2 に記載の情報処理装置。

**【請求項 4】**

前記初期化制御手段は、

前記クロックサイクル数の大きい順に、前記回路ブロックのリセット動作の優先順位を決定する優先順位決定手段と、

前記回路ブロックのリセット動作時の前記消費電力が前記所定の消費電力以下となるように、前記回路ブロックのリセット動作パラメータを前記優先順位に応じて設定する動作パラメータ設定手段と、

を有することを特徴とする請求項 1 または 2 に記載の情報処理装置。

**【請求項 5】**

前記動作パラメータ設定手段は、前記優先順位に応じて、前記所定の消費電力から前記回路ブロックに対して割り当て可能な消費電力の範囲内で前記リセット動作にかかる時間が最短となる前記リセット動作パラメータを設定することを特徴とする請求項 4 に記載の情報処理装置。

**【請求項 6】**

前記動作パラメータ設定手段は、前記所定の消費電力から割り当て可能な消費電力では前記リセット動作が不能である前記回路ブロックについて、前記リセット動作を行わせない前記リセット動作パラメータを設定することを特徴とする請求項 4 又は 5 に記載の情報処理装置。

**【請求項 7】**

前記動作パラメータ設定手段は、前記回路ブロックごとに、

前記リセット動作パラメータの候補を、所定の選定対象群から選定する選定手段と、

前記リセット動作パラメータの候補でリセット動作を行った場合の前記消費電力を予測する予測手段と、

前記予測された消費電力が前記所定の消費電力以下である場合に、前記リセット動作パラメータの候補を前記リセット動作パラメータとして設定する設定手段と、を有し、

前記選定手段は、前記予測された消費電力が前記所定の消費電力を超えた場合に、前記予測された消費電力が前記所定の消費電力以下となるまで、前記リセット動作パラメータの候補の選定を繰り返すことを特徴とする請求項 4 乃至 6 の何れか 1 項に記載の情報処理装置。

**【請求項 8】**

さらに、前記回路ブロックのリセット動作を行う前の前記消費電力を検出する電力検出手段を有し、

前記予測手段は、前記検出された消費電力と、前記リセット動作により増加する消費電力との加算により前記予測を行うこと特徴とする請求項 7 に記載の情報処理装置。

**【請求項 9】**

さらに、前記情報処理装置の温度を検出する温度検出手段を有し、

前記予測手段は、前記リセット動作により増加する消費電力を、前記温度に基づくりーク電力と前記リセット動作パラメータに基づくダイナミック電力の加算により算出することを特徴とする請求項 8 に記載の情報処理装置。

**【請求項 10】**

前記初期化制御手段はさらに、

10

20

30

40

50

前記リセット動作対象の複数の回路ブロックを指定する指示を受信する受信手段と、

前記リセット動作対象の各回路ブロックのリセット動作の完了を検出する検出手段と

、を有し、

前記初期化制御手段は、前記指定されたリセット動作対象の複数の回路ブロックの全て

についてリセット動作の完了が検出されるまで、前記リセット動作が未完了の回路ブロック

に対する前記リセット動作パラメータの設定を継続することを特徴とする請求項1乃至

9の何れか1項に記載の情報処理装置。

#### 【請求項11】

さらに、前記パラメーターテーブル情報を予め保持する保持手段を有することを特徴とする

請求項3に記載の情報処理装置。 10

#### 【請求項12】

さらに、前記回路ブロックごとの前記クロックサイクル数を予め保持するクロックサイ

クル数保持手段を有することを特徴とする請求項1乃至11のいずれか1項に記載の情報

処理装置。

#### 【請求項13】

割り当てられた演算を行い、電力供給の遮断状態から復帰する際にリセット動作を行う

複数の回路ブロックを有し、少なくとも1つの回路ブロックを含む電源ドメインに対する

電力供給を制御可能な情報処理装置の制御方法であって、

前記リセット動作時の前記情報処理装置の消費電力が所定の消費電力以下となるように

、電力供給が再開される回路ブロックがリセット動作に要するクロックサイクル数に基づ

き、前記回路ブロックのリセット動作時のリセット動作パラメータを設定し、 20

前記リセット動作パラメータは動作周波数であることを特徴とする情報処理装置の制御

方法。

#### 【請求項14】

割り当てられた演算を行い、電力供給の遮断状態から復帰する際にリセット動作を行う

複数の回路ブロックを有し、少なくとも1つの回路ブロックを含む電源ドメインに対する

電力供給を制御可能な情報処理装置の制御方法であって、

前記リセット動作時の前記情報処理装置の消費電力が所定の消費電力以下となるように

、電力供給が再開される回路ブロックがリセット動作に要するクロックサイクル数に基づ

き、前記回路ブロックのリセット動作時のリセット動作パラメータを設定し、 30

前記リセット動作パラメータは動作電圧であることを特徴とする情報処理装置の制御

方法。

#### 【請求項15】

コンピュータ装置で実行されることにより、該コンピュータ装置を請求項1乃至12の

いずれか1項に記載の情報処理装置の各手段として機能させるためのプログラム。

#### 【請求項16】

請求項15に記載のプログラムを記憶したことを特徴とするコンピュータ可読の記憶媒

体。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、電力供給の遮断状態から復帰する際にリセット動作を行う複数の回路ブロック

を有する情報処理装置およびその制御方法に関する。

##### 【背景技術】

##### 【0002】

近年、環境問題に配慮した省エネルギー化の流れから、半導体集積回路に対し低電力化

が求められている。一般的に、論理ゲートで構成される半導体集積回路の消費電力は、ダ

イナミック電力とスタティック電力に大別される。

##### 【0003】

ダイナミック電力は、論理ゲートに接続される配線容量や後段のゲート容量に対する充 50

放電電流により消費される電力であり、信号変化を抑えることによって削減できる。例えば、クロックゲーティングによって信号変化の無いフリップフロップへのクロック供給を止めることで、ダイナミック電流を削減できる。

#### 【0004】

一方、スタティック電力は、オフしているトランジスタの漏れ電流により消費される電力であり、動作周波数には依存しない。一般に、接合リーア電力、ゲートリーア電力、ゲート誘導ドレインリーア電力、サブスレッショルドリーア電力はスタティック電力に分類される。これらのスタティック電力は、半導体集積回路の一部の回路ブロックへの電源を遮断することで抑制することができる。通常、電源を遮断した回路ブロックを復帰させる際には、電力を供給した後に初期化を行う必要があるため、通常動作に入る前にリセットを行う。10

#### 【0005】

一般にリセット動作中には、回路ブロック内部のフリップフロップ等の記憶素子に対して積極的に信号変化を起こさせることで状態を初期化するため、クロックゲーティングは行わない。そのため、リセット動作中の消費電力は通常動作時よりも大きくなることが多い。

#### 【0006】

また、近年の半導体集積回路において、電源を遮断される対象となる領域(回路ブロック、以下では電源ドメインと称する)の数は増加傾向にある。機能を実現させるための複数の回路ブロックのそれぞれを異なる電源ドメインに配置することで、使わない機能を有する回路ブロックが配置されている電源ドメインへの電力を遮断することができる。これにより、不要なスタティック電力を削減できる。20

#### 【0007】

ここで、各電源ドメインは、電力供給の再開後にリセット動作(特に、リセット信号の解除)をする。一般的な半導体集積回路では、複数の回路ブロックをリセット対象とする場合、回路全体の処理効率を上げるために複数のリセット動作(リセット信号の発行タイミングや解除タイミング)を合わせている。このように複数の電源ドメインにおいてリセット動作が重なると、リセット動作中の瞬間的な消費電力の増加度合いが集中してしまう。

#### 【0008】

そこで、リセット動作中に入力されるクロックの周波数を分周し、動作率を低下させることで消費電力を削減する技術が提案されている(例えば、特許文献1参照)。また、複数の回路ブロックに入力するクロックのタイミングを異ならせることで、電力の増加度合いを分散させる技術が提案されている(例えば、特許文献2参照)。30

#### 【先行技術文献】

##### 【特許文献】

##### 【0009】

【特許文献1】特開2002-312073号公報

【特許文献2】特開2011-65529号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

しかしながら、回路ブロックのリセット動作を完了させるためには、所定のサイクル数分のクロックを入力する必要がある。上記特許文献1の技術によれば、消費電力のピークをある程度低減できるものの、周波数を落とした分、リセット動作に要する時間は長期化してしまう。また、上記特許文献2の技術によれば、回路ブロックに入力するクロックの周波数は落とさないものの、入力するクロックのタイミングが異なるため、リセット動作に要する期間はやはり長期化してしまう。

#### 【0011】

本発明は上述した問題を解決するためになされたものであり、複数の回路ブロックに対40

50

するリセット動作時の消費電力を抑制し、かつリセット動作にかかる時間を短縮することを目的とする。

**【課題を解決するための手段】**

**【0012】**

上記目的を達成するために、本発明に係る情報処理装置は以下の構成を備える。すなわち、割り当てられた演算を行い、電力供給の遮断状態から復帰する際にリセット動作を行う複数の回路ブロックを有する情報処理装置であって、少なくとも1つの回路ブロックを含む電源ドメインに対する電力供給を制御する電力制御手段と、前記電力制御手段により電力供給が再開される回路ブロックのリセット動作を制御する初期化制御手段と、を有し、前記初期化制御手段は、前記リセット動作による前記情報処理装置の消費電力が所定の消費電力以下となるように、前記回路ブロックが前記リセット動作に要するクロックサイクル数に基づき、前記回路ブロックのリセット動作時のリセット動作パラメータを設定し、前記リセット動作パラメータは動作周波数または動作電圧であることを特徴とする。

**【発明の効果】**

**【0013】**

本発明によれば、複数の回路ブロックに対するリセット動作時の消費電力を抑制し、かつリセット動作にかかる時間を短縮できる。

**【図面の簡単な説明】**

**【0014】**

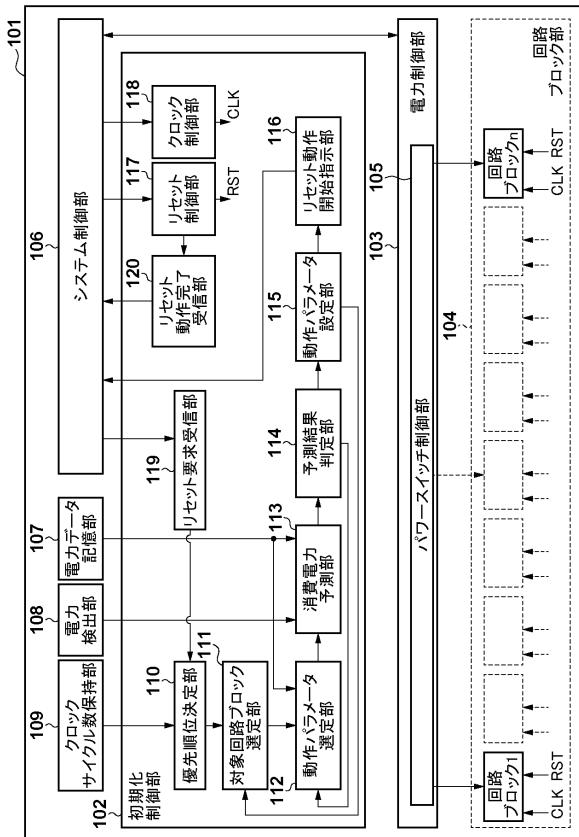

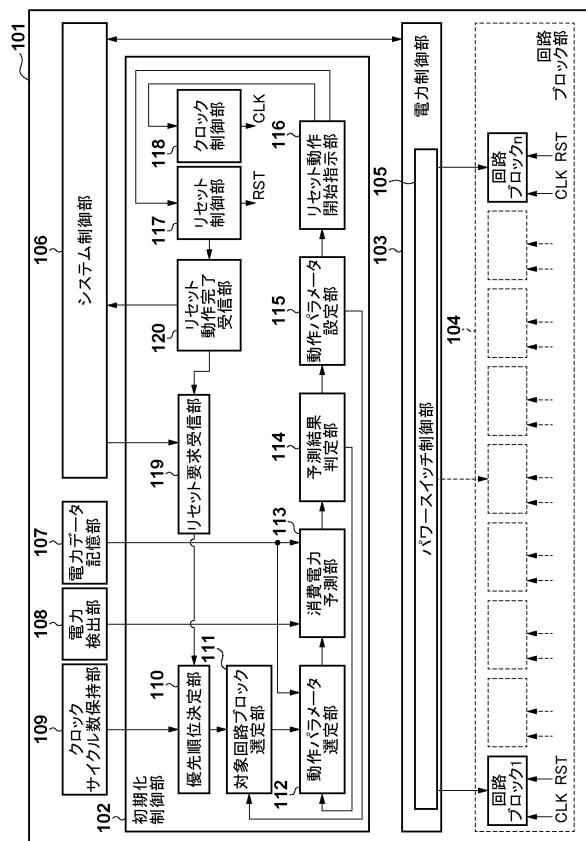

**【図1】第1実施形態における半導体集積回路の概略構成を示すブロック図、**

20

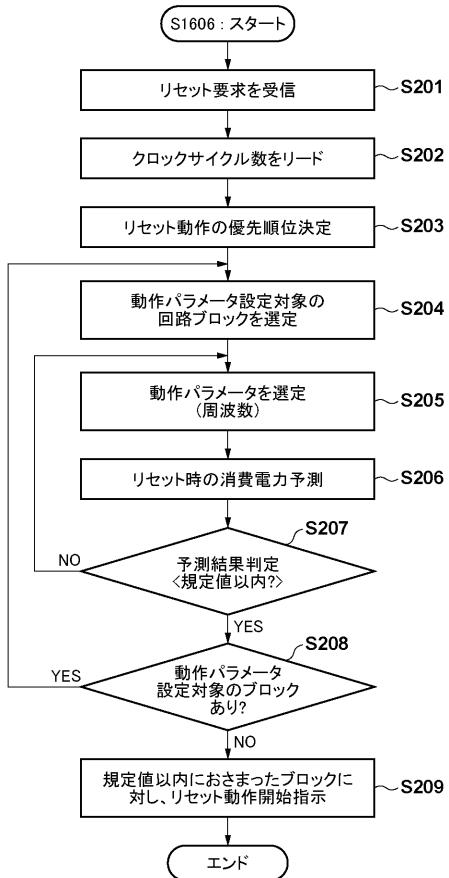

**【図2】第1実施形態における初期化制御処理を示すフローチャート、**

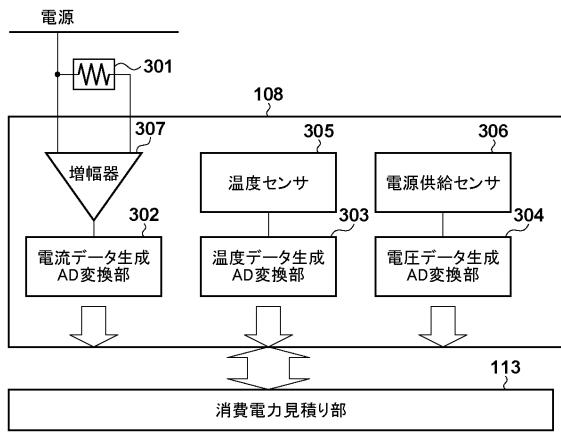

**【図3】電力検出部の構成を示すブロック図、**

**【図4】クロックサイクル数のテーブル例を示す図、**

**【図5】第1実施形態における動作パラメータのテーブル例を示す図、**

**【図6】第1実施形態における動作パラメータの推移例を示す図、**

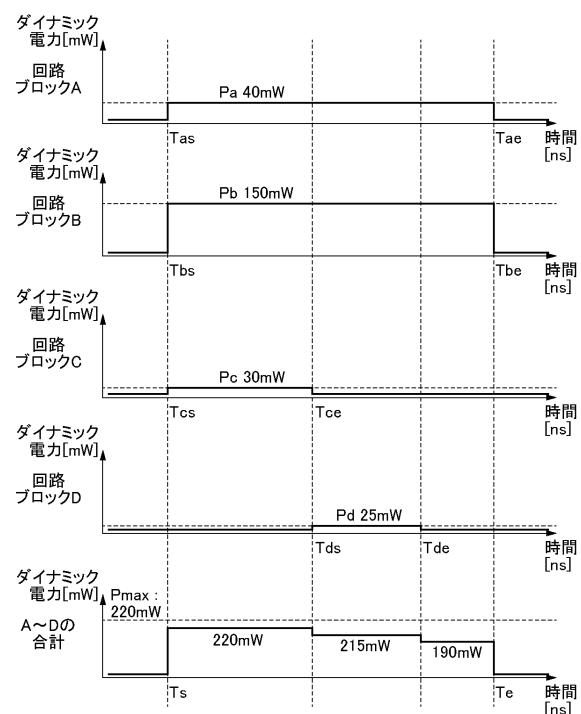

**【図7】第1実施形態におけるダイナミック電力の推移例を示す図、**

**【図8】第1実施形態の動作パラメータによるリセット動作のタイミングチャート、**

**【図9】一般的なリセット動作における所要時間や消費電力の特性を示す図、**

**【図10】第2実施形態における動作パラメータのテーブル例を示す図、**

30

**【図11】第2実施形態における動作パラメータの推移を例を示す図、**

**【図12】第2実施形態におけるダイナミック電力の推移を示す図、**

**【図13】第2実施形態の動作パラメータによるリセット動作のタイミングチャート、**

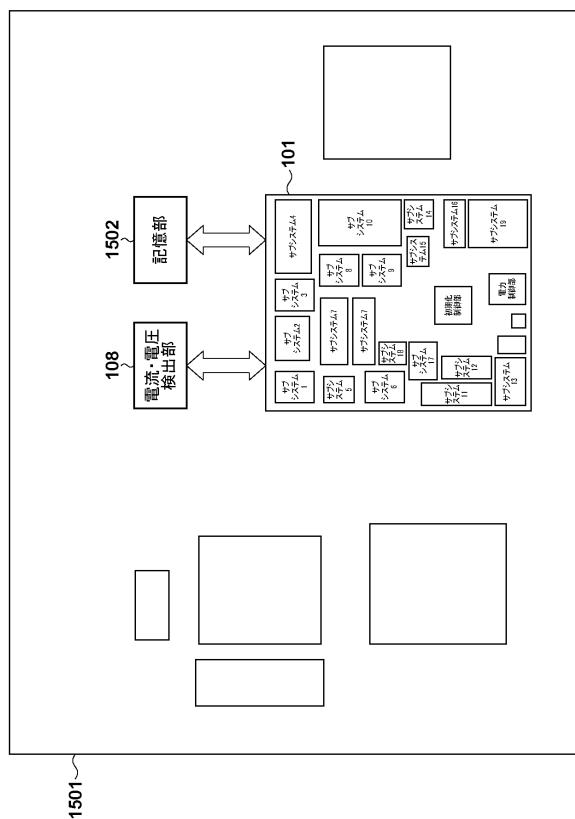

**【図14】第3実施形態における半導体集積回路の概略構成を示すブロック図、**

**【図15】第4実施形態における省電力システムの概略構成を示すブロック図、**

**【図16】第1実施形態における電力制御の基本動作を示すフローチャート、**

**【図17】第2実施形態における初期化制御処理を示すフローチャート、である。**

**【発明を実施するための形態】**

**【0015】**

以下、添付の図面を参照して、本発明をその好適な実施形態に基づいて詳細に説明する。なお、以下の実施形態において示す構成は一例に過ぎず、本発明は図示された構成に限定されるものではない。

40

**【0016】**

<第1実施形態>

半導体集積回路構成

まず、本実施形態の半導体集積回路101についての概略を説明する。図1は、半導体集積回路101の内部の概略構成を示すブロック図である。半導体集積回路101は、それぞれが異なる電源ドメインに対応するn個の回路ブロックから構成される回路ブロック部104を備える。回路ブロックの其々は、供給されるクロックCLKに応じて演算を行うことで、予めまたは動的に割り当てられてた機能を実現する。そして、リセット信号RSTが供給されている間は、内部のフリップフロップなどの記憶素子に対してリセットをかけ続ける。

50

**【0017】**

電力制御部103は、パワースイッチ制御部105によって回路ブロック部104の回路ブロック毎に、電源からの電力を供給するか否かを切り替える。

**【0018】**

電力検出部108は、半導体集積回路101の温度、電圧、電流などの動作状態を検知する。電力データ記憶部107は、各回路ブロックについて、電力供給を再開する際のリセット動作中に消費するダイナミック電力を示す値をテーブルとして保持している。電力データ記憶部107はまた、半導体集積回路101が安定して動作するための基準となる消費電力を示す値や、温度とリーク電力の関係を示すテーブルを保持している。

**【0019】**

10

システム制御部106は、電力制御部103からの回路ブロックの電源復帰完了通知、あるいは、リセット動作完了受信部120からのリセット動作完了通知を受けて、リセット要求受信部119、クロック制御部118、リセット制御部117を制御する。システム制御部106はまた、半導体集積回路101のパワーモードの遷移や、各回路ブロックのデータ処理モードの制御など、システム全体を制御するシーケンサとしても機能する。

**【0020】**

クロックサイクル数保持部109は、各回路ブロックについて、リセット動作を完了させるまでに入力する必要があるクロックのサイクル数をテーブルとして保持している。

**【0021】**

20

初期化制御部102は、システム制御部106の指示を受信した後、各回路ブロックに対するリセット動作のパラメータとして、動作周波数や動作電圧を決定する。以下、初期化制御部102の詳細構成について説明する。

**【0022】**

クロック制御部118は、システム制御部106からの指示に基づいて、複数の回路ブロックについて個別にクロックを供給するか否かを制御する。リセット制御部117は、システム制御部106からの指示に基づいて、回路ブロックにリセット信号を発行したり、発行しているリセット信号を停止することで、リセット動作の開始・終了を制御する。

**【0023】**

リセット要求受信部119は、システム制御部106からの指示を受信して、優先順位決定部110に対しリセット動作対象として指定された回路ブロック(指定回路ブロック)を通知する。優先順位決定部110は、リセット要求受信部119からの通知された指定回路ブロックについて、クロックサイクル数保持部109から読み出した各回路ブロックのクロックサイクル数の大小に従い、リセット動作の優先順位を決定する。対象回路ブロック選定部111は、優先順位決定部110で決められた優先順に従い、リセット動作の動作パラメータの設定対象となる回路ブロックを選定する。動作パラメータ選定部112は、対象回路ブロック選定部111で選定された回路ブロックに対し、リセット動作の動作パラメータ(動作周波数や動作電圧)の候補を、所定の選定対象群から選定する。

30

**【0024】**

消費電力予測部113は、動作パラメータ選定部112で選定された動作パラメータ候補、すなわち選定された動作周波数および動作電圧でリセット動作を行った場合における、半導体集積回路101の消費電力を予測する。この予測処理の詳細については後述する。

40

**【0025】**

予測結果判定部114は、消費電力予測部113で予測された消費電力が、所定の基準消費電力以下であるか否かを判定する。動作パラメータ設定部115は、消費電力が基準消費電力以下であると判定された場合に、その時の動作パラメータを実際のリセット動作に適用するパラメータとして、リセット動作を制御するレジスタ(不図示)に設定する。リセット動作開始指示部116は、対象となる回路ブロックすべてについて、リセット動作を制御するレジスタ設定が完了しているのを確認して、システム制御部106にその旨を通知する。

**【0026】**

このように初期化制御部102は、リセット制御部117とクロック制御部118によって、回

50

路ブロック部104の初期化を実現する初期化制御手段として機能する。

**【0027】**

なお、図1では回路ブロック数をn個とした例を示すが、本発明は複数の電力制御対象があれば適用可能であり、回路ブロックの個数に制限はない。また、説明の簡便のため、回路ブロックと電源ドメインとが1対1で対応する例を示すが、これらは必ずしも1対1対応である必要はない。例えば、2つ以上の回路ブロックを1つの電源ドメインと対応させたり、1つの回路ブロックを2つ以上の電源ドメインにより管理したりしてもよい。ここで電源ドメインとは、同一の電力制御素子(例えば、パワースイッチ)によって電源の供給を止められる領域を示し、半導体集積回路101のリーク電流を抑制するためのものであり、この定義を満たす回路ブロックや機能モジュール、IC等であってもよい。

10

**【0028】**

**電力制御の基本処理**

以下、上記図1に示す構成からなる本実施形態の半導体集積回路における、各回路ブロックに対する電力制御の基本動作(電力遮断動作、電力復帰動作)について、図16のフローチャートを用いて説明する。

**【0029】**

まずS1601においてシステム制御部106が、電力遮断対象の回路ブロック(以下、遮断対象ブロックと称する)への電力を遮断する指示に応じて、リセット制御部117に対して、該遮断対象ブロックへのリセットをアクティブ状態にするように命令する。リセット制御部117はこの命令に応じて、遮断対象ブロックに対してリセット動作を開始(リセット信号をアサート)する。

20

**【0030】**

次にS1602でシステム制御部106が、クロック制御部118に対し、遮断対象ブロックへのクロックの供給を停止するように命令する。クロック制御部118はこの命令に応じて、不図示のクロックゲートセルをアクティブにすることで、遮断対象ブロックへのクロック供給を停止する。

**【0031】**

次にS1603でシステム制御部106が、遮断対象ブロックへの電力供給の遮断を要求するコマンド(以下、遮断要求)を電力制御部103に送信する。電力制御部103はこの遮断要求を受信した後、パワースイッチ制御部105によって、遮断対象ブロックへの電力供給を停止する。

30

**【0032】**

S1604ではシステム制御部106が、電源遮断状態の回路ブロックを復帰させるためのトリガが発生したか否かを判定する。このようなトリガとしては、ユーザやアプリケーションプログラム等からの要求を半導体集積回路101が受けたことなどが挙げられる。このトリガが発生するまで、S1604は自己遷移を続ける。S1604でトリガが発生したと判定されると、S1605に遷移して電力復帰動作を開始する。

**【0033】**

S1605ではシステム制御部106が、電源遮断状態の回路ブロックへの電力の供給を再開させる。詳細には、システム制御部106が電力制御部103に対し、電源遮断状態の回路ブロックへの電源供給の復帰を要求するコマンド(以下、復帰要求)を送信する。電力制御部103はこの復帰要求コマンドを受信後、パワースイッチ制御部105によって、電源遮断状態の回路ブロックへの電力の供給を開始する。そして、電源遮断状態の回路ブロックへの電荷のチャージが完了した後、S1606へ遷移する。

40

**【0034】**

S1606では、初期化制御部102がリセット動作対象である回路ブロック(リセット対象ブロック)の其々に対する初期化制御処理として、動作周波数や動作電圧を設定してシステム制御部106に該設定値を通知する。この初期化制御部102による初期化制御処理の詳細については後述する。この通知を受けたシステム制御部106は、クロック制御部118およびリセット制御部117に対して、リセット対象ブロックへのリセット動作を開始するように指

50

示を出す。

**【0035】**

次にS1607では、リセット動作を開始する指示を受けたクロック制御部118が、不図示のクロックゲートセルのゲーティングを無効化することにより、リセット対象ブロックに対してクロックの供給を再開する。なお、リセット対象ブロックのリセットが解除されるまで、クロックゲートセルの制御ピンは、クロックの供給を停止しているDisable状態のままで維持する。クロック制御部118はすなわち、少なくともリセット動作の開始命令(初期化動作命令)を受信してからリセットが解除されるまでの間、リセット対象ブロックにクロックを供給し続ける。

**【0036】**

10

S1607でシステム制御部106からのリセット動作命令を受信した後の所定時間、リセット対象ブロックへクロックを供給し続けた後、S1608でリセット制御部117が、リセット対象ブロックへのリセットを解除(リセット信号をデアサーント)する。なお、リセットにかかる時間経過の測定にはカウンタ回路などを用いればよく、カウンタ値に回路ブロックの回路規模等に応じた値を予め設定しておくことで、リセット期間が制御可能となる。

**【0037】**

リセット解除後、リセット対象ブロックは定常動作を開始できる状態になる。なお、システム制御部106へのリセット解除の通知は、リセット制御部117からの通知を受けたりセット動作完了受信部120によって行われる

S1609ではシステム制御部106が、リセット動作が未完了のリセット対象ブロックが有るか否かを判断し、該ブロックがあればS1606～S1608の処理を繰り返す。リセット動作未完了のリセット対象ブロックが無い場合は処理を終了とする。

20

**【0038】**

初期化制御処理(S1606)

以下、上記S1606で初期化制御部102が行う初期化制御(リセット制御)について、詳細に説明する。以下では便宜上、回路ブロックA、回路ブロックB、回路ブロックC、回路ブロックD、の4つの回路ブロックがリセット対象として指定された場合を例として説明する。

**【0039】**

図2は、S1606の初期化制御処理の詳細を示すフローチャートである。まずS201においてリセット要求受信部119が、システム制御部106から回路ブロックA,B,C,Dのリセット動作を要求するコマンドを受信する。受信された要求コマンドは、優先順位決定部110に通知される。そしてS202において優先順位決定部110が、クロックサイクル数保持部109から回路ブロックA,B,C,Dのリセット動作に要するクロックサイクル数を読み出す。ここで図4に、クロックサイクル数保持部109に保持されている、各回路ブロックのクロックサイクル数のテーブル例を示す。

30

**【0040】**

次にS203で優先順位決定部110が、クロックサイクル数の大小に応じて、回路ブロックA,B,C,Dのリセット動作の優先順位を決定する。ここで図9に、一般的なリセット動作におけるリセット所要時間や消費電力の特性として、サイクル数や周波数、電圧、温度等との関係を示す。図9(a)に示されるように、クロックサイクル数に比例してリセット動作に要する時間は増加する。したがって、複数の回路ブロックのリセット動作を同タイミングで行うと、クロックサイクル数が大きい回路ブロックがボトルネックとなり、リセット動作全体の期間が長期化してしまう。そこで優先順位決定部110では、ボトルネックとなり得るクロックサイクル数が大きい回路ブロックを優先的にリセット動作するように、優先順位を決定する。図4のクロックサイクル数に従えば、本実施形態におけるリセット動作の優先順位は、優先度が高い順から、回路ブロックB、回路ブロックA、回路ブロックC、回路ブロックDの順になる。

40

**【0041】**

次にS204に移り、対象回路ブロック選定部111が、動作パラメータの設定対象となる回路ブロックを選定する。回路ブロックの選定は、リセット動作の優先順位が高いブロック

50

から優先して行うため、本実施形態では回路ブロックBが最初に選定される。

#### 【0042】

次にS205で動作パラメータ選定部112が、S204で選定した回路ブロックをリセット動作させる際の動作パラメータの候補を、動作パラメータのテーブル情報を参照して選定する。この動作パラメータとしては動作周波数や動作電圧等が挙げられるが、以下では動作周波数のみを設定する場合を例として説明する。ここで図5に、各回路ブロックの動作パラメータのテーブル情報の例を示す。このテーブルは、電力データ記憶部107に予め保持されている。このテーブルに記載された動作パラメータを選定対象群として、動作パラメータ候補を選定する。同図によれば、図9(b),(d)にも示されるように、リセット動作の周波数が高いほど高速処理が行えるが、反面、ダイナミック電力が大きくなる。このように、リセット動作を早く完了させるには高い周波数を設定した方が良いので、ここでは回路ブロックBのリセット動作パラメータ候補として、高速用の周波数200MHzを選択する。詳細には、回路ブロックごとに、それぞれに割り当て可能な消費電力の範囲内で、リセット動作にかかる時間が最短となる動作パラメータを設定する。10

#### 【0043】

次にS206で消費電力予測部113が、今までに選定された動作パラメータでリセット動作を行った場合に、半導体集積回路101の全体における消費電力を予測する。すなわち、S204で選定した回路ブロックBを、S205で選定した動作パラメータ候補(周波数200MHz)でリセット動作させた場合における、半導体集積回路101の消費電力を予測する。この予測は、半導体集積回路101におけるリセット動作の開始前の消費電力に、リセット動作によって増加するであろう消費電力を加算することにより行われる。リセット動作で増加する消費電力は、リーク電力の増加分とダイナミック電力の増加分の加算として得られる。したがってここでは、リセット動作開始前の消費電力に、回路ブロックBを周波数200MHzでリセット動作させた時に増加するダイナミック電力とリーク電力を加算した値が、リセット動作時の半導体集積回路101の消費電力として算出される。20

#### 【0044】

ここで、消費電力予測部113における消費電力の予測処理の詳細について説明する。まず、リセット前の消費電力は、電力検出部108からの出力データ(電流・電圧データ)より算出可能である。そして、リセット動作で増加する消費電力は、リーク電力の増加分とダイナミック電力の増加分それぞれを算出し、合算することで得られる。30

#### 【0045】

リーク電力の増加分は、電力検出部108から温度データを取得し、並行して電力データ記憶部107からリセット動作による温度上昇見込みを取得し、両者を図9(f)に示すような温度とリーク電力の特性テーブルと照合することで得られる。なお、温度とリーク電力の特性テーブルは、電力データ記憶部107に格納されているものとする。図9(e),(f)に示されるようにリーク電力は、リセット動作の動作周波数には依存せず、チップ温度に依存して指数関数的に増加する。なお、電力検出部108によるチップ温度および電流/電圧検出の詳細については後述する。

#### 【0046】

一方、ダイナミック電力の増加分は、電力データ記憶部107から予測対象の回路ブロックについてのリセット動作時のダイナミック電力を読み出し、それぞれの回路ブロックのダイナミック電力を加算することで得られる。なお、電力データ記憶部107が保持する種々のデータは、半導体集積回路101の電源投入時のPower On Resetが解除された後に、予めファームウェア制御により設定しておけばよい。また、電力投入後に電力データ記憶部107の保持するデータを変更する場合は、必要に応じてファームウェア制御によって書き換えればよい。40

#### 【0047】

次にS207で予測結果判定部114が、S206で予測された消費電力が、半導体集積回路101における所定の基準消費電力以下であるかを確認する。消費電力が基準消費電力以下であればS208に移るが、基準消費電力を超えているのであればS205に戻り、動作パラメータを再50

設定する。この再設定時には、リセット動作によるダイナミック電力の増加分が減少するように、パラメータを設定する。例えば、回路ブロックBを200MHzでリセット動作させた時の消費電力の予測が基準消費電力を超えてしまった場合であれば、周波数を100MHzに再設定する。それでも基準消費電力を超えてしまう場合にはさらに周波数を50MHzに再設定する。それでも基準消費電力を超えてしまうのであれば、回路ブロックBについては割り当てる可能な消費電力ではリセット動作が不能であるとして、周波数を実質的にリセット動作を行わない10MHzに再設定して、S208に移る。ここで基準消費電力とは、半導体集積回路101が安定して動作するための指標で電力から導ける値であれば、電流値(規定電流)などであってもよい。

## 【0048】

10

次にS208で動作パラメータ設定部115が、S205で選定された動作パラメータ候補を、実際に適用するパラメータとしてリセット動作の制御レジスタ(不図示)に設定した後、この時点で動作パラメータが未設定である回路ブロックがあるかを確認する。未設定のブロックがある場合はS204に戻って該ブロックについて上述した処理を繰り返すが、未設定のブロックがない場合はS209に移る。本実施形態であれば、未だ回路ブロックBの動作パラメータしか設定していないので、S204に戻って、回路ブロックA,C,Dの順に動作パラメータを選定していく。

## 【0049】

全ての回路ブロックについて動作パラメータの設定が終了したら、S209でリセット動作開始指示部116がシステム制御部106に対して、設定した動作パラメータで各回路ブロックのリセット動作を開始するように要求する。以降、システム制御部106はリセット動作の開始要求に応じてクロック制御部118、リセット制御部117を制御して、各回路ブロックのリセット動作を開始する。このとき実質的には、S207で有効な周波数が設定された回路ブロックのみが、リセット動作を開始する。

20

## リセット推移例

以下、回路ブロックA,B,C,Dについて、上述したリセット処理の推移を図6、図7を用いて説明する。ここでは、半導体集積回路101の消費電力を基準消費電力以下とするために、ダイナミック電力の増加分を220mW以下にしなければならないという制約があるとする。また、リセット動作に必要なクロックサイクル数、リセット動作パラメータ、リセット動作時のダイナミック電力の増加見込み値は、図4、図5に示すテーブルに従うものとする。

30

## 【0050】

図6は、回路ブロックA,B,C,Dの全てのリセット動作が完了するまでに、動作パラメータがどのように遷移したかを示す図である。また図7は、動作パラメータの遷移に合わせて、ダイナミック電力の増加分がどのように遷移したかを示す図である。なお、図中のTs,T<sub>e</sub>はそれぞれ、全ブロックについてのリセット動作の開始、終了のタイミングを示す。さらに、例えばT<sub>as</sub>,T<sub>ae</sub>は回路ブロックAについてのリセット開始、完了のタイミングを示す。回路ブロックB,C,Dについても同様であり、例えばT<sub>bs</sub>,T<sub>be</sub>は回路ブロックBについてのリセット開始、終了のタイミングを示す。

## 【0051】

まず図6の601に示すようにTsのタイミングにおいて初期動作パラメータが設定される。すなわち、優先順位が最も高い回路ブロックBについてリセット動作モードが「高速」に設定されるため、図5よりダイナミック電力が150mWと見込まれる。するとダイナミック電力見込みの増加制限はあと70mWとなるため、次の優先順位である回路ブロックAについては、ダイナミック電力見込みが40mWである「中速」モードが設定される。そして次の優先順位である回路ブロックCについても同様に、ダイナミック電力見込みが30mWである「中速」モードが設定される。ここまで既にダイナミック電力見込みの総計が増加制限の220mWに到達してしまうため、次の優先順位である回路ブロックDについては「低速」モードすら設定できず、したがってリセット動作を行わないように設定される。

40

## 【0052】

次に602に示すように、まず回路ブロックCについてのリセット動作が終了(T<sub>ce</sub>)するこ

50

とにより、動作パラメータが以下のように更新される。これにより、回路ブロックCについてのダイナミック電力見込み分(30mW)がなくなるため、このタイミングで回路ブロックDについてのリセット動作が設定可能となり、電力見込み分が25mWである「中速」モードが設定される。すなわち、回路ブロックCのリセット終了タイミング(Tce)で、回路ブロックDのリセット開始(Tds)となる。

#### 【0053】

次に603に示すように、回路ブロックDについてのリセット動作が終了(Tde)すると、そのまま回路ブロックA,Bについてのリセット動作が継続される。そして604に示すように、回路ブロックA,Bのリセット終了タイミング(Tae,Tbe)で、全ブロックについてのリセット動作が終了(Te)となる。

10

#### 【0054】

このように図6および図7によれば、クロックサイクル数が大きい回路ブロックから優先して、高い周波数でリセット動作がなされていく様子が分かる。

#### 【0055】

また、図6に示した動作パラメータに則って、回路ブロックA,B,C,Dのリセット動作を実際に行った際のタイミングチャート例を図8に示す。

#### 【0056】

##### 電力検出部108の詳細構成

以下、電力検出部108の構成および動作について説明する。電力検出部108は、半導体集積回路101における電流および電圧データの検出のみならず、温度検出も行う。

20

#### 【0057】

図3は、電力検出部108の概略構成を示すブロック図である。図3において、センス抵抗301によって検出された電流は、増幅器307でゲインを増幅され、電流データ生成AD変換部302によってA/D変換された後に、消費電力予測部113に向けて出力される。なお、センス抵抗301によって検出される電流が十分大きい場合は増幅器307を設けなくてもよい。温度センサ305は、半導体集積回路101の温度(チップ温度)を検知する。検知された温度も同様に、温度データ生成AD変換部303によってA/D変換された後、消費電力予測部113に出力される。電源供給センサ306は、半導体集積回路101の各種電源電圧を検知する。検知された電源電圧は、電圧データ生成AD変換部304によってA/D変換された後、消費電力予測部113に出力される。なお、消費電力予測部113への出力は、上記図2のS206における、消費電力予測部113からの要求に応じて行われる。

30

#### 【0058】

以上説明したように本実施形態によれば、半導体集積回路における複数の回路ブロックに対するリセット動作中に、各回路ブロックの動作パラメータを基準消費電力を満たす範囲で動的に書き換えることにより、効率の良いリセット動作を実現できる。

#### 【0059】

##### <第2実施形態>

以下、本発明に係る第2実施形態について説明する。上述した第1実施形態ではリセット動作の動作パラメータを周波数のみとして説明したが、第2実施形態では動作パラメータを周波数と電圧とした例を示す。なお、第2実施形態における半導体集積回路101の全体構成は、上述した第1実施形態の図1とほぼ同様であるが、第2実施形態では図1の構成に電圧生成部(不図示)が追加される。第2実施形態における電力制御の基本動作についても、第1実施形態の図2とほぼ同様である。

40

#### 【0060】

##### 初期化制御処理(S1606)

以下、図1のS1606における、第2実施形態の初期化制御(リセット制御)処理について、図17のフローチャートを用いて詳細に説明する。図17において、第1実施形態の図2と同様の処理を行うステップには同一ステップ番号を付し、説明を省略する。図17では、S1705で動作パラメータを設定する際に、周波数に加えて電圧を設定することを特徴とする。

#### 【0061】

50

第2実施形態におけるリセット処理は、第1実施形態とは以下の2点が相違する。まず1つ目は、電力データ記憶部107において、第1実施形態では周波数条件の電力情報だけが格納されているのに対し、第2実施形態では、周波数と電圧、双方の条件に合わせた電力情報が格納されている点が異なる。図10に、第2実施形態における各回路ブロック(A~D)の動作パラメータのテーブル情報の例を示す。第1実施形態で図5に示したテーブル例と比較すると、動作パラメータとして周波数に加えて電圧が追加されたことで、リセット動作モードとして「高速」「中速」「低速」に加えて、「超高速」および「超低速」の設定が可能となっている。図10によれば、図9(c)にも示されるように、リセット動作の電圧が高いほどダイナミック電力が大きくなる。

## 【0062】

10

第1実施形態との2つ目の相違点としては、動作パラメータを設定するレジスタ種である。第1実施形態では周波数を制御するためのレジスタ(不図示)にパラメータを設定するのみであったが、第2実施形態では、周波数を制御するためのレジスタに加えて、電圧を制御するレジスタに対しても設定が必要となる。実際のリセット動作では、まず電圧を制御するレジスタにセットされた値に基づき、電圧生成部(不図示)で電圧が生成される。その後クロック制御部118において、周波数を制御するレジスタにセットされた値に基づいてクロックが生成され、回路ブロックに対して出力される。

## 【0063】

## リセット推移例

以下、回路ブロックA,B,C,Dについて、第2実施形態のリセット処理が行われる場合の推移を図11、図12を用いて説明する。ここでは、半導体集積回路101の消費電力を基準消費電力以下とするにはダイナミック電力の増加分を450mW以下にしなければならないという制約があるとする。また、リセット動作に必要なクロックサイクル数、リセット動作パラメータ、リセット動作時のダイナミック電力の増加見込み値は、図4、図10に示すテーブルに従うものとする。

20

## 【0064】

図11は、回路ブロックA,B,C,Dの全てのリセット動作が完了するまでに、動作パラメータ(周波数、電圧)がどのように遷移したかを示す図である。また図12は、動作パラメータの遷移に合わせて、ダイナミック電力の増加分がどのように遷移したかを示す図である。図11および図12によれば、第1実施形態と同様に、クロックサイクル数が大きい回路ブロック順に、高い周波数でリセット動作がなされていくが、各回路ブロックに対するリセット動作モードの動的変化が、第1実施形態よりもさらに細かく制御されている。

30

## 【0065】

図11に示した動作パラメータに則って、回路ブロックA,B,C,Dのリセット動作を実際に行った際のタイミングチャート例を図13に示す。特筆すべきは、例えば回路ブロックDに顕著であるが、「超高速」モードを含めたリセット動作モードの動的切り替えが第1実施形態よりも細かくなされている点である。したがって第1実施形態における図8のタイミングチャートに示す例よりも、リセット動作状態である時間、すなわち $T_s$ から $T_e$ までの全体リセット動作期間が短縮されている点である。

## 【0066】

40

以上説明したように第2実施形態によれば、リセット動作の動作パラメータとして周波数と電圧を設定可能とすることで、リセット動作時のダイナミック電力の増加量を、第1実施形態よりも細かく制御することができる。よって、さらに効率の良いリセット動作が実現される。

## 【0067】

## &lt;第3実施形態&gt;

以下、本発明に係る第3実施形態について説明する。第3実施形態における半導体集積回路101の全体構成を図14に示す。図14において、上述した第1実施形態で示した図1と同様の構成には同一番号を付し、説明を省略する。図14では、リセット制御部117とクロック制御部118がシステム制御部106の制御下にない点が図1とは異なる。

50

**【 0 0 6 8 】**

上述した第1実施形態では、システム制御部106が初期化制御部102からのリセット動作開始指示を受けて、リセット制御部117やクロック制御部118を制御する例を示した。第3実施形態では、初期化制御部102の内部にてリセット制御部117やクロック制御部118を制御する例を示す。さらに、複数の回路ブロックのリセット動作において、全ての回路ブロックのリセット動作が完了するまでの制御を、初期化制御部102内部で閉じて実施する。

**【 0 0 6 9 】**

つまり、第3実施形態のシステム制御部106は、複数の回路ブロックのリセット要求を初期化制御部102に発行したら、後はリセット要求した回路ブロックの全てについてのリセット動作が完了した旨の信号が返ってくるのを待っているだけでよい。従って、第3実施形態では図14に示すように、リセット動作開始指示部116の出力がリセット制御部117およびクロック制御部118に直接接続されている。また、リセット動作完了受信部120の出力が、システム制御部106だけでなくリセット要求受信部119にも接続されている。10

**【 0 0 7 0 】**

以上説明したように第3実施形態によれば、第1実施形態ではシステム制御部106で行っていたリセット制御・クロック制御の負荷を、初期化制御部102において担うことが可能となる。

**【 0 0 7 1 】****< 第4実施形態 >**

以下、本発明に係る第4実施形態について説明する。上述した第1～第3実施形態では、半導体集積回路101の内部に電力検出部108や電力データ記憶部107を設ける例を示したが、これらの構成は同一のシステム(または情報処理装置)内にあれば、半導体集積回路101の外部に設置されていても良い。20

**【 0 0 7 2 】**

図15に、第4実施形態における省電力システム1501の概略構成例を示す。同図に示す省電力システム1501は例えば、半導体集積回路101が実装されたプリント基板として実現される。記憶部1502は、回路ブロック部104を構成する各回路ブロックのリセット動作時のダイナミック電力の增加分とその時の温度上昇値、および図9(f)に示すような半導体集積回路101の温度-リーケ特性を含む予測用データを保持している。なお、記憶部1402には、半導体集積回路101の起動時に使用するブートプログラム等も格納されている。30

**【 0 0 7 3 】**

以上説明したように第4実施形態によれば、半導体集積回路101に電力検出部108や電力データ記憶部107を設ける必要がなくなるため、半導体集積回路101のチップサイズを小さくしてコストダウンを図ることができる。

**【 0 0 7 4 】****< その他の実施形態 >**

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又はコンピュータ可読の各種記憶媒体を介してシステム或いは装置に供給する。そして、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。40

【図1】

【図2】

【図3】

【図5】

|           | 回路ブロックA |      |      |       | 回路ブロックB |      |        |        | 回路ブロックC |       |        |        | 回路ブロックD |        |        |       |

|-----------|---------|------|------|-------|---------|------|--------|--------|---------|-------|--------|--------|---------|--------|--------|-------|

|           | 高速      | 中速   | 低速   | 高速    | 中速      | 低速   | 高速     | 中速     | 低速      | 高速    | 中速     | 低速     | 高速      | 中速     | 低速     | 低速    |

| クロックサイクル数 | 45      | 90   | 20   | 150mW | 75mW    | 38mW | 200MHz | 100MHz | 50MHz   | 50MHz | 200MHz | 100MHz | 50MHz   | 200MHz | 100MHz | 50MHz |

| 電力見込み     | 80mW    | 40mW | 20mW | 150mW | 75mW    | 38mW | 60mW   | 30mW   | 15mW    | 50mW  | 25mW   | 13mW   | 50mW    | 25mW   | 13mW   | 13mW  |

【図6】

初期動作パラメータ( $T_s$ )

|              | 回路ブロックA | 回路ブロックB | 回路ブロックC | 回路ブロックD   | 合計    |

|--------------|---------|---------|---------|-----------|-------|

| リセット動作モード    | 中速      | 高速      | 中速      | リセット動作しない |       |

| 動作パラメータ(周波数) | 100MHz  | 200MHz  | 100MHz  | 0MHz      |       |

| ダイナミック電力見込み  | 40mW    | 150mW   | 30mW    | 0mW       | 220mW |

動作パラメータ更新( $T_{ce}$ )

|              | 回路ブロックA | 回路ブロックB | 回路ブロックC | 回路ブロックD | 合計    |

|--------------|---------|---------|---------|---------|-------|

| リセット動作モード    | 中速      | 高速      | リセット動作完 | 中速      |       |

| 動作パラメータ(周波数) | 100MHz  | 200MHz  | 0MHz    | 100MHz  |       |

| ダイナミック電力見込み  | 40mW    | 150mW   | 0mW     | 25mW    | 215mW |

動作パラメータ更新( $T_{de}$ )

|              | 回路ブロックA | 回路ブロックB | 回路ブロックC | 回路ブロックD | 合計    |

|--------------|---------|---------|---------|---------|-------|

| リセット動作モード    | 中速      | 高速      | リセット動作完 | リセット動作完 |       |

| 動作パラメータ(周波数) | 100MHz  | 200MHz  | 0MHz    | 0MHz    |       |

| ダイナミック電力見込み  | 40mW    | 150mW   | 0mW     | 0mW     | 190mW |

リセット動作完了( $T_{ae}$ ,  $T_{be}$ ,  $T_{ce}$ )

|              | 回路ブロックA | 回路ブロックB | 回路ブロックC | 回路ブロックD | 合計  |

|--------------|---------|---------|---------|---------|-----|

| リセット動作モード    | リセット動作完 | リセット動作完 | リセット動作完 | リセット動作完 |     |

| 動作パラメータ(周波数) | 0MHz    | 0MHz    | 0MHz    | 0MHz    |     |

| ダイナミック電力見込み  | 0mW     | 0mW     | 0mW     | 0mW     | 0mW |

【図7】

【図8】

【図9】

【図10】

|                |           | 回路ブロックD                                                |                                              |                                              |                                                           |

|----------------|-----------|--------------------------------------------------------|----------------------------------------------|----------------------------------------------|-----------------------------------------------------------|

|                |           | 低速                                                     | 中速                                           | 高速                                           | 超高速                                                       |

| 回路ブロックC        | 低速        | 25MHz<br>50MHz<br>100MHz<br>200MHz<br>400MHz<br>800MHz | 1.1V<br>1.1V<br>1.1V<br>1.1V<br>1.3V<br>1.3V | 1.1V<br>1.1V<br>1.1V<br>1.1V<br>1.3V<br>1.3V | 0.9W<br>5mW<br>10mW<br>20mW<br>40mW<br>80mW               |

|                | 中速        | 25MHz<br>50MHz<br>100MHz<br>200MHz<br>400MHz<br>800MHz | 1.1V<br>1.1V<br>1.1V<br>1.1V<br>1.3V<br>1.3V | 1.1V<br>1.1V<br>1.1V<br>1.1V<br>1.3V<br>1.3V | 5mW<br>10mW<br>20mW<br>40mW<br>80mW<br>160mW              |

| 回路ブロックB        | 高速        | 25MHz<br>50MHz<br>100MHz<br>200MHz<br>400MHz<br>800MHz | 1.1V<br>1.1V<br>1.1V<br>1.1V<br>1.3V<br>1.3V | 1.1V<br>1.1V<br>1.1V<br>1.1V<br>1.3V<br>1.3V | 15mW<br>30mW<br>60mW<br>120mW<br>240mW<br>480mW           |

|                | 超高速       | 25MHz<br>50MHz<br>100MHz<br>200MHz<br>400MHz<br>800MHz | 1.1V<br>1.1V<br>1.1V<br>1.1V<br>1.3V<br>1.3V | 1.1V<br>1.1V<br>1.1V<br>1.1V<br>1.3V<br>1.3V | 6.7mW<br>13.4mW<br>26.8mW<br>53.6mW<br>107.2mW<br>214.4mW |

| 回路ブロックA        | 超高速       | 25MHz<br>50MHz<br>100MHz<br>200MHz<br>400MHz<br>800MHz | 1.1V<br>1.1V<br>1.1V<br>1.1V<br>1.3V<br>1.3V | 1.1V<br>1.1V<br>1.1V<br>1.1V<br>1.3V<br>1.3V | 20mW<br>40mW<br>80mW<br>160mW<br>320mW<br>640mW           |

|                | リセット動作モード | 400MHz<br>800MHz                                       | 1.3V<br>1.3V                                 | 1.1V<br>1.1V                                 | 419mW<br>223mW                                            |

| 動作パラメータ(電圧)    |           | 400MHz<br>800MHz                                       | 0.9V<br>0.9V                                 | 0.9V<br>0.9V                                 | 4.4mW<br>223mW                                            |

| 動作パラメータ(電力見込み) |           | 400MHz<br>800MHz                                       | 223mW<br>223mW                               | 0mW<br>0mW                                   | 448.4mW<br>440.6mW                                        |

【図11】

| 初期動作/パラメータ(Ts) |         |         |         |         | 1101    |

|----------------|---------|---------|---------|---------|---------|

|                | 回路ブロックA | 回路ブロックB | 回路ブロックC | 回路ブロックD | 合計      |

| リセット動作モード      | 低速      | 超高速     | 超低速     | 超低速     |         |

| 動作パラメータ(周波数)   | 50MHz   | 400MHz  | 25MHz   | 25MHz   |         |

| 動作パラメータ(電圧)    | 1.1V    | 1.3V    | 0.9V    | 0.9V    |         |

| ダイナミック電力見込み    | 20mW    | 419mW   | 5mW     | 4.4mW   | 448.4mW |

| 動作パラメータ更新(Tbe) |         |         |         |         | 1102    |

|----------------|---------|---------|---------|---------|---------|

|                | 回路ブロックA | 回路ブロックB | 回路ブロックC | 回路ブロックD | 合計      |

| リセット動作モード      | 超高速     | リセット動作完 | 超高速     | 高速      |         |

| 動作パラメータ(周波数)   | 400MHz  | 0MHz    | 400MHz  | 200MHz  |         |

| 動作パラメータ(電圧)    | 1.3V    | 1.1V    | 1.3V    | 1.1V    |         |

| ダイナミック電力見込み    | 223mW   | 0mW     | 167.6mW | 50mW    | 440.6mW |

| 動作パラメータ更新(Tce) |         |         |         |         | 1103  |

|----------------|---------|---------|---------|---------|-------|

|                | 回路ブロックA | 回路ブロックB | 回路ブロックC | 回路ブロックD | 合計    |

| リセット動作モード      | 超高速     | リセット動作完 | リセット動作完 | 超高速     |       |

| 動作パラメータ(周波数)   | 400MHz  | 0MHz    | 0MHz    | 400MHz  |       |

| 動作パラメータ(電圧)    | 1.3V    | 1.1V    | 1.1V    | 1.3V    |       |

| ダイナミック電力見込み    | 223mW   | 0mW     | 0mW     | 140mW   | 363mW |

| 動作パラメータ更新(Tde) |         |         |         |         | 1104  |

|----------------|---------|---------|---------|---------|-------|

|                | 回路ブロックA | 回路ブロックB | 回路ブロックC | 回路ブロックD | 合計    |

| リセット動作モード      | 超高速     | リセット動作完 | リセット動作完 | リセット動作完 |       |

| 動作パラメータ(周波数)   | 400MHz  | 0MHz    | 0MHz    | 0MHz    |       |

| 動作パラメータ(電圧)    | 1.3V    | 1.1V    | 1.1V    | 1.1V    |       |

| ダイナミック電力見込み    | 223mW   | 0mW     | 0mW     | 0mW     | 223mW |

| 動作パラメータ更新(Tae, Te) |         |         |         |         | 1105 |

|--------------------|---------|---------|---------|---------|------|

|                    | 回路ブロックA | 回路ブロックB | 回路ブロックC | 回路ブロックD | 合計   |

| リセット動作モード          | リセット動作完 | リセット動作完 | リセット動作完 | リセット動作完 |      |

| 動作パラメータ(周波数)       | 0MHz    | 0MHz    | 0MHz    | 0MHz    |      |

| 動作パラメータ(電圧)        | 1.1V    | 1.1V    | 1.1V    | 1.1V    |      |

| ダイナミック電力見込み        | 0mW     | 0mW     | 0mW     | 0mW     | 0mW  |

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(72)発明者 加山 和也

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 宮下 誠

(56)参考文献 特開2009-054031(JP,A)

特開2013-206309(JP,A)

米国特許第06429704(US,B1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 1 / 26

G 06 F 1 / 22

G 06 F 1 / 04