(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6176062号

(P6176062)

(45) 発行日 平成29年8月9日(2017.8.9)

(24) 登録日 平成29年7月21日(2017.7.21)

(51) Int.Cl.

F 1

H04N 5/369 (2011.01)

H04N 5/369

H04N 5/3745 (2011.01)

H04N 5/3745 700

H01L 27/146 (2006.01)

H01L 27/146 A

請求項の数 11 (全 19 頁)

(21) 出願番号

特願2013-230219 (P2013-230219)

(22) 出願日

平成25年11月6日 (2013.11.6)

(65) 公開番号

特開2015-91025 (P2015-91025A)

(43) 公開日

平成27年5月11日 (2015.5.11)

審査請求日

平成28年2月9日 (2016.2.9)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100082131

弁理士 稲本 義雄

(74) 代理人 100121131

弁理士 西川 孝

(72) 発明者 石渡 宏明

東京都港区港南1丁目7番1号 ソニー株

式会社内

(72) 発明者 城戸 英男

東京都港区港南1丁目7番1号 ソニー株

式会社内

最終頁に続く

(54) 【発明の名称】 固体撮像装置およびその駆動方法、並びに電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素として、撮像画像を生成するための撮像画素と、位相差検出を行うための位相差検出画素とが配置された画素アレイ部を備え、

前記位相差検出画素は、

第1および第2の光電変換部と、

前記第1および第2の光電変換部それぞれに蓄積された電荷を電圧に変換する2つのFD(フローティングディフュージョン)と、

前記FDそれぞれの電圧を増幅する2つの増幅トランジスタと

を有し、

前記第1の光電変換部は、前記位相差検出画素に隣接する第1の撮像画素と、前記FDおよび前記増幅トランジスタを共有し、

前記第2の光電変換部は、前記位相差検出画素に隣接する、前記第1の撮像画素とは異なる第2の撮像画素と、前記FDおよび前記増幅トランジスタを共有し、

前記位相差検出画素と前記第1の撮像画素とは、1つの画素共有単位に含まれ、

前記第2の撮像画素は他の画素共有単位に含まれ、

前記増幅トランジスタを含む画素トランジスタは、前記画素共有単位を構成する画素同士の間に配置される

固体撮像装置。

## 【請求項 2】

10

20

前記画素共有単位は、

前記画素共有単位を構成する画素それぞれの前記FDに蓄積されている電荷を排出するリセットトランジスタと、

前記リセットトランジスタそれぞれに接続され、前記画素共有単位を構成する画素それぞれの前記FDの容量を変化させる変換効率切替トランジスタとを有する

請求項1に記載の固体撮像装置。

【請求項3】

前記リセットトランジスタそれぞれのソースは、前記画素共有単位を構成する画素それぞれの前記FDに接続され、

前記リセットトランジスタそれぞれのドレインは、前記変換効率切替トランジスタのソースに接続される

請求項2に記載の固体撮像装置。

【請求項4】

前記FDは、STI (Shallow Trench Isolation) による素子分離領域に囲まれて形成される

請求項1乃至3のいずれかに記載の固体撮像装置。

【請求項5】

前記第2の撮像画素を含む前記画素共有単位は、前記位相差検出画素と前記第1の撮像画素とを含む前記画素共有単位の隣接行に配置される

請求項1に記載の固体撮像装置。

【請求項6】

前記第2の光電変換部に対応する前記FDと、前記第2の撮像画素の前記FDとの間に、前記第2の光電変換部に蓄積された電荷を読み出すための読み出し用トランジスタが形成される

請求項5に記載の固体撮像装置。

【請求項7】

前記画素はそれぞれ、前記光電変換部に蓄積された電荷を前記FDに転送する転送トランジスタを有し、

前記転送トランジスタは、矩形状に形成される前記光電変換部の角部に形成される

請求項1乃至6のいずれかに記載の固体撮像装置。

【請求項8】

前記画素共有単位は、縦2画素共有で構成される

請求項1乃至7のいずれかに記載の固体撮像装置。

【請求項9】

前記画素共有単位は、 $2 \times 2$ 画素共有で構成される

請求項1乃至7のいずれかに記載の固体撮像装置。

【請求項10】

複数の画素として、撮像画像を生成するための撮像画素と、位相差検出を行うための位相差検出画素とが配置された画素アレイ部を備え、

前記位相差検出画素が、第1および第2の光電変換部と、前記第1および第2の光電変換部それぞれに蓄積された電荷を電圧に変換する2つのFD (フローティングディフュージョン)と、前記FDそれぞれの電圧を増幅する2つの増幅トランジスタとを有し、

前記第1の光電変換部は、前記位相差検出画素に隣接する第1の撮像画素と、前記FDおよび前記増幅トランジスタを共有し、

前記第2の光電変換部は、前記位相差検出画素に隣接する、前記第1の撮像画素とは異なる第2の撮像画素と、前記FDおよび前記増幅トランジスタを共有し、

前記位相差検出画素と前記第1の撮像画素とは、1つの画素共有単位に含まれ、

前記第2の撮像画素は他の画素共有単位に含まれ、

前記増幅トランジスタを含む画素トランジスタは、前記画素共有単位を構成する画素同士の間に配置される固体撮像装置の駆動方法であって、

10

20

30

40

50

前記固体撮像装置が、

前記位相差検出画素において、前記第1および第2の光電変換部における電荷の蓄積、および、前記第1および第2の光電変換部に蓄積された電荷に対応する信号の読み出しを、それぞれ同時に行う

ステップを含む固体撮像装置の駆動方法。

【請求項11】

複数の画素として、撮像画像を生成するための撮像画素と、位相差検出を行うための位相差検出画素とが配置された画素アレイ部を備え、

前記位相差検出画素は、

第1および第2の光電変換部と、

10

前記第1および第2の光電変換部それぞれに蓄積された電荷を電圧に変換する2つのFD(フローティングディフィュージョン)と、

前記FDそれぞれの電圧を増幅する2つの増幅トランジスタと

を有し、

前記第1の光電変換部は、前記位相差検出画素に隣接する第1の撮像画素と、前記FDおよび前記増幅トランジスタを共有し、

前記第2の光電変換部は、前記位相差検出画素に隣接する、前記第1の撮像画素とは異なる第2の撮像画素と、前記FDおよび前記増幅トランジスタを共有し、

前記位相差検出画素と前記第1の撮像画素とは、1つの画素共有単位に含まれ、

前記第2の撮像画素は他の画素共有単位に含まれ、

20

前記増幅トランジスタを含む画素トランジスタは、前記画素共有単位を構成する画素同士の間に配置される固体撮像装置

を備える電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本技術は、固体撮像装置およびその駆動方法、並びに電子機器に関し、特に、AF速度とAF精度の向上を図ることができるようとする固体撮像装置およびその駆動方法、並びに電子機器に関する。

【背景技術】

30

【0002】

画素アレイ部に、撮像画素とともに位相差検出画素を設け、一対の位相差検出画素によって出力される信号のずれ量に基づいてAF(Auto Focus)を行う、いわゆる位相差検出方式によるAFを行う固体撮像装置が知られている。

【0003】

このような固体撮像装置の中には、1画素内に2つの光電変換部を設けることで、位相差検出画素の数を増やし、AF精度を向上させるようにしたものがある(例えば、特許文献1,2参照)。

【先行技術文献】

【特許文献】

40

【0004】

【特許文献1】特開2012-165070号公報

【特許文献2】特開2007-243744号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1の位相差検出画素においては、2つの光電変換部が1つの増幅トランジスタを共有しているため、2つの光電変換部それぞれの露光、読み出しを行なうことができず、動きの速い被写体に対するAFの追従が不十分となってしまう。

【0006】

50

一方、特許文献2の位相差検出画素においては、2つの光電変換部それについて、電荷を蓄積する電荷格納部を設けることで、2つの光電変換部それとの露光、読み出しを同時に行うことが可能とされる。

【0007】

しかしながら、電荷格納部を設けることで光電変換部の面積が小さくなつて、位相差検出画素の感度が低下し、AF精度が下がつてしまつ。

【0008】

本技術は、このような状況に鑑みてなされたものであり、AF速度とAF精度の向上を図ることができるようとするものである。

【課題を解決するための手段】

10

【0009】

本技術の一側面の固体撮像装置は、複数の画素として、撮像画像を生成するための撮像画素と、位相差検出を行うための位相差検出画素とが配置された画素アレイ部を備え、前記位相差検出画素は、第1および第2の光電変換部と、前記第1および第2の光電変換部それぞれに蓄積された電荷を電圧に変換する2つのFD（フローティングディフュージョン）と、前記FDそれぞれの電圧を増幅する2つの増幅トランジスタとを有し、前記第1の光電変換部は、前記位相差検出画素に隣接する第1の撮像画素と、前記FDおよび前記増幅トランジスタを共有し、前記第2の光電変換部は、前記位相差検出画素に隣接する、前記第1の撮像画素とは異なる第2の撮像画素と、前記FDおよび前記増幅トランジスタを共有し、前記位相差検出画素と前記第1の撮像画素とは、1つの画素共有単位に含まれ、前記第2の撮像画素は他の画素共有単位に含まれ、前記増幅トランジスタを含む画素トランジスタは、前記画素共有単位を構成する画素同士の間に配置される。

20

【0013】

本技術の一側面の固体撮像装置の駆動方法は、複数の画素として、撮像画像を生成するための撮像画素と、位相差検出を行うための位相差検出画素とが配置された画素アレイ部を備え、前記位相差検出画素が、第1および第2の光電変換部と、前記第1および第2の光電変換部それぞれに蓄積された電荷を電圧に変換する2つのFD（フローティングディフュージョン）と、前記FDそれぞれの電圧を増幅する2つの増幅トランジスタとを有し、前記第1の光電変換部は、前記位相差検出画素に隣接する第1の撮像画素と、前記FDおよび前記増幅トランジスタを共有し、前記第2の光電変換部は、前記位相差検出画素に隣接する、前記第1の撮像画素とは異なる第2の撮像画素と、前記FDおよび前記増幅トランジスタを共有し、前記位相差検出画素と前記第1の撮像画素とは、1つの画素共有単位に含まれ、前記第2の撮像画素は他の画素共有単位に含まれ、前記増幅トランジスタを含む画素トランジスタは、前記画素共有単位を構成する画素同士の間に配置される固体撮像装置の駆動方法であつて、前記固体撮像装置が、前記位相差検出画素において、前記第1および第2の光電変換部における電荷の蓄積、および、前記第1および第2の光電変換部に蓄積された電荷に対応する信号の読み出しを、それぞれ同時に行うステップを含む。

30

【0014】

本技術の一側面の電子機器は、複数の画素として、撮像画像を生成するための撮像画素と、位相差検出を行うための位相差検出画素とが配置された画素アレイ部を備え、前記位相差検出画素は、第1および第2の光電変換部と、前記第1および第2の光電変換部それぞれに蓄積された電荷を電圧に変換する2つのFD（フローティングディフュージョン）と、前記FDそれぞれの電圧を増幅する2つの増幅トランジスタとを有し、前記第1の光電変換部は、前記位相差検出画素に隣接する第1の撮像画素と、前記FDおよび前記増幅トランジスタを共有し、前記第2の光電変換部は、前記位相差検出画素に隣接する、前記第1の撮像画素とは異なる第2の撮像画素と、前記FDおよび前記増幅トランジスタを共有し、前記位相差検出画素と前記第1の撮像画素とは、1つの画素共有単位に含まれ、前記第2の撮像画素は他の画素共有単位に含まれ、前記増幅トランジスタを含む画素トランジスタは、前記画素共有単位を構成する画素同士の間に配置される固体撮像装置を備える。

40

【0015】

50

本技術の一側面においては、位相差検出画素において、2つのFDによって、第1および第2の光電変換部それに蓄積された電荷が電圧に変換され、2つの増幅トランジスタによって、FDそれぞれの電圧が増幅される。第1の光電変換部において、位相差検出画素に隣接する第1の撮像画素と、FDおよび増幅トランジスタが共有され、第2の光電変換部において、位相差検出画素に隣接する、第1の撮像画素とは異なる第2の撮像画素と、FDおよび増幅トランジスタが共有され、位相差検出画素と第1の撮像画素とは、1つの画素共有単位に含まれ、第2の撮像画素は他の画素共有単位に含まれ、増幅トランジスタを含む画素トランジスタは、画素共有単位を構成する画素同士の間に配置される。

【発明の効果】

【0016】

本技術の一側面によれば、AF速度とAF精度の向上を図ることが可能となる。

10

【図面の簡単な説明】

【0017】

【図1】本技術を適用した固体撮像装置を備える電子機器の構成例を示すブロック図である。

【図2】画素配置について説明する図である。

【図3】FDおよび増幅トランジスタの共有について説明する図である。

【図4】本技術の第1の実施の形態の画素の構成例を示す平面図である。

【図5】本技術の第1の実施の形態の画素の構成例を示す回路図である。

【図6】本技術の第1の実施の形態の画素の他の構成例を示す平面図である。

20

【図7】本技術の第1の実施の形態の画素の他の構成例を示す回路図である。

【図8】本技術の第2の実施の形態の画素の構成例を示す平面図である。

【図9】本技術の第2の実施の形態の画素の構成例を示す回路図である。

【図10】FDの構成について説明するフローチャートである。

【図11】FDの構成について説明するフローチャートである。

【図12】本技術の第3の実施の形態の画素の構成例を示す平面図である。

【図13】本技術の第3の実施の形態の画素の構成例を示す回路図である。

【図14】本技術の第3の実施の形態の画素の他の構成例を示す平面図である。

【図15】本技術の第3の実施の形態の画素の他の構成例を示す回路図である。

【発明を実施するための形態】

30

【0018】

以下、本技術の実施の形態について図を参照して説明する。

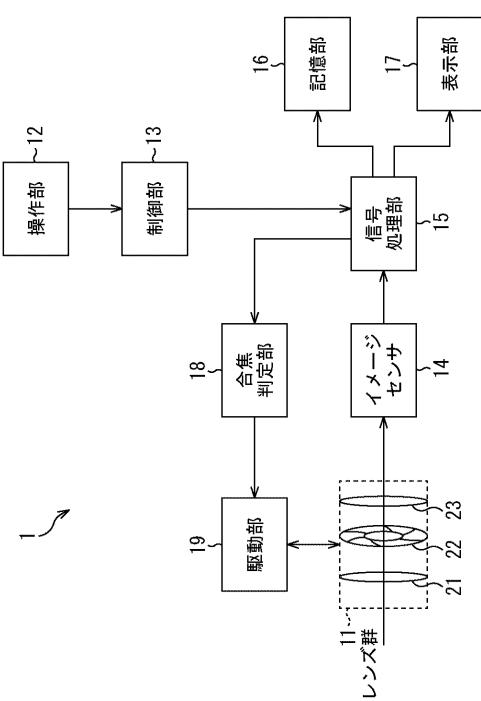

【0019】

<電子機器の機能構成例>

図1は、本技術を適用した固体撮像装置を備える電子機器の一実施の形態を示すブロック図である。

【0020】

図1の電子機器1は、デジタルカメラや撮像機能を有する携帯端末等として構成され、AF(Auto Focus)機能により、被写体を撮像して撮像画像を生成し、静止画像または動画像として記録する。以下においては、主に静止画像が記録されるものとする。

40

【0021】

電子機器1は、レンズ部11、操作部12、制御部13、イメージセンサ14、信号処理部15、記憶部16、表示部17、合焦判定部18、および駆動部19から構成される。

【0022】

レンズ部11は、被写体からの光(被写体光)を集光する。レンズ部11により集光された被写体光は、イメージセンサ14に入射される。

【0023】

レンズ部11は、ズームレンズ21、絞り22、フォーカスレンズ23を備えている。

【0024】

50

ズームレンズ21は、駆動部19の駆動により光軸方向に移動することにより焦点距離を変動させて、撮像画像に含まれる被写体の倍率を調整する。絞り22は、駆動部19の駆動により開口の度合いを変化させて、イメージセンサ14に入射する被写体光の光量を調整する。フォーカスレンズ23は、駆動部19の駆動により光軸方向に移動することによりフォーカスを調整する。

【0025】

操作部12は、ユーザからの操作を受け付ける。操作部12は、例えば、シャッターボタン(図示せず)が押下された場合、その旨の操作信号を制御部13に供給する。

【0026】

制御部13は、電子機器1の各部の動作を制御する。 10

【0027】

例えば、制御部13は、シャッターボタンが押下された旨の操作信号を受け付けた場合、静止画像の記録の指示を、信号処理部15に供給する。また、制御部13は、表示部17に、被写体のリアルタイムな画像であるライブビュー画像を表示する場合、ライブビュー画像の生成の指示を、信号処理部15に供給する。

【0028】

また、制御部13は、位相差検出方式によりフォーカスの合焦判定を行う場合、合焦判定を行う動作(位相差検出動作)の指示を、信号処理部15に供給する。位相差検出方式とは、撮像レンズを通過した光を瞳分割して一対の像を形成し、形成された像の間隔(像の間のずれ量)を計測(位相差を検出)することによって合焦の度合いを検出する焦点検出方法である。 20

【0029】

イメージセンサ14は、受光した被写体光を電気信号に光電変換する固体撮像装置である。

【0030】

例えば、イメージセンサ14は、CMOS(Complementary Metal Oxide Semiconductor)イメージセンサやCCD(Charge Coupled Device)イメージセンサ等により実現される。イメージセンサ14がCMOSイメージセンサである場合、表面照射型であってもよいし、裏面照射型であってもよい。また、イメージセンサ14が裏面照射型のCMOSイメージセンサである場合、画素アレイ部を含む半導体基板とロジック回路を含む半導体基板とを貼り合わせた、積層型のCMOSイメージセンサとして構成されるようにしてもよい。 30

【0031】

イメージセンサ14は、複数の画素として、受光した被写体光に基づいて撮像画像を生成するための信号を生成する画素(撮像画素)と、位相差検出を行うための信号を生成する画素(位相差検出画素)とが配置される画素アレイ部を備える。イメージセンサ14は、光電変換により発生した電気信号を信号処理部15に供給する。

【0032】

信号処理部15は、イメージセンサ14から供給された電気信号に対して各種の信号処理を施す。

【0033】

例えば、信号処理部15は、制御部13から静止画像の記録の指示が供給されている場合、静止画像のデータ(静止画像データ)を生成し、記憶部16に供給する。また、信号処理部15は、制御部13からライブビュー画像の生成の指示が供給されている場合、イメージセンサ14における撮像画素からの出力信号に基づいて、ライブビュー画像のデータ(ライブビュー画像データ)を生成し、表示部17に供給する。 40

【0034】

また、信号処理部15は、制御部13から位相差検出動作の指示が供給されている場合、イメージセンサ14における位相差検出画素からの出力信号に基づいて、位相差を検出するためのデータ(位相差検出用データ)を生成し、合焦判定部18に供給する。

【0035】

記憶部 16 は、信号処理部 15 から供給された画像データを記録する。記憶部 16 は、例えば、DVD (Digital Versatile Disk) 等のディスクやメモリカード等の半導体メモリ等、1 または複数のリムーバブルな記録媒体として構成される。これらの記録媒体は、電子機器 1 に内蔵されるようにしてもよいし、電子機器 1 から着脱可能とするようにしてもよい。

【0036】

表示部 17 は、信号処理部 15 から供給された画像データに基づいて、画像を表示する。例えば、表示部 17 は、信号処理部 15 からライブビュー画像データが供給された場合、ライブビュー画像を表示する。表示部 17 は、例えば、LCD (Liquid Crystal Display) や有機EL (Electro-Luminescence) ディスプレイ等により実現される。

10

【0037】

合焦判定部 18 は、信号処理部 15 から供給された位相差検出用データに基づいて、フォーカスを合わせる対象の物体（合焦対象物）に対してフォーカスが合っているか否かを判定する。合焦判定部 18 は、フォーカスエリアにおける物体にフォーカスが合っている場合、合焦していることを示す情報を合焦判定結果として、駆動部 19 に供給する。また、合焦判定部 18 は、合焦対象物にフォーカスが合っていない場合、フォーカスのずれの量（デフォーカス量）を算出し、その算出したデフォーカス量を示す情報を合焦判定結果として、駆動部 19 に供給する。

【0038】

駆動部 19 は、ズームレンズ 21、絞り 22、およびフォーカスレンズ 23 を駆動させる。例えば、駆動部 19 は、合焦判定部 18 から供給された合焦判定結果に基づいて、フォーカスレンズ 23 の駆動量を算出し、その算出した駆動量に応じてフォーカスレンズ 23 を移動させる。

20

【0039】

具体的には、駆動部 19 は、フォーカスが合っている場合には、フォーカスレンズ 23 の現在の位置を維持させる。また、駆動部 19 は、フォーカスが合っていない場合には、デフォーカス量を示す合焦判定結果およびフォーカスレンズ 23 の位置に基づいて駆動量（移動距離）を算出し、その駆動量に応じてフォーカスレンズ 23 を移動させる。

【0040】

<画素アレイ部の画素配列について>

30

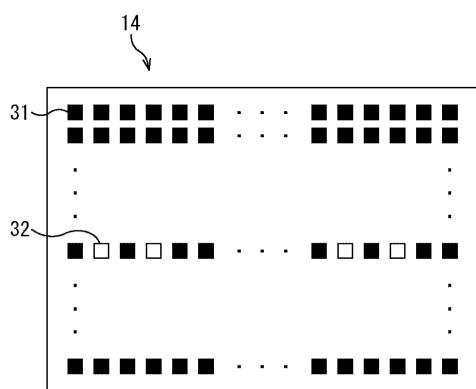

次に、図 2 を参照して、イメージセンサ 14 の画素アレイ部の画素配置について説明する。

【0041】

図 2 に示されるように、イメージセンサ 14 の画素アレイ部には、黒色の正方形で示される複数の撮像画素 31 が行列状に 2 次元配置されている。撮像画素 31 は、R 画素、G 画素、および B 画素からなり、これらは、ベイヤ配列に従い規則的に配置されている。

【0042】

また、イメージセンサ 14 の画素アレイ部には、行列状に 2 次元配置される複数の撮像画素 31 の中に、白色の正方形で示される複数の位相差検出画素 32 が散在して配置されている。具体的には、位相差検出画素 32 は、イメージセンサ 14 の画素アレイ部において、撮像画素 31 の一部を置き換えることで、特定のパターンで規則的に配置されている。なお、イメージセンサ 14 における撮像画素 31 および位相差検出画素 32 の配置は、これに限られるものではなく、他のパターンで配置されるようにしてもよい。

40

【0043】

<画素の詳細な構成例>

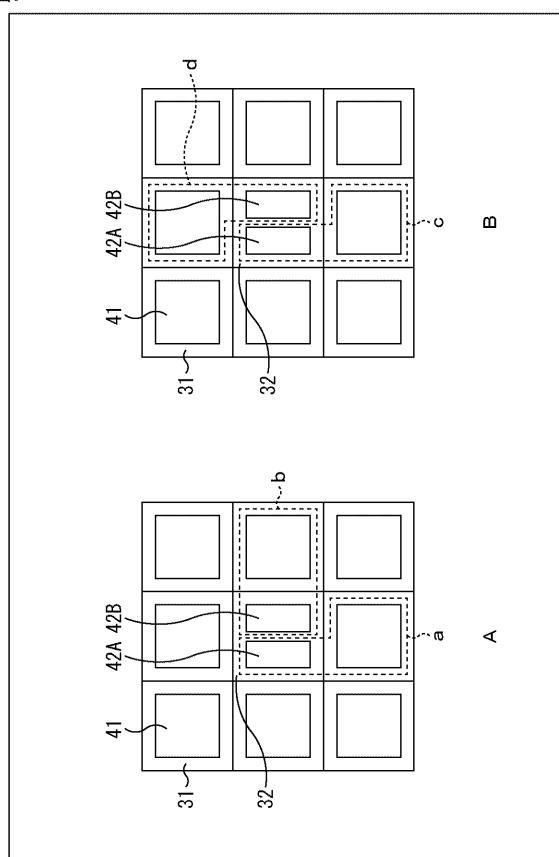

図 3 は、画素アレイ部に配置される撮像画素 31 および位相差検出画素 32 のより詳細な構成例を示している。

【0044】

図 3 A, B に示されるように、撮像画素 31 は、1 つの光電変換部（フォトダイオード）41 を備えている。撮像画素 31 においては、受光した被写体光が光電変換部 41 によ

50

り光電変換されることで生じる電荷に基づいて、撮像画像を生成するための信号が生成される。

【0045】

また、図示はしないが、撮像画素31は、光電変換部41に蓄積された電荷を転送する転送トランジスタ、光電変換部41から転送された電荷を蓄積し電圧に変換するFD(フローティングディフェュージョン)、FDに蓄積されている電荷を排出(リセット)するリセットトランジスタ、FDの電圧を增幅し垂直信号線に出力する増幅トランジスタを、少なくとも備えている。なお、増幅トランジスタと垂直信号線との間に、増幅トランジスタの電圧の垂直信号線への出力をオン/オフする選択トランジスタが設けられるようにしてもよい。

10

【0046】

一方、位相差検出画素32は、2つの光電変換部42A, 42Bを備えている。位相差検出画素32においては、受光した被写体光が光電変換部42A, 42Bそれぞれにより光電変換されることで生じる電荷に基づいて、位相差検出を行うための信号が生成される。

【0047】

また、図示はしないが、位相差検出画素32は、光電変換部42A, 42Bそれぞれに対応して、転送トランジスタ、FD、リセットトランジスタ、増幅トランジスタを2つずつ有している。

【0048】

具体的には、光電変換部42A, 42Bは、それぞれ、位相差検出画素32に隣接する撮像画素31の光電変換部41と、FD、リセットトランジスタ、および増幅トランジスタを共有している。

20

【0049】

例えば、図3Aにおいて、光電変換部42Aは、破線aで示されるように、位相差検出画素32の下側に隣接する撮像画素31の光電変換部41と、FD、リセットトランジスタ、および増幅トランジスタを共有する一方、光電変換部42Bは、破線bで示されるように、位相差検出画素32の右側に隣接する撮像画素31の光電変換部41と、FD、リセットトランジスタ、および増幅トランジスタを共有するようにできる。

【0050】

また、図3Bにおいて、光電変換部42Aは、破線cで示されるように、位相差検出画素32の下側に隣接する撮像画素31の光電変換部41と、FD、リセットトランジスタ、および増幅トランジスタを共有する一方、光電変換部42Bは、破線dで示されるように、位相差検出画素32の上側に隣接する撮像画素31の光電変換部41と、FD、リセットトランジスタ、および増幅トランジスタを共有するようにしてもよい。

30

【0051】

このように、位相差検出画素32において、2つの光電変換部42A, 42Bが、それぞれ異なる隣接画素のFDおよび増幅トランジスタを共有しているので、イメージセンサ14は、2つの光電変換部42A, 42Bそれぞれの露光(電荷の蓄積)、および、蓄積された電荷に対応する信号の読み出しを同時に行うようになる。

40

【0052】

以下、光電変換部42A, 42Bが、隣接する撮像画素31の光電変換部41と、FD、リセットトランジスタ、および増幅トランジスタを共有する実施の形態について説明する。

【0053】

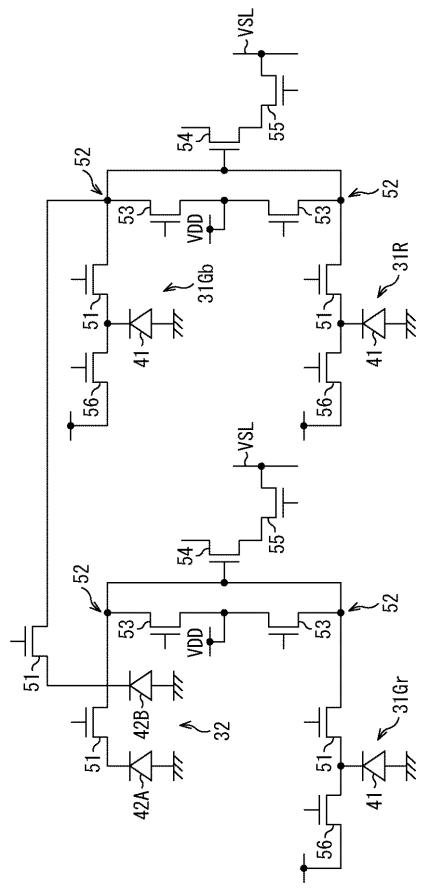

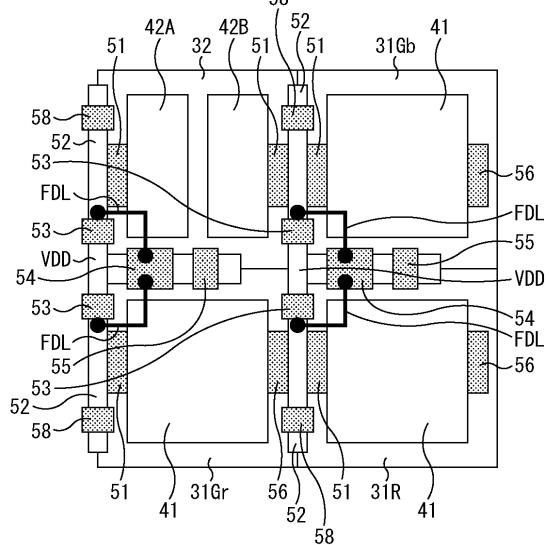

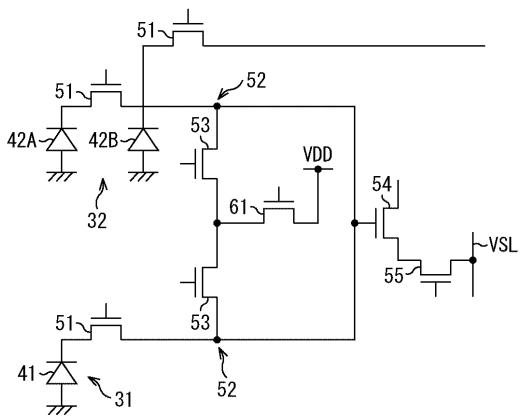

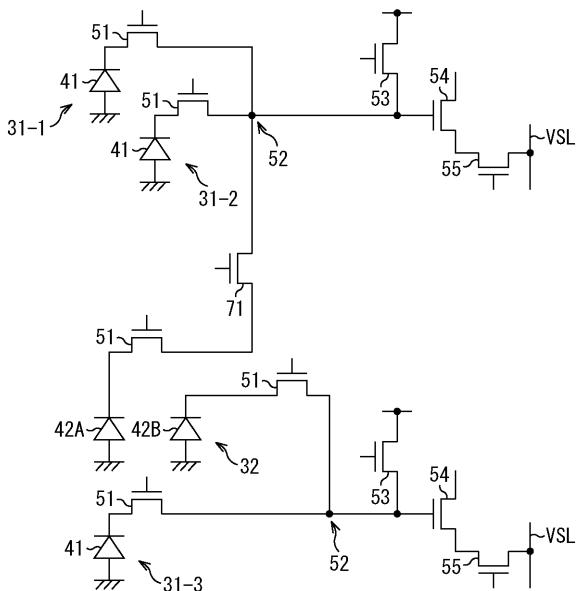

<第1の実施の形態の構成例>

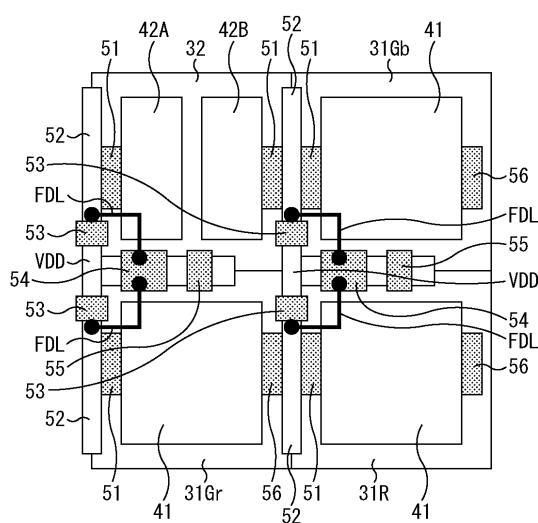

まず、図4および図5を参照して、本技術の第1の実施の形態の撮像画素および位相差検出画素の構成例について説明する。図4は、撮像画素および位相差検出画素の構成例を示す平面図であり、図5は、撮像画素および位相差検出画素の構成例を示す回路図である。

50

## 【0054】

図4および図5には、3つの撮像画素31Gr, 31Gb, 31Rと、1つの位相差検出画素32が示されている。

## 【0055】

この例では、位相差検出画素32と撮像画素31Gr、撮像画素31Gbと撮像画素31Rが、それぞれ縦2画素共有の構成をなしている。

## 【0056】

撮像画素31Gr, 31Gb, 31Rはそれぞれ、光電変換部41、転送トランジスタ51、FD52、リセットトランジスタ53、増幅トランジスタ54、選択トランジスタ55、および、光電変換部41に蓄積されている電荷を排出するオーバーフロー制御トランジスタ56を有している。10

## 【0057】

撮像画素31Gr, 31Gb, 31Rにオーバーフロー制御トランジスタ56を設けることにより、画素間の光学対称性が保たれ、撮像特性の差を低減することができる。また、オーバーフロー制御トランジスタ56をオンすることで、隣接する画素のブルーミングを抑制することができる。

## 【0058】

また、位相差検出画素32は、光電変換部42A, 42Bと、光電変換部42A, 42Bそれぞれに対応する転送トランジスタ51、FD52、リセットトランジスタ53、増幅トランジスタ54、および選択トランジスタ55を有している。20

## 【0059】

なお、光電変換部42Bに対応するFD52は、撮像画素31Gbの光電変換部41と共有されている。

## 【0060】

さらに、図4に示されるように、位相差検出画素32において光電変換部42Aに対応するFD52と、撮像画素31GrのFD52とは、それぞれ配線FDLによって、増幅トランジスタ54のゲート電極に接続されている。これにより、光電変換部42Aは、撮像画素31Grの光電変換部41と、FD52、増幅トランジスタ54、および選択トランジスタ55を共有するようになる。

## 【0061】

また、位相差検出画素32において光電変換部42Bに対応するFD52（すなわち、撮像画素31GbのFD52）と、撮像画素31RのFD52は、それぞれ配線FDLによって、増幅トランジスタ54のゲート電極に接続されている。これにより、光電変換部42Bは、撮像画素31Gb, 31Rの光電変換部41と、FD52、増幅トランジスタ54、および選択トランジスタ55を共有するようになる。30

## 【0062】

以上の構成によれば、位相差検出画素において、2つの光電変換部が、それぞれ異なる隣接画素のFDおよび増幅トランジスタを共有しているので、電荷格納部を設けることなく、2つの光電変換部それぞれの露光、読み出しを同時にを行うことができ、AF速度とAF精度の向上を図ることが可能となる。40

## 【0063】

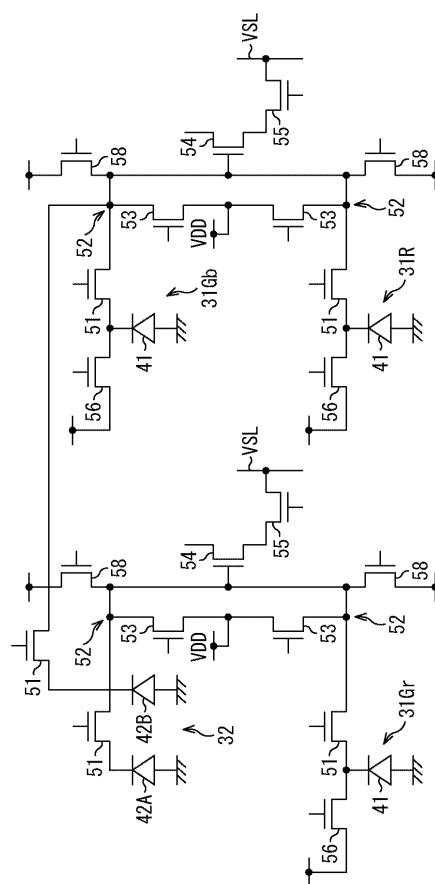

<第1の実施の形態の他の構成例>

次に、図6および図7を参照して、本技術の第1の実施の形態の撮像画素および位相差検出画素の他の構成例について説明する。図6は、撮像画素および位相差検出画素の構成例を示す平面図であり、図7は、撮像画素および位相差検出画素の構成例を示す回路図である。

## 【0064】

なお、図6および図7に示される撮像画素31Gb, Gr, R、および位相差検出画素32と、図4および図5に示される撮像画素31Gb, Gr, R、および位相差検出画素32とで、同様にして形成される部分については、その説明を省略する。50

## 【0065】

すなわち、図6および図7に示される撮像画素31Gr, 31Gb, 31R、および位相差検出画素32は、図4および図5に示される構成に加え、画素共有単位で、変換効率切替トランジスタ58を2つずつ有している。具体的には、撮像画素31Gr, 31Gb, 31R、および位相差検出画素32におけるFD52に、それぞれ変換効率切替トランジスタ58が接続されている。

## 【0066】

画素共有単位（例えば、位相差検出画素32と撮像画素31Grの2画素）において、2つの変換効率切替トランジスタ58のうちのいずれか一方がオンされると、その変換効率切替トランジスタ58とFD52とが電気的に結合され、FD52の浮遊拡散領域が拡大し、FD52の容量が増え、変換効率が下げられる。また、2つの変換効率切替トランジスタ58の両方がオンされると、FD52の浮遊拡散領域がさらに拡大し、変換効率がさらに下げられる。

10

## 【0067】

このように、変換効率切替トランジスタ58のオン／オフによって、FD52の変換効率を切り替えることができる、低照度下では、2つの変換効率切替トランジスタ58の両方をオフし、変換効率を上げることで、S/N(Signal to Noise)比を良くするとともに、高照度下では、変換効率切替トランジスタ58をオンすることで、光電変換部41(42A, 42B)からの飽和信号量をFD52が全て受け取ることが可能となる。

## 【0068】

20

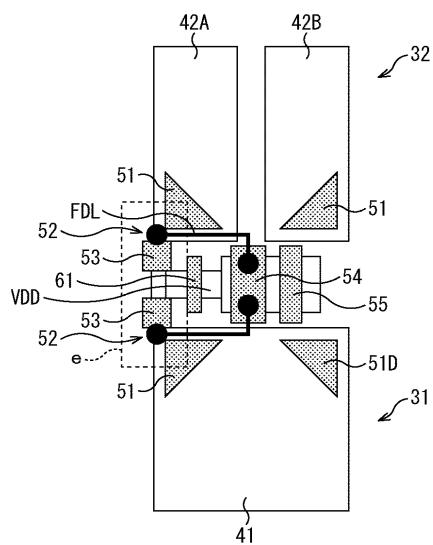

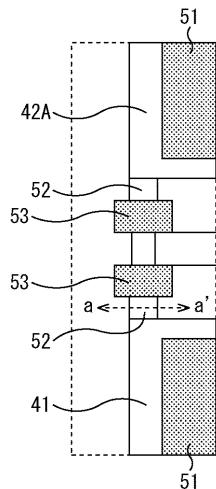

＜第2の実施の形態の構成例＞

次に、図8および図9を参照して、本技術の第2の実施の形態の撮像画素および位相差検出画素の構成例について説明する。図8は、撮像画素および位相差検出画素の構成例を示す平面図であり、図9は、撮像画素および位相差検出画素の構成例を示す回路図である。

## 【0069】

図8および図9には、1つの撮像画素31と、1つの位相差検出画素32が示されている。

## 【0070】

30

この例では、位相差検出画素32と撮像画素31が縦2画素共有の構成をなしている。

## 【0071】

撮像画素31は、光電変換部41、転送トランジスタ51, 51D、FD52、リセットトランジスタ53、増幅トランジスタ54、および選択トランジスタ55を有している。ここで、転送トランジスタ51Dは、画素構造の対称性を保つために設けられており、転送トランジスタ51と異なり、光電変換部41の電荷を転送する等の機能を有しない。なお、撮像画素31において、光電変換部41に蓄積されている電荷を排出するオーバーフロー制御トランジスタを設けるようにしてもよい。

## 【0072】

また、位相差検出画素32は、光電変換部42A, 42Bと、光電変換部42A, 42Bそれぞれに対応する転送トランジスタ51、FD52、リセットトランジスタ53、増幅トランジスタ54、および選択トランジスタ55を有している。

40

## 【0073】

なお、光電変換部42Bに対応するFDは、位相差検出画素32に隣接する図示せぬ撮像画素の光電変換部と共有されている。

## 【0074】

さらに、図8に示されるように、位相差検出画素32において光電変換部42Aに対応するFD52と、撮像画素31のFD52とは、それぞれ配線FDLによって、増幅トランジスタ54のゲート電極に接続されている。これにより、光電変換部42Aは、撮像画素31の光電変換部41と、FD52、増幅トランジスタ54、および選択トランジスタ55を共有するようになる。

50

## 【0075】

また、位相差検出画素32において光電変換部42Bに対応するFD52と、図示せぬ撮像画素のFDは、それぞれ図示せぬ配線FDLによって、図示せぬ撮像画素の増幅トランジスタのゲート電極に接続される。これにより、光電変換部42Bは、図示せぬ撮像画素の光電変換部と、FD、増幅トランジスタ、および選択トランジスタを共有するようになる。

## 【0076】

以上の構成によれば、位相差検出画素において、2つの光電変換部が、それぞれ異なる隣接画素のFDおよび増幅トランジスタを共有しているので、電荷格納部を設けることなく、2つの光電変換部それぞれの露光、読み出しを同時に行うことができ、AF速度とAF精度の向上を図ることが可能となる。

10

## 【0077】

なお、この例では、画素共有単位を構成する画素同士（撮像画素31および位相差検出画素32）の間に、増幅トランジスタ54を含む画素トランジスタが配置されている。このような構成により、図8の破線eで囲まれる部分を拡大した図10に示されるように、それぞれの画素におけるFD52と、増幅トランジスタ54とが互いに隣接する位置に配置されるようになるので、FD52と増幅トランジスタ54とを接続する配線FDLの配線長を短く設計することができ、変換効率を上げることができる。

## 【0078】

さらに、この例では、撮像画素31および位相差検出画素32それぞれのリセットトランジスタ53のソースは、画素それぞれのFD52に接続されている。これにより、FD52の容量を減らすことができ、変換効率を上げることができる。

20

## 【0079】

さらにまた、この例では、撮像画素31および位相差検出画素32それぞれのリセットトランジスタ53のドレインは、それぞれ変換効率切替トランジスタ61のソースに接続されている。このような構成により、画素それぞれのリセットトランジスタ53のオン／オフによってFD52の容量を変化させることができ、変換効率を設定することができる。

## 【0080】

具体的には、撮像画素31および位相差検出画素32それぞれの転送トランジスタ51がオンされた状態で、撮像画素31および位相差検出画素32それぞれのリセットトランジスタ53をオフするとともに、変換効率切替トランジスタ61をオフした場合、画素共有単位におけるFDの容量は、撮像画素31のFD52の容量と、位相差検出画素32のFD52の容量との合計となる。

30

## 【0081】

また、撮像画素31および位相差検出画素32それぞれの転送トランジスタ51がオンされた状態で、撮像画素31および位相差検出画素32のいずれかのリセットトランジスタ53をオンするとともに、変換効率切替トランジスタ61をオフした場合、画素共有単位におけるFDの容量は、撮像画素31のFD52の容量と、位相差検出画素32のFD52の容量に、オンされたリセットトランジスタ53のゲート容量とドレイン部分の容量とが加算された容量となる。これにより、上述した場合より、変換効率を下げることができる。

40

## 【0082】

さらに、撮像画素31および位相差検出画素32それぞれの転送トランジスタ51がオンされた状態で、撮像画素31および位相差検出画素32それぞれのリセットトランジスタ53をオンするとともに、変換効率切替トランジスタ61をオフした場合、画素共有単位におけるFDの容量は、撮像画素31のFD52の容量と、位相差検出画素32のFD52の容量に、撮像画素31および位相差検出画素32それぞれのリセットトランジスタ53のゲート容量とドレイン部分の容量とが加算された容量となる。これにより、上述した場合より、変換効率をさらに下げることができる。

## 【0083】

なお、撮像画素31および位相差検出画素32それぞれのリセットトランジスタ53をオンするとともに、変換効率切替トランジスタ61をオンした場合、FD52に蓄積された

50

電荷はリセットされる。

【0084】

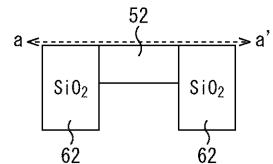

また、この例では、FD52（リセットトランジスタ53のソース）は、STI（Shallow Trench Isolation）による素子分離領域に囲まれて形成されている。

【0085】

図11は、図10における両矢印a-a'でのFD52部分の断面図を示している。

【0086】

図11に示されるように、FD52の周囲を、SiO<sub>2</sub>等よりなる、STIによる素子分離領域62に囲まれて形成されるようとする。これにより、FD52の拡散を素子分離領域62で抑制することができ、FD線幅を素子分離領域62間の幅で規定することができる。したがって、FD52の容量減少による変換効率の向上だけでなく、生産ばらつき（具体的には、FD52形成の際のチャネルラインプラント工程における、レジストに対する線幅のばらつきや重ね合わせのばらつき）を抑制することができる。

【0087】

さらに、この例では、図8に示されるように、各画素の転送トランジスタ51は、矩形状に形成される、各画素の光電変換部の角部に形成されている。このような構成により、1画素セル内における素子分離面積が小さくなり、光電変換部の面積を拡大することができる。したがって、位相差検出画素32のように、1画素セル内で光電変換部が2つに分けられた場合でも、飽和電荷量Qsの観点で有利に設計を行うことができる。

【0088】

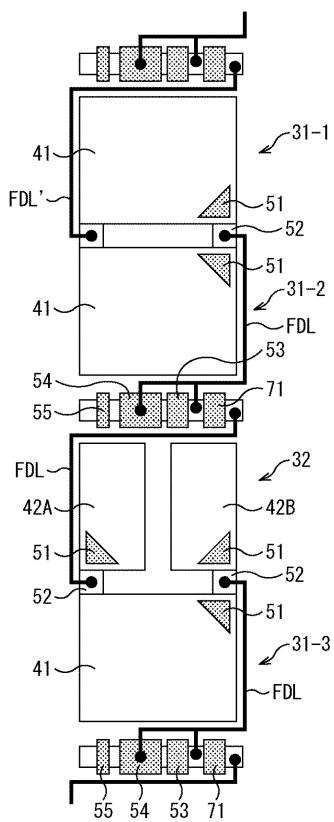

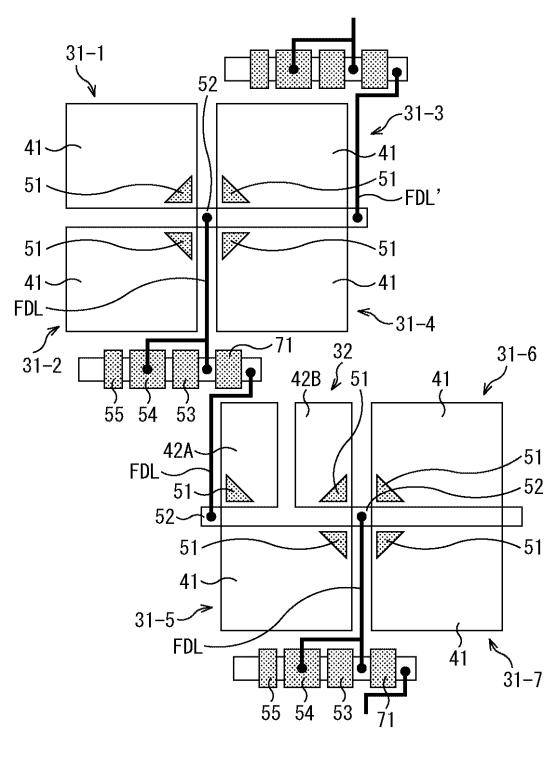

<第3の実施の形態の構成例>

次に、図12および図13を参照して、本技術の第3の実施の形態の撮像画素および位相差検出画素の構成例について説明する。図12は、撮像画素および位相差検出画素の構成例を示す平面図であり、図13は、撮像画素および位相差検出画素の構成例を示す回路図である。

【0089】

図12および図13には、3つの撮像画素31-1乃至31-3と、1つの位相差検出画素32が示されている。

【0090】

この例では、撮像画素31-1と撮像画素31-2、位相差検出画素32と撮像画素31-3が、それぞれ縦2画素共有の構成をなしている。また、それぞれの画素共有単位は、互いに隣接する行に配置されている。

【0091】

撮像画素31-1, 31-2はそれぞれ、光電変換部41および転送トランジスタ51を有し、それぞれの光電変換部41は、FD52、リセットトランジスタ53、増幅トランジスタ54、および選択トランジスタ55を共有している。

【0092】

撮像画素31-3もまた、光電変換部41および転送トランジスタ51を有し、位相差検出画素32は、光電変換部42A, 42Bと、それに対応する転送トランジスタ51を有している。そして、撮像画素31-3の光電変換部41と、位相差検出画素32の光電変換部42Bとは、FD52、リセットトランジスタ53、増幅トランジスタ54、および選択トランジスタ55を共有している。

【0093】

また、位相差検出画素32において光電変換部42Aに対応する転送トランジスタ51は、隣接するFD52および配線FDLを介して、読み出し用トランジスタ71に接続されている。

【0094】

読み出し用トランジスタ71は、光電変換部42Aに対応するFD52と、撮像画素31-1, 31-2に共有されているFD52との間に形成されており、読み出し用トランジスタ71がオンされることで、光電変換部42Aは、撮像画素31-1, 31-2それぞれ

10

20

30

40

50

(すなわち、隣接行の画素)と、FD52、増幅トランジスタ54、および選択トランジスタ55を共有するようになる。

【0095】

以上の構成によれば、位相差検出画素において、2つの光電変換部が、それぞれ異なる隣接画素のFDおよび増幅トランジスタを共有しているので、電荷格納部を設けることなく、2つの光電変換部それぞれの露光、読み出しを同時に行うことができ、AF速度とAF精度の向上を図ることが可能となる。

【0096】

なお、図12において、撮像画素31-1, 31-2で構成される画素共有単位と、その上側の隣接行の画素トランジスタとを接続する配線FDL'は、光電変換部42Aに対応する転送トランジスタ51と、撮像画素31-1, 31-2で構成される画素共有単位の画素トランジスタとを接続する配線FDLとの対称性を保つために設けられている。10

【0097】

以上の構成においては、位相差検出のための信号の読み出しの際に、読み出し用トランジスタ71がオンされることで、光電変換部42Aに蓄積された電荷に対応する信号は、撮像画素31-1, 31-2から構成される画素共有単位の画素トランジスタから読み出され、光電変換部42Bに蓄積された電荷に対応する信号は、撮像画素31-3および位相差検出画素32から構成される画素共有単位の画素トランジスタから読み出される。このとき、それぞれの画素トランジスタに含まれる読み出し用トランジスタ71がオンされるようにすることで、光電変換部42A, 42Bそれぞれについて読み出される信号の変換効率を同じにすることができる。20

【0098】

一方、撮像画像のための信号の読み出しの際には、読み出し用トランジスタ71をオフさせることで、撮像画素の変換効率を高く保て、特性の悪化を避けることができる。また、飽和信号量がFDのレンジで擦り切れるような場合には、読み出し用トランジスタ71をオンさせることで変換効率を低くすることができ、FDにおける電荷の擦り切れを回避することができる。すなわち、この場合、読み出し用トランジスタ71は、変換効率切替トランジスタとして機能するようになる。

【0099】

さらに、この例でも、図12に示されるように、各画素の転送トランジスタ51は、矩形状に形成される、各画素の光電変換部の角部に形成されている。このような構成により、1画素セル内における素子分離面積が小さくなり、光電変換部の面積を拡大することができる。したがって、位相差検出画素32のように、1画素セル内で光電変換部が2つに分けられた場合でも、飽和電荷量Qsの観点で有利に設計を行うことができる。30

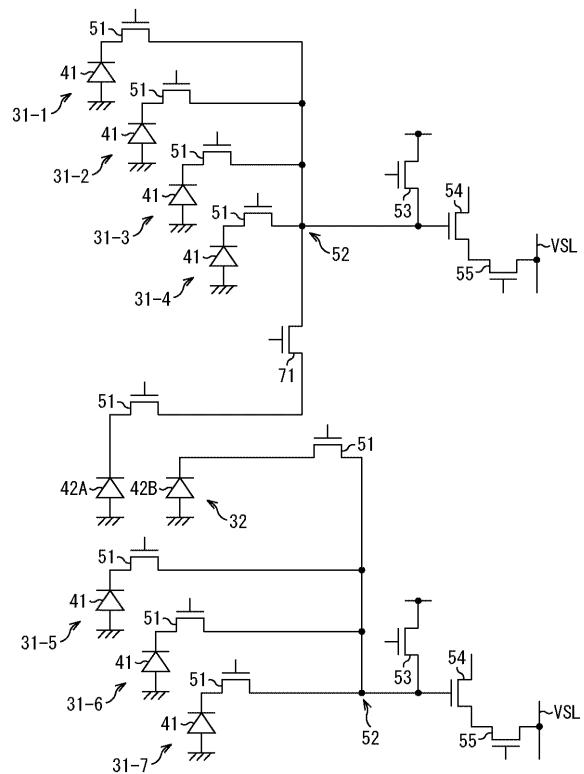

【0100】

<第3の実施の形態の他の構成例>

次に、図14および図15を参照して、本技術の第3の実施の形態の撮像画素および位相差検出画素の他の構成例について説明する。図14は、撮像画素および位相差検出画素の構成例を示す平面図であり、図15は、撮像画素および位相差検出画素の構成例を示す回路図である。40

【0101】

図14および図15には、7つの撮像画素31-1乃至31-7と、1つの位相差検出画素32が示されている。

【0102】

この例では、撮像画素31-1乃至31-4、位相差検出画素32および撮像画素31-5乃至31-7が、それぞれ2×2画素共有の構成をなしている。また、それぞれの画素共有単位は、互いに隣接する行に配置されている。

【0103】

撮像画素31-1乃至31-4はそれぞれ、光電変換部41および転送トランジスタ51を有し、それぞれの光電変換部41は、FD52、リセットトランジスタ53、増幅トランジスタ54を有する。50

ンジスタ 5 4、および選択トランジスタ 5 5 を共有している。

【0104】

撮像画素 3 1 - 5 乃至 3 1 - 7 もまた、光電変換部 4 1 および転送トランジスタ 5 1 を有し、位相差検出画素 3 2 は、光電変換部 4 2 A, 4 2 B と、それぞれに対応する転送トランジスタ 5 1 を有している。そして、撮像画素 3 1 - 5 乃至 3 1 - 7 の光電変換部 4 1 と、位相差検出画素 3 2 の光電変換部 4 2 B とは、FD 5 2、リセットトランジスタ 5 3、増幅トランジスタ 5 4、および選択トランジスタ 5 5 を共有している。

【0105】

また、位相差検出画素 3 2 において光電変換部 4 2 A に対応する転送トランジスタ 5 1 は、隣接する FD 5 2 および配線 FDL を介して、読み出し用トランジスタ 7 1 に接続されている。

10

【0106】

読み出し用トランジスタ 7 1 は、光電変換部 4 2 A に対応する FD 5 2 と、撮像画素 3 1 - 1 乃至 3 1 - 4 に共有されている FD 5 2 との間に形成されており、読み出し用トランジスタ 7 1 がオンされることで、光電変換部 4 2 A は、撮像画素 3 1 - 1 乃至 3 1 - 4 それぞれ（すなわち、隣接行の画素）と、FD 5 2、増幅トランジスタ 5 4、および選択トランジスタ 5 5 を共有するようになる。

【0107】

以上の構成においても、位相差検出画素において、2つの光電変換部が、それぞれ異なる隣接画素の FD および増幅トランジスタを共有しているので、電荷格納部を設けることなく、2つの光電変換部それぞれの露光、読み出しを同時にを行うことができ、AF速度とAF精度の向上を図ることが可能となる。

20

【0108】

なお、図 14において、撮像画素 3 1 - 1 乃至 3 1 - 4 で構成される画素共有単位と、その上側の隣接行の画素トランジスタとを接続する配線 FDL' は、光電変換部 4 2 A に対応する転送トランジスタ 5 1 と、撮像画素 3 1 - 1 乃至 3 1 - 4 で構成される画素共有単位の画素トランジスタとを接続する配線 FDL との対称性を保つために設けられている。

【0109】

なお、上述した実施の形態においては、位相差検出画素は2つの光電変換部を有するものとしたが、2つに限らず、3つ以上の光電変換部を有するようにしてもよい。

30

【0110】

また、本技術の実施の形態は、上述した実施の形態に限定されるものではなく、本技術の要旨を逸脱しない範囲において種々の変更が可能である。

【符号の説明】

【0112】

1 電子機器, 14 イメージセンサ, 31 撮像画素, 32 位相差検出画素,

, 41 光電変換部, 42 A, 42 B 光電変換部, 51 転送トランジスタ,

52 FD, 53 リセットトランジスタ, 54 増幅トランジスタ, 55 選択トランジスタ,

56 オーバーフロー制御トランジスタ, 58 変換効率切替トランジスタ,

61 変換効率切替トランジスタ, 71 読み出し用トランジスタ

40

【図1】

図1【図2】

図2【図3】

図3【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

## 【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

図14

【図15】

図15

---

フロントページの続き

(72)発明者 久保 典弘

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 内田 哲弥

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 粕谷 満成

(56)参考文献 特開2014-086781(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/369

H01L 27/146

H04N 5/3745