(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 11 2004 000 146 B4 2010.05.06

(12)

## Patentschrift

(21) Deutsches Aktenzeichen: 11 2004 000 146.3

(51) Int Cl.<sup>8</sup>: H01L 21/336 (2006.01)

(86) PCT-Aktenzeichen: PCT/US2004/000981

(87) PCT-Veröffentlichungs-Nr.: WO 2004/068586

(86) PCT-Anmeldetag: 13.01.2004

(87) PCT-Veröffentlichungstag: 12.08.2004

(43) Veröffentlichungstag der PCT Anmeldung

in deutscher Übersetzung: 02.02.2006

(45) Veröffentlichungstag

der Patenterteilung: 06.05.2010

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

10/346,617 17.01.2003 US

(72) Erfinder:

Ngo, Minh-Van, Fremont, Calif., US; Besser, Paul R., Sunnyvale, Calif., US; Lin, Ming-Ren, Cupertino, Calif., US; Wang, Haihong, Fremont, Calif., US

(73) Patentinhaber:

Advanced Micro Devices, Inc., Sunnyvale, Calif.,

US

(56) Für die Beurteilung der Patentfähigkeit in Betracht

gezogene Druckschriften:

US 64 26 285 B1

US 64 92 216 B1

(74) Vertreter:

Grünecker, Kinkeldey, Stockmair &

Schwanhäusser, 80802 München

(54) Bezeichnung: Verfahren zur Herstellung eines MOSFET-Bauelements mit zugspannungsverformtem Substrat

(57) Hauptanspruch: Verfahren zur Herstellung eines Metalloxidhalbleiterfeldeffekttransistors, MOSFET, mit:

Bereitstellen eines Substrats (40) mit einem Gate (54), das über dem Substrat (40) ausgebildet ist;

Abscheiden einer Abstandsschicht und Bilden eines Abstandselement (60) um das Gate (54) und um einen Gateisolator (56) herum, die über einer Schicht aus Silizium (42) über dem Substrat (40) angeordnet sind;

Abscheiden einer Ätzstoppschicht (63) über dem Abstandselement (60), dem Gate (54) und der Schicht aus Silizium (42); und

Abscheiden einer dielektrischen Schicht (65) über der Ätzstoppschicht (63);

wobei zumindest einer der Schritte des Abscheidens der Abstandsschicht, des Abscheidens der Ätzstoppschicht (63) und des Abscheidens der dielektrischen Schicht (65) eine Abscheidung mit Druckspannung umfasst, um eine Zugverformung in der Schicht aus Silizium (42) zu erhöhen.

**Beschreibung****GEBIET DER ERFINDUNG**

**[0001]** Die vorliegende Erfindung betrifft im Allgemeinen integrierte Schaltungen und Verfahren zur Herstellung integrierter Schaltungen. Insbesondere betrifft die vorliegende Erfindung einen Halbleiter mit einem zugspannungsverformten Substrat und ein Verfahren zur Herstellung eines derartigen Halbleiters.

**HINTERGRUND DER ERFINDUNG**

**[0002]** US 6 492 216 B1 offenbart ein Verfahren zur Herstellung eines MOSFET-Transistors mit einem zugverformten oder druckverformten Kanalgebiet. Das Verfahren umfasst das epitaxiale Aufwachsen einer Silizium- oder Silizium/Germanium-Schicht mit Einbau von Kohlenstoffatomen. Die Kohlenstoffkonzentration der resultierenden Silizium/Germanium/Kohlenstoff Schicht steuert die biaxiale Zugverformung oder Druckverformung, die für das Kanalgebiet gewünscht ist.

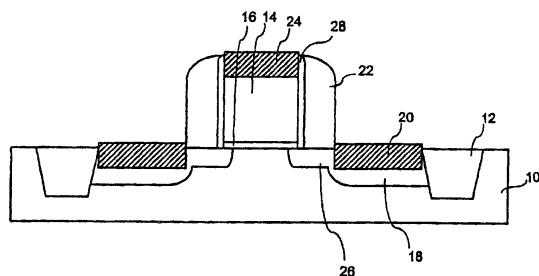

**[0003]** Halbleiterhersteller wenden eine Vielzahl von Techniken an, um das Leistungsverhalten von Halbleiterbauelementen, etwa von Metalloxidhalbleiterfeldeffekttransistoren (MOSFET) zu verbessern. **Fig. 1** zeigt ein konventionelles MOSFET-Bauelement. Der MOSFET aus **Fig. 1** ist auf einem Halbleitersubstrat **10** innerhalb eines aktiven Bereichs hergestellt, der durch Flachgrabenisolationen **12** begrenzt ist, die den aktiven Bereich des MOSFET von anderen IC-Komponenten, die auf dem Substrat **10** hergestellt sind, elektrisch isolieren.

**[0004]** Der MOSFET weist eine Gateelektrode **14** auf, die von einem Kanalgebiet in dem Substrat **10** durch einen dünnen ersten Gateisolator **16**, etwa Siliziumoxid oder Oxid-Nitrid-Oxid (ONO) getrennt ist. Um den Widerstand des Gates **14** zu minimieren, ist das Gate **14** typischerweise aus einem dotierten Halbleitermaterial, etwa Polysilizium, hergestellt.

**[0005]** Source und Drain des MOSFET sind als tiefe Source- und Draingebeite **18** vorgesehen, die an gegenüberliegenden Seiten des Gates **14** ausgebildet sind. Source- und Drainsilizide **20** sind auf den Source- und Draingebeiten **18** ausgebildet und weisen eine Verbindung mit dem Substrathalbleitermaterial und einem Metall, etwa Kobalt (Co) oder Nickel (Ni) auf, um den Kontaktwiderstand zu den Source- und Draingebeiten **18** zu reduzieren. Die Source- und Draingebeite **18** sind ausreichend tief ausgebildet, um sich über die Tiefe hinaus zu erstrecken, bis zu der die Source- und Drainsilizide **20** ausgebildet sind. Die Source- und Draingebeite **18** werden nachfolgend zur Herstellung eines Abstandselements **28** um das Gate **14** herum und der Herstellung des Gateiso-

lators **16**, die als eine Implantationsmaske dienen, implantiert, um damit die laterale Position der Source- und Draingebeite **18** in Bezug auf das Kanalgebiet unterhalb des Gates zu definieren.

**[0006]** Das Gate **14** besitzt ebenso ein Silizid **24**, das an der oberen Fläche ausgebildet ist. Die Gatestruktur mit einem Polysiliziummaterial und einem darüberliegenden Silizid wird häufig auch als ein Polydiz-Gate bezeichnet.

**[0007]** Das Source und das Drain des MOSFET weisen ferner flache Source- und Drainerweiterungen **26** auf. In dem Maße wie die Abmessungen des MOSFETS kleiner werden, verursachen Kurzkanaleffekte, die sich aus dem kleinen Abstand zwischen dem Source und dem Drain ergeben, eine Beeinträchtigung des MOSFET-Leistungsverhaltens. Die Verwendung flacher Source- und Drainerweiterungen **26** anstelle der tiefen Source- und Draingebeite in der Nähe des Endes des Kanals hilft dabei, die Kurzkanaleffekte zu reduzieren. Die flachen Source- und Drainerweiterungen werden vor der Ausbildung des Abstandselements **22** implantiert, wobei das Gate **14** als eine Implantationsmaske dient, um die laterale Position der flachen Source- und Drainerweiterungen **26** in Bezug auf das Kanalgebiet **18** zu definieren. Die Diffusion während des nachfolgenden Ausheizens bewirkt, dass sich die Source- und Drainerweiterungen **26** geringfügig unter das Gate **14** erstrecken.

**[0008]** Eine Option zum Verbessern des Leistungsverhaltens von MOSFETS besteht darin, die Ladungsträgerbeweglichkeit von Silizium zu verbessern, um damit den Widerstand und die Leistungsaufnahme zu reduzieren und um die Stromtreiberfähigkeit, das Frequenzverhalten, die Arbeitsgeschwindigkeit zu verbessern. Ein Verfahren zum Verbessern der Ladungsträgerbeweglichkeit, das in jüngster Zeit viel Aufmerksamkeit erregt hat, ist die Verwendung von Siliziummaterial, auf das eine Zugverformung ausgeübt wird.

**[0009]** Es ist aus der US 6 426 285 B1 bekannt, eine SiO<sub>2</sub>-Schicht mit Druckspannung über einer MOS-Struktur abzuscheiden.

**[0010]** „Verformtes“ Silizium kann gebildet werden, indem eine Schicht aus Silizium auf einem Silizium/Germanium-Substrat aufgewachsen wird. Das Silizium/Germanium-Gitter weist im Allgemeinen einen größeren Abstand auf als ein reines Siliziumgitter auf Grund der Anwesenheit der größeren Germaniumatome in dem Gitter. Da sich die Atome des Siliziumgitters zu dem Silizium/Germanium-Gitter mit größerem Abstand ausrichten, wird eine Zugverformung in der Siliziumschicht erzeugt. Die Siliziumatome werden im Wesentlichen auseinandergesogen. Der Betrag der Zugverformung, der auf das Siliziumgitter

ausgeübt wird, wächst mit dem Anteil an Germanium in dem Silizium/Germanium-Gitter.

**[0011]** Entspanntes Silizium weist sechs gleiche Valenzbänder auf. Das Anwenden einer Zugverformung auf das Siliziumgitter bewirkt, dass vier der Valenzbänder eine höhere Energie erhalten und zwei der Valenzbänder eine geringere Energie aufweisen. Als Folge von Quanteneffekten besitzen Elektronen eine 30%ig geringere effektive Masse, wenn sie durch die Energiebänder mit geringerer Energie laufen. Somit bieten die Bänder mit geringerer Energie einen geringeren Widerstand für die Elektronenbewegung. Des weiteren treffen die Elektronen auf geringere Schwingungsenergien von den Kernen der Siliziumatome, so dass damit eine Streuung mit einer 500 bis 1000fach geringeren Rate als im entspannten Silizium hervorgerufen wird. Als Folge davon wird die Ladungsträgerbeweglichkeit in verformten Silizium im Vergleich zum entspannten Silizium deutlich verbessert, wodurch eine mögliche Steigerung der Beweglichkeit von 80% oder mehr für Elektronen und 20% oder mehr für Löcher gegeben ist. Man fand heraus, dass der Anstieg der Beweglichkeit für elektrische Felder von bis zu 1,5 Megavolt/cm bestehen bleibt. Mit diesen Faktoren wird angenommen, dass eine Bauteilgeschwindigkeitserhöhung von 35% ohne weitere Reduzierung der Bauteilgröße oder eine 25%ige Verringerung der Leistungsaufnahme ohne Einbuße des Leistungsverhaltens möglich ist.

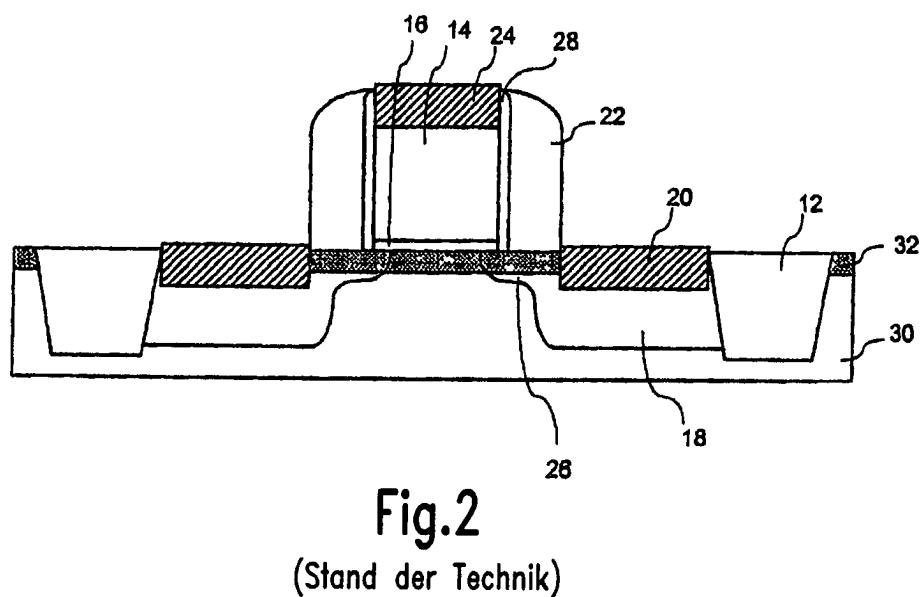

**[0012]** Ein Beispiel eines MOSFET unter Anwendung einer verformten Siliziumschicht ist in [Fig. 2](#) gezeigt. Der MOSFET ist auf einen Substrat mit einer Silizium/Germanium-Schicht **30** hergestellt, auf der eine Epitaxieschicht aus verformten Silizium **32** ausgebildet ist. In dem MOSFET sind konventionelle MOSFET-Strukturen einschließlich tiefer Source- und Draingebiete **18**, flacher Source- und Drainerweiterungen **26**, einer Gateoxidschicht **16**, einem Gate **14**, das von Abstandselementen **28**, **22** umgeben ist, Silizid-Source- und Drainkontakte **20**, einem Silizidgeatekontakt **24** und Flachgrabenisolationen **12** verwendet. Das Kanalgebiet des MOSFET enthält das verformte Siliziummaterial, das eine verbesserte Ladungsträgerbeweglichkeit zwischen dem Source und dem Drain bereitstellt.

**[0013]** Eine gegenläufige Eigenschaft von MOSFETS mit verformten Silizium der Art, wie er in [Fig. 2](#) gezeigt ist, besteht darin, dass die Bandlücke von Silizium/Germanium kleiner als die von Silizium ist. Anders ausgedrückt, der zum Überführen eines Elektrons in das Leitungsbau erforderliche Energiebetrag ist im Mittel in einem Silizium/Germanium-Gitter kleiner als in einem Siliziumgitter. Als Folge davon sind die Leckströme am Übergang in Bauelementen, deren Source- und Draingebiete in dem Silizium/Germanium ausgebildet sind, größer als in vergleichbaren Bauelementen, die ihre Source- und Draingebie-

te in Silizium ausgebildet aufweisen.

**[0014]** Eine weitere nachteilige Eigenschaft von MOSFETS mit verformtem Silizium der Art, wie sie in [Fig. 2](#) gezeigt sind, besteht darin, dass die Dielektrizitätskonstante von Silizium/Germanium größer als jene von Silizium ist. Als Folge davon weisen MOSFETS mit Silizium/Germanium höhere parasitäre Kapazitäten auf, wodurch die Bauteilleistungsaufnahme erhöht und die Stromtreiberfähigkeit und die Frequenzantwort reduziert werden.

**[0015]** Daher werden die Vorteile, die durch das Einbauen von verformten Silizium in MOSFET-Strukturen erreicht werden, teilweise durch die Nachteile aufgehoben, die sich aus der Verwendung eines Silizium/Germanium-Substrats ergeben.

**[0016]** Es besteht daher ein Bedarf für einen MOSFET-Herstellungsprozess, in welchem Silizium durch die äußerst zugverformende Abscheidung von Schichten auf dem Silizium verformt wird. Ferner besteht ein Bedarf, eine Zugverformung in einem Silizium-MOSFET zu erhöhen, ohne dass eine Silizium/Germanium-Schicht geändert wird. Des weiteren besteht ein Bedarf darin, die Ladungsträgerbeweglichkeit durch Verwendung verformten Siliziums zu erhöhen.

## ÜBERBLICK OBER DIE ERFINDUNG

**[0017]** Eine beispielhafte Ausführungsform betrifft ein Verfahren zur Herstellung eines Metalloxidhalbleiterfeldtransistors (MOSFET). Das Verfahren umfasst die Schritte

Bereitstellen eines Substrats mit einem Gate, das über dem Substrat ausgebildet ist;

Abscheiden einer Abstandsschicht und Bilden eines Abstandselements um das Gate und um einen Gateseparator herum, die über einer Schicht aus Silizium über dem Substrat angeordnet sind;

Abscheiden einer Ätzstoppschicht über dem Abstandselement, dem Gate und der Schicht aus Silizium; und

Abscheiden einer dielektrischen Schicht über der Ätzstoppschicht;

wobei zumindest einer der Schritte des Abscheidens der Abstandsschicht, des Abscheidens einer Ätzstoppschicht und des Abscheidens einer dielektrischen Schicht eine Abscheidung mit Druckspannung umfasst, um eine Zugverformung in der Schicht aus Silizium zu erhöhen.

**[0018]** Andere wesentliche Merkmale und Vorteile der Erfindung werden für den Fachmann angesichts des Studiums der folgenden Zeichnungen, der detaillierten Beschreibung und der angefügten Patentansprüche ersichtlich.

## KURZE BESCHREIBUNG DER ZEICHNUNGEN

[0019] Die beispielhaften Ausführungsformen der Offenbarung werden im Folgenden mit Bezugnahme zu den begleitenden Zeichnungen beschrieben, wobei gleiche Bezugszeichen gleiche Elemente bezeichnen, und:

[0020] [Fig. 1](#) eine schematische Querschnittsansicht eines konventionellen MOSFETS ist, der entsprechend einer konventionellen Bearbeitungssequenz hergestellt ist;

[0021] [Fig. 2](#) eine schematische Ansicht eines verformten Silizium-MOSFET-Bauelements ist, das gemäß der konventionellen Bearbeitungsweise, die zur Herstellung des MOSFETS aus [Fig. 1](#) verwendet wurde, gebildet ist;

[0022] [Fig. 3a](#) bis [Fig. 3e](#) schematische Querschnittsansichten von Strukturen sind, die während der Herstellung eines MOSFET-Bauelements gemäß einer beispielhaften Ausführungsform gebildet werden; und

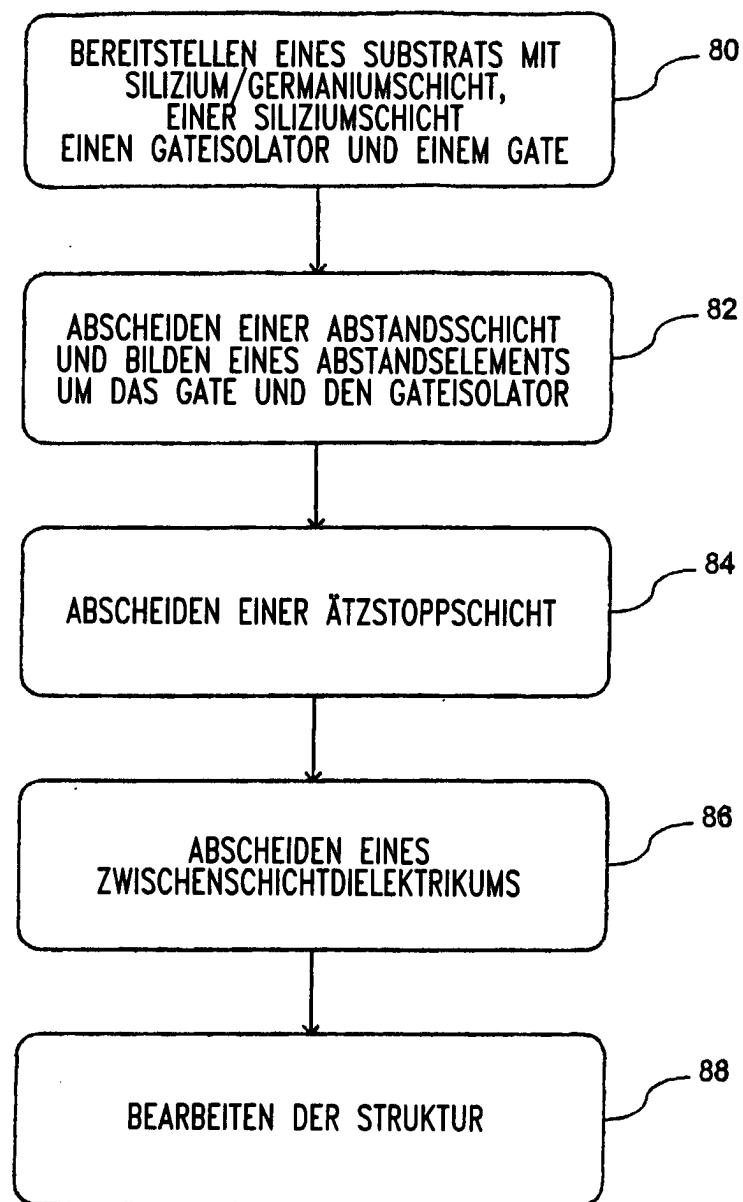

[0023] [Fig. 4](#) ein Prozessablauf entsprechend einer beispielhaften Ausführungsform und alternativer Ausführungsformen ist.

## DETAILLIERTE BESCHREIBUNG BEISPIELHAFTER AUSFÜHRUNGSFORMEN

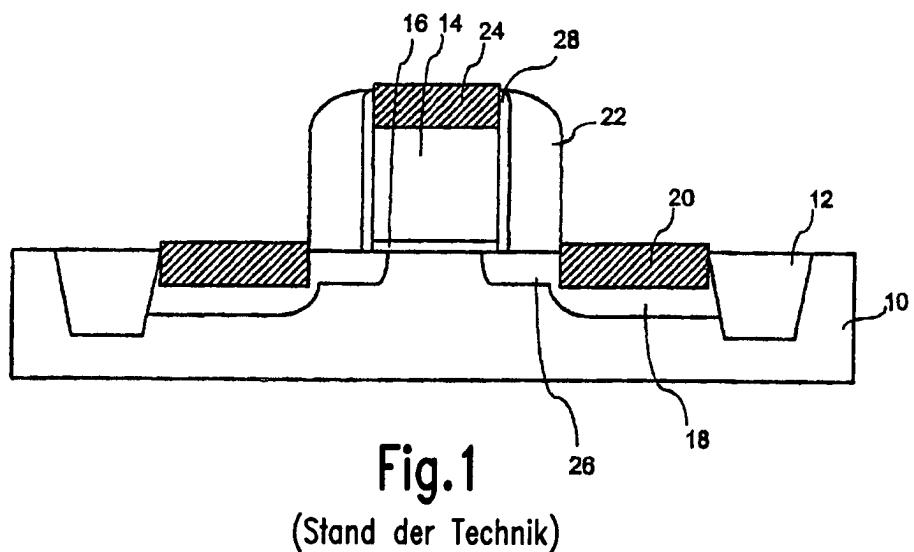

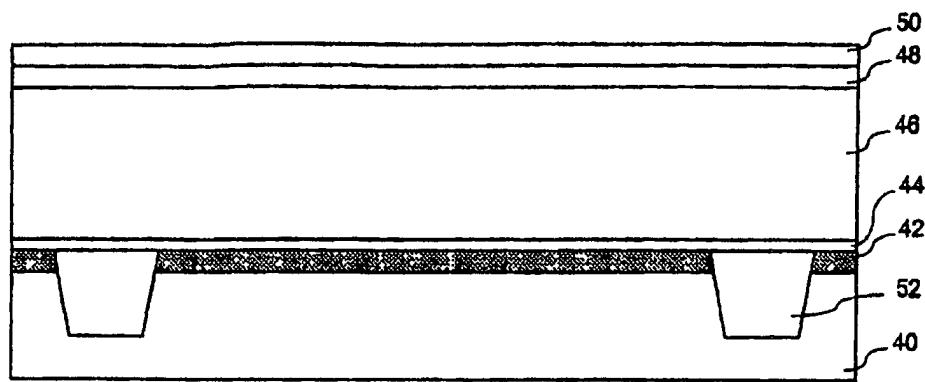

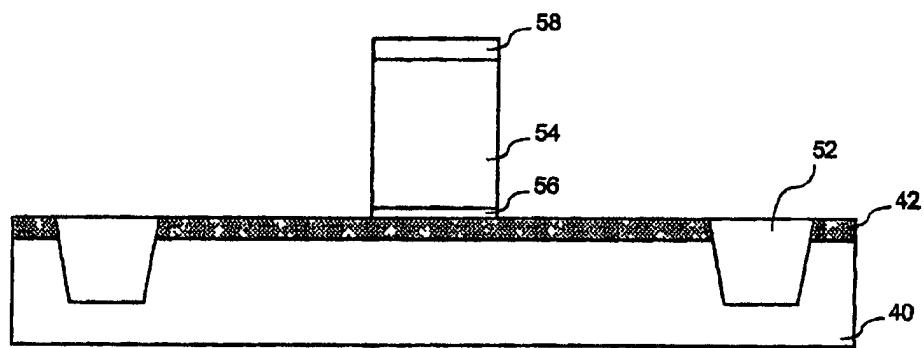

[0024] [Fig. 3a](#) bis [Fig. 3e](#) zeigen Strukturen, die während der Herstellung eines verformten Silizium-MOSFETS gemäß einer anschaulichen Ausführungsform gebildet werden. [Fig. 3a](#) zeigt eine Struktur mit einer Schicht aus Silizium/Germanium **40** mit einer Epitaxialschicht aus Silizium **42**, die an deren Oberfläche ausgebildet ist. Die Silizium/Germanium-Schicht **40** weist vorzugsweise eine Zusammensetzung von  $\text{Si}_{1-x}\text{Ge}_x$ , wobei  $x$  ungefähr 0,2 und noch allgemeiner im Bereich von 0,1 bis 0,3 liegt.

[0025] Die Silizium/Germanium-Schicht **40** wird typischerweise auf einer Siliziumscheibe aufgewachsen. Silizium/Germanium kann beispielsweise durch chemische Dampfabscheidung unter Verwendung von  $\text{Si}_2\text{H}_6$  (Disilan) und  $\text{GeH}_4$  (German) als Quellengase mit einer Substrattemperatur von 600 bis 900°C, einem  $\text{Si}_2\text{H}_6$ -Partialdruck von 30 mPa und einem  $\text{GeH}_4$  Partialdruck von 60 mPa aufgewachsen werden.  $\text{SiH}_4$  (Silan) kann in alternativen Prozessen verwendet werden. Das Wachstum des Silizium/Germanium-Materials kann durch Anwendung dieser Verhältnisse initiiert werden, oder alternativ kann der Partialdruck von  $\text{GeH}_4$  beginnend bei geringem Druck oder Druck Null graduell gesteigert werden, um eine Gradientenverbindung zu bilden. Die Dicke der Silizium/Germanium-Schicht kann gemäß der speziellen Anwendung bestimmt werden. Der obere

Bereich des Silizium/Germanium-Substrats **40**, auf dem die verformte Siliziumschicht **42** aufgewachsen wird, sollte eine gleichförmige Zusammensetzung aufweisen.

[0026] Die Siliziumschicht **42** wird vorzugsweise durch chemische Dampfabscheidung (CVD) unter Verwendung von  $\text{Si}_2\text{H}_6$  als ein Quellengas mit einem Partialdruck von 30 mPa und einer Substrattemperatur von ungefähr 600 bis 900°C aufgewachsen. Die Siliziumschicht **42** wird vorzugsweise bis zu einer Dicke von 200 nm gewachsen.

[0027] Wie ferner in [Fig. 3a](#) gezeigt ist, ist eine Gateisolationsschicht **44** auf der Siliziumschicht **42** gebildet. Die Gateisolationsschicht **44** weist typischerweise Siliziumoxid auf, kann jedoch ein weiteres Material sein, etwa Oxid-Nitrid-Oxid (ONO). Ein Oxid kann durch thermische Oxidation auf der verformten Siliziumschicht gewachsen werden, wird aber vorzugsweise durch chemische Dampfabscheidung aufgebracht.

[0028] Über der Gateisolationsschicht **44** ist eine Gateleiterschicht **46** ausgebildet. Die Gateleiterschicht **46** umfasst typischerweise Polysilizium, kann jedoch auch alternativ aus anderen Materialien, etwa Polysilizium mit implantiertem Germanium aufgebaut sein.

[0029] Über der Gateleiterschicht **46** liegt eine Zweischichthartmaskenstruktur mit einer unteren Hartmaskenschicht **48**, die auch als unterseitenantireflektierende Beschichtung (BARC) bezeichnet wird, und einer oberen Hartmaskenschicht **50**. Die untere Hartmaskenschicht **48** ist typischerweise Siliziumoxid (z. B.  $\text{SiO}_2$ ) und die obere Hartmaskenschicht **50** ist typischerweise Siliziumnitrid (beispielsweise  $\text{Si}_3\text{N}_4$ ).

[0030] Das Silizium/Germanium-Substrat besitzt darin ausgebildet ferner flache Grabenisolierungen **52**. Die Flachgrabenisolierungen können hergestellt werden, indem Gräben mit sich verjüngenden Seitenwänden in der Silizium/Germanium-Schicht **40** und der Siliziumschicht **42** gebildet werden, eine kurze thermische Oxidation ausgeführt wird und anschließend eine Schicht aus Siliziumoxid mit einer Dicke abgeschieden wird, die ausreicht, um die Gräben zu füllen, etwa mittels Niederdruck-CVD (LPCVD) aus TEOS oder aus TEOS mit Ozon bei Atmosphärendruck. Die Siliziumoxidschicht wird dann verdichtet und eingeebnet, etwa durch chemisch-mechanisches Polieren oder einen Rückätzprozess, wodurch die flachen Grabenisolierungen **52** verbleiben, die näherungsweise mit der Oberfläche der Siliziumschicht **42** bündig sind.

[0031] [Fig. 3b](#) zeigt die Struktur aus [Fig. 3a](#) nach dem Strukturieren der Gateleiterschicht und der Gateisolationsschicht, um ein Gate **54** und einen

selbstjustierten Gateisolator **56** zu bilden. Das Strukturieren wird unter Anwendung einer Reihe von anisotroper Ätzprozesse ausgeführt, die die obere Hartmaskenschicht **50** unter Verwendung einer Photolackmaske als eine Ätzmaske strukturieren, sodann die untere Hartmaskenschicht **48** unter Verwendung der strukturierten oberen Hartmaskenschicht **50** als eine Ätzmaske strukturieren, anschließend das Polysilizium unter Anwendung der strukturierten Hartmaskenschicht als eine Ätzmaske strukturieren, und dann die Gateisolationsschicht unter Anwendung des Gate **54** als eine Hartmaske strukturieren. Wie in [Fig. 3b](#) gezeigt ist, ist die Dicke der unteren Hartmaskenschicht **48** so gewählt, dass nach dem Strukturieren der Gateisolationsschicht ein Teil der unteren Hartmaskenschicht auf dem Gate als eine Schutzabdeckung **58** zurückbleibt.

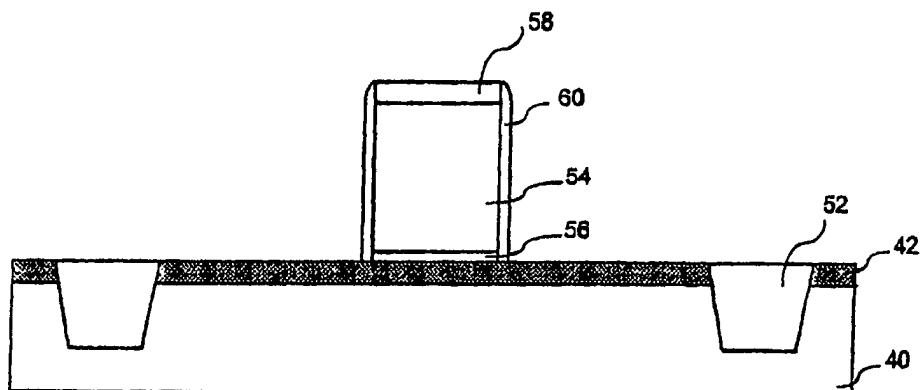

**[0032]** [Fig. 3c](#) zeigt die Struktur aus [Fig. 3b](#) nach der Herstellung von Abstandselementen **60** um das Gate **54**, den Gateisolator **56** und die Schutzabdeckung **58** herum. Die Abstandselemente **60** werden vorzugsweise durch Abscheiden einer konformen Schicht aus schützendem Material gebildet, woran sich ein anisotroper Ätzvorgang anschließt, um das schützende Material von den nicht vertikalen Oberflächen zu entfernen, um damit die Abstandselemente **60** zurückzulassen. Die Abstandselemente **60** werden vorzugsweise aus Siliziumoxid oder Siliziumnitrid gebildet.

**[0033]** In einer beispielhaften Ausführungsform wird die bei der Herstellung der Abstandselemente **60** verwendete konforme Schicht unter Anwendung eines plasmaunterstützten chemischen Dampfabscheide-(PECVD)Prozesses abgeschieden. Dieser PECVD-Prozess ist vorzugsweise eine Abscheidung mit hoher Druckspannung, die eine Zugverformung in der Siliziumschicht **42** erzeugt. Eine Abscheidung mit hoher Druckspannung kann durch eine Vorspannungs-RF-Leistung erreicht werden, woraus sich ein höherer Ionenbeschuss und eine Kompression in der Richtung der Siliziumschicht **42** ergibt.

**[0034]** [Fig. 3d](#) zeigt die Struktur aus [Fig. 3c](#) nach dem Abscheiden einer Ätzstoppeschicht (ESL) **63**, die konform über dem Gate **54**, der schützenden Abdeckung **58**, den Abstandselementen **60** und der Siliziumschicht **42** vorgesehen ist. In einer beispielhaften Ausführungsform wird die Ätzstoppeschicht **63** in einem PECVD-Prozess mit hoher Spannung abgeschieden, um damit eine Zugverformung in der Siliziumschicht **42** zu vergrößern. Eine Abscheidung mit hoher Druckspannung kann durch erhöhen Ionenbeschuss erreicht werden.

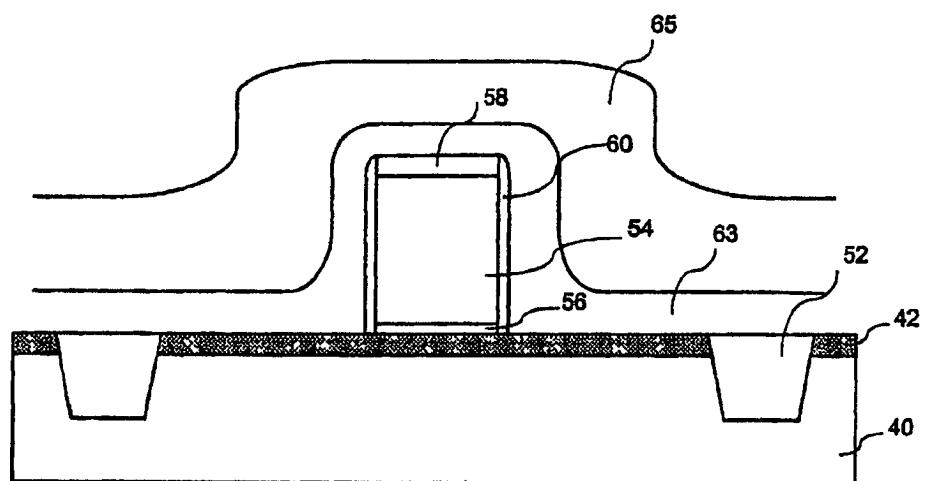

**[0035]** [Fig. 3e](#) zeigt die Struktur aus [Fig. 3d](#) nach der Abscheidung einer Zwischendielektrikumsschicht (ILD) **65**. Die ILD-Schicht **65** wird konform über der Ätzstoppeschicht **63** abgeschieden. Vorzugsweise

wird die ILD-Schicht **65** in einem PECVD-Prozess mit hoher Druckspannung abgeschieden. Die Abscheidung mit hoher Druckspannung erhöht die Kompression in der Richtung der Siliziumschicht **42**, wodurch eine Zugverformung hinzugefügt wird und damit die Ladungsträgerbeweglichkeit verbessert wird.

**[0036]** Es können andere Schichten abgeschieden werden, etwa Beschichtungen oder eine weitere Abstandsschicht. Derartige zusätzliche Schichten können ebenso mit Abscheidetechniken mit hoher Druckspannung aufgebracht werden, um die Zugverformung in der Siliziumschicht **42** zu erhöhen.

**[0037]** Obwohl die in den [Fig. 3a](#) bis [Fig. 3e](#) gezeigte Bearbeitung eine gegenwärtig bevorzugte Ausführungsform repräsentiert, können eine Vielzahl von Alternativen durchgeführt werden. Folglich können eine Vielzahl von Ausführungsformen gemäß der Erfindung eingerichtet werden. Im Allgemeinen beinhalten derartige Ausführungsformen einen MOSFET, der ein verformtes Siliziumkanalgebiet auf einer Silizium/Germanium-Schicht aufweist, und der ferner Source- und Draingebiete besitzt, die in Siliziumgebieten ausgebildet sind, die an gegenüberliegenden Seiten des Gates vorgesehen sind. Die Tiefe der Source- und Draingebiete erstreckt sich nicht über die Tiefe der Siliziumgebiete hinaus, wodurch der nachteilige Leckstrom am Übergang und die parasitäre Kapazität konventioneller Silizium/Germanium-Bauelemente reduziert werden.

**[0038]** In einer alternativen Ausführungsform kann ein Diffusionsofen nach dem Prozessieren des SiGe benutzt werden, um nicht-SiGe-Material durch Durchführen eines Nassoxidationsreinigungszyklusses zu prozessieren. Dieser Nassoxidationszyklus beinhaltet eine Hochtemperatur H<sub>2</sub>O-Oxidation, um Ge in Ge-Oxid umzuwandeln, das flüchtig ist. Ein derartiger Prozess kann wiederholt werden, um die Kontamination unter die Nachweisgrenzen zu reduzieren.

**[0039]** In einer weiteren alternativen Ausführungsform kann die Si-Verformungstechnologie mit der Technologie des vollständig verarmten Siliziums auf Isolator (SOI) kombiniert werden. Es gibt jedoch ein Problem dahingehend, dass das verformte Silizium von einer darunterliegenden SiGe-Schicht getragen wird und die Verformung kann verschwinden, wenn das SiGe entfernt wird. Die Verformung kann erhalten werden, indem ein einkristallines Material mit großem  $\epsilon$  eingeführt wird, das eine ähnliche Gitterkonstante wie SiGe aufweist. Beispielsweise können 20% SiGe mit DySiO<sub>3</sub> oder GdSiO<sub>3</sub> erreicht werden.

**[0040]** In einer weiteren alternativen Ausführungsform wird ein Epoxiever siegelungsmittel oder eine Versiegelung aus einem weiteren geeigneten Material auf die obere Fläche eines Siliziumchips aufge-

bracht. Durch Modifizieren der Eigenschaften des Versiegelungsmaterials kann die Spannung in dem Siliziumchip so modifiziert werden, dass eine Zugspannung hervorgerufen wird. Wie zuvor erläutert ist, verbessert die Zugspannung die Ladungsträgerbeweglichkeit, wodurch die Bauteilgeschwindigkeit verbessert wird. Eine weitere Möglichkeit, um die Zugspannung zu erhöhen, besteht darin, ein kuppelförmiges Metallsubstrat zu verwenden, auf dem der Chip angeordnet werden kann. Die Kuppelform kann durch Formung oder Ätzen hergestellt werden. Die Kuppelform liefert eine physikalische mechanische Spannung für den Siliziumchip, woraus sich eine Zugspannung ergibt.

**[0041]** [Fig. 4](#) zeigt einen Prozessablauf, der die bevorzugte Ausführungsform aus den [Fig. 3a](#) bis [Fig. 3e](#), die zuvor genannten Alternativen und weitere Alternativen repräsentiert. Zunächst wird ein Substrat in einem Vorgang 80 bereitgestellt. Das Substrat umfasst eine Schicht aus Silizium/Germanium mit einer darauf ausgebildeten Schicht aus Silizium. Das Substrat umfasst ferner einen Gateisolator, der auf der verformten Siliziumschicht ausgebildet ist, und umfasst ein Gate, das auf dem Gateisolator gebildet ist. Eine Abstandsschicht wird abgeschieden und es wird ein Abstandselement um das Gate und den Gateisolator in einem Vorgang 82 herum gebildet. In einer anschaulichen Ausführungsform wird die Abstandsschicht in einer äußerst druckverformenden Weise abgeschieden, woraus eine Kompression und damit eine Zugverformung in der darunterliegenden Siliziumschicht hervorgerufen wird.

**[0042]** Es wird eine Ätzstoppschicht konform über dem Gate, dem Abstandselement und den Siliziumschichten in einem Vorgang 84 vorgesehen. In einer anschaulichen Ausführungsform wird die Ätzstoppschicht mit hoher Druckspannung abgeschieden, wodurch die Zugverformung in der Siliziumschicht erhöht wird. Eine Zwischendielektrikumsschicht (ILD) wird über der Ätzstoppschicht in einem Vorgang 86 abgeschieden. Alternativ kann eine beliebige Materialschicht abgeschieden werden. In einer beispielhaften Ausführungsform wird die ILD-Schicht in einem PECVD-Prozess mit hoher Druckspannung abgeschieden. Eine Abscheidung mit hoher Druckspannung kann zumindest in einer der Abscheidungen der Vorgänge 82, 84 und 86 angewendet werden. Alternativ kann die Abscheidung mit hoher Druckspannung in allen drei Vorgängen 82, 84 und 86 eingesetzt werden. In einem Vorgang 88 wird die Struktur bearbeitet, was die Herstellung eines oder einer Vielzahl von Strukturelementen, etwa Kontakten für Source- und Draingebiete, Metallverbindungen, IMD-Schichten und einer Passivierungsschicht beinhaltet.

**[0043]** Der Fachmann erkennt, dass die in den obigen Prozessen beschriebenen Aufgaben nicht notwendigerweise andere Aufgaben ausschließen, und dass diese weiteren Aufgaben in die obigen Prozesse entsprechend den speziellen herzustellenden Strukturen eingeführt werden können. Beispielsweise können zwischenzeitliche Prozessaufgaben, etwa die Ausbildung und das Entfernen von Passivierungsschichten oder Schutzschichten zwischen den eigentlichen Prozessaufgaben, die Herstellung und das Entfernen von Photolackmasken und anderer maskierender Schichten, das Dotieren und Gegendotieren, das Reinigen, das Einebnen und andere Aufgaben zusammen mit den speziell zuvor beschriebenen Aufgaben ausgeführt werden.

**[0044]** Der in der Beschreibung der beispielhaften Ausführungsformen angegebene Prozess muss nicht an dem ganzen Substrat, etwa einer gesamten Scheibe, ausgeführt werden, sondern dieser kann selektiv auf Abschnitten des Substrats ausgeführt werden. Obwohl daher die in den Figuren gezeigten und zuvor beschriebenen Ausführungsformen momentan die bevorzugten Ausführungsformen sind, sollte es selbstverständlich sein, dass diese Ausführungsformen lediglich zum Zwecke der Darstellung angegeben sind. Die Erfindung ist nicht auf eine spezielle Ausführungsform eingeschränkt, sondern erstreckt sich über diverse Modifizierungen, Kombinationen und Permutationen, die innerhalb des Schutzbereichs der beanspruchten Erfindung und ihrer Äquivalente liegen.

## Patentansprüche

1. Verfahren zur Herstellung eines Metalloxidhalbleiterfeldeffekttransistors, MOSFET, mit: Bereitstellen eines Substrats (40) mit einem Gate (54), das über dem Substrat (40) ausgebildet ist; Abscheiden einer Abstandsschicht und Bilden eines Abstandselements (60) um das Gate (54) und um einen Gateisolator (56) herum, die über einer Schicht aus Silizium (42) über dem Substrat (40) angeordnet sind; Abscheiden einer Ätzstoppschicht (63) über dem Abstandselement (60), dem Gate (54) und der Schicht aus Silizium (42); und Abscheiden einer dielektrischen Schicht (65) über der Ätzstoppschicht (63); wobei zumindest einer der Schritte des Abscheidens der Abstandsschicht, des Abscheidens der Ätzstoppschicht (63) und des Abscheidens der dielektrischen Schicht (65) eine Abscheidung mit Druckspannung umfasst, um eine Zugverformung in der Schicht aus Silizium (42) zu erhöhen.

2. Verfahren nach Anspruch 1, wobei Abscheiden einer Abstandsschicht, Abscheiden einer Ätzstoppschicht (63) und Abscheiden einer dielektrischen Schicht (65) jeweils eine plasmaunterstützte chemische Dampfabscheidung, PECVD, beinhaltet.

3. Verfahren nach Anspruch 1 oder 2, das ferner Abscheiden einer Beschichtung unter Anwendung einer Vorspannungs-RF-Leistung für einen Ionenbeschuss umfasst.

4. Verfahren nach Anspruch 1, 2 oder 3, wobei die Schicht aus Silizium (**42**) eine Dicke von mindestens 200 nm aufweist.

5. Verfahren nach einem der vorhergehenden Ansprüche, wobei eine Beschichtung zwischen dem Gate (**54**) und dem Abstandselement (**60**) enthalten ist.

6. Verfahren nach einem der vorhergehenden Ansprüche, wobei die Ätzstoppschicht (**63**) Siliziumnitrid aufweist.

7. Verfahren nach einem der vorhergehenden Ansprüche, wobei das Substrat (**40**) eine Silizium/Germanium-Schicht aufweist.

8. Verfahren nach einem der vorhergehenden Ansprüche, das ferner umfasst: Bilden von Source- und Draingebieten in der Schicht aus Silizium (**42**) an gegenüberliegenden Seiten des Gates (**54**), wobei die Tiefe der Source- und Draingebiete sich nicht über die Tiefe der Schicht aus Silizium (**42**) hinaus erstreckt.

Es folgen 4 Blatt Zeichnungen

Anhängende Zeichnungen

Fig.3a

Fig.3b

Fig.3c

Fig.3d

Fig.3e

Fig.4