**【特許請求の範囲】****【請求項 1】**

電源の出力を調節する集積回路であって、

外部電流を受け取るように結合されたスイッチと、

外部制御信号と前記スイッチの電流に比例する内部電流検出信号に応答して、前記スイッチによる前記外部電流のスイッチングを制御するように前記スイッチに結合されたコントローラとを備え、前記内部電流検出信号がないとき、前記電源の出力が調節される集積回路。

**【請求項 2】**

前記スイッチの導通時間が、前記外部制御信号と前記内部電流検出信号に応答する請求項 1 に記載の集積回路。

**【請求項 3】**

前記スイッチの導通時間が、前記スイッチの前記電流の連続値に応答し、前記連続値の範囲が、ほぼゼロの電流と前記スイッチの最大許容電流の間である請求項 1 に記載の集積回路。

**【請求項 4】**

前記内部電流検出信号に応答する、前記スイッチの導通時間の調整が、前記スイッチの電流に比例する請求項 1 に記載の集積回路。

**【請求項 5】**

前記スイッチの前記導通時間の前記調整が、前記スイッチの前記電流の増加に応答した、前記スイッチの前記導通時間の減少である請求項 4 に記載の集積回路。

**【請求項 6】**

前記電流検出信号が、前記スイッチの前記電流と、集積回路の領域間を接続する金属導体の抵抗とに比例する第 1 の電圧である請求項 1 に記載の集積回路。

**【請求項 7】**

パルス幅変調器に結合された発振器をさらに備え、前記パルス幅変調器が、前記外部制御信号と前記内部電流検出信号とに応答する、前記スイッチのデューティ比を有する出力を発生するように前記発振器に結合される請求項 1 に記載の集積回路。

**【請求項 8】**

前記スイッチが、前記パルス幅変調器の出力に結合された請求項 7 に記載の集積回路。

**【請求項 9】**

電源の出力を制御する方法であって、

スイッチを用いて外部電流を受け取るステップと、

外部制御信号に応答して、前記スイッチのスイッチングを制御するステップと、

外部電流を受け取るように結合されたスイッチに応答して、前記スイッチのスイッチングを調整するステップと、

コントローラであって、外部制御信号と、前記スイッチの電流に比例する内部電流検出信号とに応答して、前記スイッチによる前記外部電流のスイッチングを制御するように前記スイッチに結合されたコントローラとを含み、前記内部電流検出信号がないとき、前記電源の出力が調節される方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は一般に電源に関し、より具体的には本発明はスイッチング電源内のスイッチの制御に関する。

**【背景技術】****【0002】**

知られているスイッチング電源では、制御信号に応答して、電源の入力から電源の出力へ供給される電力を調節するために、スイッチがスイッチ・オンおよびオフされる。制御信号は、出力を調節する帰還信号である。通常、帰還信号の値と、スイッチの所望の導通

10

20

30

40

50

時間の間には 1 対 1 の対応がある。したがって所与の 1 組の動作状態に対しては、帰還信号の値だけで、スイッチの導通時間が決まる。

【0003】

スイッチの導通時間が帰還信号のみに応答する、知られている電源では、電源の動作における外乱は、スイッチが応答できる前に外乱が帰還信号中に現れるまで、システムを伝搬しなければならない。帰還回路は通常、多くのスイッチング周期にわたって出力の平均値を調節するように設計されているので、応答が遅い。したがってスタートアップなどの過渡事象は、制御回路が所望の定常状態を確立する前に、電源内の電圧と電流に望ましくない逸脱を生じ得る。

【発明を実施するための最良の形態】

10

【0004】

本発明の非限定的かつ非網羅的な実施形態について、別段の指定がない限り様々な図を通して同じ参照番号は同じ部品を指している以下の図を参照して説明する。

【0005】

スイッチング電源内のスイッチを制御する方法および装置が開示される。以下の説明では本発明の十分な理解を得るために、数多くの具体的な詳細が記載される。しかし当業者には、本発明を実施するのに具体的な詳細を用いる必要はないことは明らかであろう。その他、本発明が不明瞭になるのを避けるため、良く知られている材料または方法については詳細に説明していない。

【0006】

20

本明細書全体にわたって「一実施形態」とは、実施形態に関連して説明される特定の機能、構造、または特性が本発明の少なくとも 1 つの実施形態に含まれることを意味する。したがって本明細書全体にわたって様々な所で現れる「一実施形態では」という語句は、必ずしもすべて同じ実施形態を指すものではない。さらに特定の機能、構造、または特性は、1 つまたは複数の実施形態の任意の適当な組合せおよび / または部分的組合せに、組み合わせができる。また本明細書に示される図面は当分野の技術者に説明するためのものであり、かつ図面は必ずしも原寸に比例して描かれていないことを理解されたい。

【0007】

本発明の教示による回路の様々な例において、スイッチング電源内のスイッチの制御について説明する。一例ではスイッチと制御回路が集積回路に含まれる。制御回路は、スイッチの所望の導通時間に対応する制御信号を受け取る。スイッチング周期ごとに制御回路は、そのスイッチング周期の間のスイッチの電流に応答して、所望の導通時間をわずかに低減させる。本発明の教示による、この、制御信号に無関係な導通時間の低減は、過渡外乱に対する電源の応答を改善する。本発明の教示による、スイッチング周期ごとのスイッチ電流の増加に対するスイッチの導通時間の低減は、過渡外乱による逸脱を制限するダンピング効果を生じ、帰還回路の複雑さを少なくし、安定化電源の安定性を向上させる。

30

【0008】

本発明の教示による一例では、スイッチは、スイッチの導通時間をスイッチの電流に依存させるための、スイッチと一体の機構と共に集積化される。導通時間の電流に対する依存性は、集積化スイッチの固有の特性である。この特徴を利用するのに、外部の接続または構成部品は必要ない。本発明の教示による一例では、集積化スイッチは、スイッチの電流を、集積回路の一部である金属導体の両端に生じる電圧として検出する。

40

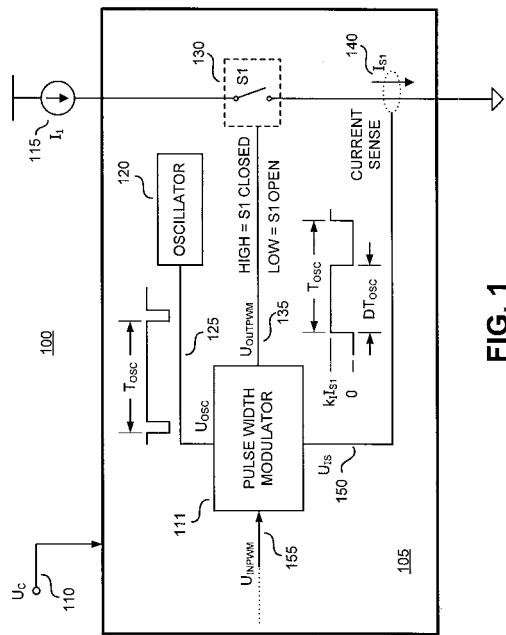

【0009】

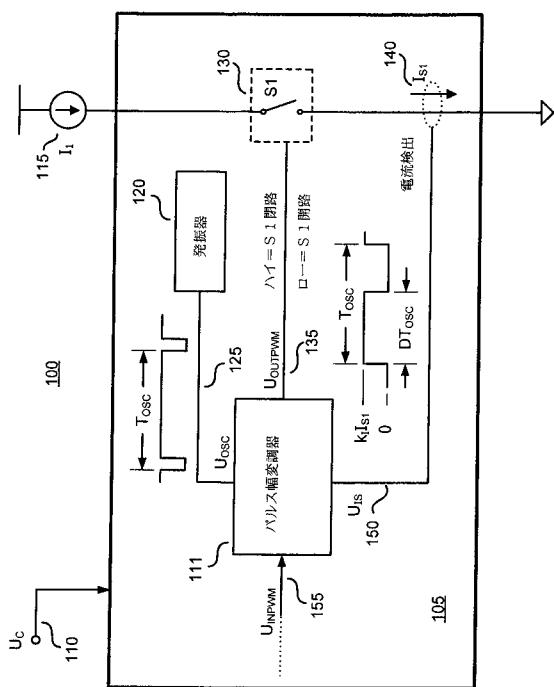

図 1 は説明のために、本発明の教示による集積回路 105 の一例の応用例 100 を全体的に示す。図示のように集積回路 105 は、制御信号  $U_c$  110 を受け取る。この信号は電圧でも電流でもよい。パルス幅変調器 111 は、制御信号  $U_c$  110 に関する入力信号  $U_{INPWM}$  155 を受け取る。パルス幅変調器 111 はまた、発振器 120 から周期的タイミング信号  $U_{osc}$  125 を受け取る。タイミング信号  $U_{osc}$  125 は周期  $T_{os}$  を有する電圧でも電流でもよい。パルス幅変調器 111 は、スイッチ S1 130 を切り替えるように結合された出力  $U_{OUTPWM}$  135 を発生する。この出力は電圧でも電流で

50

もよい。スイッチ S<sub>1</sub> 130 は、集積回路 105 によって受け取られるように結合された外部電流 I<sub>1</sub> 115 を切り替える。スイッチ S<sub>1</sub> 130 は、周期 T<sub>osc</sub> の一部分 D の間、導通し、ここで D はデューティ比である。スイッチ S<sub>1</sub> 130 の電流 I<sub>S1</sub> 140 は、内部信号 U<sub>IS</sub> 150 として検出される。内部信号 U<sub>IS</sub> 150 は、電圧でも電流でもよく、次のように係数 k<sub>1</sub> によって電流 I<sub>S1</sub> 140 に関係付けられる。

$$U_{IS} = k_1 I_{S1} \quad (1)$$

例では、内部電流検出信号 U<sub>IS</sub> 150 が電圧のときは、係数 k<sub>1</sub> は抵抗の単位または次元を有する。電流検出信号 U<sub>IS</sub> 150 が電流のときは、係数 k<sub>1</sub> は無次元となる。本発明の教示によるパルス幅変調器 111 は、デューティ比 D を調整するために、電流検出信号 U<sub>IS</sub> 150 を受け取る。本発明の教示による一例では、スイッチの電流 I<sub>S1</sub> はアナログの連続値であり、したがってデューティ比 D によって影響を受けるスイッチの導通時間は、スイッチの電流 I<sub>S1</sub> の連続値に応答することに留意されたい。本発明の教示による一例では、スイッチの電流の連続値 I<sub>S1</sub> の範囲は、ほぼゼロの電流とスイッチの最大許容電流の間である。

10

## 【0010】

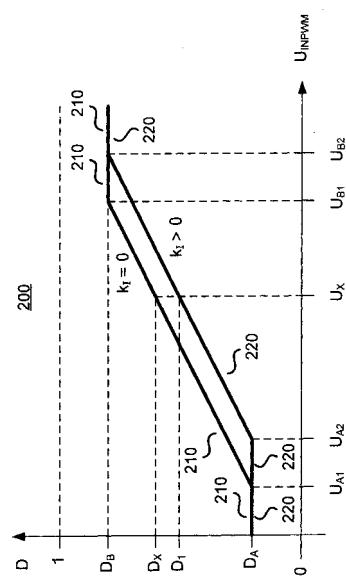

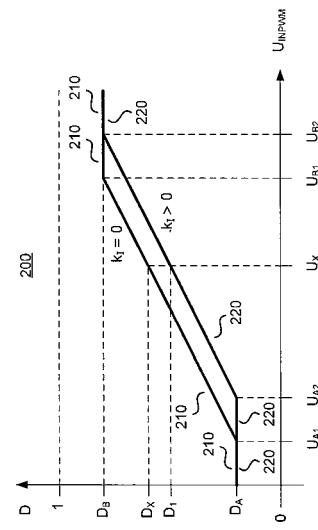

図 2 は、図 1 の例のパルス幅変調器 111 の動作を全体的に示すグラフ 200 である。特性の線分 210 と 220 は、電流検出信号 U<sub>IS</sub> 150 の 2 つの値に対する入力信号 U<sub>IN PWM</sub> 155 に応答するスイッチ S<sub>1</sub> 130 のデューティ比 D の値を示している。線分 210 は、電流検出信号 U<sub>IS</sub> 150 が常にゼロのときのデューティ比 D の値を表し、値がゼロの係数 k<sub>1</sub> に対応する。線分 220 は、電流検出信号 U<sub>IS</sub> 150 が、スイッチ S<sub>1</sub> 130 のゼロでない電流 I<sub>S1</sub> 140 の一部分であるときのデューティ比 D の値を表す。

20

## 【0011】

図 2 は、デューティ比 D はゼロと 1 の間であり、入力信号 U<sub>IN PWM</sub> が値 U<sub>A1</sub> または U<sub>A2</sub> からそれより高い値 U<sub>B1</sub> または U<sub>B2</sub> に増加するのに従って、最小値 D<sub>A</sub> から最大値 D<sub>B</sub> まで直線的に増加することを示す。U<sub>A2</sub> と U<sub>B1</sub> の間の値 U<sub>X</sub> を有する入力信号 U<sub>IN PWM</sub> に対しては、ゼロでない電流検出信号 U<sub>IS</sub> 150 が存在する場合、デューティ比は値 D<sub>X</sub> から低い値 D<sub>1</sub> に減少される。D<sub>1</sub> の値は、U<sub>IS</sub> の値が増加するのに従って減少する。

20

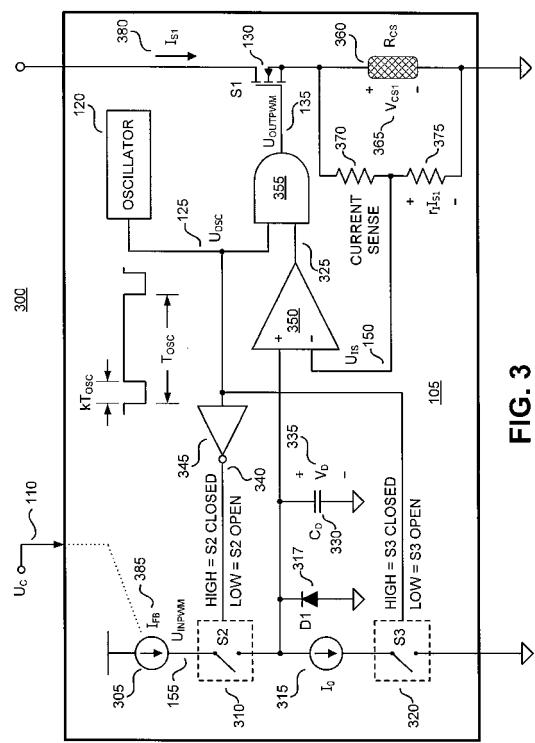

## 【0012】

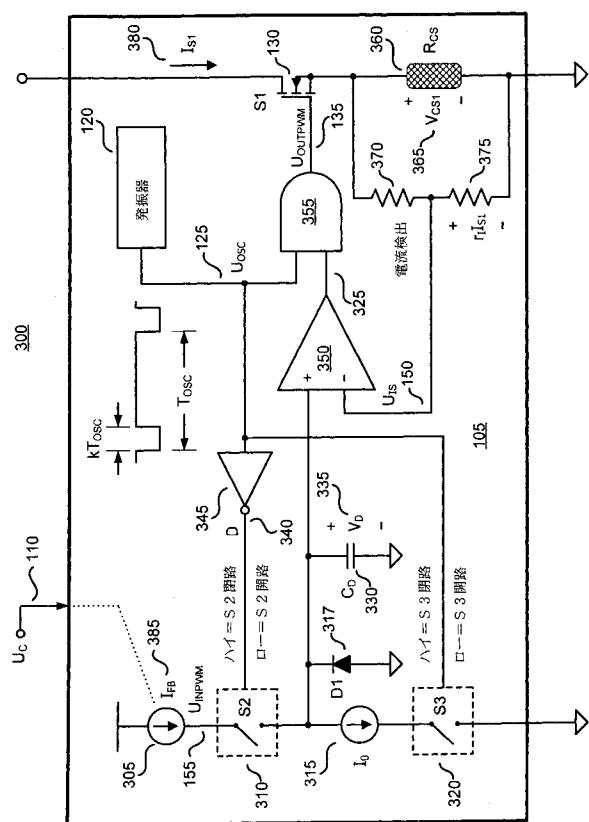

図 3 は、本発明の教示による集積回路 105 に含まれた集積化スイッチの一例 300 を全体的に示す。集積回路 105 は、電流源 305 と 315、スイッチ 310 と 320、ダイオード D<sub>1</sub> 317、コンデンサ C<sub>D</sub> 330、インバータ 345、比較器 350、AND ゲート 355 を備えるパルス幅変調器を含む。発振器 120 は、周期が T<sub>osc</sub> である周期的なタイミング信号 U<sub>osc</sub> 125 を発生する。発振器 120 からのタイミング信号 U<sub>osc</sub> 125 は、周期 T<sub>osc</sub> の一部分 k の間、ローとなる。タイミング信号 U<sub>osc</sub> は、インバータ 345 の入力、および AND ゲート 355 の入力に結合される。スイッチ S<sub>2</sub> 310 は、インバータ 345 の出力 340 がハイのときに閉じるように結合される。スイッチ S<sub>3</sub> 320 は、タイミング信号 U<sub>osc</sub> がハイのときに閉じるように結合される。当業者には、電流源 115、305、315 は有限のコンプライアンス電圧を有し、それによりそれぞれのスイッチ S<sub>1</sub> 130、S<sub>2</sub> 310、S<sub>3</sub> 320 が開路のときは、それらの電流はゼロになることが理解されよう。

30

## 【0013】

一例ではスイッチ S<sub>1</sub> 130 は、パルス幅変調器の出力でもある AND ゲート 355 の出力からの信号 U<sub>OUT PWM</sub> 135 を受け取るように結合された金属酸化膜電界効果トランジスタ (MOSFET) である。集積化トランジスタ・スイッチ S<sub>1</sub> 130 は、集積回路の外部の電流をスイッチングする。例では集積化トランジスタ・スイッチ S<sub>1</sub> 130 は、信号 U<sub>OUT PWM</sub> 135 がハイのとき、スイッチングされた電流 I<sub>S1</sub> 380 を導通する。電流検出回路網は、電流検出要素 360、抵抗器 370、抵抗器 375 を含む。一例では電流検出要素 360 は、集積回路の製造時に、集積回路の領域間を電気的に接続するため堆積される金属の層の一部分である。一例では電流検出要素 360 は、抵抗 R<sub>CS</sub>

40

50

を有する。スイッチングされた電流  $I_{S1}$  380 は、電流検出要素 360 の電圧  $V_{CS1}$  365 として検出される。図示のように抵抗器 370、375 は共に抵抗分圧器を形成し、この抵抗分圧器は電流検出要素 360 の両端に結合され、電圧  $V_{CS1}$  365 を、電流検出信号  $U_{IS}$  150 である電流検出電圧  $r_{IS} I_{S1}$  にスケーリングする。

#### 【0014】

例では集積回路 105 は、電流源 305 からの電流  $I_{FB}$  385 の値を決定する制御信号  $U_C$  110 を受け取る。電流  $I_{FB}$  385 は、図 1 に示されるパルス幅変調器 111 の入力信号  $U_{IN PWM}$  155 である。コンデンサ  $C_D$  330 は、タイミング信号  $U_{OSC}$  125 がローのとき、スイッチ S2 310 を通して、電流源 305 からの電流  $I_{FB}$  385 によって充電される。コンデンサ  $C_D$  330 は、タイミング信号  $U_{OSC}$  125 がハイのとき、スイッチ S3 を通して、電流源 315 からのほぼ固定の電流  $I_o$  によって放電する。ダイオード D1 317 は、電圧  $V_D$  335 に下限を設定する。比較器 350 は、コンデンサ  $C_D$  330 の電圧  $V_D$  335 を、内部電流検出信号  $U_{IS}$  150 と比較する。コンデンサ  $C_D$  330 の電圧  $V_D$  335 が電流検出信号  $U_{IS}$  150 より大きいときは、比較器 350 の出力 325 はハイとなる。コンデンサ  $C_D$  330 の電圧  $V_D$  335 が電流検出信号  $U_{IS}$  150 以下のときは、比較器 350 の出力 325 はローとなる。したがって本発明の教示により、集積回路 105 は、集積化スイッチ S1 130 を、 $T_{OSC}$  の周期で周期的に、かつ制御信号  $U_C$  110 とスイッチングされた電流  $I_{S1}$  380 の両方の共同によりまたは両方に応答して決定される導通時間で周期的にスイッチングする。

10

20

30

40

50

#### 【0015】

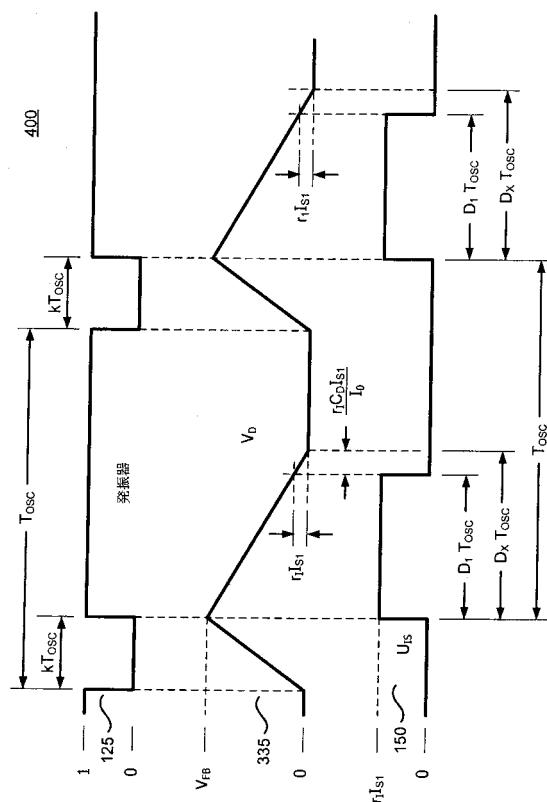

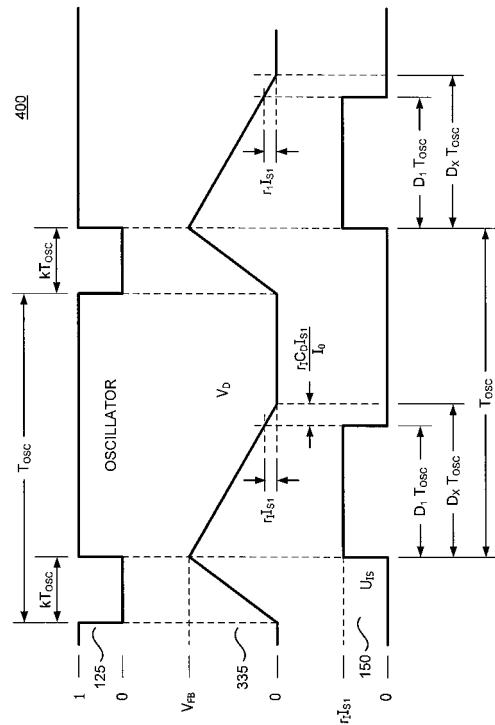

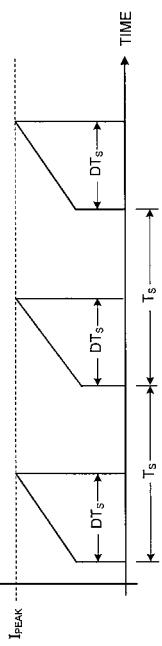

図 4 は、図 3 の例の集積化スイッチ 300 の信号のタイミング関係 400 を説明する例示の波形を全体的に示す。コンデンサ  $C_D$  330 は、時間  $k T_{OSC}$  の間、電流源 305 からの電流  $I_{FB}$  385 によって充電され、タイミング信号  $U_{OSC}$  125 がハイになるとき電圧  $V_{FB}$  に達する。次いでスイッチ S1 130 は、電流  $I_{S1}$  380 の導通を開始する。図 4 に示される例では、スイッチ S1 130 が導通している間、スイッチングされた電流  $I_{S1}$  380 は一定の電流である。次いでコンデンサ  $C_D$  330 は、電流源 315 からの電流  $I_o$  によって放電される。コンデンサ  $C_D$  の電圧  $V_D$  が、電流検出信号  $U_{IS}$  150 の値に達すると、スイッチ S1 130 は導通を停止する。したがってスイッチ S1 の導通時間は、スイッチ S1 130 の電流  $I_{S1}$  380 の値によって影響を受ける。所与の制御信号  $U_C$  110 の値に対して、集積化スイッチ S1 130 の導通時間は、内部電流検出信号  $U_{IS}$  150 に比例する量だけ減少する。すなわち図 4 は本発明の教示により、内部電流検出信号  $U_{IS}$  150 の影響によって、図 2 のデューティ比 D がどのようにして値  $D_x$  から値  $D_1$  に減少するかを示している。したがって本発明の教示による例では、内部電流検出信号  $U_{IS}$  150 に応答した、スイッチのデューティ比 D すなわち導通時間の調整量は、スイッチ S1 130 の電流  $I_{S1}$  380 に比例する。

#### 【0016】

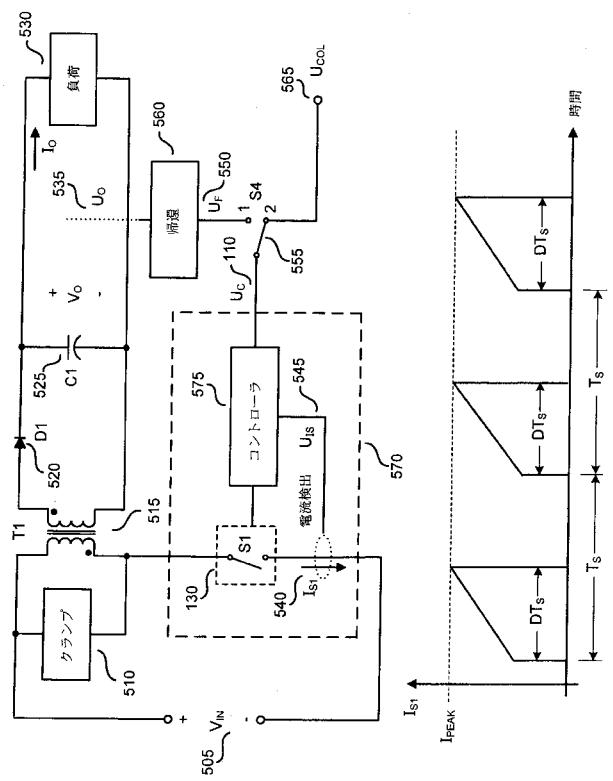

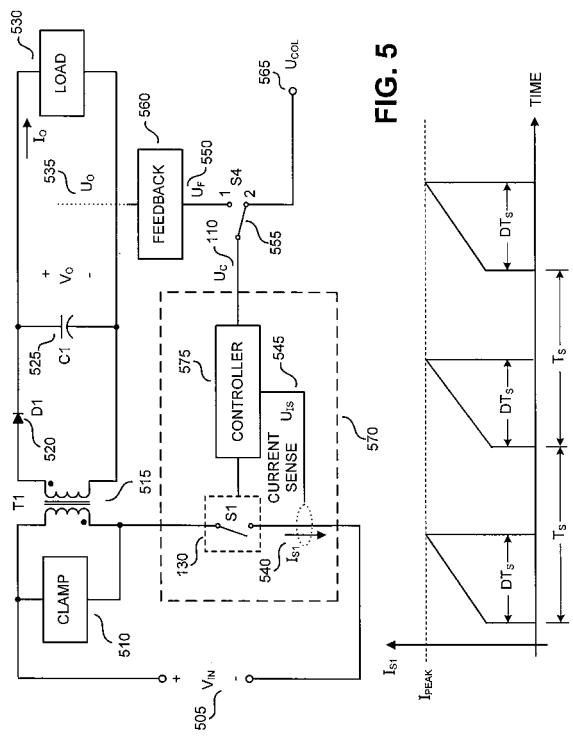

図 5 は、本発明の教示によるスイッチング電源の例を全体的に示す。図示の例で、図 5 の電源のトポロジーは、フライバック・レギュレータとして知られている。スイッチング・レギュレータには多くのトポロジーと構成があり、図 5 に示されるフライバック・トポロジーは説明を目的としたものであり、本発明の教示によれば、他の電源トポロジーを含み得ることを理解されたい。

#### 【0017】

図示の例に示されるように、図 5 の電源は、非安定化入力電圧  $V_{IN}$  505 から、負荷 530 に出力電力を供給する。入力電圧  $V_{IN}$  505 は、エネルギー伝達要素 T1 515 と集積化スイッチ S1 130 に結合される。図 1 の例では、エネルギー伝達要素 T1 515 は、電源の入力と電源の出力の間に結合されることに留意されたい。図 5 の例では、エネルギー伝達要素 T1 115 は、2つの巻線を有する変圧器として示される。一般に変圧器は、追加の負荷に電力を供給するため、バイアス電圧を供給するため、または負荷の電圧を検出するための追加の巻線を含めて、3つ以上の巻線をもつことができる。

図5に示される例では、集積回路570に含まれる集積化スイッチS1 130の最大電圧を制御するために、エネルギー伝達要素T1 515の一次巻線にクランプ回路510が結合される。

【0018】

例では本発明の教示により、集積化スイッチS1 130は、発振器とパルス幅変調器を含む例示のコントローラ回路575に応答して、スイッチをオン・オフする。一例ではスイッチS1 130は、たとえばパワー金属酸化膜半導体電界効果トランジスタ(MOSFET)などのトランジスタである。動作時には、例示の集積化スイッチS1 130は、整流器D1 520に脈動電流を発生し、この電流は、負荷530にほぼ一定の出力電圧 $V_o$ またはほぼ一定の出力電流 $I_o$ を生じるように、コンデンサC1 525によってフィルタリングされる。

【0019】

一例では調節されるべき出力量は、一般に出力電圧 $V_o$ 、出力電流 $I_o$ 、またはこの2つの組合せである $U_o$  535である。例では調節される量は、必ずしも固定でなく、帰還信号に応答して所望の形に変化するように調節することができる。帰還回路560は、出力量 $U_o$  535に結合されて帰還信号 $U_F$  550を発生する。帰還信号 $U_F$  550は、集積回路570に含まれるコントローラ575への外部入力 $U_c$  110となる。コントローラ575への内部入力は、本発明の教示による、スイッチS1 130のスイッチングされた電流 $I_{s1}$  540を検出する、電流検出信号 $U_{is}$  545である。

【0020】

図5のスイッチング電源の例において、スイッチS1 130が導通しているときのスイッチングされた電流 $I_{s1}$ は一定ではなく、スイッチング周期 $T_s$ の一部分Dである導通時間の間、ピーク値 $I_{PEAK}$ まで直線的に増加する。スイッチングされた電流 $I_{s1}$ のピーク値は、負荷530の電流 $I_o$ と共に変化する。通常動作時はコントローラ575は、入力電圧 $V_{IN}$  505の変化と負荷530の変化に応答して出力 $U_o$  535を調節するよう、帰還信号 $U_F$ に応答してスイッチのデューティ比Dを変化させる。

【0021】

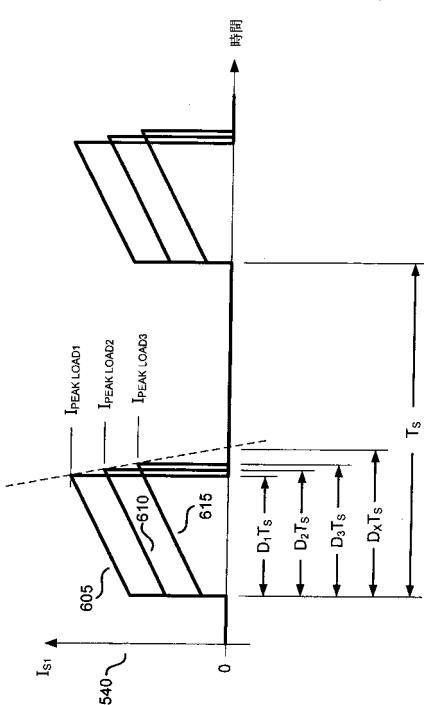

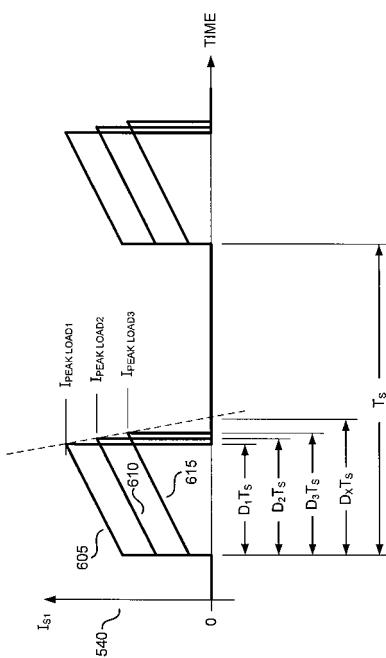

一例では図5の電源回路には、帰還信号 $U_F$  550または一定の開ループ信号 $U_{COL}$  565のいずれかを、入力 $U_c$  110とすることができるようにスイッチS4 555が含まれる。例ではスイッチS4 555が位置1にあるときは、コントローラ575への入力 $U_c$ は帰還信号 $U_F$ である。スイッチS4 555が位置2にあるときは、コントローラ575への入力 $U_c$ は一定の開ループ信号 $U_{COL}$  565となる。本発明の教示により、例ではスイッチが位置2にあるときは、帰還信号の影響は取り除かれ、図6に示されるようにデューティ比はピーク電流 $I_{PEAK}$ の変化のみに応答する。

【0022】

図6は説明のため、入力 $U_c$  110を一定の開ループ信号 $U_{COL}$  565に設定するようにスイッチS4 555が位置2にあるときの、負荷530の3つの異なる値に対するスイッチングされた電流 $I_{s1}$  540の例示の波形を全体的に示す。例では、導通時間 $D_x T_s$ のデューティ比 $D_x$ は、電流検出信号 $U_{is}$  545がゼロとなった状態に対応する。図示のようにゼロでない有限の電流検出信号 $U_{is}$  545は、それぞれ電流605、610、615で示されるように、それぞれピーク電流 $I_{PEAK\_LOAD1}$ 、 $I_{PEAK\_LOAD2}$ 、 $I_{PEAK\_LOAD3}$ に対する導通時間 $D_1 T_s$ 、 $D_2 T_s$ 、 $D_3 T_s$ に対応する $D_1$ 、 $D_2$ 、 $D_3$ に、デューティ比を減少させる。したがって本発明の教示により、内部電流検出信号 $U_{is}$  545は、内部集積化スイッチS1 130の電流が増加するにつれて、スイッチS1 130の導通時間と対応する減じられるデューティ比が減少されるように、内部スイッチS1 130の導通時間を調整する。したがって電流検出信号 $U_{is}$  545による導通時間の調整は、出力 $U_o$  535の調節に認め得るほどの影響を及ぼすほど大きくはない。通常動作時はスイッチS4 555は位置1にあり、入力 $U_c$ は帰還信号 $U_F$  550であり、電源の出力 $U_o$  535は、電流検出信号 $U_{is}$ がないとき依然として調節される。言い換えれば、本発明の教示によれば、内部電流検出信号がない場合でも電源の出力は調節される。

10

20

30

40

50

## 【0023】

上記の本発明の図示の例についての説明は、要約書での説明を含めて、網羅的ではなく、あるいは開示された正確な形に限定されるものではない。本明細書には例示のために、本発明の特定の実施形態や、その例が述べられているが、本発明の、より広い趣旨および範囲から逸脱せずに様々な等価な変形形態が可能である。確かに、具体的な電圧、電流、周波数、電力範囲の値、時間などは説明のために記載しており、本発明の教示による他の実施形態および例には他の値も用い得ることを理解されたい。

## 【0024】

本発明の例に対するこれらの変更は、上記の詳細な説明に照らして行うことができる。添付の特許請求の範囲で用いられる用語は、本発明を、明細書および特許請求の範囲に開示される特定の実施形態に限定するものと理解されるべきではない。むしろ範囲は専ら請求項の解釈の確立された原則によって理解されるべき添付の請求項によって規定されるべきである。したがって本明細書および図面は、限定的ではなく例示的なものと見なされるべきである。

10

## 【図面の簡単な説明】

## 【0025】

【図1】本発明の教示による、集積回路105の一例の応用例100を全体的に示す図である。

20

【図2】本発明の教示による、図1の例によるパルス幅変調器111の動作を全体的に示すグラフ200である。

【図3】本発明の教示による、集積回路105内に含まれる集積化スイッチの一例300を全体的に示す図である。

【図4】本発明の教示による、図3の例の集積化スイッチ300の信号のタイミング関係400を示す波形を全体的に示す図である。

30

【図5】本発明の教示による、一例のスイッチング電源を全体的に示す図である。

【図6】本発明の教示による、入力 $U_C$ を一定の開ループ信号 $U_{COL}$ に設定するためにスイッチが位置2にあるときの、負荷の3つの異なる値に対する、スイッチングされた電流 $I_{S1}$ の例示の波形を全体的に示す図である。

## 【符号の説明】

## 【0026】

100 応用例、105 集積回路、110 制御信号、111 パルス幅変調器、115 外部電流、120 発振器、125 タイミング信号、130 スイッチ、135 信号、140 電流、150 電流検出信号、155 入力信号

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

## 【外国語明細書】

## INTEGRATED SWITCH WITH INTERNALLY ADJUSTED CONDUCTION TIME

BACKGROUND INFORMATIONField of the Disclosure

**[0001]** The present invention relates generally to power supplies and, more specifically, the present invention relates to the control of a switch in a switching power supply.

Background

**[0002]** In known switching power supplies, a switch is switched on and off to regulate the power that is delivered to an output of the power supply from an input of the power supply in response to a control signal. The control signal is a feedback signal that regulates the output. There is typically a one-to-one correspondence between the value of the feedback signal and the desired conduction time of the switch. Thus, for a given set of operating conditions, the value of the feedback signal alone determines the conduction time of the switch.

**[0003]** In a known power supply where the conduction time of the switch responds only to the feedback signal, any disturbance in the operation of the power supply must propagate through the system until the disturbance appears in the feedback signal before the switch can respond. The feedback circuit is usually slow to respond because it is designed to regulate the average value of an output over many switching periods. Therefore, transient events such as start-up can cause undesirable

deviations in voltage and current within the power supply before the control circuit can establish the desired steady state conditions.

BRIEF DESCRIPTION OF THE DRAWINGS

**[0004]** Non-limiting and non-exhaustive embodiments of the present invention are described with reference to the following figures, wherein like reference numerals refer to like parts throughout the various views unless otherwise specified.

**[0005]** FIG. 1 shows generally an application 100 of one example of an integrated circuit 105 in accordance with the teachings of the present invention.

**[0006]** FIG. 2 is a graph 200 that illustrates generally the behavior of the pulse width modulator 111 according to the example of FIG. 1 in accordance with the teachings of the present invention.

**[0007]** FIG. 3 illustrates generally one example 300 of an integrated switch included in an integrated circuit 105 in accordance with the teaching of the invention.

**[0008]** FIG. 4 shows generally waveforms that illustrate the timing relationships 400 of signals for the example integrated switch 300 of FIG. 3 in accordance with the teachings of the present invention.

**[0009]** FIG. 5 illustrates generally an example switching power supply in accordance with the teachings of the present invention.

**[0010]** FIG. 6 shows generally example waveforms of the switched current  $I_{S1}$  for three different values of the load when the switch is in position 2 to set the input  $U_C$  to the constant open loop signal  $U_{COL}$  in accordance with the teachings of the present invention.

DETAILED DESCRIPTION

**[0011]** Methods and apparatuses for controlling a switch in a switching power supply are disclosed. In the following description numerous specific details are set forth in order to provide a thorough understanding of the present invention. It will be apparent, however, to one having ordinary skill in the art that the specific detail need not be employed to practice the present invention. In other instances, well-known materials or methods have not been described in detail in order to avoid obscuring the present invention.

**[0012]** Reference throughout this specification to "one embodiment" or "an embodiment" means that a particular feature, structure or characteristic described in connection with the embodiment is included in at least one embodiment of the present invention. Thus, appearances of the phrases "in one embodiment" or "in an embodiment" in various places throughout this specification are not necessarily all referring to the same embodiment. Furthermore, the particular features, structures or characteristics may be combined in any suitable combinations and/or subcombinations in one or more embodiments. In addition, it is appreciated that the figures provided herewith are for explanation purposes to persons ordinarily skilled in the art and that the drawings are not necessarily drawn to scale.

**[0013]** In various examples of circuits according to the teachings of the present invention, the control of a switch in a switching power supply is

described. In one example, the switch and a control circuit are included in an integrated circuit. The control circuit receives a control signal that corresponds to a desired conduction time of the switch. In every switching period, the control circuit makes a small reduction in the desired conduction time in response to the current in the switch during that switching period. This reduction of conduction time that is independent of the control signal improves the response of the power supply to transient disturbances in accordance with the teachings of the present invention. A reduction in the conduction time of the switch for an increase in switch current in each switching period produces a damping effect that restricts deviations from transient disturbances, reduces complexity of the feedback circuit, and increases the stability of the regulated power supply in accordance with the teachings of the present invention.

**[0014]** In one example, a switch is integrated with a mechanism that is integral with the switch to make the conduction time of the switch dependent on the current in the switch in accordance with the teachings of the present invention. The dependence of the conduction time on the current is an inherent property of the integrated switch. No external connections or components are required to benefit from the feature. In one example, the integrated switch senses the current in the switch as a voltage developed across a metal conductor that is part of the integrated circuit in accordance with the teachings of the present invention.

**[0015]** To illustrate, FIG. 1 shows generally an application 100 of one example of an integrated circuit 105 in accordance with the teachings of the present invention. As shown, an integrated circuit 105 receives a control signal  $U_c$  110 that may be a voltage or a current. A pulse width modulator 111 receives an input signal  $U_{INPWM}$  155 that is related to control signal  $U_c$  110. The pulse width modulator 111 also receives a periodic timing signal  $U_{osc}$  125 from an oscillator 120. Timing signal  $U_{osc}$  125 may be a voltage or a current that has a period  $T_{osc}$ . Pulse width modulator 111 produces an output  $U_{OUTPWM}$  135 that may be a voltage or a current coupled to switch a switch  $S_1$  130. Switch  $S_1$  130 switches an external current  $I_1$  115 that is coupled to be received by integrated circuit 105. Switch  $S_1$  130 conducts for a fraction  $D$  of period  $T_{osc}$  where  $D$  is the duty ratio. The current  $I_{S1}$  140 in switch  $S_1$  130 is sensed as an internal signal  $U_{IS}$  150 that may be a voltage or a current that is related to current  $I_{S1}$  140 by the factor  $k_I$  such that

$$U_{IS} = k_I I_{S1} \quad (1)$$

In the example, the factor  $k_I$  has units or dimensions of resistance when the internal current sense signal  $U_{IS}$  150 is a voltage. The factor  $k_I$  is dimensionless when the current sense signal  $U_{IS}$  150 is a current. The pulse width modulator 111 receives current sense signal  $U_{IS}$  150 to adjust the duty ratio  $D$  in accordance with the teaching of the invention. In one example, it is noted that the current in the switch,  $I_{S1}$ , is an analog signal having a continuum of values and therefore, the conduction time of the

switch as affected by the duty ratio D is responsive to a continuum of values of the current  $I_{S1}$  in the switch in accordance with the teachings of the present invention. In one example, the continuum of values of the current in the switch,  $I_{S1}$ , ranges between substantially zero current and a maximum permissible current in the switch in accordance with the teachings of the present invention.

**[0016]** FIG. 2 is a graph 200 that illustrates generally the behavior of the pulse width modulator 111 in the example of FIG. 1. Characteristic line segments 210 and 220 show the value of duty ratio D of switch S1 130 in response to the input signal  $U_{INPWM}$  155 for two values of the current sense signal  $U_{IS}$  150. Line segments 210 give the value of duty ratio D when the current sense signal  $U_{IS}$  150 is always zero, corresponding to a zero value for the factor  $k_I$ . Line segments 220 give the value of duty ratio D when the current sense signal  $U_{IS}$  150 is a nonzero fraction of the current  $I_{S1}$  150 in switch S1 130.

**[0017]** FIG. 2 shows that the duty ratio D is between zero and one, increasing linearly from a minimum value  $D_A$  to a maximum value  $D_B$  as the input signal  $U_{INPWM}$  increases from a value  $U_{A1}$  or  $U_{A2}$  to a greater value  $U_{B1}$  or  $U_{B2}$ , respectively. For an input signal  $U_{INPWM}$  with value  $U_x$  between  $U_{A2}$  and  $U_{B1}$ , the presence of a nonzero current sense signal  $U_{IS}$  150 reduces the duty ratio from a value  $D_x$  to a lower value  $D_1$ . The value of  $D_1$  decreases as the value of  $U_{IS}$  increases.

**[0018]** FIG. 3 illustrates generally one example 300 of an integrated switch included in an integrated circuit 105 in accordance with the teaching of the invention. Integrated circuit 105 includes a pulse width modulator comprising current sources 305 and 315, switches 310 and 320, diode D1 317, capacitor C<sub>D</sub> 330, inverter 345, comparator 350, and AND gate 355. An oscillator 120 produces a timing signal U<sub>osc</sub> 125 that is periodic with period T<sub>osc</sub>. Timing signal U<sub>osc</sub> 125 from oscillator 120 is low for a fraction k of the period T<sub>osc</sub>. Timing signal U<sub>osc</sub> is coupled to the input of the inverter 345 and to an input of AND gate 355. Switch S2 310 is coupled to be closed when the output 340 of inverter 345 is high. Switch S3 320 is coupled to be closed when timing signal U<sub>osc</sub> is high. One skilled in the art will appreciate that current sources 115, 305, and 315 have finite compliance voltages that cause their currents to become zero when the respective switches S1 130, S2 310, and S3 320 are open.

**[0019]** In one example, switch S1 130 is a metal oxide field effect transistor (MOSFET) coupled to receive a signal U<sub>OUTPWM</sub> 135 from the output of AND gate 355 that is also the output of the pulse width modulator. Integrated transistor switch S1 130 switches a current external to the integrated circuit. In the example, integrated transistor switch S1 130 conducts the switched current I<sub>S1</sub> 380 when the signal U<sub>OUTPWM</sub> 135 is high. A current sense network includes a current sensing element 360, a resistor 370, and a resistor 375. In one example, the current sensing element 360 is a portion of a layer of metal that is deposited during the

fabrication of the integrated circuit to make electrical connections between regions of the integrated circuit. In one example, the current sensing element 360 has a resistance  $R_{CS}$ . The switched current  $I_{S1}$  380 is sensed as a voltage  $V_{CS1}$  365 on current sensing element 360. As shown, resistors 370 and 375 together form a resistor divider, which is coupled across current sensing element 360 and scales the voltage  $V_{CS1}$  365 to a current sense voltage  $r_{IS1}$  that is the current sense signal  $U_{IS}$  150.

**[0020]** In the example, integrated circuit 105 receives a control signal  $U_C$  110 that determines the value of a current  $I_{FB}$  385 from a current source 305. Current  $I_{FB}$  385 is the input signal  $U_{INPWM}$  155 of the pulse width modulator 111 shown in FIG. 1. Capacitor  $C_D$  330 charges with current  $I_{FB}$  385 from current source 305 through switch S2 310 while the timing signal  $U_{osc}$  125 is low. Capacitor  $C_D$  330 discharges with a substantially fixed current  $I_0$  from current source 315 through switch S3 when the timing signal  $U_{osc}$  125 is high. Diode D1 317 places a lower limit on voltage  $V_D$  335. Comparator 350 compares the voltage  $V_D$  335 on capacitor  $C_D$  330 to the internal current sense signal  $U_{IS}$  150. The output 325 of comparator 350 is high when the voltage  $V_D$  335 on capacitor  $C_D$  335 is greater than the current sense signal  $U_{IS}$  150. The output 325 of comparator 350 is low when the voltage  $V_D$  335 on capacitor  $C_D$  335 is less than or equal to the current sense signal  $U_{IS}$  150. Thus, integrated circuit 105 switches an integrated switch S1 130 periodically with period  $T_{osc}$  and a conduction time determined jointly by or responsive to both the control signal  $U_C$  110

and the switched current  $I_{S1}$  380 in accordance with the teachings of the present invention.

**[0021]** FIG. 4 shows generally example waveforms that illustrate timing relationships 400 of signals for the example integrated switch 300 of FIG. 3. Capacitor  $C_D$  330 charges with current  $I_{FB}$  385 from current source 305 for a time  $kT_{osc}$  to reach a voltage  $V_{FB}$  when timing signal  $U_{osc}$  125 goes high. Switch  $S1$  130 then begins to conduct current  $I_{S1}$  380. In the example illustrated in FIG. 4, switched current  $I_{S1}$  380 is a constant current while switch  $S1$  130 is conducting. Capacitor  $C_D$  330 then discharges with current  $I_0$  from current source 315. Switch  $S1$  130 stops conducting when the voltage  $V_D$  on capacitor  $C_D$  reaches the value of current sense signal  $U_{IS}$  150. Thus, conduction time of switch  $S1$  is influenced by the value of the current  $I_{S1}$  380 in switch  $S1$  130. For a given value of a control signal  $U_C$  110, the conduction time of the integrated switch  $S1$  130 is reduced by an amount proportional to the internal current sense signal  $U_{IS}$  150. Therefore, FIG. 4 shows how the duty ratio  $D$  in FIG. 2 is reduced from the value  $D_x$  to the value  $D_1$  by the influence of the internal current sense signal  $U_{IS}$  150 in accordance with the teachings of the present invention. Thus in the example, the adjustment to the duty ratio  $D$ , or the conduction time, of the switch in response to the internal current sense signal  $U_{IS}$  150 is proportional to the current  $I_{S1}$  380 in the switch  $S1$  130 in accordance with the teachings of the present invention.

**[0022]** FIG. 5 illustrates generally an example of a switching power supply in accordance with the teachings of the present invention. In the illustrated example, the topology of the power supply in FIG. 5 is known as a flyback regulator. It is appreciated that there are many topologies and configurations of switching regulators, and that the flyback topology shown in FIG. 5 is provided for explanation purposes and that other power supply topologies may be included in accordance with the teachings of the present invention.

**[0023]** As shown in the illustrated example, the power supply in FIG. 5 provides output power to a load 530 from an unregulated input voltage  $V_{IN}$  505. The input voltage  $V_{IN}$  505 is coupled to an energy transfer element T1 515 and an integrated switch S1 130. In the example of FIG. 1, it is noted that the energy transfer element T1 515 may be coupled between an input of the power supply and an output of the power supply. In the example of FIG. 5, the energy transfer element T1 515 is illustrated as a transformer with two windings. In general, the transformer can have more than two windings, with additional windings to provide power to additional loads, to provide bias voltages, or to sense the voltage at a load. In the example illustrated in FIG. 5, a clamp circuit 510 is coupled to the primary winding of the energy transfer element T1 525 to control the maximum voltage on the integrated switch S1 130 included in an integrated circuit 570.

**[0024]** In the example, integrated switch S1 130 is switched on and off in response to an example controller circuit 575 that includes an

oscillator and a pulse width modulator in accordance with the teachings of the present invention. In one example, switch S1 130 is a transistor such as for example a power metal oxide semiconductor field effect transistor (MOSFET). In operation, example integrated switch S1 130 produces pulsating current in the rectifier D1 520 that is filtered by capacitor C1 525 to produce a substantially constant output voltage  $V_o$  or a substantially constant output current  $I_o$  at the load 530.

**[0025]** In one example, the output quantity to be regulated is  $U_o$  535, which in general could be an output voltage  $V_o$ , an output current  $I_o$ , or a combination of the two. In the example, the regulated quantity is not necessarily fixed, but can be regulated to change in a desired way in response to a feedback signal. A feedback circuit 560 is coupled to the output quantity  $U_o$  535 to produce a feedback signal  $U_F$  550 that may be an external input  $U_c$  110 to the controller 575 that is included in the integrated circuit 570. An internal input to the controller 545 is the current sense signal  $U_{IS}$  545 that senses a switched current  $I_{S1}$  540 in switch S1 130 in accordance with the teaching of the present invention.

**[0026]** Switched current  $I_{S1}$  in the switching power supply example of FIG. 5 is not constant when the switch S1 130 is conducting, but increases linearly to a peak value  $I_{PEAK}$  during the conduction time that is a fraction D of a switching period  $T_s$ . The peak value of the switched current  $I_{S1}$  changes with the current  $I_o$  in the load 530. In normal operation, controller 575 changes the duty ratio D of the switch in response to feedback signal  $U_F$  to

regulate the output  $U_o$  535 in response to changes in the input voltage  $V_{IN}$  505 and to changes in the load 530.

**[0027]** In one example, a switch S4 555 is included in the power supply circuit of FIG. 5 that allows the input  $U_c$  110 to be either the feedback signal  $U_F$  550 or a constant open loop signal  $U_{COL}$  565. In the example, when the switch S4 555 is in position 1, the input  $U_c$  to the controller 575 is the feedback signal  $U_F$ . When the switch S4 555 is in position 2, the input  $U_c$  to the controller 575 is the constant open loop signal  $U_{COL}$  565. In the example, when the switch is position 2, the influence of the feedback signal is removed, and the duty ratio is responsive only to changes in the peak current  $I_{PEAK}$  as will be shown in FIG. 6 in accordance with the teachings of the present invention.

**[0028]** To illustrate, FIG. 6 shows generally example waveforms of the switched current  $I_{S1}$  540 for three different values of the load 530 when the switch S4 555 is in position 2 to set the input  $U_c$  110 to the constant open loop signal  $U_{COL}$  565. In the example, duty ratio  $D_x$  for conduction time  $D_x T_s$  corresponds to a condition when current sense signal  $U_{IS}$  545 is reduced to zero. As shown, a finite non-zero current sense signal  $U_{IS}$  545 reduces the duty ratio to  $D_1$ ,  $D_2$ , and  $D_3$ , corresponding to conduction times  $D_1 T_s$ ,  $D_2 T_s$ , and  $D_3 T_s$ , for respective peak currents  $I_{PEAK\ LOAD1}$ ,  $I_{PEAK\ LOAD2}$ , and  $I_{PEAK\ LOAD3}$ , as shown by respective currents 605, 610, and 615. Thus, the internal current sense signal  $U_{IS}$  545 makes adjustments to the conduction time of the internal switch S1 130 such as currents in the

internal integrated switch S1 130 increase, conduction times and corresponding reduced duty ratios of the switch S1 130 are reduced in accordance with the teachings of the present invention. Therefore, the adjustment to the conduction time by the current sense signal  $U_{IS}$  545 is not sufficient to appreciably affect the regulation of the output  $U_O$  535. In normal operation, with the switch S4 555 in position 1 such that the input  $U_C$  is the feedback signal  $U_F$  550, the output  $U_O$  535 of the power supply remains in regulation when the current sense signal  $U_{IS}$  is absent. In other words, the output of the power supply is regulated even in the absence of the internal current sense signal in accordance with the teachings of the present invention.

**[0029]** The above description of illustrated examples of the present invention, including what is described in the Abstract, are not intended to be exhaustive or to be limitation to the precise forms disclosed. While specific embodiments of, and examples for, the invention are described herein for illustrative purposes, various equivalent modifications are possible without departing from the broader spirit and scope of the present invention. Indeed, it is appreciated that the specific voltages, currents, frequencies, power range values, times, etc., are provided for explanation purposes and that other values may also be employed in other embodiments and examples in accordance with the teachings of the present invention.

**[0030]** These modifications can be made to examples of the invention in light of the above detailed description. The terms used in the following

claims should not be construed to limit the invention to the specific embodiments disclosed in the specification and the claims. Rather, the scope is to be determined entirely by the following claims, which are to be construed in accordance with established doctrines of claim interpretation. The present specification and figures are accordingly to be regarded as illustrative rather than restrictive.

CLAIMS

What is claimed is:

1. An integrated circuit that regulates an output of a power supply, the integrated circuit comprising:

a switch coupled to receive an external current; and

a controller coupled to the switch to control a switching of the external current by the switch in response to an external control signal and an internal current sense signal, which is proportional to a current in the switch, wherein the output of the power supply is regulated in the absence of the internal current sense signal.

2. The integrated circuit of claim 1 wherein a conduction time of the switch is responsive to the external control signal and the internal current sense signal.

3. The integrated circuit of claim 1 wherein a conduction time of the switch is responsive to a continuum of values of the current in the switch, the continuum of values ranging between substantially zero current and a maximum permissible current in the switch.

4. The integrated circuit of claim 1 wherein an adjustment to a conduction time of the switch in response to the internal current sense signal is proportional to the current in the switch.

5. The integrated circuit of claim 4 wherein the adjustment to the conduction time of the switch is a reduction in the conduction time of the switch in response to an increase in the current in the switch.

6. The integrated circuit of claim 1 wherein the current sense signal is a first voltage, the first voltage being proportional to the current in the switch and the resistance of a metal conductor that makes connections between regions of the integrated circuit.

7. The integrated circuit of claim 1 further comprising an oscillator coupled to a pulse width modulator, wherein the pulse width modulator is coupled to the oscillator to produce an output that has a duty ratio of the switch responsive to the external control signal and the internal current sense signal.

8. The integrated circuit of claim 7 wherein the switch is coupled to an output of the pulse width modulator.

9. A method of controlling an output of a power supply, comprising:

- receiving an external current with a switch;

- controlling a switching of the switch in response to an external control signal;

- adjusting the switching of the switch in response to a switch coupled to receive an external current; and

- a controller coupled to the switch to control a switching of the external current by the switch in response to an external control signal and an internal current sense signal, which is proportional to a current in the switch, wherein the output of the power supply is regulated in the absence of the internal current sense signal.

ABSTRACT OF THE DISCLOSURE

**[0031]** An apparatus and method of providing a pulse width modulated signal that is responsive to a current are disclosed. An integrated circuit according to aspects of the present invention regulates an output of a power supply and includes a switch coupled to receive an external current. The integrated circuit also includes a controller coupled to the switch to control a switching of the external current by the switch in response to an external control signal and an internal current sense signal. The internal current sense signal is proportional to a current in the switch. The output of the power supply is also regulated in the absence of the internal current sense signal.

FIG. 1

FIG. 3

FIG. 2

FIG. 4

FIG. 5

FIG. 6