(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-318381

(P2006-318381A)

(43) 公開日 平成18年11月24日(2006.11.24)

| (51) Int.CI.                | F 1                     | テーマコード (参考)       |

|-----------------------------|-------------------------|-------------------|

| <b>G05F 3/24 (2006.01)</b>  | G05F 3/24               | B 2 H093          |

| <b>G09G 3/36 (2006.01)</b>  | G09G 3/36               | 5 C006            |

| <b>G02F 1/133 (2006.01)</b> | G02F 1/133              | 5 C080            |

| <b>G09G 3/20 (2006.01)</b>  | G02F 1/133<br>G09G 3/20 | 5 H420<br>6 1 1 A |

審査請求 有 請求項の数 19 O L (全 45 頁) 最終頁に続く

|           |                              |                                                        |

|-----------|------------------------------|--------------------------------------------------------|

| (21) 出願番号 | 特願2005-142780 (P2005-142780) | (71) 出願人 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (22) 出願日  | 平成17年5月16日 (2005.5.16)       | (74) 代理人 100090479<br>弁理士 井上 一                         |

|           |                              | (74) 代理人 100124626<br>弁理士 榎並 智和                        |

|           |                              | (74) 代理人 100124682<br>弁理士 黒田 泰                         |

|           |                              | (74) 代理人 100090387<br>弁理士 布施 行夫                        |

|           |                              | (74) 代理人 100090398<br>弁理士 大渕 美千栄                       |

|           |                              | (74) 代理人 100101649<br>弁理士 伊奈 達也                        |

最終頁に続く

## (54) 【発明の名称】電圧発生回路

## (57) 【要約】 (修正有)

【課題】パネルの表示特性に最適な階調電圧を供給し、且つ、消費電力を低減可能な電圧発生回路を提供する。

【解決手段】電圧発生回路は、第1の電源電圧VDDと第2の電源電圧VSSとから第1～第M(Mは2以上の整数)の分割電圧を生成する電圧分割回路80と、第1～第Mの分割電圧のインピーダンス変換を行うインピーダンス変換回路IP1～IP10とを含む。第1～第K(K < M)のインピーダンス変換回路及び第L(K < L < M)～第Mのインピーダンス変換回路は、その動作範囲が第1の電源電圧VDDと第2の電源電圧VSSとの間の範囲に設定された第1型の演算増幅器VOPRを含み、第K+1～第L-1のインピーダンス変換回路は、その動作範囲が第1の電源電圧VDDよりも低い第3の電圧V3と、第1の電源電圧VDDよりも低く第2の電源電圧VSSよりも高い第4の電圧V4との間の範囲に設定された第2型の演算増幅器VOPを含む。

【選択図】図3

**【特許請求の範囲】**

**【請求項 1】**

第1の電源電圧を供給する第1の電源と、前記第1の電源電圧よりも電源電圧の低い第2の電源電圧を供給する第2の電源とを用いて第1～第M (Mは2以上の整数)の分割電圧を生成して出力する電圧分割回路と、

前記第1～第Mの分割電圧のインピーダンス変換を行う第1～第Mのインピーダンス変換回路と、

を含み、

前記第1～第P (1 < P < M、Pは整数)のインピーダンス変換回路及び前記第Q (P < Q < M、Qは整数)～第Mのインピーダンス変換回路は、その動作範囲が前記第1の電源電圧と前記第2の電源電圧との間の範囲に設定されたRail-to-Rail型である第1型の演算增幅器を含み、

前記第P+1～第Q-1のインピーダンス変換回路は、その動作範囲が前記第1の電源電圧よりも低い第3の電圧と、前記第1の電源電圧よりも低く前記第2の電源電圧よりも高い第4の電圧との間の範囲に設定された第2型の演算增幅器を含むことを特徴とする電圧発生回路。

**【請求項 2】**

請求項1において、

第2～第Pのインピーダンス変換回路及び第Q～第M-1のインピーダンス変換回路は、前記第2型の演算增幅器をさらに含み、

前記第2～第Pのインピーダンス変換回路及び前記第Q～第M-1のインピーダンス変換回路の各々に設けられた前記第1型の演算增幅器及び前記第2型の演算增幅器は、排他的に選択され、インピーダンス変換電圧を出力することを特徴とする電圧発生回路。

**【請求項 3】**

請求項2において、

前記第2～第Pのインピーダンス変換回路及び前記第Q～第M-1のインピーダンス変換回路の各々に設けられた前記第1及び第2型の演算增幅器は、

前記第1型の演算增幅器及び前記第2型の演算增幅器の選択・非選択を設定する初期設定レジスタの設定値に基づいて、排他的に選択されてインピーダンス変換電圧を出力することを特徴とする電圧発生回路。

**【請求項 4】**

請求項3において、

前記第2～第Pのインピーダンス変換回路及び前記第Q～第M-1のインピーダンス変換回路の各々に設けられた前記第1及び第2型の演算增幅器のうち、選択された演算增幅器ではバイアス電流用トランジスタがオンに設定され、非選択された演算增幅器ではバイアス電流用トランジスタがオフに設定されることを特徴とする電圧発生回路。

**【請求項 5】**

請求項3又は4において、

前記第1型及び第2型の演算增幅器は、

一端に第1の電源電圧(VDD)が供給された第1の電流源(CS1)の他端に各トランジスタのソースが接続されると共に、入力信号(Vin)及び出力信号(Vout)が各トランジスタのゲートに入力される第1の導電型の第1の差動トランジスタ対(PT1、PT2)と、前記第1の差動トランジスタ対の各トランジスタのドレイン電流を生成する第1のカレントミラー回路(CM1)とを有する第1の導電型差動增幅回路(100)と、

一端に第2の電源電圧(VSS)が供給された第2の電流源(CS2)の他端に各トランジスタのソースが接続されると共に、前記入力信号及び前記出力信号が各トランジスタのゲートに入力される第2の導電型の第2の差動トランジスタ対(NT3、NT4)と、前記第2の差動トランジスタ対の各トランジスタのドレイン電流を生成する第2のカレントミラー回路(CM2)とを有する第2の導電型差動增幅回路(110)と、

10

20

30

40

50

前記第1の差動トランジスタ対を構成する2つのトランジスタのドレインである第1の出力ノード(ND1)の電圧に基づいてそのゲート電圧が制御される第2の導電型の第1の駆動トランジスタ(NTO1)と、そのドレインが前記第1の駆動トランジスタのドレインに接続され前記第2の差動トランジスタ対を構成する2つのトランジスタのドレインである第2の出力ノード(ND2)の電圧に基づいてそのゲート電圧が制御される第1の導電型の第2の駆動トランジスタ(PTO1)とを有し、前記第1の駆動トランジスタ(NTO1)のドレインの電圧を前記出力信号(Vout)として出力する出力回路(120)とを含むことを特徴とする電圧発生回路。

#### 【請求項6】

請求項5において、

10

前記第1型及び第2型の演算増幅器は、

前記入力信号(Vin)がゲートに入力されるトランジスタ(NT3)のゲートと、前記出力信号(Vout)がゲートに入力されるトランジスタ(NT4)のゲートとを電気的に接続する第1のスイッチをさらに含み、

前記第1及び第2型の演算増幅器のうち、

非選択に設定された演算増幅器の前記第1のスイッチはオンに設定され、

選択された演算増幅器の前記第1のスイッチはオフに設定されることを特徴とする電圧発生回路。

#### 【請求項7】

請求項5又は6において、

20

前記第1型及び第2型の演算増幅器は、

前記第1の出力ノード(ND1)と前記第2の電源とを電気的に接続する第2のスイッチと、

前記第2の出力ノード(ND2)と前記第1の電源とを電気的に接続する第3のスイッチと、

をさらに含み、

前記第1及び第2型の演算増幅器のうち、

非選択に設定された演算増幅器の前記第2及び第3のスイッチはオンに設定され、

選択された演算増幅器の前記第2及び第3のスイッチはオフに設定されることを特徴とする電圧発生回路。

30

#### 【請求項8】

請求項5乃至7のいずれかにおいて、

40

前記第1及び第2型の演算増幅器は、

前記出力信号(Vout)がゲートに入力されるトランジスタ(NT4)のゲートと出力信号(Vout)が出力される出力部とを電気的に接続する第4のスイッチをさらに含み、

前記第1及び第2型の演算増幅器のうち、

非選択に設定された演算増幅器の前記第4のスイッチはオフに設定され、

選択された演算増幅器の前記第4のスイッチはオンに設定されることを特徴とする電圧発生回路。

40

#### 【請求項9】

請求項5乃至8のいずれかにおいて、

50

前記第1及び第2型の演算増幅器は、

前記第2の駆動トランジスタ(PTO1)と前記第1の駆動トランジスタ(NTO1)との間の中間ノードと、前記第2の駆動トランジスタ(PTO1)のドレインとを電気的に接続する第5のスイッチと、

前記第1の駆動トランジスタ(NTO1)のドレインと、前記中間ノードとを電気的に接続する第6のスイッチと、

をさらに含み、

前記第1及び第2型の演算増幅器のうち、

非選択に設定された演算増幅器の前記第5及び第6のスイッチはオフに設定され、選択された演算増幅器の前記第5及び第6のスイッチはオンに設定されることを特徴とする電圧発生回路。

#### 【請求項10】

請求項5乃至9のいずれかにおいて、

前記第1及び第2型の演算増幅器は、

前記第2の駆動トランジスタ(PTO1)と前記第1の駆動トランジスタ(NTO1)との間の中間ノードと、出力信号(Vout)が出力される出力部とを電気的に接続する出力イネーブルスイッチをさらに含み、

前記第1及び第2型の演算増幅器のうち、

10

非選択に設定された演算増幅器の前記出力イネーブルスイッチはオフに設定され、選択された演算増幅器の前記出力イネーブルスイッチはオンに設定されることを特徴とする電圧発生回路。

#### 【請求項11】

請求項5乃至10のいずれかにおいて、

前記第1型の演算増幅器は、

前記入力信号(Vin)及び前記出力信号(Vout)に基づいて、前記第1の差動トランジスタ対を構成する2つのトランジスタのドレインである前記第1の出力ノード(ND1)及び第1の反転出力ノード(NXD1)のうち少なくとも一方を駆動する第1の補助回路(130)と、

20

前記入力信号(Vin)及び前記出力信号(Vout)に基づいて、前記第2の差動トランジスタ対を構成する2つのトランジスタのドレインである第2の出力ノード(ND2)及び第2の反転出力ノード(NXD2)のうち少なくとも一方を駆動する第2の補助回路(140)と、

をさらに含むことを特徴とする電圧発生回路。

#### 【請求項12】

請求項11において、

前記第1の補助回路(130)は、

前記第1の差動トランジスタ対(PT1、PT2)を構成するトランジスタのうち前記入力信号(Vin)がゲートに入力されるトランジスタ(PT1)のゲート・ソース間の電圧の絶対値が該トランジスタの閾値電圧の絶対値より小さいとき、

30

前記第1の出力ノード(ND1)及び前記第1の反転出力ノード(NXD1)の少なくとも一方を駆動することで、前記第1の駆動トランジスタ(NTO1)のゲート電圧を制御し、

前記第2の補助回路(140)は、

前記第2の差動トランジスタ対(NT3、NT4)を構成するトランジスタのうち前記入力信号(Vin)がゲートに入力されるトランジスタ(NT3)のゲート・ソース間電圧の絶対値が該トランジスタの閾値電圧の絶対値より小さいとき、

前記第2の出力ノード(ND2)及び前記第2の反転出力ノード(NXD2)の少なくとも一方を駆動することで、前記第2の駆動トランジスタ(PTO1)のゲート電圧を制御することを特徴とする電圧発生回路。

40

#### 【請求項13】

請求項11又は12において、

前記第1の補助回路が、

各トランジスタのソースに前記第1の電源電圧(VDD)が供給され、各トランジスタのドレインがそれぞれ前記第1の出力ノード(ND1)及び前記第1の反転出力ノード(NXD1)に接続された第1の導電型の第1及び第2の電流駆動トランジスタ(PA1、PA2)と、

前記入力信号(Vin)及び前記出力信号(Vout)に基づいて前記第1及び第2の電流駆動トランジスタ(PA1、PA2)のゲート電圧を制御する第1の電流制御回路(

50

132)とを含み、

前記第1の差動トランジスタ対(PT1、PT2)を構成するトランジスタのうち前記入力信号(Vin)がゲートに入力されるトランジスタ(PT1)のゲート・ソース間の電圧の絶対値が該トランジスタの閾値電圧の絶対値より小さいとき、

前記第1の電流制御回路(132)が、

前記第1の出力ノード(ND1)及び前記第1の反転出力ノード(NXD1)の少なくとも一方を駆動するように前記第1及び第2の電流駆動トランジスタ(PA1、PA2)のゲート電圧を制御することを特徴とする電圧発生回路。

#### 【請求項14】

請求項13において、

10

前記第1の電流制御回路(132)が、

一端に前記第2の電源電圧(VSS)が供給された第3の電流源(CS3)と、

前記第3の電流源(CS3)の他端に各トランジスタのソースが接続され、前記入力信号(Vin)及び前記出力信号(Vout)が各トランジスタのゲートに入力される第2の導電型の第3の差動トランジスタ対(NS5、NS6)と、

各トランジスタのソースに前記第1の電源電圧(VDD)が供給され、各トランジスタのドレインがそれぞれ前記第3の差動トランジスタ対(NS5、NS6)の各トランジスタのドレインに接続され、各トランジスタのゲート及びドレインが接続された第1の導電型の第5及び第6の電流駆動トランジスタ(PS5、PS6)とを含み、

前記第3の差動トランジスタ対を構成するトランジスタのうちそのゲートに前記入力信号(Vin)が入力されるトランジスタ(NS5)のドレインが前記第2の電流駆動トランジスタ(PA2)のゲートに接続され、

20

前記第3の差動トランジスタ対を構成するトランジスタのうちそのゲートに前記出力信号(Vout)が入力されるトランジスタ(NS6)のドレインが前記第1の電流駆動トランジスタ(PA1)のゲートに接続されることを特徴とする演算増幅器。

#### 【請求項15】

請求項13又は14において、

30

前記第1型の演算増幅器は、

前記第1の電流駆動トランジスタ(PA1)のゲートと、前記第1の電源とを電気的に接続する第1の補助スイッチと、

前記第2の電流駆動トランジスタ(PA2)のゲートと、前記第1の電源とを電気的に接続する第2の補助スイッチと、

をさらに含み、

前記第1型の演算増幅器が非選択に設定された場合には、前記第1及び第2の補助スイッチはオンに設定され、

前記第1型の演算増幅器が選択された場合には、前記第1及び第2の補助スイッチはオフに設定されることを特徴とする電圧発生回路。

#### 【請求項16】

請求項11乃至15のいずれかにおいて、

40

前記第2の補助回路(140)は、

各トランジスタのソースに前記第2の電源電圧(VSS)が供給され、各トランジスタのドレインがそれぞれ前記第2の出力ノード(ND2)及び前記第2の反転出力ノード(NXD2)に接続された第2の導電型の第3及び第4の電流駆動トランジスタ(NA3、NA4)と、

前記入力信号(Vin)及び前記出力信号(Vout)に基づいて前記第3及び第4の電流駆動トランジスタ(NA3、NA4)のゲート電圧を制御する第2の電流制御回路(142)とを含み、

前記第2の電流制御回路(142)は、

前記第2の差動トランジスタ対(NT3、NT4)を構成するトランジスタのうち前記入力信号(Vin)がゲートに入力されるトランジスタ(NT3)のゲート・ソース間の

50

電圧の絶対値が該トランジスタの閾値電圧の絶対値より小さいとき、

前記第2の出力ノード(ND2)及び前記第2の反転出力ノード(NXD2)の少なくとも一方を駆動するように前記第3及び第4の電流駆動トランジスタ(NA3、NA4)のゲート電圧を制御することを特徴とする電圧発生回路。

#### 【請求項17】

請求項16において、

前記第2の電流制御回路(142)は、

一端に前記第1の電源電圧(VDD)が供給された第4の電流源(CS4)と、

前記第4の電流源(CS4)の他端に各トランジスタのソースが接続され、前記入力信号(Vin)及び前記出力信号(Vout)が各トランジスタのゲートに入力される第1の導電型の第4の差動トランジスタ対(PS7、PS8)と、10

各トランジスタのソースに前記第2の電源電圧(VSS)が供給され、各トランジスタのドレインがそれぞれ前記第4の差動トランジスタ対(PS7、PS8)の各トランジスタのドレインに接続され、各トランジスタのゲート及びドレインが接続された第2の導電型の第7及び第8の電流駆動トランジスタ(NS7、NS8)とを含み、

前記第4の差動トランジスタ対を構成するトランジスタのうちそのゲートに前記入力信号(Vin)が入力されるトランジスタ(PS7)のドレインが前記第4の電流駆動トランジスタ(NA4)のゲートに接続され、15

前記第4の差動トランジスタ対を構成するトランジスタのうちそのゲートに前記出力信号(Vout)が入力されるトランジスタ(PS8)のドレインが前記第3の電流駆動トランジスタ(NA3)のゲートに接続されることを特徴とする演算増幅器。20

#### 【請求項18】

請求項16又は17において、

前記第1型の演算増幅器は、

前記第3の電流駆動トランジスタ(NA3)のゲートと、前記第2の電源とを電気的に接続する第3の補助スイッチと、25

前記第4の電流駆動トランジスタ(NA4)のゲートと、前記第2の電源とを電気的に接続する第4の補助スイッチと、30

をさらに含み、

前記第1型の演算増幅器が非選択に設定された場合には、前記第3及び第4の補助スイッチはオンに設定され、35

前記第1型の演算増幅器が選択された場合には、前記第3及び第4の補助スイッチはオフに設定されることを特徴とする電圧発生回路。

#### 【請求項19】

請求項1乃至4のいずれかにおいて、

前記第1型の演算増幅器は、

入力信号(Vin)及び出力信号(Vout)の差分を増幅する第1の導電型差動増幅回路(100)と、40

前記入力信号(Vin)及び前記出力信号(Vout)の差分を増幅する第2の導電型差動増幅回路(110)と、

前記入力信号(Vin)及び前記出力信号(Vout)に基づいて、前記第1の導電型差動増幅回路の第1の出力ノード(ND1)及び第1の反転出力ノード(NXD1)のうち少なくとも一方を駆動する第1の補助回路(130)と、45

前記入力信号(Vin)及び前記出力信号(Vout)に基づいて、前記第2の導電型差動増幅回路の第2の出力ノード(ND2)及び第2の反転出力ノード(NXD2)のうち少なくとも一方を駆動する第2の補助回路(140)と、

前記第1及び第2の出力ノード(ND1、ND2)の電圧に基づいて前記出力信号(Vout)を生成する出力回路(120)とを含むことを特徴とする電圧発生回路。

#### 【発明の詳細な説明】

#### 【技術分野】

**【0001】**

本発明は、電圧発生回路に関する。

**【背景技術】****【0002】**

従来より、携帯電話機などの電子機器に用いられる液晶パネル（電気光学装置）として、単純マトリクス方式の液晶パネルと、薄膜トランジスタ（Thin Film Transistor：以下、TFTと略す）などのスイッチング素子を用いたアクティブマトリクス方式の液晶パネルとが知られている。

**【0003】**

単純マトリクス方式は、アクティブマトリクス方式に比べて低消費電力化が容易であるという利点がある反面、多色化や動画表示が難しいという不利点がある。一方、アクティブマトリクス方式は、多色化や動画表示に適しているという利点がある反面、低消費電力化が難しいという不利点がある。

**【0004】**

そして、近年、携帯電話機などの携帯型電子機器では、高品質な画像の提供のために、多色化、動画表示への要望が強まっている。このため、これまで用いられてきた単純マトリクス方式の液晶パネルに代えて、アクティブマトリクス方式の液晶パネルが用いられるようになってきた。

**【0005】**

アクティブマトリクス方式の液晶パネルでは、液晶パネルのデータ線を駆動するデータ線駆動回路の中に、出力バッファとして機能する演算増幅器（オペアンプ）を設けることが望ましい。しかしながら、近年の表示パネルの高画質化、高解像度、高階調化に伴い、データ線駆動回路の消費電力の増大が課題となる。

**【特許文献1】特開2003-022063号公報****【発明の開示】****【発明が解決しようとする課題】****【0006】**

本発明は、以上のような技術的課題に鑑みてなされたものであり、その目的とするところは、さまざまな表示パネルの表示特性に対して柔軟に対応でき、且つ、消費電力の低い電圧発生回路を提供することにある。

**【課題を解決するための手段】****【0007】**

本発明は、第1の電源電圧を供給する第1の電源と、前記第1の電源電圧よりも電源電圧の低い第2の電源電圧を供給する第2の電源とを用いて第1～第M（Mは2以上の整数）の分割電圧を生成して出力する電圧分割回路と、前記第1～第Mの分割電圧のインピーダンス変換を行う第1～第Mのインピーダンス変換回路と、を含み、前記第1～第P（ $1 < P < M$ 、Pは整数）のインピーダンス変換回路及び前記第Q（ $P < Q < M$ 、Qは整数）～第Mのインピーダンス変換回路は、その動作範囲が前記第1の電源電圧と前記第2の電源電圧との間の範囲に設定されたRail-to-Rail型である第1型の演算増幅器を含み、前記第P+1～第Q-1のインピーダンス変換回路は、その動作範囲が前記第1の電源電圧よりも低い第3の電圧と、前記第1の電源電圧よりも低く前記第2の電源電圧よりも高い第4の電圧との間の範囲に設定された第2型の演算増幅器を含む電圧発生回路に関する。

**【0008】**

これにより、例えば表示パネルに本実施形態を適用する場合、パネルの表示特性に適した階調電圧を、全て第1型の演算増幅器で構成された場合よりも低消費電力で供給することができる。

**【0009】**

また、本発明では、第2～第Pのインピーダンス変換回路及び第Q～第M-1のインピーダンス変換回路は、前記第2型の演算増幅器をさらに含み、前記第2～第Pのインピ-

10

20

30

40

50

ダンス変換回路及び前記第Q～第M-1のインピーダンス変換回路の各々に設けられた前記第1型の演算増幅器及び前記第2型の演算増幅器は、排他的に選択され、インピーダンス変換電圧を出力するようにしてもよい。

#### 【0010】

本発明によれば、第2～第Pのインピーダンス変換回路及び第Q～第M-1のインピーダンス変換回路は、動作範囲の異なる第1型、第2型の演算増幅器を排他的に選択することができる。これにより、例えば表示パネルに本実施形態を適用する場合、様々なパネルに対して、最適な階調電圧をより低い消費電力で供給することができる。

#### 【0011】

また、本発明では、前記第2～第Pのインピーダンス変換回路及び前記第Q～第M-1のインピーダンス変換回路の各々に設けられた前記第1及び第2型の演算増幅器は、前記第1型の演算増幅器及び前記第2型の演算増幅器の選択・非選択を設定する初期設定レジスタの設定値に基づいて、排他のに選択されてインピーダンス変換電圧を出力するようにしてもよい。

#### 【0012】

これにより、第1型の演算増幅器及び前記第2型の演算増幅器の選択・非選択の情報を自由に設定して保存することができる。例えば表示パネルに本実施形態を適用する場合、ユーザーは、適用するパネルの表示特性に最適な設定情報を初期設定レジスタに格納することができるため、電圧発生回路を該パネルに特化した設定で常に使用できる。

#### 【0013】

また、本発明では、前記第2～第Pのインピーダンス変換回路及び前記第Q～第M-1のインピーダンス変換回路の各々に設けられた前記第1及び第2型の演算増幅器のうち、選択された演算増幅器ではバイアス電流用トランジスタがオンに設定され、非選択された演算増幅器ではバイアス電流用トランジスタがオフに設定されるようにしてもよい。

#### 【0014】

これにより、非選択に設定されている演算増幅器よって消費される無駄な電流を抑制できる。

#### 【0015】

また、本発明では、前記第1型及び第2型の演算増幅器は、一端に第1の電源電圧(VDD)が供給された第1の電流源(CS1)の他端に各トランジスタのソースが接続されると共に、入力信号(Vin)及び出力信号(Vout)が各トランジスタのゲートに入力される第1の導電型の第1の差動トランジスタ対(PT1、PT2)と、前記第1の差動トランジスタ対の各トランジスタのドレイン電流を生成する第1のカレントミラー回路(CM1)とを有する第1の導電型差動増幅回路(100)と、一端に第2の電源電圧(VSS)が供給された第2の電流源(CS2)の他端に各トランジスタのソースが接続されると共に、前記入力信号及び前記出力信号が各トランジスタのゲートに入力される第2の導電型の第2の差動トランジスタ対(NT3、NT4)と、前記第2の差動トランジスタ対の各トランジスタのドレイン電流を生成する第2のカレントミラー回路(CM2)とを有する第2の導電型差動増幅回路(110)と、前記第1の差動トランジスタ対を構成する2つのトランジスタのドレインである第1の出力ノード(ND1)の電圧に基づいてそのゲート電圧が制御される第2の導電型の第1の駆動トランジスタ(NT01)と、そのドレインが前記第1の駆動トランジスタのドレインに接続され前記第2の差動トランジスタ対を構成する2つのトランジスタのドレインである第2の出力ノード(ND2)の電圧に基づいてそのゲート電圧が制御される第1の導電型の第2の駆動トランジスタ(PT01)とを有し、前記第1の駆動トランジスタ(NT01)のドレインの電圧を前記出力信号(Vout)として出力する出力回路(120)とを含むようにしてもよい。

#### 【0016】

本発明では、演算増幅器が、第1の導電型差動増幅回路と第2の導電型差動増幅回路とを含み、入力信号及び出力信号が、それぞれ異なる導電型の差動トランジスタ対に入力される。各差動トランジスタ対を構成するトランジスタが電流源に接続されると共に、各ト

10

20

30

40

50

ランジスタのドレイン電流がカレントミラー回路によって生成されることで、出力回路は、各差動増幅回路の出力ノードの電圧に基づいて出力信号を出力することができる。

【0017】

また、本発明では、前記第1型及び第2型の演算増幅器は、前記入力信号( $V_{in}$ )がゲートに入力されるトランジスタ(NT3)のゲートと、前記出力信号( $V_{out}$ )がゲートに入力されるトランジスタ(NT4)のゲートとを電気的に接続する第1のスイッチをさらに含み、前記第1及び第2型の演算増幅器のうち、非選択に設定された演算増幅器の前記第1のスイッチはオンに設定され、選択された演算増幅器の前記第1のスイッチはオフに設定されるようにしてもよい。

【0018】

これにより、インピーダンス変換回路の出力電圧値が、非選択に設定されている演算増幅器の出力に影響されないようにすることができる。

【0019】

また、本発明では、前記第1型及び第2型の演算増幅器は、前記第1の出力ノード(ND1)と前記第2の電源とを電気的に接続する第2のスイッチと、前記第2の出力ノード(ND2)と前記第1の電源とを電気的に接続する第3のスイッチと、をさらに含み、前記第1及び第2型の演算増幅器のうち、非選択に設定された演算増幅器の前記第2及び第3のスイッチはオンに設定され、選択された演算増幅器の前記第2及び第3のスイッチはオフに設定されるようにしてもよい。

【0020】

これにより、インピーダンス変換回路の出力電圧値が、非選択に設定されている演算増幅器の出力に影響されないようにすることができる。

【0021】

また、本発明では、前記第1及び第2型の演算増幅器は、前記出力信号( $V_{out}$ )がゲートに入力されるトランジスタ(NT4)のゲートと出力信号( $V_{out}$ )が出力される出力部とを電気的に接続する第4のスイッチをさらに含み、前記第1及び第2型の演算増幅器のうち、非選択に設定された演算増幅器の前記第4のスイッチはオフに設定され、選択された演算増幅器の前記第4のスイッチはオンに設定されるようにしてもよい。

【0022】

これにより、インピーダンス変換回路の出力電圧値が、非選択に設定されている演算増幅器の出力に影響されないようにすることができる。

【0023】

また、本発明では、前記第1及び第2型の演算増幅器は、前記第2の駆動トランジスタ(PTO1)と前記第1の駆動トランジスタ(NT01)との間の中間ノードと、前記第2の駆動トランジスタ(PTO1)のドレインとを電気的に接続する第5のスイッチと、前記第1の駆動トランジスタ(NT01)のドレインと、前記中間ノードとを電気的に接続する第6のスイッチと、をさらに含み、前記第1及び第2型の演算増幅器のうち、非選択に設定された演算増幅器の前記第5及び第6のスイッチはオフに設定され、選択された演算増幅器の前記第5及び第6のスイッチはオンに設定されるようにしてもよい。

【0024】

これにより、インピーダンス変換回路の出力電圧値が、非選択に設定されている演算増幅器の出力に影響されないようにすることができる。

【0025】

また、本発明では、前記第1及び第2型の演算増幅器は、前記第2の駆動トランジスタ(PTO1)と前記第1の駆動トランジスタ(NT01)との間の中間ノードと、出力信号( $V_{out}$ )が出力される出力部とを電気的に接続する出力イネーブルスイッチをさらに含み、前記第1及び第2型の演算増幅器のうち、非選択に設定された演算増幅器の前記出力イネーブルスイッチはオフに設定され、選択された演算増幅器の前記出力イネーブルスイッチはオンに設定されるようにしてもよい。

【0026】

10

20

30

40

50

これにより、インピーダンス変換回路の出力電圧値が、非選択に設定されている演算増幅器の出力に影響されないようにすることができる。

#### 【0027】

また、本発明では、前記第1型の演算増幅器は、前記入力信号( $V_{in}$ )及び前記出力信号( $V_{out}$ )に基づいて、前記第1の差動トランジスタ対を構成する2つのトランジスタのドレインである前記第1の出力ノード(ND1)及び第1の反転出力ノード(NXD1)のうち少なくとも一方を駆動する第1の補助回路(130)と、前記入力信号( $V_{in}$ )及び前記出力信号( $V_{out}$ )に基づいて、前記第2の差動トランジスタ対を構成する2つのトランジスタのドレインである第2の出力ノード(ND2)及び第2の反転出力ノード(NXD2)のうち少なくとも一方を駆動する第2の補助回路(140)と、をさらに含むようにしてもよい。10

#### 【0028】

これにより、出力回路を構成する第1及び第2の駆動トランジスタのゲート電圧が制御できる。

#### 【0029】

また、本発明では、前記第1の補助回路(130)は、前記第1の差動トランジスタ対(PT1、PT2)を構成するトランジスタのうち前記入力信号( $V_{in}$ )がゲートに入力されるトランジスタ(PT1)のゲート・ソース間の電圧の絶対値が該トランジスタの閾値電圧の絶対値より小さいとき、前記第1の出力ノード(ND1)及び前記第1の反転出力ノード(NXD1)の少なくとも一方を駆動することで、前記第1の駆動トランジスタ(NT01)のゲート電圧を制御し、前記第2の補助回路(140)は、前記第2の差動トランジスタ対(NT3、NT4)を構成するトランジスタのうち前記入力信号( $V_{in}$ )がゲートに入力されるトランジスタ(NT3)のゲート・ソース間電圧の絶対値が該トランジスタの閾値電圧の絶対値より小さいとき、前記第2の出力ノード(ND2)及び前記第2の反転出力ノード(NXD2)の少なくとも一方を駆動することで、前記第2の駆動トランジスタ(PT01)のゲート電圧を制御するようにしてもよい。20

#### 【0030】

これにより、第1の差動トランジスタ対が動作し、かつ第2の差動トランジスタ対が動作しない範囲の入力信号が入力された場合には、第1の導電型差動増幅回路が入力信号及び出力信号の差動増幅を行って出力回路を構成する第1の駆動トランジスタのゲート電圧を制御することができる。一方、第2の導電型差動増幅回路の各ノードが不定となるため、第2の補助回路が、第2の導電型差動増幅回路の第2の出力ノード及び第2の反転出力ノードの少なくとも一方を駆動することで、第2の駆動トランジスタのゲート電圧を制御することができる。30

#### 【0031】

また、第2の差動トランジスタ対が動作せず、かつ第1の差動トランジスタ対が動作する範囲の入力信号が入力された場合には、第2の導電型差動増幅回路が入力信号及び出力信号の差動増幅を行って出力回路を構成する第2の駆動トランジスタのゲート電圧を制御することができる。一方、第1の導電型差動増幅回路の各ノードが不定となるため、第1の補助回路が、第1の導電型差動増幅回路の第1の出力ノード及び第1の反転出力ノードの少なくとも一方を駆動することで、第1の駆動トランジスタのゲート電圧を制御することができる。40

#### 【0032】

こうすることで、出力回路を構成する第1及び第2の駆動トランジスタのゲート電圧が制御できるようになり、入力信号が入力不感帯の範囲であることに起因する不要な貫通電流の発生を無くすことができる。そのため、高電位側の電源電圧と低電位側の電源電圧との間の電圧を振幅として、演算増幅器を形成できるようになるので、駆動能力を低下させることなく動作電圧を狭くでき、更に消費電力を削減できるようになる。これは、昇圧回路の実装や製造プロセスの低耐圧化を意味し、低コスト化を実現する。

#### 【0033】

10

20

30

40

50

また、本発明では、前記第1の補助回路が、各トランジスタのソースに前記第1の電源電圧( $V_{DD}$ )が供給され、各トランジスタのドレインがそれぞれ前記第1の出力ノード( $N_{D1}$ )及び前記第1の反転出力ノード( $N_{XD1}$ )に接続された第1の導電型の第1及び第2の電流駆動トランジスタ( $P_A1$ 、 $P_A2$ )と、前記入力信号( $V_{in}$ )及び前記出力信号( $V_{out}$ )に基づいて前記第1及び第2の電流駆動トランジスタ( $P_A1$ 、 $P_A2$ )のゲート電圧を制御する第1の電流制御回路(132)とを含み、前記第1の差動トランジスタ対( $P_T1$ 、 $P_T2$ )を構成するトランジスタのうち前記入力信号( $V_{in}$ )がゲートに入力されるトランジスタ( $P_T1$ )のゲート・ソース間の電圧の絶対値が該トランジスタの閾値電圧の絶対値より小さいとき、前記第1の電流制御回路(132)が、前記第1の出力ノード( $N_{D1}$ )及び前記第1の反転出力ノード( $N_{XD1}$ )の少なくとも一方を駆動するように前記第1及び第2の電流駆動トランジスタ( $P_A1$ 、 $P_A2$ )のゲート電圧を制御するようにしてもよい。10

#### 【0034】

本発明によれば、第1及び第2の電流駆動トランジスタのゲート電圧を制御することで、簡素な構成で、第1の出力ノード又は第1の反転出力ノードを駆動できるようになる。その結果、簡素な構成で、第1の駆動トランジスタのゲート電圧を制御できるようになる。。20

#### 【0035】

なお第1又は第2の電流駆動トランジスタのドレインと第1の出力ノード又は第1の反転出力ノードとの間に、他の素子(例えばスイッチング素子等)を設けてもよい。20

#### 【0036】

また、本発明では、前記第1の電流制御回路(132)が、一端に前記第2の電源電圧( $V_{SS}$ )が供給された第3の電流源( $C_S3$ )と、前記第3の電流源( $C_S3$ )の他端に各トランジスタのソースが接続され、前記入力信号( $V_{in}$ )及び前記出力信号( $V_{out}$ )が各トランジスタのゲートに入力される第2の導電型の第3の差動トランジスタ対( $N_S5$ 、 $N_S6$ )と、各トランジスタのソースに前記第1の電源電圧( $V_{DD}$ )が供給され、各トランジスタのドレインがそれぞれ前記第3の差動トランジスタ対( $N_S5$ 、 $N_S6$ )の各トランジスタのドレインに接続され、各トランジスタのゲート及びドレインが接続された第1の導電型の第5及び第6の電流駆動トランジスタ( $P_S5$ 、 $P_S6$ )とを含み、前記第3の差動トランジスタ対を構成するトランジスタのうちそのゲートに前記入力信号( $V_{in}$ )が入力されるトランジスタ( $N_S5$ )のドレインが前記第2の電流駆動トランジスタ( $P_A2$ )のゲートに接続され、前記第3の差動トランジスタ対を構成するトランジスタのうちそのゲートに前記出力信号( $V_{out}$ )が入力されるトランジスタ( $N_S6$ )のドレインが前記第1の電流駆動トランジスタ( $P_A1$ )のゲートに接続されるようにしてもよい。30

#### 【0037】

本発明によれば、第1の差動トランジスタ対が動作しない範囲の入力信号が入力された場合に、第1の電流制御回路で制御される第1及び第2の電流駆動トランジスタにより、簡素な構成で、第1の出力ノード及び第1の反転出力ノードを補助的に駆動できるようになる。40

#### 【0038】

なお、第3の差動トランジスタ対を構成する各トランジスタのソースと第3の電流源との間、第3の差動トランジスタ対を構成する各トランジスタのドレインと第5又は第6の電流駆動トランジスタのドレインとの間、又は第3の差動トランジスタ対を構成するトランジスタのうちそのゲートに入力信号が入力されるトランジスタのドレインと第2の電流駆動トランジスタのゲートとの間、又は第3の差動トランジスタ対を構成するトランジスタのうちそのゲートに出力信号が入力されるトランジスタのドレインと第1の電流駆動トランジスタのゲートとの間に、他の素子(例えばスイッチング素子等)を設けてもよい。

#### 【0039】

また、本発明では、前記第1型の演算増幅器は、前記第1の電流駆動トランジスタ( $P$ 50

A 1 ) のゲートと、前記第 1 の電源とを電気的に接続する第 1 の補助スイッチと、前記第 2 の電流駆動トランジスタ ( P A 2 ) のゲートと、前記第 1 の電源とを電気的に接続する第 2 の補助スイッチと、をさらに含み、前記第 1 型の演算増幅器が非選択に設定された場合には、前記第 1 及び第 2 の補助スイッチはオンに設定され、前記第 1 型の演算増幅器が選択された場合には、前記第 1 及び第 2 の補助スイッチはオフに設定されるようにしてよい。

#### 【 0 0 4 0 】

これにより、インピーダンス変換回路の出力電圧値が、非選択に設定されている演算増幅器の出力に影響されないようにすることができる。

#### 【 0 0 4 1 】

また、本発明では、前記第 2 の補助回路 ( 1 4 0 ) は、各トランジスタのソースに前記第 2 の電源電圧 ( V S S ) が供給され、各トランジスタのドレインがそれぞれ前記第 2 の出力ノード ( N D 2 ) 及び前記第 2 の反転出力ノード ( N X D 2 ) に接続された第 2 の導電型の第 3 及び第 4 の電流駆動トランジスタ ( N A 3 、 N A 4 ) と、前記入力信号 ( V i n ) 及び前記出力信号 ( V o u t ) に基づいて前記第 3 及び第 4 の電流駆動トランジスタ ( N A 3 、 N A 4 ) のゲート電圧を制御する第 2 の電流制御回路 ( 1 4 2 ) とを含み、前記第 2 の電流制御回路 ( 1 4 2 ) は、前記第 2 の差動トランジスタ対 ( N T 3 、 N T 4 ) を構成するトランジスタのうち前記入力信号 ( V i n ) がゲートに入力されるトランジスタ ( N T 3 ) のゲート・ソース間の電圧の絶対値が該トランジスタの閾値電圧の絶対値より小さいとき、前記第 2 の出力ノード ( N D 2 ) 及び前記第 2 の反転出力ノード ( N X D 2 ) の少なくとも一方を駆動するように前記第 3 及び第 4 の電流駆動トランジスタ ( N A 3 、 N A 4 ) のゲート電圧を制御するようにしてよい。

10

#### 【 0 0 4 2 】

本発明によれば、第 3 及び第 4 の電流駆動トランジスタのゲート電圧を制御することで、簡素な構成で、第 2 の出力ノード又は第 2 の反転出力ノードを駆動できるようになる。その結果、簡素な構成で、第 2 の駆動トランジスタのゲート電圧を制御できるようになる。

20

#### 【 0 0 4 3 】

なお第 3 又は第 4 の電流駆動トランジスタのドレインと第 2 の出力ノード又は第 2 の反転出力ノードとの間に、他の素子 ( 例えばスイッチング素子等 ) を設けてよい。

30

#### 【 0 0 4 4 】

また、本発明では、前記第 2 の電流制御回路 ( 1 4 2 ) は、一端に前記第 1 の電源電圧 ( V D D ) が供給された第 4 の電流源 ( C S 4 ) と、前記第 4 の電流源 ( C S 4 ) の他端に各トランジスタのソースが接続され、前記入力信号 ( V i n ) 及び前記出力信号 ( V o u t ) が各トランジスタのゲートに入力される第 1 の導電型の第 4 の差動トランジスタ対 ( P S 7 、 P S 8 ) と、各トランジスタのソースに前記第 2 の電源電圧 ( V S S ) が供給され、各トランジスタのドレインがそれぞれ前記第 4 の差動トランジスタ対 ( P S 7 、 P S 8 ) の各トランジスタのドレインに接続され、各トランジスタのゲート及びドレインが接続された第 2 の導電型の第 7 及び第 8 の電流駆動トランジスタ ( N S 7 、 N S 8 ) とを含み、前記第 4 の差動トランジスタ対を構成するトランジスタのうちそのゲートに前記入力信号 ( V i n ) が入力されるトランジスタ ( P S 7 ) のドレインが前記第 4 の電流駆動トランジスタ ( N A 4 ) のゲートに接続され、前記第 4 の差動トランジスタ対を構成するトランジスタのうちそのゲートに前記出力信号 ( V o u t ) が入力されるトランジスタ ( P S 8 ) のドレインが前記第 3 の電流駆動トランジスタ ( N A 3 ) のゲートに接続されるようにしてよい。

40

#### 【 0 0 4 5 】

本発明によれば、第 2 の差動トランジスタ対が動作しない範囲の入力信号が入力された場合に、第 2 の電流制御回路で制御される第 3 及び第 4 の電流駆動トランジスタにより、簡素な構成で、第 2 の出力ノード及び第 2 の反転出力ノードを補助的に駆動できるようになる。

50

## 【0046】

なお、第4の差動トランジスタ対を構成する各トランジスタのソースと第4の電流源との間、第4の差動トランジスタ対を構成する各トランジスタのドレインと第7又は第8の電流駆動トランジスタのドレインとの間、又は第4の差動トランジスタ対を構成するトランジスタのうちそのゲートに入力信号が入力されるトランジスタのドレインと第7の電流駆動トランジスタのゲートとの間、又は第4の差動トランジスタ対を構成するトランジスタのうちそのゲートに出力信号が入力されるトランジスタのドレインと第8の電流駆動トランジスタのゲートとの間に、他の素子（例えばスイッチング素子等）を設けてもよい。

## 【0047】

また、本発明では、前記第1型の演算増幅器は、前記第3の電流駆動トランジスタ（N A3）のゲートと、前記第2の電源とを電気的に接続する第3の補助スイッチと、前記第4の電流駆動トランジスタ（N A4）のゲートと、前記第2の電源とを電気的に接続する第4の補助スイッチと、をさらに含み、前記第1型の演算増幅器が非選択に設定された場合には、前記第3及び第4の補助スイッチはオンに設定され、前記第1型の演算増幅器が選択された場合には、前記第3及び第4の補助スイッチはオフに設定されるようにしてよい。

## 【0048】

これにより、インピーダンス変換回路の出力電圧値が、非選択に設定されている演算増幅器の出力に影響されないようにすることができる。

## 【0049】

また、本発明では、前記第1型の演算増幅器は、入力信号（V<sub>in</sub>）及び出力信号（V<sub>out</sub>）の差分を増幅する第1の導電型差動増幅回路（100）と、前記入力信号（V<sub>in</sub>）及び前記出力信号（V<sub>out</sub>）の差分を増幅する第2の導電型差動増幅回路（110）と、前記入力信号（V<sub>in</sub>）及び前記出力信号（V<sub>out</sub>）に基づいて、前記第1の導電型差動増幅回路の第1の出力ノード（ND1）及び第1の反転出力ノード（NxD1）のうち少なくとも一方を駆動する第1の補助回路（130）と、前記入力信号（V<sub>in</sub>）及び前記出力信号（V<sub>out</sub>）に基づいて、前記第2の導電型差動増幅回路の第2の出力ノード（ND2）及び第2の反転出力ノード（NxD2）のうち少なくとも一方を駆動する第2の補助回路（140）と、前記第1及び第2の出力ノード（ND1、ND2）の電圧に基づいて前記出力信号（V<sub>out</sub>）を生成する出力回路（120）とを含むようにしてよい。

## 【0050】

これにより、第1型の演算増幅器は、第1の電源電圧から第2の電源電圧の間で動作可能である。

## 【発明を実施するための最良の形態】

## 【0051】

以下、本発明の一実施形態について、図面を参照して説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない。また以下で説明される構成のすべてが本発明の必須構成要件であるとは限らない。なお、以下の図において同符号のものは同様の意味を表す。

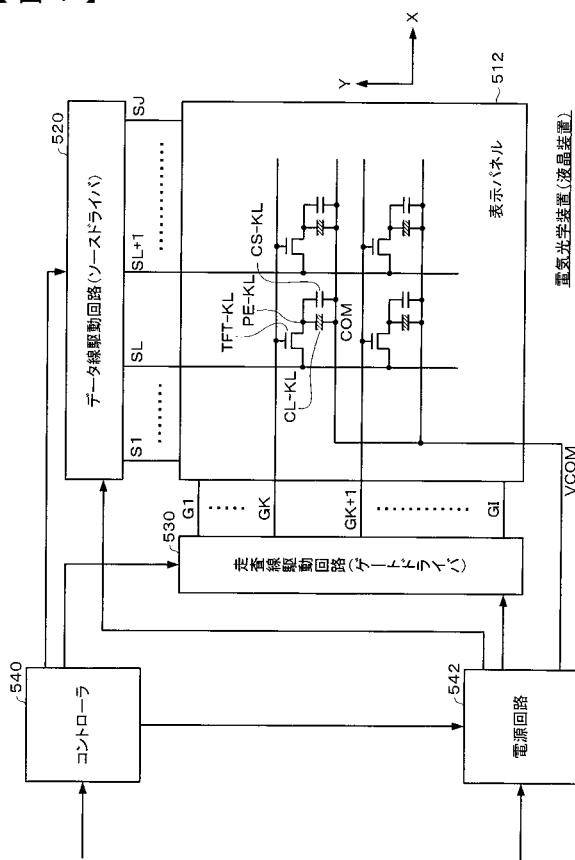

## 【0052】

## 1. 電気光学装置

図1に、本実施形態の電気光学装置（狭義には液晶装置）の構成例を示す。この電気光学装置は、携帯電話、携帯型情報機器（PDA等）、デジタルカメラ、プロジェクタ、携帯型オーディオプレーヤ、マスストレージデバイス、ビデオカメラ、電子手帳、或いはGPS(Global Positioning System)などの種々の電子機器に組み込むことができる。

## 【0053】

図1の電気光学装置は、表示パネル512（狭義にはLCD（Liquid Crystal Display）パネル）、データ線駆動回路520（狭義にはソースドライバ）、走査線駆動回路530（狭義にはゲートドライバ）、コントローラ540、電源回路542を含む。なお、電

10

20

30

40

50

気光学装置にこれらの全ての回路ブロックを含める必要はなく、その一部の回路ブロックを省略する構成にしてもよい。

#### 【0054】

ここで表示パネル512(電気光学パネル)は、複数の走査線(狭義にはゲート線)と、複数のデータ線(狭義にはソース線と)と、走査線及びデータ線により特定される画素を含む。この場合、データ線に薄膜トランジスタTFT(Thin Film Transistor、広義には画素用スイッチング素子)を接続し、このTFTに画素電極を接続することで、アクティピマトリクス型の電気光学装置を構成できる。

#### 【0055】

より具体的には、表示パネル512はアクティピマトリクス基板(例えばガラス基板)により構成される。このアクティピマトリクス基板には、図1のY方向に複数配列されそれぞれX方向に伸びる走査線G1～GI(Iは2以上の自然数)と、X方向に複数配列されそれぞれY方向に伸びるデータ線S1～SJ(Jは2以上の自然数)とが配置されている。また、走査線GK(1～K、Kは自然数)とデータ線SL(1～L、Lは自然数)との交差点に対応する位置に画素が設けられ、各画素は、薄膜トランジスタTFT-KL(広義には画素用スイッチング素子)、画素電極PE-KLを含む。

#### 【0056】

TFT-KLのゲート電極は走査線GKに接続され、TFT-KLのソース電極はデータ線SLに接続され、TFT-KLのドレイン電極は画素電極PE-KLに接続されている。この画素電極PE-KLと、画素電極PE-KLと液晶素子(広義には電気光学物質)を挟んで対向する対向電極COM(コモン電極)との間には、液晶容量CL-KL(電気光学物質の容量)及び補助容量CS-KLが形成されている。そして、TFT-KL、画素電極PE-KL等が形成されるアクティピマトリクス基板と、対向電極COMが形成される対向基板との間に液晶が封入され、画素電極PE-KLと対向電極COMの間の印加電圧に応じて液晶素子の透過率が変化するようになっている。

#### 【0057】

なお、対向電極COMに与えられる電圧VCOM(第1、第2のコモン電圧)は、電源回路542により生成される。また、対向電極COMを対向基板上にベタに形成せずに、各走査線に対応するように帯状に形成してもよい。

#### 【0058】

データ線駆動回路520は、画像データに基づいて表示パネル512のデータ線S1～SJを駆動する。一方、走査線駆動回路530は、表示パネル512の走査線G1～GIを順次走査駆動する。

#### 【0059】

コントローラ540は、図示しない中央処理装置(Central Processing Unit:以下、CPUと略す)等のホストにより設定された内容に従って、データ線駆動回路520、走査線駆動回路530及び電源回路542を制御する。

#### 【0060】

より具体的には、コントローラ540は、データ線駆動回路520及び走査線駆動回路530に対しては、例えば動作モードの設定や内部で生成した垂直同期信号や水平同期信号の供給を行い、電源回路542に対しては、対向電極COMの電圧VCOMの極性反転タイミングの制御を行う。

#### 【0061】

電源回路542は、外部から供給される基準電圧に基づいて、表示パネル512の駆動に必要な各種の電圧や、対向電極COMの電圧VCOMを生成する。

#### 【0062】

なお、図1では、電気光学装置がコントローラ540を含む構成になっているが、コントローラ540を電気光学装置の外部に設けてもよい。或いは、コントローラ540と共にホストを電気光学装置に含めるようにしてもよい。

#### 【0063】

10

20

30

40

50

また、走査線駆動回路 530、コントローラ 540、電源回路 542 の少なくとも 1つをデータ線駆動回路 520 に内蔵させてもよい。また、データ線駆動回路 520、走査線駆動回路 530、コントローラ 540、電源回路 542 の一部又は全部を表示パネル 512 上に形成してもよい。

#### 【0064】

なお、液晶素子には、直流電圧を長時間印加すると劣化するという性質がある。このため、液晶素子に印加する電圧の極性を所定期間毎に反転させる駆動方式が必要になる。このような駆動方式としては、フレーム反転駆動、走査(ゲート)ライン反転駆動、データ(ソース)ライン反転駆動、ドット反転駆動などがある。

#### 【0065】

ここで、走査ライン反転駆動では、液晶素子に印加される電圧が走査期間毎(1又は複数の走査線毎)に極性反転される。例えば、第Nの走査期間(第Nの走査線の選択期間)では正極性の電圧が液晶素子に印加され、第N+1の走査期間では負極性の電圧が印加され、第N+2の走査期間では正極性の電圧が印加される。一方、次のフレームにおいては、今度は、第Nの走査期間では負極性の電圧が液晶素子に印加され、第N+1の走査期間では正極性の電圧が印加され、第N+2の走査期間では負極性の電圧が印加されるようになる。

#### 【0066】

そして、この走査ライン反転駆動では、対向電極 COM の電圧 VCOM(以下、コモン電圧と呼ぶ)が走査期間毎に極性反転される。コモン電圧 VCOM を極性反転することで、表示パネルの駆動に必要な電圧を低くすることができる。これにより、駆動回路の耐圧を低くでき、駆動回路の製造プロセスの簡素化、低コスト化を図れる。

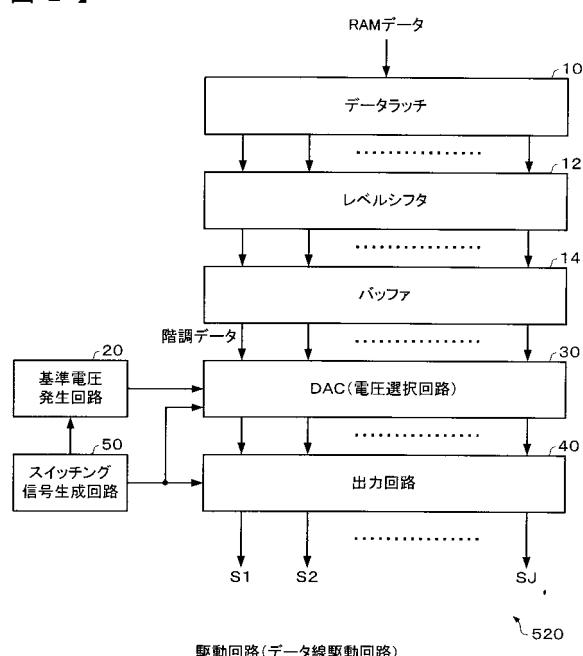

#### 【0067】

##### 2. データ線駆動回路

図2はデータ線駆動回路 520 の構成例を示すブロック図である。データ線駆動回路 520 は、データラッチ 10、レベルシフタ 12、バッファ 14、基準電圧発生回路(広義には電圧発生回路) 20、DAC(デジタル/アナログ変換回路、電圧選択回路) 30、出力回路 40 及びスイッチング信号生成回路 50 を含むが、これに限定されない。データ線駆動回路 520 に、これらの全ての回路ブロックを含める必要はなく、その一部の回路ブロックを省略する構成にしてもよい。

データ線駆動回路 520 は、例えば基準電圧発生回路 20 やスイッチング信号生成回路 50 等を省略するように構成されても良い。

#### 【0068】

データラッチ 10 は、表示メモリである RAM からのデータをラッチする。レベルシフタ 12 は、データラッチ 10 の出力の電圧レベルをシフトする。バッファ 14 は、レベルシフタ 12 からのデータをバッファリングして、デジタル階調データとして DAC 30 に出力する。

#### 【0069】

基準電圧発生回路 20 は、 $\gamma$  (ガンマ)補正用のラダー抵抗を含むように構成されてもよく、階調電圧を生成するための複数の基準電圧を発生する。

#### 【0070】

DAC 30 は、基準電圧発生回路 20 からの複数の基準電圧を用いて、バッファ 14 からのデジタル階調データ(R、G、B 用データ)をアナログ階調電圧に変換する。より具体的には、デジタル階調データをデコードし、デコード結果に基づいて、複数の基準電圧のいずれかを選択し、選択した基準電圧をアナログ階調電圧として出力回路 40 に出力する。この DAC 30 が有するデコーダは ROMなどを用いて実現できる。

#### 【0071】

なお、出力回路 40 は、演算増幅器を含まず、DAC 30 の出力端子とデータ線との間の接続のオン・オフを行うスイッチング素子などを含む。そして、出力回路 40 に演算増幅器を含ませない代わりに、基準電圧発生回路 20 に、ボルテージフォロワ接続の演算増

10

20

30

40

50

幅器（広義にはインピーダンス変換回路）を含ませている。

#### 【0072】

出力回路40は、D A C 30からのアナログ階調電圧をデータ線に伝達する回路である。この出力回路40には、D A C 30の出力端子とデータ線との間の接続のオン・オフ制御を行うスイッチング素子（コモン電圧の極性反転時にデータ線をハイインピーダンス状態に設定するためのスイッチング素子）を含ませることができる。

#### 【0073】

スイッチング信号生成回路50は、基準電圧発生回路20、D A C 30、出力回路40が有する種々のスイッチング素子をオン・オフ制御するためのスイッチング信号を生成する。

#### 【0074】

##### 3. 基準電圧発生回路

###### 3.1. 構成

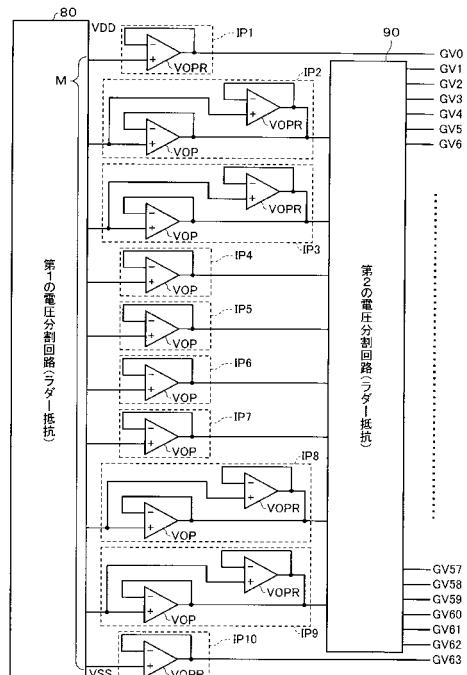

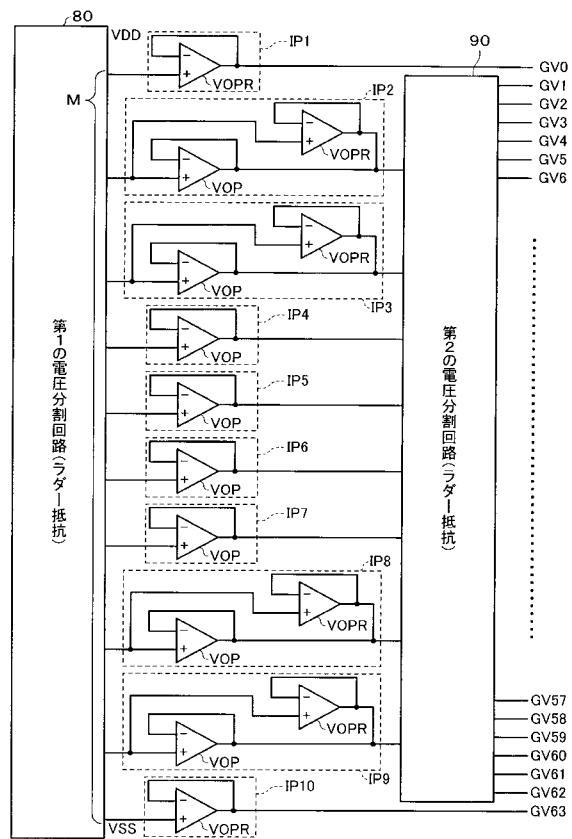

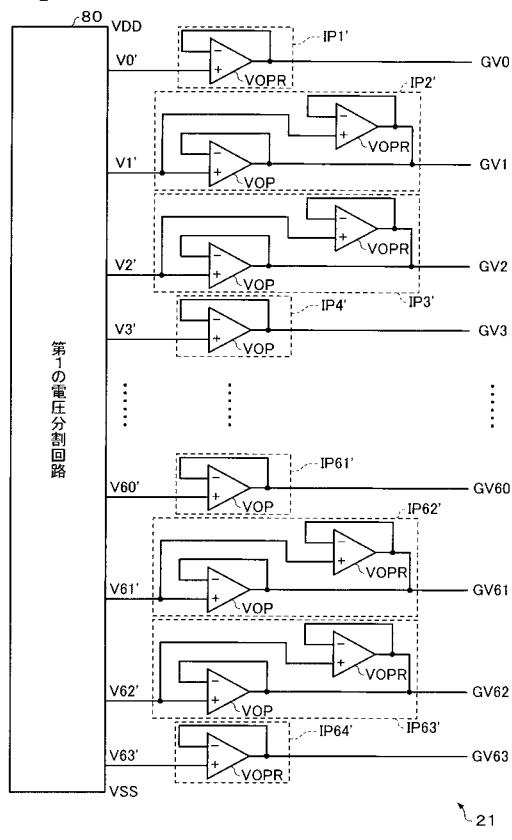

図3は、基準電圧発生回路20の構成例を示す図である。基準電圧発生回路20は、第1の電圧分割回路（広義には電圧分割回路）80と、第1の電圧分割回路80から供給される電圧のインピーダンス変換を行う複数のインピーダンス変換回路I P 1 ~ I P 10（広義には第1~第Mのインピーダンス変換回路、Mは2以上の整数）と、第2の電圧分割回路90を含む。

#### 【0075】

インピーダンス変換回路I P 1 ~ I P 3（広義には第1~第P（P < M）のインピーダンス変換回路）及びインピーダンス変換回路I P 8 ~ I P 10（広義には第Q（P < Q < M）~第Mのインピーダンス変換回路）は、その動作範囲が例えば電圧V D D（広義には第1の電源電圧）と電圧V S S（広義には第2の電源電圧）との間に設定されたR a i l - t o - R a i l型であるオペアンプV O P R（広義には第1型の演算増幅器）を含む。

#### 【0076】

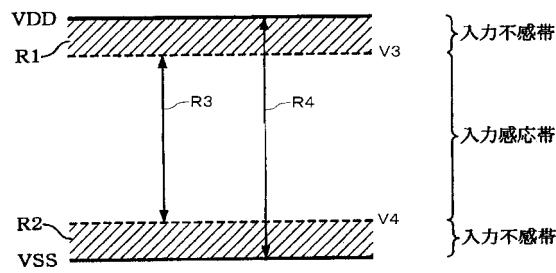

インピーダンス変換回路I P 4 ~ I P 7（広義には第P+1~第P-1のインピーダンス変換回路）は、その動作範囲が電圧V D Dよりも低い電圧V 3（広義には第3の電圧）と、電圧V 3よりも低く電圧V S Sよりも高い電圧V 4（広義には第4の電圧）との間に設定された通常型オペアンプV O P（広義には第2型の演算増幅器）を含む。なお

、図4に通常型オペアンプV O Pの動作範囲を示す。通常型オペアンプV O Pでは、図4のR 1、R 2に示すように入力電圧と出力電圧を等しくすることのできない入力不感帯を有する。これは、入力電圧が供給されるトランジスタの閾値に起因する。即ち、通常型オペアンプV O Pの動作範囲は、R 3に示すように電圧V 3から電圧V 4の間である。これに対して、R 4に示すように例えば電圧V D D ~ 電圧V S Sの間で動作可能なオペアンプがR a i l - t o - R a i l型のオペアンプV O P Rである。即ち、通常型オペアンプV O PとR a i l - t o - R a i l型オペアンプV O P Rとでは、その動作範囲が異なる。オペアンプV O P及びV O P Rの構成は後述する。

#### 【0077】

第1、第2の電圧分割回路80、90は、例えば複数の抵抗素子が直列接続されるラダー抵抗を含み、ラダー抵抗の各電圧分割端子に基準電圧を発生する。第1の電圧分割回路80は、例えばM種類（図3では例えば10種類）の電圧を出力する。

#### 【0078】

基準電圧発生回路20は、複数の電圧を発生し、例えば階調電圧G V 0 ~ G V 6 3の64種類の電圧を発生するが、これに限定されない。例えば上記のオペアンプV O P 1 ~ V O P 8の数を変更したり、第2の電圧分割回路90の抵抗分割数を変更することで、基準電圧発生回路20の発生する電圧の種類を増やしたり減らしたりすることができる。

#### 【0079】

第2の電圧分割回路90は、オペアンプV O P 1 ~ V O P 8、オペアンプV O P R 1 ~ V O P R 4等から供給された電圧をラダー抵抗で抵抗分割することで複数種類の電圧を発

生する。第2の電圧分割回路90が output する複数種類の電圧は例えば基準電圧発生回路20が output する階調電圧GV1～GV62に設定される。

#### 【0080】

なお、オペアンプVOPR5、VOPR6には、それぞれ電圧VDD(例えば電源電圧)、電圧VSS(例えば接地電圧)が供給され、オペアンプVOPR5の出力は例えば基準電圧発生回路20が output する階調電圧GV0に設定され、オペアンプVOPR6の出力は例えば階調電圧GV63に設定される。

#### 【0081】

基準電圧発生回路20は、上記の構成に限定されず、例えば第2の電圧分割回路90を省略するようにしてもよい。また、基準電圧発生回路20のオペアンプVOP及びVOPRの数は一例であって、上記の構成に限定されない。例えば、オペアンプVOPを8個ではなく、9個、10個、11個・・・としてもよいし、逆に7個、6個、・・・としてもよい。また、インピーダンス変換回路IP3、IP8のオペアンプVOPR2、VOPR3を省略するようにしても良いし、インピーダンス変換回路IP4～IP7のオペアンプVOPの後段にRaill-to-Raill型のオペアンプVOPRを設けるようにしても良い。

10

#### 【0082】

例えば、インピーダンス変換回路IP2、IP3、IP8、IP9は、通常型オペアンプVOP及びRaill-to-Raill型オペアンプVOPRを含む。各インピーダンス変換回路IP2、IP3、IP8、IP9では、この2つのオペアンプVOP、VOPRのオン・オフを例えばレジスタ(広義には初期設定レジスタ)等の設定情報に基づいて排他的に制御する。例えば、インピーダンス変換回路IP2において、オペアンプVOPがオンに設定された場合には、オペアンプVOPRがオフに設定される。なお、使用されないオペアンプVOP、VOPRはオフに設定されるため、無駄な電力消費を抑制できる。

20

#### 【0083】

このように、フレキシブルに各インピーダンス変換回路IP2、IP3、IP8、IP9の各オペアンプVOP、VOPRのオン・オフを制御することができる。これにより、基準電圧発生回路20は、さまざまなパネルの表示特性(例えば(ガンマ)特性)に対して、柔軟に対応することができる。また、ユーザーは初期設定レジスタを適宜に設定することで、適用したいパネルの表示特性に最適な設定を保存できる。これにより、基準電圧発生回路20は常にパネルに対して最適な階調電圧GV0～GV63を低消費電力で供給することができる。

30

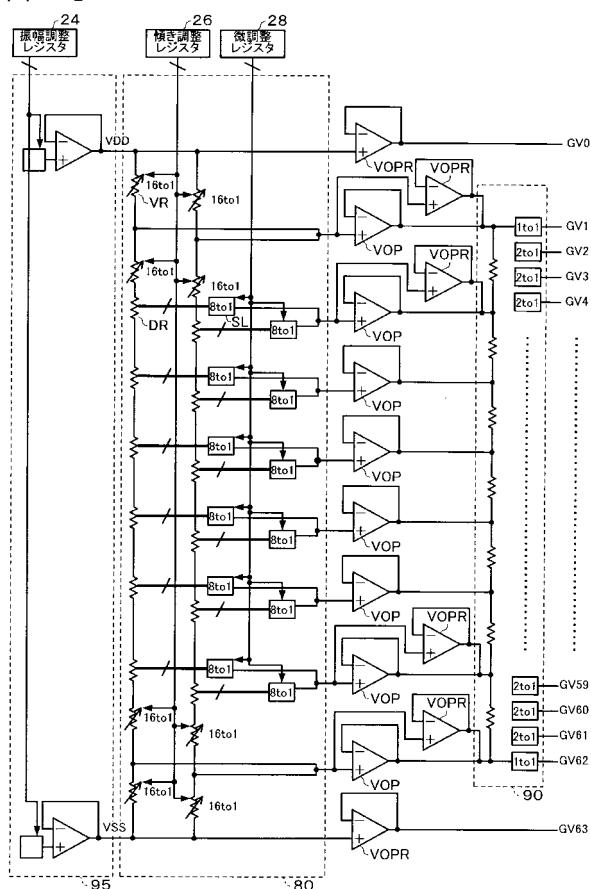

#### 【0084】

また、図5に示すように、第2の電圧分割回路90を省略し、各階調電圧GV0～GV63の出力にオペアンプを用いるような構成でも良い。図5の基準電圧発生回路21は、例えば64階調表示に対応するためにインピーダンス変換回路IP1'～IP64'を含む。各インピーダンス変換回路IP1'～IP64'の出力が階調電圧GV0～GV63に設定される。また、第1の電圧分割回路80は64種類の電圧V0'～V63'を出力する。

40

#### 【0085】

インピーダンス変換回路IP1'～IP3'、IP62'～IP64'にはRaill-to-Raill型オペアンプVOPRが設けられ、インピーダンス変換回路IP2'～IP63'には通常型オペアンプVOPが設けられている。この場合も同様に、インピーダンス変換回路IP2'、IP3'、IP62'、IP63'では、設定情報に基づいてRaill-to-Raill型オペアンプVOPR及び通常型オペアンプVOPのオン・オフを排他的に制御する。

#### 【0086】

図6は、図3の基準電圧発生回路20の第1、第2の電圧分割回路80、90の詳細を示す。電圧発生回路95は振幅調整レジスタ24の設定情報に基づいて、第1の電圧分割回路80に供給する電圧を生成する。ここでは、第1の電圧分割回路80には例えば電圧

50

V D D 及び電圧 V S S が供給されることとする。

#### 【0087】

第1の電圧分割回路 80 は、複数の可変抵抗 V R と、複数のラダー抵抗 D R を含む。傾き調整レジスタ 26 によって、階調電圧 G V 0 ~ G V 63 の変化の傾きを調整することができる。傾き調整レジスタ 26 には、可変抵抗 V R の抵抗値を設定する情報が格納されている。各可変抵抗 V R は、傾き調整レジスタ 26 の設定情報に基づいて、その抵抗値が設定される。なお、図 6 に記載されている “16 t o 1” は、例えば 16 種類に抵抗値が可変である場合の、そのうちの 1 種類に選択することを意味する。

#### 【0088】

微調整レジスタ 28 は、階調電圧 G V 0 ~ G V 63 の電圧レベルの微調整を行うための設定情報が格納されている。セレクタ S L は、ラダー抵抗 D R から抵抗分割によって電圧分割された複数種類の電圧のうち、微調整レジスタの設定情報に基づいて、その複数種類の電圧から一つの電圧を選択する。図 6 に記載されている “8 t o 1” は、例えば 8 種類に電圧分割された電圧値のうちの 1 種類を選択することを意味する。

#### 【0089】

なお、各レジスタ 24、26、28 は、ユーザーが適宜に設定可能な情報が格納される。

#### 【0090】

また、第2の電圧分割回路 90 は、複数の抵抗が直列に接続されたラダー抵抗を含む。階調電圧 G V 1 ~ G V 62 は、第2の電圧分割回路 90 によって電圧分割された電圧に基づく。ここで、例えば階調電圧 G V 2 ~ G V 61 に対応して “2 t o 1” と記載されているのは、基準電圧 V C O M の正極時と負極時とで階調電圧 G V 2 ~ G V 61 の電圧値を変更するためである。例えば階調電圧 G V 2 として用意された 2 種類の電圧値のうち、基準電圧 V C O M が正極である場合には一方の電圧を選択し、基準電圧 V C O M が負極である場合には他方の電圧を選択する。

#### 【0091】

これは、一般的に、V C O M の正極期間と負極期間とでは縫 i ガンマ ) 補正特性 ( 階調特性 ) が非対称になるためである。つまり、このように縫 i ガンマ ) 補正特性が非対称になる場合にも、図 6 のようにラダー抵抗の抵抗分割を正極性用、負極性用とで変更することで、V C O M の正極期間、負極期間の各期間に最適な縫 i ガンマ ) 補正を行うことが可能になる。なお、第1の電圧分割回路 80 においても、基準電圧 V C O M の正極・負極に基づいて、微調整レジスタ 28 を設定することで、各インピーダンス変換回路 I P 3 ~ I P 8 に入力される電圧を変更可能である。

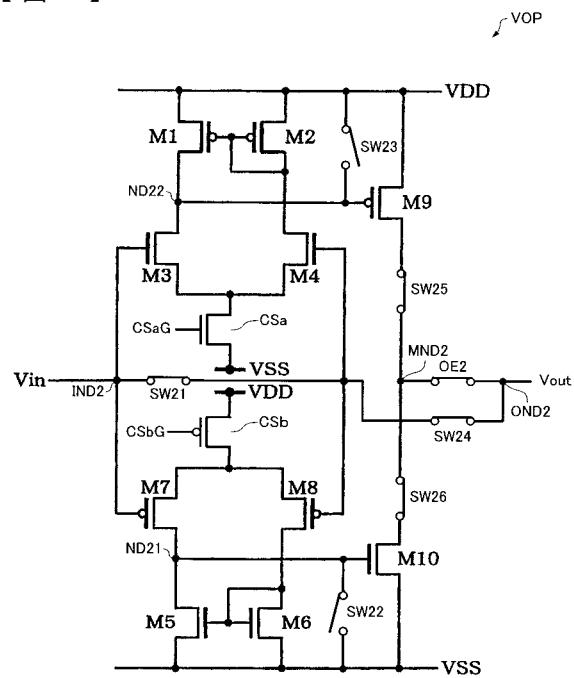

#### 【0092】

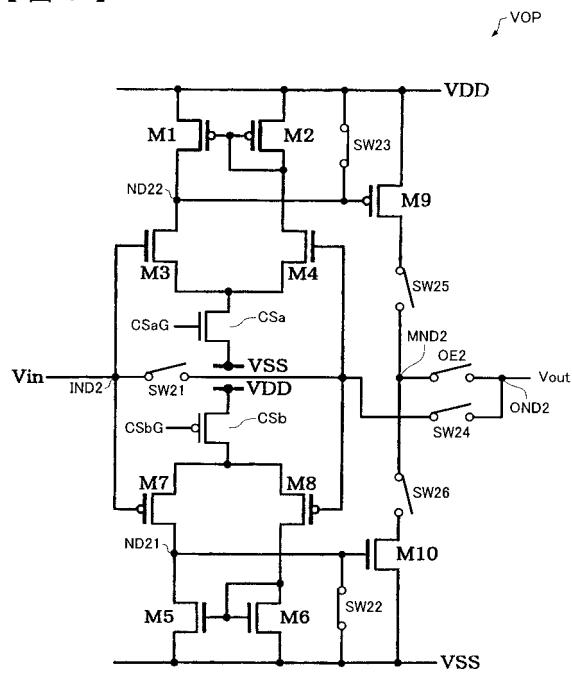

##### 3 . 2 . 通常型オペアンプ V O P

図 7 に通常型オペアンプ V O P の回路例を示す。図 7 のオペアンプ V O P は、p 型トランジスタ M 7、M 8、n 型トランジスタ M 5、M 6、及びトランジスタ C S b ( 広義にはバイアス電流用トランジスタ ) を含む p 型差動入力回路により n 型駆動トランジスタ M 1 0 を制御する。また p 型トランジスタ M 1、M 2、n 型トランジスタ M 3、M 4、及びトランジスタ C S a ( 広義にはバイアス電流用トランジスタ ) を含む n 型差動入力回路により p 型駆動トランジスタ M 9 を制御する。

#### 【0093】

n 型差動入力回路に着目して、入力信号 V i n の電圧が出力信号 V o u t の電圧より大きい場合を考える。この場合、n 型トランジスタ M 4 のインピーダンスが n 型トランジスタ M 3 より大きくなるため、p 型トランジスタ M 2、M 1 のゲート電圧が上昇し、p 型トランジスタ M 1 のインピーダンスが大きくなる。そのため、p 型駆動トランジスタ M 9 のゲート電圧が下降し、p 型駆動トランジスタ M 9 はオンする方向に向かう。

#### 【0094】

p 型差動入力回路に着目すると、入力信号 V i n の電圧が出力信号 V o u t の電圧より大きい場合、p 型トランジスタ M 8 のインピーダンスが p 型トランジスタ M 7 のインピー-

10

20

30

40

50

ダンスより小さくなるため、n型トランジスタM5、M6のゲート電圧が上昇し、n型トランジスタM5のインピーダンスが小さくなる。そのため、n型駆動トランジスタM10のゲート電圧が下降し、n型駆動トランジスタM10がオフする方向に向かう。

#### 【0095】

このように、入力信号Vinの電圧が出力信号Voutの電圧より大きい場合は、出力信号Voutの電圧が大きくなる方向にp型駆動トランジスタM9、n型駆動トランジスタM10が動作する。なお、入力信号Vinの電圧が出力信号Voutの電圧より小さい場合は、上述と逆の動作を行う。以上のような動作の結果、演算増幅器では、入力信号Vinの電圧と出力信号Voutの電圧とがほぼ等しくなる平衡状態に移行していく。

#### 【0096】

しかしながら、p型差動入力回路では入力信号Vinがゲート電圧としてp型トランジスタM7に供給され、n型差動入力回路では入力信号Vinがゲート電圧としてn型トランジスタM3に供給される。そのため、図4に示すように、入力信号Vinが、高電位側の電源電圧VDD～VDD-|Vthp|（Vthpは、p型トランジスタM7の閾値電圧）の範囲R1と、低電位側の電源電圧VSS～VSS+Vthn（Vthnは、n型トランジスタM3の閾値電圧）の範囲R2では、入力信号Vinの電圧と出力信号Voutの電圧とを等しくできない入力不感帯となる。これは、低電位側の電源電圧VSS～VSS+Vthnの範囲R2では、n型トランジスタM3がオフ状態のままであるためn型差動入力回路が動作せず、高電位側の電源電圧VDD～VDD-|Vthp|の範囲R1では、p型トランジスタM7がオフ状態のままであるためp型差動入力回路が動作しないからである。

#### 【0097】

なお、トランジスタCSa、CSbの各ゲートに入力されるゲート電圧CSaG、CSbGを調整することで、n型差動入力回路及びp型差動入力回路の電流源を調整することができる。

#### 【0098】

また、通常型オペアンプVOPは、スイッチSW21（広義には第1のスイッチ）、スイッチSW22（広義には第2のスイッチ）、スイッチSW23（広義には第3のスイッチ）、スイッチSW24（広義には第4のスイッチ）、スイッチSW25（広義には第5のスイッチ）、スイッチSW26（広義には第6のスイッチ）及び出力イネーブルスイッチOEE2（広義には出力イネーブルスイッチ）を含む。

#### 【0099】

スイッチSW21は、入力信号Vinが入力される入力ノードIND2と出力信号Voutが出力される出力ノードOND2（広義には出力部）との間に設けられている。スイッチSW22は、電圧VSSを発生する電源（広義には第2の電源）と出力ノードND21との間に設けられている。スイッチSW23は、電圧VDDを発生する電源（広義には第1の電源）と出力ノードND22との間に設けられている。スイッチSW24は、出力ノードOND2とトランジスタM4のゲートとの間に設けられている。スイッチSW25は、電圧VDDを発生する電源と中間ノードMND2との間に設けられている。スイッチSW26は、電圧VSSを発生する電源と中間ノードMND2との間に設けられている。出力イネーブルスイッチOEE2は中間ノードMND2と出力ノードOND2との間に設けられている。

#### 【0100】

例えば図3のインピーダンス変換回路IP2、IP3、IP8、IP9等のいずれかにおいて、通常型オペアンプVOPがオンに設定された場合には、スイッチSW21、スイッチSW24、スイッチSW25、スイッチSW26、出力イネーブルスイッチOEE2がオンに設定される。また、スイッチSW22、SW23はオフに設定される。即ち、図7に示すような状態になる。

#### 【0101】

一方、インピーダンス変換回路IP2等において、Rail-to-Rail型オペア

10

20

30

40

50

ンプV O P Rがオンに設定され、通常型オペアンプV O Pがオフに設定された場合には、スイッチSW21、スイッチSW24、スイッチSW25、スイッチSW26、出力イネーブルスイッチOE2がオフに設定される。また、スイッチSW22、SW23はオンに設定される。即ち、図8に示すような状態になる。これにより、トランジスタM9、M10は確実にオフにされ、出力ノードOND2はハイインピーダンス状態に設定される。さらに、トランジスタCSa、CSbのゲートに入力されるゲート電圧CSaG、CSbGを制御する（例えばトランジスタCSa、CSbをオフにする）ことで、n型差動入力回路及びp型差動入力回路の電流源の電流供給をオフにすることができる。これにより、通常型オペアンプV O Pがオフに設定されている場合に、通常型オペアンプV O Pによる無駄な電力消費を抑制できる。

10

## 【0102】

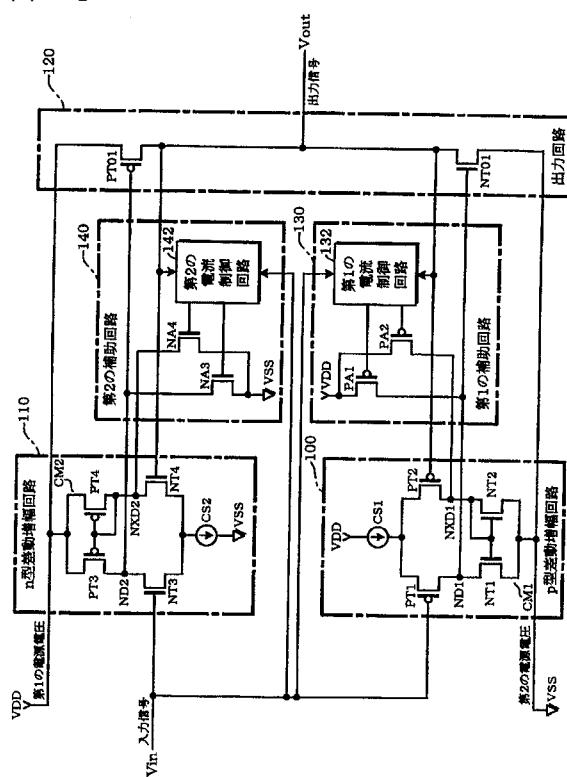

## 3.3.Rail-to-Rail型オペアンプV O P R

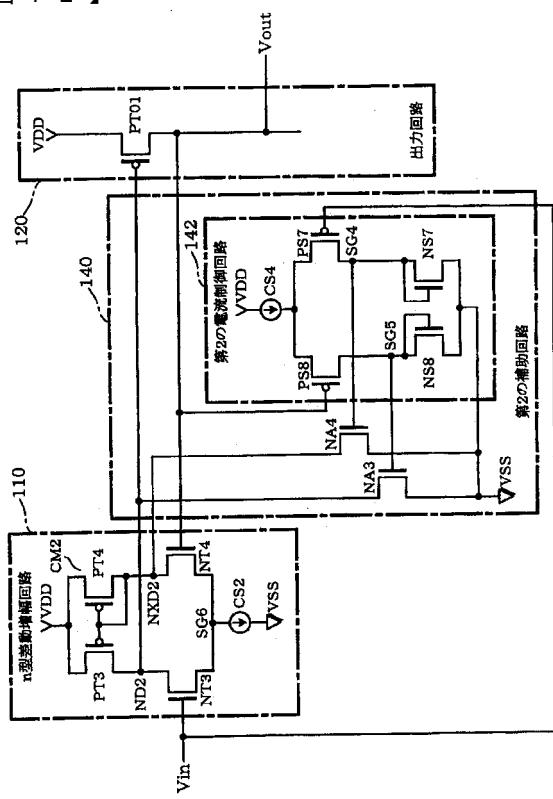

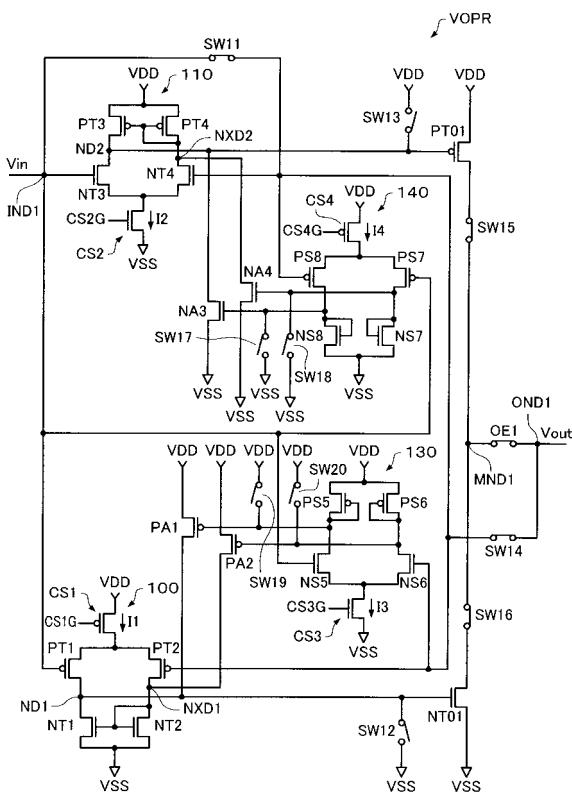

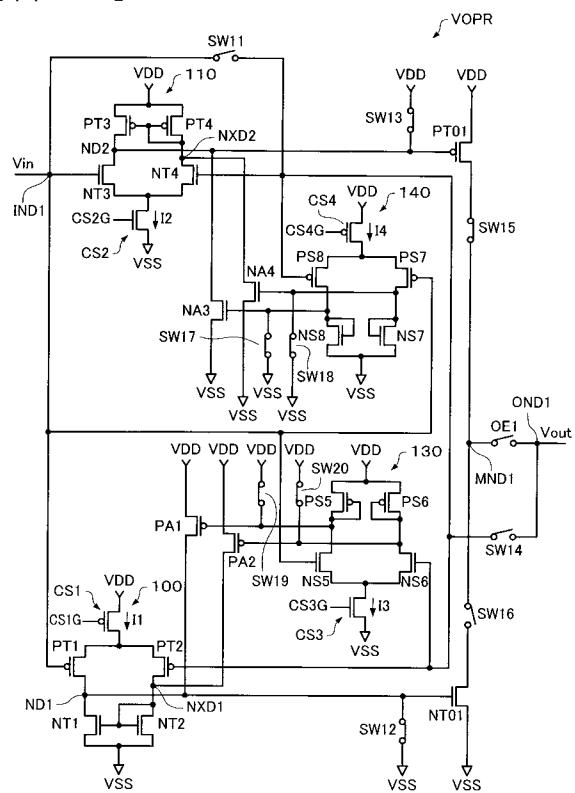

図9に本実施形態に係るRail-to-Rail型オペアンプV O P Rの構成例を示す。

## 【0103】

このオペアンプV O P Rは、p型（例えば第1の導電型）差動增幅回路100と、n型（例えば第2の導電型）差動增幅回路110と、出力回路120とを含む。p型差動增幅回路100、n型差動增幅回路110、及び出力回路120は、高電位側の電源電圧V D D（広義には第1の電源電圧）と低電位側の電源電圧V S S（広義には第2の電源電圧）との間の電圧を動作電圧とする。

20

## 【0104】

p型差動增幅回路100は、入力信号V i n及び出力信号V o u tの差分を増幅する。p型差動增幅回路100は、出力ノードND1（第1の出力ノード）及び反転出力ノードNXD1（第1の反転出力ノード）を有し、出力ノードND1及び反転出力ノードNXD1の間に入力信号V i n及び出力信号V o u tの差分に対応した電圧を出力する。

## 【0105】

このp型差動增幅回路100は、第1のカレントミラー回路CM1と、p型（第1の導電型）の第1の差動トランジスタ対を有する。第1の差動トランジスタ対は、p型金属酸化膜半導体（Metal Oxide Semiconductor：以下MOSと略す）トランジスタ（以下、MOSトランジスタを単にトランジスタと略す）PT1、PT2を含む。p型トランジスタPT1、PT2の各トランジスタのソースが第1の電流源CS1に接続されると共に、入力信号V i n及び出力信号V o u tが各トランジスタのゲートに入力される。p型トランジスタPT1、PT2のドレイン電流は、第1のカレントミラー回路CM1によって生成される。p型トランジスタPT1のゲートに入力信号V i nが入力される。p型トランジスタPT2のゲートに出力信号V o u tが入力される。p型トランジスタPT1のドレインが、出力ノードND1（第1の出力ノード）になる。p型トランジスタPT2のドレインが、反転出力ノードNXD1（第1の反転出力ノード）になる。

30

## 【0106】

n型差動增幅回路110は、入力信号V i n及び出力信号V o u tの差分を増幅する。n型差動增幅回路110は、出力ノードND2（第2の出力ノード）及び反転出力ノードNXD2（第2の反転出力ノード）を有し、出力ノードND2及び反転出力ノードNXD2の間に入力信号V i n及び出力信号V o u tの差分に対応した電圧を出力する。

40

## 【0107】

このn型差動增幅回路110は、第2のカレントミラー回路CM2と、n型（第2の導電型）の第2の差動トランジスタ対を含む。第2の差動トランジスタ対は、n型トランジスタNT3、NT4を含む。n型トランジスタNT3、NT4の各トランジスタのソースが第2の電流源CS2に接続されると共に、入力信号V i n及び出力信号V o u tが各トランジスタのゲートに入力される。n型トランジスタNT3、NT4のドレイン電流は、第2のカレントミラー回路CM2によって生成される。n型トランジスタNT3のゲートに入力信号V i nが入力される。n型トランジスタNT4のゲートに出力信号V o u tが

50

入力される。n型トランジスタNT3のドレインが、出力ノードND2（第2の出力ノード）になる。n型トランジスタNT4のドレインが、反転出力ノードNXD2（第2の反転出力ノード）になる。

#### 【0108】

出力回路120は、p型差動増幅回路100の出力ノードND1（第1の出力ノード）の電圧とn型差動増幅回路110の出力ノードND2（第2の出力ノード）の電圧とに基づいて、出力信号Voutを生成する。

#### 【0109】

この出力回路120は、n型（第2の導電型）の第1の駆動トランジスタNTO1とp型（第1の導電型）の第2の駆動トランジスタPTO1とを含む。第1の駆動トランジスタNTO1のゲート（電圧）は、p型差動増幅回路100の出力ノードND1（第1の出力ノード）の電圧に基づいて制御される。第2の駆動トランジスタPTO1のゲート（電圧）は、n型差動増幅回路110の出力ノード（ND2）（第2の出力ノード）の電圧に基づいて制御される。第2の駆動トランジスタPTO1のドレインは、第1の駆動トランジスタNTO1のドレインに接続される。そして出力回路120は、第1の駆動トランジスタNTO1のドレインの電圧（第2の駆動トランジスタPTO1のドレインの電圧）を、出力信号Voutとして出力する。10

#### 【0110】

更に本実施形態における演算増幅器は、第1及び第2の補助回路130、140を含むことで、入力不感帯をなくし、かつ貫通電流を抑える。この結果、動作電圧の範囲を不要に広げることなく、貫通電流を抑えて低消費電力化を実現する。20

#### 【0111】

ここで、第1の補助回路130は、入力信号Vin及び出力信号Voutに基づいて、p型差動増幅回路100の出力ノードND1（第1の出力ノード）及び反転出力ノードNXD1（第1の反転出力ノード）のうち少なくとも一方を駆動する。また第2の補助回路130は、入力信号Vin及び出力信号Voutに基づいて、n型差動増幅回路110の出力ノードND2（第2の出力ノード）及び第2の反転出力ノードNXD2（第2の反転出力ノード）のうち少なくとも一方を駆動する。30

#### 【0112】

そして、p型トランジスタPT1（第1の差動トランジスタ対を構成するトランジスタのうち入力信号Vinがゲートに入力されるトランジスタ）のゲート・ソース間（ゲートとソースとの間）の電圧の絶対値がp型トランジスタPT1の閾値電圧の絶対値より小さいとき、第1の補助回路130が、出力ノードND1（第1の出力ノード）及び反転出力ノードNXD1（第1の反転出力ノード）の少なくとも一方を駆動することで、第1の駆動トランジスタNTO1のゲート電圧を制御する。30

#### 【0113】

更に、n型トランジスタNT3（第2の差動トランジスタ対を構成するトランジスタのうち入力信号Vinがゲートに入力されるトランジスタ）のゲート・ソース間の電圧の絶対値がn型トランジスタNT3の閾値電圧の絶対値より小さいとき、第2の補助回路140が、出力ノードND2（第2の出力ノード）及び反転出力ノードNXD2（第2の反転出力ノード）の少なくとも一方を駆動することで、第2の駆動トランジスタPTO1のゲート電圧を制御する。40

#### 【0114】

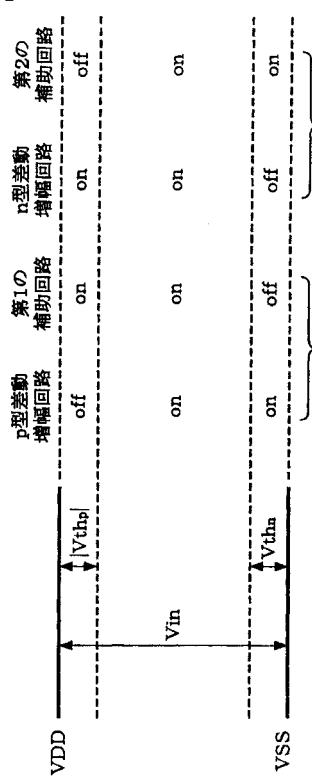

図10に、図5に示すオペアンプVOPRの動作説明図を示す。

#### 【0115】

ここで、高電位側の電源電圧をVDD、低電位側の電源電圧をVSS、入力信号の電圧をVin、p型トランジスタPT1の閾値電圧をVthp、n型トランジスタNT3の閾値電圧Vthnとする。

#### 【0116】

VDD - Vin > VDD - |Vthp| では、p型トランジスタがオフ、n型トランジ

10

スタがオンとなる。ここで p 型トランジスタがゲート電圧に応じてカットオフ領域、線形領域、又は飽和領域で動作する場合、p 型トランジスタがオフとは、カットオフ領域であることを意味する。同様に n 型トランジスタがゲート電圧に応じてカットオフ領域、線形領域、又は飽和領域で動作する場合、n 型トランジスタがオンとは、線形領域又は飽和領域であることを意味する。従って、 $V_{DD} - V_{in} > V_{DD} - |V_{thp}|$  では、p 型差動増幅回路 100 は動作せず（オフ）、n 型差動増幅回路 110 は動作する（オン）。そこで第 1 の補助回路 130 の動作をオン（出力ノード ND1（第 1 の出力ノード）及び反転出力ノード NXD1（第 1 の反転出力ノード）の少なくとも一方を駆動させ）し、第 2 の補助回路 140 の動作をオフ（出力ノード ND2（第 2 の出力ノード）及び反転出力ノード NXD1（第 2 の反転出力ノード）を駆動させない）する。このように、p 型差動増幅回路 100 が動作しない範囲で、第 1 の補助回路 130 により p 型差動増幅回路 100 の出力ノード ND1（反転出力ノード NXD1）を駆動することで、p 型差動増幅回路 100 の第 1 の差動トランジスタ対の入力不感帯の範囲の入力信号  $V_{in}$  に対しても、出力ノード ND1 の電圧を不定状態にすることがなくなる。

#### 【0117】

20

$V_{DD} - |V_{thp}| - V_{in} - V_{thn} + V_{SS}$  では、p 型トランジスタがオン、n 型トランジスタがオンとなる。ここで p 型トランジスタがゲート電圧に応じてカットオフ領域、線形領域、又は飽和領域で動作する場合、p 型トランジスタがオンとは、線形領域又は飽和領域であることを意味する。従って、p 型差動増幅回路 100 は動作し（オン）、n 型差動増幅回路 110 も動作する（オン）。この場合、第 1 の補助回路 130 の動作をオン又はオフし、第 2 の補助回路 140 の動作をオン又はオフする。即ち、p 型差動増幅回路 100 及び n 型差動増幅回路 110 が動作するため、出力ノード ND1、ND2 が不定状態にならず、図 13 に示す構成の差動増幅器と同様に、出力回路 120 により出力信号  $V_{out}$  を出力する。従って、第 1 及び第 2 補助回路 130、140 を動作させててもよいし、動作させなくてもよい。図 5 では、動作をオンさせている。

#### 【0118】

30

$V_{thn} + V_{SS} > V_{in} - V_{SS}$  では、p 型トランジスタがオン、n 型トランジスタがオフとなる。ここで n 型トランジスタがゲート電圧に応じてカットオフ領域、線形領域、又は飽和領域で動作する場合、n 型トランジスタがオフとは、カットオフ領域であることを意味する。従って、n 型差動増幅回路 110 は動作せず（オフ）、p 型差動増幅回路 100 は動作する（オン）。そこで第 2 の補助回路 140 の動作をオン（出力ノード ND2（第 2 の出力ノード）及び反転出力ノード NXD2（第 2 の反転出力ノード）の少なくとも一方を駆動させ）し、第 1 の補助回路 130 の動作をオフする。このように、n 型差動増幅回路 110 が動作しない範囲で、第 2 の補助回路 140 により n 型差動増幅回路 100 の出力ノード ND2（反転出力ノード NXD2）を駆動することで、n 型差動増幅回路 110 の第 2 の差動トランジスタ対の入力不感帯の範囲の入力信号  $V_{in}$  に対しても、出力ノード ND2 の電圧を不定状態にすることがなくなる。

#### 【0119】

40

以上のように第 1 及び第 2 の補助回路 130、140 により、出力回路 120 を構成する第 1 及び第 2 の駆動トランジスタ NTO1、PTO1 のゲート電圧が制御できるようになり、入力信号  $V_{in}$  が入力不感帯の範囲であることに起因する不要な貫通電流の発生を無くすことができる。しかも、入力信号  $V_{in}$  の入力不感帯を無くすることで、p 型トランジスタの閾値電圧  $V_{thp}$  及び n 型トランジスタの閾値電圧  $V_{thn}$  のばらつきを考慮して約 1.9 ボルトのオフセットを設ける必要がなくなる。そのため、高電位側の電源電圧  $V_{DD}$  と低電位側の電源電圧  $V_{SS}$  との間の電圧を振幅として、演算増幅器を形成できるようになるので、駆動能力を低下させることなく動作電圧を狭くでき、更に消費電力を削減できるようになる。これは、昇圧回路の実装や製造プロセスの低耐圧化を意味し、低コスト化を実現する。

#### 【0120】

50

以下では、本実施形態におけるオペアンプ VOPR の詳細な構成例について説明する。

## 【0121】

図9において、p型差動増幅回路100は、第1の電流源CS1と、上述の第1の差動トランジスタ対と、第1のカレントミラー回路CM1とを含む。第1の電流源CS1の一端に、高電位側の電源電圧VDD(第1の電源電圧)が供給される。第1の電流源CS1の他端に、上述の第1の差動トランジスタ対を構成するp型トランジスタPT1、PT2のソースが接続される。

## 【0122】

第1のカレントミラー回路CM1は、ゲート同士が互いに接続されたn型(第2の導電型)の第1のトランジスタ対を含む。この第1のトランジスタ対は、n型トランジスタNT1、NT2を含む。n型トランジスタNT1、NT2の各トランジスタのソースに低電位側の電源電圧VSS(第2の電源電圧)が供給される。n型トランジスタNT1のドレンが出力ノードND1(第1の出力ノード)に接続される。n型トランジスタNT2のドレンが反転出力ノードNXD1(第1の反転出力ノード)に接続される。n型トランジスタNT2(第1の差動トランジスタ対を構成するトランジスタのうち反転出力ノードNXD1に接続されるトランジスタ)のドレン及びゲートが接続される。

## 【0123】

またn型差動増幅回路110は、第2の電流源CS2と、上述の第2の差動トランジスタ対と、第2のカレントミラー回路CM2とを含む。第2の電流源CS2の一端に、低電位側の電源電圧VSS(第2の電源電圧)が供給される。第2の電流源CS2の他端に、上述の第2の差動トランジスタ対を構成するn型トランジスタNT3、NT4のソースが接続される。

## 【0124】

第2のカレントミラー回路CM2は、ゲート同士が互いに接続されたp型(第1の導電型)の第2のトランジスタ対を含む。この第2のトランジスタ対は、p型トランジスタPT3、PT4を含む。p型トランジスタPT3、PT4の各トランジスタのソースに高電位側の電源電圧VDD(第1の電源電圧)が供給される。p型トランジスタPT3のドレンが出力ノードND2(第2の出力ノード)に接続される。p型トランジスタPT4のドレンが反転出力ノードNXD2(第2の反転出力ノード)に接続される。p型トランジスタPT4(第2のトランジスタ対を構成するトランジスタのうち反転出力ノードNXD2に接続されるトランジスタ)のドレン及びゲートが接続される。

## 【0125】

また第1の補助回路130は、p型(第1の導電型)の第1及び第2の電流駆動トランジスタPA1、PA2と、第1の電流制御回路132とを含むことができる。第1及び第2の電流駆動トランジスタPA1、PA2の各トランジスタのソースに、高電位側の電源電圧VDD(第1の電源電圧)が供給される。第1の電流駆動トランジスタPA1のドレンは、出力ノードND1(第1の出力ノード)に接続される。第2の電流駆動トランジスタPA2のドレンは、反転出力ノードNXD1(第1の反転出力ノード)に接続される。

## 【0126】

そして、第1の電流制御回路132が、入力信号Vin及び出力信号Voutに基づいて第1及び第2の電流駆動トランジスタPA1、PA2のゲート電圧を制御する。より具体的には、第1の差動トランジスタ対を構成するトランジスタのうち入力信号Vinがゲートに入力されるp型トランジスタPT1のゲート・ソース間の電圧(の絶対値)が該トランジスタの閾値電圧(の絶対値)より小さいとき、第1の電流制御回路132が、出力ノードND1(第1の出力ノード)及び反転出力ノードNXD1(第1の反転出力ノード)の少なくとも一方を駆動するよう第1及び第2の電流駆動トランジスタPA1、PA2のゲート電圧を制御する。

## 【0127】

また第2の補助回路140は、n型(第2の導電型)の第3及び第4の電流駆動トランジスタNA3、NA4と、第2の電流制御回路142とを含むことができる。第3及び第

10

20

30

40

50

4 の電流駆動トランジスタ N A 3、N A 4 の各トランジスタのソースに、低電位側の電源電圧 V S S (第2の電源電圧) が供給される。第3の電流駆動トランジスタ N A 3 のドレインは、出力ノード N D 2 (第2の出力ノード) に接続される。第4の電流駆動トランジスタ N A 4 のドレインは、反転出力ノード N X D 2 (第2の反転出力ノード) に接続される。

#### 【0128】

そして、第2の電流制御回路 142 が、入力信号 V i n 及び出力信号 V o u t に基づいて第3及び第4の電流駆動トランジスタ N A 3、N A 4 のゲート電圧を制御する。より具体的には、第2の差動トランジスタ対を構成するトランジスタのうち入力信号 V i n がゲートに入力される n 型トランジスタ N T 3 のゲート・ソース間の電圧の絶対値が該トランジスタの閾値電圧の絶対値より小さいとき、第2の電流制御回路 142 が、出力ノード N D 2 (第2の出力ノード) 及び反転出力ノード N X D 2 (第2の反転出力ノード) の少なくとも一方を駆動するように第3及び第4の電流駆動トランジスタ N A 3、N A 4 のゲート電圧を制御する。

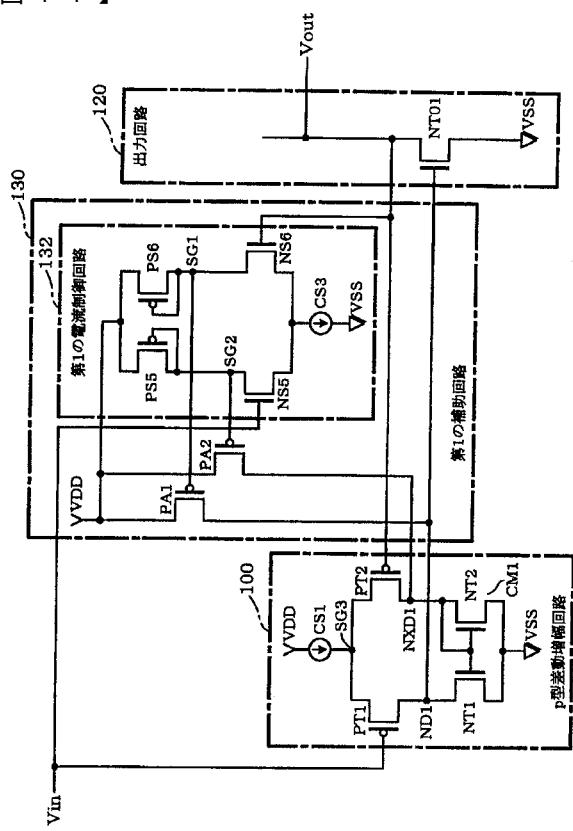

#### 【0129】

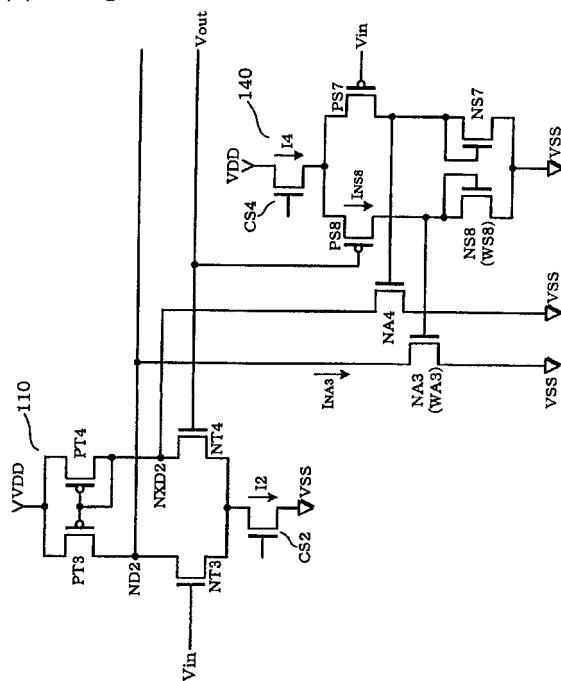

図11に、第1の電流制御回路 132 の構成例を示す。

#### 【0130】

第1の電流制御回路 132 は、第3の電流源 C S 3 と、n 型 (第2の導電型) の第3の差動トランジスタ対と、p 型 (第1の導電型) の第5及び第6の電流駆動トランジスタ P S 5、P S 6 とを含む。

#### 【0131】

第3の電流源 C S 3 の一端に、低電位側の電源電圧 V S S (第2の電源電圧) が供給される。

#### 【0132】

第3の差動トランジスタ対は、n 型トランジスタ N S 5、N S 6 を含む。n 型トランジスタ N S 5、N S 6 の各トランジスタのソースが、第3の電流源 C S 3 の他端に接続される。n 型トランジスタ N S 5 のゲートに、入力信号 V i n が入力される。n 型トランジスタ N S 6 のゲートに、出力信号 V o u t が入力される。

#### 【0133】

第5及び第6の電流駆動トランジスタ P S 5、P S 6 の各トランジスタのソースに、高電位側の電源電圧 V D D (第1の電源電圧) が供給される。第5の電流駆動トランジスタ P S 5 のドレインが、第3の差動トランジスタ対を構成する n 型トランジスタ N S 5 のドレインに接続される。第6の電流駆動トランジスタ P S 6 のドレインが、第3の差動トランジスタ対を構成する n 型トランジスタ N S 6 のドレインに接続される。第5の電流駆動トランジスタ P S 5 のゲート及びドレインが接続される。第6の電流駆動トランジスタ P S 6 のゲート及びドレインが接続される。

#### 【0134】

そして、第3の差動トランジスタ対を構成する n 型トランジスタ N S 5 (第3の差動トランジスタ対を構成するトランジスタのうちそのゲートに入力信号 V i n が入力されるトランジスタ) のドレイン (或いは第5の電流駆動トランジスタ P S 5 のドレイン) が、第2の電流駆動トランジスタ P A 2 のゲートに接続される。また、第3の差動トランジスタ対を構成する n 型トランジスタ N S 6 (第3の差動トランジスタ対を構成するトランジスタのうちそのゲートに出力信号 V o u t が入力されるトランジスタ) のドレイン (或いは第6の電流駆動トランジスタ P S 6 のドレイン) が、第1の電流駆動トランジスタ P A 1 のゲートに接続される。

#### 【0135】

即ち、第1及び第6の電流駆動トランジスタ P A 1、P S 6 は、カレントミラー回路を構成する。同様に、第2及び第5の電流駆動トランジスタ P A 2、P S 5 は、カレントミラー回路を構成する。

#### 【0136】

10

20

30

40

50

図 1 2 に、第 2 の電流制御回路 1 4 2 の構成例を示す。

【 0 1 3 7 】

第 2 の電流制御回路 1 4 2 は、第 4 の電流源 C S 4 と、p 型（第 1 の導電型）の第 4 の差動トランジスタ対と、n 型（第 2 の導電型）の第 7 及び第 8 の電流駆動トランジスタ N S 7、N S 8 とを含む。

【 0 1 3 8 】

第 4 の電流源 C S 4 の一端に、高電位側の電源電圧 V D D ( 第 1 の電源電圧 ) が供給される。

【 0 1 3 9 】

第 4 の差動トランジスタ対は、p 型トランジスタ P S 7、P S 8 を含む。p 型トランジスタ P S 7、P S 8 の各トランジスタのソースが、第 4 の電流源 C S 4 の他端に接続される。p 型トランジスタ P S 7 のゲートに、入力信号 V i n が入力される。p 型トランジスタ P S 8 のゲートに、出力信号 V o u t が入力される。10

【 0 1 4 0 】

第 7 及び第 8 の電流駆動トランジスタ N S 7、N S 8 の各トランジスタのソースに、低電位側の電源電圧 V S S ( 第 2 の電源電圧 ) が供給される。第 7 の電流駆動トランジスタ N S 7 のドレインが、第 4 の差動トランジスタ対を構成する p 型トランジスタ P S 7 のドレインに接続される。第 8 の電流駆動トランジスタ N S 8 のドレインが、第 4 の差動トランジスタ対を構成する p 型トランジスタ P S 8 のドレインに接続される。第 7 の電流駆動トランジスタ N S 7 のゲート及びドレインが接続される。第 8 の電流駆動トランジスタ N S 8 のゲート及びドレインが接続される。20

【 0 1 4 1 】

そして、第 4 の差動トランジスタ対を構成する p 型トランジスタ P S 7 ( 第 4 の差動トランジスタ対を構成するトランジスタのうちそのゲートに入力信号 V i n が入力されるトランジスタ ) のドレイン ( 或いは第 7 の電流駆動トランジスタ N S 7 のドレイン ) が、第 4 の電流駆動トランジスタ N A 4 のゲートに接続される。また、第 4 の差動トランジスタ対を構成する p 型トランジスタ P S 8 ( 第 4 の差動トランジスタ対を構成するトランジスタのうちそのゲートに出力信号 V o u t が入力されるトランジスタ ) のドレイン ( 或いは第 8 の電流駆動トランジスタ N S 8 のドレイン ) が、第 3 の電流駆動トランジスタ N A 3 のゲートに接続される。30

【 0 1 4 2 】

即ち、第 3 及び第 8 の電流駆動トランジスタ N A 3、N S 8 は、カレントミラー回路を構成する。同様に、第 4 及び第 7 の電流駆動トランジスタ N A 4、N S 7 は、カレントミラー回路を構成する。

【 0 1 4 3 】

次に、第 1 の補助回路 1 3 0 が図 1 1 に示す第 1 の電流制御回路 1 3 2 を有し、第 2 の補助回路 1 4 0 が図 1 2 に示す構成の第 2 の電流制御回路 1 4 2 を有するものとして、図 9 に示す構成の演算増幅器の動作について説明する。

【 0 1 4 4 】

まず、 $V_{t h n} + V_{S S} > V_{S S}$  のとき、p 型差動増幅回路 1 0 0 は、p 型トランジスタ P T 1 がオンとなって適正な動作を行なうが、n 型差動増幅回路 1 1 0 は、n 型トランジスタ N T 3 が動作しないため、n 型差動増幅回路 1 1 0 の各ノードの電圧は不定となる。40

【 0 1 4 5 】

ここで第 2 の補助回路 1 4 0 に着目すると、p 型トランジスタ P S 7 がオンしてインピーダンスが小さくなるため、第 4 の電流駆動トランジスタ N A 4 のゲート電圧が上がる。この結果、第 4 の電流駆動トランジスタ N A 4 のインピーダンスが小さくなる。即ち、第 4 の電流駆動トランジスタ N A 4 が反転出力ノード N X D 2 を駆動して電流を引き込み、反転出力ノード N X D 2 の電位が低くなる。この結果、p 型トランジスタ P T 3 のインピーダンスが小さくなつて、出力ノード N D 2 の電位が上がる。そして、出力回路 1 2 0 の50

第2の駆動トランジスタPTO1のインピーダンスが大きくなつて、出力信号Voutの電位が下がる。これにより、p型トランジスタPS8のインピーダンスが小さくなつて、第3の電流駆動トランジスタNA3のゲート電圧が上昇する。従つて、第3の電流駆動トランジスタNA3のインピーダンスが小さくなり、出力ノードND2の電位が下がる。

#### 【0146】

こうして、p型トランジスタPT3のインピーダンスを小さくして出力ノードND2の電位を上げた結果がフィードバックされ、第3の電流駆動トランジスタNA3のインピーダンスを小さくして出力ノードND2の電位を下げる。この結果、入力信号Vinの電圧と出力信号Voutの電圧がほぼ等しくなる平衡状態になり、第2の駆動トランジスタPTO1のゲート電圧が最適なところに確定する。

10

#### 【0147】

次に、 $VDD - Vin > VDD - |Vthp|$  のとき、上述の場合と逆に動作する。即ち、n型差動増幅回路110は、n型トランジスタNT3がオンとなって適正な動作を行うが、p型差動増幅回路100は、p型トランジスタPT1が動作しないため、p型差動増幅回路100の各ノードの電圧は不定となる。

#### 【0148】

ここで第1の補助回路130に着目すると、n型トランジスタNS5がオンしてインピーダンスが小さくなるため、第2の電流駆動トランジスタPA2のゲート電圧が下がる。この結果、第2の電流駆動トランジスタPA2のインピーダンスが小さくなる。即ち、第2の電流駆動トランジスタPA2が反転出力ノードNXD1を駆動して電流を供給し、反転出力ノードNXD1の電位が高くなる。この結果、n型トランジスタNT2のインピーダンスが小さくなつて、出力ノードND1の電位が下がる。そして、出力回路120の第1の駆動トランジスタNTO1のインピーダンスが大きくなつて、出力信号Voutの電位が上がる。これにより、n型トランジスタNS6のインピーダンスが小さくなつて、第1の電流駆動トランジスタPA1のゲート電圧が下がる。従つて、第1の電流駆動トランジスタPA1のインピーダンスが小さくなり、出力ノードND1の電位が上がる。

20

#### 【0149】

こうして、n型トランジスタNT2のインピーダンスを小さくして出力ノードND1の電位を下げた結果がフィードバックされ、第1の電流駆動トランジスタPA1のインピーダンスを小さくして出力ノードND1の電位を上げる。この結果、入力信号Vinの電圧と出力信号Voutの電圧がほぼ等しくなる平衡状態になり、第1の駆動トランジスタNTO1のゲート電圧が最適なところに確定する。

30

#### 【0150】

なお $VDD - |Vthp| - Vin - Vthn + VSS$ では、p型差動増幅回路100及びn型差動増幅回路110が動作し、出力ノードND1、ND2の電位が確定するため、第1及び第2の補助回路130、140を動作させなくても、入力信号Vinの電圧と出力信号Voutの電圧がほぼ等しくなる平衡状態になる。

40

#### 【0151】

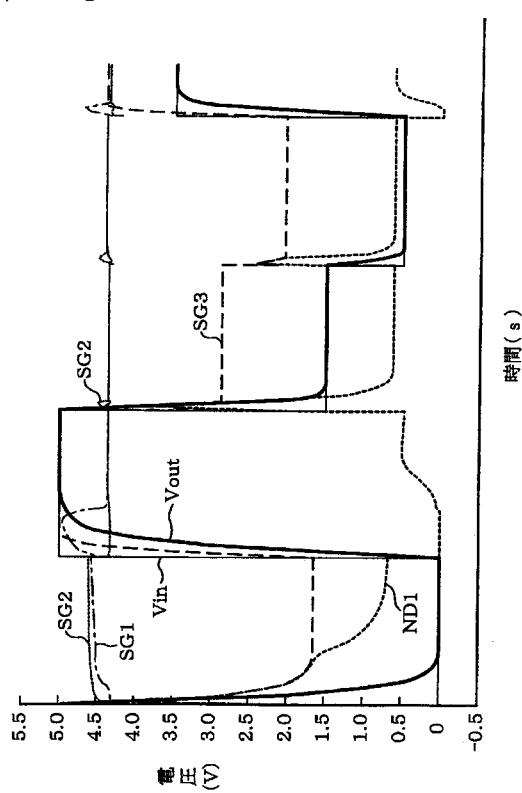

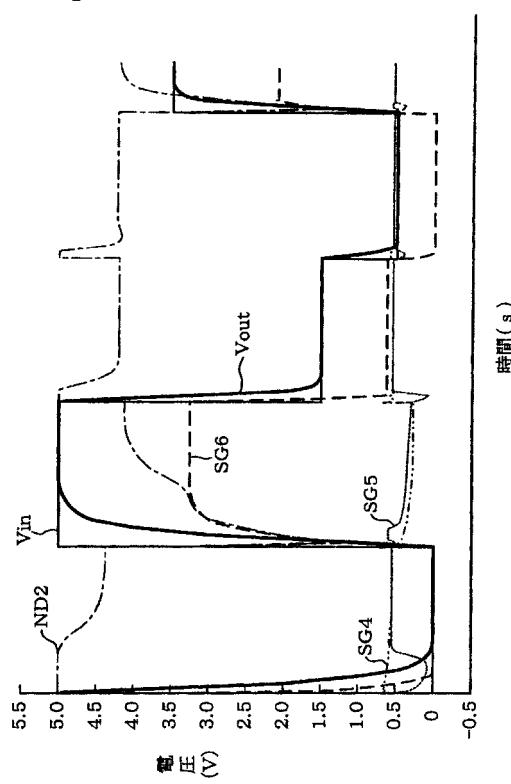

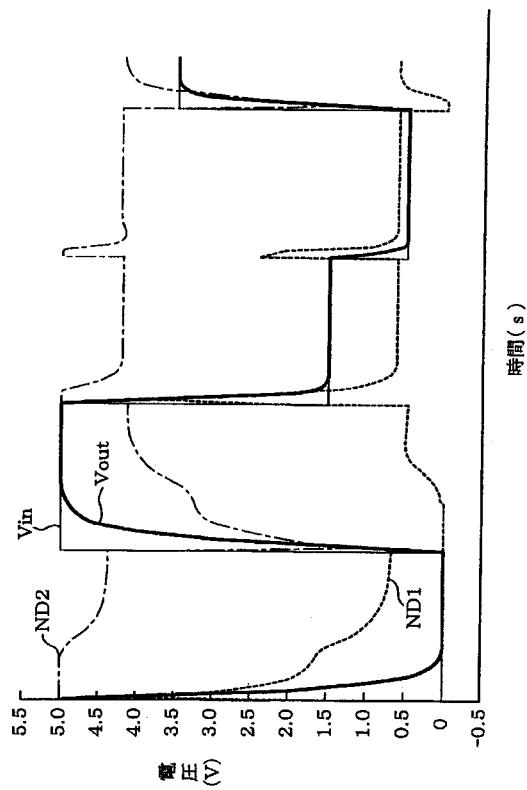

図13に、p型差動増幅回路100及び第1の補助回路130のノードの電圧変化についてのシミュレーション結果を示す。図14に、n型差動増幅回路110及び第2の補助回路140のノードの電圧変化についてのシミュレーション結果を示す。更に図15に、出力ノードND1、ND2の電圧変化についてのシミュレーション結果を示す。

#### 【0152】

図13において、ノードSG1は、第1の電流駆動トランジスタPA1のゲートである。ノードSG2は、第2の電流駆動トランジスタPA2のゲートである。ノードSG3は、第1の差動トランジスタ対を構成するp型トランジスタPT1、PT2のソースである。

#### 【0153】

図14において、ノードSG4は、第4の電流駆動トランジスタNA4のゲートである。ノードSG5は、第3の電流駆動トランジスタNA3のゲートである。ノードSG6は

50

、第2の差動トランジスタ対を構成するn型トランジスタNT3、NT4のソースである。

#### 【0154】

図13～図15に示すように、0.5ボルト付近の入力信号Vinが入力された場合であっても、出力ノードND1が不定状態とならず、出力回路120を構成する第1の駆動トランジスタNTO1のゲート電圧を制御している。

#### 【0155】

以上説明したように、本実施形態によれば、入力不感帯をなくし、いわゆるrail-to-railで動作し、かつ出力回路120の貫通電流を確実に抑える制御が可能となる。これにより、大幅に低消費電力化を実現する演算増幅器を提供できる。更にAB級動作が可能となるため、液晶の印加電圧を反転させる極性反転駆動において、極性に関わらずデータ線を安定して駆動できるようになる。

#### 【0156】

##### 3.3.1 電流値の調整

本実施形態における演算増幅器では、p型差動増幅回路100、n型差動増幅回路110、第1の補助回路130、及び第2の補助回路140の電流源の動作時の電流値を工夫することで、更に発振しにくくして回路の安定性を向上させることができる。

#### 【0157】

図16に、本実施形態におけるオペアンプVOPRの回路図を示す。図16では、各電流源CS1～CS4をトランジスタ（広義にはバイアス電流用トランジスタ）で構成している。この場合、各トランジスタのゲート電圧CS1G、CS2G、CS3G、CS4Gを制御することで、電流源の無駄な電流消費を削減できる。

#### 【0158】

本実施形態における演算増幅器の発振を防止するためには、出力回路120を構成する第1及び第2の駆動トランジスタNTO1、PTO1のドレイン電流を等しくすることが有効である。第1の駆動トランジスタNTO1のドレイン電流は、p型差動増幅回路100の第1の電流源CS1の動作時の電流値I1と、第1の補助回路130の第3の電流源CS3の動作時の電流値I3とにより定まる。第2の駆動トランジスタPTO1のドレイン電流は、n型差動増幅回路110の第2の電流源CS2の動作時の電流値I2と、第2の補助回路140の第4の電流源CS4の動作時の電流値I4とにより定まる。

#### 【0159】

ここで、電流値I1と電流値I3とが等しくないものとする。例えば電流値I1を10、電流値I3を5とする。同様に、電流値I2と電流値I4とが等しくないものとする。例えば電流値I2を10、電流値I4を5とする。

#### 【0160】

入力信号Vinの電圧が、p型差動増幅回路100と第1の補助回路130が動作する範囲の場合、第1の駆動トランジスタNTO1のドレイン電流は例えば15（=I1+I3=10+5）に相当する分が流れる。同様に、入力信号Vinの電圧が、n型差動増幅回路110と第2の補助回路140が動作する範囲の場合、第2の駆動トランジスタPTO1のドレイン電流は例えば15（=I2+I4=10+5）に相当する分が流れる。

#### 【0161】

これに対して、例えば入力信号Vinの電圧が低くなつてn型トランジスタが動作しなくなると、n型差動増幅回路110と第1の補助回路130が動作しなくなる。従って、第2及び第3の電流源CS2、CS3が流れなくなる（I2=0、I3=0）。そのため、第1の駆動トランジスタNTO1のドレイン電流は例えば10（=I1）に相当する分が流れ、第2の駆動トランジスタPTO1のドレイン電流は例えば5（=I4）に相当する分が流れる。例えば入力信号Vinの電圧が高くなつてp型トランジスタが動作しなくなる場合も同様である。

#### 【0162】

このように、出力回路120を構成する第1及び第2の駆動トランジスタNTO1、PTO1

10

20

30

40

50

T O 1 のドレイン電流が異なり、出力信号 V o u t の立ち上がり又は立ち下がりが異なると、出力が安定する時間が異なることとなり、発振し易くなる。

#### 【 0 1 6 3 】

そこで、本実施形態における演算増幅器では、第 1 及び第 3 の電流源 C S 1、C S 3 の動作時の電流値が等しく ( $I_1 = I_3$ )、かつ第 2 及び第 4 の電流源 C S 2、C S 4 の動作時の電流値が等しい ( $I_2 = I_4$ ) ことが望ましい。これは、第 1 ~ 第 4 の電流源 C S 1 ~ C S 4 を構成するトランジスタのチャネル長 L を共通にし、第 1 及び第 3 の電流源 C S 1、C S 3 を構成するトランジスタのチャネル幅を等しくし、かつ第 2 及び第 4 の電流源 C S 2、C S 4 を構成するトランジスタのチャネル幅を等しくすることで実現できる。

#### 【 0 1 6 4 】

更に、第 1 ~ 第 4 の電流源 C S 1 ~ C S 4 の各電流源の動作時の電流値が等しいこと ( $I_1 = I_2 = I_3 = I_4$ ) が望ましい。この場合、設計が容易になるからである。

#### 【 0 1 6 5 】

また第 3 及び第 4 の電流源 C S 3、C S 4 の動作時の電流値の少なくとも一方を削減することで、より低消費電力化を図ることができる。この場合、第 1 ~ 第 4 の電流駆動トランジスタ P A 1、P A 2、N A 3、N A 4 の各トランジスタの電流駆動能力を低下させることなく、第 3 及び第 4 の電流源 C S 3、C S 4 の動作時の電流値の少なくとも一方を削減する必要がある。

#### 【 0 1 6 6 】

##### 3 . 3 . 2 . 電流値の削減

図 18 に、第 4 の電流源 C S 4 の動作時の電流値を削減する構成例の説明図を示す。

#### 【 0 1 6 7 】

図 18 では、第 4 の電流源 C S 4 の動作時の電流値を削減するために、第 3 及び第 8 の電流駆動トランジスタ N A 3、N S 8 がカレントミラー回路を構成することを利用する。第 3 の電流駆動トランジスタ N A 3 のチャネル長を L、チャネル幅を W A 3、第 3 の電流駆動トランジスタ N A 3 のドレイン電流を  $I_{N A 3}$  とし、第 8 の電流駆動トランジスタ N S 8 のチャネル長を L、チャネル幅を W S 8、第 8 の電流駆動トランジスタ N S 8 のドレイン電流を  $I_{N S 8}$  とする。このとき、 $I_{N A 3} = (W A 3 / W S 8) \times I_{N S 8}$  と表わすことができる。ここで、 $(W A 3 / W S 8)$  は、第 8 の電流駆動トランジスタ N S 8 の電流駆動能力に対する第 3 の電流駆動トランジスタ N A 3 の電流駆動能力の比を意味する。従って、 $(W A 3 / W S 8)$  を 1 より大きくすることで、第 3 の電流駆動トランジスタ N A 3 の電流駆動能力を低下させることなくドレイン電流  $I_{N S 8}$  を小さくでき、第 4 の電流源 C S 4 の動作時の電流値  $I_4$  も小さくできる。

#### 【 0 1 6 8 】

なお図 12において、第 4 及び第 7 の電流駆動トランジスタ N A 4、N S 7 がカレントミラー回路を構成することを利用してよい。

#### 【 0 1 6 9 】

また同様に、第 3 の電流源 C S 3 の動作時の電流値を削減することが望ましい。この場合、第 1 及び第 6 の電流駆動トランジスタ P A 1、P S 6 がカレントミラー回路を構成することを利用したり、第 2 及び第 5 の電流駆動トランジスタ P A 2、P S 5 がカレントミラー回路を構成することを利用したりする。

#### 【 0 1 7 0 】

以上のように、第 6 の電流駆動トランジスタ P S 6 の電流駆動能力に対する第 1 の電流駆動トランジスタ P A 1 の電流駆動能力の比、第 5 の電流駆動トランジスタ P S 5 の電流駆動能力に対する第 2 の電流駆動トランジスタ P A 2 の電流駆動能力の比、第 8 の電流駆動トランジスタ N S 8 の電流駆動能力に対する第 3 の電流駆動トランジスタ N A 3 の電流駆動能力の比、及び第 7 の電流駆動トランジスタ N S 7 の電流駆動能力に対する第 4 の電流駆動トランジスタ N A 4 の電流駆動能力の比のうち少なくとも 1 つを、1 より大きくする。こうすることで、第 3 及び第 4 の電流源 C S 3、C S 4 のうち少なくとも 1 つの動作時の電流値を削減できる。

## 【0171】

3.3.3. オペアンプVOPRのオン・オフ制御

図16に示すように、Rail-to-Rail型オペアンプVOPRは、スイッチSW11（広義には第1のスイッチ）、スイッチSW12（広義には第2のスイッチ）、スイッチSW13（広義には第3のスイッチ）、スイッチSW14（広義には第4のスイッチ）、スイッチSW15（広義には第5のスイッチ）、スイッチSW16（広義には第6のスイッチ）及び出力イネーブルスイッチOE1（広義には出力イネーブルスイッチ）を含む。

## 【0172】

スイッチSW11は、入力信号Vinが入力される入力ノードIND1と出力信号Voutが出力される出力ノードOND1（広義には出力部）との間に設けられている。スイッチSW12は、電圧VSSを発生する電源と出力ノードND1との間に設けられている。スイッチSW13は、電圧VDDを発生する電源と出力ノードND2との間に設けられている。スイッチSW14は、出力ノードOND1とトランジスタNT4のゲートの間に設けられている。スイッチSW15は、電圧VDDを発生する電源と中間ノードMND1との間に設けられている。スイッチSW16は、電圧VSSを発生する電源と中間ノードMNDとの間に設けられている。出力イネーブルスイッチOE1は中間ノードMND1と出力ノードOND1との間に設けられている。

## 【0173】

さらに、Rail-to-Rail型オペアンプVOPRは、スイッチSW17～SW20を含む。

## 【0174】

スイッチSW17（広義には第3の補助スイッチ）は、第2の補助回路140のトランジスタNA3のゲートと、電圧VSSを発生する電源の間に設けられている。スイッチSW18（広義には第4の補助スイッチ）は、第2の補助回路140のトランジスタNA4のゲートと電圧VSSを発生する電源の間に設けられている。スイッチSW19（広義には第1の補助スイッチ）は、第1の補助回路130のトランジスタPA1のゲートと、電圧VDDを発生する電源の間に設けられている。スイッチSW20（広義には第2の補助スイッチ）は、第1の補助回路130のトランジスタPA2のゲートと電圧VDDを発生する電源の間に設けられている。

## 【0175】

例えば図3のインピーダンス変換回路IP2、IP3、IP8、IP9等のいずれかにおいて、Rail-to-Rail型オペアンプVOPRがオンに設定された場合には、スイッチSW11、スイッチSW14、スイッチSW15、スイッチSW16、出力イネーブルスイッチOE1がオンに設定される。また、スイッチSW12、SW13はオフに設定される。即ち、図16に示すような状態になる。

## 【0176】

一方、インピーダンス変換回路IP2等において、Rail-to-Rail型オペアンプVOPRがオフに設定され、通常型オペアンプVOPがオンに設定された場合には、スイッチSW11、スイッチSW14、スイッチSW15、スイッチSW16、出力イネーブルスイッチOE1がオフに設定される。また、スイッチSW12、SW13はオンに設定される。即ち、図17に示すような状態になる。これにより、トランジスタPT01、NT01は確実にオフにされ、出力ノードOND1はハイインピーダンス状態に設定される。さらに、各電流源CS1～CS4を構成するトランジスタのゲートに入力されるゲート電圧CS1G、CS2G、CS3G、CS4Gを制御する（例えば各電流源CS1～CS4を構成する各トランジスタをオフにする）ことで、各電流源の電流供給をオフにすることができる。これにより、Rail-to-Rail型オペアンプVOPRがオフに設定されている場合に、Rail-to-Rail型オペアンプVOPRによる無駄な電力消費を抑制できる。

## 【0177】

10

20

30

40

50

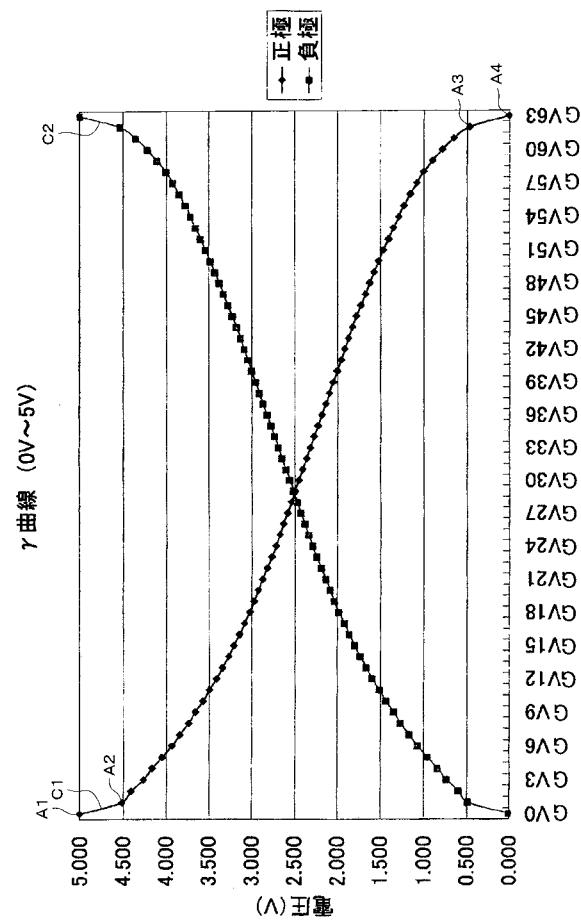

### 3.4. 基準電圧発生回路の動作

一例として、0V～5Vの電圧範囲で駆動されるパネルの（ガンマ）曲線を図19に示す。曲線C1は基準電圧VCOMが盛況である場合の（ガンマ）曲線であり、曲線C2は基準電圧VCOMが負極である場合の（ガンマ）曲線である。

#### 【0178】

Rail-to-Rail型オペアンプVOPRは電圧VDD～電圧VSSの間で動作可能なため、図19に示すような場合であっても0V～5Vの電圧範囲で動作可能である。しかしながら、通常型オペアンプVOPの動作範囲はオペアンプVOPRの動作範囲よりも狭い。図19に示すように電圧VDD～電圧VSSが5V～0Vである場合、通常型オペアンプVOPの動作範囲は例えば約1V～約4Vである。

10

#### 【0179】

これに対して、本実施形態の基準電圧発生回路20は、階調電圧に応じて、動作させるオペアンプの種類を切り替えることができるため、このようなパネルに対しても適用できる。

#### 【0180】

例えばA1に示すようにVCOMが正極である場合には、階調電圧GV0は5Vである。図3や図6に示すように基準電圧発生回路20では、階調電圧GV0はRail-to-Rail型オペアンプVOPRは上記のように入力信号Vinの電圧が5Vであっても動作する。即ち、基準電圧発生回路20は、A1に示すように階調電圧GV0として5Vを出力することができる。

20

#### 【0181】

また、A2に示すようにVCOMが正極である場合には、階調電圧GV1は4.5Vである。図3や図6に示すように基準電圧発生回路20では、階調電圧GV1はインピーダンス変換回路IP2の出力に設定されている。このとき、インピーダンス変換回路IP2では、通常型オペアンプVOPがオフに設定され、Rail-to-Rail型オペアンプVOPRがオンに設定される。Rail-to-Rail型オペアンプVOPRは上記のように入力信号Vinの電圧が4.5Vであっても動作する。即ち、基準電圧発生回路20は、A2に示すように階調電圧GV1として4.5Vを出力することができる。

30

#### 【0182】

また、A3に示すようにVCOMが正極である場合には、階調電圧GV62は0.5Vである。図3や図6に示すように基準電圧発生回路20では、階調電圧GV1はインピーダンス変換回路IP9の出力に設定されている。このとき、インピーダンス変換回路IP9では、通常型オペアンプVOPがオフに設定され、Rail-to-Rail型オペアンプVOPRがオンに設定される。Rail-to-Rail型オペアンプVOPRは上記のように入力信号Vinの電圧が0.5Vであっても動作する。即ち、基準電圧発生回路20は、A3に示すように階調電圧GV62として0.5Vを出力することができる。

#### 【0183】

また、A4に示すようにVCOMが正極である場合には、階調電圧GV63は0Vである。図3や図6に示すように基準電圧発生回路20では、階調電圧GV63はRail-to-Rail型オペアンプVOPRの出力に設定されている。Rail-to-Rail型オペアンプVOPRは上記のように入力信号Vinの電圧が0Vであっても動作する。即ち、基準電圧発生回路20は、A4に示すように階調電圧GV63として0Vを出力することができる。

40

#### 【0184】

曲線C2についても、上記と同様である。

#### 【0185】

上記のように、パネルの（ガンマ）曲線にあわせて、インピーダンス変換回路IP2、IP3、IP8、IP9のオペアンプVOP、VOPRのオン・オフ設定を切り替えることで、様々なパネルに対する（ガンマ）補正が可能である。

50

## 【0186】

## 4. 基準電圧発生回路の効果

例えば、図20に示すように、階調電圧GV0～GV63に対応するオペアンプを全てRaill-to-Raill型オペアンプVOPRにする構成（以下、比較例とする）も考えられる。このような構成であれば、本実施形態の基準電圧発生回路20と同様に様々なパネルに対して（ガンマ）補正が可能である。

## 【0187】

しかしながら、Raill-to-Raill型オペアンプVOPRは通常型オペアンプVOPに比べて、消費電力が大きい。図7に示すように通常型オペアンプVOPでは、その電流源が例えば電流源CSa、CSbの2つである。これに対して、Raill-to-Raill型オペアンプVOPRは、例えば図11、図12に示すようにその電流源が電流源CS1～CS4の4つである。さらに、Raill-to-Raill型オペアンプVOPRの回路は通常型オペアンプVOPの回路に比べて回路規模が大きい。従って、Raill-to-Raill型オペアンプVOPRは、通常型オペアンプVOPよりもその消費電力が大きく、オペアンプVOPRの消費電力は例えば30mAであるのに対し、オペアンプVOPの消費電力は15mAである。

10

## 【0188】

つまり、比較例では、消費電力の大きなオペアンプVOPRをたくさん使用するため、消費電力の低減が難しい。特に、階調数が増加するたびに、オペアンプVOPRの数を増やす必要がある場合があり、そのときにはさらに消費電力が増大する。

20

## 【0189】

これらに対して、本実施形態の基準電圧発生回路20では、一部のインピーダンス変換回路にて通常型オペアンプVOPとRaill-to-Raill型オペアンプVOPRを排他的に用いているため、比較例に比べて消費電力の低減が可能である。

30

## 【0190】

また、パネルによっては、図21の（ガンマ）曲線で示すような表示特性を持つパネルもある。このようなパネルの場合、階調電圧が1V～4Vであるため、比較例のように全てのオペアンプをRaill-to-Raill型オペアンプVOPRにしなくても良い。つまり、比較例の基準電圧発生回路をこのパネルに適用した場合、無駄に電力を消費することになる。

30

## 【0191】

これに対して、本実施形態の基準電圧発生回路20は図21の（ガンマ）曲線に対応する場合にインピーダンス変換回路IP2、IP3、IP8、IP9にてRaill-to-Raill型オペアンプVOPRをオフに設定可能である。そのため、消費電力の低減が可能となる。

40

## 【0192】

また、上記のように図21の（ガンマ）曲線に対応するために、オペアンプの組み合わせを変更して、消費電力の低減を図ることも可能であるが、パネルに特化した設計は、設計コストの削減を妨げる。

## 【0193】

これに対して、本実施形態の基準電圧発生回路20は図21の（ガンマ）曲線に対応可能であり、その場合には、インピーダンス変換回路IP2、IP3、IP8、IP9にてRaill-to-Raill型オペアンプVOPRをオフに設定可能である。そのため、消費電力の低減を実現しながら、図21の（ガンマ）曲線にも対応できる。つまり、パネルに特化した設計を行わずに、様々なパネルに適応できるため、設計コストの削減が可能となる。

## 【0194】

つまり、（ガンマ）曲線で求められた階調電圧に対して、その階調電圧を通常型オペアンプVOPで補うことができれば、通常型オペアンプVOPをオンに設定し、補うことのできない場合にはRaill-to-Raill型オペアンプVOPRをオンに設定するこ

50

とができる。

【0195】

以上のように、本実施形態は、低設計コスト、低消費電力を備えながら、そのパネルの表示特性に最適な階調電圧を供給することができる。

【0196】

例えば、本実施形態では、TFTを用いたアクティブマトリクス型液晶装置に本発明の駆動回路を適用する場合について説明したが、本発明はこれに限定されない。例えば、アクティブマトリクス型液晶装置以外の液晶装置に本発明の駆動回路を適用したり、エレクトロルミネッセンス(EL)装置、有機EL装置、プラズマディスプレイ装置などの電気光学装置に本発明の駆動回路を適用することも可能である。

10

【0197】

また、駆動回路の構成も図5～図19で説明した構成に限定されず、これらと均等な種々の構成を採用できる。

【0198】

また、本発明は、走査ライン反転駆動に限らず、他の反転駆動方式を採用する場合にも適用可能である。

【0199】

上記のように、本発明の実施例について詳細に説明したが、本発明の新規事項及び効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。したがって、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書または図面において、少なくとも一度、より広義又は同義な異なる用語と共に記載された用語は、明細書または図面のいかなる箇所においても、その異なる用語に置き換えることができる。

20

【図面の簡単な説明】

【0200】

【図1】電気光学装置(液晶装置)の構成例を示すブロック図。

【図2】駆動回路の構成例を示す図。

【図3】基準電圧発生回路の構成例。

【図4】演算増幅器の動作範囲の説明図。

【図5】基準電圧発生回路の他の構成例。

30

【図6】電圧分割回路の構成例の回路図。

【図7】第2型の演算増幅器の構成例の回路図。

【図8】第2型の演算増幅器の構成例の他の回路図。

【図9】本実施形態における演算増幅器の構成例を示す図。

【図10】図9に示す演算増幅器の動作説明図。

【図11】第1の電流制御回路の構成例の回路図。

【図12】第2の電流制御回路の構成例の回路図。

【図13】p型差動増幅回路及び第1の補助回路のノードの電圧変化についてのシミュレーション結果を示す図。

【図14】n型差動増幅回路及び第2の補助回路のノードの電圧変化についてのシミュレーション結果を示す図。

40

【図15】出力ノードの電圧変化についてのシミュレーション結果を示す図。

【図16】本実施形態における演算増幅器の構成例の他の回路図。

【図17】本実施形態における演算増幅器の構成例の他の回路図。

【図18】第4の電流源の動作時の電流値を削減する構成例の説明図。

【図19】(ガンマ)曲線の一例を示す図。

【図20】本実施形態に係る比較例の構成例。

【図21】(ガンマ)曲線の一例を示す他の図。

【符号の説明】

【0201】

50

20 基準電圧発生回路、80 電圧分割回路、

100 p型差動増幅回路(第1の導電型差動増幅回路)、

110 n型差動増幅回路(第2の導電型差動増幅回路)、

120 出力回路、130 第1の補助回路、132 第1の電流制御回路、

140 第2の補助回路、142 第2の電流制御回路、

I P 1 ~ I P 10 インピーダンス変換回路、

V D D 高電位側の電源電圧(第1の電源電圧)、V i n 入力信号、

V o u t 出力信号、V S S 低電位側の電源電圧(第2の電源電圧)、

V 3 第3の電源電圧、V 4 第4の電源電圧、

V O P 通常型オペアンプ(第2型のオペアンプ)、

V O P R Rail-to-Rail型オペアンプ(第1型のオペアンプ)

P A 1 第1の電流駆動トランジスタ、P A 2 第2の電流駆動トランジスタ、

P S 7、P S 8、P T 1、P T 2、P T 3、P T 4 p型トランジスタ、

P S 5 第5の電流駆動トランジスタ、P S 6 第6の電流駆動トランジスタ、

P T O 1 第2の駆動トランジスタ、

N A 3 第3の電流駆動トランジスタ、N A 4 第4の電流駆動トランジスタ、

N S 5、N S 6、N T 1、N T 2、N T 3、N T 4 n型トランジスタ、

N S 7 第7の電流駆動トランジスタ、N S 8 第8の電流駆動トランジスタ、

N T O 1 第1の駆動トランジスタ、

C S a、C S b バイアス電流用トランジスタ

10

20

【図1】

【図2】

〔 図 3 〕

【 図 4 】

【図5】

【 四 6 】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

**【手続補正書】**

【提出日】平成18年4月27日(2006.4.27)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

第1の電源電圧を供給する第1の電源と、前記第1の電源電圧よりも電源電圧の低い第2の電源電圧を供給する第2の電源とを用いて第1～第M(Mは2以上の整数)の分割電圧を生成して出力する電圧分割回路と、

前記第1～第Mの分割電圧のインピーダンス変換を行う第1～第Mのインピーダンス変換回路と、

を含み、

前記第1～第P(1 < P < M、Pは整数)のインピーダンス変換回路及び前記第Q(P < Q < M、Qは整数)～第Mのインピーダンス変換回路は、その動作範囲が前記第1の電源電圧と前記第2の電源電圧との間の範囲に設定されたRail-to-Rail型である第1型の演算增幅器を含み、

前記第P+1～第Q-1のインピーダンス変換回路は、その動作範囲が前記第1の電源電圧よりも低い第3の電圧と、前記第1の電源電圧よりも低く前記第2の電源電圧よりも高い第4の電圧との間の範囲に設定された第2型の演算增幅器を含むことを特徴とする電圧発生回路。

**【請求項2】**

請求項1において、

第2～第Pのインピーダンス変換回路及び第Q～第M-1のインピーダンス変換回路は、前記第2型の演算增幅器をさらに含み、

前記第2～第Pのインピーダンス変換回路及び前記第Q～第M-1のインピーダンス変換回路の各々に設けられた前記第1型の演算增幅器及び前記第2型の演算增幅器は、排他的に選択され、インピーダンス変換電圧を出力することを特徴とする電圧発生回路。

**【請求項3】**

請求項2において、

前記第2～第Pのインピーダンス変換回路及び前記第Q～第M-1のインピーダンス変換回路の各々に設けられた前記第1及び第2型の演算增幅器は、

前記第1型の演算增幅器及び前記第2型の演算增幅器の選択・非選択を設定する初期設定レジスタの設定値に基づいて、排他のに選択されてインピーダンス変換電圧を出力することを特徴とする電圧発生回路。

**【請求項4】**

請求項3において、

前記第2～第Pのインピーダンス変換回路及び前記第Q～第M-1のインピーダンス変換回路の各々に設けられた前記第1及び第2型の演算增幅器のうち、選択された演算增幅器ではバイアス電流用トランジスタがオンに設定され、非選択された演算增幅器ではバイアス電流用トランジスタがオフに設定されることを特徴とする電圧発生回路。

**【請求項5】**

請求項3又は4において、

前記第1型及び第2型の演算增幅器は、

一端に第1の電源電圧(VDD)が供給された第1の電流源(CS1)の他端に各トランジスタのソースが接続されると共に、入力信号(Vin)及び出力信号(Vout)が各トランジスタのゲートに入力される第1の導電型の第1の差動トランジスタ対(PT1、PT2)と、前記第1の差動トランジスタ対の各トランジスタのドレン電流を生成す

る第1のカレントミラー回路(CM1)とを有する第1の導電型差動增幅回路(100)と、

一端に第2の電源電圧(VSS)が供給された第2の電流源(CS2)の他端に各トランジスタのソースが接続されると共に、前記入力信号及び前記出力信号が各トランジスタのゲートに入力される第2の導電型の第2の差動トランジスタ対(NT3、NT4)と、前記第2の差動トランジスタ対の各トランジスタのドレイン電流を生成する第2のカレントミラー回路(CM2)とを有する第2の導電型差動增幅回路(110)と、

前記第1の差動トランジスタ対を構成する2つのトランジスタの一方のドレインである第1の出力ノード(ND1)の電圧に基づいてそのゲート電圧が制御される第2の導電型の第1の駆動トランジスタ(NT01)と、そのドレインが前記第1の駆動トランジスタのドレインに接続され前記第2の差動トランジスタ対を構成する2つのトランジスタの一方のドレインである第2の出力ノード(ND2)の電圧に基づいてそのゲート電圧が制御される第1の導電型の第2の駆動トランジスタ(PT01)とを有し、前記第1の駆動トランジスタ(NT01)のドレインの電圧を前記出力信号(Vout)として出力する出力回路(120)とを含むことを特徴とする電圧発生回路。

#### 【請求項6】

請求項5において、

前記第1型及び第2型の演算増幅器は、

前記入力信号(Vin)がゲートに入力されるトランジスタ(NT3)のゲートと、前記出力信号(Vout)がゲートに入力されるトランジスタ(NT4)のゲートとを電気的に接続する第1のスイッチをさらに含み、

前記第1及び第2型の演算増幅器のうち、

非選択に設定された演算増幅器の前記第1のスイッチはオンに設定され、

選択された演算増幅器の前記第1のスイッチはオフに設定されることを特徴とする電圧発生回路。

#### 【請求項7】

請求項5又は6において、

前記第1型及び第2型の演算増幅器は、

前記第1の出力ノード(ND1)と前記第2の電源とを電気的に接続する第2のスイッチと、

前記第2の出力ノード(ND2)と前記第1の電源とを電気的に接続する第3のスイッチと、

をさらに含み、

前記第1及び第2型の演算増幅器のうち、

非選択に設定された演算増幅器の前記第2及び第3のスイッチはオンに設定され、

選択された演算増幅器の前記第2及び第3のスイッチはオフに設定されることを特徴とする電圧発生回路。

#### 【請求項8】

請求項5乃至7のいずれかにおいて、

前記第1及び第2型の演算増幅器は、

前記出力信号(Vout)がゲートに入力されるトランジスタ(NT4)のゲートと出力信号(Vout)が出力される出力部とを電気的に接続する第4のスイッチをさらに含み、

前記第1及び第2型の演算増幅器のうち、

非選択に設定された演算増幅器の前記第4のスイッチはオフに設定され、

選択された演算増幅器の前記第4のスイッチはオンに設定されることを特徴とする電圧発生回路。

#### 【請求項9】

請求項5乃至8のいずれかにおいて、

前記第1及び第2型の演算増幅器は、

前記第2の駆動トランジスタ(PTO1)と前記第1の駆動トランジスタ(NTO1)との間の中間ノードと、前記第2の駆動トランジスタ(PTO1)のドレインとを電気的に接続する第5のスイッチと、

前記第1の駆動トランジスタ(NTO1)のドレインと、前記中間ノードとを電気的に接続する第6のスイッチと、

をさらに含み、

前記第1及び第2型の演算増幅器のうち、

非選択に設定された演算増幅器の前記第5及び第6のスイッチはオフに設定され、

選択された演算増幅器の前記第5及び第6のスイッチはオンに設定されることを特徴とする電圧発生回路。

#### 【請求項10】

請求項5乃至9のいずれかにおいて、

前記第1及び第2型の演算増幅器は、

前記第2の駆動トランジスタ(PTO1)と前記第1の駆動トランジスタ(NTO1)との間の中間ノードと、出力信号(Vout)が出力される出力部とを電気的に接続する出力イネーブルスイッチをさらに含み、

前記第1及び第2型の演算増幅器のうち、

非選択に設定された演算増幅器の前記出力イネーブルスイッチはオフに設定され、

選択された演算増幅器の前記出力イネーブルスイッチはオンに設定されることを特徴とする電圧発生回路。

#### 【請求項11】

請求項5乃至10のいずれかにおいて、

前記第1型の演算増幅器は、

前記入力信号(Vin)及び前記出力信号(Vout)に基づいて、前記第1の差動トランジスタ対を構成する2つのトランジスタのドレインである前記第1の出力ノード(ND1)及び第1の反転出力ノード(NXD1)のうち少なくとも一方を駆動する第1の補助回路(130)と、

前記入力信号(Vin)及び前記出力信号(Vout)に基づいて、前記第2の差動トランジスタ対を構成する2つのトランジスタのドレインである第2の出力ノード(ND2)及び第2の反転出力ノード(NXD2)のうち少なくとも一方を駆動する第2の補助回路(140)と、

をさらに含むことを特徴とする電圧発生回路。

#### 【請求項12】

請求項11において、

前記第1の補助回路(130)は、

前記第1の差動トランジスタ対(PT1、PT2)を構成するトランジスタのうち前記入力信号(Vin)がゲートに入力されるトランジスタ(PT1)のゲート・ソース間の電圧の絶対値が該トランジスタの閾値電圧の絶対値より小さいとき、

前記第1の出力ノード(ND1)及び前記第1の反転出力ノード(NXD1)の少なくとも一方を駆動することで、前記第1の駆動トランジスタ(NTO1)のゲート電圧を制御し、

前記第2の補助回路(140)は、

前記第2の差動トランジスタ対(NT3、NT4)を構成するトランジスタのうち前記入力信号(Vin)がゲートに入力されるトランジスタ(NT3)のゲート・ソース間電圧の絶対値が該トランジスタの閾値電圧の絶対値より小さいとき、

前記第2の出力ノード(ND2)及び前記第2の反転出力ノード(NXD2)の少なくとも一方を駆動することで、前記第2の駆動トランジスタ(PTO1)のゲート電圧を制御することを特徴とする電圧発生回路。

#### 【請求項13】

請求項11又は12において、

前記第1の補助回路が、

各トランジスタのソースに前記第1の電源電圧( VDD )が供給され、各トランジスタのドレインがそれぞれ前記第1の出力ノード( ND1 )及び前記第1の反転出力ノード( NXD1 )に接続された第1の導電型の第1及び第2の電流駆動トランジスタ( PA1 、 PA2 )と、

前記入力信号( Vin )及び前記出力信号( Vout )に基づいて前記第1及び第2の電流駆動トランジスタ( PA1 、 PA2 )のゲート電圧を制御する第1の電流制御回路( 132 )とを含み、

前記第1の差動トランジスタ対( PT1 、 PT2 )を構成するトランジスタのうち前記入力信号( Vin )がゲートに入力されるトランジスタ( PT1 )のゲート・ソース間の電圧の絶対値が該トランジスタの閾値電圧の絶対値より小さいとき、

前記第1の電流制御回路( 132 )が、

前記第1の出力ノード( ND1 )及び前記第1の反転出力ノード( NXD1 )の少なくとも一方を駆動するように前記第1及び第2の電流駆動トランジスタ( PA1 、 PA2 )のゲート電圧を制御することを特徴とする電圧発生回路。

#### 【請求項14】

請求項13において、

前記第1の電流制御回路( 132 )が、

一端に前記第2の電源電圧( VSS )が供給された第3の電流源( CS3 )と、

前記第3の電流源( CS3 )の他端に各トランジスタのソースが接続され、前記入力信号( Vin )及び前記出力信号( Vout )が各トランジスタのゲートに入力される第2の導電型の第3の差動トランジスタ対( NS5 、 NS6 )と、

各トランジスタのソースに前記第1の電源電圧( VDD )が供給され、各トランジスタのドレインがそれぞれ前記第3の差動トランジスタ対( NS5 、 NS6 )の各トランジスタのドレインに接続され、各トランジスタのゲート及びドレインが接続された第1の導電型の第5及び第6の電流駆動トランジスタ( PS5 、 PS6 )とを含み、

前記第3の差動トランジスタ対を構成するトランジスタのうちそのゲートに前記入力信号( Vin )が入力されるトランジスタ( NS5 )のドレインが前記第2の電流駆動トランジスタ( PA2 )のゲートに接続され、

前記第3の差動トランジスタ対を構成するトランジスタのうちそのゲートに前記出力信号( Vout )が入力されるトランジスタ( NS6 )のドレインが前記第1の電流駆動トランジスタ( PA1 )のゲートに接続されることを特徴とする演算増幅器。

#### 【請求項15】

請求項13又は14において、

前記第1型の演算増幅器は、

前記第1の電流駆動トランジスタ( PA1 )のゲートと、前記第1の電源とを電気的に接続する第1の補助スイッチと、

前記第2の電流駆動トランジスタ( PA2 )のゲートと、前記第1の電源とを電気的に接続する第2の補助スイッチと、

をさらに含み、

前記第1型の演算増幅器が非選択に設定された場合には、前記第1及び第2の補助スイッチはオンに設定され、

前記第1型の演算増幅器が選択された場合には、前記第1及び第2の補助スイッチはオフに設定されることを特徴とする電圧発生回路。

#### 【請求項16】

請求項11乃至15のいずれかにおいて、

前記第2の補助回路( 140 )は、

各トランジスタのソースに前記第2の電源電圧( VSS )が供給され、各トランジスタのドレインがそれぞれ前記第2の出力ノード( ND2 )及び前記第2の反転出力ノード( NXD2 )に接続された第2の導電型の第3及び第4の電流駆動トランジスタ( NA3 、

N A 4 ) と、

前記入力信号 ( V i n ) 及び前記出力信号 ( V o u t ) に基づいて前記第 3 及び第 4 の電流駆動トランジスタ ( N A 3 、 N A 4 ) のゲート電圧を制御する第 2 の電流制御回路 ( 1 4 2 ) とを含み、

前記第 2 の電流制御回路 ( 1 4 2 ) は、

前記第 2 の差動トランジスタ対 ( N T 3 、 N T 4 ) を構成するトランジスタのうち前記入力信号 ( V i n ) がゲートに入力されるトランジスタ ( N T 3 ) のゲート・ソース間の電圧の絶対値が該トランジスタの閾値電圧の絶対値より小さいとき、

前記第 2 の出力ノード ( N D 2 ) 及び前記第 2 の反転出力ノード ( N X D 2 ) の少なくとも一方を駆動するように前記第 3 及び第 4 の電流駆動トランジスタ ( N A 3 、 N A 4 ) のゲート電圧を制御することを特徴とする電圧発生回路。

#### 【請求項 1 7】

請求項 1 6 において、

前記第 2 の電流制御回路 ( 1 4 2 ) は、

一端に前記第 1 の電源電圧 ( V D D ) が供給された第 4 の電流源 ( C S 4 ) と、

前記第 4 の電流源 ( C S 4 ) の他端に各トランジスタのソースが接続され、前記入力信号 ( V i n ) 及び前記出力信号 ( V o u t ) が各トランジスタのゲートに入力される第 1 の導電型の第 4 の差動トランジスタ対 ( P S 7 、 P S 8 ) と、

各トランジスタのソースに前記第 2 の電源電圧 ( V S S ) が供給され、各トランジスタのドレインがそれぞれ前記第 4 の差動トランジスタ対 ( P S 7 、 P S 8 ) の各トランジスタのドレインに接続され、各トランジスタのゲート及びドレインが接続された第 2 の導電型の第 7 及び第 8 の電流駆動トランジスタ ( N S 7 、 N S 8 ) とを含み、

前記第 4 の差動トランジスタ対を構成するトランジスタのうちそのゲートに前記入力信号 ( V i n ) が入力されるトランジスタ ( P S 7 ) のドレインが前記第 4 の電流駆動トランジスタ ( N A 4 ) のゲートに接続され、

前記第 4 の差動トランジスタ対を構成するトランジスタのうちそのゲートに前記出力信号 ( V o u t ) が入力されるトランジスタ ( P S 8 ) のドレインが前記第 3 の電流駆動トランジスタ ( N A 3 ) のゲートに接続されることを特徴とする演算増幅器。

#### 【請求項 1 8】

請求項 1 6 又は 1 7 において、

前記第 1 型の演算増幅器は、

前記第 3 の電流駆動トランジスタ ( N A 3 ) のゲートと、前記第 2 の電源とを電気的に接続する第 3 の補助スイッチと、

前記第 4 の電流駆動トランジスタ ( N A 4 ) のゲートと、前記第 2 の電源とを電気的に接続する第 4 の補助スイッチと、

をさらに含み、

前記第 1 型の演算増幅器が非選択に設定された場合には、前記第 3 及び第 4 の補助スイッチはオンに設定され、

前記第 1 型の演算増幅器が選択された場合には、前記第 3 及び第 4 の補助スイッチはオフに設定されることを特徴とする電圧発生回路。

#### 【請求項 1 9】

請求項 1 乃至 4 のいずれかにおいて、

前記第 1 型の演算増幅器は、

入力信号 ( V i n ) 及び出力信号 ( V o u t ) の差分を増幅する第 1 の導電型差動増幅回路 ( 1 0 0 ) と、

前記入力信号 ( V i n ) 及び前記出力信号 ( V o u t ) の差分を増幅する第 2 の導電型差動増幅回路 ( 1 1 0 ) と、

前記入力信号 ( V i n ) 及び前記出力信号 ( V o u t ) に基づいて、前記第 1 の導電型差動増幅回路の第 1 の出力ノード ( N D 1 ) 及び第 1 の反転出力ノード ( N X D 1 ) のうち少なくとも一方を駆動する第 1 の補助回路 ( 1 3 0 ) と、

前記入力信号(  $V_{in}$  )及び前記出力信号(  $V_{out}$  )に基づいて、前記第2の導電型差動増幅回路の第2の出力ノード(  $N_D 2$  )及び第2の反転出力ノード(  $N_{XD} 2$  )のうち少なくとも一方を駆動する第2の補助回路( 140 )と、

前記第1及び第2の出力ノード(  $N_D 1$  、  $N_D 2$  )の電圧に基づいて前記出力信号(  $V_{out}$  )を生成する出力回路( 120 )とを含むことを特徴とする電圧発生回路。

#### 【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0015

【補正方法】変更

【補正の内容】

#### 【0015】

また、本発明では、前記第1型及び第2型の演算増幅器は、一端に第1の電源電圧(  $V_{DD}$  )が供給された第1の電流源(  $C_S 1$  )の他端に各トランジスタのソースが接続されると共に、入力信号(  $V_{in}$  )及び出力信号(  $V_{out}$  )が各トランジスタのゲートに入力される第1の導電型の第1の差動トランジスタ対(  $P_T 1$  、  $P_T 2$  )と、前記第1の差動トランジスタ対の各トランジスタのドレイン電流を生成する第1のカレントミラー回路(  $C_M 1$  )とを有する第1の導電型差動増幅回路( 100 )と、一端に第2の電源電圧(  $V_{SS}$  )が供給された第2の電流源(  $C_S 2$  )の他端に各トランジスタのソースが接続されると共に、前記入力信号及び前記出力信号が各トランジスタのゲートに入力される第2の導電型の第2の差動トランジスタ対(  $N_T 3$  、  $N_T 4$  )と、前記第2の差動トランジスタ対の各トランジスタのドレイン電流を生成する第2のカレントミラー回路(  $C_M 2$  )とを有する第2の導電型差動増幅回路( 110 )と、前記第1の差動トランジスタ対を構成する2つのトランジスタの一方のドレインである第1の出力ノード(  $N_D 1$  )の電圧に基づいてそのゲート電圧が制御される第2の導電型の第1の駆動トランジスタ(  $N_{TO} 1$  )と、そのドレインが前記第1の駆動トランジスタのドレインに接続され前記第2の差動トランジスタ対を構成する2つのトランジスタの一方のドレインである第2の出力ノード(  $N_D 2$  )の電圧に基づいてそのゲート電圧が制御される第1の導電型の第2の駆動トランジスタ(  $P_{TO} 1$  )とを有し、前記第1の駆動トランジスタ(  $N_{TO} 1$  )のドレインの電圧を前記出力信号(  $V_{out}$  )として出力する出力回路( 120 )とを含むようにしてもよい。

#### 【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0076

【補正方法】変更

【補正の内容】

#### 【0076】

インピーダンス変換回路IP4～IP7( 広義には第P+1～第Q-1のインピーダンス変換回路 )は、その動作範囲が電圧  $V_{DD}$  よりも低い電圧  $V_3$  ( 広義には第3の電圧 )と、電圧  $V_3$  よりも低く電圧  $V_{SS}$  よりも高い電圧  $V_4$  ( 広義には第4の電圧 )との間の範囲に設定された通常型オペアンプVOP( 広義には第2型の演算増幅器 )を含む。なお、図4に通常型オペアンプVOPの動作範囲を示す。通常型オペアンプVOPでは、図4のR1、R2に示すように入力電圧と出力電圧を等しくすることのできない入力不感帯を有する。これは、入力電圧が供給されるトランジスタの閾値に起因する。即ち、通常型オペアンプVOPの動作範囲は、R3に示すように電圧  $V_3$  から電圧  $V_4$  の間である。これに対して、R4に示すように例えば電圧  $V_{DD}$  ～電圧  $V_{SS}$  の間で動作可能なオペアンプがRail-to-Rail型のオペアンプVOPRである。即ち、通常型オペアンプVOPとRail-to-Rail型オペアンプVOPRとでは、その動作範囲が異なる。オペアンプVOP及びVOPRの構成は後述する。

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 1 2 F

(74)代理人 100104710

弁理士 竹腰 昇

(72)発明者 小林 弘典

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 2H093 NA16 NA53 NC03 NC13 NC14 NC34 ND39 ND54

5C006 AF83 BC12 BF25 BF43 FA47

5C080 AA10 BB05 DD26 EE29 FF03 FF11 JJ02 JJ03 JJ04 JJ05

KK01 KK07 KK43 KK47

5H420 CC02 DD02 EA14 EA18 EA24 EA40 EA42 EA43 EA47 EB37

GG04 GG06 NA12 NA17 NB02 NB14 NB18 NB25 NB37 NC03

NC22 NC23 NC33 NE26 NE28