(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6929804号

(P6929804)

(45) 発行日 令和3年9月1日(2021.9.1)

(24) 登録日 令和3年8月13日(2021.8.13)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 29/78   | (2006.01) | HO1L 29/78 | 657G |

| HO1L 29/739  | (2006.01) | HO1L 29/78 | 655G |

| HO1L 21/329  | (2006.01) | HO1L 29/78 | 653C |

| HO1L 29/866  | (2006.01) | HO1L 29/78 | 652J |

| HO1L 21/8234 | (2006.01) | HO1L 29/78 | 652Q |

請求項の数 3 (全 31 頁) 最終頁に続く

|                    |                              |

|--------------------|------------------------------|

| (21) 出願番号          | 特願2018-25759 (P2018-25759)   |

| (22) 出願日           | 平成30年2月16日(2018.2.16)        |

| (65) 公開番号          | 特開2019-57702 (P2019-57702A)  |

| (43) 公開日           | 平成31年4月11日(2019.4.11)        |

| 審査請求日              | 令和2年1月22日(2020.1.22)         |

| (31) 優先権主張番号       | 特願2017-180287 (P2017-180287) |

| (32) 優先日           | 平成29年9月20日(2017.9.20)        |

| (33) 優先権主張国・地域又は機関 | 日本国 (JP)                     |

|           |                                                 |

|-----------|-------------------------------------------------|

| (73) 特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号           |

| (73) 特許権者 | 317011920<br>東芝デバイス&ストレージ株式会社<br>東京都港区芝浦一丁目1番1号 |

| (74) 代理人  | 100119035<br>弁理士 池上 徹真                          |

| (74) 代理人  | 100141036<br>弁理士 須藤 章                           |

| (74) 代理人  | 100088487<br>弁理士 松山 允之                          |

| (72) 発明者  | 松下 憲一<br>東京都港区芝浦一丁目1番1号 東芝デバイス&ストレージ株式会社内       |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の面と、前記第1の面と対向する第2の面を有する半導体層と、少なくとも一部が前記第1の面に接するエミッタ電極と、少なくとも一部が前記第2の面に接するコレクタ電極と、前記半導体層の中に設けられ、前記第1の面に略平行な第1の方向に伸長する上部トレンチゲート電極と、

前記半導体層の中に設けられ、前記上部トレンチゲート電極と前記第2の面との間に設けられ、前記第1の方向に伸長し、前記上部トレンチゲート電極と電気的に分離される下部トレンチゲート電極と、

前記半導体層の中に設けられ、前記第1の方向に伸長する上部ダミートレンチゲート電極と、

前記半導体層の中に設けられ、前記上部ダミートレンチゲート電極と前記第2の面との間に設けられ、前記第1の方向に伸長し、前記上部ダミートレンチゲート電極と電気的に分離される下部ダミートレンチゲート電極と、

前記半導体層の中に設けられたp型のpベース領域と、

前記半導体層の中に設けられ、前記pベース領域と前記第1の面との間に設けられ、前記エミッタ電極に電気的に接続されたn型のエミッタ領域と、

前記半導体層の中に設けられ、前記pベース領域と、前記第2の面との間に設けられたn型のnベース領域と、

10

20

前記半導体層の中に設けられ、前記nベース領域と前記第2の面との間に設けられ、前記コレクタ電極に電気的に接続されたp型のコレクタ領域と、

前記上部トレンチゲート電極と前記pベース領域との間、前記上部トレンチゲート電極と前記エミッタ領域との間、及び、前記下部トレンチゲート電極と前記nベース領域との間に設けられ、前記pベース領域、前記エミッタ領域、及び、前記nベース領域に接するトレンチゲート絶縁膜と、

前記上部ダミートレンチゲート電極と前記pベース領域との間、及び、前記下部ダミートレンチゲート電極と前記nベース領域との間に設けられ、前記pベース領域、及び、前記nベース領域に接するダミートレンチゲート絶縁膜と、

前記上部トレンチゲート電極、前記下部トレンチゲート電極、及び、前記下部ダミートレンチゲート電極に電気的に接続された第1のゲートパッド電極と、

前記第1のゲートパッド電極と前記上部トレンチゲート電極との間に電気的に接続された第1の電気抵抗と、

前記第1のゲートパッド電極と前記下部トレンチゲート電極との間、及び、前記第1のゲートパッド電極と前記下部ダミートレンチゲート電極との間に電気的に接続された第2の電気抵抗と、

を備え、

前記上部トレンチゲート電極の容量と抵抗値の積に基づくC R時定数は、前記下部ダミートレンチゲート電極の容量と抵抗値の積に基づくC R時定数よりも小さい半導体装置。

#### 【請求項2】

前記上部トレンチゲート電極と前記第1の電気抵抗との間に電気的に接続された第1の接続配線と、

前記下部ダミートレンチゲート電極と前記第2の電気抵抗との間に電気的に接続された第2の接続配線と、を更に備え、

前記上部トレンチゲート電極及び前記下部ダミートレンチゲート電極は、前記第1の接続配線と前記第2の接続配線との間に位置する請求項1記載の半導体装置。

#### 【請求項3】

前記第1の電気抵抗、及び、前記第2の電気抵抗の材料の比抵抗は、前記第1の接続配線と前記第2の接続配線の材料の比抵抗よりも高い請求項2記載の半導体装置。

#### 【発明の詳細な説明】

30

#### 【技術分野】

#### 【0001】

本発明の実施形態は、半導体装置に関する。

#### 【背景技術】

#### 【0002】

電力用の半導体装置の一例として、IGBT (Insulated Gate Bipolar Transistor)がある。IGBTは、例えば、コレクタ電極上に、p型コレクタ領域、nベース領域、pベース領域が設けられる。そして、pベース領域を貫通し、nベース領域に達するトレンチ内に、トレンチゲート絶縁膜を介してトレンチゲート電極が設けられる。さらに、pベース領域表面のトレンチに隣接する領域に、エミッタ電極に接続されるエミッタ領域が設けられる。

40

#### 【0003】

IGBTでは、ゲート電極に正電圧が印加されることにより、pベース領域にチャネルが形成される。そして、エミッタ領域からnベース領域に電子が注入されると同時に、コレクタ領域からnベース領域に正孔が注入される。これにより、コレクタ電極とエミッタ電極間に電流が流れる。

#### 【0004】

IGBTのコレクタ電極とエミッタ電極との間のオン抵抗を低減するため、nベース領域からの正孔の排出を抑制する方法がある。この方法では、nベース領域からエミッタ電極への正孔の排出を抑制することで、相対的に電子の注入量を増大させ、IGBTのオン

50

抵抗を低減する。

**【0005】**

例えば、上記方法を実現するために、トレンチゲート電極の間に、チャネルの形成に寄与しないダミートレンチゲート電極を設ける間引き型IGBTが提案されている。スイッチング速度の向上やオン抵抗の低減等、特性の向上した間引き型IGBTの実現が望まれる。

**【先行技術文献】**

**【特許文献】**

**【0006】**

**【特許文献1】特開2013-251296号公報**

10

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0007】**

本発明が解決しようとする課題は、間引き型IGBTの特性の向上を可能とする半導体装置を提供することにある。

**【課題を解決するための手段】**

**【0008】**

実施形態の半導体装置は、第1の面と、前記第1の面と対向する第2の面を有する半導体層と、少なくとも一部が前記第1の面に接するエミッタ電極と、少なくとも一部が前記第2の面に接するコレクタ電極と、前記半導体層の中に設けられ、前記第1の面に略平行な第1の方向に伸長する上部トレンチゲート電極と、前記半導体層の中に設けられ、前記上部トレンチゲート電極と前記第2の面との間に設けられ、前記第1の方向に伸長し、前記上部トレンチゲート電極と電気的に分離される下部トレンチゲート電極と、前記半導体層の中に設けられ、前記第1の方向に伸長する上部ダミートレンチゲート電極と、前記半導体層の中に設けられ、前記上部ダミートレンチゲート電極と前記第2の面との間に設けられ、前記第1の方向に伸長し、前記上部ダミートレンチゲート電極と電気的に分離される下部ダミートレンチゲート電極と、前記半導体層の中に設けられたp型のpベース領域と、前記半導体層の中に設けられ、前記pベース領域と前記第1の面との間に設けられ、前記エミッタ電極に電気的に接続されたn型のエミッタ領域と、前記半導体層の中に設けられ、前記pベース領域と、前記第2の面との間に設けられたn型のnベース領域と、前記半導体層の中に設けられ、前記nベース領域と前記第2の面との間に設けられ、前記コレクタ電極に電気的に接続されたp型のコレクタ領域と、前記上部トレンチゲート電極と前記pベース領域との間、前記上部トレンチゲート電極と前記エミッタ領域との間、及び、前記下部トレンチゲート電極と前記nベース領域との間に設けられ、前記pベース領域、前記エミッタ領域、及び、前記nベース領域に接するトレンチゲート絶縁膜と、前記上部ダミートレンチゲート電極と前記pベース領域との間、及び、前記下部ダミートレンチゲート電極と前記nベース領域との間に設けられ、前記pベース領域、及び、前記nベース領域に接するダミートレンチゲート絶縁膜と、前記上部トレンチゲート電極、前記下部トレンチゲート電極、及び、前記下部ダミートレンチゲート電極に電気的に接続された第1のゲートパッド電極と、前記第1のゲートパッド電極と前記上部トレンチゲート電極との間に電気的に接続された第1の電気抵抗と、前記第1のゲートパッド電極と前記下部トレンチゲート電極との間、及び、前記第1のゲートパッド電極と前記下部ダミートレンチゲート電極との間に電気的に接続された第2の電気抵抗と、を備え、前記上部トレンチゲート電極の容量と抵抗値の積に基づくCR時定数は、前記下部ダミートレンチゲート電極の容量と抵抗値の積に基づくCR時定数よりも小さい。

20

30

30

40

**【図面の簡単な説明】**

**【0009】**

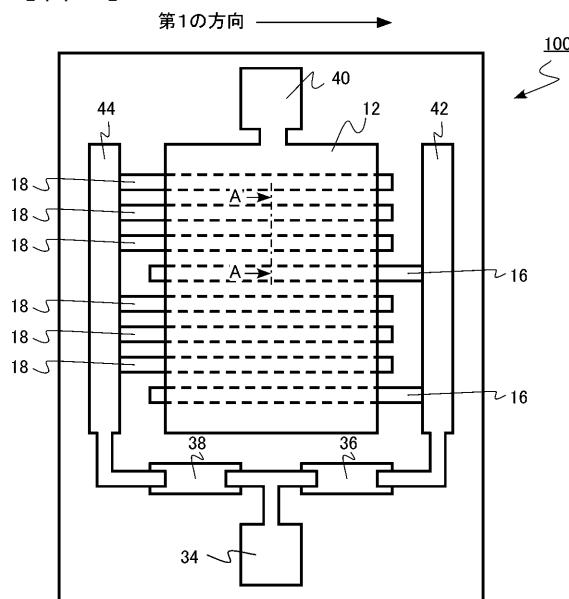

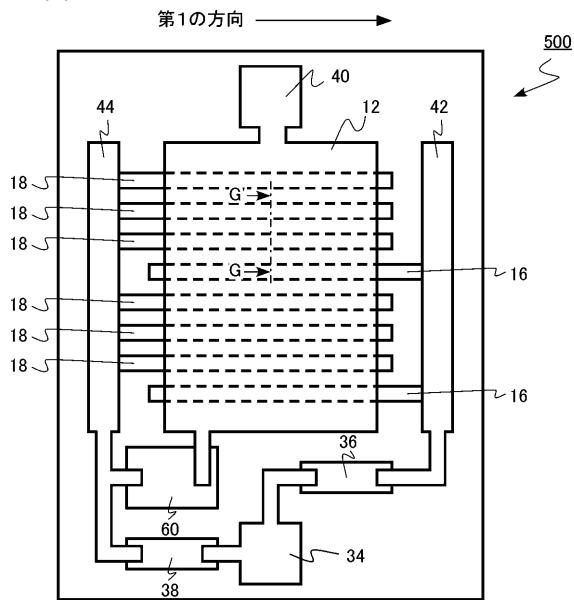

**【図1】第1の実施形態の半導体装置の模式平面図。**

**【図2】第1の実施形態の半導体装置の模式断面図。**

**【図3】第1の比較形態の半導体装置の模式平面図。**

50

- 【図4】第1の比較形態の半導体装置の模式断面図。

【図5】第2の比較形態の半導体装置の模式平面図。

【図6】第2の比較形態の半導体装置の模式断面図。

【図7】第1の実施形態の半導体装置の作用及び効果の説明図。

【図8】第1の実施形態の半導体装置の作用及び効果の説明図。

【図9】第2の実施形態の半導体装置の模式平面図。

【図10】第2の実施形態の半導体装置の模式断面図。

【図11】第2の実施形態の半導体装置の等価回路図。

【図12】第3の実施形態の半導体装置の模式平面図。

【図13】第4の実施形態の半導体装置の模式平面図。

【図14】第4の実施形態の半導体装置の模式断面図。

【図15】第4の実施形態の半導体装置の作用及び効果の説明図。

【図16】第5の実施形態の半導体装置の模式平面図。

【図17】第5の実施形態の半導体装置の模式断面図。

【図18】第5の実施形態の半導体装置の作用及び効果の説明図。

【図19】第5の実施形態の半導体装置の模式平面図。

【図20】第5の実施形態の半導体装置の模式断面図。

【図21】第5の実施形態の半導体装置の作用及び効果の説明図。

**【発明を実施するための形態】****【0010】**

以下、図面を参照しつつ本発明の実施形態を説明する。なお、以下の説明では、同一の部材等には同一の符号を付し、一度説明した部材等については適宜その説明を省略する。

**【0011】**

本明細書中、 $n^+$ 型、 $n$ 型、 $n^-$ 型との表記がある場合、 $n^+$ 型、 $n$ 型、 $n^-$ 型の順で $n$ 型の不純物濃度が低くなっていることを意味する。また、 $p^+$ 型、 $p$ 型、 $p^-$ 型の表記がある場合、 $p^+$ 型、 $p$ 型、 $p^-$ 型の順で、 $p$ 型の不純物濃度が低くなっていることを意味する。

**【0012】****(第1の実施形態)**

本実施形態の半導体装置は、第1の面と、第1の面と対向する第2の面を有する半導体層と、少なくとも一部が第1の面に接するエミッタ電極と、少なくとも一部が第2の面に接するコレクタ電極と、半導体層の中に設けられ、第1の面に略平行な第1の方向に伸長するトレンチゲート電極と、半導体層の中に設けられ、第1の方向に伸長するダミートレンチゲート電極と、半導体層の中に設けられた $p$ 型の $p$ ベース領域と、半導体層の中に設けられ、 $p$ ベース領域と第1の面との間に設けられ、エミッタ電極に電気的に接続された $n$ 型のエミッタ領域と、半導体層の中に設けられ、 $p$ ベース領域と、第2の面との間に設けられた $n$ 型の $n$ ベース領域と、半導体層の中に設けられ、 $n$ ベース領域と第2の面との間に設けられ、コレクタ電極に電気的に接続された $p$ 型のコレクタ領域と、トレンチゲート電極と $p$ ベース領域との間、トレンチゲート電極とエミッタ領域との間、及び、トレンチゲート電極と $n$ ベース領域との間に設けられ、 $p$ ベース領域、エミッタ領域、及び、 $n$ ベース領域に接するトレンチゲート絶縁膜と、ダミートレンチゲート電極と $p$ ベース領域との間、及び、ダミートレンチゲート電極と $n$ ベース領域との間に設けられ、 $p$ ベース領域、及び、 $n$ ベース領域に接するダミートレンチゲート絶縁膜と、トレンチゲート電極、及び、ダミートレンチゲート電極に電気的に接続された第1のゲートパッド電極と、第1のゲートパッド電極とトレンチゲート電極との間に電気的に接続された第1の電気抵抗と、第1のゲートパッド電極とダミートレンチゲート電極との間に電気的に接続された第2の電気抵抗と、を備え、トレンチゲート電極のC R時定数は、ダミートレンチゲート電極のC R時定数よりも小さい。

**【0013】**

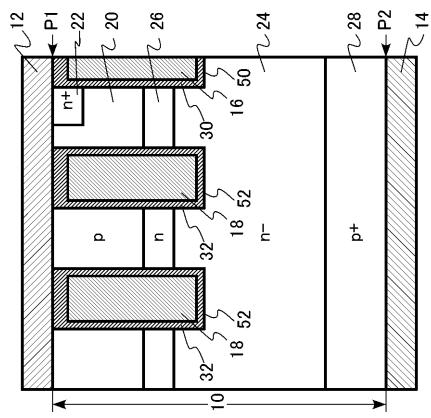

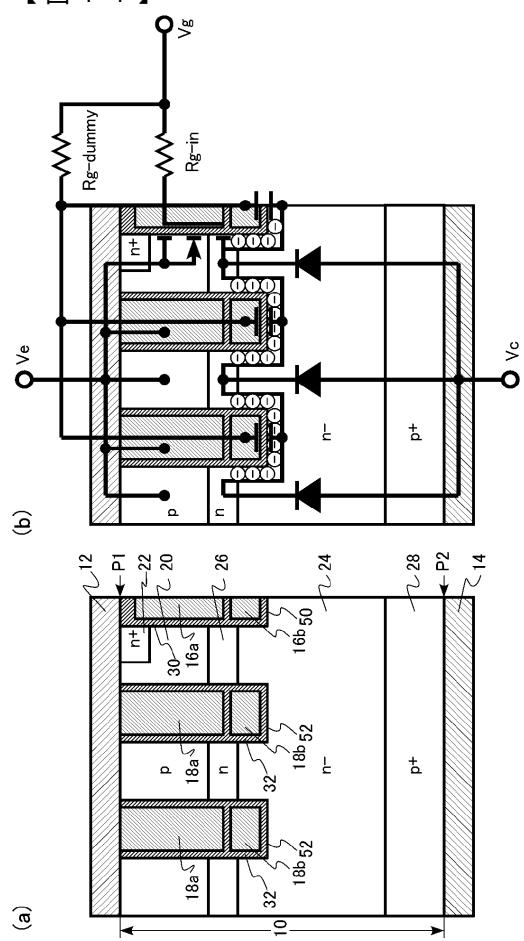

図1は、本実施形態の半導体装置の模式平面図である。図2は、本実施形態の半導体装

10

20

30

40

50

置の模式断面図である。図2(a)は図1のAA'断面図である。図2(b)は図2(a)に等価回路を重ね書きした説明図である。

#### 【0014】

本実施形態の半導体装置は、半導体層に形成されたトレンチの中にゲート電極を備えるトレンチIGBT100である。トレンチIGBT100は、ダミートレンチゲート電極を有する間引き型IGBTである。

#### 【0015】

本実施形態のトレンチIGBT100は、半導体層10、エミッタ電極12、コレクタ電極14、トレンチゲート電極16、ダミートレンチゲート電極18、pベース領域20、エミッタ領域22、nベース領域24、バリア領域26(n型半導体領域)、コレクタ領域28、トレンチゲート絶縁膜30、ダミートレンチゲート絶縁膜32、ゲートパッド電極34(第1のゲートパッド電極)、内部ゲート抵抗36(第1の電気抵抗)、ダミーゲート抵抗38(第2の電気抵抗)、エミッタパッド電極40、ゲート電極接続配線42(第1の接続配線)、ダミーゲート電極接続配線44(第2の接続配線)、トレンチ50、ダミートレンチ52を備える。

10

#### 【0016】

半導体層10は、第1の面P1と、第1の面P1に対向する第2の面P2とを有する。半導体層10は、例えば、単結晶シリコンである。半導体層10の膜厚は、例えば、50μm以上700μm以下である。

20

#### 【0017】

エミッタ電極12の少なくとも一部は半導体層10の第1の面P1に接する。エミッタ電極12は、例えば、金属である。エミッタ電極12には、エミッタ電圧(Ve)が印加される。エミッタ電圧は、例えば、0Vである。

#### 【0018】

コレクタ電極14の少なくとも一部は半導体層10の第2の面P2に接する。コレクタ電極14は、例えば、金属である。コレクタ電極14には、コレクタ電圧(Vc)が印加される。コレクタ電圧は、例えば、200V以上6500V以下である。

30

#### 【0019】

トレンチゲート電極16は、半導体層10の中に複数設けられる。トレンチゲート電極16は、半導体層10に形成されたトレンチ50の中に設けられる。トレンチゲート電極16は、第1の面P1に略平行な第1の方向に伸長する。トレンチゲート電極16は、例えば、n型不純物又はp型不純物を含む多結晶シリコンである。

#### 【0020】

ダミートレンチゲート電極18は、半導体層10の中に複数設けられる。ダミートレンチゲート電極18は、半導体層10に形成されたダミートレンチ52の中に設けられる。ダミートレンチゲート電極18は、第1の面P1に略平行な第1の方向に伸長する。ダミートレンチゲート電極18は、トレンチゲート電極16の間に、トレンチゲート電極16に平行に設けられる。ダミートレンチゲート電極18は、例えば、n型不純物又はp型不純物を含む多結晶シリコンである。

40

#### 【0021】

pベース領域20は、半導体層10の中に設けられる。pベース領域20は、p型の半導体領域である。pベース領域20のトレンチゲート絶縁膜30に接する領域は、IGBT100のチャネル領域として機能する。

#### 【0022】

エミッタ領域22は、半導体層10の中に設けられる。エミッタ領域22は、pベース領域20と第1の面P1との間に設けられ、トレンチゲート絶縁膜30と接している。エミッタ領域22は、n型の半導体領域である。エミッタ領域22は、2つのダミートレンチゲート電極18の間には設けられない。エミッタ領域22は、エミッタ電極12に電気的に接続される。

#### 【0023】

50

n ベース領域 2 4 は、半導体層 1 0 の中に設けられる。n ベース領域 2 4 は、p ベース領域 2 0 と第 2 の面との間に設けられる。n ベース領域 2 4 は、n 型の半導体領域である。

#### 【 0 0 2 4 】

バリア領域 2 6 は、半導体層 1 0 の中に設けられる。バリア領域 2 6 は、p ベース領域 2 0 と n ベース領域 2 4 との間に設けられる。バリア領域 2 6 は、n 型の半導体領域である。バリア領域 2 6 の n 型不純物濃度は、n ベース領域 2 4 の n 型不純物濃度よりも高い。バリア領域 2 6 の n 型不純物濃度は、エミッタ領域 2 2 の n 型不純物濃度よりも低い。バリア領域 2 6 はトレンチ I G B T 1 0 0 のオン抵抗を低減する機能を有する。

#### 【 0 0 2 5 】

コレクタ領域 2 8 は、半導体層 1 0 の中に設けられる。コレクタ領域 2 8 は、n ベース領域 2 4 と第 2 の面 P 2 との間に設けられる。コレクタ領域 2 8 は、p 型の半導体領域である。コレクタ領域 2 8 の p 型不純物濃度は、p ベース領域 2 0 の p 型不純物濃度よりも高い。コレクタ領域 2 8 は、コレクタ電極 1 4 に電気的に接続される。

#### 【 0 0 2 6 】

なお、n ベース領域 2 4 とコレクタ領域 2 8 との間に、n ベース領域 2 4 よりも n 型不純物濃度の高いバッファ領域を設けることも可能である。バッファ領域を設けることにより、トレンチ I G B T 1 0 0 がオフ状態の際に、空乏層の伸びを抑制することが可能となる。

#### 【 0 0 2 7 】

トレンチゲート絶縁膜 3 0 は、トレンチゲート電極 1 6 と、p ベース領域 2 0 、エミッタ領域 2 2 、及び、n ベース領域 2 4 との間に設けられる。トレンチゲート絶縁膜 3 0 は、トレンチ 5 0 の中に設けられる。トレンチゲート絶縁膜 3 0 は、p ベース領域 2 0 、エミッタ領域 2 2 、及び、n ベース領域 2 4 に接する。トレンチゲート絶縁膜 3 0 は、例えば、酸化シリコンである。

#### 【 0 0 2 8 】

ダミートレンチゲート絶縁膜 3 2 は、ダミートレンチゲート電極 1 8 と、p ベース領域 2 0 、及び、n ベース領域 2 4 との間に設けられる。ダミートレンチゲート絶縁膜 3 2 は、ダミートレンチ 5 2 の中に設けられる。ダミートレンチゲート絶縁膜 3 2 は、p ベース領域 2 0 、及び、n ベース領域 2 4 に接する。ダミートレンチゲート絶縁膜 3 2 は、エミッタ領域 2 2 とは接しない。ダミートレンチゲート絶縁膜 3 2 は、例えば、酸化シリコンである。

#### 【 0 0 2 9 】

ゲートパッド電極 3 4 は、半導体層 1 0 の上に設けられる。ゲートパッド電極 3 4 は、半導体層 1 0 の第 1 の面 P 1 の側に設けられる。ゲートパッド電極 3 4 は、トレンチゲート電極 1 6 、及び、ダミートレンチゲート電極 1 8 に電気的に接続される。ゲートパッド電極 3 4 は、例えば、金属である。

#### 【 0 0 3 0 】

内部ゲート抵抗 3 6 は、半導体層 1 0 の上に設けられる。内部ゲート抵抗 3 6 は、半導体層 1 0 の第 1 の面 P 1 の側に設けられる。内部ゲート抵抗 3 6 は、ゲートパッド電極 3 4 とトレンチゲート電極 1 6 との間に電気的に接続される。

#### 【 0 0 3 1 】

内部ゲート抵抗 3 6 は、例えば、半導体である。内部ゲート抵抗 3 6 は、例えば、導電性不純物を含む多結晶シリコンである。内部ゲート抵抗 3 6 は、例えば、ゲート電極接続配線 4 2 よりも比抵抗の高い材料で形成される。

#### 【 0 0 3 2 】

ダミーゲート抵抗 3 8 は、半導体層 1 0 の上に設けられる。ダミーゲート抵抗 3 8 は、半導体層 1 0 の第 1 の面 P 1 の側に設けられる。ダミーゲート抵抗 3 8 は、ゲートパッド電極 3 4 とダミートレンチゲート電極 1 8 との間に電気的に接続される。

#### 【 0 0 3 3 】

10

20

30

40

50

ダミーゲート抵抗38は、例えば、半導体である。ダミーゲート抵抗38は、例えば、導電性不純物を含む多結晶シリコンである。ダミーゲート抵抗38は、例えば、ゲート電極接続配線42よりも比抵抗の高い材料で形成される。

#### 【0034】

ゲート電極接続配線42は、トレンチゲート電極16と内部ゲート抵抗36との間に電気的に接続される。ゲート電極接続配線42は、トレンチゲート電極16の端部に接続される。ゲート電極接続配線42は、例えば、図示しないコンタクト部でトレンチゲート電極16に接続される。ゲート電極接続配線42は、例えば、金属である。

#### 【0035】

ダミーゲート電極接続配線44は、ダミートレンチゲート電極18とダミーゲート抵抗38との間に電気的に接続される。ダミーゲート電極接続配線44は、ダミートレンチゲート電極18の端部に接続される。ダミーゲート電極接続配線44は、例えば、図示しないコンタクト部でダミートレンチゲート電極18に接続される。ダミートレンチゲート電極18は、例えば、金属である。

10

#### 【0036】

トレンチゲート電極16、及び、ダミートレンチゲート電極18は、ゲート電極接続配線42とダミーゲート電極接続配線44との間に位置する。言い換えれば、ゲート電極接続配線42は、トレンチゲート電極16、及び、ダミートレンチゲート電極18の一方の端部に位置し、ダミーゲート電極接続配線44は、トレンチゲート電極16、及び、ダミートレンチゲート電極18の他方の端部に位置する。

20

#### 【0037】

トレンチゲート電極16のCR時定数は、ダミートレンチゲート電極18のCR時定数よりも小さい。トレンチゲート電極16のCR時定数は、主に、トレンチゲート電極16と半導体層10との間の容量、トレンチゲート電極16の抵抗値、及び、内部ゲート抵抗36の抵抗値で規定される。ダミートレンチゲート電極18のCR時定数は、主に、ダミートレンチゲート電極18と半導体層10との間の容量、ダミートレンチゲート電極18の抵抗値、及び、ダミーゲート抵抗38の抵抗値で規定される。

#### 【0038】

エミッタパッド電極40は、半導体層10の上に設けられる。エミッタパッド電極40は、半導体層10の第1の面P1の側に設けられる。エミッタパッド電極40は、エミッタ電極12に電気的に接続される。

30

#### 【0039】

IGBT100は、エミッタパッド電極40、コレクタ電極14、及び、ゲートパッド電極34の3つの電極を端子とする3端子デバイスである。

#### 【0040】

図2(b)に示すように、本実施形態のトレンチIGBT100は、内部ゲート抵抗(Rg-in)とダミーゲート抵抗(Rg-dummy)が並列に接続される。内部ゲート抵抗(Rg-in)とダミーゲート抵抗(Rg-dummy)は、IGBT100の外部で、例えば、外部ゲート抵抗を介してゲートドライバに接続される。ゲートドライバにより、トレンチゲート電極16、及び、ダミートレンチゲート電極18にゲート電圧(Vg)が印加される。

40

#### 【0041】

内部ゲート抵抗(Rg-in)は図1の内部ゲート抵抗36に対応する。ダミーゲート抵抗(Rg-dummy)は、図1のダミーゲート抵抗38に対応する。

#### 【0042】

pベース領域20は、例えば、エミッタ電極12に電気的に接続される。pベース領域20は、例えば、グラウンド電位に固定される。ダミートレンチゲート電極18に挟まれるpベース領域20は、例えば、フローティングであっても構わない。

#### 【0043】

以下、本実施形態のトレンチIGBT100の作用及び効果について説明する。

50

**【 0 0 4 4 】**

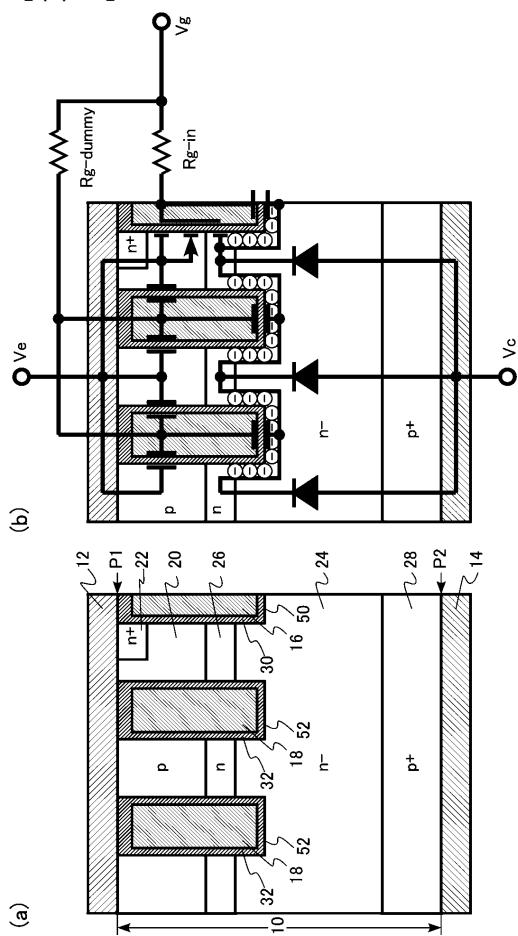

図3は、第1の比較形態の半導体装置の模式平面図である。図4は、第1の比較形態の半導体装置の模式断面図である。図4(a)は図3のBB'断面図である。図4(b)は図4(a)に等価回路を重ね書きした説明図である。

**【 0 0 4 5 】**

第1の比較形態の半導体装置は、半導体層に形成されたトレンチの中にゲート電極を備えるトレンチIGBT800である。トレンチIGBT800は、ダミートレンチゲート電極を有する間引き型IGBTである。

**【 0 0 4 6 】**

トレンチIGBT800は、ダミートレンチゲート電極18がエミッタ電極12に電気的に接続される点、及び、ダミーゲート抵抗38が設けられない点で、実施形態のトレンチIGBT100と異なる。

**【 0 0 4 7 】**

トレンチIGBT800のダミートレンチゲート電極18は、エミッタ電極12に電気的に接続される。ダミートレンチゲート電極18には、エミッタ電圧(V<sub>e</sub>)が印加される。エミッタ電圧は、例えば、0Vである。このため、ダミートレンチ52底部近傍のnベース領域24には、電子の蓄積層が形成されない。

**【 0 0 4 8 】**

図4(b)から分かるように、ダミートレンチ52底部近傍のnベース領域24に電子の蓄積層が形成されないため、ダミートレンチゲート電極18の間に存在し、コレクタ領域28、nベース領域24、及び、バリア領域26で構成される寄生pnダイオードが、トレンチゲート電極16をゲートとするトランジスタと回路的に分断されている。したがって、nベース領域24のキャリア濃度が上がりず、寄生pnダイオードがオン電流の経路として有効に寄与しない。よって、トレンチIGBT800のオン抵抗の低減が困難である。言い換えれば、コレクタ-エミッタ間電圧(V<sub>ce</sub>)の飽和電圧(V<sub>ce(sat)</sub>)が高くなる。

**【 0 0 4 9 】**

図5は、第2の比較形態の半導体装置の模式平面図である。図6は、第2の比較形態の半導体装置の模式断面図である。図6(a)は図5のCC'断面図である。図6(b)は図6(a)に等価回路を重ね書きした説明図である。

**【 0 0 5 0 】**

第2の比較形態の半導体装置は、半導体層に形成されたトレンチの中にゲート電極を備えるトレンチIGBT900である。トレンチIGBT900は、ダミートレンチゲート電極を有する間引き型IGBTである。

**【 0 0 5 1 】**

トレンチIGBT900は、ダミートレンチゲート電極18が、トレンチゲート電極16と電気的に接続される点で、第1の比較形態のトレンチIGBT800と異なる。

**【 0 0 5 2 】**

トレンチIGBT900がオン状態の際には、トレンチIGBT900のダミートレンチゲート電極18には、トレンチゲート電極16と同様、ゲート電圧(V<sub>g</sub>)が印加される。このため、ダミートレンチ52底部近傍のnベース領域24には、電子の蓄積層が形成される。

**【 0 0 5 3 】**

図6(b)から分かるように、電子の蓄積層が形成されるため、ダミートレンチゲート電極18の間に存在し、コレクタ領域28、nベース領域24、及び、バリア領域26で構成される寄生pnダイオードが、トレンチゲート電極16をゲートとするトランジスタと回路的に接続されている。したがって、nベース領域24のキャリア濃度が高くなり、寄生pnダイオードがオン電流の経路として有効に寄与する。よって、トレンチIGBT900のオン抵抗が低減する。言い換えれば、コレクタ-エミッタ間電圧(V<sub>ce</sub>)の飽和電圧(V<sub>ce(sat)</sub>)が低くなる。n型不純物濃度がnベース領域24よりも高く

10

20

30

40

50

、低抵抗なバリア領域 2 6 を備える場合、特に、オン抵抗が低減する。

#### 【 0 0 5 4 】

一方、トレンチ I G B T 9 0 0 では、ダミートレンチゲート電極 1 8 がトレンチゲート電極 1 6 と電気的に接続されるため、ゲート容量が大きくなる。したがって、ゲート電極の C R 時定数が大きくなる。このため、スイッチング速度が低下するという問題が生じる。

#### 【 0 0 5 5 】

また、ゲート容量が大きくなるため、トレンチ I G B T 9 0 0 の外に設けられる外部ゲート抵抗に対するスイッチング速度の非線形性が増大する。したがって、外部ゲート抵抗によるスイッチング速度の調整が困難であるという問題が生じる。

10

#### 【 0 0 5 6 】

本実施形態のトレンチ I G B T 1 0 0 では、半導体チップの中に設けられるゲート抵抗を、内部ゲート抵抗 3 6 とダミーゲート抵抗 3 8 の 2 つに分離する。そして、ゲートパッド電極 3 4 とトレンチゲート電極 1 6 との間には内部ゲート抵抗 3 6 のみを電気的に接続し、ゲートパッド電極 3 4 とダミートレンチゲート電極 1 8 との間にはダミーゲート抵抗 3 8 のみを電気的に接続する。

#### 【 0 0 5 7 】

ゲート抵抗を、内部ゲート抵抗 3 6 とダミーゲート抵抗 3 8 の 2 つに分離することで、トレンチゲート電極 1 6 に流れる電流と、ダミートレンチゲート電極 1 8 に流れる電流を、内部ゲート抵抗 3 6 とダミーゲート抵抗 3 8 の抵抗値で制御することが可能となる。トレンチゲート電極 1 6 に流れる電流とダミートレンチゲート電極 1 8 に流れる電流の比を、内部ゲート抵抗 3 6 とダミーゲート抵抗 3 8 の抵抗値の比をかえることで制御することが可能となる。例えば、内部ゲート抵抗 3 6 の抵抗値を小さくすることで、トレンチゲート電極 1 6 に流れる電流を増加させることができる。

20

#### 【 0 0 5 8 】

例えば、内部ゲート抵抗 3 6 とダミーゲート抵抗 3 8 の抵抗値を調整し、トレンチゲート電極 1 6 の C R 時定数を、ダミートレンチゲート電極 1 8 の C R 時定数よりも小さくする。これにより、トレンチゲート電極 1 6 の充放電をダミートレンチゲート電極 1 8 の充放電よりも早くすることができる。したがって、トレンチ I G B T 1 0 0 のスイッチング速度を向上させることができる。

30

#### 【 0 0 5 9 】

また、トレンチ I G B T 1 0 0 がオン状態の際には、ダミートレンチゲート電極 1 8 もトレンチゲート電極 1 6 に遅れてゲート電圧 ( V g ) に充電される。したがって、第 2 の比較形態同様、ダミートレンチ 5 2 底部近傍の n ベース領域 2 4 には、電子の蓄積層が形成され、オン抵抗が低減する。

#### 【 0 0 6 0 】

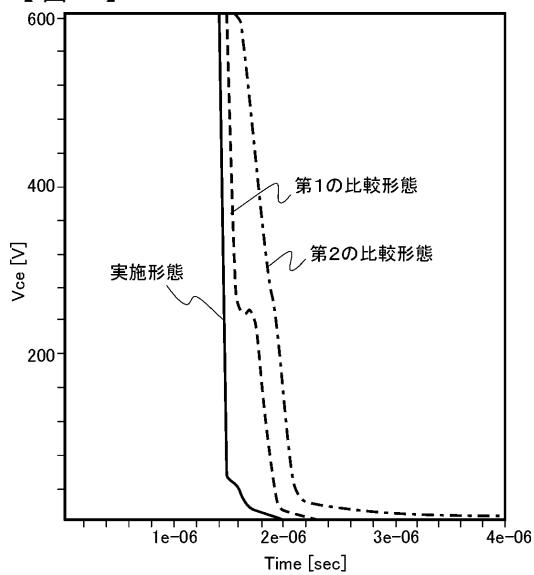

図 7 は、本実施形態の半導体装置の作用及び効果の説明図である。図 7 は、 I G B T のターンオン時のコレクタ - エミッタ間電圧 ( V c e ) の時間変化を示す図である。

#### 【 0 0 6 1 】

第 2 の比較形態のトレンチ I G B T 9 0 0 の場合、第 1 の比較形態のトレンチ I G B T 8 0 0 に比べターンオンの速度が遅いため、コレクタ - エミッタ間電圧の低下速度が遅い。これは、ダミートレンチゲート電極 1 8 がトレンチゲート電極 1 6 に接続され、ダミートレンチゲート電極 1 8 とトレンチゲート電極 1 6 の充電に時間を要するためである。

40

#### 【 0 0 6 2 】

第 1 の比較形態のトレンチ I G B T 8 0 0 では波形に段差が見られる。これは、コレクタ領域 2 8 、 n ベース領域 2 4 、及び、バリア領域 2 6 で構成される寄生 p n ダイオードが、トレンチゲート電極 1 6 をゲートとするトランジスタと回路的に分断されているため、正孔がエミッタ電極 1 2 に抜けやすく、キャリアの蓄積が遅れるためと考えられる。

#### 【 0 0 6 3 】

本実施形態のトレンチ I G B T 1 0 0 では、内部ゲート抵抗 3 6 とダミーゲート抵抗 3

50

8の2つに分離することで、トレンチゲート電極16の充電をダミートレンチゲート電極18の充電よりも早くすることができる。また、コレクタ領域28、nベース領域24、及び、バリア領域26で構成される寄生pnダイオードが、トレンチゲート電極16をゲートとするトランジスタと回路的に接続されているため、キャリアの蓄積の遅れも生じにくい。したがって、ターンオンの速度が第1の比較形態及び第2の比較形態よりも速くなる。

#### 【0064】

なお、本実施形態のトレンチIGBT100のターンオフ時には、トレンチゲート電極16の放電をダミートレンチゲート電極18の放電よりも早くすることができる。したがって、ターンオフの速度も第1の比較形態及び第2の比較形態よりも速くなる。

10

#### 【0065】

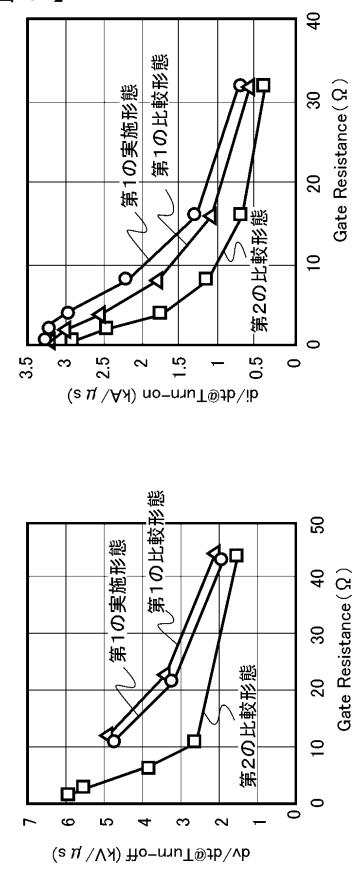

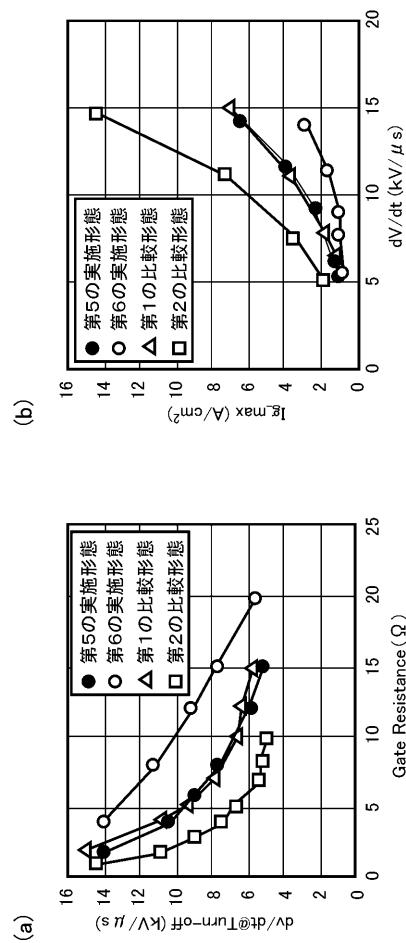

図8は、本実施形態の半導体装置の作用及び効果の説明図である。図8(a)は、IGBTのターンオフ時のゲート抵抗とコレクタ-エミッタ間電圧(Vce)の時間変化率(dV/dt)との関係を示す図である。図8(b)は、IGBTのターンオン時のゲート抵抗とコレクタ-エミッタ間電流の時間変化率(di/dt)との関係を示す図である。ゲート抵抗の抵抗値は、IGBTの外に設けられる外部ゲート抵抗の抵抗値である。コレクタ-エミッタ間電圧(Vce)の時間変化率(dV/dt)、及び、コレクタ電流の時間変化率(di/dt)は、それぞれ、ターンオフ時とターンオン時のスイッチング速度の指標となる。

#### 【0066】

20

図8(a)、(b)から分かるように、第2の比較形態の場合、コレクタ-エミッタ間電圧(Vce)の時間変化率(dV/dt)、及び、コレクタ電流の時間変化率(di/dt)の非線形性が大きくなる。これは、ダミートレンチゲート電極18がトレンチゲート電極16に接続されたため、ゲートミラー容量が大きくなるからと考えられる。非線形性が大きいため、外部ゲート抵抗によるスイッチング速度の制御性が悪化する。

#### 【0067】

本実施形態の場合、第1の比較形態と同程度の線形性が得られる。これは、トレンチゲート電極16の充放電がダミートレンチゲート電極18の充放電よりも早くおこなわれるため、ダミートレンチゲート電極18をトレンチゲート電極16に接続した影響が顕在化しないためと考えられる。したがって、外部ゲート抵抗によるスイッチング速度の制御性が良好となる。

30

#### 【0068】

さらに、第2の比較形態のトレンチIGBT900では、ゲート負性容量によるゲート振動や、ゲート電圧のオーバーシュート/アンダーシュートといった問題が生じやすい。これは、ダミートレンチゲート電極18がトレンチゲート電極16に直接接続されているため、ダミートレンチゲート電極とコレクタ電極で構成される寄生容量がそのままトレンチゲート電極16に伝わるためであると考えられる。

#### 【0069】

本実施形態のトレンチIGBT100によれば、トレンチゲート電極16のCR時定数を、独立に小さくすることが可能となる。したがって、ゲート負性容量によるゲート振動や、ゲート電圧のオーバーシュート/アンダーシュートといった問題が抑制される。

40

#### 【0070】

図1に示すように、トレンチゲート電極16、及び、ダミートレンチゲート電極18が、ゲート電極接続配線42とダミーゲート電極接続配線44との間に位置するように、ゲート電極接続配線42及びダミーゲート電極接続配線44が配置されることが好ましい。言い換えれば、トレンチゲート電極16、及び、ダミートレンチゲート電極18が、ゲート電極接続配線42及びダミーゲート電極接続配線44に挟まれるように配置されることが好ましい。

#### 【0071】

上記配置により、例えば、配線同士の交差等が回避でき、ゲート電極接続配線42及び

50

ダミーゲート電極接続配線 44 の引き回しが容易になる。したがって、例えば、チップ面積の縮小や、製造プロセスの簡略化が実現できる。

#### 【0072】

以上、本実施形態のトレンチ IGBT 100により、オン抵抗が低く、スイッチング速度の速い IGBT が実現できる。また、ゲート電圧の振動やオーバーシュート / アンダーシュートの抑制が可能な IGBT が実現できる。また、チップ面積の縮小や、製造プロセスの簡略化が実現できる。

#### 【0073】

##### (第2の実施形態)

本実施形態の半導体装置は、第1の面と、第1の面と対向する第2の面を有する半導体層と、少なくとも一部が第1の面に接する第1のエミッタ電極と、少なくとも一部が第2の面に接する第1のコレクタ電極と、半導体層の中に設けられ、第1の面に略平行な第1の方向に伸長する第1のトレンチゲート電極と、半導体層の中に設けられ、第1の方向に伸長する第1のダミートレンチゲート電極と、半導体層の中に設けられた p 型の第1の p ベース領域と、半導体層の中に設けられ、第1の p ベース領域と第1の面との間に設けられ、第1のエミッタ電極に電気的に接続された n 型の第1のエミッタ領域と、半導体層の中に設けられ、第1の p ベース領域と、第2の面との間に設けられた n 型の第1の n ベース領域と、半導体層の中に設けられ、第1のコレクタ電極に電気的に接続された p 型の第1のコレクタ領域と、第1のトレンチゲート電極と第1の p ベース領域との間、第1のトレンチゲート電極と第1のエミッタ領域との間、及び、第1のトレンチゲート電極と第1の n ベース領域との間に設けられ、第1の p ベース領域、第1のエミッタ領域、及び、第1の n ベース領域に接する第1のトレンチゲート絶縁膜と、第1のダミートレンチゲート電極と第1の p ベース領域との間、及び、第1のダミートレンチゲート電極と第1の n ベース領域との間に設けられ、第1の p ベース領域、及び、第1の n ベース領域に接する第1のダミートレンチゲート絶縁膜と、少なくとも一部が第1の面に接する第2のエミッタ電極と、少なくとも一部が第2の面に接する第2のコレクタ電極と、半導体層の中に設けられ、第1の面に略平行な第1の方向に伸長する第2のトレンチゲート電極と、半導体層の中に設けられ、第1の方向に伸長する第2のダミートレンチゲート電極と、半導体層の中に設けられた p 型の第2の p ベース領域と、半導体層の中に設けられ、第2の p ベース領域と第1の面との間に設けられ、第2のエミッタ電極に電気的に接続された n 型の第2のエミッタ領域と、半導体層の中に設けられ、第2の p ベース領域と、第2の面との間に設けられた n 型の第2の n ベース領域と、半導体層の中に設けられ第2の n ベース領域と第2の面との間に設けられ、第2のコレクタ電極に電気的に接続された p 型の第2のコレクタ領域と、第2のトレンチゲート電極と第2の p ベース領域との間、第2のトレンチゲート電極と第2のエミッタ領域との間、及び、第2のトレンチゲート電極と第2の n ベース領域との間に設けられ、第2の p ベース領域、第2のエミッタ領域、及び、第2の n ベース領域に接する第2のトレンチゲート絶縁膜と、第2のダミートレンチゲート電極と第2の p ベース領域との間、及び、第2のダミートレンチゲート電極と第2の n ベース領域との間に設けられ、第2の p ベース領域、及び、第2の n ベース領域に接する第2のダミートレンチゲート絶縁膜と、第1のトレンチゲート電極、第1のダミートレンチゲート電極、第2のトレンチゲート電極、及び、第2のダミートレンチゲート電極に電気的に接続されたゲートパッド電極と、ゲートパッド電極と第1のトレンチゲート電極との間に電気的に接続された第1の電気抵抗と、ゲートパッド電極と第1のダミートレンチゲート電極との間に電気的に接続された第2の電気抵抗と、ゲートパッド電極と第2のトレンチゲート電極との間に電気的に接続された第3の電気抵抗と、ゲートパッド電極と第2のダミートレンチゲート電極との間に電気的に接続された第4の電気抵抗と、を備え、第1のトレンチゲート電極の CR 時定数は、第1のダミートレンチゲート電極の CR 時定数よりも小さく、かつ、第2のトレンチゲート電極の CR 時定数は、第2のダミートレンチゲート電極の CR 時定数よりも小さい。

#### 【0074】

10

20

30

40

50

本実施形態の半導体装置は、第1の実施形態の半導体装置の構成と同様の構成を有する第1のセグメントと、第1の実施形態の半導体装置の構成と同様の構成を有する第2のセグメントを備える点で、第1の実施形態の半導体装置と異なっている。以下、第1の実施形態と重複する内容については一部記述を省略する。

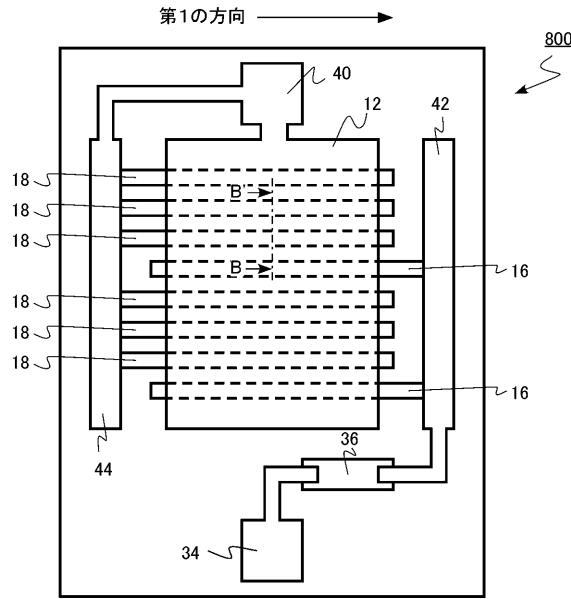

#### 【0075】

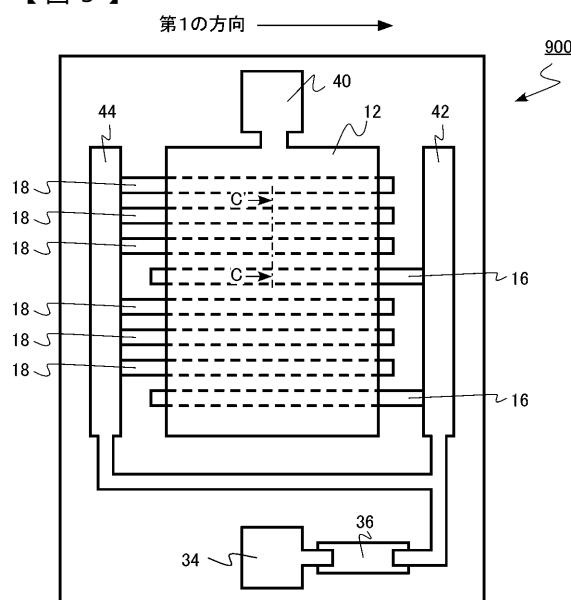

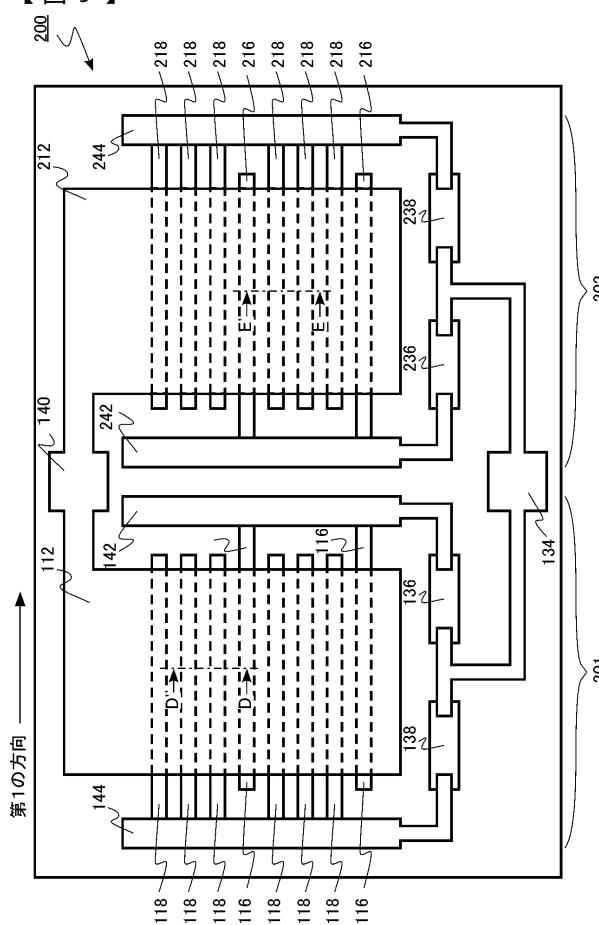

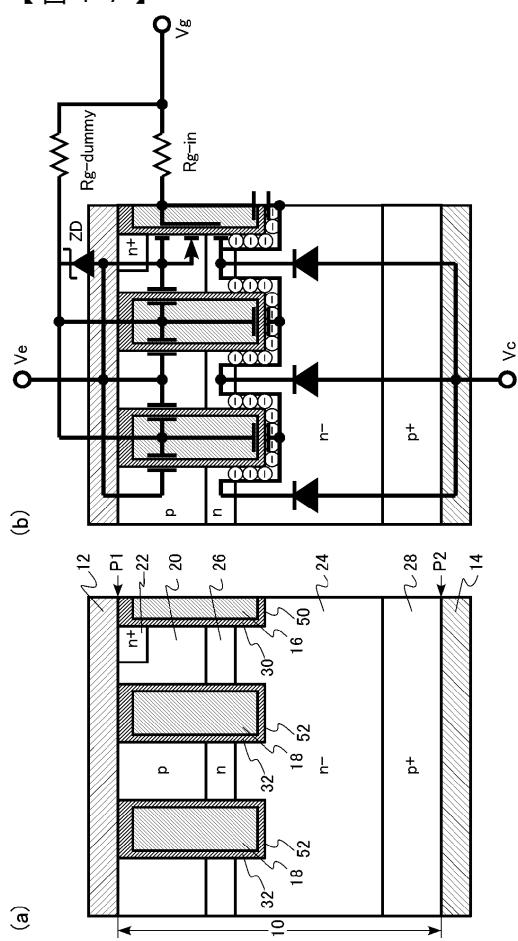

図9は、本実施形態の半導体装置の模式平面図である。図10は、本実施形態の半導体装置の模式断面図である。図10(a)は図9のDD'断面図である。図10(b)は図9のEE'断面図である。図11は、本実施形態の半導体装置の等価回路図である。図11は、図10に等価回路を重ね書きした説明図である。

#### 【0076】

本実施形態の半導体装置は、半導体層に形成されたトレンチの中にゲート電極を備えるトレンチIGBT200である。トレンチIGBT200は、ダミートレンチゲート電極を有する間引き型IGBTである。

#### 【0077】

トレンチIGBT200は、第1のセグメント201、及び、第2のセグメント202を備える。第1のセグメント201、及び、第2のセグメント202は、それぞれ、第1の実施形態のIGBT100と同様の構成を有する。ただし、エミッタパッド電極、コレクタ電極、ゲートパッド電極は、第1のセグメント201、及び、第2のセグメント202の間で共有される。

#### 【0078】

本実施形態のトレンチIGBT200は、半導体層110、ゲートパッド電極134、エミッタパッド電極140を備える。

#### 【0079】

第1のセグメント201は、第1のエミッタ電極112、第1のコレクタ電極114、第1のトレンチゲート電極116、第1のダミートレンチゲート電極118、第1のpベース領域120、第1のエミッタ領域122、第1のnベース領域124、第1のバリア領域126、第1のコレクタ領域128、第1のトレンチゲート絶縁膜130、第1のダミートレンチゲート絶縁膜132、第1の内部ゲート抵抗136(第1の抵抗)、第1のダミーゲート抵抗138(第2の抵抗)、第1のゲート電極接続配線142(第1の接続配線)、第1のダミーゲート電極接続配線144(第2の接続配線)、第1のトレンチ150、第1のダミートレンチ152を備える。

#### 【0080】

第2のセグメント202は、第2のエミッタ電極212、第2のコレクタ電極214、第2のトレンチゲート電極216、第2のダミートレンチゲート電極218、第2のpベース領域220、第2のエミッタ領域222、第2のnベース領域224、第2のバリア領域226、第2のコレクタ領域228、第2のトレンチゲート絶縁膜230、第2のダミートレンチゲート絶縁膜232、第2の内部ゲート抵抗236(第3の抵抗)、第2のダミーゲート抵抗238(第4の抵抗)、第2のゲート電極接続配線242(第3の接続配線)、第2のダミーゲート電極接続配線244(第4の接続配線)、第2のトレンチ250、第2のダミートレンチ252を備える。

#### 【0081】

第1の内部ゲート抵抗136は、半導体層110の上に設けられる。第1の内部ゲート抵抗136は、半導体層110の第1の面P1の側に設けられる。第1の内部ゲート抵抗136は、ゲートパッド電極134と第1のトレンチゲート電極116との間に電気的に接続される。第1の内部ゲート抵抗136は、例えば、多結晶シリコンである。

#### 【0082】

第1のダミーゲート抵抗138は、半導体層110の上に設けられる。第1のダミーゲート抵抗138は、半導体層110の第1の面P1の側に設けられる。第1のダミーゲート抵抗138は、ゲートパッド電極134と第1のダミートレンチゲート電極118との間に電気的に接続される。第1のダミーゲート抵抗138は、例えば、多結晶シリコンで

10

20

30

40

50

ある。

**【0083】**

第1のゲート電極接続配線142は、第1のトレンチゲート電極116と第1の内部ゲート抵抗136との間に電気的に接続される。第1のゲート電極接続配線142は、第1のトレンチゲート電極116の端部に接続される。第1のゲート電極接続配線142は、例えば、図示しないコントクト部で第1のトレンチゲート電極116に接続される。

**【0084】**

第1のダミーゲート電極接続配線144は、第1のダミートレンチゲート電極118と第1のダミーゲート抵抗138との間に電気的に接続される。第1のダミーゲート電極接続配線144は、第1のダミートレンチゲート電極118の端部に接続される。第1のダミーゲート電極接続配線144は、例えば、図示しないコントクト部で第1のダミートレンチゲート電極118に接続される。10

**【0085】**

第1のトレンチゲート電極116、及び、第1のダミートレンチゲート電極118は、第1のゲート電極接続配線142と第1のダミーゲート電極接続配線144との間に位置する。言い換えれば、第1のゲート電極接続配線142は、第1のトレンチゲート電極116、及び、第1のダミートレンチゲート電極118の一方の端部に位置し、第1のダミーゲート電極接続配線144は、第1のトレンチゲート電極116、及び、第1のダミートレンチゲート電極118の他方の端部に位置する。

**【0086】**

第1のトレンチゲート電極116のCR時定数は、第1のダミートレンチゲート電極118のCR時定数よりも小さい。第1のトレンチゲート電極116のCR時定数は、主に、第1のトレンチゲート電極116と半導体層110との間の容量、第1のトレンチゲート電極116の抵抗値、及び、第1の内部ゲート抵抗136の抵抗値で規定される。第1のダミートレンチゲート電極118のCR時定数は、主に、第1のダミートレンチゲート電極118と半導体層110との間の容量、第1のダミートレンチゲート電極118の抵抗値、及び、第1のダミーゲート抵抗138の抵抗値で規定される。20

**【0087】**

第2の内部ゲート抵抗236は、半導体層110の上に設けられる。第2の内部ゲート抵抗236は、半導体層110の第1の面P1の側に設けられる。第2の内部ゲート抵抗236は、ゲートパッド電極134と第2のトレンチゲート電極216との間に電気的に接続される。第2の内部ゲート抵抗236は、例えば、多結晶シリコンである。30

**【0088】**

第2のダミーゲート抵抗238は、半導体層110の上に設けられる。第2のダミーゲート抵抗238は、半導体層110の第1の面P1の側に設けられる。第2のダミーゲート抵抗238は、ゲートパッド電極234と第2のダミートレンチゲート電極218との間に電気的に接続される。第2のダミーゲート抵抗238は、例えば、多結晶シリコンである。

**【0089】**

第2のゲート電極接続配線242は、第2のトレンチゲート電極216と第2の内部ゲート抵抗236との間に電気的に接続される。第2のゲート電極接続配線242は、第2のトレンチゲート電極216の端部に接続される。第2のゲート電極接続配線242は、例えば、図示しないコントクト部で第2のトレンチゲート電極216に接続される。40

**【0090】**

第2のダミーゲート電極接続配線244は、第2のダミートレンチゲート電極218と第2のダミーゲート抵抗238との間に電気的に接続される。第2のダミーゲート電極接続配線244は、第2のダミートレンチゲート電極218の端部に接続される。第2のダミーゲート電極接続配線244は、例えば、図示しないコントクト部で第2のダミートレンチゲート電極218に接続される。

**【0091】**

10

20

30

40

50

第2のトレンチゲート電極216、及び、第2のダミートレンチゲート電極218は、第2のゲート電極接続配線242と第2のダミーゲート電極接続配線244との間に位置する。言い換れば、第2のゲート電極接続配線242は、第2のトレンチゲート電極216、及び、第2のダミートレンチゲート電極218の一方の端部に位置し、第2のダミーゲート電極接続配線244は、第2のトレンチゲート電極216、及び、第2のダミートレンチゲート電極218の他方の端部に位置する。

#### 【0092】

第2のトレンチゲート電極216のCR時定数は、第2のダミートレンチゲート電極218のCR時定数よりも小さい。第2のトレンチゲート電極216のCR時定数は、主に、第2のトレンチゲート電極216と半導体層110との間の容量、第2のトレンチゲート電極216の抵抗値、及び、第2の内部ゲート抵抗236の抵抗値で規定される。第2のダミートレンチゲート電極218のCR時定数は、主に、第2のダミートレンチゲート電極218と半導体層110との間の容量、第2のダミートレンチゲート電極218の抵抗値、及び、第2のダミーゲート抵抗238の抵抗値で規定される。10

#### 【0093】

図11に示すように、本実施形態のトレンチIGBT200は、第1の内部ゲート抵抗( $R_{g-in}(1)$ )と第1のダミーゲート抵抗( $R_{g-dummy}(1)$ )が並列に接続される。第1の内部ゲート抵抗( $R_{g-in}(1)$ )と第1のダミーゲート抵抗( $R_{g-dummy}(1)$ )は、IGBT200の外部で、例えば、外部ゲート抵抗を介してゲートドライバに接続される。ゲートドライバにより、第1のトレンチゲート電極116、及び、第1のダミートレンチゲート電極118にゲート電圧( $V_g$ )が印加される。20

#### 【0094】

第1の内部ゲート抵抗( $R_{g-in}(1)$ )は図9の第1の内部ゲート抵抗136に対応する。第1のダミーゲート抵抗( $R_{g-dummy}(1)$ )は、図9の第1のダミーゲート抵抗138に対応する。

#### 【0095】

また、実施形態のトレンチIGBT200は、第2の内部ゲート抵抗( $R_{g-in}(2)$ )と第2のダミーゲート抵抗( $R_{g-dummy}(2)$ )が並列に接続される。第2の内部ゲート抵抗( $R_{g-in}(2)$ )と第2のダミーゲート抵抗( $R_{g-dummy}(2)$ )は、IGBT200の外部で、例えば、外部ゲート抵抗を介してゲートドライバに接続される。ゲートドライバにより、第2のトレンチゲート電極216、及び、第2のダミートレンチゲート電極218にゲート電圧( $V_g$ )が印加される。30

#### 【0096】

第2の内部ゲート抵抗( $R_{g-in}(2)$ )は図9の第2の内部ゲート抵抗236に対応する。第2のダミーゲート抵抗( $R_{g-dummy}(2)$ )は、図9の第2のダミーゲート抵抗238に対応する。

#### 【0097】

本実施形態のトレンチIGBT200は、第1のセグメント201と第2のセグメント202のそれぞれが、内部ゲート抵抗、及び、ダミーゲート抵抗を備える。第1のセグメント201の第1のトレンチゲート電極116と、第2のセグメント202の第2のトレンチゲート電極216との間には、第1の内部ゲート抵抗136と第2の内部ゲート抵抗236が存在する。また、第1のセグメント201の第1のダミートレンチゲート電極118と、第2のセグメント202の第2のダミートレンチゲート電極218との間には、第1のダミーゲート抵抗138と第2のダミーゲート抵抗238が存在する。40

#### 【0098】

したがって、例えば、一方のセグメントでゲート電圧の振動が生じたとしても、その振動が他方のセグメントに伝搬することが抑制される。よって、ゲート電圧の振動に起因するIGBTの動作不良が低減できる。

#### 【0099】

以上、本実施形態のトレンチIGBT200によれば、第1の実施形態のトレンチIG

B T 1 0 0 と同様、オン抵抗が低く、スイッチング速度の速い I G B T が実現できる。また、ゲート電圧の振動やオーバーシュート / アンダーシュートの抑制が可能な I G B T が実現できる。また、チップ面積の縮小や、製造プロセスの簡略化が実現できる。さらに、ゲート電圧の振動に起因する I G B T の不良が低減できる。

#### 【 0 1 0 0 】

##### ( 第 3 の実施形態 )

本実施形態の半導体装置は、第 2 の電気抵抗とダミートレンチゲート電極との間に電気的に接続された第 3 の電気抵抗と、第 3 の電気抵抗とダミートレンチゲート電極との間に電気的に接続された第 4 の電気抵抗と、第 2 の電気抵抗と第 3 の電気抵抗との間に電気的に接続された第 2 のゲート電極パッドと、第 3 の電気抵抗とダミートレンチゲート電極との間に電気的に接続された第 3 のゲート電極パッドと、を更に備える点で、第 1 の実施形態と異なる。以下、第 1 の実施形態と重複する内容については一部記述を省略する。

10

#### 【 0 1 0 1 】

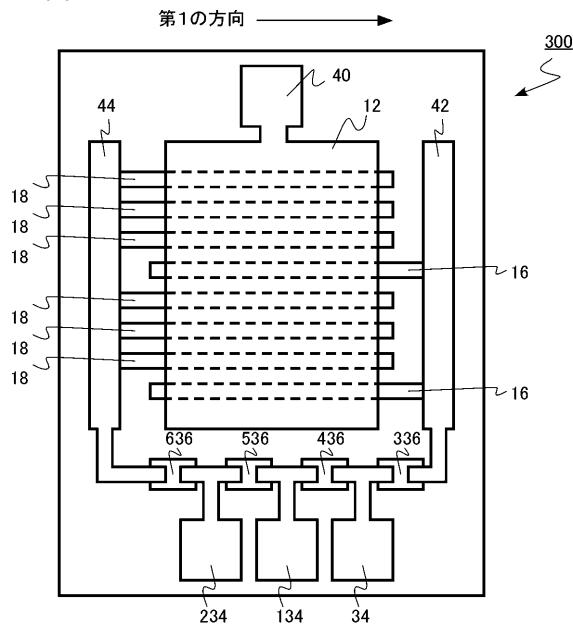

図 1 2 は、本実施形態の半導体装置の模式平面図である。

#### 【 0 1 0 2 】

本実施形態の半導体装置は、半導体層に形成されたトレンチの中にゲート電極を備えるトレンチ I G B T 3 0 0 である。トレンチ I G B T 3 0 0 は、ダミートレンチゲート電極を有する間引き型 I G B T である。

#### 【 0 1 0 3 】

本実施形態のトレンチ I G B T 3 0 0 は、エミッタ電極 1 2 、トレンチゲート電極 1 6 、ダミートレンチゲート電極 1 8 、ゲートパッド電極 3 4 ( 第 1 のゲートパッド電極 ) 、ゲートパッド電極 1 3 4 ( 第 2 のゲートパッド電極 ) 、ゲートパッド電極 2 3 4 ( 第 3 のゲートパッド電極 ) 、第 1 の内部ゲート抵抗 3 3 6 ( 第 1 の電気抵抗 ) 、第 2 の内部ゲート抵抗 4 3 6 ( 第 2 の電気抵抗 ) 、第 3 の内部ゲート抵抗 5 3 6 ( 第 3 の電気抵抗 ) 、第 4 の内部ゲート抵抗 6 3 6 ( 第 4 の電気抵抗 ) 、エミッタパッド電極 4 0 、ゲート電極接続配線 4 2 ( 第 1 の接続配線 ) 、ダミーゲート電極接続配線 4 4 ( 第 2 の接続配線 ) を備える。

20

#### 【 0 1 0 4 】

第 1 の内部ゲート抵抗 3 3 6 は、ゲートパッド電極 3 4 とトレンチゲート電極 1 6 との間に電気的に接続される。第 2 の内部ゲート抵抗 4 3 6 ( 第 2 の電気抵抗 ) は、ゲートパッド電極 3 4 とダミートレンチゲート電極 1 8 との間に電気的に接続される。第 3 の内部ゲート抵抗 5 3 6 ( 第 3 の電気抵抗 ) は、第 2 の内部ゲート抵抗 4 3 6 ( 第 2 の電気抵抗 ) とダミートレンチゲート電極 1 8 との間に電気的に接続される。第 4 の内部ゲート抵抗 6 3 6 ( 第 4 の電気抵抗 ) は、第 3 の内部ゲート抵抗 5 3 6 ( 第 3 の電気抵抗 ) とダミートレンチゲート電極 1 8 との間に電気的に接続される。

30

#### 【 0 1 0 5 】

ゲートパッド電極 1 3 4 は、第 2 の内部ゲート抵抗 4 3 6 ( 第 2 の電気抵抗 ) と第 3 の内部ゲート抵抗 5 3 6 との間に電気的に接続される。ゲートパッド電極 2 3 4 は、第 3 の内部ゲート抵抗 5 3 6 と第 4 の内部ゲート抵抗 6 3 6 との間に電気的に接続される。

#### 【 0 1 0 6 】

40

本実施形態の I G B T 3 0 0 によれば、3 個のゲートパッド電極 3 4 、 1 3 4 、 2 3 4 の中から所望のゲートパッド電極を選択してゲート電圧を印加することにより、トレンチゲート電極 1 6 に接続される内部ゲート抵抗 ( R g - i n ) と、ダミートレンチゲート電極 1 8 に接続されるダミーゲート抵抗 ( R g - d u m m y ) の比を変化させることが可能である。言い換えれば、トレンチゲート電極 1 6 の C R 時定数と、ダミートレンチゲート電極 1 8 の C R 時定数の比を変化させることができる。したがって、例えば、デバイス製造後に、 I G B T のアプリケーションに応じたスイッチング速度の調整が可能となる。

#### 【 0 1 0 7 】

以上、本実施形態のトレンチ I G B T 3 0 0 によれば、第 1 の実施形態の I G B T 1 0

50

0と同様、オン抵抗が低く、スイッチング速度の速いIGBTが実現できる。また、ゲート電圧の振動やオーバーシュート／アンダーシュートの抑制が可能なIGBTが実現できる。また、チップ面積の縮小や、製造プロセスの簡略化が実現できる。さらに、デバイス製造後のスイッチング速度の調整が可能となる。

#### 【0108】

##### (第4の実施形態)

本実施形態の半導体装置は、第1の面と、第1の面と対向する第2の面を有する半導体層と、少なくとも一部が第1の面に接するエミッタ電極と、少なくとも一部が第2の面に接するコレクタ電極と、半導体層の中に設けられ、第1の面に略平行な第1の方向に伸長する上部トレンチゲート電極と、半導体層の中に設けられ、上部トレンチゲート電極と第2の面との間に設けられ、第1の方向に伸長し、上部トレンチゲート電極と電気的に分離される下部トレンチゲート電極と、半導体層の中に設けられ、第1の方向に伸長する上部ダミートレンチゲート電極と、半導体層の中に設けられ、上部ダミートレンチゲート電極と第2の面との間に設けられ、第1の方向に伸長し、上部ダミートレンチゲート電極と電気的に分離される下部ダミートレンチゲート電極と、半導体層の中に設けられたp型のpベース領域と、半導体層の中に設けられ、pベース領域と第1の面との間に設けられ、エミッタ電極に電気的に接続されたn型のエミッタ領域と、半導体層の中に設けられ、pベース領域と、第2の面との間に設けられたn型のnベース領域と、半導体層の中に設けられ、nベース領域と第2の面との間に設けられ、コレクタ電極に電気的に接続されたp型のコレクタ領域と、上部トレンチゲート電極とpベース領域との間、上部トレンチゲート電極とエミッタ領域との間、及び、下部トレンチゲート電極とnベース領域との間に設けられ、pベース領域、エミッタ領域、及び、nベース領域に接するトレンチゲート絶縁膜と、上部ダミートレンチゲート電極とpベース領域との間、及び、下部ダミートレンチゲート電極とnベース領域との間に設けられ、pベース領域、及び、nベース領域に接するダミートレンチゲート絶縁膜と、上部トレンチゲート電極、下部トレンチゲート電極、及び、下部ダミートレンチゲート電極に電気的に接続された第1のゲートパッド電極と、第1のゲートパッド電極と上部トレンチゲート電極との間に電気的に接続された第1の電気抵抗と、第1のゲートパッド電極と下部トレンチゲート電極との間、及び、第1のゲートパッド電極と下部ダミートレンチゲート電極との間に電気的に接続された第2の電気抵抗と、を備え、上部トレンチゲート電極のCR時定数は、下部ダミートレンチゲート電極のCR時定数よりも小さい。

10

20

30

40

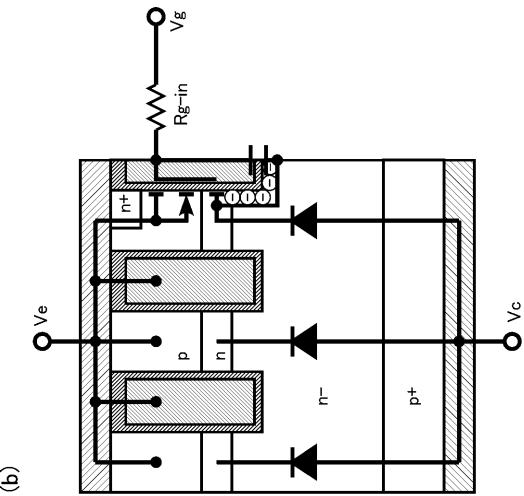

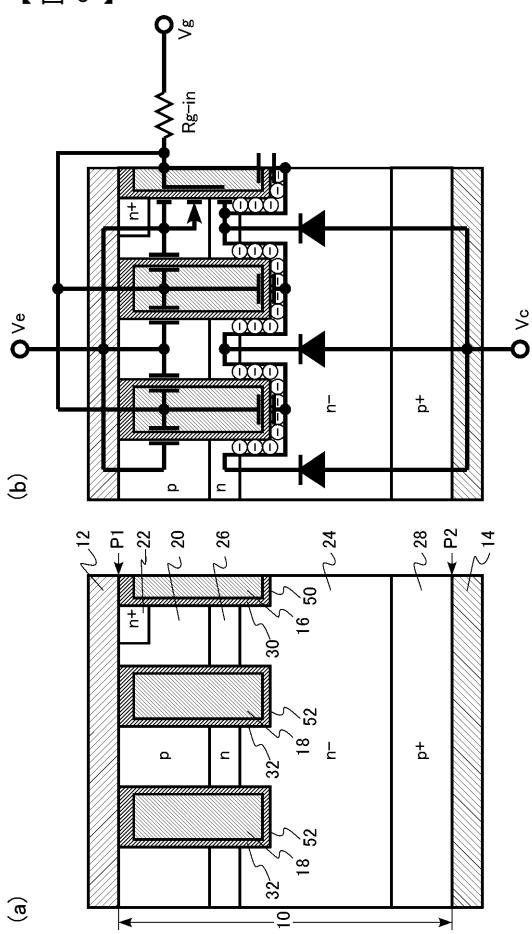

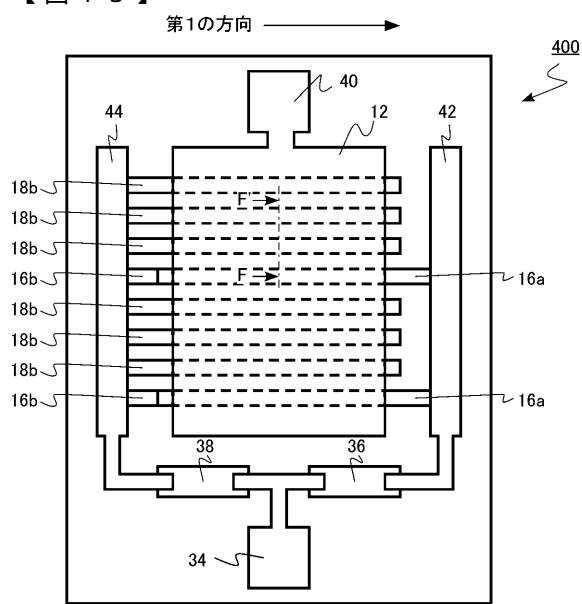

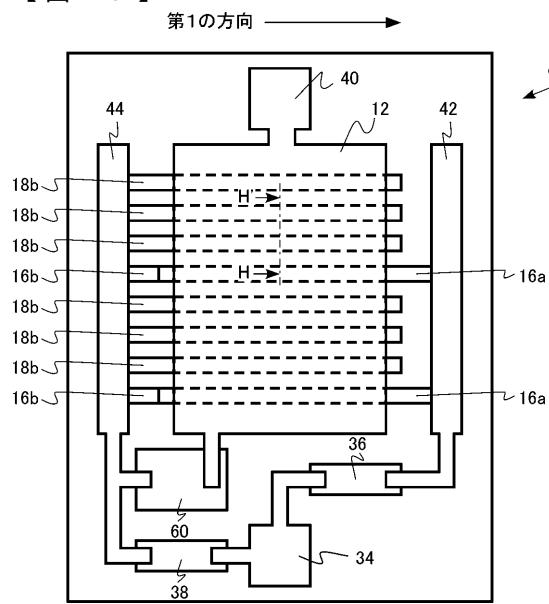

#### 【0109】

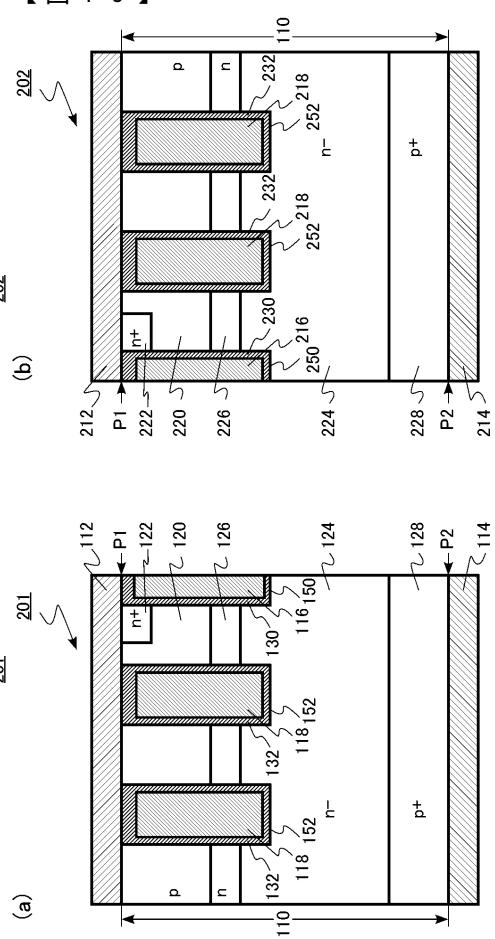

図13は、本実施形態の半導体装置の模式平面図である。図14は、本実施形態の半導体装置の模式断面図である。図14(a)は図13のFF'断面図である。図14(b)は図14(a)に等価回路を重ね書きした説明図である。

#### 【0110】

本実施形態の半導体装置は、半導体層に形成されたトレンチの中にゲート電極を備えるトレンチIGBT400である。トレンチIGBT400は、ダミートレンチゲート電極を有する間引き型IGBTである。トレンチIGBT400は、一つのトレンチ内に上下に分離したゲート電極を有する、ダブルゲート電極構造のIGBTである。

#### 【0111】

本実施形態のトレンチIGBT400は、半導体層10、エミッタ電極12、コレクタ電極14、上部トレンチゲート電極16a、下部トレンチゲート電極16b、上部ダミートレンチゲート電極18a、下部ダミートレンチゲート電極18c、pベース領域20、エミッタ領域22、nベース領域24、バリア領域26(n型半導体領域)、コレクタ領域28、トレンチゲート絶縁膜30、ダミートレンチゲート絶縁膜32、ゲートパッド電極34(第1のゲートパッド電極)、内部ゲート抵抗36(第1の電気抵抗)、ダミゲート抵抗38(第2の電気抵抗)、エミッタパッド電極40、ゲート電極接続配線42(第1の接続配線)、ダミゲート電極接続配線44(第2の接続配線)、トレンチ50、ダミートレンチ52を備える。

50

## 【0112】

半導体層10は、第1の面P1と、第1の面P1に対向する第2の面P2とを有する。半導体層10は、例えば、単結晶シリコンである。半導体層10の膜厚は、例えば、50μm以上700μm以下である。

## 【0113】

エミッタ電極12の少なくとも一部は半導体層10の第1の面P1に接する。例えば、エミッタ電極12の少なくとも一部は、上部ダミートレンチゲート電極18aに接する。エミッタ電極12は、例えば、金属である。エミッタ電極12には、エミッタ電圧(Ve)が印加される。エミッタ電圧は、例えば、0Vである。

## 【0114】

コレクタ電極14の少なくとも一部は半導体層10の第2の面P2に接する。コレクタ電極14は、例えば、金属である。コレクタ電極14には、コレクタ電圧(Vc)が印加される。コレクタ電圧は、例えば、200V以上6500V以下である。

## 【0115】

上部トレンチゲート電極16a、及び、下部トレンチゲート電極16bは、半導体層10の中に複数設けられる。上部トレンチゲート電極16a、及び、下部トレンチゲート電極16bは、半導体層10に形成されたトレンチ50の中に設けられる。上部トレンチゲート電極16a、及び、下部トレンチゲート電極16bは、第1の面P1に略平行な第1の方向に伸長する。下部トレンチゲート電極16bは、上部トレンチゲート電極16aと第2の面P2との間に設けられる。上部トレンチゲート電極16aと下部トレンチゲート電極16bは、電気的に分離される。上部トレンチゲート電極16aと下部トレンチゲート電極16bとの間には、絶縁膜が設けられる。上部トレンチゲート電極16a、及び、下部トレンチゲート電極16bは、例えば、n型不純物又はp型不純物を含む多結晶シリコンである。

## 【0116】

上部ダミートレンチゲート電極18a、及び、下部ダミートレンチゲート電極18bは、半導体層10の中に複数設けられる。上部ダミートレンチゲート電極18a、及び、下部ダミートレンチゲート電極18bは、半導体層10に形成されたダミートレンチ52の中に設けられる。上部ダミートレンチゲート電極18a、及び、下部ダミートレンチゲート電極18bは、第1の面P1に略平行な第1の方向に伸長する。下部ダミートレンチゲート電極18bは、上部ダミートレンチゲート電極18aと第2の面P2との間に設けられる。上部ダミートレンチゲート電極18aと下部ダミートレンチゲート電極18bは、電気的に分離される。上部ダミートレンチゲート電極18aと下部ダミートレンチゲート電極18bとの間には、絶縁膜が設けられる。上部ダミートレンチゲート電極18aは、2つの上部トレンチゲート電極16aの間に、上部トレンチゲート電極16aに平行に設けられる。下部ダミートレンチゲート電極18bは、2つの下部トレンチゲート電極16bの間に、下部トレンチゲート電極16bに平行に設けられる。上部ダミートレンチゲート電極18a、及び、下部ダミートレンチゲート電極18bは、例えば、n型不純物又はp型不純物を含む多結晶シリコンである。

## 【0117】

上部ダミートレンチゲート電極18aは、例えば、エミッタ電極12に電気的に接続される。上部ダミートレンチゲート電極18aは、例えば、エミッタ電極12に接する。上部ダミートレンチゲート電極18aは、例えば、フローティングとすることも可能である。

## 【0118】

pベース領域20は、半導体層10の中に設けられる。pベース領域20は、p型の半導体領域である。pベース領域20のトレンチゲート絶縁膜30に接する領域は、IGBT400のチャネル領域として機能する。

## 【0119】

エミッタ領域22は、半導体層10の中に設けられる。エミッタ領域22は、pベース

10

20

30

30

40

50

領域 2 0 と第 1 の面 P 1 との間に設けられ、トレンチゲート絶縁膜 3 0 と接している。エミッタ領域 2 2 は、n 型の半導体領域である。エミッタ領域 2 2 は、2 つのダミートレンチ 5 2 の間には設けられない。エミッタ領域 2 2 は、エミッタ電極 1 2 に電気的に接続される。

#### 【 0 1 2 0 】

n ベース領域 2 4 は、半導体層 1 0 の中に設けられる。n ベース領域 2 4 は、p ベース領域 2 0 と第 2 の面との間に設けられる。n ベース領域 2 4 は、n 型の半導体領域である。

#### 【 0 1 2 1 】

バリア領域 2 6 は、半導体層 1 0 の中に設けられる。バリア領域 2 6 は、p ベース領域 2 0 とn ベース領域 2 4 との間に設けられる。バリア領域 2 6 は、n 型の半導体領域である。バリア領域 2 6 の n 型不純物濃度は、n ベース領域 2 4 の n 型不純物濃度よりも高い。バリア領域 2 6 の n 型不純物濃度は、エミッタ領域 2 2 の n 型不純物濃度よりも低い。バリア領域 2 6 はトレンチ I G B T 4 0 0 のオン抵抗を低減する機能を有する。

#### 【 0 1 2 2 】

第 1 の面 P 1 から n ベース領域 2 4 とバリア領域 2 6 の界面までの距離は、第 1 の面 P 1 から下部トレンチゲート電極 1 6 b までの距離よりも大きい。また、第 1 の面 P 1 から n ベース領域 2 4 とバリア領域 2 6 の界面までの距離は、第 1 の面 P 1 から下部ダミートレンチゲート電極 1 8 b までの距離よりも大きい。

#### 【 0 1 2 3 】

コレクタ領域 2 8 は、半導体層 1 0 の中に設けられる。コレクタ領域 2 8 は、n ベース領域 2 4 と第 2 の面 P 2 との間に設けられる。コレクタ領域 2 8 は、p 型の半導体領域である。コレクタ領域 2 8 の p 型不純物濃度は、p ベース領域 2 0 の p 型不純物濃度よりも高い。コレクタ領域 2 8 は、コレクタ電極 1 4 に電気的に接続される。

#### 【 0 1 2 4 】

なお、n ベース領域 2 4 とコレクタ領域 2 8 との間に、n ベース領域 2 4 よりも n 型不純物濃度の高いバッファ領域を設けることも可能である。バッファ領域を設けることにより、トレンチ I G B T 4 0 0 がオフ状態の際に、空乏層の伸びを抑制することが可能となる。

#### 【 0 1 2 5 】

トレンチゲート絶縁膜 3 0 は、上部トレンチゲート電極 1 6 a と p ベース領域 2 0 との間、上部トレンチゲート電極 1 6 a とエミッタ領域 2 2 との間、上部トレンチゲート電極 1 6 a とバリア領域 2 6 との間、及び、下部トレンチゲート電極 1 6 b と n ベース領域 2 4 との間に設けられる。トレンチゲート絶縁膜 3 0 は、トレンチ 5 0 の中に設けられる。トレンチゲート絶縁膜 3 0 は、p ベース領域 2 0 、エミッタ領域 2 2 、バリア領域 2 6 、及び、n ベース領域 2 4 に接する。トレンチゲート絶縁膜 3 0 は、例えば、酸化シリコンである。

#### 【 0 1 2 6 】

ダミートレンチゲート絶縁膜 3 2 は、上部ダミートレンチゲート電極 1 8 a と p ベース領域 2 0 との間、上部ダミートレンチゲート電極 1 8 a とバリア領域 2 6 との間、及び、下部ダミートレンチゲート電極 1 8 b と n ベース領域 2 4 との間に設けられる。ダミートレンチゲート絶縁膜 3 2 は、ダミートレンチ 5 2 の中に設けられる。ダミートレンチゲート絶縁膜 3 2 は、p ベース領域 2 0 、バリア領域 2 6 、及び、n ベース領域 2 4 に接する。ダミートレンチゲート絶縁膜 3 2 は、エミッタ領域 2 2 とは接しない。ダミートレンチゲート絶縁膜 3 2 は、例えば、酸化シリコンである。

#### 【 0 1 2 7 】

ゲートパッド電極 3 4 は、半導体層 1 0 の上に設けられる。ゲートパッド電極 3 4 は、半導体層 1 0 の第 1 の面 P 1 の側に設けられる。ゲートパッド電極 3 4 は、上部トレンチゲート電極 1 6 a 、下部トレンチゲート電極 1 6 b 、及び、下部ダミートレンチゲート電極 1 8 b に電気的に接続される。ゲートパッド電極 3 4 は、例えば、金属である。

10

20

30

40

50

## 【0128】

内部ゲート抵抗36は、半導体層10の上に設けられる。内部ゲート抵抗36は、半導体層10の第1の面P1の側に設けられる。内部ゲート抵抗36は、ゲートパッド電極34と上部トレンチゲート電極16aとの間に電気的に接続される。

## 【0129】

内部ゲート抵抗36は、例えば、半導体である。内部ゲート抵抗36は、例えば、導電性不純物を含む多結晶シリコンである。内部ゲート抵抗36は、例えば、ゲート電極接続配線42よりも比抵抗の高い材料で形成される。

## 【0130】

ダミーゲート抵抗38は、半導体層10の上に設けられる。ダミーゲート抵抗38は、半導体層10の第1の面P1の側に設けられる。ダミーゲート抵抗38は、ゲートパッド電極34と下部トレンチゲート電極16bとの間、及び、下部ダミートレンチゲート電極18bとの間に電気的に接続される。10

## 【0131】

ダミーゲート抵抗38は、例えば、半導体である。ダミーゲート抵抗38は、例えば、導電性不純物を含む多結晶シリコンである。ダミーゲート抵抗38は、例えば、ダミーゲート電極接続配線44よりも比抵抗の高い材料で形成される。

## 【0132】

ゲート電極接続配線42は、上部トレンチゲート電極16aと内部ゲート抵抗36との間に電気的に接続される。ゲート電極接続配線42は、上部トレンチゲート電極16aの端部に接続される。ゲート電極接続配線42は、例えば、図示しないコンタクト部で上部トレンチゲート電極16aに接続される。ゲート電極接続配線42は、例えば、金属である。20

## 【0133】

ダミーゲート電極接続配線44は、下部トレンチゲート電極16b、及び、下部ダミートレンチゲート電極18bと、ダミーゲート抵抗38との間に電気的に接続される。ダミーゲート電極接続配線44は、下部トレンチゲート電極16b、及び、下部ダミートレンチゲート電極18bの端部に接続される。ダミーゲート電極接続配線44は、例えば、図示しないコンタクト部で下部トレンチゲート電極16b、及び、下部ダミートレンチゲート電極18bに接続される。ダミーゲート電極接続配線44は、例えば、金属である。30

## 【0134】

上部トレンチゲート電極16a、及び、下部ダミートレンチゲート電極18bは、ゲート電極接続配線42とダミーゲート電極接続配線44との間に位置する。言い換えれば、ゲート電極接続配線42は、上部トレンチゲート電極16a、及び、下部ダミートレンチゲート電極18bの一方の端部に位置し、ダミーゲート電極接続配線44は、上部トレンチゲート電極16a、及び、下部ダミートレンチゲート電極18bの他方の端部に位置する。

## 【0135】

上部トレンチゲート電極16aのCR時定数は、下部ダミートレンチゲート電極18bのCR時定数よりも小さい。上部トレンチゲート電極16aのCR時定数は、主に、上部トレンチゲート電極16aと半導体層10との間の容量、上部トレンチゲート電極16aの抵抗値、及び、内部ゲート抵抗36の抵抗値で規定される。下部ダミートレンチゲート電極18bのCR時定数は、主に、下部ダミートレンチゲート電極18bと半導体層10との間の容量、下部ダミートレンチゲート電極18bの抵抗値、及び、ダミーゲート抵抗38の抵抗値で規定される。40

## 【0136】

また、上部トレンチゲート電極16aのCR時定数は、下部トレンチゲート電極16bのCR時定数よりも小さい。

## 【0137】

エミッタパッド電極40は、半導体層10の上に設けられる。エミッタパッド電極4050

は、半導体層 10 の第 1 の面 P1 の側に設けられる。エミッタパッド電極 40 は、エミッタ電極 12 に電気的に接続される。

#### 【0138】

IGBT400 は、エミッタパッド電極 40 、コレクタ電極 14 、及び、ゲートパッド電極 34 の 3 つの電極を端子とする 3 端子デバイスである。

#### 【0139】

図 14 (b) に示すように、本実施形態のトレンチ IGBT400 は、内部ゲート抵抗 (Rg-in) とダミーゲート抵抗 (Rg-dummy) が並列に接続される。内部ゲート抵抗 (Rg-in) とダミーゲート抵抗 (Rg-dummy) は、IGBT400 の外部で、例えば、外部ゲート抵抗を介してゲートドライバに接続される。ゲートドライバにより、上部トレンチゲート電極 16a 、下部トレンチゲート電極 16b 、及び、下部ダミートレンチゲート電極 18b にゲート電圧 (Vg) が印加される。

10

#### 【0140】

内部ゲート抵抗 (Rg-in) は図 13 の内部ゲート抵抗 36 に対応する。ダミーゲート抵抗 (Rg-dummy) は、図 13 のダミーゲート抵抗 38 に対応する。

#### 【0141】

p ベース領域 20 は、例えば、エミッタ電極 12 に電気的に接続される。p ベース領域 20 は、例えば、グラウンド電位に固定される。ダミートレンチ 52 に挟まれる p ベース領域 20 は、例えば、フローティングであっても構わない。

#### 【0142】

以下、本実施形態のトレンチ IGBT400 の作用及び効果について説明する。

20

#### 【0143】

本実施形態のトレンチ IGBT400 では、一つのトレンチ 50 内に上部トレンチゲート電極 16a と下部トレンチゲート電極 16b とを有するダブルゲート電極構造を有する。

。

#### 【0144】

例えば、内部ゲート抵抗 36 とダミーゲート抵抗 38 の抵抗値を調整し、上部トレンチゲート電極 16a の CR 時定数を、下部トレンチゲート電極 16b の CR 時定数よりも小さくする。これにより、上部トレンチゲート電極 16a の充放電を下部トレンチゲート電極 16b の充放電よりも早くすることができる。したがって、トレンチ IGBT400 のスイッチング速度を向上させることができる。

30

#### 【0145】

トレンチ IGBT400 がオン状態の際には、下部トレンチゲート電極 16b も上部トレンチゲート電極 16a に遅れてゲート電圧 (Vg) に充電される。したがって、トレンチ 50 底部近傍の n ベース領域 24 には、電子の蓄積層が形成され、オン抵抗が低減する。

。

#### 【0146】

また、第 1 の実施形態のトレンチ IGBT100 と同様、例えば、内部ゲート抵抗 36 とダミーゲート抵抗 38 の抵抗値を調整し、上部トレンチゲート電極 16a の CR 時定数を、下部ダミートレンチゲート電極 18b の CR 時定数よりも小さくする。これにより、上部トレンチゲート電極 16a の充放電を下部ダミートレンチゲート電極 18b の充放電よりも早くすることができる。したがって、トレンチ IGBT400 のスイッチング速度を向上させることができる。

40

#### 【0147】

また、第 1 の実施形態のトレンチ IGBT100 と同様、トレンチ IGBT400 がオン状態の際には、下部ダミートレンチゲート電極 18b も上部トレンチゲート電極 16a に遅れてゲート電圧 (Vg) に充電される。したがってダミートレンチ 52 底部近傍の n ベース領域 24 には、電子の蓄積層が形成され、オン抵抗が低減する。

#### 【0148】

さらに、上部ダミートレンチゲート電極 18a は、下部ダミートレンチゲート電極 18

50

bと電気的に分離される。したがって、第1の実施形態のトレンチIGBT100の場合と比較して、上部ダミートレンチゲート電極18aの分だけ、ゲート容量が小さくなる。したがって、例えば、ゲートドライバの駆動能力を小さくすることができ、ゲートドライバのサイズを小さくすることが可能となる。

#### 【0149】

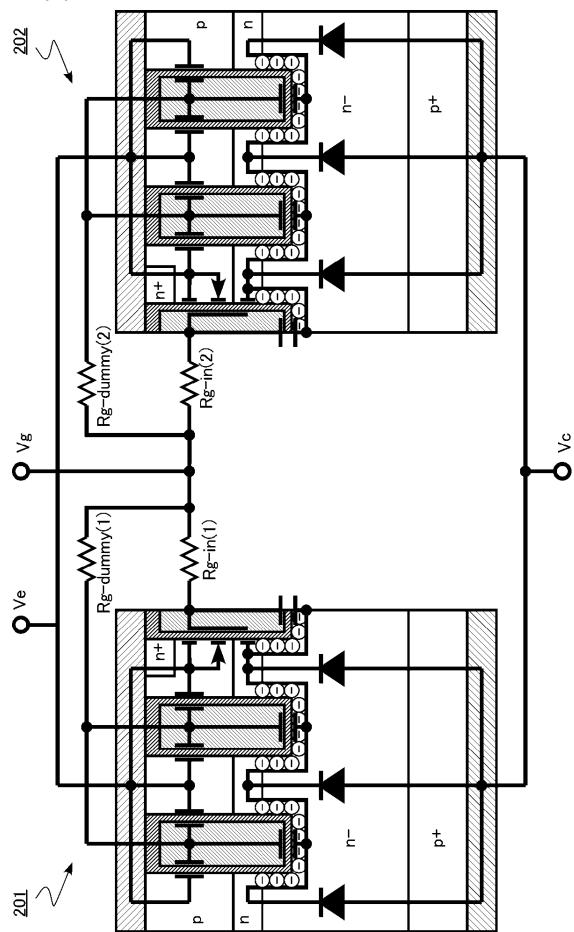

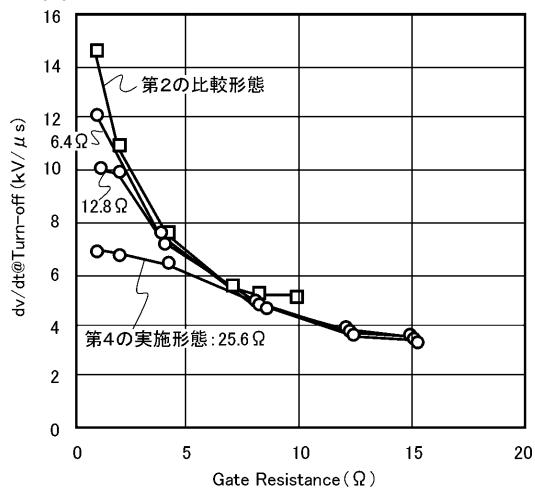

図15は、本実施形態の半導体装置の作用及び効果の説明図である。図15は、IGBTのターンオフ時の、ゲート抵抗とコレクタ-エミッタ間電圧(Vce)の時間変化率(dV/dt)との関係を示す図である。ゲート抵抗の抵抗値は、IGBTの外に設けられる外部ゲート抵抗の抵抗値である。コレクタ-エミッタ間電圧(Vce)の時間変化率(dV/dt)は、ターンオフ時のスイッチング速度の指標となる。

10

#### 【0150】

図15には、比較のために、第1の実施形態で説明した第2の比較形態の構造の場合も示す。また、本実施形態(第4の実施形態)について、ダミーゲート抵抗(Rg-dummmy)の値が、6.4、12.8、25.6の場合を示している。

#### 【0151】

本実施形態では、コレクタ・ゲート間の帰還容量が、全てダミーゲート抵抗(Rg-dummmy)を流れる電流(Ig-dummmy)で充放電される。したがって、時間変化率(dV/dt)を、ダミーゲート抵抗(Rg-dummmy)の値で調整することが可能となる。

#### 【0152】

20

図15から分かるように、ダミーゲート抵抗(Rg-dummmy)の値を高くすることで、高い線形性が得られる。したがって、ダミーゲート抵抗(Rg-dummmy)の値を高くすることで、外部ゲート抵抗によるスイッチング速度の制御性が良好となる。

#### 【0153】

##### (第5の実施形態)

本実施形態の半導体装置は、アノードとカソードを有し、アノードがエミッタ電極に電気的に接続され、カソードが第2の電気抵抗とダミートレンチゲート電極との間に接続されたツェナーダイオードを、更に備える点で、第1の実施形態と異なる。以下、第1の実施形態と重複する内容については一部記述を省略する。

#### 【0154】

30

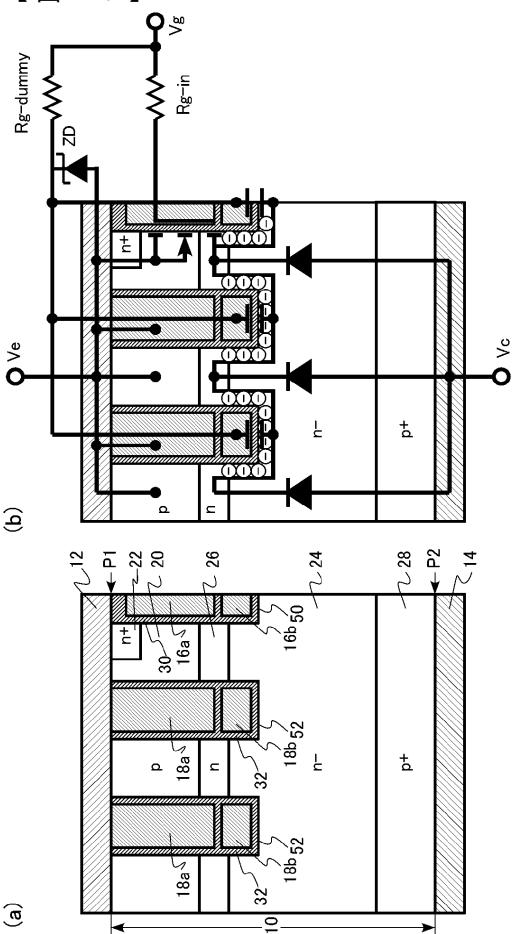

図16は、本実施形態の半導体装置の模式平面図である。図17は、本実施形態の半導体装置の模式断面図である。図17(a)は図16のGG'断面図である。図17(b)は図17(a)に等価回路を重ね書きした説明図である。

#### 【0155】

本実施形態の半導体装置は、半導体層に形成されたトレンチの中にゲート電極を備えるトレンチIGBT500である。トレンチIGBT500は、ダミートレンチゲート電極を有する間引き型IGBTである。

#### 【0156】

トレンチIGBT500は、アノードとカソードを有するツェナーダイオード60(図17(b)のZD)を備える。アノードはエミッタ電極12に電気的に接続される。カソードはダミーゲート抵抗38(第2の電気抵抗)とダミートレンチゲート電極18との間に接続される。ツェナーダイオード60は、例えば、多結晶シリコンを用いて形成される。

40

#### 【0157】

本実施形態では、コレクタ・ゲート間の帰還容量を、ツェナーダイオード60を設けることで、エミッタ電極12にバイパスする。したがって、ツェナーダイオード60が無い場合と比較して、小さなゲート電流で帰還容量を充放電できる。よって、ターンオフ時のスイッチング速度が向上する。

#### 【0158】

ツェナーダイオード60をトレンチIGBT500のターンオフ時に、オン動作させる

50

観点からは、ダミーゲート抵抗 ( $R_{g-dummy}$ ) の値を高くすることが好ましい。ダミーゲート抵抗 ( $R_{g-dummy}$ ) の値を高くすることにより、ダミートレンチゲート電極 18 の電圧が、コレクタ電圧に引っ張られることで、ツェナーダイオード 60 のツェナー電圧よりも高くなり、ツェナーダイオード 60 がオン動作する。

#### 【0159】

ツェナーダイオード 60 のツェナー電圧は、トレンチ IGBT 500 のオン動作時にゲートパッド電極 34 (第1のゲートパッド電極) に印加されるゲートオン電圧よりも高い。ツェナーダイオード 60 のツェナー電圧をトレンチ IGBT 500 のオン動作時のゲートオン電圧よりも高くすることで、トレンチ IGBT 500 のオン動作時にツェナーダイオード 60 がオン動作してトレンチ IGBT 500 の誤動作が生じることを防ぐ。

10

#### 【0160】

図 18 は、本実施形態の半導体装置の作用及び効果の説明図である。図 18 は、IGBT のターンオフ時の、ゲート抵抗とコレクタ - エミッタ間電圧 ( $V_{ce}$ ) の時間変化率 ( $dV/dt$ ) との関係を示す図である。ゲート抵抗の抵抗値は、IGBT の外に設けられる外部ゲート抵抗の抵抗値である。コレクタ - エミッタ間電圧 ( $V_{ce}$ ) の時間変化率 ( $dV/dt$ ) は、ターンオフ時のスイッチング速度の指標となる。

#### 【0161】

図 18 には、比較のために、第1の実施形態の IGBT 100 構造、第1の実施形態で説明した第1の比較形態の IGBT 800 及び第2の比較形態の IGBT 900 の場合も示す。本実施形態では、第1の実施形態よりも時間変化率 ( $dV/dt$ ) が大きく、ターンオフ時のスイッチング速度が向上する。また、第1の比較形態と同等のスイッチング速度が得られる。

20

#### 【0162】

以上、本実施形態のトレンチ IGBT 500 により、更に、オン抵抗が低く、スイッチング速度の速い IGBT が実現できる。

#### 【0163】

##### (第6の実施形態)

本実施形態の半導体装置は、アノードとカソードを有し、アノードがエミッタ電極に電気的に接続され、カソードが、第2の電気抵抗と下部ダミートレンチゲート電極との間、及び、第2の電気抵抗と下部トレンチゲート電極との間に接続されたツェナーダイオードを、更に備える点で、第4の実施形態と異なる。以下、第4の実施形態と重複する内容については一部記述を省略する。

30

#### 【0164】

図 19 は、本実施形態の半導体装置の模式平面図である。図 20 は、本実施形態の半導体装置の模式断面図である。図 20 (a) は図 19 の HH' 断面図である。図 20 (b) は図 20 (a) に等価回路を重ね書きした説明図である。

#### 【0165】

本実施形態の半導体装置は、半導体層に形成されたトレンチの中にゲート電極を備えるトレンチ IGBT 600 である。トレンチ IGBT 600 は、ダミートレンチゲート電極を有する間引き型 IGBT である。トレンチ IGBT 600 は、一つのトレンチ内に上下に分離したゲート電極を有する、ダブルゲート電極構造の IGBT である。

40

#### 【0166】

トレンチ IGBT 600 は、アノードとカソードを有するツェナーダイオード 60 (図 20 (b) の ZD) を備える。アノードはエミッタ電極 12 に電気的に接続される。カソードはダミーゲート抵抗 38 (第2の電気抵抗) と下部ダミートレンチゲート電極 18 b との間に接続される。カソードはダミーゲート抵抗 38 (第2の電気抵抗) と下部トレンチゲート電極 16 b との間に接続される。ツェナーダイオード 60 は、例えば、多結晶シリコンを用いて形成される。

#### 【0167】

本実施形態では、コレクタ・ゲート間の帰還容量を、ツェナーダイオード 60 を設ける

50

ことで、エミッタ電極 12 にバイパスする。したがって、ツェナーダイオード 60 が無い場合と比較して、小さなゲート電流で帰還容量を充放電できる。よって、ターンオフ時のスイッチング速度が向上する。

#### 【 0168 】

ツェナーダイオード 60 をトレンチ IGBT 600 のターンオフ時に、オン動作させる観点からは、ダミーゲート抵抗 (Rg - dummy) の値を高くすることが好ましい。

#### 【 0169 】

ツェナーダイオード 60 のツェナー電圧は、トレンチ IGBT 600 のオン動作時にゲートパッド電極 34 (第1のゲートパッド電極) に印加されるゲートオン電圧よりも高い。ツェナーダイオード 60 のツェナー電圧をトレンチ IGBT 600 のオン動作時のゲートオン電圧よりも高くすることで、トレンチ IGBT 600 のオン動作時にツェナーダイオード 60 がオン動作してトレンチ IGBT 600 の誤動作が生じることを防ぐ。10

#### 【 0170 】

図 21 は、本実施形態の半導体装置の作用及び効果の説明図である。図 21 (a) は、IGBT のターンオフ時の、ゲート抵抗とコレクタ - エミッタ間電圧 (Vce) の時間変化率 ( $dV/dt$ ) との関係を示す図である。ゲート抵抗の抵抗値は、IGBT の外に設けられる外部ゲート抵抗の抵抗値である。コレクタ - エミッタ間電圧 (Vce) の時間変化率 ( $dV/dt$ ) は、ターンオフ時のスイッチング速度の指標となる。図 21 (b) は、IGBT のターンオフ時の、コレクタ - エミッタ間電圧 (Vce) の時間変化率 ( $dV/dt$ ) とゲート電流 (Ig) の最大値との関係を示す図である。20

#### 【 0171 】

図 21 には、比較のために、第 5 の実施形態の IGBT 500、第 1 の実施形態で説明した第 1 の比較形態の IGBT 800 及び第 2 の比較形態の IGBT 900 の場合も示す。20

#### 【 0172 】

図 21 (a) から明らかなように、本実施形態では、第 1 の比較形態よりも時間変化率 ( $dV/dt$ ) が大きく、ターンオフ時のスイッチング速度が向上する。また、第 1 の比較形態よりも高い線形性が得られるため、外部ゲート抵抗によるスイッチング速度の制御性が良好となる。

#### 【 0173 】

また、図 21 (a) から明らかなように、本実施形態では、第 5 の実施形態よりも時間変化率 ( $dV/dt$ ) が大きく、ターンオフ時のスイッチング速度が向上する。また、第 5 の実施形態よりも高い線形性が得られるため、外部ゲート抵抗によるスイッチング速度の制御性が良好となる。これは、本実施形態の場合、第 5 の実施形態と異なり、下部トレンチゲート電極 16b が設けられることにより、ほぼすべての帰還容量がエミッタ電極にバイパスされるためである。30

#### 【 0174 】

また、図 21 (b) から明らかなように、本実施形態では、小さいゲート電流で早いスイッチング速度が実現できる。

#### 【 0175 】

以上、本実施形態のトレンチ IGBT 600 により、更に、オン抵抗が低く、スイッチング速度の速い IGBT が実現できる。40

#### 【 0176 】

第 1 ないし第 6 の実施形態においては、半導体層が単結晶シリコンである場合を例に説明したが、半導体層は単結晶シリコンに限られることはない。例えば、単結晶炭化珪素等、その他の単結晶半導体であっても構わない。

#### 【 0177 】

第 1 ないし第 6 の実施形態においては、2 本のトレンチゲート電極の間に挟まれるダミートレンチゲート電極の数が 3 本である場合を例に説明したが、ダミートレンチゲート電極の数は 3 本に限られず、1 本又は 2 本であっても、4 本以上であっても構わない。50

## 【0178】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。例えば、一実施形態の構成要素を他の実施形態の構成要素と置き換え又は変更してもよい。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

## 【符号の説明】

## 【0179】

|       |                          |    |

|-------|--------------------------|----|

| 1 0   | 半導体層                     | 10 |

| 1 2   | エミッタ電極                   |    |

| 1 4   | コレクタ電極                   |    |

| 1 6   | トレンチゲート電極                |    |

| 1 6 a | 上部トレンチゲート電極              |    |

| 1 6 b | 下部トレンチゲート電極              |    |

| 1 8   | ダミートレンチゲート電極             |    |

| 1 8 a | 上部ダミートレンチゲート電極           |    |

| 1 8 b | 下部ダミートレンチゲート電極           |    |

| 2 0   | pベース領域                   | 20 |

| 2 2   | エミッタ領域                   |    |

| 2 4   | nベース領域                   |    |

| 2 6   | バリア領域 (n型半導体領域)          |    |

| 2 8   | コレクタ領域                   |    |

| 3 0   | トレンチゲート絶縁膜               |    |

| 3 2   | ダミートレンチゲート絶縁膜            |    |

| 3 4   | ゲートパッド電極 (第1のゲートパッド電極)   |    |

| 3 6   | 内部ゲート抵抗 (第1の電気抵抗)        |    |

| 3 8   | ダミゲート抵抗 (第2の電気抵抗)        |    |

| 4 2   | ゲート電極接続配線 (第1の接続配線)      | 30 |

| 4 4   | ダミゲート電極接続配線 (第2の接続配線)    |    |

| 6 0   | ツエナーダイオード                |    |

| 1 0 0 | トレンチIGBT (半導体装置)         |    |

| 1 1 0 | 半導体層                     |    |

| 1 1 2 | 第1のエミッタ電極                |    |

| 1 1 4 | 第1のコレクタ電極                |    |

| 1 1 6 | 第1のトレンチゲート電極             |    |

| 1 1 8 | 第1のダミートレンチゲート電極          |    |

| 1 2 0 | 第1のpベース領域                |    |

| 1 2 2 | 第1のエミッタ領域                | 40 |

| 1 2 4 | 第1のnベース領域                |    |

| 1 2 8 | 第1のコレクタ領域                |    |

| 1 3 0 | 第1のトレンチゲート絶縁膜            |    |

| 1 3 2 | 第1のダミートレンチゲート絶縁膜         |    |

| 1 3 4 | ゲートパッド電極 (第2のゲートパッド電極)   |    |

| 1 3 6 | 第1の内部ゲート抵抗 (第1の電気抵抗)     |    |

| 1 3 8 | 第1のダミゲート抵抗 (第2の電気抵抗)     |    |

| 1 4 2 | 第1のゲート電極接続配線 (第1の接続配線)   |    |

| 1 4 4 | 第1のダミゲート電極接続配線 (第2の接続配線) |    |

| 2 0 0 | トレンチIGBT (半導体装置)         | 50 |

|       |                              |    |

|-------|------------------------------|----|

| 2 1 2 | 第 2 のエミッタ電極                  |    |

| 2 1 4 | 第 2 のコレクタ電極                  |    |

| 2 1 6 | 第 2 のトレンチゲート電極               |    |

| 2 1 8 | 第 2 のダミートレンチゲート電極            |    |

| 2 2 0 | 第 2 の p ベース領域                |    |

| 2 2 2 | 第 2 のエミッタ領域                  |    |

| 2 2 4 | 第 2 の n ベース領域                |    |

| 2 2 8 | 第 2 のコレクタ領域                  |    |

| 2 3 0 | 第 2 のトレンチゲート絶縁膜              | 10 |

| 2 3 2 | 第 2 のダミートレンチゲート絶縁膜           |    |

| 2 3 4 | ゲートパッド電極（第 3 のゲートパッド電極）      |    |

| 2 3 6 | 第 2 の内部ゲート抵抗（第 3 の電気抵抗）      |    |

| 2 3 8 | 第 2 のダミーゲート抵抗（第 4 の電気抵抗）     |    |

| 2 4 2 | 第 2 のゲート電極接続配線（第 3 の接続配線）    |    |

| 2 4 4 | 第 2 のダミーゲート電極接続配線（第 4 の接続配線） |    |

| 3 0 0 | トレンチ IGBT（半導体装置）             |    |

| 3 3 6 | 第 1 の内部ゲート抵抗（第 1 の電気抵抗）      |    |

| 4 0 0 | トレンチ IGBT（半導体装置）             |    |

| 4 3 6 | 第 2 の内部ゲート抵抗 436（第 2 の電気抵抗）  | 20 |

| 5 3 6 | 第 3 の内部ゲート抵抗（第 3 の電気抵抗）      |    |

| 6 3 6 | 第 4 の内部ゲート抵抗（第 4 の電気抵抗）      |    |

| P 1   | 第 1 の面                       |    |

| P 2   | 第 2 の面                       |    |

【図 1】

【図 2】

【図3】

【図4】

(b)

【図5】

【図6】

(a)

【図7】

【 図 8 】

【図9】

【図10】

【図11】

【 図 1 3 】

【図12】

【 図 1 4 】

【図 1 5】

【図 1 6】

【図 1 7】

【図19】

【図20】

【図21】

---

フロントページの続き

| (51)Int.Cl.             | F I                  |

|-------------------------|----------------------|

| H 01 L 27/06 (2006.01)  | H 01 L 29/78 6 5 2 K |

| H 01 L 21/822 (2006.01) | H 01 L 29/78 6 5 6 A |

| H 01 L 27/04 (2006.01)  | H 01 L 29/78 6 5 7 A |

| H 01 L 27/088 (2006.01) | H 01 L 29/90 D       |

|                         | H 01 L 27/06 1 0 2 A |

|                         | H 01 L 27/04 E       |

|                         | H 01 L 27/088 E      |

審査官 棚田 一也

(56)参考文献 特開2016-154218(JP,A)

特開2012-164851(JP,A)

特開2018-117025(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 2 9 / 7 8

H 01 L 2 1 / 3 2 9

H 01 L 2 1 / 8 2 2

H 01 L 2 1 / 8 2 3 4

H 01 L 2 7 / 0 4

H 01 L 2 7 / 0 6

H 01 L 2 7 / 0 8 8

H 01 L 2 9 / 7 3 9

H 01 L 2 9 / 8 6 6