(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number

WO 2013/042696 A1

(43) International Publication Date

28 March 2013 (28.03.2013)

WIPO | PCT

(51) International Patent Classification:

*H01L 29/786* (2006.01) *H01L 21/8247* (2006.01)

*C01G 9/02* (2006.01) *H01L 27/108* (2006.01)

*C01G 15/00* (2006.01) *H01L 27/11* (2006.01)

*C01G 19/00* (2006.01) *H01L 27/115* (2006.01)

*C01G 19/02* (2006.01) *H01L 29/41* (2006.01)

*H01L 21/28* (2006.01) *H01L 29/417* (2006.01)

*H01L 21/336* (2006.01) *H01L 29/788* (2006.01)

*H01L 21/8242* (2006.01) *H01L 29/792* (2006.01)

*H01L 21/8244* (2006.01)

2430036 (JP). ISOBE, Atsuo. OKAZAKI, Yutaka. HATANO, Takehisa. TEZUKA, Sachiaki. HONDO, Suguru. SAITO, Toshihiko.

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(21) International Application Number:

PCT/JP2012/073965

(22) International Filing Date:

12 September 2012 (12.09.2012)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

2011-208232 23 September 2011 (23.09.2011) JP

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— with international search report (Art. 21(3))

(72) Inventors; and

(75) Inventors/Applicants (for US only): YAMAZAKI, Shunpei [JP/JP]; c/o SEMICONDUCTOR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa,

(54) Title: SEMICONDUCTOR DEVICE

FIG. 1

(57) Abstract: A highly reliable structure for high-speed response and high-speed driving of a semiconductor device, in which on-state characteristics of a transistor are increased is provided. In the coplanar transistor, an oxide semiconductor layer, a source and drain electrode layers including a stack of a first conductive layer and a second conductive layer, a gate insulating layer, and a gate electrode layer are sequentially stacked in this order. The gate electrode layer is overlapped with the first conductive layer with the gate insulating layer provided there between, and is not overlapped with the second conductive layer with the gate insulating layer provided there between.

WO 2013/042696 A1

## DESCRIPTION

## SEMICONDUCTOR DEVICE

## 5 TECHNICAL FIELD

[0001]

The present invention relates to a semiconductor device and a method for manufacturing the semiconductor device.

[0002]

10 In this specification, the semiconductor device means any device which can function by utilizing semiconductor characteristics, and an electrooptic device, a semiconductor circuit, and an electronic device are all included in the category of the semiconductor device.

## 15 BACKGROUND ART

[0003]

Attention has been focused on a technique for forming a transistor using a semiconductor thin film formed over a substrate having an insulating surface (the transistor is also referred to as a thin film transistor (TFT)). The transistor has been 20 widely applied to electronic devices such as an integrated circuit (IC) or an image display device (display device). A silicon-based semiconductor material is widely known as a material for a semiconductor thin film applicable to the transistor. As another material for the same, an oxide semiconductor has been attracting attention.

[0004]

25 For example, disclosure has been made of a coplanar-type, top-gate transistor whose active layer is formed using an amorphous oxide containing indium (In), gallium (Ga), and zinc (Zn) (see Patent Document 1).

[Reference]

[0005]

30 Patent Document 1: Japanese Published Patent Application No. 2006-165528

## DISCLOSURE OF INVENTION

[0006]

A structure in which a gate electrode is surely overlapped with a channel formation region in an active layer is preferable in order to increase on-state characteristics (e.g., on-state current or field-effect mobility) of a transistor to enable high-speed response and high-speed driving of a semiconductor device. According to the structure, a gate voltage can be surely applied to the channel formation region between a source and a drain of the transistor, whereby the resistance between the source and the drain can be reduced.

[0007]

In a coplanar transistor in which a source electrode and a drain electrode are provided with a space therebetween with a gate electrode provided between the source electrode and the drain electrode, there exists a space between the gate electrode and each of the source electrode and the drain electrode when seen in the top plane or the cross section. That space behaves as a resistor in operating the transistor.

[0008]

Thus, in the case of using a silicon-based semiconductor material, an impurity is added to a semiconductor region in that space to reduce the resistance of that space, whereby the gate electrode is surely overlapped with a channel formation region in an active layer to increase on-state characteristics. On the other hand, in the case of using an oxide semiconductor as a semiconductor material, a structure in which respective end portions of the source electrode and the drain electrode are aligned with or overlapped with an end portion of the gate electrode is preferable to reduce the resistance of that space.

[0009]

However, in such a structure of the transistor in which respective end portions of the source electrode and the drain electrode are aligned with or overlapped with an end portion of the gate electrode when seen in the top plane or the cross section, there is a problem of a short circuit between the gate electrode and the source electrode or the

drain electrode. This short circuit between the electrodes is attributed to coverage failure to the source electrode, the drain electrode, and the oxide semiconductor layer with a gate insulating layer. In particular, such coverage failure is likely to become obvious as the gate insulating layer is thinned by miniaturization of the transistor.

5 [0010]

Coverage failure or the like particularly of the gate insulating layer provided over the source electrode, the drain electrode, and the oxide semiconductor layer is more likely to cause a short circuit particularly in a region which is in contact with a part of the oxide semiconductor layer and is a channel formation region. In many 10 cases, the source electrode and the drain electrode are provided to be thicker than the gate insulating layer in order to increase the on-state characteristics. Therefore, when the gate insulating layer is formed to be thin, the coverage failure further increases over edge portions of the source electrode and the drain electrode as the thickness of each of the source electrode and the drain electrode is increased; consequently, a short circuit is 15 more likely to occur between the electrodes, leading to a reduction in reliability.

[0011]

One object of one embodiment of the present invention is to provide a highly reliable structure for high-speed response and high-speed driving of a semiconductor device, in which on-state characteristics of a transistor are increased.

20 [0012]

One embodiment of the present invention is a semiconductor device in which an oxide semiconductor layer, a source and drain electrode layers including a stack of a first conductive layer and a second conductive layer, a gate insulating layer, and a gate electrode layer are sequentially stacked in a transistor. The gate electrode layer is 25 overlapped with the first conductive layer with the gate insulating layer provided therebetween, and is not overlapped with the second conductive layer with the gate insulating layer provided therebetween.

[0013]

One embodiment of the present invention is a semiconductor device in which 30 an oxide semiconductor layer is provided over a substrate having an insulating surface,

5 a first conductive layer is provided partly over the oxide semiconductor layer, a second conductive layer is provided partly over the first conductive layer, a gate insulating layer is provided over the oxide semiconductor layer, the first conductive layer, and the second conductive layer, and a gate electrode layer is provided over the oxide semiconductor layer with the gate insulating layer provided therebetween. The gate electrode layer is overlapped with the first conductive layer with the gate insulating layer provided therebetween, and is not overlapped with the second conductive layer with the gate insulating layer provided therebetween.

[0014]

10 One embodiment of the present invention is a semiconductor device in which an oxide semiconductor layer is provided over a substrate having an insulating surface, a first conductive layer is provided partly over the oxide semiconductor layer, a second conductive layer is provided partly over the first conductive layer, an insulating layer is provided over the second conductive layer, a gate insulating layer is provided over the oxide semiconductor layer, the first conductive layer, the second conductive layer, and the insulating layer, and a gate electrode layer is provided over the oxide semiconductor layer with the gate insulating layer provided therebetween. The gate electrode layer is overlapped with the first conductive layer with the gate insulating layer provided therebetween, and is not overlapped with the second conductive layer with the gate 15 insulating layer provided therebetween.

20

[0015]

One embodiment of the present invention is a semiconductor device in which an oxide semiconductor layer is provided over a substrate having an insulating surface, a first conductive layer is provided partly over the oxide semiconductor layer, an 25 insulating layer is provided partly over the first conductive layer, a second conductive layer is provided partly over the insulating layer and is in contact with the first conductive layer in an opening in the insulating layer, a gate insulating layer is provided over the oxide semiconductor layer, the first conductive layer, the second conductive layer, and the insulating layer, and a gate electrode layer is provided over the oxide 30 semiconductor layer with the gate insulating layer provided therebetween. The gate

electrode layer is overlapped with the first conductive layer with the gate insulating layer provided therebetween, and is not overlapped with the second conductive layer with the gate insulating layer provided therebetween.

[0016]

5 One embodiment of the present invention is a semiconductor device in which an oxide semiconductor layer is provided over an insulating layer partly having an embedded conductive layer over a substrate having an insulating surface, a first conductive layer is provided partly over the oxide semiconductor layer, a second conductive layer is provided partly over the first conductive layer, a gate insulating 10 layer is provided over the oxide semiconductor layer, the first conductive layer, and the second conductive layer, and a gate electrode layer is provided over the oxide semiconductor layer with the gate insulating layer provided therebetween. The gate electrode layer is overlapped with the first conductive layer with the gate insulating layer provided therebetween, and is not overlapped with the second conductive layer 15 with the gate insulating layer provided therebetween.

[0017]

In one embodiment of the present invention, it is preferable that the insulating layer partly having the embedded conductive layer be provided such that the embedded conductive layer is in contact with the first conductive layer in an opening in the oxide 20 semiconductor layer in the semiconductor device.

[0018]

In one embodiment of the present invention, it is preferable that the insulating layer partly having the embedded conductive layer have an embedded oxide semiconductor layer over the embedded conductive layer in the semiconductor device.

25 [0019]

In one embodiment of the present invention, it is preferable that the insulating layer partly having the embedded conductive layer and the embedded oxide semiconductor layer be provided such that the embedded oxide semiconductor layer be in contact with the first conductive layer in the opening in the oxide semiconductor 30 layer in the semiconductor device.

[0020]

In one embodiment of the present invention, it is preferable that the thickness of the first conductive layer be greater than or equal to 5 nm and less than or equal to 20 nm in the semiconductor device.

5 [0021]

In one embodiment of the present invention, it is preferable that the thickness of the gate insulating layer be greater than or equal to 10 nm and less than or equal to 20 nm in the semiconductor device.

[0022]

10 In one embodiment of the present invention, it is preferable that the thickness of the oxide semiconductor layer be greater than or equal to 5 nm and less than or equal to 20 nm in the semiconductor device.

[0023]

15 In one embodiment of the present invention, it is preferable that a buffer layer be provided over the substrate having the insulating surface in the semiconductor device.

[0024]

20 In one embodiment of the present invention, it is preferable that the buffer layer be a layer containing an oxide of at least one element selected from aluminum, gallium, zirconium, hafnium, and rare-earth elements in the semiconductor device.

[0025]

In one embodiment of the present invention, it is preferable that the oxide semiconductor layer have crystals whose c-axes are aligned in the semiconductor device.

25 [0026]

To realize a semiconductor device with higher performance, according to one embodiment of the present invention, a highly reliable structure for high-speed response and high-speed driving of a semiconductor device can be provided, in which on-state characteristics (e.g., on-state current or field-effect mobility) of a transistor are increased.

## BRIEF DESCRIPTION OF DRAWINGS

[0027]

In the accompanying drawings:

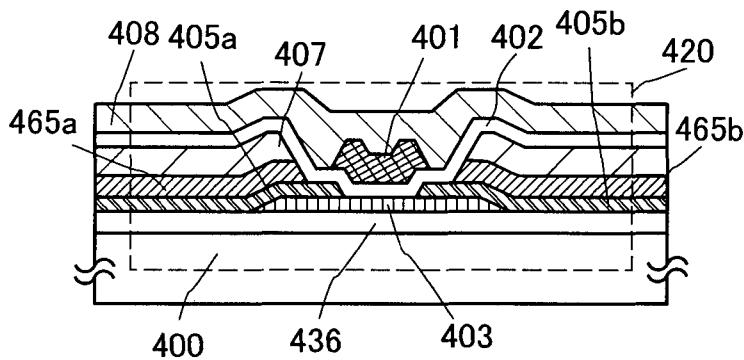

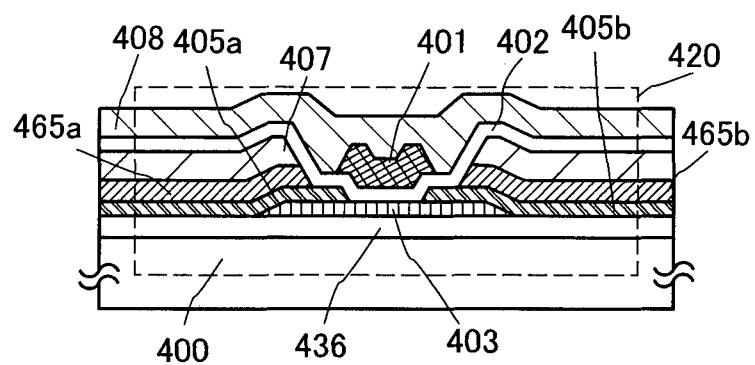

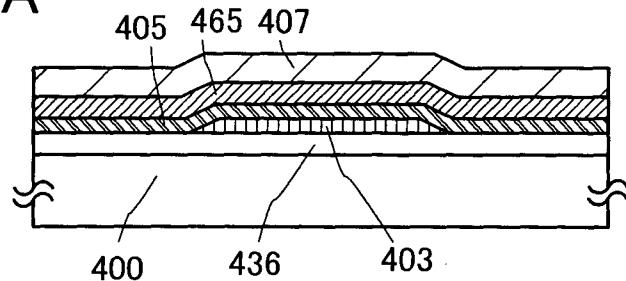

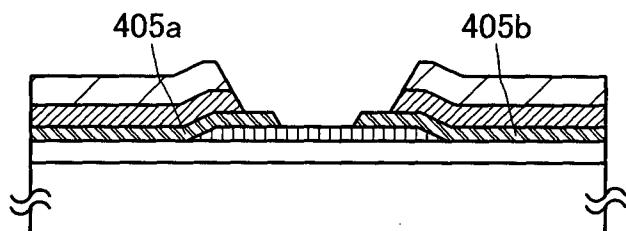

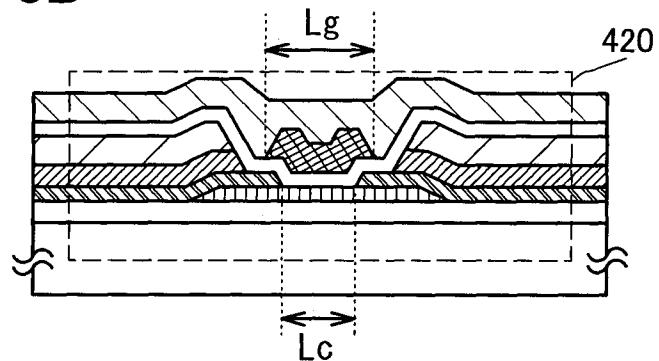

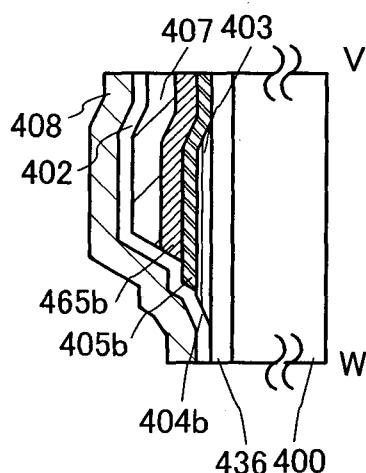

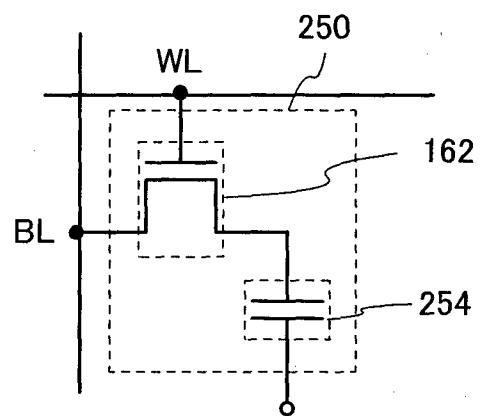

5 FIG. 1 is a diagram illustrating one embodiment of a semiconductor device;

FIGS. 2A to 2E are diagrams illustrating one embodiment of a manufacturing method of a semiconductor device;

10 FIGS. 3A and 3B are diagrams each illustrating one embodiment of a semiconductor device;

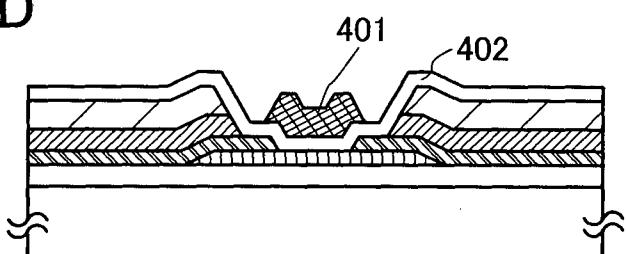

FIG. 4 is a diagram illustrating one embodiment of a semiconductor device;

FIGS. 5A and 5B are diagrams each illustrating one embodiment of a semiconductor device;

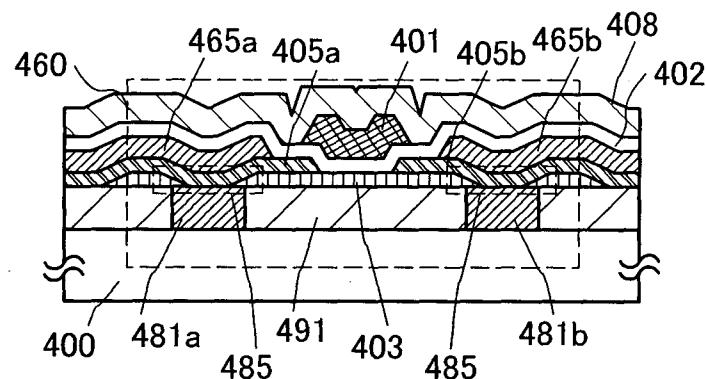

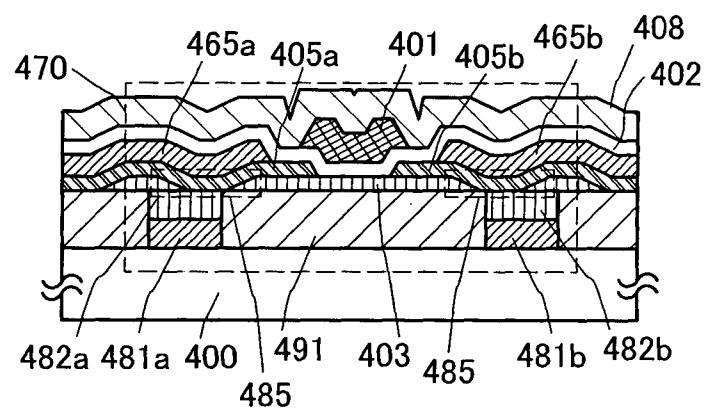

15 FIGS. 6A and 6B are diagrams each illustrating one embodiment of a semiconductor device;

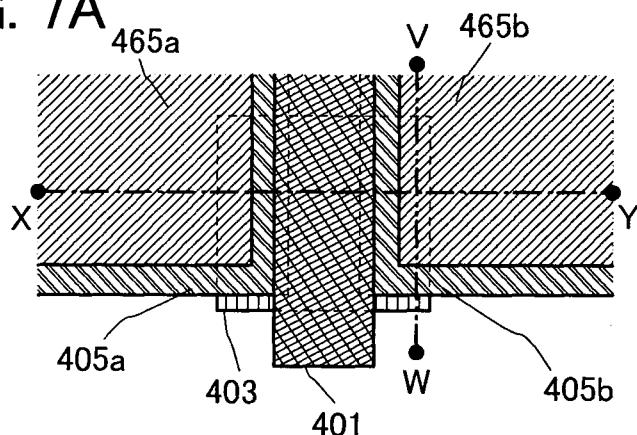

FIGS. 7A to 7C are diagrams illustrating one embodiment of a semiconductor device;

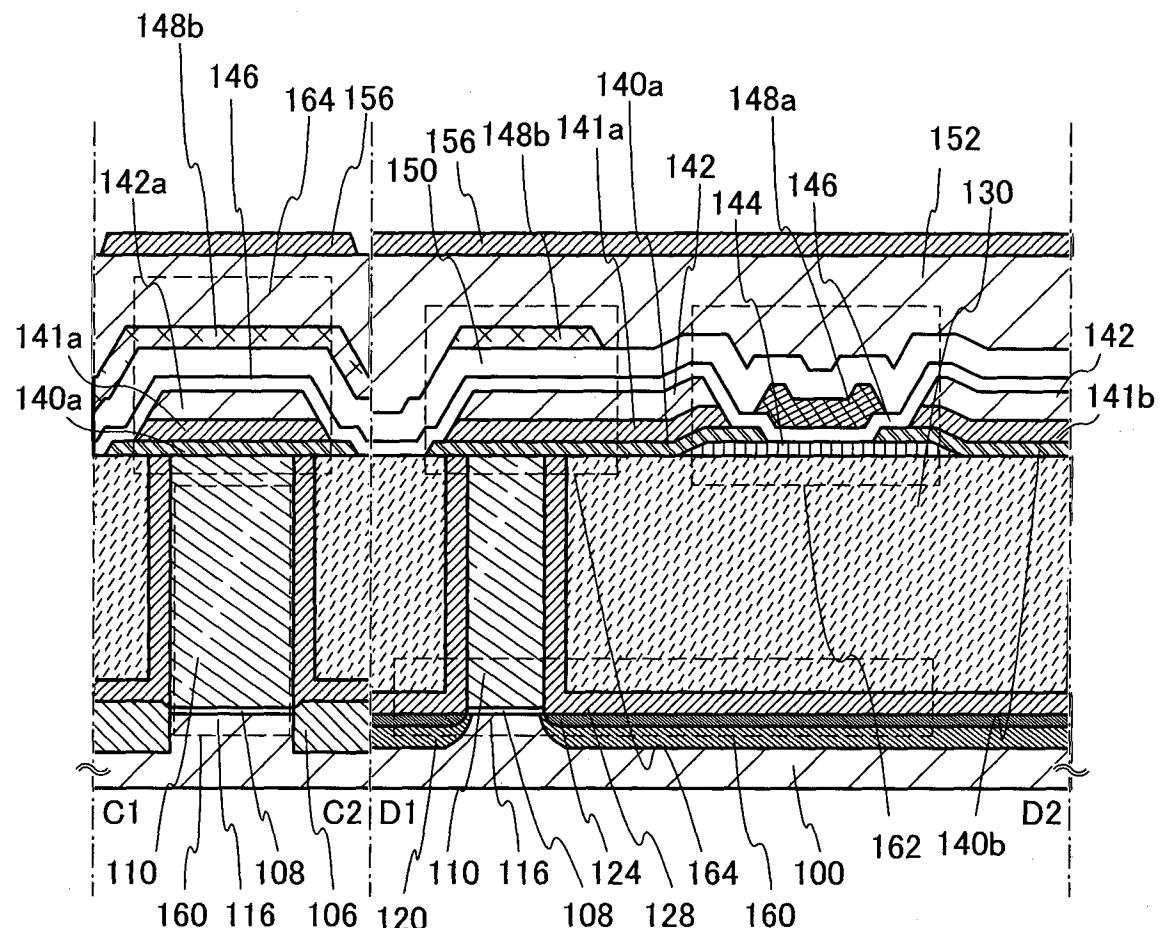

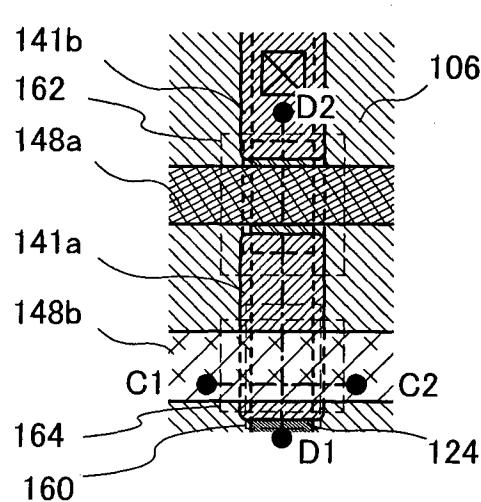

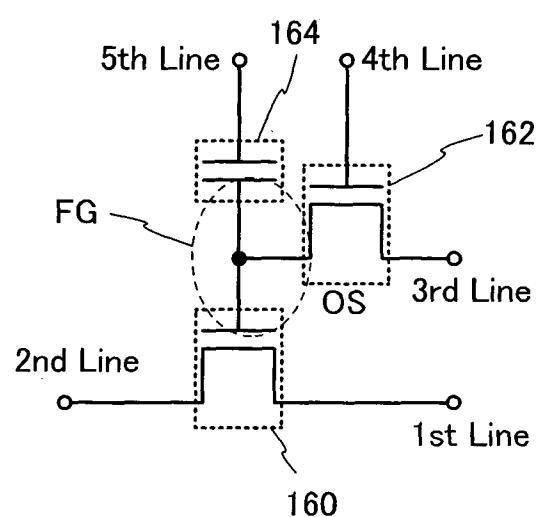

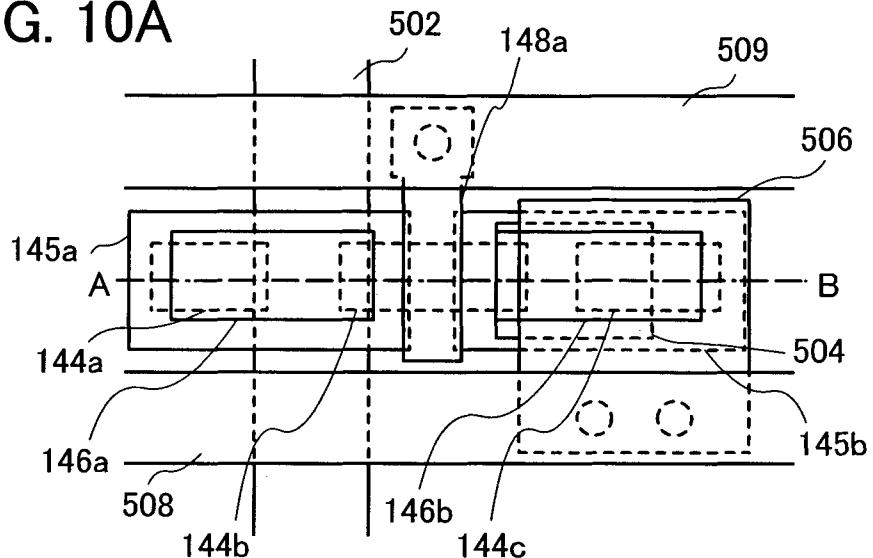

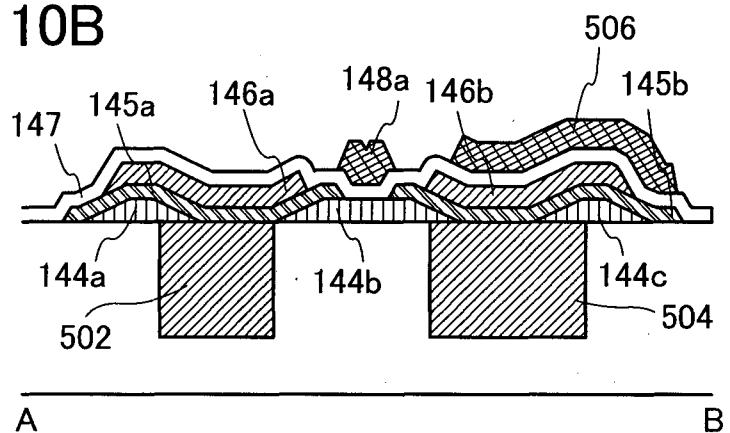

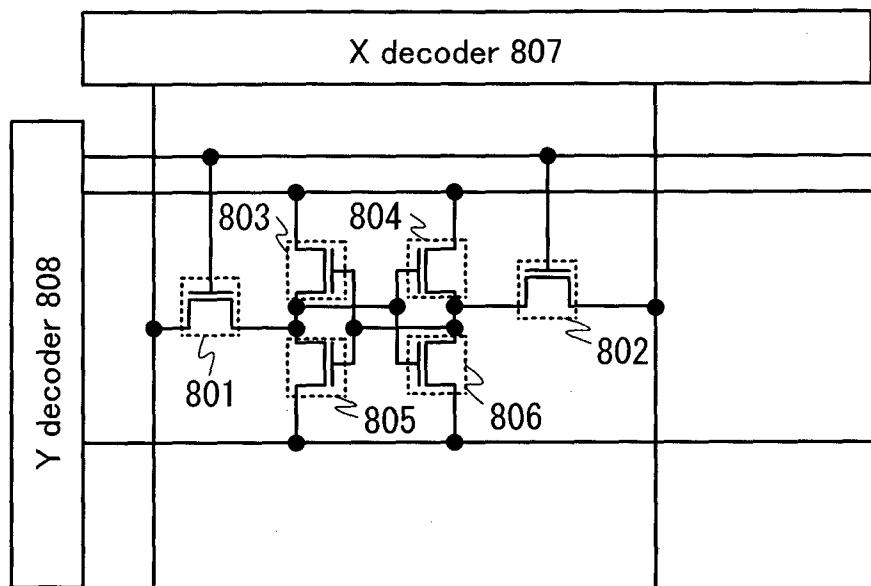

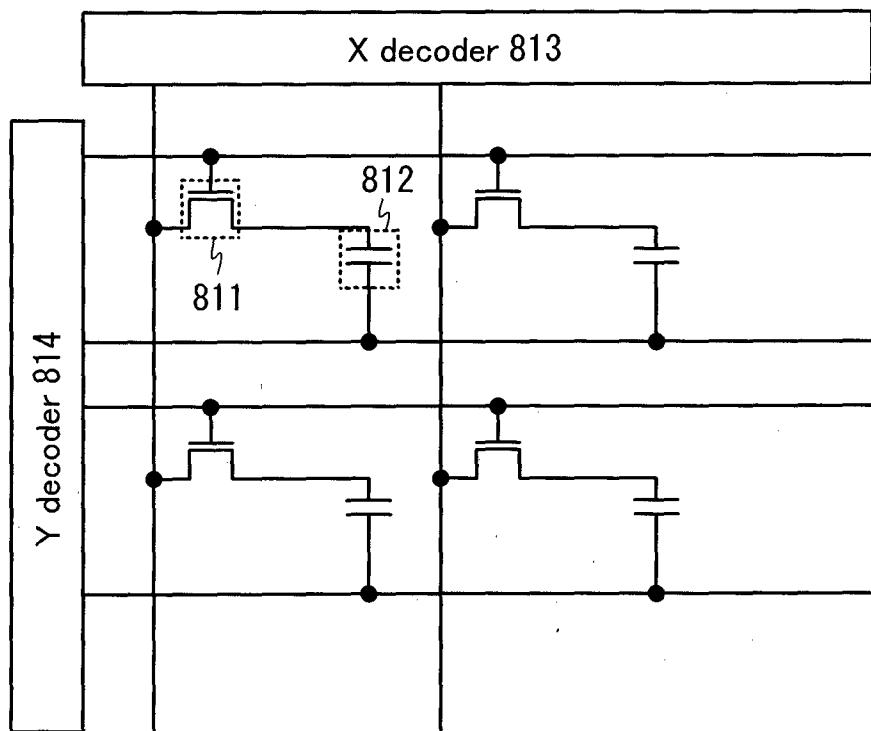

FIGS. 8A to 8C are a cross-sectional diagram, a plane view, and a circuit diagram illustrating one embodiment of a semiconductor device;

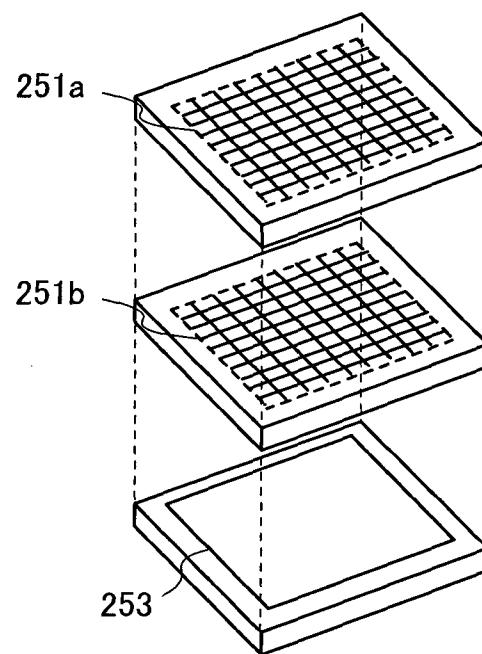

20 FIGS. 9A and 9B are a circuit diagram and a perspective view illustrating one embodiment of a semiconductor device;

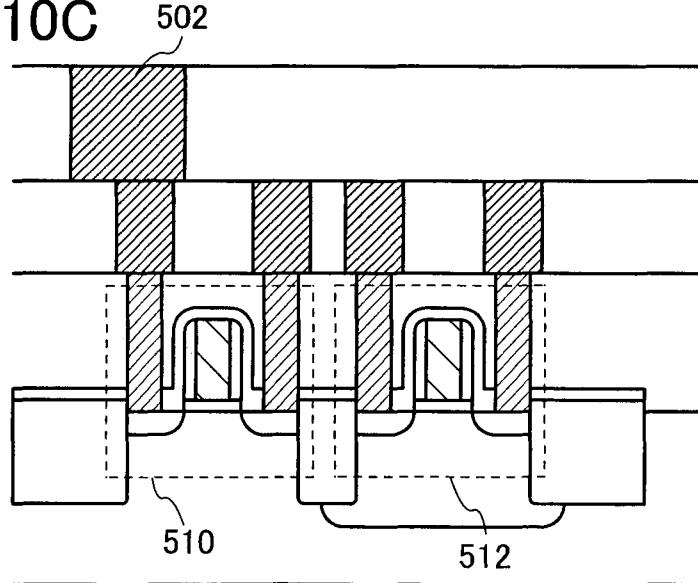

FIG. 10A is a plane view illustrating one embodiment of a semiconductor device, and FIGS. 10B and 10C are cross-sectional diagrams illustrating the same;

FIGS. 11A and 11B are circuit diagrams each illustrating one embodiment of a semiconductor device;

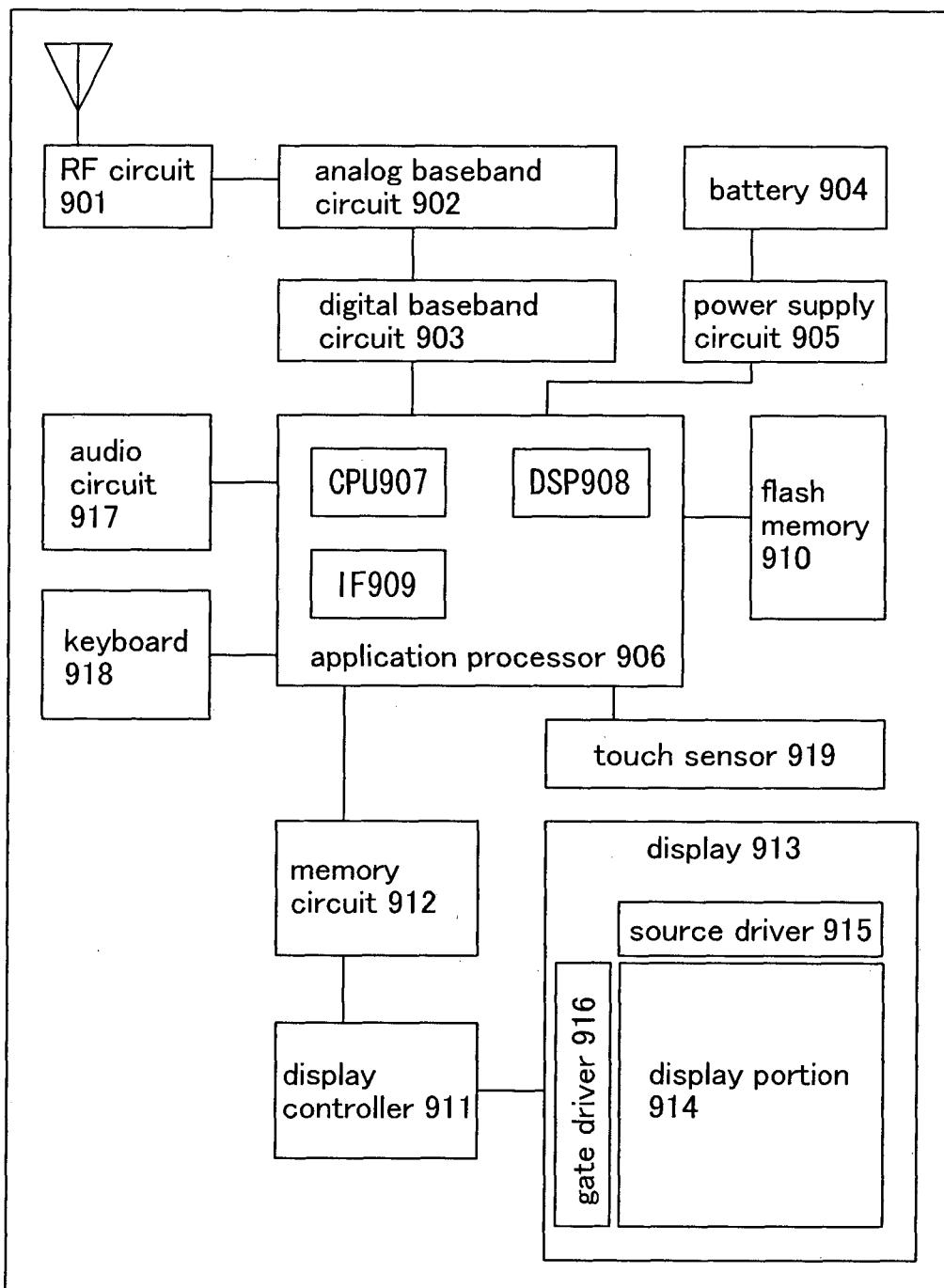

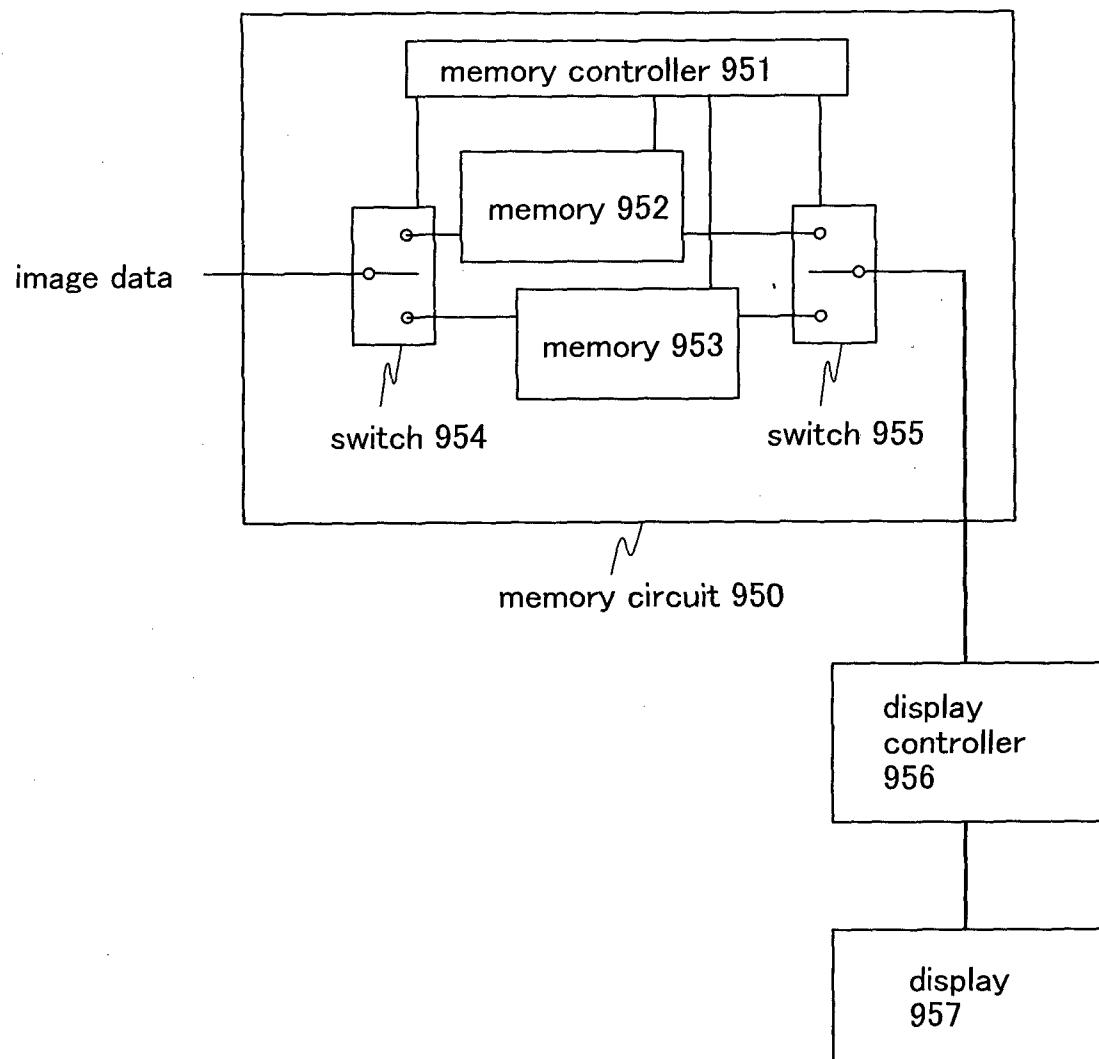

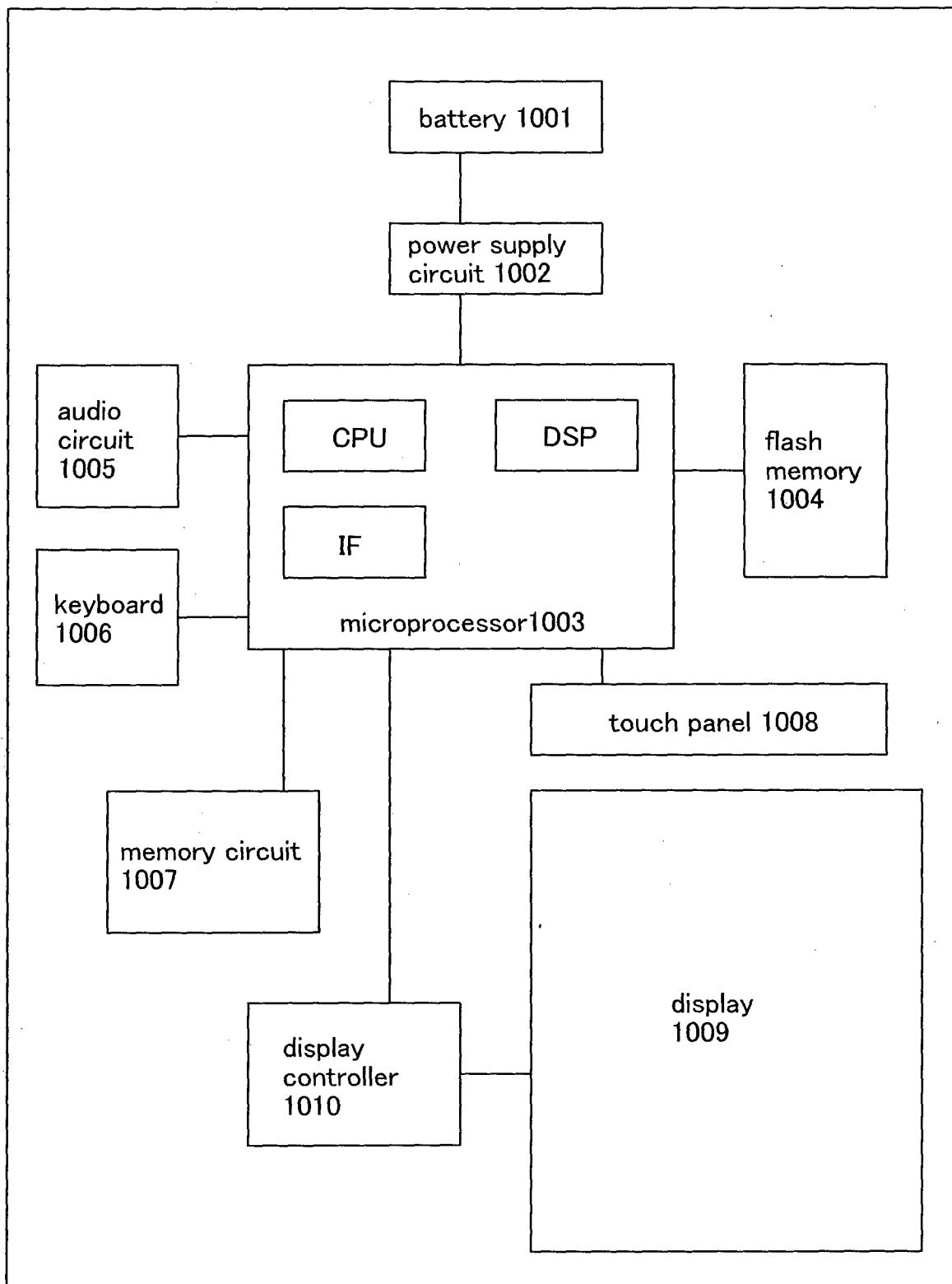

25 FIG. 12 is a block diagram illustrating one embodiment of a semiconductor device;

FIG. 13 is a block diagram illustrating one embodiment of a semiconductor device;

30 FIG. 14 is a block diagram illustrating one embodiment of a semiconductor device; and

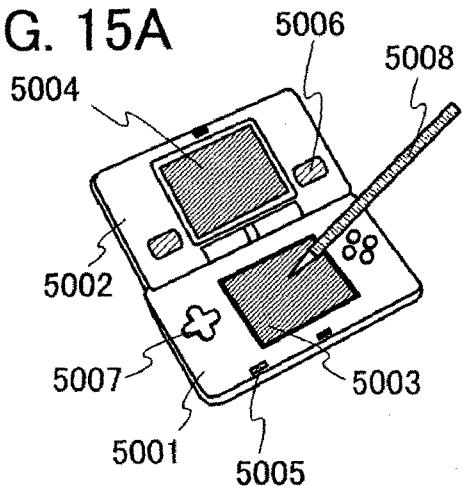

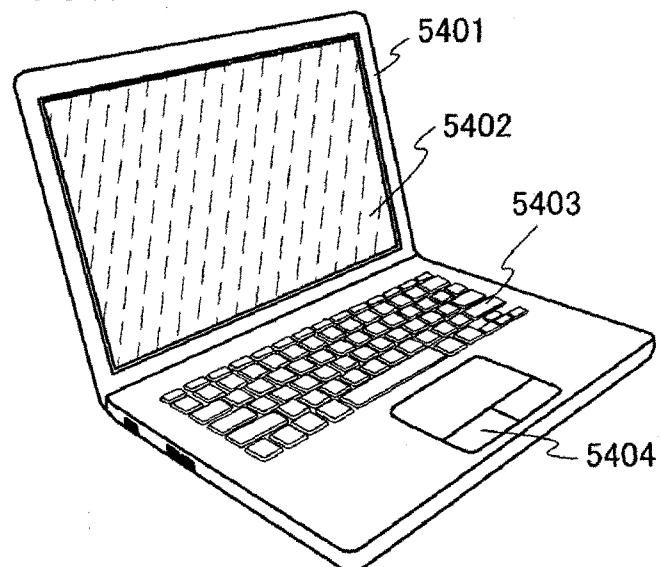

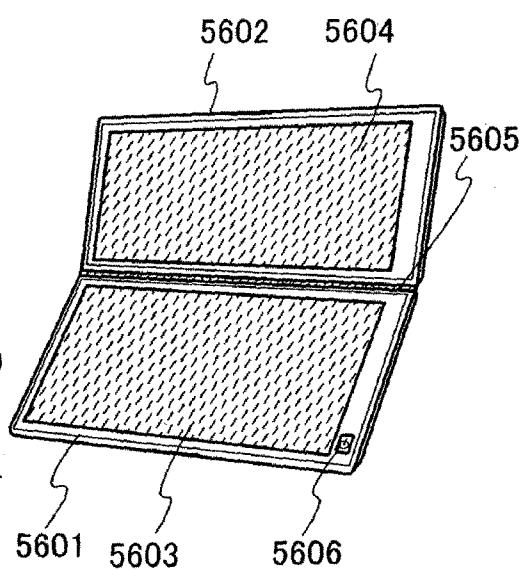

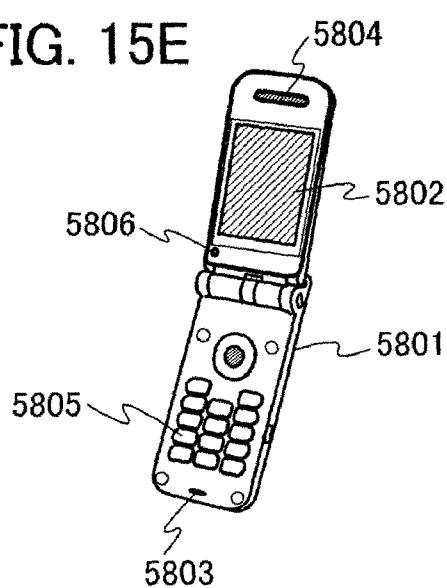

FIGS. 15A to 15E are diagrams each illustrating one embodiment of an electronic device using a semiconductor device.

#### BEST MODE FOR CARRYING OUT THE INVENTION

##### 5 [0028]

Hereinafter, embodiments of the present invention are described with reference to the accompanying drawings. However, the present invention can be carried out in many different modes, and those skilled in the art could appreciate that a variety of modifications can be made to the embodiment and details of the present invention without 10 departing from the spirit and scope of the present invention. Therefore, the present invention should not be interpreted as being limited to the description in the following embodiments.

##### [0029]

Note that the size, the thickness of a layer, and a region of each structure 15 illustrated in the drawings and the like in the embodiments are exaggerated for simplicity in some cases. Therefore, embodiments of the present invention are not confined to such scales.

##### [0030]

Further, ordinal numbers such as first, second, third, ...Nth ( $N$  is a natural 20 number) in this specification are used in order to avoid confusion among components, and thus give no numeral limitation.

##### [0031]

###### (Embodiment 1)

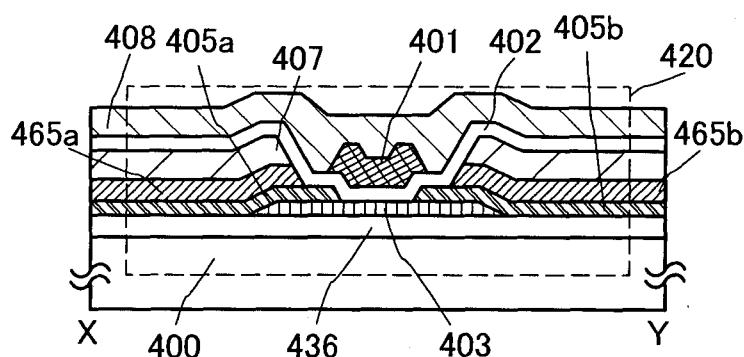

In this embodiment, a semiconductor device and a manufacturing method 25 thereof according to one embodiment of the present invention are described using FIG. 1, FIGS. 2A to 2E, FIGS. 3A and 3B, and FIG. 4.

##### [0032]

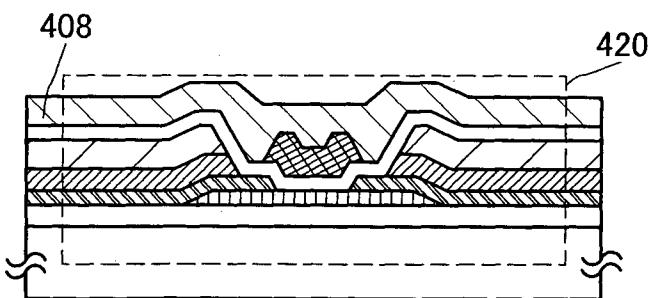

FIG. 1 is a cross-sectional diagram of a transistor 420 which is an example of a 30 structure of a semiconductor device. The transistor 420 has a single-gate structure in which one channel formation region is formed, but instead may have a double-gate

structure in which two channel formation regions are formed, or a triple-gate structure in which three channel formation regions are formed.

[0033]

5 The transistor 420 includes, over a substrate 400 having an insulating surface, a buffer layer 436, an oxide semiconductor layer 403, first conductive layers 405a and 405b, second conductive layers 465a and 465b, an insulating layer 407, a gate insulating layer 402, a gate electrode layer 401, and an interlayer insulating layer 408 (see FIG. 1).

[0034]

10 In the structure shown in FIG. 1 described in this embodiment, the first conductive layers 405a and 405b, which function as a source and drain electrodes of the transistor 420, are overlapped with the gate electrode layer 401 with the gate insulating layer 402 provided therebetween, in respective regions of the first conductive layers 405a and 405b which are overlapped with the oxide semiconductor layer 403. In addition, in the structure shown in FIG. 1 described in this embodiment, the second 15 conductive layers 465a and 465b, which function as a source and drain electrodes of the transistor 420, are not overlapped with the gate electrode layer 401 with the gate insulating layer 402 provided therebetween, in respective regions of the second conductive layers 465a and 465b which are overlapped with the oxide semiconductor layer 403.

20 [0035]

25 In the structure shown in FIG. 1 described in this embodiment, respective end portions of the first conductive layers 405a and 405b, which function as the source and drain electrodes of the transistor, can be overlapped with an end portion of the gate electrode layer 401 which functions as a gate electrode of the transistor. Accordingly, on-state characteristics (e.g., on-state current or field-effect mobility) of the transistor can be increased, enabling high-speed response and high-speed driving of the semiconductor device.

[0036]

30 Further, in the structure shown in FIG. 1 described in this embodiment, the first conductive layers 405a and 405b, which function as the source and drain electrodes of

the transistor, can be formed to be thin. By forming the first conductive layers 405a and 405b to be thin, the level of a step in the surface on which the gate insulating layer 402 is formed particularly in the vicinity of a channel formation region of the oxide semiconductor layer 403 can be low. Accordingly, the gate insulating layer 402 can be 5 formed with good coverage. A reduction in coverage failure leads to a reduction in occurrence of a short circuit between electrodes, increasing the reliability. In addition, since the respective end portions of the second conductive layers 465a and 465b, which function as the source and drain electrodes of the transistor, can be prevented from being overlapped with the end portion of the gate electrode layer 401, which functions 10 as the gate electrode, in the structure shown in FIG. 1 described in this embodiment, an increase in the thickness of the second conductive layers 465a and 465b as compared to the thickness of the first conductive layers 405a and 405b does not lead to generation of a short circuit between electrodes. Therefore, by increasing the thickness of the second conductive layers 465a and 465b, the source-drain current can be increased 15 without causing a short circuit between electrodes.

[0037]

Further, in the structure shown in FIG. 1 described in this embodiment, the first conductive layers 405a and 405b can be formed to be thin, whereby the time taken to process for forming the first conductive layers 405a and 405b by a step such as etching 20 can be shortened. Accordingly, the oxide semiconductor layer 403 can be less damaged by processing to form the first conductive layers 405a and 405b by a step such as etching. Consequently, the reliability can be increased.

[0038]

Further, according to the structure shown in FIG. 1 described in this embodiment, a coplanar structure in which the gate insulating layer 402 is thin can be 25 provided, and the oxide semiconductor layer 403 can be provided to be thin over the buffer layer 436 whose flatness is increased. Reduction in the thicknesses of the gate insulating layer 402 and the oxide semiconductor layer 403 not only leads to an increase in on-state characteristics but also enables the transistor to operate as a fully-depleted 30 transistor. Such an operation of the transistor as the fully-depleted transistor enables

high integration, high-speed driving, and low power consumption.

[0039]

Further, in the structure shown in FIG. 1 described in this embodiment, the second conductive layers 465a and 465b and the insulating layer 407 are overlapped with each other and their side surfaces can be tapered by a process such as etching. Therefore, favorable coverage can be obtained even when the thickness of the second conductive layers 465a and 465b is increased.

[0040]

As described above, in the structure shown in FIG. 1 described in this embodiment, the source electrode and the drain electrode of the transistor can be overlapped with the gate electrode without decreasing the source-drain current of the transistor, whereby on-state characteristics can be increased. Further, in the structure shown in FIG. 1 described in this embodiment, the coverage failure with the gate insulating layer can be decreased, which enables the oxide semiconductor layer and the gate insulating layer to be thin. In that case, the transistor in which an oxide semiconductor is used for a channel formation region can be miniaturized, which is preferable.

[0041]

Next, an example of a method for manufacturing the transistor 420 shown in FIG. 1 is described using FIGS. 2A to 2E.

[0042]

First, the buffer layer 436 is formed over the substrate 400 having an insulating surface. The buffer layer 436 is a layer for suppressing reaction between the oxide semiconductor layer 403 formed over the buffer layer 436 and the substrate 400 having an insulating surface.

[0043]

There is no particular limitation on a substrate that can be used as the substrate 400 having an insulating surface as long as it has heat resistance enough to withstand heat treatment performed later. For example, a glass substrate of barium borosilicate glass, aluminoborosilicate glass, or the like, a ceramic substrate, a quartz substrate, or a sapphire

substrate can be used. A single crystal semiconductor substrate or a polycrystalline semiconductor substrate of silicon, carbon silicon, or the like; a compound semiconductor substrate of silicon germanium or the like; an SOI substrate; or the like can also be used as the substrate 400, or the substrate provided with a semiconductor element can also be 5 used as the substrate 400.

[0044]

The buffer layer 436, which is in contact with the oxide semiconductor layer 403, is preferably formed using an oxide of the same kind(s) of constituent(s) as the oxide semiconductor layer 403. Specifically, it is preferable that the buffer layer 436 10 be a layer containing an oxide of at least one element selected from constituent elements of the oxide semiconductor layer 403 such as aluminum (Al), gallium (Ga), zirconium (Zr), and hafnium (Hf), and rare-earth elements belonging in the same group as aluminum, gallium, and the like. Among these elements, an oxide of aluminum, gallium, or a rare-earth element, which is a Group III element, is more preferably used. 15 As the rare-earth element, scandium (Sc), yttrium (Y), cerium (Ce), samarium (Sm), or gadolinium (Gd) is preferably used. Such a material is compatible with the oxide semiconductor layer 403, and the use of such a material for the buffer layer 436 enables a state of the interface between the oxide semiconductor layer 403 and the buffer layer 436 to be favorable. Further, the crystallinity of the oxide semiconductor layer 403 can be 20 improved.

[0045]

Since the oxide semiconductor layer 403 is used as an active layer of the transistor 420, it is requisite that the energy gap of the buffer layer 436 be larger than that of the oxide semiconductor layer 403; it is preferable that the buffer layer 436 have 25 electrical insulating properties.

[0046]

The buffer layer 436 is either a single layer or a stacked layer.

[0047]

There is no particular limitation on the forming method of the buffer layer 436; 30 a plasma-enhanced CVD method, a sputtering method, or the like can be employed.

[0048]

A planarization treatment may be performed on the surface of the buffer layer 436. The planarization treatment may be, but not particularly limited to, a polishing treatment (such as chemical mechanical polishing (CMP)), a dry etching treatment, or a 5 plasma treatment.

[0049]

Next, the oxide semiconductor layer 403 is formed over the buffer layer 436.

[0050]

In the formation of the oxide semiconductor layer 403, the concentration of 10 hydrogen in the oxide semiconductor layer 403 is preferably reduced as much as possible. For example, in the case where the oxide semiconductor layer 403 is formed by a sputtering method, in order to reduce the hydrogen concentration, a high-purity rare gas (typically argon), high-purity oxygen, or a high-purity mixed gas of a rare gas and oxygen, from which impurities such as hydrogen, water, a hydroxyl group, and hydride have been 15 removed, is supplied as an atmosphere gas into a treatment chamber of a sputtering apparatus as appropriate.

[0051]

Further, it is preferable that the oxide semiconductor layer 403 and the buffer layer 436 be formed continuously without exposure to the atmosphere. By 20 continuously forming the oxide semiconductor layer 403 and the buffer layer 436 without exposure to the atmosphere, adsorption of impurities such as hydrogen and moisture to the interface between the oxide semiconductor layer 403 and the buffer layer 436 can be prevented.

[0052]

25 Further, to reduce the impurity concentration in the oxide semiconductor layer 403, it is also effective to form the oxide semiconductor layer 403 while the substrate 400 is kept at high temperature. The temperature at which the substrate 400 is heated may be higher than or equal to 150 °C and lower than or equal to 450 °C; it is preferable that the substrate temperature be higher than or equal to 200 °C and lower than or equal to 350 °C. 30 Further, by forming the oxide semiconductor layer 403 while heating the substrate 400

at a high temperature, a crystalline oxide semiconductor layer can be formed as the oxide semiconductor layer 403.

[0053]

An oxide semiconductor used for the oxide semiconductor layer 403 preferably 5 contains at least indium (In) or zinc (Zn). In particular, In and Zn are preferably contained. As a stabilizer for reducing variation in electrical characteristics of the transistor using the oxide semiconductor, gallium (Ga) is preferably further contained. Tin (Sn) is preferably contained as a stabilizer. Hafnium (Hf) is preferably contained as a stabilizer. Aluminum (Al) is preferably contained as a stabilizer. Zirconium (Zr) is 10 preferably contained as a stabilizer.

[0054]

As another stabilizer, one or plural kinds of lanthanoid selected from lanthanum (La), cerium (Ce), praseodymium (Pr), neodymium (Nd), samarium (Sm), europium (Eu), gadolinium (Gd), terbium (Tb), dysprosium (Dy), holmium (Ho), erbium (Er), thulium 15 (Tm), ytterbium (Yb), and lutetium (Lu) may be contained.

[0055]

For example, as the oxide semiconductor, any of the following can be used: an indium oxide; a tin oxide; a zinc oxide; a two-component metal oxide such as an 20 In-Zn-based oxide, a Sn-Zn-based oxide, an Al-Zn-based oxide, a Zn-Mg-based oxide, a Sn-Mg-based oxide, an In-Mg-based oxide, or an In-Ga-based oxide; a three-component metal oxide such as an In-Ga-Zn-based oxide (also referred to as IGZO), an In-Al-Zn-based oxide, an In-Sn-Zn-based oxide, a Sn-Ga-Zn-based oxide, an Al-Ga-Zn-based oxide, a Sn-Al-Zn-based oxide, an In-Hf-Zn-based oxide, an 25 In-La-Zn-based oxide, an In-Ce-Zn-based oxide, an In-Pr-Zn-based oxide, an In-Nd-Zn-based oxide, an In-Sm-Zn-based oxide, an In-Eu-Zn-based oxide, an In-Gd-Zn-based oxide, an In-Tb-Zn-based oxide, an In-Dy-Zn-based oxide, an In-Ho-Zn-based oxide, an In-Er-Zn-based oxide, an In-Tm-Zn-based oxide, an 30 In-Yb-Zn-based oxide, or an In-Lu-Zn-based oxide; and a four-component metal oxide such as an In-Sn-Ga-Zn-based oxide, an In-Hf-Ga-Zn-based oxide, an In-Al-Ga-Zn-based oxide, an In-Sn-Al-Zn-based oxide, an In-Sn-Hf-Zn-based oxide, or

an In-Hf-Al-Zn-based oxide.

[0056]

Note that, for example, the In-Ga-Zn-based oxide means an oxide containing In, Ga, and Zn, and there is no limitation on the composition ratio of In, Ga, and Zn. The 5 In-Ga-Zn-based oxide may further contain a metal element other than In, Ga, and Zn.

[0057]

The oxide semiconductor layer 403 is preferably deposited under a condition such that much oxygen is contained (for example, by a sputtering method in an atmosphere where the proportion of oxygen is 100 %) so as to be a film containing much 10 oxygen (preferably containing excessive oxygen as compared to the stoichiometric composition ratio of the oxide semiconductor in a crystalline state).

[0058]

It is preferable to use a high-purity gas from which impurities such as hydrogen, water, a hydroxyl group, or hydride have been removed, as a sputtering gas used for 15 forming the oxide semiconductor layer 403.

[0059]

Note that a highly-purified oxide semiconductor (purified oxide semiconductor) obtained by reduction of impurities such as moisture or hydrogen which serves as an electron donor (donor) and by reduction of oxygen vacancies is an intrinsic (i-type) 20 semiconductor or a substantially i-type semiconductor. Therefore, a transistor using the oxide semiconductor has a feature of very small off-state current. Furthermore, the band gap of the oxide semiconductor is 2 eV or more, preferably 2.5 eV or more, further preferably 3 eV or more. Use of such an oxide semiconductor layer which is highly purified by reduction of impurities such as moisture or hydrogen and by reduction of 25 oxygen vacancies leads to a reduction in the off-state current of a transistor.

[0060]

Unless otherwise specified, in the case of an n-channel transistor, the off-state current in this specification is a current which flows between a source terminal and a drain terminal at a gate potential of less than or equal to zero with respect to the potential 30 of the source terminal in the state where the potential of the drain terminal is greater than

that of any of the source terminal and the gate potential.

[0061]

5 The oxide semiconductor can have a single crystal state, a polycrystalline (also referred to as polycrystal) state, an amorphous state, or the like. In particular, it is preferable that the oxide semiconductor used for the oxide semiconductor layer 403 be a mixed layer containing a crystal region and an amorphous region and be a crystalline oxide semiconductor.

[0062]

10 In a crystalline oxide semiconductor, defects in the bulk can be more reduced, and the mobility can be more increased by increasing its surface flatness. To increase the surface flatness, the oxide semiconductor is preferably formed on a flat surface; specifically, the oxide semiconductor is preferably formed on a surface with an average surface roughness ( $R_a$ ) of less than or equal to 1 nm, further preferably less than or equal to 0.3 nm, still further preferably less than or equal to 0.1 nm.

15 [0063]

20 The average surface roughness ( $R_a$ ) is obtained by expanding, into three dimensions, arithmetic mean surface roughness that is defined by JIS B 0601:2001 (ISO4287:1997) so as to be able to apply to a curved surface, and can be expressed as an “average value of the absolute values of deviations from a reference surface to a designated surface” and is defined by the following formula:

[0064]

[FORMULA 1]

$$Ra = \frac{1}{S_0} \iint_{y_2}^{y_1} \iint_{x_2}^{x_1} |f(x, y) - Z_0| dx dy$$

[0065]

25 In the formula, the designated surface is a surface which is subjected to the roughness measurement, and is a quadrilateral region which is specified by 4 points represented by the coordinates  $(x_1, y_1, f(x_1, y_1))$ ,  $(x_1, y_2, f(x_1, y_2))$ ,  $(x_2, y_1, f(x_2, y_1))$ , and  $(x_2, y_2, f(x_2, y_2))$ , and  $S_0$  represents the area of a rectangle which is obtained by projecting the designated surface on the  $x$ - $y$  plane, and  $Z_0$  represents the height of the reference surface

(the average height of the designated surface). The average surface roughness ( $R_a$ ) can be measured with an atomic force microscope (AFM).

[0066]

The crystalline oxide semiconductor is preferably a c-axis aligned crystalline oxide semiconductor (CAAC-OS).

[0067]

The CAAC-OS is neither complete single crystal nor complete amorphous. The CAAC-OS is an oxide semiconductor with a crystal-amorphous mixed phase structure where a crystal portion(s) with a size of several nanometers to several tens of nanometers is/are included in an amorphous phase. With the transmission electron microscope (TEM), a boundary between the amorphous portion and the crystal portion in the CAAC-OS is not clear. Further, a grain boundary is not found in the CAAC-OS. Since the CAAC-OS does not include a grain boundary, a reduction in electron mobility due to a grain boundary is less likely to occur.

[0068]

In the crystal portion(s) included in the CAAC-OS, the c-axes are aligned in a direction perpendicular to a surface where the CAAC-OS is formed or a surface of the CAAC-OS, triangular or hexagonal atomic arrangement which is seen from the direction perpendicular to the a-b plane is formed, and metal atoms are arranged in a layered manner or metal atoms and oxygen atoms are arranged in a layered manner when seen from the direction perpendicular to the c-axis. Note that, among the crystal portions, the direction of any of the a-axis and the b-axis of the crystal portion may differ.

[0069]

Note that the proportions of the amorphous portion and the crystal portion in the CAAC-OS are not necessarily uniform. For example, in the case where crystal growth proceeds from a surface side of the CAAC-OS, in some cases, the proportion of the crystal portion tends to be high in the vicinity of the surface of the CAAC-OS and the proportion of the amorphous portion tends to be high in the vicinity of the surface where the CAAC-OS is formed.

[0070]

Since the c-axis of the crystal portion included in the CAAC-OS is aligned in the direction perpendicular to the surface where the CAAC-OS is formed or the surface of the CAAC-OS, the directions of the c-axes of the crystal portions may differ depending on the shape of the CAAC-OS (the cross-sectional shape of the surface where the CAAC-OS

5 is formed or the cross-sectional shape of the surface of the CAAC-OS). The direction of c-axis of the crystal portion is the direction perpendicular to the surface where the CAAC-OS is formed or the surface of the CAAC-OS. The crystal portion is formed after film deposition or is formed by performing a treatment for crystallization such as a heat treatment after film deposition.

10 [0071]

Use of the CAAC-OS leads to a reduction in fluctuation in electrical characteristics of the transistor due to irradiation with visible light or ultraviolet light, whereby a highly reliable transistor can be provided.

[0072]

15 As an example of the above-described oxide semiconductor layer 403, an In-Ga-Zn-based oxide deposited by a sputtering method using a target containing In (indium), Ga (gallium), and Zn (zinc) can be given. The oxide semiconductor layer 403 can be formed to have a thickness greater than or equal to 1 nm and less than or equal to 30 nm (preferably greater than or equal to 5 nm and less than or equal to 20 nm).

[0073]

20 The CAAC-OS is formed by, for example, a sputtering method using an oxide semiconductor sputtering target which is a polycrystal. When ions collide with the sputtering target, a crystal region included in the sputtering target may be cleaved along the a-b plane, so that a flat-plate-like or pellet-like sputtered particle having a plane parallel to the a-b plane may be separated from the sputtering target. In that case, the flat-plate-like sputtered particles reach the substrate while maintaining their crystal states, whereby the CAAC-OS can be formed.

[0074]

30 In the case where the In-Ga-Zn-based oxide is deposited by a sputtering method,

it is preferable to use an In-Ga-Zn-based oxide target having an atomic ratio of In:Ga:Zn = 1:1:1, 4:2:3, 3:1:2, 1:1:2, 2:1:3, or 3:1:4. When the oxide semiconductor layer is formed using an In-Ga-Zn-based oxide target having one of those atomic ratios, a polycrystal or CAAC-OS is more likely to be formed. In addition, the filling factor of 5 the target containing In, Ga, and Zn is greater than or equal to 90 % and less than or equal to 100 %, preferably greater than or equal to 95 % and less than 100 %. Use of the target with a high filling factor enables the oxide semiconductor layer to be dense.

[0075]

The oxide semiconductor layer may be formed as follows: the substrate is held 10 in a treatment chamber with pressure reduced, residual moisture in the treatment chamber is removed, a sputtering gas from which hydrogen and moisture are removed is introduced, and the above-described target is used. At that time, the substrate temperature may be higher than or equal to 100 °C and lower than or equal to 600 °C, preferably higher than or equal to 200 °C and lower than or equal to 400 °C. By heating 15 the substrate in forming the layer, the concentration of impurities in the oxide semiconductor layer can be reduced. In addition, damage by sputtering can be alleviated. To remove remaining moisture in the treatment chamber, an adsorption vacuum pump is preferably used. For example, a cryopump, an ion pump, or a titanium sublimation pump is preferably used. The evacuation unit may be a turbo pump 20 provided with a cold trap. In the treatment chamber which is evacuated with the cryopump, for example, a hydrogen atom, a compound containing a hydrogen atom, such as water (H<sub>2</sub>O) (preferably, also a compound containing a carbon atom), and the like are removed, whereby the impurity concentration in the oxide semiconductor layer formed in the treatment chamber can be reduced.

25 [0076]

The oxide semiconductor layer formed by a sputtering method or the like, in some cases, contains a large amount of moisture or hydrogen (including a hydroxyl group) as impurities. Therefore, to reduce impurities such as moisture or hydrogen in the oxide semiconductor layer (dehydration or dehydrogenation), the oxide 30 semiconductor layer is subjected to a heat treatment in a reduced-pressure atmosphere, an

inert gas atmosphere of nitrogen, a rare gas, or the like, an oxygen gas atmosphere, or an ultra dry air atmosphere (the amount of moisture is 20 ppm (-55 °C by conversion into a dew point) or less, preferably 1 ppm or less, further preferably 10 ppb or less, according to the measurement with a dew point meter in a cavity ring down laser spectroscopy (CRDS) method).

5 [0077]

The heat treatment performed on the oxide semiconductor layer can eliminate moisture or hydrogen in the oxide semiconductor layer. Specifically, the heat treatment may be performed at a temperature higher than or equal to 250 °C and lower than or equal 10 to 750 °C, preferably higher than or equal to 400 °C and lower than the strain point of the substrate. For example, the heat treatment may be performed at 500 °C for about 3 minutes to about 6 minutes. When an RTA method is used for the heat treatment, dehydration or dehydrogenation can be performed in a short time; therefore, the heat treatment can be performed even at a temperature higher than the strain point of a glass 15 substrate.

15 [0078]

The heat treatment to eliminate moisture or hydrogen in the oxide semiconductor layer can be performed anytime in the manufacturing process of the transistor 420 after formation of the oxide semiconductor layer 403 before formation of 20 the interlayer insulating layer 408. Further, the heat treatment for the dehydration or dehydrogenation may be performed plural times, and may double as another heat treatment.

25 [0079]

In some cases, the heat treatment makes oxygen released from the oxide semiconductor layer, so that an oxygen vacancy is formed in the oxide semiconductor layer. Therefore, it is preferable to use a gate insulating layer containing oxygen as the gate insulating layer which is formed later to be in contact with the oxide semiconductor layer. Then, a heat treatment is preferably performed thereon after formation of the gate insulating layer containing oxygen, so that oxygen is supplied from the gate insulating 30 layer to the oxide semiconductor layer. With the above-described structure, oxygen

vacancies that serve as donors can be reduced, so that the stoichiometric composition ratio of the oxide semiconductor of the oxide semiconductor layer can be satisfied. As a result, the oxide semiconductor layer can be made substantially i-type and variation in electrical characteristics of the transistor due to oxygen vacancies can be reduced, leading 5 to an improvement of electrical characteristics.

[0080]

The heat treatment for supplying oxygen to the semiconductor layer is performed in a nitrogen atmosphere, ultra-dry air, or a rare gas (e.g., argon or helium) atmosphere preferably at a temperature higher than or equal to 200 °C and lower than or 10 equal to 400 °C, for example, higher than or equal to 250 °C and lower than or equal to 350 °C. The water content in the gas is preferably less than or equal to 20 ppm, further preferably less than or equal to 1 ppm, still further preferably less than or equal to 10 ppb.

[0081]

15 Further or alternatively, oxygen (which includes at least one of an oxygen radical, an oxygen atom, and an oxygen ion) may be added to the oxide semiconductor layer having being subjected to the dehydration or dehydrogenation treatment, in order to supply oxygen to the oxide semiconductor layer.

[0082]

20 Oxygen which is added to the dehydrated or dehydrogenated oxide semiconductor layer 403 to supply oxygen to the layer can highly purify the oxide semiconductor layer 403 and make the layer i-type (intrinsic). Fluctuation in electrical characteristics of the transistor having the highly-purified, i-type oxide semiconductor layer 403 is suppressed; the transistor is electrically stabilized.

25 [0083]

As the method for adding oxygen, an ion implantation method, an ion doping method, a plasma immersion ion implantation method, a plasma treatment, or the like can be used.

[0084]

30 The oxide semiconductor layer 403 can be formed by processing an oxide

semiconductor layer into an island shape by a photolithography process.

[0085]

For the etching of the oxide semiconductor layer 403, either or both of dry etching and wet etching can be used. As an etchant used for wet etching of the oxide semiconductor layer 403, a mixed solution of phosphoric acid, acetic acid, and nitric acid can be used, for example. Further, ITO07N (produced by KANTO CHEMICAL CO., INC.) may be used.

[0086]

In FIG. 2A, the oxide semiconductor layer 403 has an island shape and an end portion thereof is tapered at a degree greater than or equal to 20° and less than or equal to 50°. If the end portion of the oxide semiconductor layer 403 is perpendicular to the bottom surface, oxygen is more likely to be released from the oxide semiconductor layer 403 to cause more oxygen vacancies; generation of oxygen vacancies can be suppressed by tapering the end portion. Such suppression of generation of oxygen vacancies can lead to suppression of generation of a leakage current (parasitic channel) of the transistor 420.

[0087]

Next, a first conductive layer 405 which serves as a source and drain electrode layers (including a wiring formed of the same layer as the source and drain electrode layers) is formed over the oxide semiconductor layer 403 and the buffer layer 436.

[0088]

The first conductive layer 405 is formed using a material that can withstand a heat treatment performed later. As the first conductive layer 405 used for the source and drain electrode layers, for example, a metal film containing an element selected from Al, Cr, Cu, Ta, Ti, Mo, and W, a metal nitride film containing any of the above elements as its component (e.g., a titanium nitride film, a molybdenum nitride film, or a tungsten nitride film), or the like can be used.

[0089]

In the case where a metal film of Al, Cu, or the like is used for the first conductive layer 405, it is preferable that a film of a high-melting-point metal such as Ti,

Mo, or W or a metal nitride film thereof (e.g., a titanium nitride film, a molybdenum nitride film, or a tungsten nitride film) be stacked over or/and below the metal film.

[0090]

Further, the first conductive layer 405 used for the source and drain electrode layers may also be formed using a conductive metal oxide. As the conductive metal oxide, indium oxide ( $In_2O_3$ ), tin oxide ( $SnO_2$ ), zinc oxide ( $ZnO$ ), indium oxide-tin oxide ( $In_2O_3-SnO_2$ ; abbreviated to ITO), indium oxide-zinc oxide ( $In_2O_3-ZnO$ ), or any of these metal oxide materials to which silicon oxide is added can be used.

[0091]

It is preferable that the first conductive layer 405 be thinner than a second conductive layer 465 formed later. Specifically, it is preferable that the first conductive layer 405 be as thin as possible to prevent a coverage failure with the gate insulating layer 402 formed later; the first conductive layer 405 may be formed to have a thickness greater than or equal to 1 nm and less than or equal to 30 nm (preferably greater than or equal to 10 nm and less than or equal to 20 nm).

[0092]

Next, the second conductive layer 465 which serves as a source and drain electrode layers (including a wiring formed of the same layer as the source and drain electrode layers) is formed over the first conductive layer 405.

[0093]

The second conductive layer 465 is formed using a material which can withstand a heat treatment later. As the second conductive layer 465 used for the source and drain electrode layers, for example, a metal film containing an element selected from Al, Cr, Cu, Ta, Ti, Mo, and W, a metal nitride film containing any of the above elements as its component (e.g., a titanium nitride film, a molybdenum nitride film, or a tungsten nitride film), or the like can be used.

[0094]

Further, a film of a high-melting-point metal such as Ti, Mo, or W or a metal nitride film thereof (e.g., a titanium nitride film, a molybdenum nitride film, or a tungsten nitride film) may be stacked over or/and below the metal film of Al, Cu, or the like.

[0095]

Further, the second conductive layer 465 used for the source and drain electrode layers may also be formed using a conductive metal oxide. As the conductive metal oxide, indium oxide ( $In_2O_3$ ), tin oxide ( $SnO_2$ ), zinc oxide ( $ZnO$ ), indium oxide-tin oxide 5 ( $In_2O_3-SnO_2$ ; abbreviated to ITO), indium oxide-zinc oxide ( $In_2O_3-ZnO$ ), or any of these metal oxide materials to which silicon oxide is added can be used.

[0096]

In the case where a single layer of a metal film of Al, Cu, or the like is used as the second conductive layer 465, it is preferable that a film of a high-melting-point metal 10 such as Ti, Mo, or W or a metal nitride film thereof (e.g., a titanium nitride film, a molybdenum nitride film, or a tungsten nitride film) be used for the first conductive layer 405. With that structure, Al, Cu, or the like used for the second conductive layer 465 enables a reduction in wiring resistance, and an increase of resistance by oxidation of Al, Cu, or the like due to direct contact between the oxide semiconductor layer and Al, Cu, 15 or the like can be reduced. Further, it is preferable that a material whose etching selectivity relative to the first conductive layer 405 in etching in a later step (step in FIG. 2B) is high be used for the second conductive layer 465.

[0097]

It is preferable that the second conductive layer 465 be thicker than the first 20 conductive layer 405. Specifically, the second conductive layer 465 can be formed to have any thickness as small as a thickness at which the wiring resistance of the second conductive layer 465 functioning as the source or drain electrode layer is not large.

[0098]

Next, the insulating layer 407 is formed over the second conductive layer 465. 25 The insulating layer 407 is not a requisite element, but is effective as a mask in processing the first conductive layer 405 and the second conductive layer 465 in a later step or as a protection layer to protect the upper surface of the source and drain electrodes.

[0099]

30 The insulating layer 407 can be formed by a CVD method, a sputtering method,

or the like. The insulating layer 407 is preferably formed so as to include a silicon oxide, a silicon nitride, a silicon oxynitride, a silicon nitride oxide, an aluminum oxide, a hafnium oxide, a tantalum oxide, or the like. The insulating layer 407 has either a single-layer structure or a stacked-layer structure. There are no particular limitations 5 on the thickness of the insulating layer 407.

[0100]

The foregoing is the description of the process to result in the state shown in FIG. 2A.

[0101]

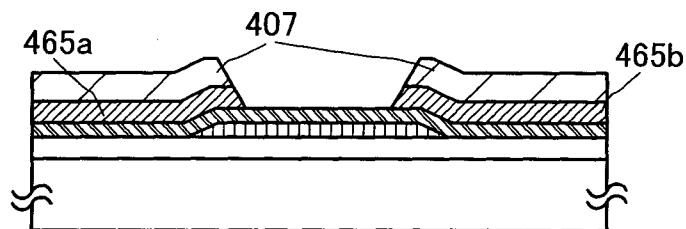

10 Next, by a photolithography process, a resist mask is formed over the insulating layer 407, and the second conductive layer 465 and the insulating layer 407 are partly subjected to an etching treatment, so that the second conductive layers 465a and 465b are formed, and then, the resist mask is removed. With the etching treatment, the second conductive layer 465 and the insulating layer 407 are each separated over the 15 oxide semiconductor layer 403. The separated second conductive layers 465a and 465b function as the source electrode layer and the drain electrode layer of the transistor 420.

[0102]

20 The foregoing is the description of the process to result in the state shown in FIG. 2B.

[0103]

Next, by a photolithography process, a resist mask is formed over the first conductive layer 405, and an etching treatment is partly thereon, so that the first conductive layers 405a and 405b are formed, and then, the resist mask is removed. 25 With the etching treatment, the first conductive layer 405 is separated over the oxide semiconductor layer 403. The separated first conductive layers 405a and 405b function as the source electrode layer and the drain electrode layer of the transistor 420.

[0104]

30 The thickness of the first conductive layer 405 over the oxide semiconductor layer 403 can be made uniform by forming the first conductive layer 405 to be thinner

than the second conductive layer 465. Also, by forming the first conductive layer 405 to be thin, the time taken to process the first conductive layer 405 by the etching treatment can be shortened. Accordingly, damage to the oxide semiconductor layer 403 in processing the first conductive layer 405 can be reduced. Accordingly, the 5 reliability can be increased.

[0105]

The foregoing is the description of the process to result in the state shown in FIG. 2C.

[0106]

10 Next, the gate insulating layer 402 is formed to cover the oxide semiconductor layer 403, the first conductive layers 405a and 405b, the second conductive layers 465a and 465b, and the insulating layer 407.

[0107]

15 The gate insulating layer 402 can be formed to have a thickness greater than or equal to 1 nm and less than or equal to 20 nm, preferably a thickness greater than or equal to 10 nm and less than or equal to 20 nm by a sputtering method, an MBE method, a CVD method, a pulse laser deposition method, an ALD method, or the like as appropriate. The gate insulating layer 402 may be formed using a sputtering apparatus which performs film deposition with surfaces of a plurality of substrates set substantially perpendicular to 20 a surface of a sputtering target.

[0108]

The gate insulating layer 402 can be formed using a silicon oxide film, a gallium oxide film, an aluminum oxide film, a silicon nitride film, a silicon oxynitride film, an aluminum oxynitride film, or a silicon nitride oxide film.

25 [0109]

It is preferable that the gate insulating layer 402 include oxygen in a portion which is in contact with the oxide semiconductor layer 403. In particular, the gate insulating layer 402 preferably includes oxygen which exceeds at least the stoichiometric ratio in the layer (bulk); for example, in the case where silicon oxide is used for the gate 30 insulating layer 402, the composition formula is  $\text{SiO}_{2+\alpha}$  ( $\alpha > 0$ ).

## [0110]

In this embodiment, silicon oxide of  $\text{SiO}_{2+\alpha}$  ( $\alpha > 0$ ) is used for the gate insulating layer 402. By using the silicon oxide for the gate insulating layer 402, oxygen can be supplied to the oxide semiconductor layer 403, leading to an increase in characteristics.

## 5 [0111]

The gate insulating layer 402 can also be formed using a high- $k$  material such as hafnium oxide, yttrium oxide, hafnium silicate ( $\text{HfSi}_x\text{O}_y$  ( $x > 0, y > 0$ )), hafnium silicate to which nitrogen is added ( $\text{HfSiO}_x\text{N}_y$  ( $x > 0, y > 0$ )), hafnium aluminate ( $\text{HfAl}_x\text{O}_y$  ( $x > 0, y > 0$ )), or lanthanum oxide, whereby the gate leakage current can be reduced. Further, the 10 gate insulating layer 402 has either a single-layer structure or a stacked-layer structure.

## [0112]

Then, the gate electrode layer 401 is formed over the gate insulating layer 402 by a plasma-enhanced CVD method, a sputtering method, or the like.

## [0113]

15 The gate electrode layer 401 can be formed using a metal material such as molybdenum, titanium, tantalum, tungsten, aluminum, copper, chromium, neodymium, or scandium or an alloy material which contains any of these materials as its main component. Further or alternatively, a semiconductor film which is doped with an impurity element such as phosphorus and is typified by a polycrystalline silicon film, or a 20 silicide film of nickel silicide or the like may be used as the gate electrode layer 401. The gate electrode layer 401 has either a single-layer structure or a stacked-layer structure.

## [0114]

25 The gate electrode layer 401 can also be formed using a conductive material such as an indium tin oxide, an indium oxide containing a tungsten oxide, an indium zinc oxide containing a tungsten oxide, an indium oxide containing a titanium oxide, an indium tin oxide containing a titanium oxide, an indium zinc oxide, or an indium tin oxide to which a silicon oxide is added. The gate electrode layer 401 can have a stacked-layer structure of the above conductive material and the above metal material.

## 30 [0115]

As one layer of the gate electrode layer 401 which is in contact with the gate insulating layer 402, a metal oxide containing nitrogen, specifically, an In-Ga-Zn-O film containing nitrogen, an In-Sn-O film containing nitrogen, an In-Ga-O film containing nitrogen, an In-Zn-O film containing nitrogen, a Sn-O film containing nitrogen, an In-O film containing nitrogen, or a metal nitride (e.g., InN or SnN) film can be used. These films each have a work function of 5 eV or higher, preferably 5.5 eV or higher, which enables the threshold voltage of the electrical characteristics of the transistor to take a positive value when used for the gate electrode layer, so that a switching element of so-called normally-off type can be provided.

10 [0116]

The foregoing is the description of the process to result in the state shown in FIG. 2D.

[0117]

Next, the interlayer insulating layer 408 is formed over the gate insulating layer 15 402 and the gate electrode layer 401 (see FIG. 2E).

[0118]

The interlayer insulating layer 408 can be formed by a plasma-enhanced CVD method, a sputtering method, an evaporation method, or the like. As the interlayer insulating layer 408, an inorganic insulating layer of a silicon oxide, a silicon oxynitride, 20 an aluminum oxynitride, a gallium oxide, or the like can be typically used.

[0119]

For the interlayer insulating layer 408, an aluminum oxide, a hafnium oxide, a magnesium oxide, a zirconium oxide, a lanthanum oxide, a barium oxide, or a metal nitride (e.g., an aluminum nitride film) can also be used.

25 [0120]

The interlayer insulating layer 408 has either a single-layer structure or a stacked-layer structure; for example, a stack of a silicon oxide film and an aluminum oxide film can be used.

[0121]

30 The interlayer insulating layer 408 is preferably formed by a method by which

impurities such as water and hydrogen do not enter the interlayer insulating layer 408, such as a sputtering method. It is preferable that the interlayer insulating layer 408 be a film containing excessive oxygen because it can serve as an oxygen supply source to the oxide semiconductor layer 403 through the gate insulating layer 402 in contact with 5 the oxide semiconductor layer 403.

[0122]

In this embodiment, a 100-nm-thick silicon oxide film is formed as the interlayer insulating layer 408 by a sputtering method. The deposition of a silicon oxide film by a sputtering method can be performed in a rare gas (typically, argon) atmosphere, an 10 oxygen atmosphere, or a mixed atmosphere of a rare gas and oxygen.

[0123]

In order to remove moisture remaining in the deposition chamber of the interlayer insulating layer 408, in a manner similar to that of the deposition of the oxide semiconductor layer, an adsorption vacuum pump (e.g., a cryopump) is preferably used. 15 By depositing the interlayer insulating layer 408 in the deposition chamber which is exhausted with a cryopump, the impurity concentration in the interlayer insulating layer 408 can be reduced. In addition, as an exhaustion unit for removing moisture remaining in the deposition chamber of the interlayer insulating layer 408, a turbo molecular pump provided with a cold trap may be used.

20 [0124]

A high-purity gas from which impurities such as hydrogen, water, a hydroxyl group, and hydride have been removed is preferably used as a sputtering gas used for deposition of the interlayer insulating layer 408.

[0125]

25 The aluminum oxide film which can be used as the interlayer insulating layer 408 provided over the oxide semiconductor layer 403 has a high shielding (blocking) effect of preventing penetration of both oxygen and impurities such as hydrogen and moisture.

[0126]

30 Therefore, in and after the manufacturing process, the aluminum oxide film

functions as a protective film for preventing entry of impurities such as hydrogen and moisture, which cause a change, into the oxide semiconductor layer 403 and release of oxygen, which is a main constituent material of the oxide semiconductor, from the oxide semiconductor layer 403.

5 [0127]

Further, a planarization insulating film may be formed thereover in order to reduce surface roughness due to the transistor. As the planarization insulating film, an organic material such as polyimide, acrylic, or a benzocyclobutene-based resin can be used. Other than the organic material, it is also possible to use a low-dielectric constant material (low- $k$  material) or the like. The planarization insulating film may also be formed by stacking a plurality of insulating films formed from these materials.

10 [0128]

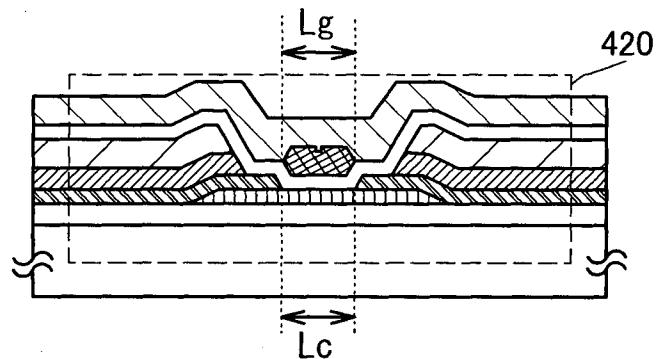

In the structure of the transistor described in this embodiment, a distance  $L_c$  between the first conductive layer 405a and the first conductive layer 405b which function as the source and drain electrodes is a channel length of the transistor 420. In the structure described in this embodiment, a length in the channel length direction  $L_g$  of the gate electrode layer 401 can be either equal to the channel length  $L_c$  as shown in FIG. 3A or greater than the channel length  $L_c$  as shown in FIG. 3B. That is, according to the structure of the transistor described in this embodiment, an end portion of the gate 15 electrode layer 401, which functions as a gate electrode of the transistor, can be overlapped with an end portion of the first conductive layer 405a, which functions as one of the source and drain electrodes, and an end portion of the first conductive layer 405b which functions as the other of the source and drain electrodes. Accordingly, on-state characteristics (e.g., on-state current or field-effect mobility) of the transistor 20 can be increased, enabling high-speed response and high-speed driving of the semiconductor device.

25 [0129]

Through the above-described process, the transistor 420 of this embodiment is manufactured (see FIG. 2E). The transistor in which the oxide semiconductor layer 30 403 containing at least indium, zinc, and oxygen is used, the gate electrode is

overlapped with the source and drain electrodes, and the coverage is good can be provided. Accordingly, a highly reliable structure for high-speed response and high-speed driving of a semiconductor device, in which on-state characteristics of a transistor are increased can be provided.

5 [0130]

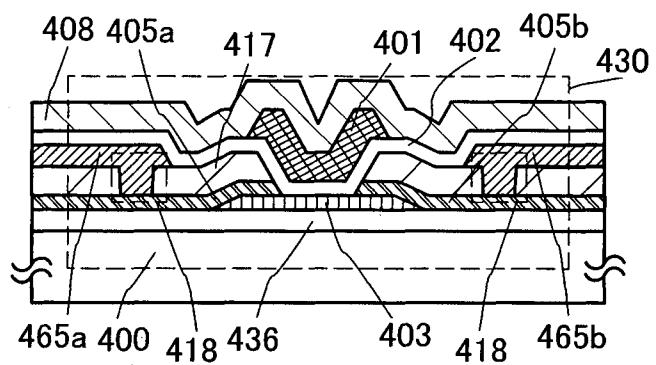

A modified example of the transistor 420 shown in FIG. 1 is described using FIG. 4. Repetitive description on portions which are the same as or have functions which are the same as those in portions in FIG. 1 is skipped in the following description of FIG. 4. In addition, detailed description of the same portions is skipped.

10 [0131]

A structure of a transistor shown in FIG. 4 is different from that of the transistor shown in FIG. 1 in which the second conductive layer is directly stacked over the first conductive layer, and is a structure in which an insulating layer is provided between a first conductive layer and a second conductive layer.

15 [0132]

FIG. 4 is a cross-sectional diagram of a transistor 430 which is an example which is different from the structure of the transistor 420 shown in FIG. 1.

[0133]

The transistor 430 includes, over a substrate 400 having an insulating surface, a 20 buffer layer 436, an oxide semiconductor layer 403, first conductive layers 405a and 405b, second conductive layers 465a and 465b, an insulating layer 417, a gate insulating layer 402, a gate electrode layer 401, and an interlayer insulating layer 408 (see FIG. 4).

[0134]

In the structure shown in FIG. 4, like the structure shown in FIG. 1, the first 25 conductive layers 405a and 405b, which function as a source and drain electrodes of the transistor 430, are overlapped with the gate electrode layer 401 with the gate insulating layer 402 provided therebetween, in respective regions of the first conductive layers 405a and 405b which are overlapped with the oxide semiconductor layer 403. In addition, in the structure shown in FIG. 4, like the structure shown in FIG. 1, the second 30 conductive layers 465a and 465b, which function as a source and drain electrodes of the

transistor 430, are not overlapped with the gate electrode layer 401 with the gate insulating layer 402 provided therebetween in respective regions of the second conductive layers 465a and 465b which are overlapped with the oxide semiconductor layer 403.

5 [0135]

Accordingly, in the structure shown in FIG. 4, the source electrode and the drain electrode of the transistor can be overlapped with a gate electrode without decreasing the source-drain current of the transistor, whereby on-state characteristics can be increased. Further, in the structure shown in FIG. 4, the coverage failure with 10 the gate insulating layer can be decreased, which enables the oxide semiconductor layer and the gate insulating layer to be thin.

[0136]

Further, in particular, in the structure shown in FIG. 4, the insulating layer 417 is provided between the first conductive layers 405a and 405b and the second 15 conductive layers 465a and 465b, and the first conductive layer 405a, 405b is directly connected to the second conductive layer 465a, 465b in an opening 418. According to the structure, the first conductive layer and the second conductive layer can be processed into an appropriate shape even if the etching selectivity of the second conductive layer relative to the first conductive layer is low in manufacturing the 20 transistor 430. Therefore, the same material can be used for the first conductive layer and the second conductive layer.

[0137]

As described above, in the structure described in this embodiment, the source electrode and the drain electrode of the transistor can be overlapped with the gate electrode without decreasing the source-drain current of the transistor, whereby on-state 25 characteristics can be increased. Further, in the structure described in this embodiment, the coverage failure with the gate insulating layer can be decreased, which enables the oxide semiconductor layer and the gate insulating layer to be thin. In that case, the transistor in which an oxide semiconductor is used for a channel formation region can 30 be miniaturized, which is preferable.

[0138]

This embodiment can be implemented combining with another embodiment as appropriate.

[0139]

5 (Embodiment 2)

In this embodiment, another embodiment of the semiconductor device is described using FIGS. 5A and 5B and FIGS. 6A and 6B. The description of the above-described embodiment can apply to portions or steps which are the same as or have functions which are the same as those in the above-described embodiment, and 10 repetitive description thereof is skipped. In addition, detailed description of the same portions is skipped.

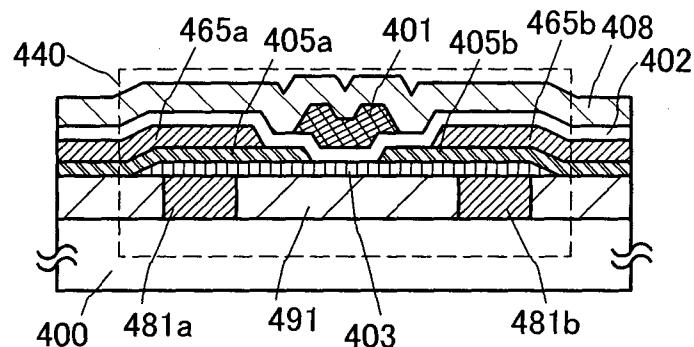

[0140]

FIG. 5A is a cross-sectional diagram of a transistor 440 which is an example which is different from the structure of the semiconductor device described in 15 Embodiment 1.

[0141]

The transistor 440 includes, over a substrate 400 having an insulating surface, an insulating layer 491 provided with embedded conductive layers 481a and 481b, an oxide semiconductor layer 403, first conductive layers 405a and 405b, second 20 conductive layers 465a and 465b, a gate insulating layer 402, a gate electrode layer 401, and an interlayer insulating layer 408 (see FIG. 5A).

[0142]

In the structure shown in FIG. 5A, like the structure shown in FIG. 1, the first conductive layers 405a and 405b, which function as a source and drain electrodes of the 25 transistor 440, are overlapped with the gate electrode layer 401 with the gate insulating layer 402 provided therebetween, in respective regions of the first conductive layers 405a and 405b which are overlapped with the oxide semiconductor layer 403. In addition, in the structure shown in FIG. 5A, like the structure shown in FIG. 1, the second conductive layers 465a and 465b, which function as a source and drain 30 electrodes of the transistor 440, are not overlapped with the gate electrode layer 401

with the gate insulating layer 402 provided therebetween, in respective regions of the second conductive layers 465a and 465b which are overlapped with the oxide semiconductor layer 403.

[0143]

5 Accordingly, in the structure shown in FIG. 5A, the source electrode and the drain electrode of the transistor can be overlapped with a gate electrode without decreasing the source-drain current of the transistor, whereby on-state characteristics can be increased. Further, in the structure shown in FIG. 5A, the coverage failure with the gate insulating layer can be decreased, which enables the oxide semiconductor layer 10 and the gate insulating layer to be thin.

[0144]

Further, in particular, in the structure shown in FIG. 5A described in this embodiment, the insulating layer 491 provided with the embedded conductive layers 481a and 481b is provided under the transistor 440 such that the embedded conductive 15 layer 481a, 481b is overlapped with the first conductive layer 405a, 405b and the second conductive layer 465a, 465b with the oxide semiconductor layer 403 provided therebetween. The structure in which the embedded conductive layers 481a and 481b are provided under the transistor 440 enables connection to another transistor and/or an external control circuit without providing an opening in the gate insulating layer 402 20 and the interlayer insulating layer 408. The embedded conductive layer 481a, 481b can be in contact with the transistor 440 in a large area, whereby contact resistance can be decreased.

[0145]

25 The embedded conductive layers 481a and 481b may be formed by the following: an embedded conductive layer is provided in each opening formed in the insulating layer 491 to fill the opening, and the surface is polished by a CMP method.

[0146]

As the embedded conductive layers 481a and 481b, for example, a metal film containing an element selected from Al, Cr, Cu, Ta, Ti, Mo, and W, a metal nitride film 30 containing any of the above elements as its component (e.g., a titanium nitride film, a

molybdenum nitride film, or a tungsten nitride film), or the like can be used.

[0147]

In the case where a metal film of Al, Cu, or the like is used for the embedded conductive layers 481a and 481b, it is preferable that a film of a high-melting-point metal such as Ti, Mo, or W or a metal nitride film thereof (e.g., a titanium nitride film, a molybdenum nitride film, or a tungsten nitride film) be stacked over or/and below the metal film.

[0148]

Further, the embedded conductive layers 481a and 481b may also be formed using a conductive metal oxide. As the conductive metal oxide, indium oxide ( $In_2O_3$ ), tin oxide ( $SnO_2$ ), zinc oxide ( $ZnO$ ), indium oxide-tin oxide ( $In_2O_3-SnO_2$ ; abbreviated to ITO), indium oxide-zinc oxide ( $In_2O_3-ZnO$ ), or any of these metal oxide materials to which silicon oxide is added can be used.

[0149]

The insulating layer 491 can be formed by a CVD method, a sputtering method, or the like. The insulating layer 491 is preferably formed so as to include a silicon oxide, a silicon nitride, a silicon oxynitride, a silicon nitride oxide, an aluminum oxide, a hafnium oxide, a tantalum oxide, or the like. The insulating layer 491 has either a single-layer structure or a stacked-layer structure.

[0150]

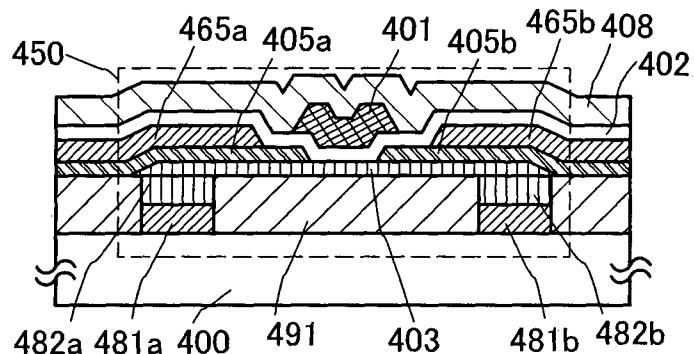

FIG. 5B is a cross-sectional diagram of a transistor 450 whose structure is different from that shown in FIG. 5A.

[0151]

The transistor 450 includes, over a substrate 400 having an insulating surface, an insulating layer 491 provided with embedded conductive layers 481a and 481b and embedded oxide semiconductor layers 482a and 482b, an oxide semiconductor layer 403, first conductive layers 405a and 405b, second conductive layers 465a and 465b, a gate insulating layer 402, a gate electrode layer 401, and an interlayer insulating layer 408 (see FIG. 5B).

[0152]

In the structure shown in FIG. 5B, like the structure shown in FIG. 1, the first conductive layers 405a and 405b, which function as a source and drain electrodes of the transistor 450, are overlapped with the gate electrode layer 401 with the gate insulating layer 402 provided therebetween, in respective regions of the first conductive layers 5 405a and 405b which are overlapped with the oxide semiconductor layer 403. In addition, in the structure shown in FIG. 5B, like the structure shown in FIG. 1, the second conductive layers 465a and 465b, which function as a source and drain electrodes of the transistor 450, are not overlapped with the gate electrode layer 401 with the gate insulating layer 402 provided therebetween, in respective regions of the 10 second conductive layers 465a and 465b which are overlapped with the oxide semiconductor layer 403.

[0153]

Accordingly, in the structure shown in FIG. 5B, the source electrode and the drain electrode of the transistor can be overlapped with a gate electrode without 15 decreasing the source-drain current of the transistor, whereby on-state characteristics can be increased. Further, in the structure shown in FIG. 5B, the coverage failure with the gate insulating layer can be decreased, which enables the oxide semiconductor layer and the gate insulating layer to be thin.

[0154]

20 Further, in particular, in the structure shown in FIG. 5B described in this embodiment, the insulating layer 491 provided with the embedded conductive layers 481a and 481b and the embedded oxide semiconductor layers 482a and 482b is provided under the transistor 450 such that the embedded conductive layer 481a, 481b and embedded oxide semiconductor layer 482a, 482b are overlapped with the first 25 conductive layer 405a, 405b and the second conductive layer 465a, 465b with the oxide semiconductor layer 403 provided therebetween. The structure in which the embedded conductive layers 481a and 481b are provided under the transistor 450 enables connection to another transistor and/or an external control circuit without providing an opening in the gate insulating layer 402 and the interlayer insulating layer 408. Further, 30 the structure in which the embedded oxide semiconductor layer 482a, 482b is provided

between the transistor 450 and the embedded conductive layer 481a, 481b enables good connection between the embedded conductive layer 481a, 481b and the transistor 450. The embedded conductive layer 481a, 481b can be in contact with the transistor 450 in a large area, and the embedded oxide semiconductor layer 482a, 482b enables good connection to the transistor 450, whereby contact resistance can be decreased.

5 [0155]

The embedded oxide semiconductor layers 482a and 482b preferably contain at least indium (In) or zinc (Zn). In particular, In and Zn are preferably contained. As a stabilizer for reducing variation in electrical characteristics of the transistor using the 10 oxide semiconductor, gallium (Ga) is preferably added thereto. Tin (Sn) is preferably contained as a stabilizer. Hafnium (Hf) is preferably contained as a stabilizer. Aluminum (Al) is preferably contained as a stabilizer. Zirconium (Zr) is preferably contained as a stabilizer.

15 [0156]

The embedded oxide semiconductor layers 482a and 482b may also be formed using a metal oxide which is an oxide semiconductor layer with electrical conductivity. As the conductive metal oxide, indium oxide ( $In_2O_3$ ), tin oxide ( $SnO_2$ ), zinc oxide ( $ZnO$ ), indium oxide-tin oxide ( $In_2O_3-SnO_2$ ; abbreviated to ITO), indium oxide-zinc oxide ( $In_2O_3-ZnO$ ), or any of these metal oxide materials to which silicon oxide is added can be 20 used.

[0157]

FIG. 6A is a cross-sectional diagram of a transistor 460 which is an example which is different from the structure of the semiconductor device shown in FIG. 5A.

[0158]

25 The transistor 460 includes, over a substrate 400 having an insulating surface, an insulating layer 491 provided with embedded conductive layers 481a and 481b, an oxide semiconductor layer 403, first conductive layers 405a and 405b, second conductive layers 465a and 465b, a gate insulating layer 402, a gate electrode layer 401, and an interlayer insulating layer 408 (see FIG. 6A).

30 [0159]