(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3670151号 (P3670151)

(45) 発行日 平成17年7月13日(2005.7.13)

(24) 登録日 平成17年4月22日 (2005.4.22)

(51) Int.C1.<sup>7</sup>

FI

GO6F 12/16 G11C 29/00 GO6F 12/16 31OP G11C 29/00 6O1B

請求項の数 9 (全 16 頁)

(21) 出願番号

特願平11-22990

(22) 出願日

平成11年1月29日 (1999.1.29)

(65) 公開番号 (43) 公開日 特開2000-222291 (P2000-222291A) 平成12年8月11日 (2000.8.11)

審査請求日

平成12年8月11日 (2000.8.11) 平成14年3月28日 (2002.3.28)

(73)特許権者 000134109

株式会社デジタル

大阪府大阪市住之江区南港東8丁目2番5

2号

||(74)代理人 100080034

弁理士 原 謙三

|(72)発明者 石川 博一

大阪府大阪市住之江区南港東8-2-52

株式会社デジタル内

審査官 須原 宏光

||(56)参考文献 特開平O5-2O4561(JP、A)

(58)調査した分野 (Int.Cl.<sup>7</sup>, DB名)

G06F12/16

(54) 【発明の名称】 フラッシュメモリのアクセス方法、フラッシュメモリへアクセスするドライバを備えるシステム 、および、フラッシュメモリ

# (57)【特許請求の範囲】

#### 【請求項1】

フラッシュメモリに設けられたセクタへデータを書き込む際、誤り訂正符号を用いてデータを書き込む書き込み工程と、

アクセス指示に対応する物理アドレスへ配された、データセクタにアクセスする第 1 アクセス工程と、

当該データセクタの制御エリアに格納され、当該データセクタが不良セクタであるか否かを示す良否識別コードに基づいて、当該データセクタが正常であるか否かを判定すると共に、当該データセクタが不良セクタだった場合、当該データセクタに対応する物理アドレスに配されたテーブルセクタから、上記データセクタの代替となるスペアセクタを示す対応情報を読み出し、当該スペアセクタへアクセスする第2アクセス工程と、

<u>当該テーブルセクタの制御エリアに格納され、当該テーブルセクタが不良セクタであるか否かを示す良否識別コードに基づいて、当該テーブルセクタが正常であるか否かを判定すると共に、当該</u>テーブルセクタが不良セクタだった場合、スペアセクタが配されるスペアセクタ領域から、テーブルセクタのスペアセクタを探索する探索工程と、

発見したスペアセクタに格納された対応情報に基づいて、上記データセクタのスペアセクタへアクセスする第3アクセス工程と、

<u>アクセスする際に</u>上記誤り訂正符号に基づいて<u>誤りが発生しているか否かを確認し、</u>アクセスしたセクタに誤りを検出した場合、検出した誤り量が、誤り訂正符号で訂正可能な 範囲の間に、誤りの発生したセクタが、上記スペアセクタ領域内で未使用のスペアセクタ

で代替されるように、誤りが発生したセクタに関連するテーブルセクタを更新する更新工程とを備えていることを特徴とするフラッシュメモリのアクセス方法。

#### 【請求項2】

上記更新工程は、テーブルセクタに誤りが発生した場合、上記スペアセクタ領域のうち、各データセクタのスペアセクタが割り当てられる側とは逆の端部から順番に、テーブルセクタのスペアセクタを割り当て、当該スペアセクタへ、代替するテーブルセクタを示す情報を書き込む工程を含み、

上記探索工程は、上記端部から順番にテーブルセクタのスペアセクタを探索することを 特徴とする請求項 1 記載のフラッシュメモリのアクセス方法。

#### 【請求項3】

<u>上記アクセスは、データの読み出しであることを特徴とする請求項1または2記載のフラッシュメモリのアクセス方法。</u>

### 【請求項4】

<u>フラッシュメモリヘアクセスするドライバを備えるシステムであって、</u>

<u>当該ドライバは、フラッシュメモリに設けられたセクタへデータを書き込む際、誤り訂</u> 正符号を用いてデータを書き込むものであり、

<u>上記ドライバは、アクセス指示に対応する物理アドレスへ配された、データセクタにア</u>クセスする第1アクセス処理と、

当該データセクタの制御エリアに格納され、当該データセクタが不良セクタであるか否かを示す良否識別コードに基づいて、当該データセクタが正常であるか否かを判定すると共に、当該データセクタが不良セクタだった場合、当該データセクタに対応する物理アドレスに配されたテーブルセクタから、上記データセクタの代替となるスペアセクタを示す対応情報を読み出し、当該スペアセクタへアクセスする第2アクセス処理と、

当該テーブルセクタの制御エリアに格納され、当該テーブルセクタが不良セクタである か否かを示す良否識別コードに基づいて、当該テーブルセクタが正常であるか否かを判定 すると共に、当該テーブルセクタが不良セクタだった場合、スペアセクタが配されるスペ アセクタ領域から、テーブルセクタのスペアセクタを探索する探索処理と、

発見したスペアセクタに格納された対応情報に基づいて、上記データセクタのスペアセクタへアクセスする第3アクセス処理と、

アクセスする際に上記誤り訂正符号に基づいて誤りが発生しているか否かを確認し、アクセスしたセクタに誤りを検出した場合、検出した誤り量が、誤り訂正符号で訂正可能な範囲の間に、誤りの発生したセクタが、上記スペアセクタ領域内で未使用のスペアセクタで代替されるように、誤りが発生したセクタに関連するテーブルセクタを更新する更新処理とを行うものであることを特徴とするシステム。

### 【請求項5】

さらに、上記ドライバが行う上記更新処理には、テーブルセクタに誤りが発生した場合、上記スペアセクタ領域のうち、各データセクタのスペアセクタが割り当てられる側とは逆の端部から順番に、テーブルセクタのスペアセクタを割り当て、当該スペアセクタへ、代替するテーブルセクタを示す情報を書き込む処理が含まれ、

<u>上記探索処理は、上記端部から順番にテーブルセクタのスペアセクタを探索する処理で</u> あることを特徴とする請求項 4 記載のシステム。

#### 【請求項6】

<u>上記アクセスは、データの読み出しであることを特徴とする請求項4または5記載のシ</u>ステム。

#### 【請求項7】

<u>誤り訂正符号で符号化されたデータが格納されている複数のセクタを備えたフラッシュ</u> メモリであって、

<u>上記各セクタには、自</u>らの良否が記録されていると共に、

<u>上記各セクタは、各論理アドレスに格納すべき情報が格納され、かつ、アクセスするセクタを特定する論理アドレスに対応する物理アドレスに配されているデータセクタと、</u>

10

30

40

20

所定のスペアセクタ領域に配され、不良が発生したセクタに格納すべき情報が格納され ているスペアセクタと、

上記論理アドレスに対応する物理アドレスに配され、上記データセクタを代替するスペ アセクタを示す対応情報が格納されていると共に、上記誤り訂正符号に基づいてアクセス したセクタに誤りが発生していた場合に、検出した誤り量が上記誤り訂正符号で訂正可能 な範囲の間に、当該セクタが上記スペアセクタ領域内で未使用のスペアセクタで代替され るように、上記対応情報のうち、誤りが発生したセクタに関連する対応情報が更新される テーブルセクタとに分けられ、

上記スペアセクタのうち、テーブルセクタを代替す<u>るスペアセクタは、上記スペアセク</u> 夕領域のうち、データセクタのスペアセクタとは逆の端部から順番に配されていると共に 、当該テーブルセクタのスペアセクタには、代替するテーブルセクタを示すセクタ情報が 記録されていることを特徴とするフラッシュメモリ。

### 【請求項8】

上記アクセスは、データの読み出しであることを特徴とする請求項7記載のフラッシュ メモリ。

#### 【請求項9】

請求項1、2または3記載のフラッシュメモリのアクセス方法で生成される信号を受け 入れるための信号線を備えていることを特徴とするフラッシュメモリ。

【発明の詳細な説明】

### [0001]

【発明の属する技術分野】

本発明は、フラッシュメモリ内に不良セクタが生じても、アクセス時間を余り増大させず に、当該セクタを代替することで、信頼性の高いフラッシュメモリを実現可能なフラッシ ュメモリのアクセス方法、および、その方法でアクセスするためのデータが格納されたフ ラッシュメモリに関するものである。

### [0002]

# 【従来の技術】

従来から、例えば、FA( Factory Automation )用途のコンピュータなど、他の用途よ りも劣悪な周囲環境で使用される機器では、信頼性を向上させるために、不揮発性の記録 媒体としても、可動部分を持たない半導体記録媒体が好適に使用されている。しかしなが ら、これらの半導体記録媒体では、情報の記録に半導体素子を使用するため、磁気や光を 用いた記録媒体に比べて、記録容量が小さく、記録容量の増大が強く要求されている。

#### [00003]

この要求に応えるために、従来の1ビット毎に読み書き可能なEEPROMのように、1 メモリセルに 2 個の素子を用いる半導体記録媒体に代えて、例えば、AND型のフラッシ ュメモリのように、1メモリセルを1個の素子で実現して、記録容量を増加させた半導体 記録媒体が普及しつつある。

### [0004]

上記AND型のフラッシュメモリでは、消去や書き込みの際に、基板と浮遊ゲートとの間 で電荷が受け渡され、トンネル酸化膜中を電荷が移動する。一方、電圧が印加されていな い状態や読み出しの際には、上記トンネル酸化膜により基板と浮遊ゲートとの間が絶縁さ れ、電荷を保持している。

### [0005]

ここで、AND型のフラッシュメモリの記録容量を増加させるためには、集積度を向上さ せる必要があり、トンネル酸化膜の膜厚を薄くすることが求められるが、トンネル酸化膜 の膜厚を薄くすれば、長期間電荷を保持することが難しくなる。特に、上記AND型のフ ラッシュメモリでは、消去や書き込みの際にトンネル酸化膜中を電荷が移動して、トンネ ル酸化膜が劣化する虞れがある。したがって、上記トンネル酸化膜の膜厚は、劣化を見込 んで設定する必要がある。さらに、トンネル酸化膜の膜厚は、製造時のプロセスバラツキ によって変動するため、マージンを低く設定すると、歩留りが低下してしまう。これらの

20

10

30

40

結果、情報記録の信頼性を向上させるためには、余りトンネル酸化膜の膜厚を薄く設定できない。

### [0006]

このように、AND型のフラッシュメモリでは、大容量化と信頼性との両立が困難であるため、大容量化が特に要求される場合には、誤り訂正符号(ECC)によって符号化した上で記録されることもある。

### [0007]

# 【発明が解決しようとする課題】

しかしながら、上記AND型のフラッシュメモリでは、ビット誤りが蓄積されていくため、誤り訂正符号を用いたとしても、長期間、高い信頼性を維持することが難しいという問題を生じる。

#### [00008]

具体的には、AND型のフラッシュメモリでは、上述したように、書き換え(消去)の際、トンネル酸化膜が劣化して、電圧が印加されていない期間に、電荷を保持できなくなってしまう。ここで、トンネル酸化膜の劣化は、回復できないため、1度ビット誤りが発生したメモリセルは、その後もビット誤りが発生する可能性が高くなり、ビット誤りが蓄積されていく。この結果、長期間使用すると、誤り訂正符号でも訂正できなくなり、情報が失われてしまう。

#### [0009]

本発明は、上記の問題点に鑑みてなされたものであり、その目的は、フラッシュメモリ内に不良セクタが生じても、アクセス時間を余り増大させずに、当該セクタを代替して、信頼性の高いフラッシュメモリを実現することにある。

### [0010]

#### 【課題を解決するための手段】

本発明に係るフラッシュメモリのアクセス方法は、上記課題を解決するために、フラッシュメモリに設けられたセクタヘデータを書き込む際、誤り訂正符号を用いてデータを書き込む書き込み工程を含むフラッシュメモリのアクセス方法において、以下の手段を講じたことを特徴としている。

# [0011]

すなわち、アクセス指示に対応する物理アドレスへ配された、データセクタにアクセスする第1アクセス工程と、アクセスしたデータセクタが不良セクタだった場合、当該データセクタに対応する物理アドレスに配されたテーブルセクタから、上記データセクタの代替となるスペアセクタを示す対応情報を読み出し、当該スペアセクタが配されるスペアセクタが不良セクタだった場合、スペアセクタが配されるスペアセクタ領域から、テーブルセクタのスペアセクタを探索する探索工程と、発見したスペアセクタに格納された対応情報に基づいて、上記データセクタのスペアセクタに誤りを検出した場合、検出した誤り量が、誤り訂正符号で訂正可能な範囲の間に、誤りの発生したセクタが、上記スペアセクタ領域内で未使用のスペアセクタで代替されるように、誤りが発生したセクタに関連するテーブルセクタを更新する更新工程とを備えている。

# [0012]

上記構成によれば、データセクタの物理アドレスとアクセス指示とが対応しているので、特に、両者の変換テーブルを参照しなくても、例えば、算術演算などによって、両者を変換できる。したがって、正常なデータセクタ(大体のデータセクタ)に関して、1セクタへのアクセスで、フラッシュメモリへのアクセスが終了する。この結果、変換テーブルを参照する場合よりも、アクセス速度が短縮できる。また、アクセスされるセクタ数が少ないので、不良セクタに遭遇する可能性も低い。

### [0013]

一方、データセクタが不良セクタであった場合は、当該データセクタに対応する物理アドレスに配されたテーブルセクタから、上記データセクタの代替となるスペアセクタを示す

10

20

30

40

20

30

40

50

対応情報を読み出し、当該スペアセクタヘアクセスする。この場合、テーブルセクタの物理アドレスと、データセクタとが対応しているので、上記と同様に、変換テーブルなしに、両者を変換でき、データセクタとテーブルセクタとの双方が不良セクタではない限り(ほとんどの場合)、データセクタおよびテーブルセクタへのアクセスが付加されるだけで、所望のデータが格納されたスペアセクタヘアクセスできる。この結果、テーブルセクタの物理アドレスとテーブルセクタとの変換テーブルを参照する場合よりも、不良セクタに遭遇する可能性が少なく、かつ、アクセス速度を向上できる。

### [0014]

また、テーブルセクタが不良セクタであった場合は、スペアセクタが配されるスペアセクタ領域から、テーブルセクタのスペアセクタが探索される。この結果、いずれの物理アドレスに配されたセクタが不良になるかを予測しにくいフラッシュメモリにおいて、データセクタ、スペアセクタおよびテーブルセクタのいずれのセクタが不良セクタであっても、所望のデータが格納されたセクタヘアクセスできる。

### [0015]

なお、この場合は、データセクタが正常な場合や、テーブルセクタが正常な場合よりもアクセス速度が低下するが、フラッシュメモリに不良セクタが発生する可能性は、例えば、実施形態で用いたフラッシュメモリの場合で 0 . 2 %以下など、十分に低いので、両者が不良セクタである可能性は極めて低く、ほとんどの場合で、速いアクセス速度を維持できる。

# [0016]

ところで、データセクタのスペアセクタや、テーブルセクタのスペアセクタを割り当てる方法は、種々の方法が考えられるが、例えば、それぞれに専用の領域を設ける場合は、いずれか一方の領域を全て使い切ってしまうと、他方の領域に空いているスペアセクタが存在しても、同じ割り当て方法では、スペアセクタを割り当てることができなくなり、メモリ効率が低下してしまう。ところが、フラッシュメモリでは、いずれの物理アドレスのセクタに不良が発生するかを予測しにくいので、上記両領域の大きさを適切に設定することが難しい。この結果、メモリ効率の低下を防止するためには、一方の領域を使い切ったか否かによって、空いているスペアセクタの探索方法を変更する必要があり、探索方法が複雑になる虞れがある。

# [0017]

これに対して、本発明に係るフラッシュメモリのアクセス方法は、上記構成に加えて、上記更新工程は、テーブルセクタに誤りが発生した場合、上記スペアセクタ領域のうち、各データセクタのスペアセクタが割り当てられる側とは逆の端部から順番に、テーブルセクタのスペアセクタを割り当て、当該スペアセクタへ、代替するテーブルセクタを示すセクタ情報を書き込む工程を含み、上記探索工程は、上記端部から順番にテーブルセクタのスペアセクタを探索することを特徴としている。

# [0018]

上記構成によれば、スペアセクタ領域の空き領域は、データセクタのスペアセクタと、データセクタのスペアセクタとの間に配されるので、予めそれぞれに専用の領域を設ける必要がない。したがって、データセクタの不良セクタ数とテーブルセクタの不良セクタ数との比率が、どのような比率であっても、空いているスペアセクタの探索方法を変更せずに、空いているスペアセクタを使い切ることができる。この結果、探索方法を複雑にすることなくメモリ効率を向上できる。

# [0019]

一方、本発明に係るフラッシュメモリは、誤り訂正符号で符号化されたデータが格納されている複数のセクタを備えたフラッシュメモリであって、上記課題を解決するために、上記各セクタには、自らの良否が記録されていると共に、上記各セクタは、各論理アドレスに格納すべき情報が格納され、かつ、アクセスするセクタを特定する論理アドレスに対応する物理アドレスに配されているデータセクタと、所定のスペアセクタ領域に配され、不良が発生したセクタに格納すべき情報が格納されているスペアセクタと、上記論理アド

レスに対応する物理アドレスに配され、上記データセクタを代替するスペアセクタを示す 対応情報が格納されているテーブルセクタとに分けられ、上記スペアセクタのうち、テー ブルセクタを代替するスペアセクタは、上記スペアセクタ領域のうち、データセクタのス ペアセクタとは逆の端部から順番に配されていると共に、当該テーブルセクタのスペアセ クタには、代替するテーブルセクタを示すセクタ情報が記録されていることを特徴として いる。

#### [0020]

上記データ構造が、フラッシュメモリに格納されていれば、上<u>記ア</u>クセス方法にて、フラッシュメモリへアクセスできる。この結果、データセクタが正常な場合、すなわち、大体の論理ブロックへのアクセスする場合の速度は、スペアセクタを設けない場合と同一に保つことができる。また、データセクタとテーブルセクタとの双方が不良セクタではない場合、すなわち、ほとんどの論理ブロックへアクセスする場合の速度は、余り低下しない

# [0021]

さらに、テーブルセクタが不良セクタの場合であっても、スペアセクタ領域のうち上記端部から順番に、所望のテーブルセクタを示すセクタ情報が格納されているスペアセクタを探索することで、確実にテーブルセクタのスペアセクタを見いだすことができる。

#### [0022]

この結果、全体的に余りアクセス速度を低下させずに、いずれの物理アドレスのセクタに不良が発生しても、当該セクタをスペアセクタで代替でき、フラッシュメモリの信頼性を向上できる。

### [0023]

# 【発明の実施の形態】

本発明の一実施形態について図1ないし図9に基づいて説明すると以下の通りである。すなわち、本実施形態に係るAND型のフラッシュメモリ(フラッシュEEPROM)は、他の型のフラッシュメモリと同様に、電力が供給されていない状態でも格納された情報を保持可能であり、可動部分を持たない。また、OR型など、他の型のフラッシュメモリに比べて、低コストで容量を増大させやすい。したがって、例えば、FA(Factory Automation )用途でのマン・マシン・インターフェースとなるグラフィック操作パネルなど、劣悪な周囲環境での安定動作が要求されるシステムでの大容量記録媒体として、特に好適に使用できる。

# [0024]

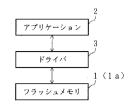

上記グラフィック操作パネルは、例えば、図2に示すように、上記フラッシュメモリ1と、フラッシュメモリ1に格納された情報を利用するアプリケーション2と、アプリケーション2からの要求に応じて、フラッシュメモリ1にアクセスするドライバ3とを備えている。なお、上記アプリケーション2およびドライバ3は、インターフェース用ICを介してフラッシュメモリ1へアクセス可能なCPU、または、その機能を有するCPU自体が、ROMやRAMなどの記憶媒体に記憶されたプログラムを実行することに実現される機能ブロックである。

### [0025]

上記アプリケーション 2 は、記録媒体として、後述するセクタ長が異なるフラッシュメモリ、あるいは、OA(Office Automation)用途のコンピュータで使用されるフロッピーディスクなど、実際のアクセス方法が異なる他の記録媒体を使用する場合であっても、同一の方法でアクセスできるように、アクセスするアドレスやアクセスする長さなどを、論理的なブロックで指示しており、上記ドライバ 3 が、自らで使用されているフラッシュメモリ1に応じた方法でアクセスしている。これにより、他の記録媒体を使用する場合であっても、アプリケーション 2 の移植性を向上させている。また、ドライバ 3 が論理ブロック長に拘わらず、フラッシュメモリ 1 に適したセクタ長でアクセスするので、両者の相違に起因するメモリ効率の低減を防止できる。

### [0026]

10

20

30

30

40

50

ここで、本実施形態で使用されるフラッシュメモリ1では、予め命令セットが定義されており、フラッシュメモリ1は、例えば、アドレス信号、コマンド信号およびデータ信号を伝送するIO信号線や、CE信号などの制御信号を伝送する制御信号線など、フラッシュメモリ1に設けられた信号線を介して命令セット中の命令が指示されると、それぞれの命令に応じた処理を実行する。

### [0027]

上記フラッシュメモリ1は、AND型のフラッシュメモリであり、EEPROMに比べて、1メモリセルあたりのトランジスタ数が少なく、例えば、64Mビットや256Mビット以上と、大きな記録容量を持っている一方で、ランダムアクセス速度が遅い。したがって、上記フラッシュメモリ1では、所定長のセクタSを単位とするブロックアクセス用の命令が設けられており、当該命令を実行するために、指示されたスタートアドレスに続くアドレスを順次発生するアドレスカウンタと、順次入力される書き込みデータを蓄積する入力バッファと、順次読み出されるデータを蓄積する出力バッファとを備えている。これにより、アドレスの指定回数が削減され、かつ、各メモリセルへのアクセスと外部の入出力とが並列して実施されるので、フラッシュメモリ1のブロックアクセス時の見かけ上のアクセス速度を向上できる。

### [0028]

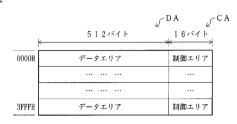

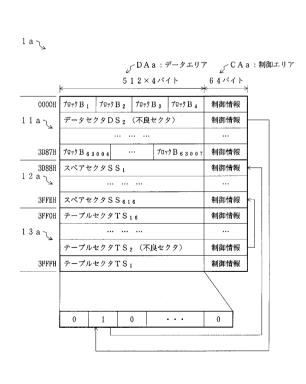

また、上記フラッシュメモリ1は、大容量化を達成するために、トンネル酸化膜の膜圧が比較的薄く設定されており、上記EEPROMに比べて、初期不良や経時劣化、あるいは、アクセスの繰り返しに起因する不良などが発生する確率が高くなっている。したがって、図3に示すように、フラッシュメモリ1は、冗長な構成となっており、各セクタSには、データを格納するデータエリアDAに加えて、制御エリアCAが設けられている。

### [0029]

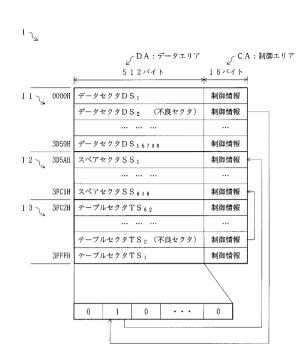

図3に例示するフラッシュメモリ1では、メモリ容量(全データエリアDAの容量)が64Mビットであり、セクタ長(データエリアDAの長さ)が512バイト、制御エリアCAの長さが16バイトに設定されている。この場合、全セクタ数は、16384セクタであり、各セクタSを特定するセクタアドレスは、0000H~3FFFH(数字の末尾のHはその数字が16進数であることを示す)の範囲となる。また、出荷時には、16384セクタのうち、16057セクタを使用できることが保証されている。

# [0030]

当該フラッシュメモリ1では、読み込みあるいは書き込みなどのアクセスは、セクタSを単位として行われており、当該セクタS全体を読み書きするシリアルリード命令 r 1 およびプログラム命令 p 1 が設けられている。さらに、上記制御エリアCAへアクセスするために、シリアルリード命令 r 2、プログラム命令 p 3 も設けられている。当該命令 r 2・p 3 では、制御エリアCAのみが読み出されるため、データエリアDAとは用途が異なり、単独でアクセスする可能性がある制御エリアCAへのアクセス速度を、セクタS全体を読み書きする場合よりも向上できる。なお、上記各プログラム命令 p 1・p 3 では、書き込む前に、消去が行われるが、消去のみを行う消去命令 e 1 や、予め消去されている場合に使用され、消去せずに書き込むプログラム命令 p 2 なども規定されている。

#### [0031]

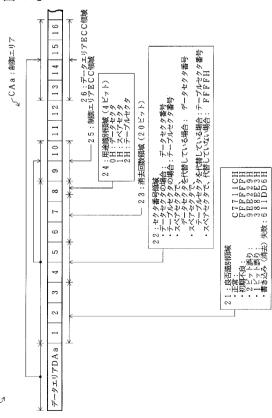

本実施形態に係るドライバ3は、上記フラッシュメモリ1に対して、予め、以下に示すフォーマットを施した後で、フラッシュメモリ1へアクセスする。具体的には、図1に示すように、上記フラッシュメモリ1は、不良が発生していない場合にアクセスされるデータセクタDSを格納するデータセクタ領域11と、不良セクタを代替するスペアセクタSSが格納されるスペアセクタ領域12と、データセクタDSとスペアセクタSSとの対応を示すテーブルセクタTSが記録されるバッドセクタテーブル領域13とに分割されている

# [0032]

なお、以下では、各データセクタDSを特定する場合、データセクタ領域11の始め(セクタアドレスの小さい方)から順番に付したデータセクタ番号dnで区別し、各スペアセ

30

40

50

クタSSを特定する場合、スペアセクタ領域12の始めから順番に付したスペアセクタ番号snで区別する。一方、バッドセクタテーブル領域13では、各テーブルセクタTSを特定するテーブルセクタ番号tnが、バッドセクタテーブル領域13の末尾から順番に付されている。また、各セクタSを区別する場合は、例えば、データセクタ番号dnが1のデータセクタDSは、データセクタDS、などのように、各セクタ番号dn・sn・tnを添字で付して表現する。

#### [0033]

上記バッドセクタテーブル領域 13 には、各データセクタDSのデータセクタ番号 d n に対応する位置に、それぞれを代替するスペアセクタSSのスペアセクタ番号(対応情報) s n が格納されている。本実施形態では、スペアセクタ番号を 2 バイトで表現できるため、各テーブルセクタTSには、 256 個のスペアセクタ番号が格納できる。したがって、例えば、データセクタDS $_2$  に対応するスペアセクタ番号 s n (この例では、 1) は、テーブルセクタTS $_1$  の 2 番目(第 3 バイトから第 4 バイトまで)に格納されている。また、この例では、他のデータセクタDSは、不良セクタではないため、テーブルセクタTS $_1$  の残余のバイトは、スペアセクタSSが対応していないことを示す値(この例では、 0 )が格納されている。

### [0034]

例えば、本実施形態に係るフラッシュメモリ1では、出荷時に正常動作が保証されている16057セクタのうち、0.18%、すなわち、616セクタをスペアセクタSSとして割り当てている。また、全セクタSのうち、スペアセクタSSを除いたセクタSを代替するために、全セクタ数をT1、スペアセクタ数をT2、1テーブルセクタTS当たりに格納可能なスペアセクタ番号snの個数をT3とすると、(T1・T2)/T3=61.59...なので、62セクタがテーブルセクタTSとして割り当てられている。したがって、残余の15706セクタ、すなわち、セクタアドレスが0000H~3D59Hの範囲(データエリアDAの記録容量で7853kバイト)が、データセクタ領域11となり、続く、3D5AH~3FC1Hまでの範囲(308kバイト)がスペアセクタ領域12、さらに、3FC2H~3FFFHまでの範囲(31kバイト)がバッドセクタテーブル領域13に設定される。

# [0035]

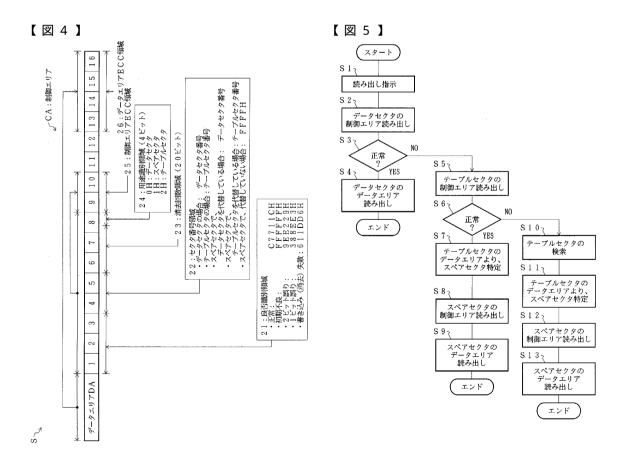

また、各セクタSの制御エリアCAは、それぞれ、図4に示す良否識別領域21、セクタ番号領域22、消去回数領域23、用途識別領域24、制御エリアECC領域25およびデータエリアECC領域26に分割されている。

#### [0036]

上記良否識別領域21は、当該セクタSが不良セクタであるか否かを示す良否識別コードが格納されている。各良否識別コードは、例えば、各コード間のハミング距離を十分に長く設定するなどして、アクセス時にビットエラーが発生しても、それぞれを区別できるように決定されている。例えば、本実施形態では、良否識別領域21が第1~第3バイト目までの3バイト幅に設定されており、各良否識別コードとして、正常を示すコード(C7711CH)、初期不良を示すコード(FFFFFFH)、2ビット誤りを示すコード(9EE229H)、1ビット誤りを示すコード(388EE3H)、並びに、書き込みや消去に失敗したことを示すコード(611DD6H)が決められている。

#### [0037]

また、セクタ番号領域22は、セクタ番号dnまたはtnを格納するために、第4および第5バイト目の2バイト幅に設定されており、データセクタDSの場合、データセクタ番号dnが格納され、テーブルセクタTSの場合は、テーブルセクタ番号tnが格納される。一方、スペアセクタSSで、データセクタDSを代替している場合は、当該データセクタDSのデータセクタ番号dn、テーブルセクタTSを代替している場合は、当該テーブルセクタTSのテーブルセクタ番号(セクタ情報)tnが格納される。また、スペアセクタSSが、いずれのセクタSをも代替していない場合は、代替していないことを示す値(例えば、FFFFH)が格納される。

#### [0038]

さらに、上記消去回数領域23には、消去回数(書き換え回数)が格納されている。フラッシュメモリ1では、正常に書き換えできると保証されている回数が例えば、10万回程度であり、この回数を越えて書き換えた場合、正常な書き換えが保証されない。したがって、書き換え毎に消去回数領域23に格納されているカウント値を増加させ、当該カウント値が所定の値を越えた場合、スペアセクタSSで代替するなどすれば、書き換え回数の超過に起因するアクセス不良を事前に防止できる。本実施形態では、第6~第8バイト目までのうちの20ビットが消去回数領域23として割り当てられている。

#### [0039]

また、用途識別領域24には、当該セクタSが、データセクタDSであるか、スペアセクタSSであるか、テーブルセクタTSであるかを示すコードが格納されている。図4の例では、用途識別領域24は、制御エリアCAの第8バイト目のうち、消去回数領域23を除いた4ビットである。

# [0040]

ところで、上述したように、フラッシュメモリ1では、初期不良あるいは経時変化によって、ビット誤りが発生する。したがって、ビット誤りが発生しても、誤りを訂正できるように、制御エリアCAおよびデータセクタDSが誤り訂正符号(ECC)で符号化されており、制御エリアCAには、それぞれの誤り訂正符号を格納するために、制御エリアECC領域25およびデータエリアECC領域26が設けられている。上記制御エリアECC領域25は、第9および第10バイト目の2バイト幅に設定され、上記各領域21~24の誤り訂正符号を格納している。また、データエリアECC領域26は、第13~第16バイト目までの4バイトである。なお、第11~第12バイト目は、将来の拡張のために確保されており、5AA5Hが格納されている。

#### [0041]

本実施形態では、例えば、1ビット誤りを訂正可能で、2ビット誤りを検出可能な誤り訂正符号が使用されており、発生したビット誤りが訂正可能なうちに、当該セクタSの正しい情報をスペアセクタSSへ代替する。これにより、情報を損失することなく、各セクタSをスペアセクタSSで代替できる。

# [0042]

これらの結果、アクセスするデータセクタDSが不良セクタであっても、当該データセクタDSに対応する位置に配されたテーブルセクタTSを参照すれば、データセクタDSのスペアセクタSSを特定でき、正常に読み書きできる。

#### [0043]

一方、テーブルセクタTSが不良セクタとなった場合は、スペアセクタ領域12の末尾から順番に、テーブルセクタTSのスペアセクタSSが割り当てられる。テーブルセクタTSのスペアセクタSSには、上述したように、代替したテーブルセクタTSのテーブルセクタ番号tnとが、制御エリアCAに格納されている。したがって、スペアセクタ領域12の末尾から探索することで、テーブルセクタTSのスペアセクタSSを特定でき、正常に読み書きできる。

# [0044]

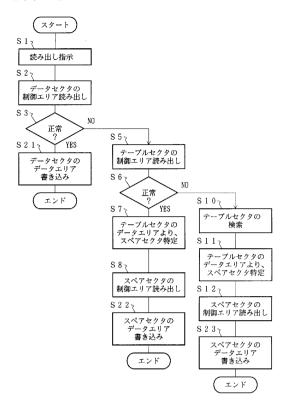

上記構成のグラフィック操作パネルにおいて、フラッシュメモリ1へアクセスする際の各部の動作を図5および図6に示すフローチャートに基づいて説明すると以下の通りである。すなわち、図5に示すステップ1(以下では、S1のように略称する)において、図2に示すアプリケーション2から、例えば、読み出しを開始する論理ブロック(開始ブロック)、読み出す論理ブロックの数、読み出したデータを格納するバッファのアドレス、および、読み出したバイト数を格納するアドレスなど、読み出しに必要なデータが指示されると、ドライバ3は、S2において、指示された論理ブロックに対応するデータセクタDSが正常であるか否かを判定するために、当該データセクタDSの制御エリアCAを読み出す。

# [0045]

20

30

アプリケーション 2 では、例えば、フロッピーディスクヘアクセスする場合と同一になるように、論理ブロックの大きさは、5 1 2 バイトに設定されている。また、本実施形態に係るフラッシュメモリ 1 では、セクタ長が 5 1 2 バイトであり、論理ブロック長と同一である。さらに、上記各データセクタDSは、番号が 0 の論理ブロックに対応するデータセクタDS 1 から、番号が 1 5 7 0 5 の論理ブロックに対応するデータセクタDS 15706 まで、論理ブロックのアドレスの順番に配されている。したがって、この例では、上記S2において、ドライバ 3 は、開始ブロックに 1 を足したデータセクタ番号 d n のデータセクタDSヘアクセスして、制御エリアCAを読み出す。

#### [0046]

さらに、ドライバ3は、S3において、制御エリアCAの良否識別領域21に格納された 良否識別コードに基づいて、当該データセクタDSが正常であるか否かを判定する。ここ で、良否識別コードが正常を示すコードの場合(S3にて YESの場合)、ドライバ3は、 S4において、当該データセクタDSのデータエリアDAを読み出して、当該データセク タDSの内容と、アプリケーション2へ読み出しが正常に終了したこととを伝える。

### [0047]

本実施形態では、論理ブロックの順番に、当該論理ブロックに対応するデータセクタDSが配されており、最初に、データセクタDSにアクセスする。したがって、論理ブロックとデータセクタDSとの対応を格納するテーブルを設けて、当該テーブルを参照しなくても、論理ブロックのアドレスから、データセクタ番号dnへ容易に変換できる。さらに、データセクタDSが正常である限り、1セクタを読み出すだけで、セクタSの内容を取得でき、アクセス速度を、代替しない場合と同様に維持できる。また、アクセスするセクタ数が少ないので、アクセスするセクタ数が多い場合と比較すると、不良セクタに遭遇する可能性が少なく、アクセス速度を短いレベルに維持できる。なお、上記S2~S4が、特許請求の範囲に記載の第1アクセス工程に対応している。

### [0048]

一方、データエリアDAが不良セクタであった場合(上記S3にてNOの場合)、ドライバ3は、特許請求の範囲に記載の第2アクセス工程に対応するS5~S9において、当該データセクタDSに対応するテーブルセクタTSへアクセスして、データセクタDSのスペアセクタSSを特定し、スペアセクタSSへアクセスする。

# [0049]

具体的には、S5 において、テーブルセクタTSの制御エリアCAが読み出され、S6 にて、当該テーブルセクタTSが正常であることが確認された後、S7 において、当該テーブルセクタTS中のデータセクタDSに対応するバイト位置から、データセクタDSのスペアセクタSSを示すスペアセクタ番号 S7 が読み出される。例えば、図1に示すように、データセクタDSS7 が不良セクタの場合は、テーブルセクタTSS7 の第2番目のスペアセクタ番号 S8 の場合は、1)が読み出される。

# [0050]

さらに、ドライバ3は、S8において、特定されたスペアセクタSSの制御エリアCAを読み出し、正常なセクタであることを確認した後、S9にて、当該スペアセクタSSのデータセクタDSを読み出して、正常終了する。なお、スペアセクタSSが不良セクタであった場合、アプリケーション2へ読み出しに失敗したことを伝える。

#### [0051]

バッドセクタテーブル領域13に、テーブルセクタTSとして格納されるスペアセクタ番号snは、バッドセクタテーブル領域13の末尾のテーブルセクタTSから、データセクタDSの順番に格納されている。したがって、特に、テーブルセクタTSとデータセクタDSとの対応を示すテーブルを設けなくても、不良が発生したデータセクタDSに対応するテーブルセクタTSnを算出できる。この結果、テーブルセクタTSが正常であれば、3つのセクタSへアクセスするだけで、所望のデータを取得でき、上記テーブルを設ける場合よりもアクセス速度を短縮できる。なお、データセクタDSの良否判定は、制御エリアCAのみの読み出しで判定されるため、データセクタDS全体を読み出す場合よりもア

10

20

30

40

クセス速度が短縮される。

### [0052]

ここで、本実施形態で使用しているフラッシュメモリ1の故障発生率は、比較的低く、全体の0.18%程度のスペアセクタ領域12を設けて、セクタSを代替すれば、10年以上データを保持でき、10万回以上、書き換えることができる。したがって、上述したように、データセクタDS、テーブルセクタTSを配すれば、ほとんどのセクタSに対して、3セクタ以内のアクセス回数でデータにアクセスできる。

### [0053]

一方、上記S6にて、テーブルセクタTSの不良が検出された場合、特許請求の範囲に記載の探索工程に対応するS10において、ドライバ3は、スペアセクタ領域12から、テーブルセクタTSのスペアセクタSSを探索する。本実施形態に係るスペアセクタSSでは、上述したように、セクタ番号領域22へ、代替するセクタ番号(dnまたはtn)が格納されている。したがって、各スペアセクタSSの制御エリアCAを順次読み出し、代替するセクタ番号を確認すれば、所望のテーブルセクタTSを代替するスペアセクタSSを発見できる。なお、スペアセクタSSを探索する際には、制御エリアCAのみが読み出されるので、セクタS全体を読み出す場合に比べて、アクセス速度が短縮されている。

#### [0054]

一方、本実施形態では、後述するように、スペアセクタ領域12中、データセクタDSのスペアセクタSSは、スペアセクタ領域12の始めから順番に配され、テーブルセクタTSのスペアセクタSSは、スペアセクタ領域12の末尾から割り当てられているので、空いているスペアセクタSSは、両者の中間に配される。したがって、データセクタDSのスペアセクタSSを格納する領域と、テーブルセクタTSのスペアセクタSSを格納する領域とを予め設定する場合とは異なり、空いているスペアセクタSSの探索方法を変更しなくても、スペアセクタ領域12を使い切ることができる。

### [0055]

ここで、フラッシュメモリ1では、どのセクタSに不良が発生するかを予測することは難しいので、データセクタ領域11に発生する不良セクタ数や、バッドセクタテーブル領域13に発生する不良セクタ数は、予測しにくい。したがって、本実施形態のようにスペアセクタSSを配すれば、上記探索方法を変更したり、不良セクタ数を予測しなくても、スペアセクタ領域12を使い切ることができ、フラッシュメモリ1のセクタSの代替に好適である。

# [0056]

上記 S 1 0 にて、テーブルセクタ T S のスペアセクタ S S が特定されると、特許請求の範囲に記載の第 3 アクセス工程に対応する S 1 1 ~ S 1 3 において、上述の S 7 ~ S 9 と同様の処理が行われ、データセクタ D S のスペアセクタ S S からデータが読み出される。

### [0057]

なお、ドライバ3は、アプリケーション2から指示された論理ブロックが複数の場合や論理ブロックが複数のデータセクタDSに対応する場合は、上記S2以降の処理を繰り返して、各データセクタDS、あるいは、そのスペアセクタSSからデータを読み出す。

### [0058]

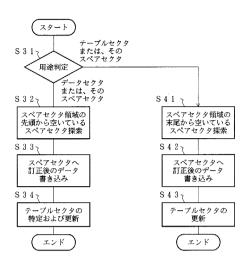

また、フラッシュメモリ1へ書き込む場合には、ドライバ3は、図6に示すように動作する。書き込みは、読み込みと略同じであるが、図5に示すS4、S9およびS13に代えて、特許請求の範囲に記載の書き込み工程に対応するS21、S22およびS23が設けられており、ドライバ3は、書き込みが指示されたデータを、正常なデータセクタDSあるいはスペアセクタSSへ書き込む。

# [0059]

ところで、ドライバ3は、各セクタSのデータセクタDSあるいは制御エリアCAにアクセスする際、当該セクタSの制御エリアCAから、制御エリアECC領域25、あるいは、データエリアECC領域26を読み出して、ビット誤りが発生しているか否かを確認している。以下では、図7に示すフローチャートを参照して、訂正可能なビット誤りが検出

10

20

30

40

30

40

50

された場合の処理について説明する。

### [0060]

すなわち、セクタSに訂正可能なビット誤りが検出されると、ドライバ3は、S31において、例えば、アクセスの状況などに基づいて、当該セクタSが、(1)データセクタDSまたはそのスペアセクタSSであるか、あるいは、(2)テーブルセクタTSまたはそのスペアセクタSSであるかを判定する。例えば、図5(図6)に示すS2・S4(S21)・S8・S9(S22)・S12・S13(S23)などでは、データセクタDS、または、そのスペアセクタSSへアクセスしていると判定され、S5・S7・S10・S11などでは、テーブルセクタTS、または、そのスペアセクタSSへアクセスしていると判定される。なお、例えば、制御エリアCAに、当該スペアセクタSSがデータセクタDSを代替しているか、テーブルセクタTSを代替しているかを示す値が書き込まれていれば、それに基づいて、スペアセクタSSの用途を判定してもよい。

#### [0061]

上記S31にて、(1)データセクタDS、または、そのスペアセクタSSと判定された場合は、S32において、空いているスペアセクタSSが探索される。本実施形態では、データセクタDSのスペアセクタSSは、スペアセクタ領域12の始めから順番に配されているので、上記S32において、ドライバ3は、スペアセクタ領域12の始めのセクタSから順番に、制御エリアCAを読み出し、例えば、セクタ番号領域22の値などに基づいて、空いているスペアセクタSSを探索する。さらに、空いているスペアセクタSSが見つかると、S33において、ドライバ3は、検出したビット誤りを訂正した後、正しいデータを当該スペアセクタSSへ書き込む。

#### [0062]

書き込みが正常に終了すると、ドライバ3は、特許請求の範囲に記載の更新工程に対応するS34において、図5のS5などと同様に、誤りが発生したデータセクタDSに関連するテーブルセクタTSを特定し、当該データセクタDSに対応するスペアセクタ番号snが、上記S33にて正しいデータを書き込んだスペアセクタ番号snになるように、上記テーブルセクタTSを更新する。また、テーブルセクタTSが不良セクタの場合は、図5に示すS10と同様に、当該テーブルセクタTSのスペアセクタSSを特定して更新する

### [0063]

なお、上記S33にて、書き込みに失敗すると、ドライバ3は、書き込みに失敗したスペアセクタSSの良否識別領域21へ、例えば、書き込みに失敗したことを示すコードなど、少なくとも、正常ではないことを示すコードを書き込んだ後、上記S32以降の処理を繰り返す。

# [0064]

一方、上記S31において、ビット誤りの発生したセクタSが、(2)テーブルセクタTSまたはそのスペアセクタSSであると判定された場合は、S41において、スペアセクタ領域12の末尾から順番に、空いているスペアセクタSSが探索される。空いているスペアセクタSSが見つかると、ドライバ3は、S42にて、ビット誤りを訂正した後のデータを当該スペアセクタSSへ書き込む。さらに、ドライバ3は、書き込みに成功したことを確認した後、特許請求の範囲に記載の更新工程に対応するS43において、ビット誤りが発生したテーブルセクタTSの良否識別領域21を書き換え、可能であれば、良否識別コードがビット誤りの状態を示すように、それが不可能な場合でも、少なくとも、良否識別コードが正常ではないことを示すように訂正される。なお、上記S42での書き込み失敗が検出されると、上記S33での失敗と同様に、少なくとも正常ではないことを示すコードが書き込まれた後、S41以降の処理が繰り返される。

#### [0065]

ところで、上記では、アプリケーション2から指示される論理ブロックの長さが、フラッシュメモリ1のセクタ長と同一である場合を例にして説明したが、これに限るものではない。例えば、図8に示すフラッシュメモリ1aでは、セクタ数は、図1に示すフラッシュ

30

40

50

メモリ 1 と同様に 3 FFFHであるが、セクタ長が 2 0 4 8 バイトに設定されており、制御エリア C A a の長さは、 6 4 バイトに設定されている。

# [0066]

この場合、全セクタ数が同じなので、スペアセクタ領域12の割合を同一に設定すると、スペアセクタSSの数は、図1の場合と同じく616セクタ(データエリアDAの記録容量で1232kバイト)である。ただし、セクタ番号(sn・dn・tn)に必要なバイト数が変わらないにも拘わらず、セクタ長が長くなっているので、1セクタに格納可能なセクタ番号の数が1024個となっており、テーブルセクタTSの数は、16個(32kパイト)で十分である。したがって、残余の15752セクタ(31504kバイト)がデータセクタDSに割り当てられる。なお、図9に示すように、制御エリアCAaの構造は、データエリアECC領域26がデータエリアDAaの誤り訂正符号を格納する他は、図4に示す制御エリアCAと同様であり、17バイト目以降は、将来の拡張に備えて確保されている。

# [0067]

また、ドライバ3は、各セクタSのデータエリアDAaを、論理ブロック長に合わせて4つのブロックBに分割し、アクセスする論理ブロックが指示されると、当該論理ブロックに対応するブロックBが含まれるセクタSにアクセスする。これにより、アプリケーション2は、セクタ長に拘わらず、アクセスする論理ブロックを指示でき、アプリケーション2の開発時の手間を削減できると共に、1論理ブロックに1セクタ割り当てる場合よりも、セクタSの利用効率を向上できる。

#### [0068]

なお、上記の説明では、データセクタ領域11におけるデータセクタDSの物理アドレスを論理セクタの順番に配し、バッドセクタテーブル領域13におけるテーブルセクタTSの物理アドレスを論理アドレスとは逆順に配したが、これに限らず、例えば、算術演算や論理演算などによって、論理アドレスから物理アドレスへ変換できれば、同様の効果が得られる。

# [0069]

#### 【発明の効果】

本発明に係るフラッシュメモリのアクセス方法は、以上のように、アクセス指示に対応する物理アドレスへ配された、データセクタにアクセスする第1アクセス工程と、アクセスしたデータセクタが不良セクタだった場合、当該データセクタに対応する物理アドレスに配されたテーブルセクタを参照して、スペアセクタへアクセスする第2アクセス工程と、テーブルセクタが不良セクタだった場合、スペアセクタ領域から、テーブルセクタのスペアセクタを探索する探索工程と、発見したスペアセクタを参照して、上記データセクタのスペアセクタへアクセスする第3アクセス工程と、誤り訂正符号で訂正可能なうちに、テーブルセクタを更新して、誤りの発生したセクタをスペアセクタで代替する更新工程とを備えている構成である。

### [0070]

上記構成では、データセクタが正常な場合や、データセクタとテーブルセクタとの双方が不良セクタではない場合など、ほとんどの論理ブロックへアクセスする場合の速度を余り低下させずに、誤りの発生したセクタを確実に代替でき、フラッシュメモリの信頼性を向上できるという効果を奏する。

### [0071]

本発明に係るフラッシュメモリのアクセス方法は、以上のように、上記構成に加えて、上記更新工程は、テーブルセクタに誤りが発生した場合、上記スペアセクタ領域のうち、各データセクタのスペアセクタが割り当てられる側とは逆の端部から順番に、テーブルセクタのスペアセクタを割り当て、当該スペアセクタへ、代替するテーブルセクタを示すセクタ情報を書き込む工程を含んでいる構成である。

### [0072]

上記構成によれば、スペアセクタ領域の空き領域は、データセクタのスペアセクタと、デ

ータセクタのスペアセクタとの間に配されるので、各セクタの不良セクタ数が、どのような比率であっても、空いているスペアセクタの探索方法を変更せずに、空いているスペアセクタを使い切ることができる。この結果、探索方法を複雑にすることなく、メモリ効率を向上できるという効果を奏する。

### [0073]

本発明に係るフラッシュメモリは、以上のように、フラッシュメモリの各セクタには、自らの良否が記録されていると共に、上記各セクタは、各論理アドレスに格納すべき情報が格納され、かつ、アクセスするセクタを特定する論理アドレスに対応する物理アドレスに配されているデータセクタと、所定のスペアセクタ領域に配され、不良が発生したセクタに格納すべき情報が格納されているスペアセクタと、上記論理アドレスに対応する物理アドレスに配され、上記データセクタを代替するスペアセクタを示す対応情報が格納されているテーブルセクタとに分けられ、上記スペアセクタのうち、テーブルセクタを代替するスペアセクタは、上記スペアセクタ領域のうち、データセクタのスペアセクタとは逆の端部から順番に配されていると共に、当該テーブルセクタのスペアセクタには、代替するテーブルセクタを示すセクタ情報が記録されている構成である。

#### [0074]

上記データ構造が、フラッシュメモリに格納されていれば、上<u>記ア</u>クセス方法にて、フラッシュメモリへアクセスできる。この結果、全体的に余りアクセス速度を低下させずに、いずれの物理アドレスのセクタに不良が発生しても、当該セクタをスペアセクタで代替でき、フラッシュメモリの信頼性を向上できるという効果を奏する。

【図面の簡単な説明】

- 【図1】本発明の一実施形態を示すものであり、フォーマット後のAND型のフラッシュ メモリに格納されているデータ構造を示す説明図である。

- 【図2】上記AND型のフラッシュメモリが含まれるシステム全体を示すブロック図である。

- 【図3】フォーマット前の上記AND型のフラッシュメモリを示す説明図である。

- 【図4】上記AND型のフラッシュメモリのセクタ構造を示す説明図である。

- 【図 5 】上記AND型のフラッシュメモリからデータを読み出す際のドライバの動作を説明するフローチャートである。

- 【図 6 】上記AND型のフラッシュメモリにデータを書き込む際のドライバの動作を説明 するフローチャートである。

- 【図7】上記AND型のフラッシュメモリにエラーが発生した場合のドライバの動作を説明するフローチャートである。

- 【図8】上記AND型のフラッシュメモリの変形例を示すものであり、当該フラッシュメモリに格納されているデータ構造を示す説明図である。

- 【図9】上記AND型のフラッシュメモリのセクタ構造を示す説明図である。

### 【符号の説明】

- 1・1a フラッシュメモリ

- 12・12a スペアセクタ領域

- DS データセクタ

- SS スペアセクタ

- TS テーブルセクタ

- sn スペアセクタ番号(対応情報)

- tn テーブルセクタ番号(セクタ情報)

20

30

# 【図1】

# 【図2】

# 【図3】

【図6】

### 【図7】

# 【図8】

# 【図9】