(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-41354

(P2006-41354A)

(43) 公開日 平成18年2月9日(2006.2.9)

(51) Int.C1.

F 1

テーマコード(参考)

HO1L 21/8247 (2006.01)

HO1L 29/792 (2006.01)

HO1L 29/788 (2006.01)

HO1L 27/115 (2006.01)

HO1L 29/78 371

HO1L 27/10 434

5FO83

5F1O1

審査請求 未請求 請求項の数 9 O L (全 43 頁)

(21) 出願番号

(22) 出願日

特願2004-221764 (P2004-221764)

平成16年7月29日 (2004.7.29)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100068504

弁理士 小川 勝男

(74) 代理人 100086656

弁理士 田中 恭助

(72) 発明者 久本 大

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 安井 感

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【要約】

【課題】 メモリセルを縮小しても読み出し電流駆動力に優れた不揮発性半導体記憶装置を提供する。

【解決手段】 スプリットゲート構造の不揮発性半導体記憶装置において、メモリゲートが凸型基板上に形成され、その側面をチャネルとして用いるようにする。

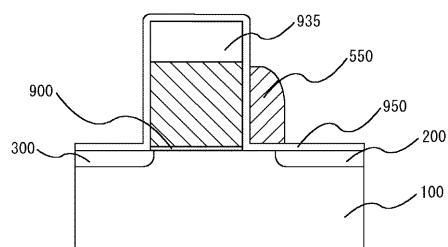

【選択図】 図43A

図 43A

## 【特許請求の範囲】

## 【請求項 1】

半導体基板と、

前記半導体基板上に形成された、第1の絶縁ゲート型電界効果トランジスタと、

前記半導体基板上に形成され且つ前記第1の絶縁ゲート型電界効果トランジスタの有する第1のゲート電極と絶縁膜を介して形成された第2のゲート電極を有する第2の絶縁ゲート型電界効果トランジスタと、を有し、

前記第1及び第2の絶縁ゲート型電界効果トランジスタの各ゲート電極と交差する方向に、

第1の拡散層電極と、

前記第1の絶縁ゲート型電界効果トランジスタの有する第1のゲート電極と当該第1のゲート電極に対応する第1のチャネル領域と、

前記第2の絶縁ゲート型電界効果トランジスタの有する第2のゲート電極と当該第2のゲート電極に対応する第2のチャネル領域と、

前記第1の拡散層電極と、前記第1のチャネル領域と第2のチャネル領域を挟んで対向する第2の拡散層電極と、を有し、

前記第2の絶縁ゲート型電界効果トランジスタのゲート絶縁膜は、電荷保持機能を有し、

前記第2のゲート電極による電圧特性の变化の寄与によって、前記第1の拡散層電極と前記第2の拡散層電極との間を流れる電流を制御し、且つ

前記第1の拡散層電極と前記第2の拡散層電極を結ぶチャネル方向に交差する方向に凸型半導体領域を有し、

前記第1の絶縁ゲート型電界効果トランジスタの有する第1のチャネル領域が、前記凸型半導体領域の側壁に形成されることを特徴とする半導体装置。

## 【請求項 2】

前記第2の絶縁ゲート型電界効果トランジスタの有する第2のチャネル領域が、前記凸型半導体領域の側壁に形成されることを特徴とする請求項1に記載の半導体装置。

## 【請求項 3】

半導体基板と、

前記半導体基板上に形成された、第1の絶縁ゲート型電界効果トランジスタと、

前記半導体基板上に形成され且つ前記第1の絶縁ゲート型電界効果トランジスタの有する第1のゲート電極と絶縁膜を介して形成された第2のゲート電極を有する第2の絶縁ゲート型電界効果トランジスタと、を有し、

前記第1及び第2の絶縁ゲート型電界効果トランジスタの各ゲート電極と交差する方向に、

第1の拡散層電極と、

前記第1の絶縁ゲート型電界効果トランジスタの有する第1のゲート電極と当該第1のゲート電極に対応する第1のチャネル領域と、

前記第2の絶縁ゲート型電界効果トランジスタの有する第2のゲート電極と当該第2のゲート電極に対応する第2のチャネル領域と、

前記第1の拡散層電極と、前記第1のチャネル領域と第2のチャネル領域を挟んで対向する第2の拡散層電極と、を有し、

前記第2の絶縁ゲート型電界効果トランジスタのゲート絶縁膜は、電荷保持機能を有し、

前記第2のゲート電極による電圧特性の变化の寄与によって、前記第1の拡散層電極と前記第2の拡散層電極との間を流れる電流を制御し、且つ

前記第1の拡散層電極と前記第2の拡散層電極を結ぶチャネル方向に交差する方向に凸型半導体領域を有し、

前記第2の絶縁ゲート型電界効果トランジスタの有する第2のチャネル領域が、前記凸型半導体領域の側壁に形成されることを特徴とする半導体装置。

10

20

30

40

50

**【請求項 4】**

前記第1の絶縁ゲート型電界効果トランジスタの有する第1のチャネル領域が、前記半導体基板の前記凸型半導体領域を除く基板面或いはこの半導体基板の上面と平行な面に形成されたことを特徴とする請求項3に記載の半導体装置。

**【請求項 5】**

半導体基板に、請求項1より請求項4の少なくともいずれかに記載の不揮発性半導体記憶装置の複数個と、絶縁ゲート型電界効果トランジスタとを有し、少なくとも一つの絶縁ゲート型電界効果トランジスタのチャネルが、前記半導体基板の前記凸型半導体領域を除く基板面或いはこの半導体基板の上面と平行な面に形成されていることを特徴とする半導体装置。

10

**【請求項 6】**

半導体基板と、

前記半導体基板に形成された第1素子分離酸化膜と、

前記半導体基板に形成された第2素子分離酸化膜と、

前記半導体基板上に、第1絶縁膜を介して形成された第1ゲート電極と、

前記半導体基板上に、第2絶縁膜を介して形成された、前記第1ゲート電極に隣接する第2ゲート電極とを有し、

前記第2絶縁膜は、電荷蓄積膜を有し、

前記第1ゲート電極は、前記第1素子分離酸化膜上に形成され、

前記第2ゲート電極は、前記第2素子分離絶縁膜上に形成され、

前記第2素子分離絶縁膜の表面は、前記第1素子分離酸化膜の表面よりも後退していることを特徴とする半導体装置。

20

**【請求項 7】**

請求項6記載の半導体装置において、

更に、前記半導体基板に形成された第3素子分離酸化膜と、

前記半導体基板上に、第3絶縁膜を介して形成された第3ゲート電極とを有し、

前記第3ゲート電極は、前記第3素子分離酸化膜上に形成され、

前記第2素子分離酸化膜の表面は、前記第3素子分離酸化膜の表面よりも後退していることを特徴とする半導体装置。

30

**【請求項 8】**

請求項7記載の半導体装置において、

前記第1ゲート電極および前記第2ゲート電極は、メモリアレー領域内に形成され、前記第3ゲート電極は、周辺回路領域内に形成されていることを特徴とする半導体装置。

40

**【請求項 9】**

所望に準備された半導体基板に、不揮発性半導体記憶装置を形成する領域に対応して、少なくとも一つの絶縁ゲート型電界効果型トランジスタの形成する領域を覆うマスクを介する、或いは当該絶縁ゲート型電界効果型トランジスタのゲート電極を介して前記半導体基板に半導体凸型領域を形成する工程、前記半導体凸型領域の少なくとも側壁に絶縁物層を介してゲート電極を形成する工程とを有することを特徴とする半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置及びその製造方法、特に不揮発性メモリ構造を有する半導体装置に関するものである。

**【背景技術】****【0002】**

LSIに組み込まれた集積半導体メモリの一つに不揮発性メモリがある。これは、LSIの電源を切っても記憶情報が残る素子であり、LSIを様々な応用に用いるためには、極めて重要な素子になっている。

**【0003】**

50

半導体素子の不揮発性メモリについては、S. Sze著のフィジックス オブ セミコンダクタ デバイス第2版、ウィリー出版 (Physics of Semiconductor Devices, 2nd edition, A Wiley-Interscience publication) の第496頁から506頁(非特許文献1)に、いわゆる浮遊ゲート型メモリや絶縁膜を用いたメモリの記載がみられる。ここでも記載があるように、絶縁膜を積層し、その界面や絶縁膜中のトラップ等に電荷を蓄えるものは、浮遊ゲート型に比べて新たな導電層を形成する必要がなく、CMOSLSIプロセスと整合性よくメモリを形成できることが知られている。

#### 【0004】

しかし、これまでの絶縁膜中に電荷を蓄えるものでは、電荷の注入と放出を行わせながら、且つ、十分に電荷保持特性を持たせることが求められるため、実現が困難なものになっている。これに対して、電荷を放出させる代わりに、異なる符号を持った電荷を注入することで記憶情報の書き換えを行うことが提案されている。この動作については、1997年のシンポジウムオンVLSIテクノロジー第63頁に記述がみられる(非特許文献2)。この構造では、メモリ動作させる多結晶シリコンゲートとセルの選択を行うゲートが分かれて形成されている。また、同様の記載が米国特許第5,969,383号(特許文献1)にもみることができる。

#### 【0005】

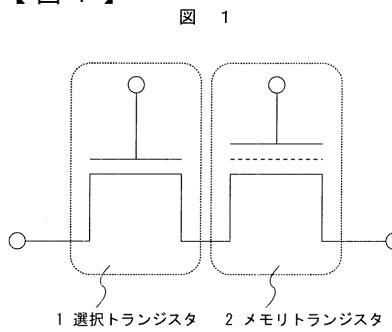

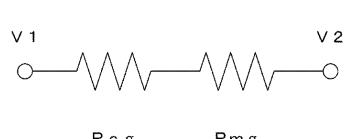

このメモリセル構造では、基本的にはNMOSをベースとした、選択ゲートの脇にメモリゲートを有する2つのトランジスタが、いわゆる「縦積み」の配置で置かれている。これを等価回路として示したのが図1である。メモリゲートのゲート絶縁膜はシリコン酸化膜でシリコン窒化膜を挟む構造で形成しており、いわゆるMONOS構造(Metal-Oxide-Nitride-Oxide-Semiconductor(Silicon))になっている。選択ゲートのゲート絶縁膜はシリコン酸化膜である。後で形成工程をもとに説明するが、周辺や、その他のロジック部にあるCMOSのゲート絶縁膜と共に通化することができる。拡散層電極は、それぞれ、選択ゲートとメモリゲートをマスクに形成している。このメモリセルの基本的な動作として、(1)書き込み、(2)消去、(3)保持、(4)読み出し、の4つの状態が考えられる。但し、この4つの状態の呼び名は、代表的なものとして用いており、書き込みと消去については、逆の呼び方をすることもできる。又、動作オペレーションも代表的なものを用いて説明するが、様々な異なるオペレーション法が考えられている。ここでは、説明のためNMOSタイプで形成したメモリセルについて述べるが、PMOSタイプでも原理的には同様に形成することができる。

#### 【0006】

(1)書き込み時、メモリゲート側拡散層に正電位を与え、選択ゲート側拡散層には基板と同じ接地電位を与える。メモリゲートに対して高いゲートオーバードライブ電圧を加えることで、メモリゲート下のチャネルをオン状態にする。ここで選択ゲートの電位を閾値より例えば0.1ないし0.2V高い値をとることで、オン状態にする。このとき、2つのゲートの境付近に最も強い電界を生じるため、多くのホットエレクトロンが発生し、メモリゲート側に注入される。この現象はソースサイドインジェクション(Source side injection:SSI)として知られているものであり、これについては、1986年アイ・イー・イー・イー・インターナショナル エレクトロン デバイス ミィーティング、テクニカルダイジェスト第586頁から589頁(IEEE International Electron Device Meeting, Technical Digest, pp 586-589, 1986)にA.T.Wu等による記述がみられる(非特許文献3)。ここでの記述は、浮遊ゲート型のメモリセルを用いているが、絶縁膜型においても注入機構は同様である。この方式でのホットエレクトロン注入の特長として、電界が選択ゲートとメモリゲート境界付近に集中するため、メモリゲートの選択ゲート側端部に集中的に注入が行なわれることである。また、浮遊ゲート型では、電荷保持層が電極により構成されているが、絶縁膜型では、絶縁膜中に蓄積されることになるため、極めて狭い領域にエレクトロンが保持されることになる。

(2)消去時、メモリゲートに負電位を与え、メモリゲート側拡散層に正電位を与えるこ

10

20

30

40

50

とにより、拡散層端部のメモリゲートと拡散層がオーバーラップした領域で、強反転が生じるようにすることで、バンド間トンネル現象を起こし、ホールを生成することができる。このバンド間トンネル現象については、例えば1987年アイ・イー・イー・イー、インターナショナル エレクトロン デバイス ミィーティング、テクニカルダイジェスト第718頁から721頁(IEEE International Electron Device Meeting, Technical Digest, pp 718-721, 1987)にT. Y. Chan等による記述が見られる(非特許文献4)。このメモリセルにおいては、発生したホールがチャネル方向へ加速され、メモリゲートのバイアスにより引かれONO膜中に注入されることにより消去動作が行なわれる。すなわち、エレクトロンの電荷により上昇していたメモリゲートの閾値を、注入されたホールの電荷により引き下げることができる。

10

(3) 保持時、電荷は絶縁膜ONONO膜中に注入されたキャリアの電荷として保持される。絶縁膜中のキャリア移動は極めて少なく遅いため電極に電圧がかけられていなくても、良好に保持することができる。

(4) 読み出し時、選択ゲート側拡散層に正電位を与え、選択ゲートに正電位を与えることで、選択ゲート下のチャネルをオン状態にする。ここで、書き込み、消去状態により与えられるメモリゲートの閾値差を判別できる適当なメモリゲート電位、(すなわち、書き込み状態の閾値と消去状態の閾値の中間電位)を与えることで、保持していた電荷情報を電流として読み出すことができる。

【0007】

20

【特許文献1】U.S.005969383

【非特許文献1】S. Sze著 Physics of Semiconductor Devices, 2nd edition, A Wiley-Interscience publication 第496頁から506頁

【非特許文献2】1997年シンポジウムオンVLSIテクノロジー第63頁

【非特許文献3】1986年アイ・イー・イー・イー、インターナショナル エレクトロン デバイス ミィーティング、テクニカルダイジェスト第586頁から589頁

【非特許文献4】1987年アイ・イー・イー・イー、インターナショナル エレクトロン デバイス ミィーティング、テクニカルダイジェスト第718頁から721頁

【発明の開示】

30

【発明が解決しようとする課題】

【0008】

上記従来技術の、スプリットゲートを持った正孔注入を用いたメモリセルの特徴は、正孔注入状態では、正孔の電荷のため、初期より低い閾値を実現することができる。このため、消去状態で大きな読み出し電流を得ることができる点にある。メモリセルの基本的な回路構成を図1に示す。このメモリセルは選択トランジスタ1とメモリトランジスタ2が直列に接続されている例である。このように、基本構成がMOSFETを基本としたメモリセルである為、デバイスのスケーリングに従い、その特性が変化することになる。ゲート長を短くすること、或いは、ゲート絶縁膜厚を薄くすることで、電流駆動力を向上させることができる。一方、チャネル幅が小さくなると、電流値は小さくなる。選択ゲートは、通常のMOSFETとして、これらのパラメータをスケーリングすることができる。しかし、メモリゲートでは、書き込み消去特性や電荷保持特性を維持するため、ゲート絶縁膜厚やゲート長等を、スケーリングすることができない。その為、メモリセルをスケーリングすると、トランジスタのチャネル幅が縮小する効果が強く現れる。この為、電流駆動力が低下する問題がある。

40

【0009】

そこで、本発明の目的は、上記問題点を解決し、スケーリングしても高い電流駆動力を持った不揮発性半導体記憶装置を提供することである。

【課題を解決するための手段】

【0010】

本願発明の骨子は、凸型形状の活性領域を形成し、当該凸部を跨るように選択ゲート或

50

いはメモリゲートを配置するものである。

【0011】

本願発明の主な形態を列挙すれば、次の通りである。尚、半導体基板の代表例はシリコン基板であるので、以下、シリコン基板をもって説明する。

【0012】

本願発明は、シリコン基板と、前記シリコン基板上に形成された、第1の絶縁ゲート型電界効果トランジスタと、前記シリコン基板上に形成され且つ前記第1の絶縁ゲート型電界効果トランジスタの有する第1のゲート電極と絶縁膜を介して形成された第2のゲート電極を有する第2の絶縁ゲート型電界効果トランジスタと、を有する。そして、前記第2の絶縁ゲート型電界効果トランジスタのゲート絶縁膜は、電荷保持機能を有し、前記第2のゲート電極による電圧特性の変化の寄与によって、前記第1の拡散層電極と前記第2の拡散層電極との間を流れる電流を制御する不揮発性半導体記憶装置であって、更に、次の特徴を有する。

【0013】

前記第1及び第2の絶縁ゲート型電界効果トランジスタの各ゲート電極と交差する方向に、第1の拡散層電極と、前記第1の絶縁ゲート型電界効果トランジスタの有する第1のゲート電極と当該第1のゲート電極に対応する第1のチャネル領域と、前記第2の絶縁ゲート型電界効果トランジスタの有する第2のゲート電極と当該第2のゲート電極に対応する第2のチャネル領域と、前記第1の拡散層電極と、前記第1のチャネル領域と第2のチャネル領域を挟んで対向する第2の拡散層電極と、を有する。

【0014】

そして、前記第1の拡散層電極と前記第2の拡散層電極を結ぶチャネル方向に交差する方向に凸型半導体領域を有し、前記絶縁ゲート型電界効果トランジスタのいずれか、或いはその両者のチャネル領域が前記凸型半導体領域の側壁に形成されるものである。

【0015】

即ち、第1の形態は、少なくとも前記第1の絶縁ゲート型電界効果トランジスタの有する第1のチャネル領域が、前記凸型半導体領域の側壁に形成される形態である。第2の形態は、少なくとも前記第2の絶縁ゲート型電界効果トランジスタの有する第2のチャネル領域が、前記凸型半導体領域の側壁に形成される形態である。第3の形態は、前記第1及び第2の絶縁ゲート型電界効果トランジスタの両者が、前記凸型半導体領域の側壁に形成される形態である。

【0016】

又、前記本願発明の形態に対して、前記第1の絶縁ゲート型電界効果トランジスタの有する第1のチャネル領域が、前記半導体基板の前記凸型半導体領域を除く基板面或いはこの半導体基板の上面と平行な面に形成された形態は、実用上有用である。即ち、当該不揮発性半導体記憶装置を半導体集積回路半導体装置に適用する場合、半導体集積回路半導体装置を構成する通例の絶縁ゲート型電界効果トランジスタは、半導体基板の上面或いはこれと平行な面上に形成されている。従って、前記凸型半導体領域の側壁にチャネルを形成する不揮発性半導体記憶装置以外の絶縁ゲート型電界効果トランジスタは、これら通例のものと同様の工程を適用して製造することができるからである。

【発明の効果】

【0017】

本願発明は、スケーリングされた平面レイアウトであっても、レイアウトされたチャネル幅に比べ、実効的なチャネル幅を大きくすることができる。従って、本願発明の不揮発性半導体記憶装置は、スケーリングしても高い電流駆動力を得ることができる。

【発明を実施するための最良の形態】

【0018】

<実施の形態1>

以下、本発明の実施例を参照して詳細に説明する。まず、本発明の主要部となるメモリセルを中心に形成法および本発明の構造を説明する。

10

20

30

40

50

## 【0019】

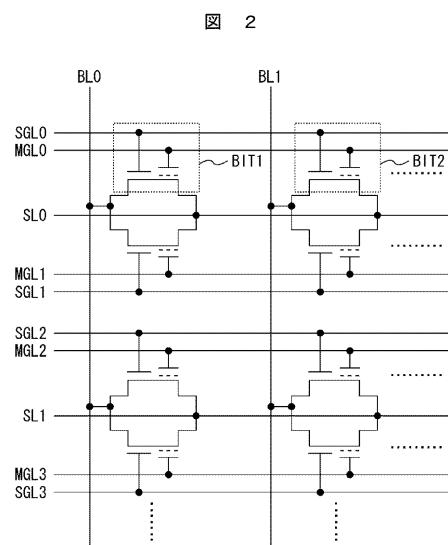

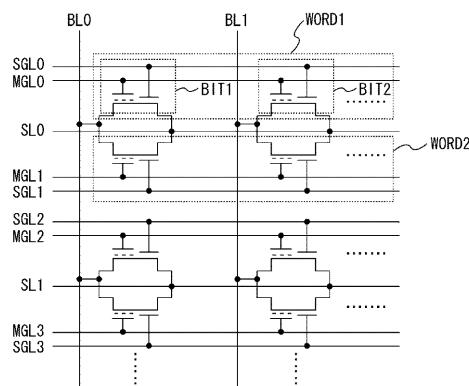

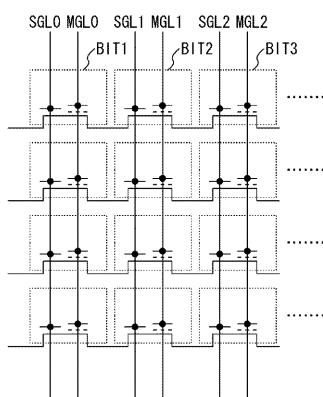

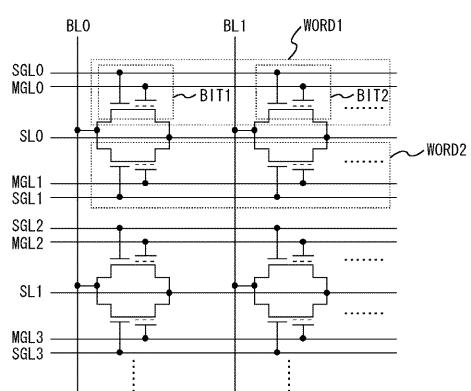

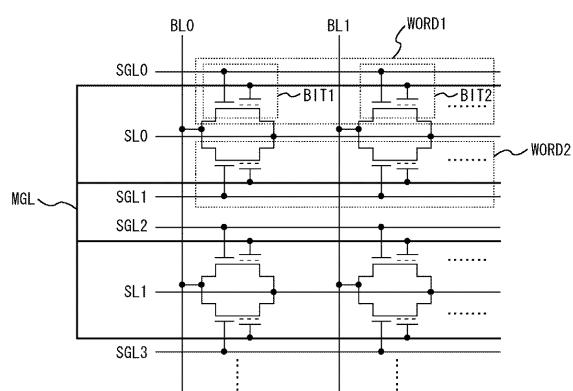

本発明のメモリセルにより、メモリアレイを構成したときの等価回路を図2に示した。ここでは、ワード線(SGL)を共通にするセルなど、8ビットを示している。これを繰り返すことで、アレイが構成される。図の例では、メモリセル(BIT1、BIT2等)が8個配置され、ビット線(BL0、BL1)とこれに交差するワード線(SGL0、SGL1、SGL2、SGL3)、及びメモリゲートがつながる線(以下、メモリゲート線の略称する: MGL0、MGL1、MGL2、MGL3)が配置されている。SL0、SL1はソース線である。

## 【0020】

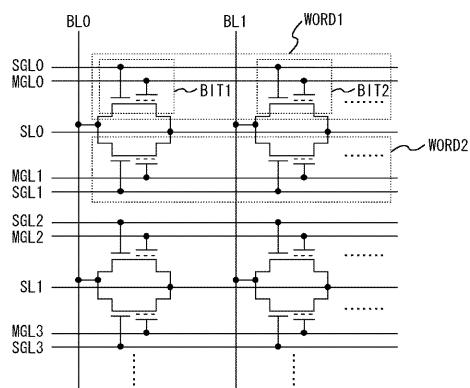

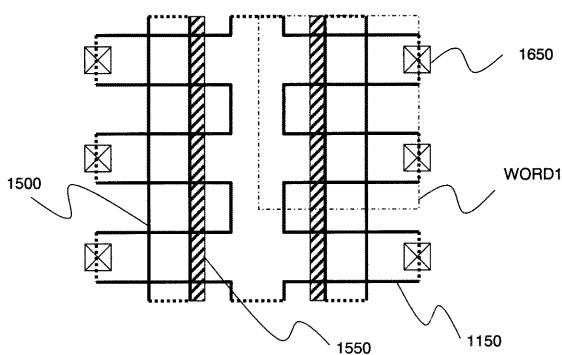

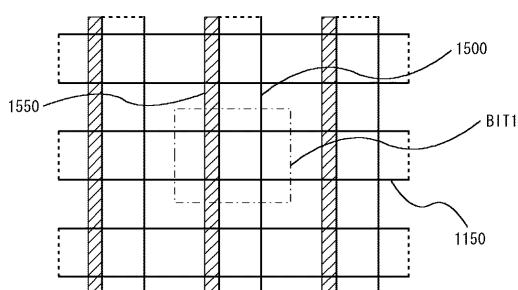

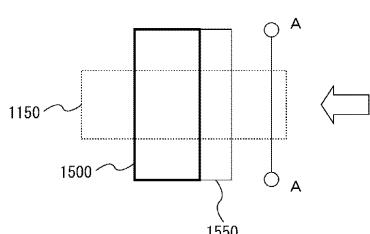

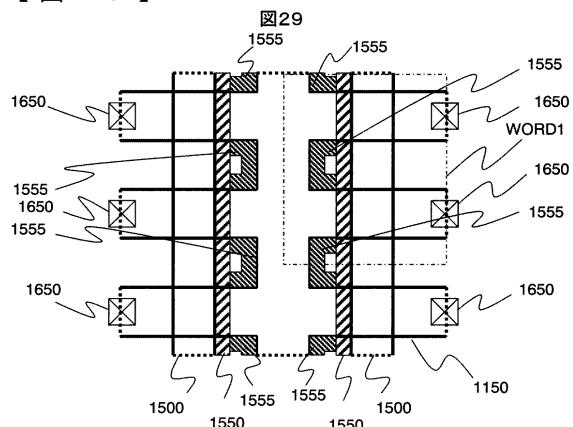

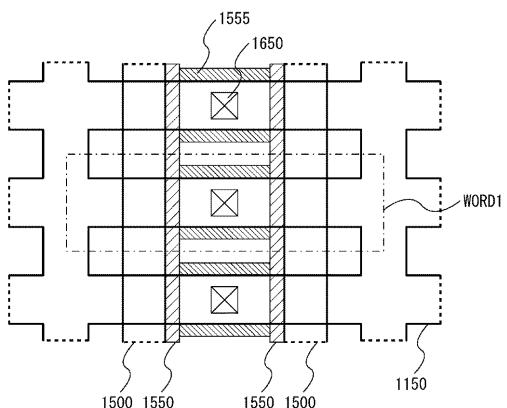

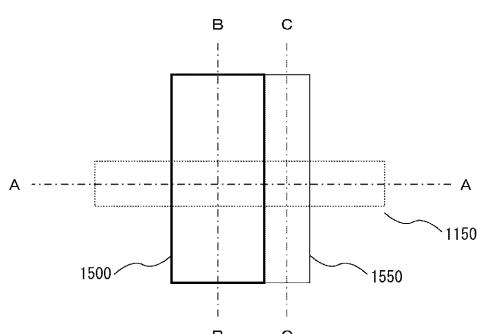

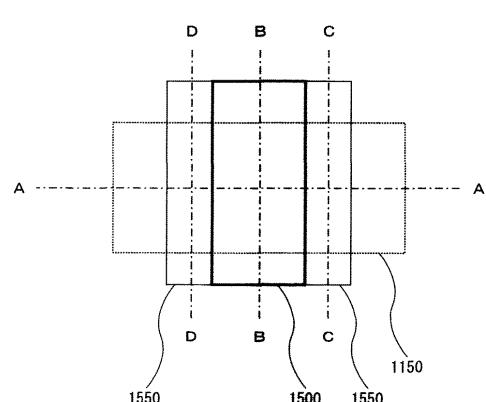

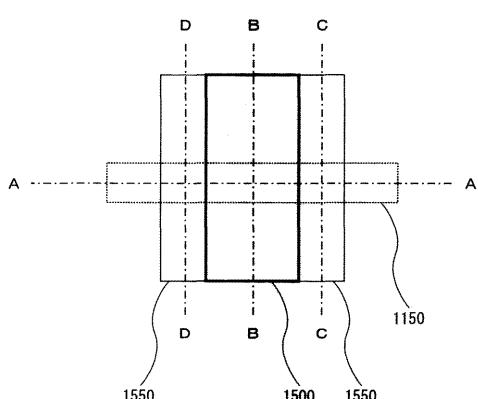

図3、図4は、等価回路図と、このメモリアレイを実現するための、半導体基板上での平面配置(レイアウト)を示したものである。平面レイアウト図では、セル配置を説明する為、活性領域1150と選択ゲート1500、及びメモリゲート1550とコンタクト配置1650のみを示した。但し、後の形成工程で説明するように、メモリゲートは自己整合プロセスにより形成できるため、形成工程で図示したようなマスクは存在せず、配置を説明するためのものである。一点鎖線で囲む領域が、等価回路図のWORD1に対応した2ビットである。図3の等価回路図を対照すれば、ビット線BL1を中心に左右に一対の選択ゲート1500及びメモリゲート1550が配置されている。

## 【0021】

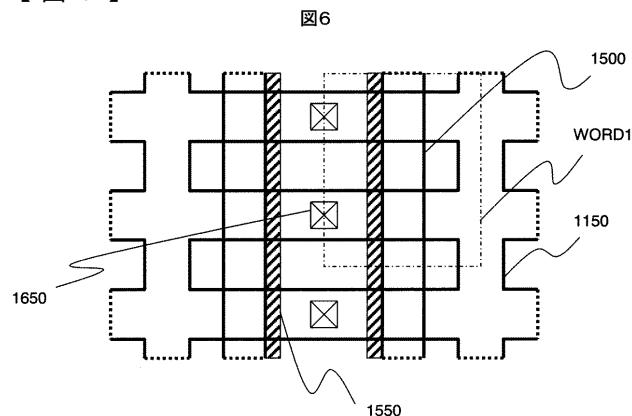

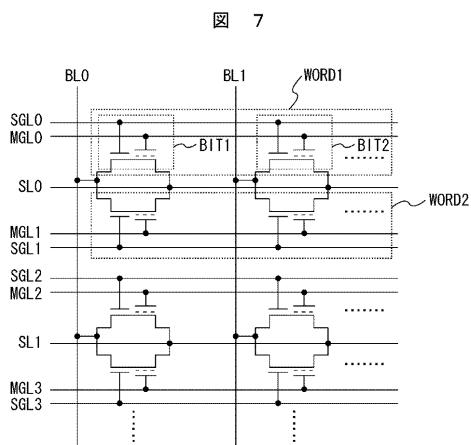

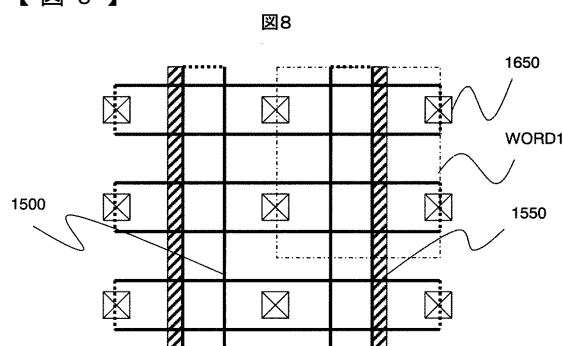

図5、図6は同様に、メモリゲートと選択ゲートの配置を入れ替えた場合の構成例の等価回路図、及びその平面レイアウトを示したものである。図7、図8は、全てのメモリセルの拡散層にkンタクトを設けた例である。活性領域をストライプ状に形成することができる。

## 【0022】

図9、図10は、メモリセルを縦積みに配置した例を示し、各々等価回路図及び平面レイアウト図である。図10には、図9におけるBIT1の部分の選択ゲート1500及びメモリゲート1550の配置を示している。そして、この例の場合、セルは各ビット毎に繰り返すことになる。

## 【0023】

以上、メモリセルの各種の形態を例示したが、いずれのレイアウトにおいても、選択ゲートとメモリゲートの基本単位では、同じ構成となる。そこで図11に示したような基本構造で、形成プロセスについて説明する。

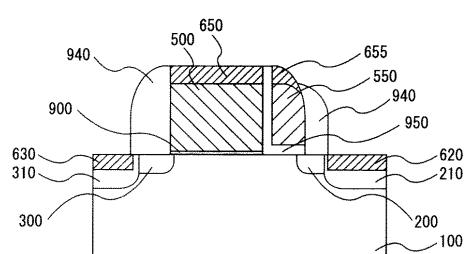

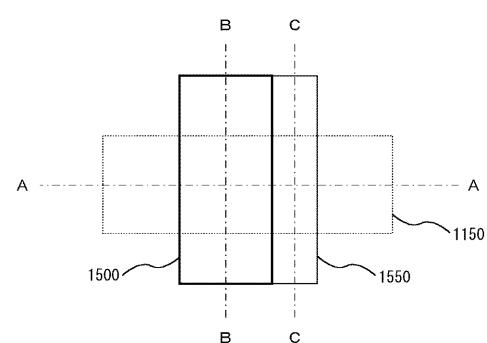

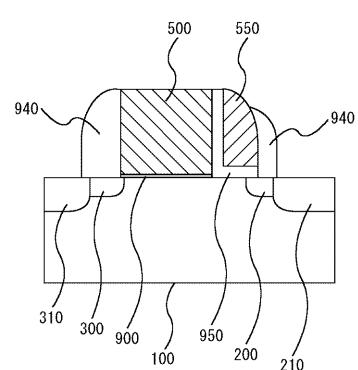

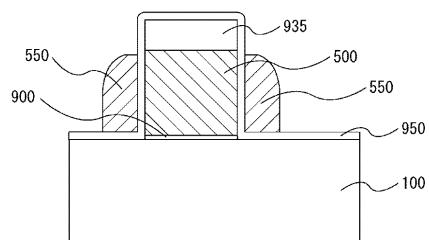

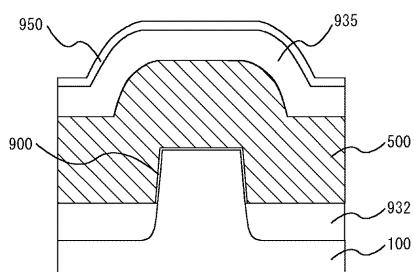

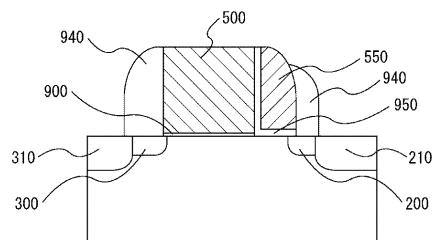

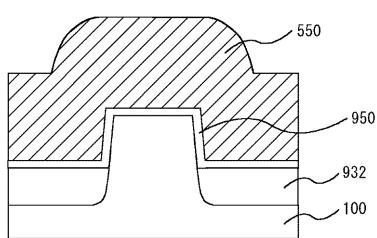

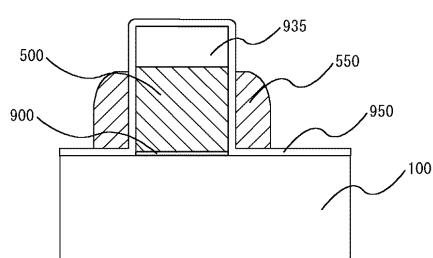

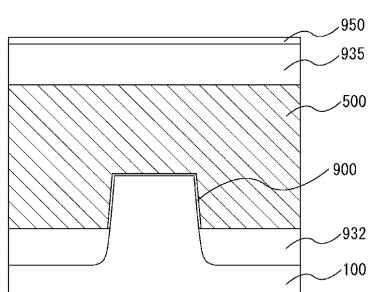

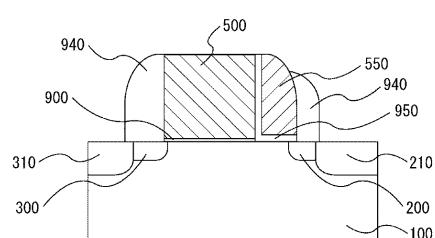

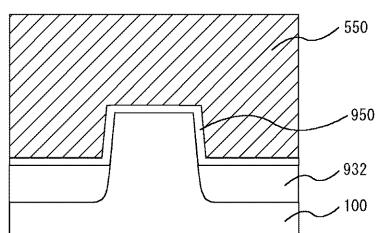

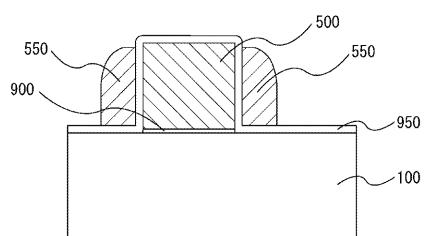

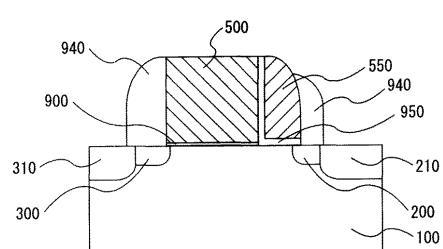

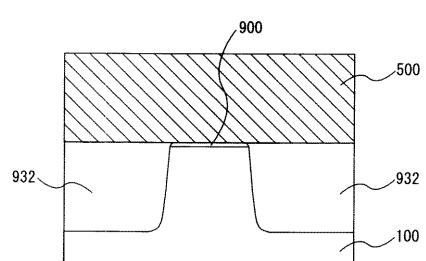

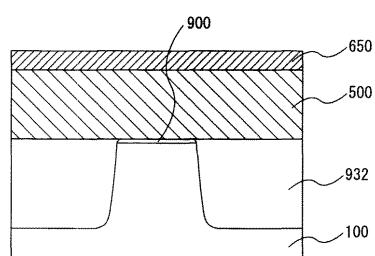

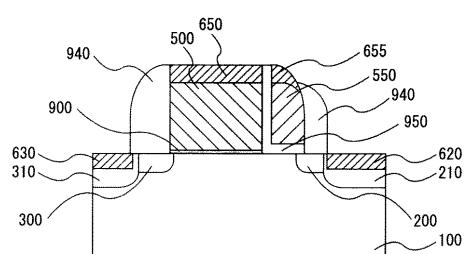

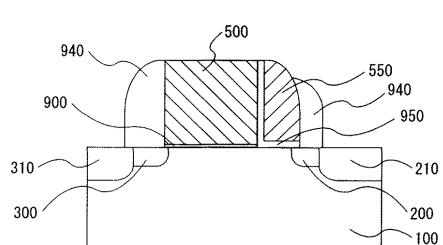

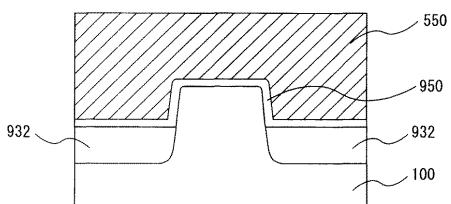

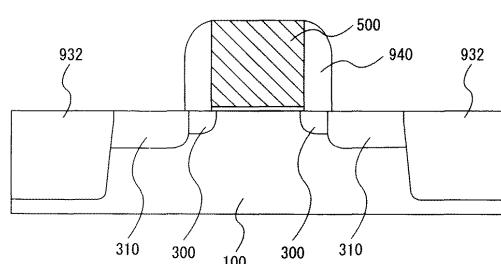

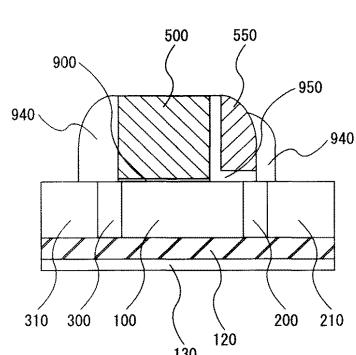

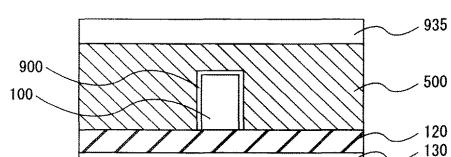

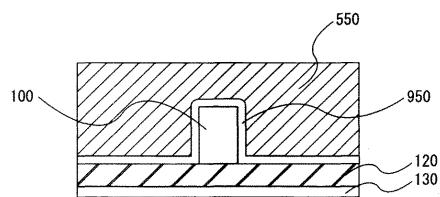

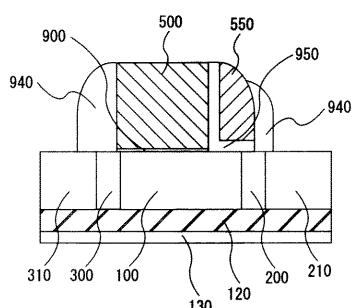

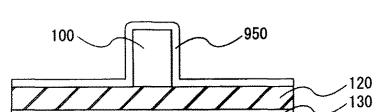

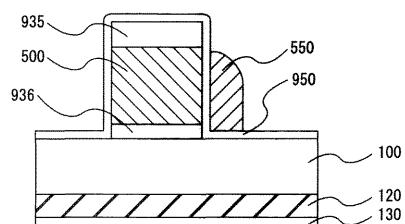

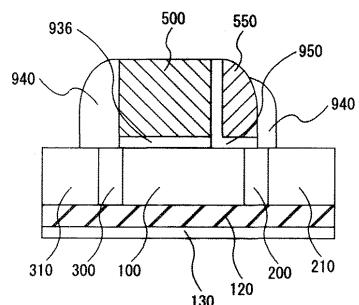

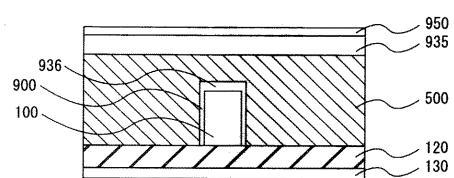

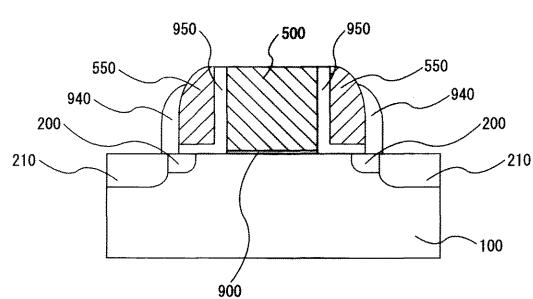

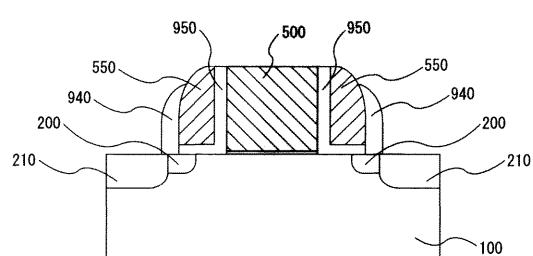

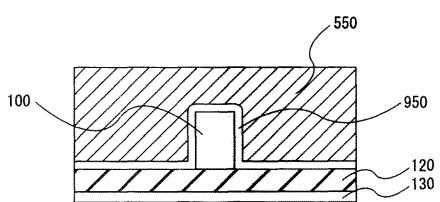

図11のレイアウトにより形成したメモリセルの断面構造を図12に示した。図11に見られるように、平面的には、活性領域1150の上部に選択ゲート1500とメモリゲート1550が並置される構成となっている。こうした構成を具現化した例が図12である。半導体基板100上にゲート絶縁膜が900および950を介して、選択ゲート500、メモリゲート550が形成される。これらの選択ゲート500、メモリゲート550の各々の一方の側壁に側面スペーサ940が形成される。選択ゲート500とメモリゲート550とは、やはりゲート絶縁膜950の延在部によって絶縁されている。符号950の部分は電荷保持部であり、例えばシリコン酸化膜とシリコン窒化膜とシリコン酸化膜を積層したものである。図中、積層膜での詳細な積層構造は省略している。メモリゲート側に拡散層200および210が形成される。ここでは、説明のため、この拡散層をソースと呼ぶことにする。選択ゲート側に拡散層300および310が形成される。ここでは、この拡散層をドレインと呼ぶことにする。本例では、拡散層210及び拡散層310は、側面スペーサ940と自己整合的に形成されている。

## 【0024】

図13Aから図20Cまでは、本発明の第1の実施例である半導体装置をその製造工程順に示した模式的な断面図である。これらの図において、図11のチャネル方向での断面(A-A断面)を各図A(例えば、図13A、図14Aなど)、選択ゲートを含む断面(B-B断面)を各図B(例えば、図13B、図14Bなど)、メモリゲートを含む断面(C-C断面)を各図C(例えば、図13C、図14Cなど)に示す。ここでは、いわゆる

10

20

30

40

50

0.13ミクロン世代相当のプロセスを用いて説明する。

【0025】

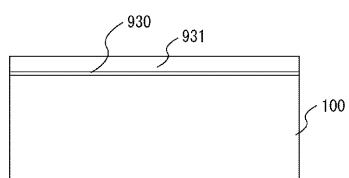

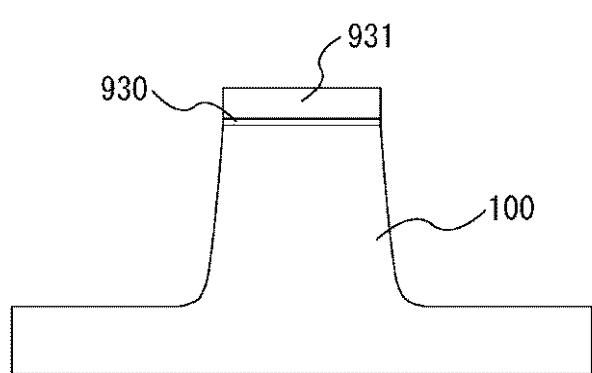

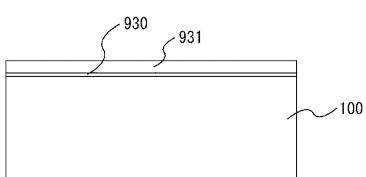

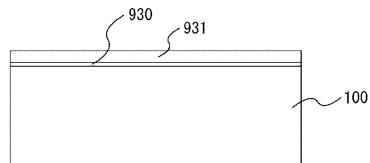

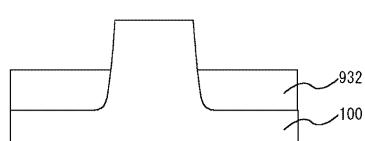

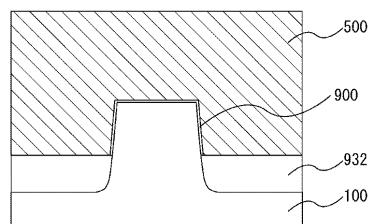

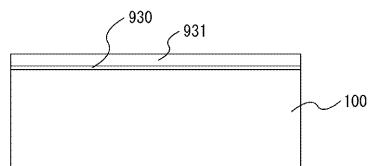

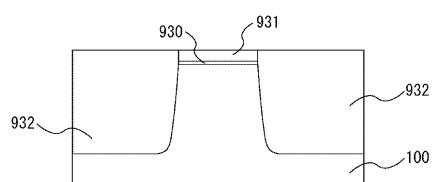

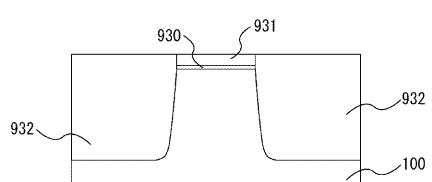

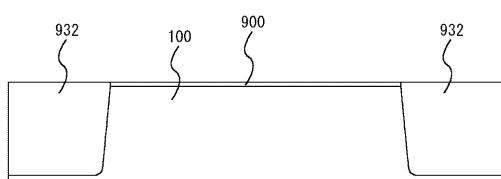

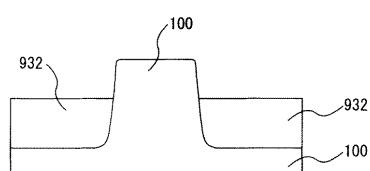

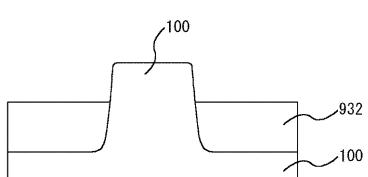

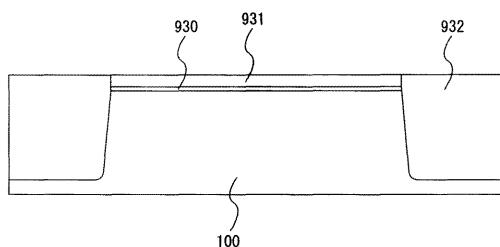

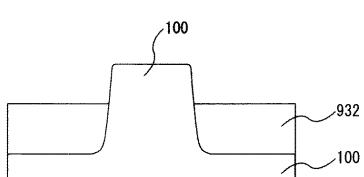

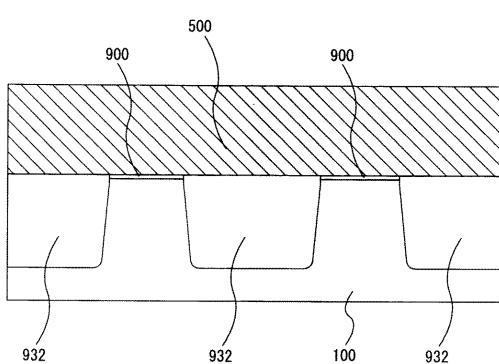

半導体基板100の活性領域表面に10nmの酸化膜930を形成した後、シリコン窒化膜931を100nmCVD法により堆積する。この後、リソグラフィ技術を用いて、前記シリコン窒化膜931、及び酸化膜930の積層膜、及び半導体基板100を300nmエッティングし、活性領域(図11、1150に相当する)を所望形状にパターニングを行う(図13A、図13B、図13C)。

【0026】

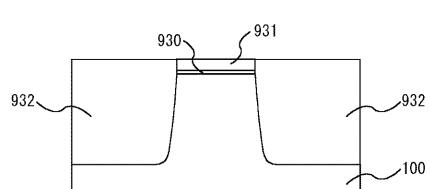

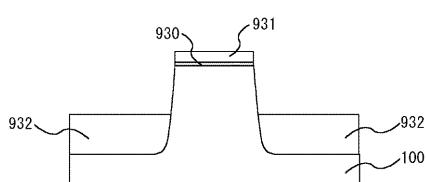

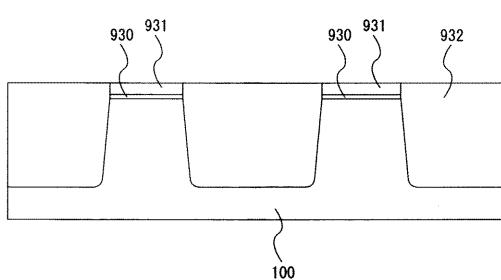

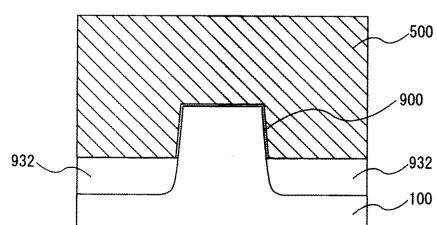

前記の工程で形成した溝の表面を酸化した後、シリコン酸化膜932を堆積させた。尚、半導体基板表面の酸化膜は、複雑になるので、図では表示を省略した。こうして準備した半導体基板表面を、化学機械的研磨(CMP:Chemical mechanical polishing)を行い、いわゆる浅溝アイソレーション(STI:Shallow Trench Isolation)を完成させる(図14A、図14B、図14C)。

【0027】

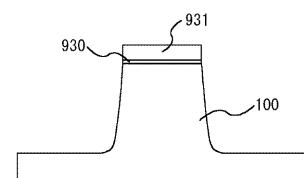

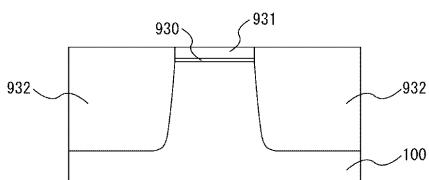

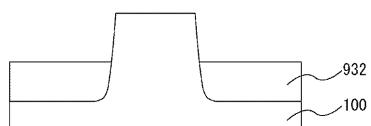

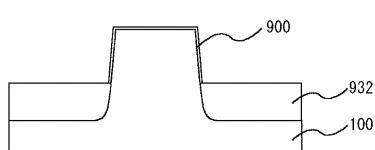

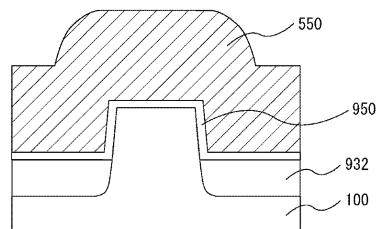

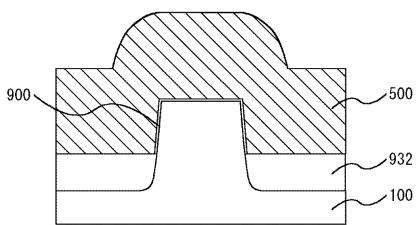

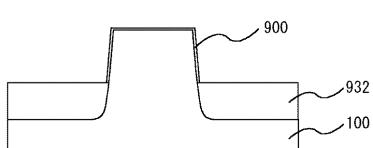

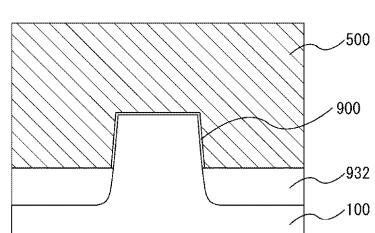

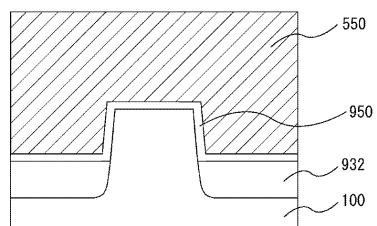

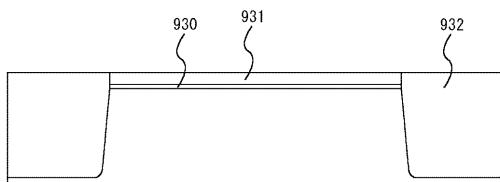

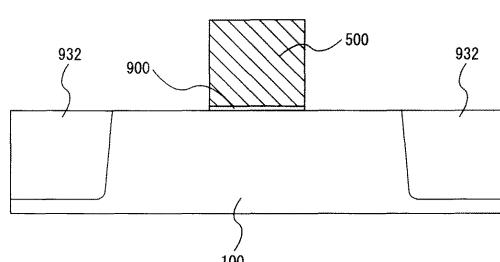

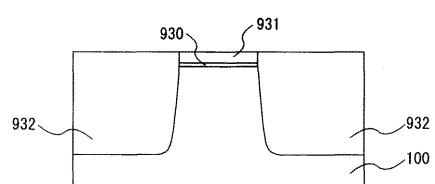

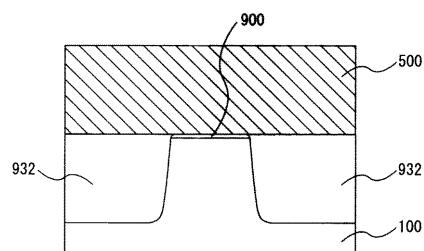

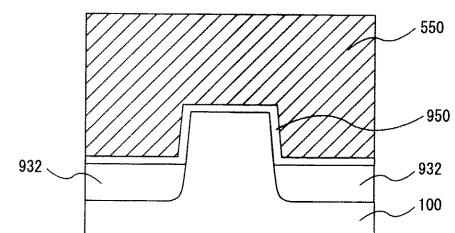

窒化膜931をマスクとして、酸化膜932を50nmエッティングすることで、凸型の形状を得ることができる。このエッティングとして、ウエット系エッティングを用いることで、基板へのダメージを与えないようにすることができる(図15A、図15B、図15C)。

【0028】

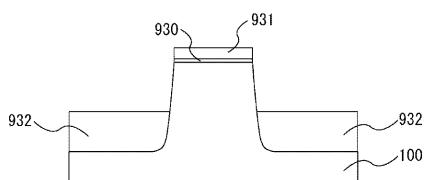

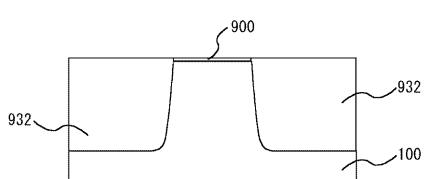

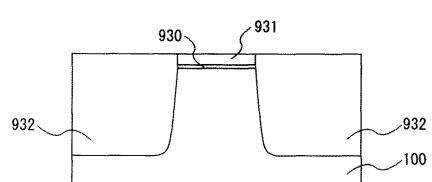

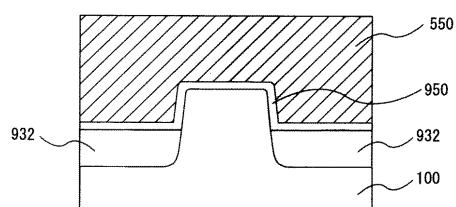

これまで、マスクとして用いて来た窒化膜931及び酸化膜930を除去することで、活性領域のシリコン表面を露出させる(図16A、図16B、図16C)。

【0029】

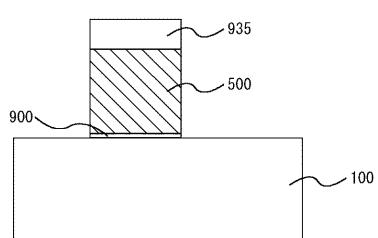

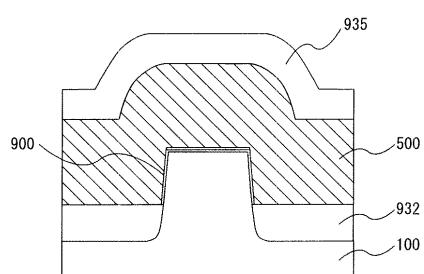

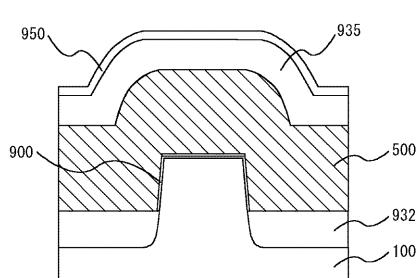

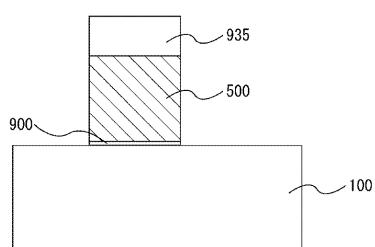

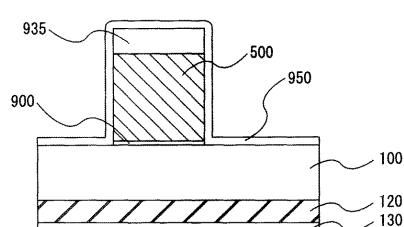

半導体基板表面を熱酸化により、2.5nmのゲート絶縁膜900を形成した後、多結晶シリコン500をCVD(Chemical Vapour Deposition)法により200nm堆積、更にシリコン酸化膜935を50nm堆積する。選択ゲートパターン(図11、1500)によりパターニングしたのち、該酸化膜935および多結晶シリコン500をエッティングし、選択ゲート電極を形成する。このとき(c)に示したように、メモリゲート領域では、凸型側面に500等が残らないように加工を行う(図17A、図17B、図17C)。

【0030】

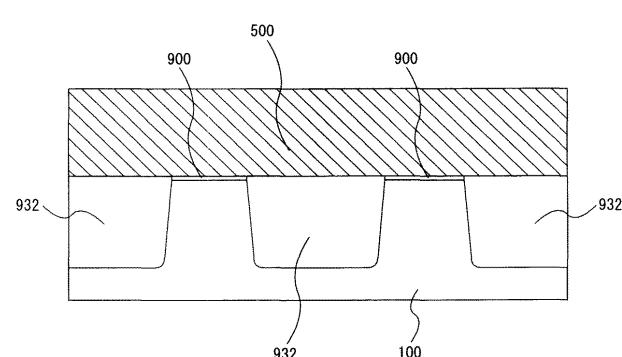

メモリゲート領域のゲート絶縁膜900を除去した後、露出した基板表面を4nm酸化する。この上部に、CVD法によりシリコン窒化膜を8nm、更にシリコン酸化膜7nmを堆積することで、ONO膜950を形成する。このONO膜950の形成においては、ISSG(In-Situ Steam Generation)酸化を用いることが出来る。即ち、基板表面をISSG酸化することで、酸化膜を5nm成長させ、シリコン窒化膜を14nm堆積する。この後、該シリコン窒化膜をISSG酸化することで、上部酸化膜6nmを形成することができる。

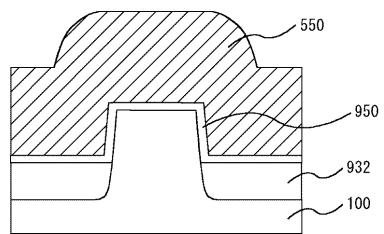

【0031】

ONO膜950を形成した後、高濃度にリンをin-situでドーピングした多結晶シリコンを70nm堆積する。そして、この多結晶シリコン膜に対して、異方性エッティングを行うことで、選択ゲート500側面にスペーサ形状のメモリゲート550を形成する。この時、コンタクト形成部には、ホトレジストパターンによりマスクをおくことができる(図18A、図18B、図18C)。又、ここでは図示していないが、不要部分の凸型側面から多結晶シリコン550を除くように、追加工エッティングを行うことができる。

【0032】

不要部分となる多結晶シリコン550をエッティング除去する。不要部分となる多結晶シリコン層は、具体的には、選択ゲート500のメモリゲートとなる領域と反対側面の多結晶シリコン層である。このときONO膜950を下地保護層として用いることができる。選択ゲート500およびメモリゲート550をマスクに砒素をイオン打ち込みすることで、ソース200およびドレイン300を形成する(図19A、図19B、図19C)。

【0033】

10

20

30

40

50

露出したONO膜950をエッティング除去し、次いで、それぞれ選択ゲート500およびメモリゲート550をマスクに砒素をイオン打ち込みすることで、ソース200及びドレイン300を形成することにより、イオン打ち込み時の加速エネルギーを低くし、浅い接合を作ることができる。又、この時、イオン打ち込みに対する表面保護層として、基板上で3nmの熱酸化膜を形成してもよい。また、この熱酸化工程でISSG酸化法を用いることで、ONO積層膜の窒化膜側面にも酸化膜を形成し、窒化膜外周に窒化膜-酸化膜の良好な界面を持つ構造を得ることができる。

#### 【0034】

更に、シリコン酸化膜を100nm堆積し、このシリコン酸化膜を異方性エッティングすることで、選択ゲート500及びメモリゲート550側面にスペーサ940を形成する。

更に、これをマスクに、拡散層210及び拡散層310を砒素のイオン打ち込み法により形成する(図20A、図20B、図20C)。これらの不純物ドーピングにあわせて選択ゲート500にも不純物をドーピングすることが出来る。これらのプロセスは通常のLDD(Lightly doped drain)プロセスを適用したものである。以下通常のCMOSプロセスの配線工程をとることで、メモリセルが形成される。

#### 【0035】

##### <実施の形態2>

前述の形成プロセスを、より安定したプロセスとした例を図21Aから図25Cに示した。これらの図においても、上述の実施例と同様に、図11に示したそれぞれの断面を用いている。即ち、各図A、B、Cは上述の例と同様の断面を示す。

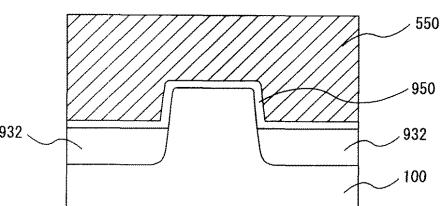

#### 【0036】

前述の実施の形態1において、図16A、16B、16Cの段階まで形成した後、ゲート絶縁膜900を形成する。更に、多結晶シリコン500を300nm堆積し、CMP法により、この多結晶シリコンを研磨することで、多結晶シリコン500表面を平坦化する。活性領域の凸部頂上において、200nmの厚さになるようする。その後、50nmのシリコン酸化膜935を堆積する。選択ゲートパターン(図11、符号1500)を用いて、酸化膜935、多結晶シリコン500をエッティングし、選択ゲートを形成する(図21A、図21B、図21C)。

#### 【0037】

メモリゲート550となる多結晶シリコンを堆積したのち、スペーサ加工を行うことで、メモリゲートを形成する(図22A、図22B、図22C)。

#### 【0038】

不要部分となるメモリゲート層550を除去し、メモリゲート550及び選択ゲート900と自己整合的に拡散層200及び拡散層300をイオン打ち込みにより形成する(図23A、図23B、図23C)。

#### 【0039】

酸化膜スペーサ940形成を行い、更に拡散層210及び拡散層310を形成する(図24A、図24B、図24C)。

#### 【0040】

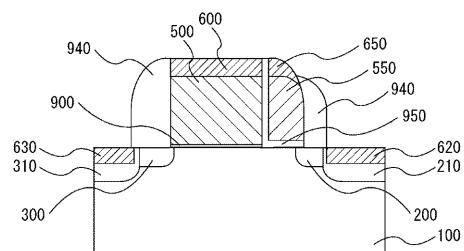

既知のいわゆるサリサイド(SALICIDE)プロセスを用いて、拡散層210、310、及び選択ゲート500とメモリゲート550の上部を選択的にシリサイド化する(図25A、図25B、図25C)。形成されたシリサイド層が600、620、630、650である。

このプロセスでは、選択ゲート上面が平坦化されているため、加工が容易になる。

#### 【0041】

##### <実施の形態3>

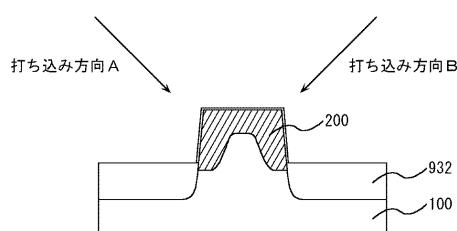

拡散層200、210、300、310を形成するイオン打ち込み時に、基板面に対して斜方から打ち込むことで、有効な拡散層を形成することが出来る。即ち、活性領域が凸型をしているため、斜めからイオン注入することで、側面に不純物を導入することができる。図26は斜めからのイオン注入の状態の例を示す断面図である。この例では、半導体

基板 100 に酸化膜 932 が設けられている。図 26 に示すように 2 方向 (A、B) から打ち込むことにより、凸部領域の両側面に沿った領域を有する拡散層 200 が形成されている。

【0042】

＜実施の形態 4 及び 5 ＞

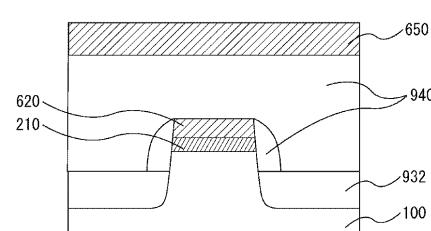

図 27A 及び図 27B は、シリサイド工程で、良好な接合特性を得る構造を説明したものである。図 27A は、平面レイアウトである。図 27A では、図 11 と同様に符号 1150 は活性領域、1500 は選択ゲート、1550 はメモリゲートである。図 27B は、図 27A の A - A 断面を矢印で示した方向から見たセル構造を示したものである。半導体基板 100 の凸型側面にスペーサ 940 を形成することで、凸型上部のみにシリサイド層 620 が形成されるようにしたものである。シリサイド 620 は、拡散層 210 内に形成することができる。尚、図において、符号 932 は酸化膜、650 はシリサイド層である。

10

【0043】

本例では、活性領域 1150 が、断面構造が凸型形状をとっている為、この段差部にメモリゲート 550 がスペーサ状に残ることが考えられる。図 28 から図 36 は、この段差について説明する為の図である。

【0044】

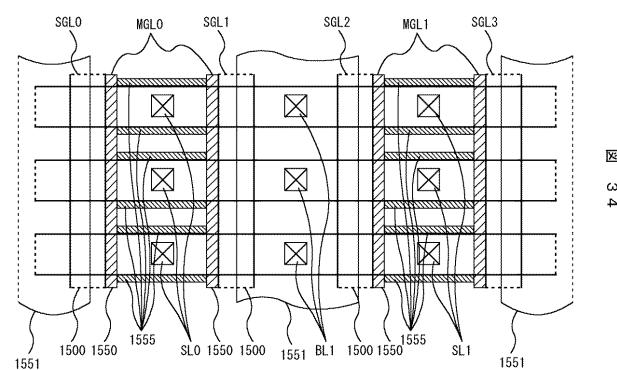

図 28 はメモリセルアレイの等価回路図、図 29 はその主要部の平面配置を示した図である。図 28 の WORD1 として示したメモリアレー領域の平面配置が、図 29 に示される。メモリアレー領域 WORD1 内のメモリセル B1T1 及び B1T2 が、図 29 の平面図の WORD1 内に示される。B1T1 及び B1T2 の各々のメモリセルにおける選択ゲート 1500、メモリゲート 1550 が、図の左右に線対称に配置されている。領域 1150 が活性領域、符号 1650 がコンタクトを示すことはこれまでの例と同様である。本例では、対向するメモリゲートが同相で駆動される例である。

20

【0045】

前述した製造工程から分かるように、メモリゲート 1550 の加工時には、活性領域 1150 の断面構造が凸型になっている。その為、符号 1555 で示した領域に活性領域 1150 段差に沿って、加工残りが発生する。選択ゲート 1500 を挟んで、メモリゲート 1550 の反対側では、メモリゲートの除去が行われているため、こうした加工残りは発生しない。図 29 からわかるように、この加工残り 1555 は、メモリゲート 1550 に付随する形になる為、メモリゲート間での短絡を起こすことはない。

30

【0046】

そのため、図 30 に示すように、メモリゲート 550 をスペーサ加工する際、オーバーエッキングすることなく加工することで、図 29 に示した加工残りの領域 1555 を形成することができる。従って、メモリゲートの抵抗を低減することができる。尚、図 30A、図 30B、及び図 30C は、これまでと同様に、図 11 の各断面に対応させている。

【0047】

図 31、図 32 はその他のアレイ構成例を示したものである。図 31 は等価回路図、図 32 はその主要部の平面配置を示した図である。この例では、メモリゲート MGL は共通化した例である。その他に部分はこれまでの例と同様であるので、詳細説明は省略する。本例は、スプリットゲート構造のセルのため、セルの選択は選択ゲートにより行うことができるため取り得る構成である。図 32 には、図 31 における WORD1 部の 2 つのメモリセル B1T1、B1T2 の部分が示される。各部の符号はこれまでと同様である。図 32 の例では、メモリゲート 1550 間をつなぐように加工残り 1555 が発生する。しかし、メモリゲートが共通化されているため、メモリゲート間での短絡による不良を発生させることなく、抵抗低減することができる。

40

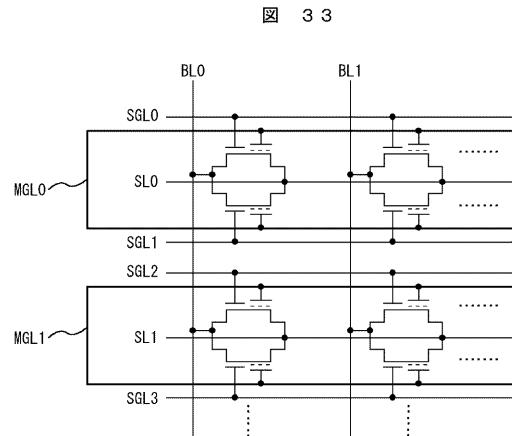

【0048】

対向セルのメモリゲートのみ共通化したのが図 33、図 34 の例である。図 33 は等価回路図、図 34 はその主要部の平面配置を示した図である。この例では、対向するメモリ

50

ゲートは共通化（MGL0、MGL1）した例である。共通化したメモリゲートMGL0、MGL1に対応する領域が、図34の左右に示される。更に、共通化したメモリゲートMGL0に対応する領域は、図33に見られる、MGL0が接続する二つのメモリゲートが左右対称に符号1550として図示される。共通化したメモリゲートMGL0に対応するワード線SGL0、SGL1が、前記符号1550の部分に平行に設けられている。又、共通化したメモリゲートMGL1に対応する領域は、図33に見られる、MGL1が接続する二つのメモリゲートが左右対称に符号1550として図示される。共通化したメモリゲートMGL1に対応するワード線SGL2、SGL3に関してMGL0の場合と同様に図示される。その他に部分はこれまでの例と同様であるので、詳細説明は省略する。

## 【0049】

このセルでは、対向するメモリゲートが共通化されているため、図34中に符号1555で示した加工残りは問題を起こすことはない。符号1551は選択ゲートのメモリゲートとは反対側に形成されたスペーサ550を除去するマスク配置例を示したものである。

## 【0050】

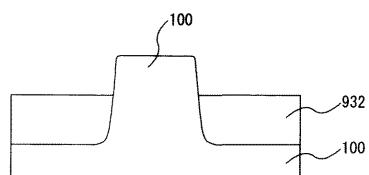

本実施例においては、メモリゲート部の素子分離酸化膜をエッチングにより、基板表面から後退させているので、メモリゲート電極が形成される活性領域が凸形状となっている。そのため、メモリゲート電極を形成したときに、メモリゲート電極材が凸形状の側面にも形成される。これによって、メモリゲート電極を有するトランジスタの実効的なチャネル幅が、活性領域を凸形状としないときと比べて増大する。一方、周辺デバイスが形成されるの活性領域を凸形状とすると、側面にもチャネルが形成され、凸形状の側面と凸形状の上面とでチャネルが形成される閾値が異なる。そのため、ゲート電極に従来のオフ状態となる電圧を印加したときに、凸形状の側面にチャネルが形成されてしまう。これにより、オフ状態であっても、側面チャネルに起因するリーク電流が流れてしまい好ましくない。

## 【0051】

そのため、本実施例では、メモリゲート部の素子分離酸化膜のみをエッチングすることによって、周辺デバイスの活性領域には凸形状を形成せずにメモリゲート電極が形成される活性領域を凸形状とした。

## 【0052】

本実施例では、メモリゲート部の素子分離絶縁膜がエッチングするプロセスを有しているので、メモリゲート部の素子分離絶縁膜の表面は、選択ゲート電極を有するトランジスタおよび周辺デバイスが形成される素子分離絶縁膜の表面よりも低くなっている。

## 【0053】

## &lt;実施の形態6&gt;

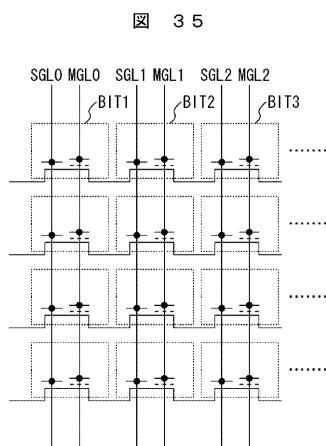

縦積みしたメモリセルをしめしたのが図35、図36の例である。図33は等価回路図、図34はその主要部の平面配置を示した図である。

## 【0054】

縦積みした場合、必ず片側のスペーサゲート550を除去するため、スペーサ加工時にオーバーエッチングしなくても、加工残りによる短絡等の問題をおこすことはない。

## 【0055】

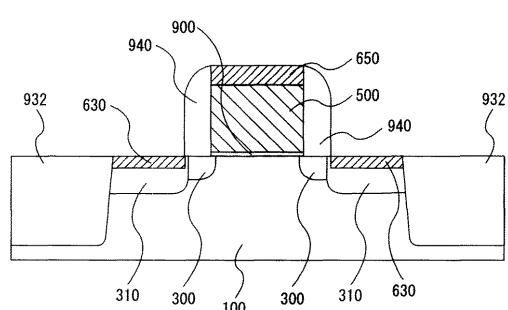

次にメモリゲートのみ凸型形状をとった例を説明する。図37Aから図43Eは、その他の実施例を製造工程順に示した素子の断面図である。この例の場合、選択ゲートと同時に周辺回路やロジック部には、通常の平坦型デバイスを形成できる。周辺回路で用いるデバイスは、回路設計上、デバイスパラメータが変わらないことが求められる。これにより、他で設計したものをそのまま用いることができるためである。そのため、周辺回路でのデバイスは、これまでと同じものができることが求められる場合がある。そのため、通常構造のデバイスができることが求められ、本発明実施例が有効である。

## 【0056】

尚、図37Aから図43Eにおいては、これまでと同様に、図11のチャネル方向での断面（A-A断面）を各A図、選択ゲートを含む断面（B-B断面）を各B図、メモリゲ

10

20

30

40

50

ートを含む断面（C-C断面）を各C図に示す。更に、各D図は、周辺デバイスのチャネル方向断面、各E図は、周辺デバイスのゲートを含む断面を示したものである。ここで、周辺デバイスは等価回路に示されてはいないが、通例の集積回路構成が用いて十分であり、各図の断面図は前記主要部の断面を取り出して示したものである。以下の例においても、周辺デバイスに言及したものは同様の断面を示している。

【0057】

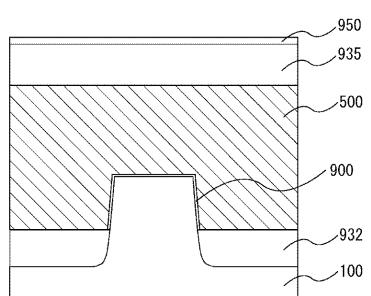

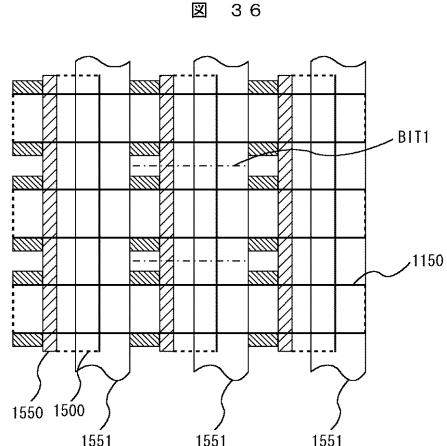

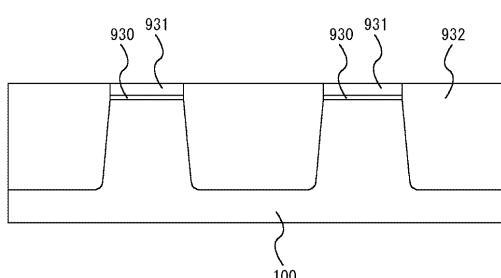

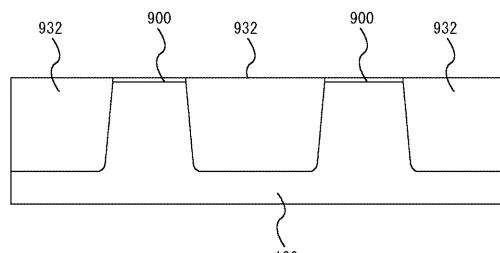

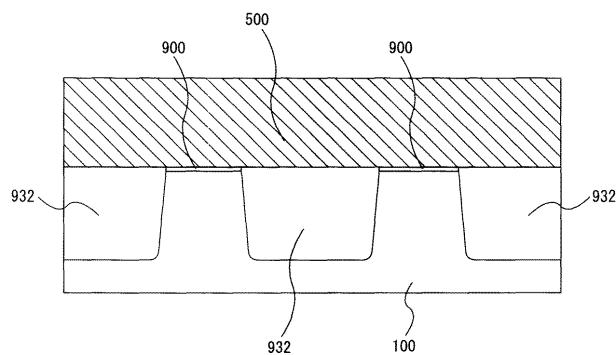

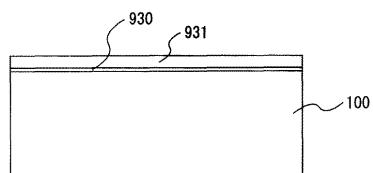

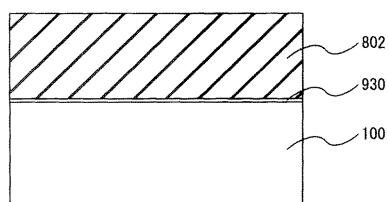

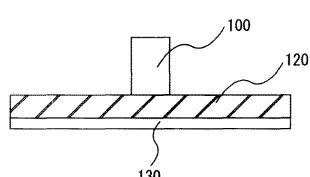

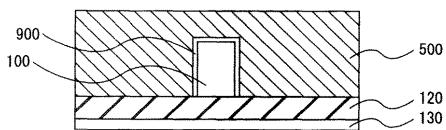

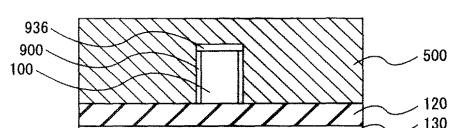

前述の浅溝アイソレーションプロセスにより、半導体基板に素子分離構造を形成する（図37A、図37B、図37C、図37D、図37E）。即ち、半導体基板100の活性領域表面に酸化膜930を形成した後、シリコン窒化膜931を堆積する。この後、リソグラフィ技術を用いて、前記シリコン窒化膜931、及び酸化膜930の積層膜、及び半導体基板100の所望部分をエッティングし、活性領域を形成する。前記の工程で形成した溝の表面を酸化した後、シリコン酸化膜932を堆積させた。尚、半導体基板表面の酸化膜は、複雑になるので、図では表示を省略した。こうして準備した半導体基板表面を、化学機械的研磨を行い、いわゆる浅溝アイソレーションを完成させる。

【0058】

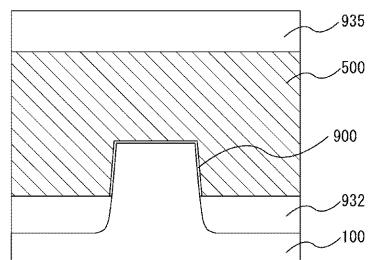

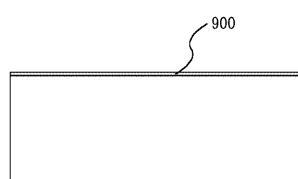

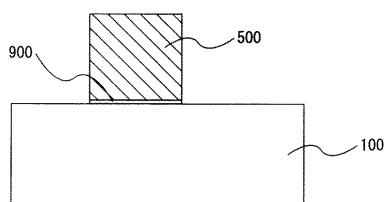

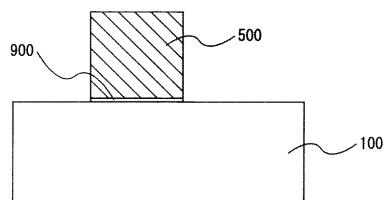

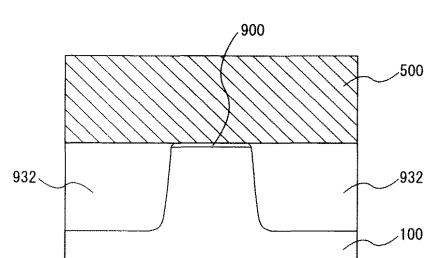

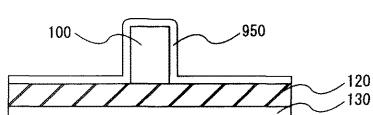

露出した基板表面を熱酸化することで、2.5nmのゲート絶縁膜900を形成する（図38A、図38B、図38C、図38D、図38E）。

【0059】

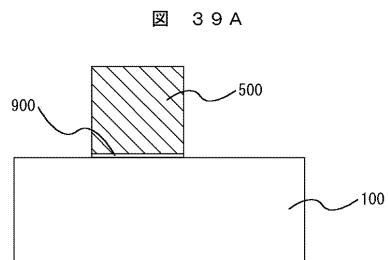

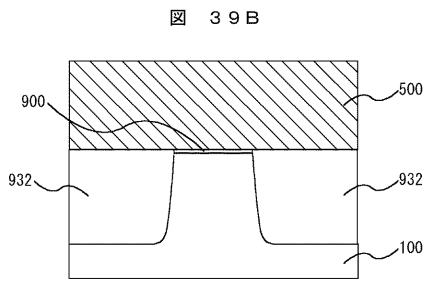

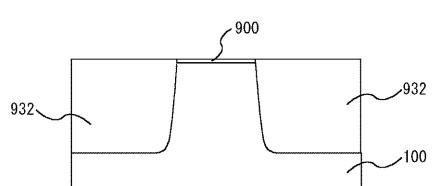

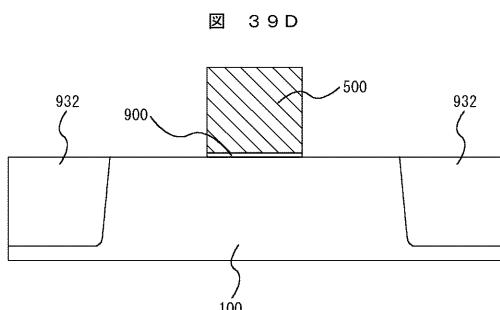

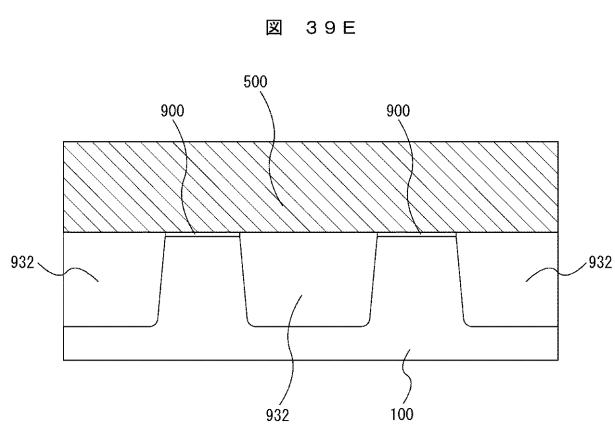

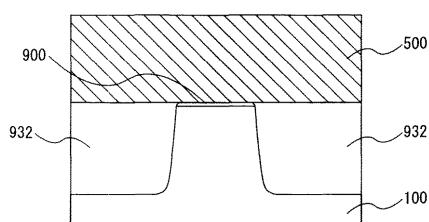

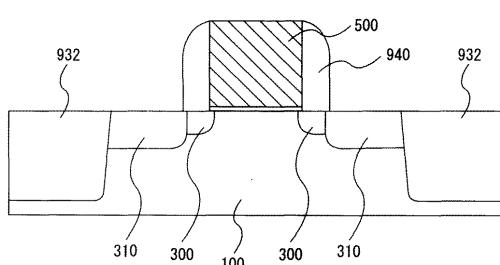

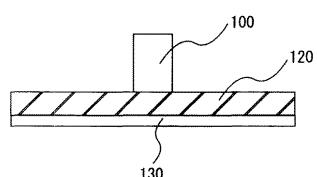

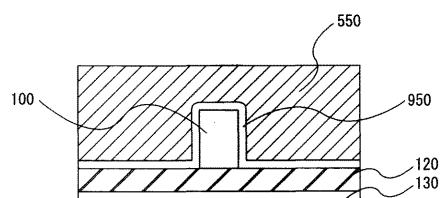

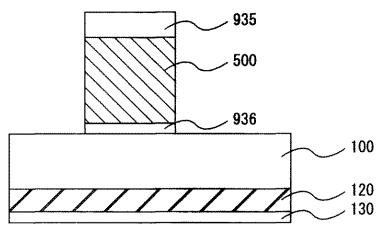

多結晶シリコン500を堆積し、パターニングすることで、選択ゲートを形成する（図39A、図39B、図39C、図39D、図39E）。このとき、周辺回路部におけるデバイスのゲート電極を同時に形成することができる。

【0060】

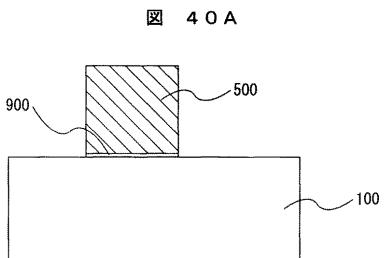

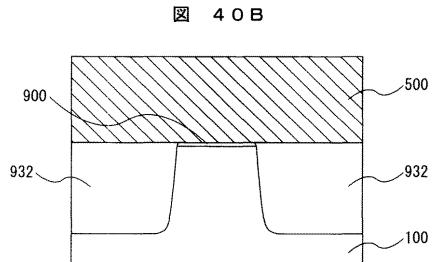

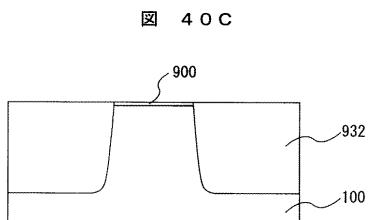

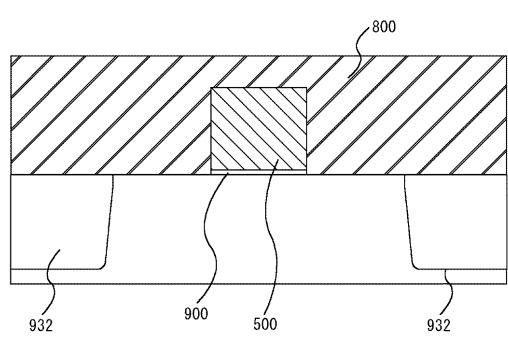

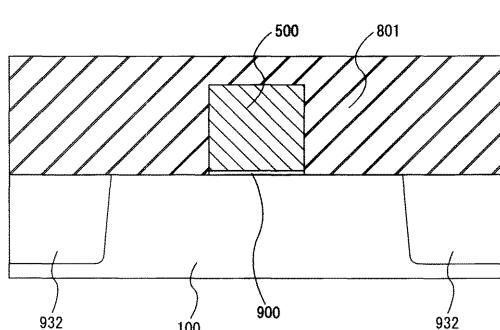

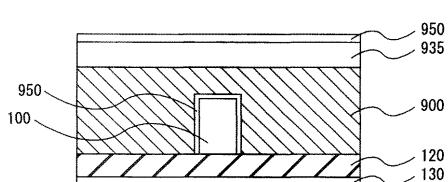

選択ゲートおよび周辺デバイス部をレジスト800でマスクする（図40A、図40B、図40C、図40D、図40E）。

【0061】

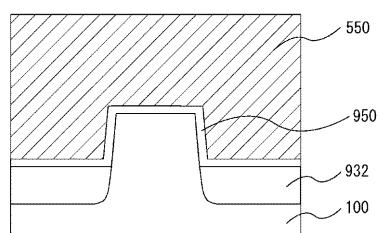

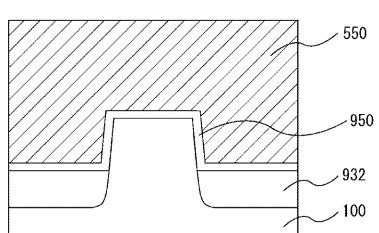

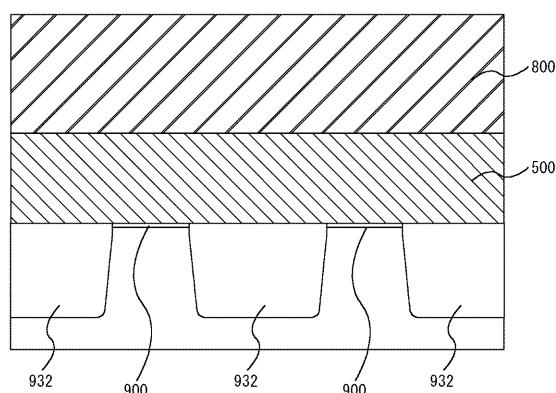

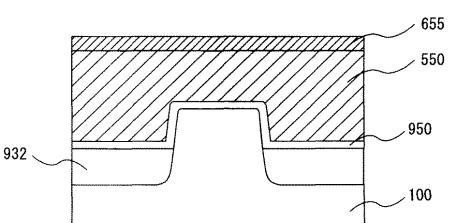

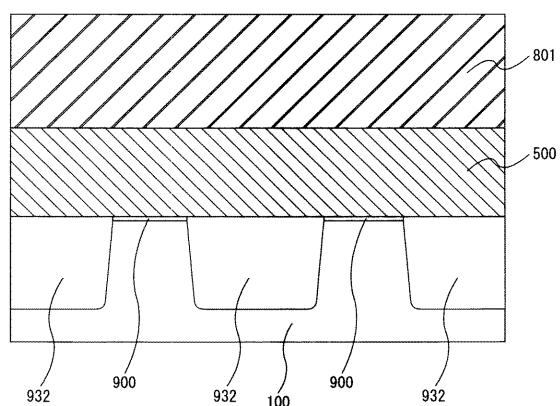

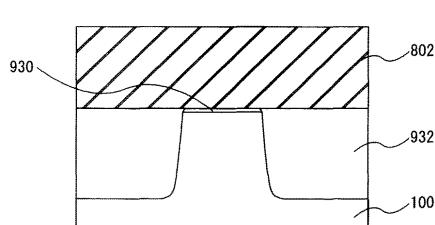

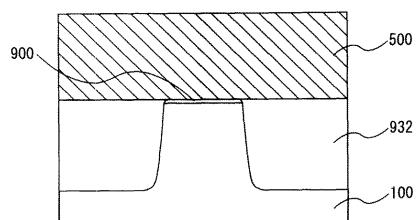

メモリゲート部の素子分離酸化膜932を50nmエッティングする（図41A、図41B、図41C、図41D、図41E）。

【0062】

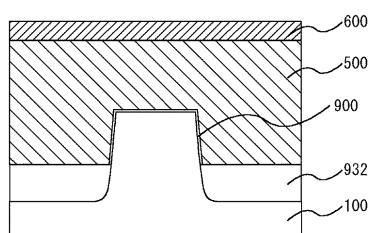

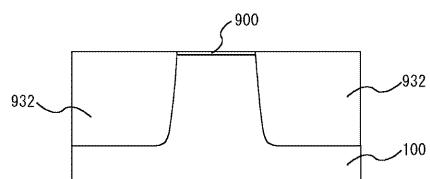

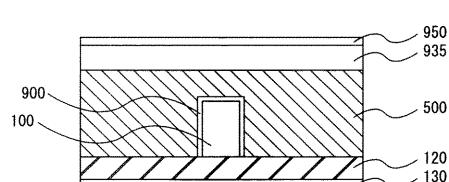

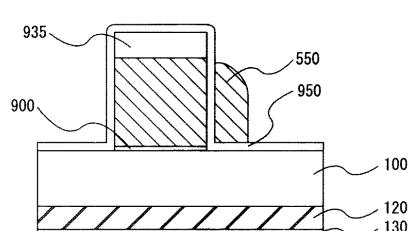

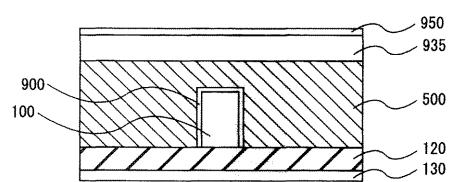

メモリゲートのゲート絶縁膜950を形成したのち、スペーサの形成プロセスによりメモリゲート550を形成する。次いで、イオン打ち込み法により、拡散層200、210、300、310を形成する（図42A、図42B、図42C、図42D、図42E）。これらのプロセスは前述の実施例と同様に行うことができる。

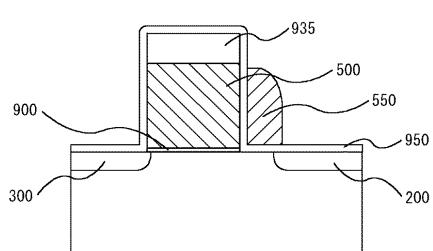

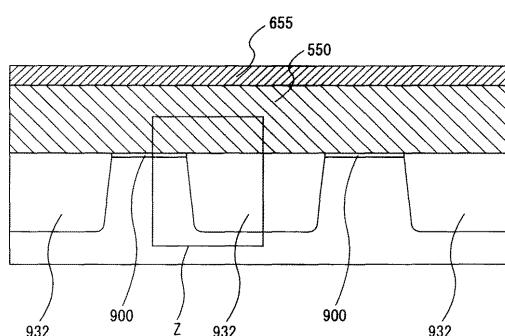

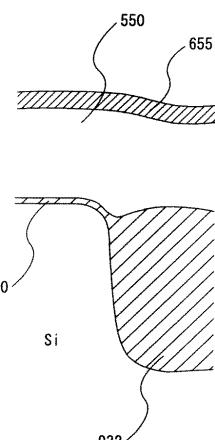

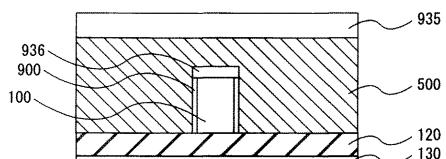

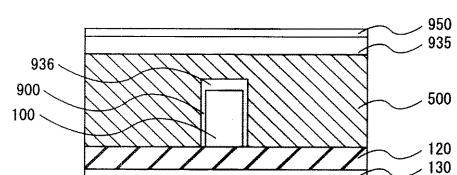

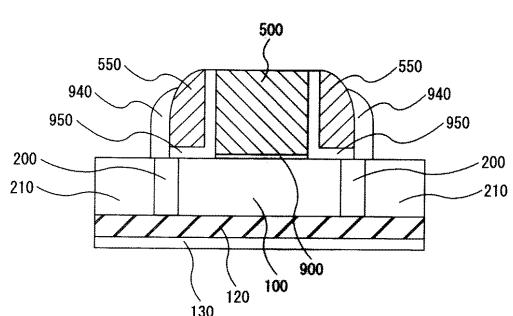

【0063】

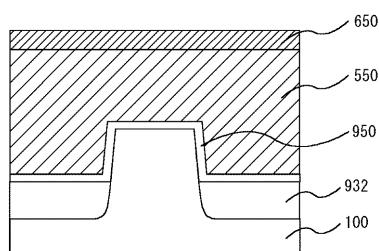

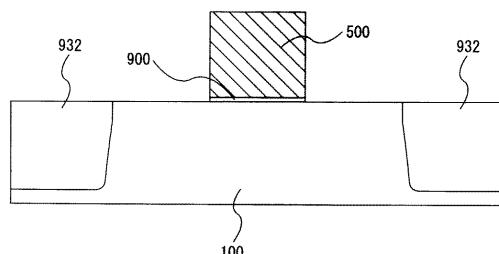

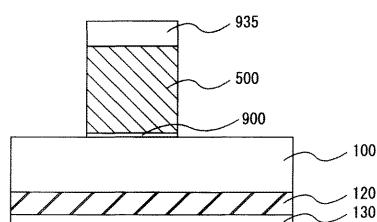

通例のサリサイドプロセスを適用し、シリサイド化部分を形成した構造を示している（図43A、図43B、図43C、図43D、図43E）。

【0064】

尚、図43Fに、図43Eの符号Zの部分の部分拡大図を示す。図43Eまでの図では、半導体基板面は直線で描かれているが、実際の工程では、図43Fのように、シリコン酸化膜の形成は、シリコンの凸部の端部に若干のくぼみが形成されることになる。特にことりはないが、本例以外でも、この状況は同様である。

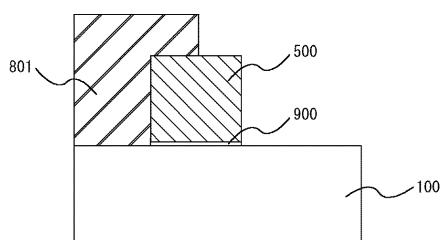

【0065】

<実施の形態7>

図44A-Eは、前記発明実施例において、凸型形状を形成する際、メモリ部でもマスクすることで、歩留まりを向上させる例を示したものである。即ち、図40A-Eにおけるマスク800をメモリ部の選択ゲート側にも配置（符号801の部分がこのマスクに相当する）することで、選択ゲート拡散層300、310が凸形状にならないようにすることが出来る。これにより、メモリアレイ内であっても、周辺回路領域と拡散層も同じ構造を得ることができる。

【0066】

<実施の形態8>

10

20

30

40

50

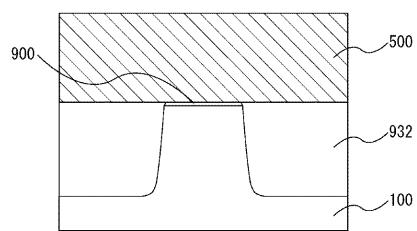

図45A-Eから図48A-Eは、その他の実施例を示す図で、選択ゲートおよび周辺回路デバイスを平坦に形成し、メモリゲートを凸型上に形成する工程を示したものである。図45A-Eから図48A-Eにおいては、これまでと同様に各A-Cは、図11のチャネル方向での各断面、更に、各D図、各E図は、周辺デバイスのチャネル方向断面及び周辺デバイスのゲートを含む断面を示したものである。以下、基本的な工程は、これまでの例と同様であるので、基本工程は簡潔に説明し、本例固有の事項を詳述する。

【0067】

これまでの例と同様に、半導体基板100に素子分離領域を形成する(図45A、図45B、図45C、図45D、図45E)。

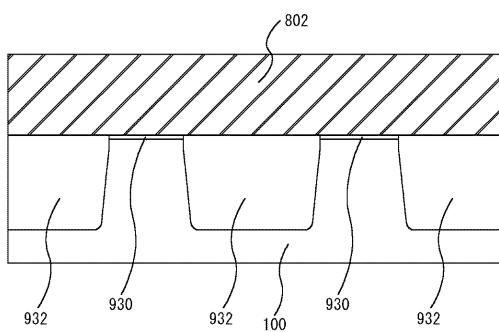

【0068】

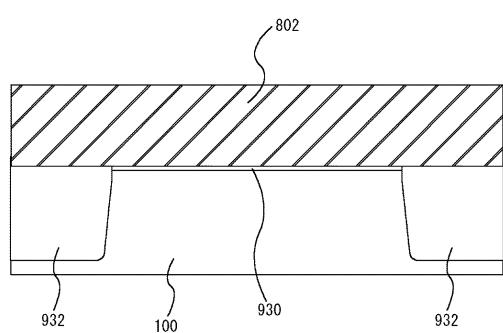

周辺回路領域及び選択ゲート領域にマスク802を置き、メモリゲート部に凸型形状を形成する(図46A、図46B、図46C、図46D、図46E)。

【0069】

選択ゲート500及び周辺回路デバイスを加工する(図47A、図47B、図47C、図47D、図47E)。

【0070】

メモリゲート絶縁膜950及びメモリゲート550を形成し、以下、前述の実施例と同様の加工プロセスを行うことで、メモリセルおよび周辺回路デバイスを得ることができる(図48A、図48B、図48C、図48D、図48E)。このプロセスにより、周辺回路領域及び選択ゲートには通常のMOSFETが形成でき、メモリゲートは凸型活性領域を持つものにすることが出来る。又、図46A-Eの工程で、レジストで周辺部のみを覆うようにすることで、選択ゲートおよびメモリゲートを、凸型活性領域上に形成することができる。

【0071】

<実施の形態9>

本発明の記憶装置においては、図1に見られるように、選択トランジスタとメモリゲートは、2つのトランジスタが縦積みされた構造とみることが出来る。ここでセルの読み出し電流を考えると、等価的には選択ゲートに対応する抵抗 $R_{cg}$ と、メモリゲートに対応する抵抗 $R_{mg}$ が直列に接続されたものとみることができる。これを等価回路として示したのが図49である。その為、上記メモリゲートのみを凸型とした場合、 $R_{mg}$ を小さくすることができる。

【0072】

そこで、前記従来読み出し法とは逆に、 $V_1 < V_2$ とすることで、大きな読み出し電流を得ることができる。選択ゲートでは表面に形成されていた反転層から、凸型形状により、基板内部にキャリアを引き込むことができるためである。

【0073】

前記凸形状による効果はSOI(Silicon On Insulator)上に形成されたメモリセルでも得ることができる。図50は平面レイアウト、図51は、その断面構造を示したものである。

【0074】

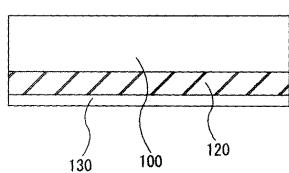

平面レイアウトでの特徴は、レイアウトされるチャネル幅をバルクに比べ小さく出来ることである。断面構造では、支持基板130上に埋め込み酸化膜120がおかれていることである。図52A-Cから図56A-Cは製造工程順にその素子の断面図を示すものである。これらの図において、各A図は、図50に示したように、チャネル方向断面(A-A断面)、各B図は選択ゲートを含む断面(B-B断面)、各C図はメモリゲートを含む断面(C-C断面)を示したものである。

【0075】

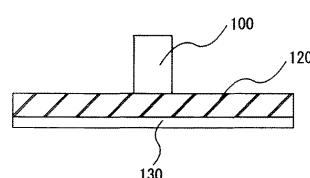

支持基板130上の、いわゆる「埋め込み酸化膜」120上にある80nmの厚さのシリコン単結晶(SOI)100を、活性領域パターン(図50、符号1150)によりエッチングする(図52A、図52B、図52C)。

10

20

30

40

50

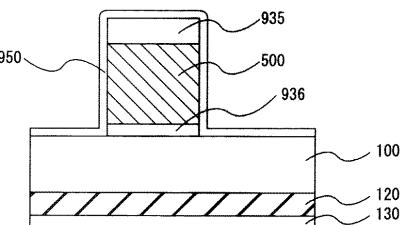

## 【0076】

SOI100表面を酸化し、2.5nmのゲート絶縁膜900を形成する。多結晶シリコン500を300nm堆積したのち、CMP法で研磨し、多結晶シリコン表面を平坦化する。更に、CVD法によりシリコン酸化膜935を50nm堆積した後、選択ゲートパターン（図50、符号1500）を用いて、酸化膜935と多結晶シリコン500の積層膜をエッティングする（図53A、図53B、図53C）。

## 【0077】

メモリゲート領域のシリコン表面を露出させ、熱酸化することで4nmの酸化膜を形成し、10nmの厚さのシリコン窒化膜及び7nmのシリコン酸化膜を積層することで、メモリゲート絶縁膜950を形成する（図54A、図54B、図54C）。

10

## 【0078】

多結晶シリコンを50nm堆積したのち、スペーサ加工プロセスを用いることで選択ゲート側面にスペーサゲート550を形成し（図55A）、不要部分の多結晶シリコンを除去する（図55A、図55B、図55C）。

## 【0079】

前述した実施例と同様にして、拡散層200、210、300、310を形成することで、凸型形状をしたメモリセル構造を得ることができる（図56A、図56B、図56C）。

## 【0080】

<実施の形態10>

図57A-Cから図61A-Cに、前記SOIを用いて凸型形状セルを形成する際、容易に加工できるプロセスを示した。これらの各図でも図50の各断面を用いている。

20

## 【0081】

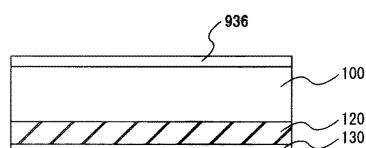

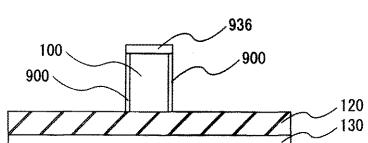

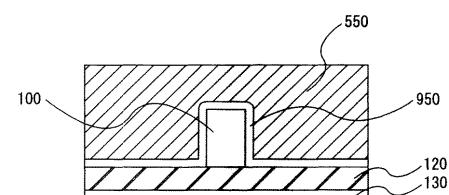

SOI基板表面のシリコン（SOI）を熱酸化し30nmの厚さの酸化膜層936を形成する。その後、活性領域パターン（図50、符号1150）を用いて酸化膜936及びSOI層を加工する（図57A、図57B、図57C）。

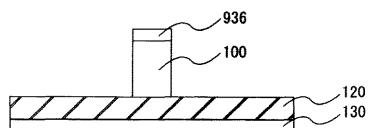

（図58）SOI100側面を酸化し2.5nmのゲート絶縁膜900を形成する。多結晶シリコン500を300nm堆積したのち、CMP法で研磨し、多結晶シリコン表面を平坦化する。さらに、CVD法によりシリコン酸化膜935を50nm堆積した後、選択ゲートパターン（図50、1500）を用いて、酸化膜935と多結晶シリコン500の積層膜（図58A）をエッティングする（図58A、図58B、図58C）。この際、層936によりSOI100はエッティングされない。

30

## 【0082】

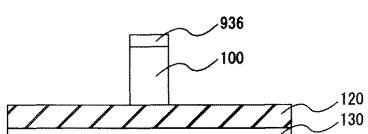

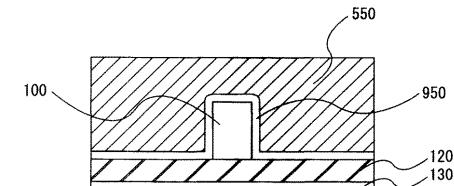

メモリゲート領域のシリコン表面を露出させ、熱酸化することで4nmの酸化膜を形成し、10nmの厚さのシリコン窒化膜及び7nmのシリコン酸化膜を積層することで、メモリゲート絶縁膜950（図59A）を形成する（図59A、図59B、図59C）。

## 【0083】

多結晶シリコンを50nm堆積した後、スペーサ加工プロセスを用いることで選択ゲート500の側面にスペーサゲート550を形成し、不要部分の多結晶シリコンを除去する（図60A、図60B、図60C）。

40

## 【0084】

前述した実施例と同様にして、拡散層200、210、300、310を形成することで、凸型形状をしたメモリセル構造を得ることができる（図61A、図61B、図61C）。

## 【0085】

メモリゲートでは、ゲート絶縁膜950が選択ゲートのゲート絶縁膜900に比べ厚いため、駆動力に劣るものになっている。しかし、この構造では、メモリゲートはSOIの上部及び両側面をチャネルとすることができるため、選択ゲートとの電流駆動力比を小さくすることができる。

## 【0086】

50

## &lt;実施の形態 11 &gt;

これまで、メモリゲートを選択ゲートの片側にのみ形成するメモリセル構造について説明してきたが、本例は、選択ゲートの両側にメモリゲートをもつ構造でも有効である。

## 【0087】

図62に、その平面レイアウトを示した。選択ゲート1500の両側にメモリゲート1550が配置されている。但し、メモリゲートを自己整合プロセスで形成する場合には、マスクパターンとしてはメモリゲートは存在しない。図63A-Cは、図62の素子断面構造を示したものである。図63Aは、図62のチャネル方向(A-A断面)での断面図、図63Bは、選択ゲートを含む図62のB-B断面、図63Cはメモリゲートを含む図62のC-C及びD-D断面である。C-C断面とD-D断面では、同じ構造が形成されている。図21A-Cから図25A-Cにおいて示した製法で、図23A-Cで説明した不要部分のメモリゲート550除去工程を変え、選択ゲートの両側にメモリゲートが形成されるようにすればよい。本実施例では、選択ゲートおよび両メモリゲートが凸型形状上に形成されている。

## 【0088】

図64は、図62および図63で説明したメモリセル構造で、選択ゲートは平坦構造で形成し、メモリゲートが凸型形状で形成されているものである。図37A-Cから図43A-Cにおいて説明した製造工程を用いることで形成することができる。

## 【0089】

## &lt;実施の形態 12 &gt;

図65、図66A-Cは、SODIを用いて選択ゲートの両側にメモリゲートを形成する場合を示したものである。

## 【0090】

図65に、その平面レイアウトを示した。選択ゲート1500の両側にメモリゲート1550が配置されている。ただし、メモリゲートを自己整合プロセスで形成する場合には、マスクパターンとしてはメモリゲートは存在しない。図66A-Cは図65の素子断面構造を示したものである。図66Aは、図62のチャネル方向(A-A断面)での断面図、図66Bは、選択ゲートを含む図65のB-B断面、図66Cはメモリゲートを含む図65のC-C及びD-D断面である。C-C断面とD-D断面では、同じ構造が形成されている。図21A-Cから図25A-Cにおいて示した製法で、図23A-Cで説明した不要部分のメモリゲート550除去工程を変え、選択ゲートの両側にメモリゲートが形成されるようにすればよい。本実施例では、選択ゲート及び両メモリゲートがSODIで作られた凸型形状上に形成することができる。

## 【0091】

本願発明の主な諸形態を列挙する。

## 【0092】

第1の例は、シリコン基板上に形成された、第1の絶縁ゲート型電界効果トランジスタと、該トランジスタゲートと並行に、かつ接して形成された第2の絶縁ゲート型電界効果トランジスタを持ち、これらゲートと直行する方向に第1の拡散層電極と、第1のゲートと該ゲートにより制御された第1のチャネルと、第2のゲートと該ゲートに制御された第2のチャネルと、第2の拡散層電極が置かれ、第2の絶縁ゲート型電界効果トランジスタのゲート絶縁膜が電荷保持機能をもち、第1の拡散層と第2の拡散層間を流れる電流を、第2のゲートによる電圧特性を変化させる不揮発性半導体記憶装置において、第1のトランジスタのチャネルが、第1の拡散層電極と第2の拡散層電極をむすぶチャネル方向に直行する方向に凸型に形成され、該凸部の側面をチャネルとして用いていることを特徴とする半導体記憶装置。

## 【0093】

第2の例は、シリコン基板上に形成された、第1の絶縁ゲート型電界効果トランジスタと、該トランジスタゲートと並行に、かつ接して形成された第2の絶縁ゲート型電界効果トランジスタを持ち、これらゲートと直行する方向に第1の拡散層電極と、第1のゲート

10

20

30

40

50

と該ゲートにより制御された第1のチャネルと、第2のゲートと該ゲートに制御された第2のチャネルと、第2の拡散層電極が置かれ、第2の絶縁ゲート型電界効果トランジスタのゲート絶縁膜が電荷保持機能をもち、第1の拡散層と第2の拡散層間を流れる電流を、第2のゲートによる電圧特性を変化させる不揮発性半導体記憶装置において、第2のトランジスタのチャネルが、第1の拡散層電極と第2の拡散層電極をむすぶチャネル方向に直行する方向に凸型に形成され、該凸部の側面をチャネルとして用いていることを特徴とする半導体記憶装置。

【0094】

第3の例は、シリコン基板上に形成された、第1の絶縁ゲート型電界効果トランジスタと、該トランジスタゲートと並行に、かつ接して形成された第2の絶縁ゲート型電界効果トランジスタを持ち、これらゲートと直行する方向に第1の拡散層電極と、第1のゲートと該ゲートにより制御された第1のチャネルと、第2のゲートと該ゲートに制御された第2のチャネルと、第2の拡散層電極が置かれ、第2の絶縁ゲート型電界効果トランジスタのゲート絶縁膜が電荷保持機能をもち、第1の拡散層と第2の拡散層間を流れる電流を、第2のゲートによる電圧特性を変化させる不揮発性半導体記憶装置において、第1と第2のトランジスタのチャネルが、第1の拡散層電極と第2の拡散層電極をむすぶチャネル方向に直行する方向に凸型に形成され、前記凸部の側面をチャネルとして用いていることを特徴とする半導体記憶装置。

【0095】

第4の例は、シリコン基板上に形成された、第1の絶縁ゲート型電界効果トランジスタと、該トランジスタゲートと並行に、かつ接して形成された第2の絶縁ゲート型電界効果トランジスタを持ち、これらゲートと直行する方向に第1の拡散層電極と、第1のゲートと該ゲートにより制御された第1のチャネルと、第2のゲートと該ゲートに制御された第2のチャネルと、第2の拡散層電極が置かれ、第2の絶縁ゲート型電界効果トランジスタのゲート絶縁膜が電荷保持機能をもち、第1の拡散層と第2の拡散層間を流れる電流を、第2のゲートによる電圧特性を変化させる不揮発性半導体記憶装置において、第1のトランジスタのチャネルは平坦な基板面をチャネルとし、第2のトランジスタのチャネルが、第1の拡散層電極と第2の拡散層電極をむすぶチャネル方向に直行する方向に凸型に形成され、前記凸部の側面をチャネルとして用いていることを特徴とする半導体記憶装置。

【0096】

第5の例は、一つの基板の上に、複数の前記第1の例なる半導体記憶装置と、絶縁膜を介してチャネルを制御する電界効果型トランジスタを持ち、少なくとも1つの電界効果型トランジスタのチャネルが平坦であることを特徴とする、集積半導体装置。

【0097】

第6の例は、一つの基板の上に、複数の前記第2の例なる半導体記憶装置と、絶縁膜を介してチャネルを制御する電界効果型トランジスタを持ち、少なくとも1つの電界効果型トランジスタのチャネルが平坦であることを特徴とする、集積半導体装置。

【0098】

第7の例は、一つの基板の上に、複数の前記第3の例なる半導体記憶装置と、絶縁膜を介してチャネルを制御する電界効果型トランジスタを持ち、少なくとも1つの電界効果型トランジスタのチャネルが平坦であることを特徴とする、集積半導体装置。

【0099】

第8の例は、一つの基板の上に、複数の前記第4の例なる半導体記憶装置と、絶縁膜を介してチャネルを制御する電界効果型トランジスタを持ち、少なくとも1つの電界効果型トランジスタのチャネルが平坦であることを特徴とする、集積半導体装置。

【0100】

第9の例は、前記第3の例なる半導体記憶装置と、絶縁膜を介してチャネルを制御する電界効果型トランジスタを持つ集積半導体装置の形成工程において、素子分離領域を形成する工程と、少なくとも1つの該電界効果トランジスタを覆う工程と、該マスクにより該半導体記憶装置のチャネル部を凸型形状に加工する工程を持つことを特徴とする半導体記

10

20

30

40

50

憶装置の形成法。

【0101】

第10の例は、前記第4の例なる半導体記憶装置の形成工程において、第1のゲート電極を形成した後、該第1のゲート電極をマスクにエッチングをする工程を持ち、第2のトランジスタのチャネルを凸型形状とする工程を持つことを特徴とする半導体記憶装置の形成法。

【0102】

以上詳細に説明した通り、本発明方式は、現行の半導体プロセスのみを用いて、より性能の高い半導体装置を得ることができるため、高い利用可能性を持つ。

【図面の簡単な説明】

10

【0103】

【図1】図1は、メモリセルを説明するためのメモリセル等価回路図である。

【図2】図2は、メモリセルアレイを説明するための等価回路図である。

【図3】図3は、メモリセルアレイを説明するための等価回路図である。

【図4】図4は、メモリセルレイアウトを説明するための平面配置図である。

【図5】図5は、メモリセルアレイを説明するための等価回路図である。

【図6】図6は、メモリセルレイアウトを説明するための平面配置図である。

【図7】図7は、メモリセルアレイを説明するための等価回路図である。

【図8】図8は、メモリセルレイアウトを説明するための平面配置図である。

【図9】図9は、メモリセルアレイを説明するための等価回路図である。

20

【図10】図10は、メモリセルレイアウトを説明するための平面配置図である。

【図11】図11は、メモリセル構造を説明するための平面配置図である。

【図12】図12は、本発明の素子構造を説明する断面構造図である。

【図13A】図13Aは、本発明の第1の素子製造工程を説明する断面構造図である。

【図13B】図13Bは、本発明の第1の素子製造工程を説明する断面構造図である。

【図13C】図13Cは、本発明の第1の素子製造工程を説明する断面構造図である。

【図14A】図14Aは、本発明の第1の素子製造工程を説明する断面構造図である。

【図14B】図14Bは、本発明の第1の素子製造工程を説明する断面構造図である。

【図14C】図14Cは、本発明の第1の素子製造工程を説明する断面構造図である。

【図15A】図15Aは、本発明の第1の素子製造工程を説明する断面構造図である。

【図15B】図15Bは、本発明の第1の素子製造工程を説明する断面構造図である。

【図15C】図15Cは、本発明の第1の素子製造工程を説明する断面構造図である。

【図16A】図16Aは、本発明の第1の素子製造工程を説明する断面構造図である。

【図16B】図16Bは、本発明の第1の素子製造工程を説明する断面構造図である。

【図16C】図16Cは、本発明の第1の素子製造工程を説明する断面構造図である。

【図17A】図17Aは、本発明の第1の素子製造工程を説明する断面構造図である。

【図17B】図17Bは、本発明の第1の素子製造工程を説明する断面構造図である。

【図17C】図17Cは、本発明の第1の素子製造工程を説明する断面構造図である。

【図18A】図18Aは、本発明の第1の素子製造工程を説明する断面構造図である。

【図18B】図18Bは、本発明の第1の素子製造工程を説明する断面構造図である。

【図18C】図18Cは、本発明の第1の素子製造工程を説明する断面構造図である。

【図19A】図19Aは、本発明の第1の素子製造工程を説明する断面構造図である。

【図19B】図19Bは、本発明の第1の素子製造工程を説明する断面構造図である。

【図19C】図19Cは、本発明の第1の素子製造工程を説明する断面構造図である。

【図20A】図20Aは、本発明の第1の素子製造工程を説明する断面構造図である。

【図20B】図20Bは、本発明の第1の素子製造工程を説明する断面構造図である。

【図20C】図20Cは、本発明の第1の素子製造工程を説明する断面構造図である。

【図21A】図21Aは、本発明の第2の素子製造工程を説明する断面構造図である。

【図21B】図21Bは、本発明の第2の素子製造工程を説明する断面構造図である。

【図21C】図21Cは、本発明の第2の素子製造工程を説明する断面構造図である。

30

40

50

10

20

30

40

50

【図50】図50は、メモリセルレイアウトを説明するための平面配置図である。

【図5.1】図5.1は、本発明のその他の電子構造を説明する断面構造図である。

- 【図52A】図52Aは、本発明の第9の素子製造工程を説明する断面構造図である。

- 【図52B】図52Bは、本発明の第9の素子製造工程を説明する断面構造図である。

- 【図52C】図52Cは、本発明の第9の素子製造工程を説明する断面構造図である。

- 【図53A】図53Aは、本発明の第9の素子製造工程を説明する断面構造図である。

- 【図53B】図53Bは、本発明の第9の素子製造工程を説明する断面構造図である。

- 【図53C】図53Cは、本発明の第9の素子製造工程を説明する断面構造図である。

- 【図54A】図54Aは、本発明の第9の素子製造工程を説明する断面構造図である。

- 【図54B】図54Bは、本発明の第9の素子製造工程を説明する断面構造図である。

- 【図54C】図54Cは、本発明の第9の素子製造工程を説明する断面構造図である。

【図 5 5 A】図 5 5 A は、本発明の第 9 の素子製造工程を説明する断面構造図である。

【図 5 5 B】図 5 5 B は、本発明の第 9 の素子製造工程を説明する断面構造図である。

【図 5 5 C】図 5 5 C は、本発明の第 9 の素子製造工程を説明する断面構造図である。

【図 5 6 A】図 5 6 A は、本発明の第 9 の素子製造工程を説明する断面構造図である。

【図 5 6 B】図 5 6 B は、本発明の第 9 の素子製造工程を説明する断面構造図である。

【図 5 6 C】図 5 6 C は、本発明の第 9 の素子製造工程を説明する断面構造図である。

【図 5 7 A】図 5 7 A は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 5 7 B】図 5 7 B は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 5 7 C】図 5 7 C は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 5 8 A】図 5 8 A は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 5 8 B】図 5 8 B は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 5 8 C】図 5 8 C は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 5 9 A】図 5 9 A は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 5 9 B】図 5 9 B は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 5 9 C】図 5 9 C は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 6 0 A】図 6 0 A は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 6 0 B】図 6 0 B は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 6 0 C】図 6 0 C は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 6 1 A】図 6 1 A は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 6 1 B】図 6 1 B は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 6 1 C】図 6 1 C は、本発明の第 10 の素子製造工程を説明する断面構造図である。

【図 6 2】図 6 2 は、メモリセルレイアウトを説明するための平面配置図である。

【図 6 3 A】図 6 3 A は、本発明のその他の素子構造を説明する断面構造図である。

【図 6 3 B】図 6 3 B は、本発明のその他の素子構造を説明する断面構造図である。

【図 6 3 C】図 6 3 C は、本発明のその他の素子構造を説明する断面構造図である。

【図 6 4 A】図 6 4 A は、本発明のその他の素子構造を説明する断面構造図である。

【図 6 4 B】図 6 4 B は、本発明のその他の素子構造を説明する断面構造図である。

【図 6 4 C】図 6 4 C は、本発明のその他の素子構造を説明する断面構造図である。

【図 6 5】図 6 5 は、メモリセルレイアウトを説明するための平面配置図である。

【図 6 6 A】図 6 6 A は、本発明のその他の素子構造を説明する断面構造図である。

【図 6 6 B】図 6 6 B は、本発明のその他の素子構造を説明する断面構造図である。

【図 6 6 C】図 6 6 C は、本発明のその他の素子構造を説明する断面構造図である。

【符号の説明】

【0 1 0 4】

1 0 0、1 3 0：基板、1 2 0：酸化膜、2 0 0、2 1 0、3 0 0、3 1 0：拡散層電極、5 0 0、5 5 0：ゲート電極、6 0 0、6 2 0、6 3 0、6 5 0、6 5 5：シリサイド層、9 0 0、9 5 0：ゲート絶縁膜、9 3 0、9 3 1、9 3 2、9 3 5、9 3 6、9 4 0：絶縁膜層、8 0 0、8 0 1、8 0 2：レジスト、1 5 0 0：選択ゲートパターン、1 1 5 0：活性領域パターン、1 5 5 0：メモリゲート配置、1 5 5 1：スペーサエッチングマスクパターン、1 5 5 5：加工残り、1 6 5 0：コンタクトパターン。

10

20

30

40

【図1】

【図2】

【図3】

図 3

【図5】

図 5

【図4】

図4

【図6】

【図7】

【図8】

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図 13 A】

図 13 A

【図 13 B】

図 13 B

【図 13 C】

図 13 C

【図 14 A】

図 14 A

【図 14 B】

図 14 B

【図 14 C】

図 14 C

【図 15 C】

図 15 C

【図 15 A】

図 15 A

【図 15 B】

図 15 B

【図 16 A】

図 16 A

【図 16 B】

図 16 B

【図 16 C】

図 16 C

【図 17 A】

図 17 A

【図 17 B】

図 17 B

【図 17 C】

図 17 C

【図 18 A】

図 18 A

【図 18 C】

図 18 C

【図 18 B】

図 18 B

【図 19 A】

図 19 A

【図 19 B】

図 19 B

【図 19 C】

図 19 C

【図 20 A】

図 20 A

【図 20 B】

図 20 B

【図 20 C】

図 20 C

【図 21 A】

図 21 A

【図 21 B】

図 21 B

【図 21 C】

図 21 C

【図 2 2 A】

図 2 2 A

【図 2 2 B】

図 2 2 B

【図 2 2 C】

図 2 2 C

【図 2 3 A】

図 2 3 A

【図 2 3 B】

図 2 3 B

【図 2 4 A】

図 2 4 A

【図 2 3 C】

図 2 3 C

【図 2 4 B】

図 2 4 B

【図 24 C】

図 24 C

【図 25 A】

図 25 A

【図 25 B】

図 25 B

【図 25 C】

図 25 C

【図 26】

図 26

【図 27 B】

図 27 B

【図 27 A】

図 27 A

【図 28】

図 28

【図29】

【図30A】

図 30 A

【図30B】

図 30 B

【図30C】

図 30 C

【図31】

図 3 1

【図32】

図 3 2

【図33】

【図34】

【図35】

【図36】

【図37A】

図 37A

【図37B】

図 37B

【図37C】

図 37C

【図37D】

図 37D

【図37E】

図 37E

【図38A】

図 38A

【図38D】

図 38D

【図38B】

図 38B

【図38E】

図 38E

【図38C】

図 38C

【図39A】

【図39B】

【図39C】

【図39D】

【図39E】

【図40A】

【図40B】

【図40C】

【図 4 0 D】

図 4 0 D

【図 4 0 E】

図 4 0 E

【図 4 1 A】

図 4 1 A

【図 4 1 B】

図 4 1 B

【図 4 1 C】

図 4 1 C

【図 4 1 D】

図 4 1 D

【図 4 1 E】

図 4 1 E

【図42A】

図42A

【図42B】

図42B

【図42C】

図42C

【図42D】

図42D

【図42E】

図42E

【図43B】

図43B

【図43A】

図43A

【図43C】

図43C

【図43D】

図43D

【図43E】

図43E

【図43F】

図43F

【図44A】

図44A

【図44B】

図44B

【図44C】

図44C

【図44D】

図44D

【図44E】

図44E

【図45A】

図45A

【図45D】

図45D

【図45E】

図45E

【図45B】

図45B

【図45C】

図45C

【図46A】

図46A

【図46B】

図46B

【図 4 6 C】

図 4 6 C

【図 4 6 D】

図 4 6 D

【図 4 6 E】

図 4 6 E

【図 4 7 A】

図 4 7 A

【図 4 7 B】

図 4 7 B

【図 4 7 D】

図 4 7 D

【図 4 7 C】

図 4 7 C

【図 4 7 E】

図 4 7 E

【図48A】

図48A

【図48B】

図48B

【図48C】

図48C

【図48D】

図48D

【図48E】

図48E

【図50】

図50

【図49】

図49

【図51】

図51

【図 5 2 A】

図 5 2 A

【図 5 2 B】

図 5 2 B

【図 5 2 C】

図 5 2 C

【図 5 3 C】

図 5 3 C

【図 5 4 A】

図 5 4 A

【図 5 4 B】

図 5 4 B

【図 5 3 A】

図 5 3 A

【図 5 3 B】

図 5 3 B

【図 5 4 C】

図 5 4 C

【図 5 5 A】

図 5 5 A

【図 5 5 B】

図 5 5 B

【図 5 5 C】

図 5 5 C

【図 5 6 A】

図 5 6 A

【図 5 6 B】

図 5 6 B

【図 5 6 C】

図 5 6 C

【図 5 7 A】

図 5 7 A

【図 5 7 B】

図 5 7 B

【図 5 7 C】

図 5 7 C

【図 5 8 A】

図 5 8 A

【図 5 8 B】

図 5 8 B

【図 5 8 C】

図 5 8 C

【図 5 9 A】

図 5 9 A

【図 5 9 B】

図 5 9 B

【図 5 9 C】

図 5 9 C

【図 6 0 A】

図 6 0 A

【図 6 1 A】

図 6 1 A

【図 6 1 B】

図 6 1 B

【図 6 0 B】

図 6 0 B

【図 6 0 C】

図 6 0 C

【図 6 1 C】

図 6 1 C

【図 6 2】

図 6 2

【図 6 3 A】

図 63A

〔 図 6 3 B 〕

図 63B

【図 6.4.B】

図 64B

【図 6-4-C】

図 64C

【図 6 3 C】

図 63c

〔図 6 4 A 〕

図 64A

【 図 6 5 】

65

【図 6 6 A】

図 6 6 A

【図 6 6 C】

図 6 6 C

【図 6 6 B】

図 6 6 B

---

フロントページの続き

(72)発明者 木村 紳一郎

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

(72)発明者 石丸 哲也

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

F ターム(参考) 5F083 EP18 EP36 EP63 EP68 EP77 ER02 ER11 ER30 HA02 JA04

JA19 JA35 JA53 NA01 PR05 PR12 PR36 PR37

5F101 BA45 BB02 BC11 BD07 BD22 BD30 BD33 BD35 BE02 BE05

BE07 BH03 BH09 BH15