(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6923886号

(P6923886)

(45) 発行日 令和3年8月25日(2021.8.25)

(24) 登録日 令和3年8月3日(2021.8.3)

|              |           |

|--------------|-----------|

| (51) Int.Cl. | F 1       |

| G06F 1/26    | (2006.01) |

| G06F 1/28    | (2006.01) |

| H02H 9/02    | (2006.01) |

| H02J 1/00    | (2006.01) |

| GO6F         | 1/26      |

| GO6F         | 1/28      |

| HO2H         | 9/02      |

| HO2J         | 1/00      |

| GO6F         | 1/26      |

| GO6F         | 1/28      |

| HO2H         | 9/02      |

| HO2J         | 1/00      |

|              | 306       |

|              | E         |

|              | 309R      |

請求項の数 17 (全 20 頁)

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2018-556875 (P2018-556875)  |

| (86) (22) 出願日      | 平成29年4月27日(2017.4.27)         |

| (65) 公表番号          | 特表2019-519837 (P2019-519837A) |

| (43) 公表日           | 令和1年7月11日(2019.7.11)          |

| (86) 国際出願番号        | PCT/US2017/029849             |

| (87) 国際公開番号        | W02017/189852                 |

| (87) 国際公開日         | 平成29年11月2日(2017.11.2)         |

| 審査請求日              | 令和2年4月19日(2020.4.19)          |

| (31) 優先権主張番号       | 15/234,722                    |

| (32) 優先日           | 平成28年8月11日(2016.8.11)         |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |

| (31) 優先権主張番号       | 62/328,711                    |

| (32) 優先日           | 平成28年4月28日(2016.4.28)         |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |

|           |                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 507107291<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 75265<br>-5474 ダラス メイル ステイショ<br>ン 3999 ピーオーボックス 655<br>474 |

| (74) 代理人  | 100098497<br>弁理士 片寄 恒三                                                                                                |

| (72) 発明者  | ハッサン ブーヤ フォーガニザーテー<br>アメリカ合衆国 76107 テキサス州<br>フォート ワース, ハミルトン アヴ<br>ェニュー 3320                                          |

最終頁に続く

(54) 【発明の名称】高速ターンオンパワースイッチ

## (57) 【特許請求の範囲】

## 【請求項 1】

電力スイッチ回路であって、

第1の電力端子と、

第2の電力端子と、

前記第1の電力端子と前記第2の電力端子との間に結合される導通経路と、第1の制御端子とを有する第1の電力スイッチトランジスタと、

チャージポンプ入力とチャージポンプ出力とを有するチャージポンプであって、前記チャージポンプ入力における第1の選択信号に応答して第1の周波数で動作することにより

、又は前記チャージポンプ入力における第2の選択信号に応答して前記第1の周波数よりも高い第2の周波数で動作することにより、前記チャージポンプ出力に電圧を生成するよう構成される、前記チャージポンプと、

前記チャージポンプ出力と前記第1の制御端子との間に結合される第1の電流源であって、第1の電流を前記第1の制御端子に印加するよう構成される、前記第1の電流源と、

、前記チャージポンプ出力と前記第1の制御端子との間に結合されるブースト電流源であって、ブースト制御入力を有し、前記ブースト制御入力におけるブースト信号に応答して前記第1の制御端子にブースト電流を印加するよう構成される、前記ブースト電流源と、

、制御論理入力と、前記チャージポンプ入力に結合される第1の制御論理出力と、前記ブ

10

20

一スト制御入力に結合される第2の制御論理出力とを有する制御論理であって、前記制御論理入力におけるモード信号に応答して前記第1の制御論理出力に前記第1の選択信号を供給し、

前記制御論理入力におけるロールスワップ信号に応答して、前記第1の制御論理出力に前記第2の選択信号を供給し、前記第2の制御論理出力に前記ブースト信号を供給する、

ように構成される、前記制御論理と、

を含む、電力スイッチ回路。

#### 【請求項2】

請求項1に記載の電力スイッチ回路であって、

前記第1及び第2の電力端子の間に導通する電力電流に対応する信号を受信するように構成される入力と、前記電力電流が或る電流制限を超えることに応答して前記第1の制御端子から電流を導通するように構成される出力とを有する電流制限回路を更に含む、電力スイッチ回路。 10

#### 【請求項3】

請求項2に記載の電力スイッチ回路であって、

前記電流制限回路が、

前記電力電流と前記電流制限との差に対応する入力電流を導通するように構成される導通経路を有する第1のミラートランジスタと、

前記第1の制御端子と基準電圧端子との間に結合される導通経路と、前記第1のミラートランジスタに結合される制御端子とを有する第2のミラートランジスタであって、前記入力電流が前記電流制限を超えることに応答してオンするように構成される、前記第2のミラートランジスタと、

を含む、電力スイッチ回路。 20

#### 【請求項4】

請求項3に記載の電力スイッチ回路であって、

前記電流制限回路が、

前記制御論理が前記ロールスワップ信号を受信することに応答して、前記第1のミラートランジスタの前記導通経路に、前記ブースト電流に対応する補償電流を印加するように構成される補償電流源を更に含む、電力スイッチ回路。 30

#### 【請求項5】

請求項1に記載の電力スイッチ回路であって、

前記第1の電力スイッチトランジスタの導通経路と前記第2の電力端子との間に結合される導通経路と、第2の制御端子とを有する第2の電力スイッチトランジスタと、

前記チャージポンプ出力から前記第2の制御端子へ第2の電流を印加するように構成される第2の電流源と、

前記チャージポンプ出力と前記第2の制御端子との間に結合されるスイッチであって、前記制御論理が前記ロールスワップ信号を受信することに応答して閉じるように構成される、前記スイッチと、

を更に含む、電力スイッチ回路。 40

#### 【請求項6】

請求項5に記載の電力スイッチ回路であって、

前記第1及び第2の電力スイッチトランジスタが電界効果トランジスタであり、前記電力スイッチ回路が、

電流制限回路であって、

前記第2の電力スイッチトランジスタの導通経路の電圧における差に対応する感知電流を生成するように構成される差動増幅器と、

ソース／ドレイン経路と、前記感知電流を受信するように構成されるゲートとを有する第1のミラートランジスタと、

前記第1のミラートランジスタのソース／ドレイン経路と並列に結合される電流制限電流源であって、制限電流を導通するように構成される、前記電流制限電流源と、 50

前記制御論理が前記ロールスワップ信号を受信することに応答して、前記第1のミラートランジスタのソース／ドレイン経路に、前記ブースト電流に対応する補償電流を印加するように構成される補償電流源と、

前記第1の制御端子と基準電圧端子との間に結合されるソース／ドレイン経路と、前記第1のミラートランジスタのゲートとドレインとに結合されるゲートとを有する第2のミラートランジスタと、

を含む、前記電流制限回路を更に含む、電力スイッチ回路。

#### 【請求項7】

電子デバイスのインターフェースにおいて電力スイッチを制御する方法であって、

第1の電力端子の電圧が安全限界を下回って下がることに応答して、チャージポンプ出力に電圧を生成するために第1の周波数でチャージポンプを動作させ、前記第1の電力端子と電源が接続される第2の電力端子との間に結合される導通経路を有する第1の電力スイッチトランジスタの第1の制御端子に前記チャージポンプ出力からの第2の制御される電流を含む第1の制御される電流を結合することと、

前記第1の電力端子の電圧が特定のレベルに達することに応答して、前記第1の周波数より低い第2の周波数で前記チャージポンプを動作させ、前記チャージポンプ出力から前記第1の制御端子への前記第1の制御される電流を削減するために前記第2の制御される電流を不活性化することと、

を含む、方法。

#### 【請求項8】

請求項7に記載の方法であって、

前記第1の電力端子の電圧が前記安全限界を下回って下がることに応答して、前記チャージポンプ出力と第2の電力スイッチトランジスタの第2の制御端子との間のスイッチを閉じることであって、前記第2の電力スイッチトランジスタが、前記第1の電力端子と前記第2の電力端子との間に前記第1の電力スイッチトランジスタの導通経路と直列に接続される導通経路を有する、前記スイッチを閉じることと、

前記第1の電力端子の電圧が前記特定のレベルに達することに応答して、前記スイッチを開け、前記チャージポンプ出力から前記第2の制御端子へ第3の制御される電流を結合することと、

を更に含む、方法。

#### 【請求項9】

請求項8に記載の方法であって、

前記第1の電力端子と前記第2の電力端子との間で導通される電流を感知することと、

前記感知された電流が電流制限を超えることに応答して、前記第1の制御端子から電流を導通することと、

前記第1の制御される電流の結合の間に、前記第1の制御される電流に対応する量だけ前記電流制限を増加させることと、

を更に含む、方法。

#### 【請求項10】

請求項9に記載の方法であって、

前記感知することが、前記第2の電力スイッチトランジスタの差動電圧に対応する感知電流を生成することを含み、

前記第1の制御端子から電流を導通することが、

制限電流源に並列の第1のミラートランジスタを介して前記感知電流を導通することと、

前記第1の制御端子と基準電圧端子との間に結合される導通経路を有する第2のミラートランジスタに前記第1のミラートランジスタを介する電流をミラーすることと、

を含み、

前記電流制限を増加させることが、前記制限電流源に並列の前記第1のミラートランジスタを介する前記感知電流に加えて補償電流を印加することを含む、方法。

10

20

30

40

50

## 【請求項 1 1】

請求項 7 に記載の方法であって、

前記第 1 の電力端子の電圧が前記電子デバイスの外側のハブにおいて前記安全限界を下回って下がることに応答して、前記ハブから前記インターフェースへのロールスワップ信号を生成することを更に含み、

前記第 1 の周波数で前記チャージポンプを動作させて前記第 1 の制御される電流を結合することが、前記ロールスワップ信号を受信することに応答して実施される、方法。

## 【請求項 1 2】

電子システムであって、

ハブデバイスであって、

第 1 の電源からの前記ハブデバイスの接続解除に応答してロールスワップ信号を生成するように構成される論理と、

端子を含むインターフェースであって、前記端子が、前記インターフェースの中で共通に接続される電力バス端子を含み、前記第 1 の電源が前記電力バス端子に脱着可能に結合される、前記インターフェースと、

を含む、前記ハブデバイスと、

プロセッサと、第 2 の電源と、前記電力バス端子に結合される電力端子を有する電力スイッチ回路とを含むホストデバイスと、

を含み、

前記電力スイッチ回路が、

第 1 の制御端子と導通経路とを有する第 1 の電力スイッチトランジスタであって、前記導通経路が前記電力端子と電力バスとの間に結合され、前記電力バスが前記第 2 の電源に結合される、前記第 1 の電力スイッチトランジスタと、

チャージポンプ入力とチャージポンプ出力とを有するチャージポンプであって、前記チャージポンプ入力における第 1 の選択信号に応答して第 1 の周波数で動作することにより、又は前記チャージポンプ入力における第 2 の選択信号に応答して前記第 1 の周波数よりも高い第 2 の周波数で動作することにより、前記チャージポンプ出力に電圧を生成するように構成される、前記チャージポンプと、

前記チャージポンプ出力と前記第 1 の制御端子との間に結合される第 1 の電流源であって、前記第 1 の制御端子に第 1 の電流を印加するように構成される、前記第 1 の電流源と、

前記チャージポンプ出力と前記第 1 の制御端子との間に結合されるブースト電流源であって、ブースト制御入力を有し、前記ブースト制御入力におけるブースト信号に応答して前記第 1 の制御端子にブースト電流を印加するように構成される、前記ブースト電流源と、

第 1 の制御論理入力と、前記論理に結合される第 2 の制御論理入力と、前記チャージポンプ入力に結合される第 1 の制御論理出力と、前記ブースト制御入力に結合される第 2 の制御論理出力とを有する制御論理であって、

前記第 1 の制御論理入力におけるモード信号に応答して前記第 1 の制御論理出力に前記第 1 の選択信号を供給し、

前記第 2 の制御論理入力における前記ロールスワップ信号に応答して、前記第 1 の制御論理出力に前記第 2 の選択信号を供給し、前記第 2 の制御論理出力に前記ブースト信号を供給する、

ように構成される、前記制御論理と、

を含む、電子システム。

## 【請求項 1 3】

請求項 1 2 に記載の電子システムであって、

前記電力スイッチ回路が、

前記電力端子と前記電力バスとの間で導通される電力電流に対応する信号を受信するように構成される入力と、前記第 1 の制御端子に結合される出力とを有する電流制限回路で、

10

20

30

40

50

あって、前記電力電流が或る電流制限を超えることに応答して前記第1の制御端子から電流を導通するように構成される、前記電流制限回路を更に含む、電子システム。

**【請求項14】**

請求項13に記載の電子システムであって、

前記電流制限回路が、

前記電力電流と前記電流制限との差に対応する入力電流を導通するように構成される導通経路を有する第1のミラートランジスタと、

前記第1の制御端子と基準電圧端子との間に結合される導通経路と、前記第1のミラートランジスタに結合される制御端子とを有する第2のミラートランジスタであって、前記入力電流が前記電流制限を超えることに応答してオンするように構成される、前記第2のミラートランジスタと、

を含む、電子システム。

**【請求項15】**

請求項14に記載の電子システムであって、

前記電流制限回路が、

前記制御論理が前記ロールスワップ信号を受信することに応答して、前記第1のミラートランジスタの導通経路に、前記ブースト電流に対応する補償電流を印加するように構成される補償電流源を更に含む、電子システム。

**【請求項16】**

請求項12に記載の電子システムであって、

前記電力スイッチ回路が、

前記第1の電力スイッチトランジスタの導通経路と前記電力バスとの間に結合される導通経路と、第2の制御端子とを有する第2の電力スイッチトランジスタと、

前記チャージポンプ出力から前記第2の制御端子に第2の電流を印加するように構成される第2の電流源と、

前記チャージポンプ出力と前記第2の制御端子との間に結合されるスイッチであって、前記制御論理が前記ロールスワップ信号を受信することに応答して閉じるように構成される、前記スイッチと、

を更に含む、電子システム。

**【請求項17】**

請求項16に記載の電子システムであって、

前記第1及び第2の電力スイッチトランジスタが電界効果トランジスタであり、前記電力スイッチ回路が電流制限回路を含み、

前記電流制限回路が、

前記第2の電力スイッチトランジスタの導通経路の電圧における差に対応する感知電流を生成するように構成される差動増幅器と、

ソース／ドレイン経路と、前記感知電流を受信するように構成されるゲートとを有する第1のミラートランジスタと、

前記第1のミラートランジスタのソース／ドレイン経路に並列に接続される電流制限電流源であって、制限電流を導通するように構成される、前記電流制限電流源と、

前記制御論理が前記ロールスワップ信号を受信することに応答して、前記第1のミラートランジスタのソース／ドレイン経路に、前記ブースト電流に対応する補償電流を印加するように構成される補償電流源と、

前記第1の制御端子と基準電圧端子との間に結合されるソース／ドレイン経路と、前記第1のミラートランジスタのゲートとドレインとに結合されるゲートとを有する第2のミラートランジスタと、

を含む、電子システム。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

10

20

30

40

50

本願は、一般に、電子システム及びデバイスを互いにインターフェースすることにおける集積回路に関し、詳細には、接続されるデバイスから電力を受け取るため及び接続されるデバイスに電力を提供するためのインターフェース回路に関する。

#### 【背景技術】

##### 【0002】

種々の電子システムのインターフェースは、種々のユニバーサルシリアルバス（USB）規格に従った、ケーブル、コネクタ、及びコントローラの広汎な実装と共に、近年、より一層標準化されてきている。様々な最近のデバイス及びシステム、特に、一般消費者及びオフィスユース向けのデバイス及びシステムが、データを伝達するため、及び場合によつては、或るUSBデバイスが別のUSBデバイスを給電するのを可能にするために、USBインターフェースを通じて今や容易に互いとインターフェースし得る。実際、ウォールチャージャから或いはホストデバイス（例えば、デスクトップ又はラップトップコンピュータ）から多くの最近のスマートフォンのバッテリを充電する際に、USBが用いられている。10

##### 【0003】

従来のUSBインターフェース（例えば、USB 1.0、USB 2.0）に対して多くの改善を提供するUSB Type-C（又は「USB-C」）インターフェースが開発されてきており、そうした改善は、リバーシブルケーブル、「フリップ可能な」プラグ（すなわち、いずれの方位にも挿入され得るプラグ）、及び一層高いレベルの電力搬送を含む一方で、USB 2.0データ通信との後方互換性を維持する。USB Type Cインターフェースによって、所与のポートが、例えばホストデバイスにおける「ダウンストリーム向きポート」（DFP、downstream-facing port）として、又は、例えばアクセサリデバイスにおける「アップストリーム向きポート」（UFP、upstream-facing port）として機能し得る。どのデバイスがホストであり、どれがアクセサリであるかをプラグの形状が識別する従来のUSBコネクタとは対照的に、USB Type-Cコネクタの2つの「チャネル構成」（「CC」）ピンが、データ及び制御通信のためのホスト-アクセサリ関係を電気的に確立する。より具体的には、ホストデバイスが、CCピンに結合されるプルアップ抵抗器を有する一方で、アクセサリデバイスが、これらのピンに結合されるプルダウン抵抗器を有する。これらのCCピンの電圧を監視することによって、或るデバイスが、別のデバイスへの接続を、及び更にそうした接続のホスト-アクセサリ関係を検出し得る。また、USB Type-Cは、USB Type-Cが接続されるデバイスの役割に応じて、DFP或いはUFPとして働き得る「デュアルロールポート」（DRP）を規定する。安定状態に達するまでデバイスが、DFPとして、その後UFPとして交互に識別することによって、DRPの方向の識別が成される。いくつかのDRPは、2つのDRPの互いに対する接続におけるネゴシエーションを促進するため、優先的なDFP又はUFP状態を有する。2030

##### 【0004】

USB Type-C規格は、単一充電器が、ラップトップ、スマートフォン、タブレット、カメラ、及び多くのその他の機能を含め、多くの異なるデバイスを安全且つ急速に充電する可能性を提供する。例えば、USB PD（「PD」は「power delivery（電力搬送）」を意味する）と名付けられた、USB Type-C下の電力搬送オプションの下で、最大100Wの電力搬送が可能であり、その単一充電器による多様なバッテリ駆動デバイスの急速充電を促進する。このUSB PDオプション下では、所与のポートが、（a）例えば充電器において、電力の「プロバイダ」又は「ソース」として、或いは、（b）例えば電力プロバイダによって充電されているバッテリにおいて、電力の「コンシューマー」又は「シンク」として機能し得る。ホスト-デバイス関係及びソース-シンク関係は、デバイス間における相互整合（co-align）を必要とせず、そのため、データ及び制御目的のためのホストが、充電されているデバイス（すなわち、電力供給のためのシンク）であり得る。USB PD下の電力搬送のためのソース-シンク関係の識別及びネゴシエーションは、USB-Cポートにおいて各デバイスにおけるコントローラ回路要素によ4050

って実施される。より具体的には、このコントローラ回路要素は、U S B - C接続のソース - シンク電力伝送関係を識別するため、U S B T y p e - CコネクタのC Cピンの電流フローの方向を検出する。役割が識別された後、ソースデバイスが、C Cピンにおける選択されたプルアップ抵抗器又は電流源値のその結合によりその出力電力能力を「宣伝する」ことによって、デフォルトU S B - Cレベル(15W)より高い電力レベルがU S B P D下でネゴシエートされる。反対に、シンクは、その端部でプルダウン抵抗器をC Cピンに結合すること、及び、電圧降下を監視することによって、電流消費のレベルを検出する。

#### 【0005】

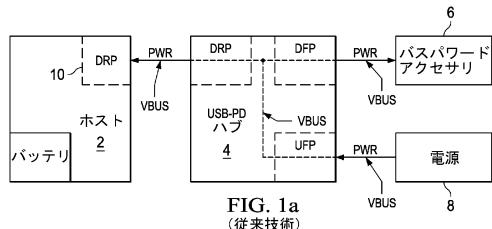

U S B P D規格下で、「ファストロールスワップ」(F R S)動作も特定されている。この動作の目的は、電源を接続から取り外す際、電力コンシューマに対する電力搬送の中止を制限することである。図1A及び図1Bは、F R Sが生じる状況の一例を図示する。図1Aにおいて、ホストデバイス2は、スマートフォンなど、U S B P D対応のホストシステムであり、外部電力を受け取らないとき、そのバッテリ3によって給電される。この例において、ホストデバイス2はホストの役割をするが、(例えば、デスクトップ又はラップトップコンピュータに接続されるとき)アクセサリとしても動作し得、それゆえ、デュアルロールU S B - Cポート(D R P)を有する。この例において、ホスト2のD R P10は、U S B P D対応のハブ4のデュアルロールポートに接続される。ハブ4は、U S B - C及びU S B P D規格下の従来のU S Bハブであり、種々のデバイスを共に結合するためのいくつかのポートを含む。この例において、ハブ4は、アクセサリ6に結合されるダウンストリーム向きポート(D F P)、及び、電源8に結合されるアップストリーム向きポート(U F P)を有する。また、この例において、アクセサリ6は、外部ドライブ、プロジェクト、プリンタ、又はその他の従来のアクセサリなど、バスパワードアクセサリデバイスである。少なくとも一つの例において、電源8はウォールチャージャである。

10

20

#### 【0006】

U S B - CラインV B U S上でのこれらのデバイス間の電力接続及び電力伝送の方向が、図1Aに示されている(データ接続は図示されない)。本質的に、デバイス間のV B U Sラインは、種々のポートの各々におけるV B U Sピンが、これらのポートによってネゴシエートされたのと同じ電圧であるように、ハブ4を介して共に接続される。図1Aは、この例において、電源8がハブ4を介してホストデバイス2及びアクセサリ6に電力を提供することを図示する。電源8によって提供される電力は、バッテリ3を充電し、ホスト2及びアクセサリ6の機能のための動作電力を提供するのに充分である。この電力伝送配置は、上述したようなU S B P D下での検出及びネゴシエーションの結果であり、U S B - C規格下の或る仕様限界(例えば、v S a f e 5 V)を上回るV B U S電圧をもたらす。

30

#### 【0007】

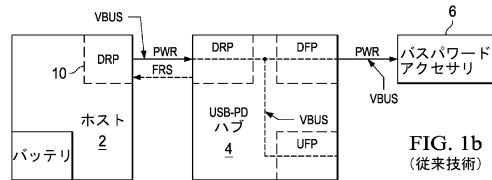

図1Bは、図1Aと同じシステムを図示するが、電源8の取り外し後である。電源8の取り外しに応答して、ハブ4のV B U Sラインの電圧は、いずれのデバイスも電源として作用しないので、仕様限界を下回って降下する。U S B P D規格に従って、ハブ4は、V B U Sライン上の電圧におけるこの降下を検出し、そのD R Pに、非接地C Cワイヤを通じてホストデバイス2におけるD R Pに対する「ファストロールスワップ」(F R S)信号を送出させる。F R S信号は、ホスト2のD R P10にそれ自体を、電力シンクではなく、電源として迅速に構成させることを意図し、そのため、そのバッテリは、最小の中止でハブ4を介してアクセサリ6に電力を供給し始め得る。

40

#### 【0008】

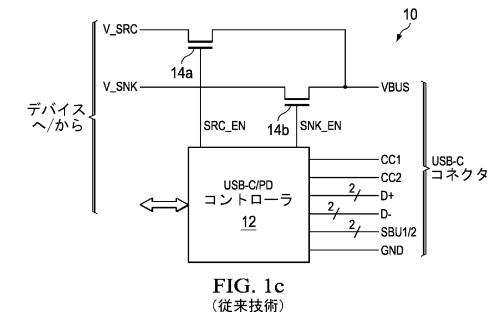

図1Cは、電力伝送を識別及びネゴシエートする際のその機能のため、図1Aの配置におけるホストデバイス2のD R P10の一部の一般的なアーキテクチャを図示する。このアーキテクチャは、概して、テキサスインスツルメンツインコーポレイテッドから入手可能なT P S 6 5 9 8 2 U S B T y p e - C及びU S B P Dコントローラ、パワ

50

ースイッチ、及び高速マルチプレクサに対応する。図1Cに示すように、USB-C/PDコントローラ12は、USB-CコネクタのCC1ピン及びCC2ピンに接続されるプログラム可能及びカスタム論理回路要素を含み、CC1ピン及びCC2ピンにおいて、コントローラ12は、USB-Cケーブルの接続及びそうした接続の向き（すなわち、ホスト-アクセサリ及びソース-シンク）を検出する。また、コントローラ12は、USB PD「契約（contracts）」（すなわち、電源能力及び電力シンクによる需要）を管理し、それに応じて、パワースイッチトランジスタ14a、14bを制御する。パワースイッチトランジスタ14aは、USB-CコネクタのV<sub>BUS</sub>ラインをホストデバイス2における電力ラインV<sub>SRC</sub>に接続するパワースイッチとして動作し、同様に、パワースイッチトランジスタ14bは、V<sub>BUS</sub>ラインを電力ラインV<sub>SNK</sub>に接続するためのパワースイッチとして動作する。ゲート信号SRC\_EN及びSNK\_ENは、それに応じて、パワースイッチトランジスタ14a、14bを制御するためにコントローラ12によって駆動される。この簡略化されたアーキテクチャにおいて、そのデバイス2が電力シンクであると判定すると、コントローラ12は、パワースイッチトランジスタ14bをオンにするためラインSNK\_EN上でアクティブレベルを、及び、パワースイッチトランジスタ14aをオフにするためラインSRC\_EN上でイナクティブレベルを送出し、USB-CコネクタのV<sub>BUS</sub>ラインをラインV<sub>SNK</sub>に接続し、V<sub>BUS</sub>ラインをラインV<sub>SRC</sub>から絶縁する。反対に、そのデバイス2が電源であると判定することに応答して、コントローラ12は、パワースイッチトランジスタ14aをオンにするためラインSRC\_EN上でアクティブレベルを、及び、パワースイッチトランジスタ14bをオフにするためラインSNK\_EN上でイナクティブレベルを送出し、ホストデバイス2のラインV<sub>SRC</sub>をUSB-CコネクタのV<sub>BUS</sub>ラインに接続し、ラインV<sub>SNK</sub>をV<sub>BUS</sub>ラインから絶縁する。例えばTPS65982デバイスによってサポートされるものなど、いくつかの従来のUSB-PDポートは、ソース及びシンクの両方として双方向電力伝送をサポートするパワースイッチングトランジスタを含む。いずれにせよ、ホスト2のDRPは、適切な向きに従って、プルダウン抵抗器或いはプルアップ抵抗器をCCラインに接続する。

10

20

#### 【0009】

図1Aに示される状態において、図1CにおけるDRPポート10のコントローラ12は電力シンクであり、ラインV<sub>SNK</sub>におけるV<sub>BUS</sub>ラインからの電力の受け取りを可能にするため、トランジスタ14bはオン及びトランジスタ14aはオフである。図1Bに対して上述したようなFRS事象において、ホスト4は、CC1及びCC2ワイヤのうちの非接地のワイヤを通じてFRS信号を送出し得る。こうした信号を受け取ると、コントローラ12は、ファストロールスワッププロセスを開始する。このプロセスは、そのUSB-CコネクタのV<sub>BUS</sub>ラインが安全な電圧であることを保証することを含み、この安全な電圧で、トランジスタ14a、14bは、ホストデバイス2の内部回路要素に損傷を与えることなく切り替えられ得る。こうした状況が検出されると、トランジスタ14bはオフにされ、トランジスタ14aはオンにされて、ホストデバイス2のバッテリが、V<sub>BUS</sub>ラインを通じてアクセサリ6に電力を供給することが可能になる。

30

40

#### 【0010】

直近のUSB-PD規格（参照により本明細書に組み込まれるUniversal Serial Bus Power Delivery Specification、Revision 3.0、V1.0a（2016年3月））下では、電力シンク方向から電源方向に切り替え、電力を供給し始めるためのDRPポートに対するFRS指示からの最大の時間遅延は、150μ秒である。このアグレッシブな制限は、100μ秒より少ない、トランジスタ14aのためのスイッチング時間を必要とする。大きな高電圧トランジスタのそのような急速スイッチングは、駆動回路要素のための充分な電流能力を必要とし、高レベルの突入電流を不必要に引き起こし得る。

#### 【発明の概要】

#### 【0011】

説明される例において、外部電力端子の電圧が安全限界を下回って下がることに応答し

50

て、チャージポンプが、チャージポンプノードにおいて電圧を生じさせるために第1の周波数で動作され、第1の制御された電流が、チャージポンプノードからパワースイッチトランジスタの制御端子に結合される。パワースイッチトランジスタは、外部電力端子と内部電源が接続される内部電力端子との間に結合される導通経路を有する。外部電力端子の電圧が、選択されたレベルに達することに応答して、チャージポンプは、第1の周波数より低い第2の周波数で動作され、第1の制御された電流より低い第2の制御された電流が、チャージポンプノードから電力トランジスタの制御端子に結合される。

**【図面の簡単な説明】**

**【0012】**

【図1A】ホストデバイス、アクセサリデバイス、及びこれらのデバイスを接続するハブを含む従来の電子システムのブロック形式の電気回路図であり、ハブに結合される外部電源を備える電力伝送の方向が図示されている。10

【図1B】ホストデバイス、アクセサリデバイス、及びこれらのデバイスを接続するハブを含む従来の電子システムのブロック形式の電気回路図であり、ハブに結合される外部電源を有さない電力伝送の方向が図示されている。

**【0013】**

【図1C】図1A及び図1Bの電子システムのホストデバイスにおける従来のインターフェースポートの、ブロック及び概略形式の電気回路図である。

**【0014】**

【図2】或る実施形態が実装されるU S B P D対応の電子システムのブロック形式の電気回路図である。20

**【0015】**

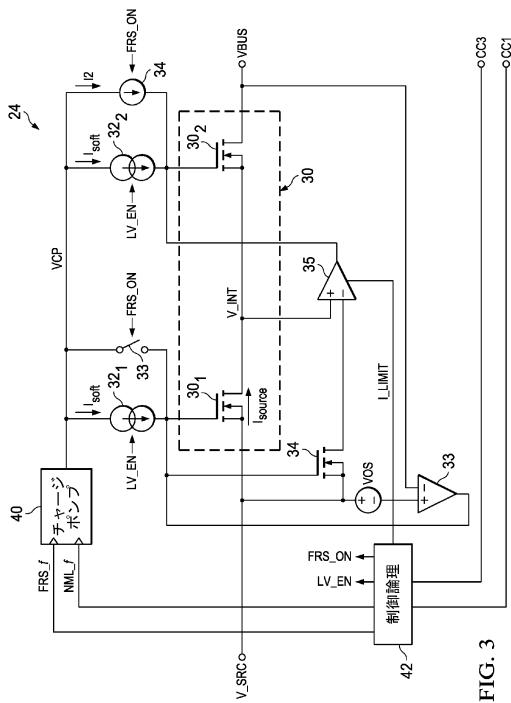

【図3】或る実施形態に従った図2の電子デバイスのインターフェースポートにおけるパワースイッチング回路要素の、ブロック及び概略形式の電気回路図である。

**【0016】**

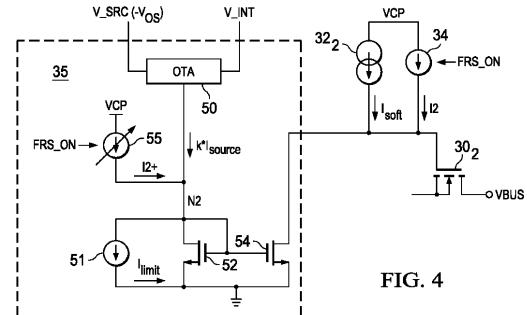

【図4】その実施形態に従った図3のパワースイッチング回路要素における電流制限回路の、ブロック及び概略形式の電気回路図である。

**【0017】**

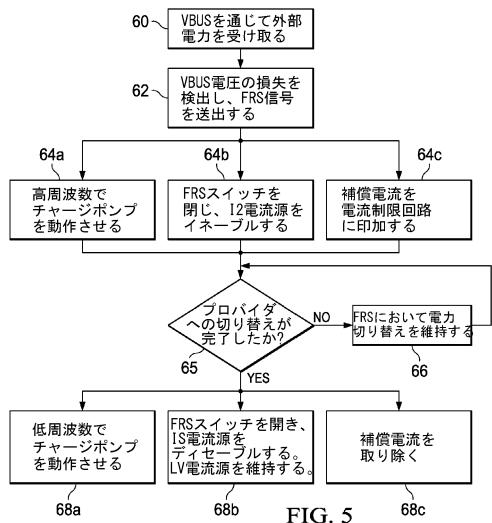

【図5】或る実施形態に従って図3のパワースイッチング回路要素の動作を図示するフローチャートである。30

**【発明を実施するための形態】**

**【0018】**

説明される例は、電子デバイスのインターフェースにおけるパワースイッチトランジスタを迅速及び制御可能にオンにするための動作の回路及び方法を含む。少なくとも一つの説明される例において、この回路及び方法は、電力伝送の方向をシンクからソースに切り替えることに関して、U S B P D (Universal Serial Bus Power Delivery) 規格など、最近のインターフェース規格の仕様を満たす。

**【0019】**

また、この回路及び方法の少なくとも一つの説明される例において、電力コンシューマーから電力プロバイダへのロールスワップの後、低減された電力消費が達成される。また、この回路及び方法は、高電流対応のU S Bハブの使用を可能にする一方で、正確な動作を維持する。40

**【0020】**

説明される例において、電子デバイスのインターフェースポートが、電力バスを介する外部電源からの電力の受け取りから、電力バスを介する外部デバイスへの電力の提供へのロールスワップを実行し得る。インターフェースポートは、内部電力供給ノードを電力バスに選択的に結合するために、(内部電力供給ノードと電力バスとの間に)直列に接続される第1及び第2のパワースイッチトランジスタを含む。急速接続が要求されることを示す「ファストロールスワップ」コマンドに応答して、スイッチ及び制御されたブースト電流源が、付加的なゲート駆動電流を、それぞれ第1及び第2のパワースイッチトランジス50

タに結合する。付加的なゲート駆動電流は、ファストロールスワップの間、高められた周波数で動作するチャージポンプからつくられ、制御された電流源を介してパワースイッチトランジスタの一つに印加される。ファストロールスワップの間、(内部電力供給ノードと電力バスとの間で)ソースされた電流が、プログラムされた限界を超える場合、電流制限回路が、ブースト電流のための補償を用いてパワースイッチトランジスタの一つをオフにする。

#### 【0021】

本明細書で説明される例示の実施形態は、U S B P D (Universal Serial Bus Power Delivery) 規格に従って動作する電子デバイスの U S B (Universal Serial Bus) T y p e C インターフェースへの実装に適しており、そのような実装は、この文脈において特に有利である。同様に、例示の実施形態は、デバイスを、外部電力のコンシューマーであることから、外部に接続されるデバイスに対する電力のプロバイダであることに切り替えるなど、電子デバイス間の電力の搬送に関するその他の応用例に有利に適用可能である。10

#### 【0022】

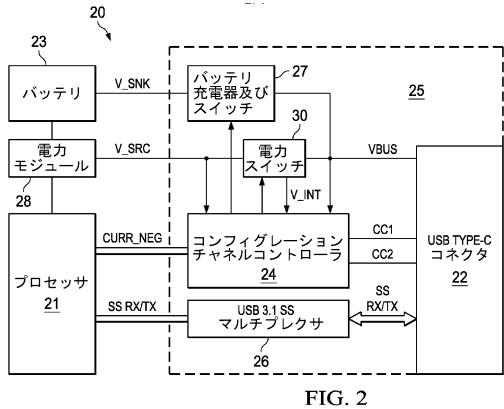

図2は、これらの実施形態に従って構成されるホストデバイス20の一般化されたアーキテクチャを図示する。ホストデバイス20の例は、ラップトップ又はデスクトップコンピュータ、スマートフォン、又はそれ自体の内部電源を備えるその他の電子デバイスなどのコンピュータシステムを含み、それゆえ、そのデバイス機能に適切な機能回路要素を含む。ホストデバイス20の例において、この機能回路要素はプロセッサ21を含み、プロセッサ21は、その所望の機能を実施するためにメモリリソース(図示せず)に記憶されるプログラム命令を実行するプログラム可能なプロセッサである。また、例えば、ホストデバイス20への及びホストデバイス20からの入力及び出力のために用いられる従来の回路機能が含まれる。上記したように、ホストデバイス20は内部電源を含み、内部電源は、この例では、バッテリ23及び電力モジュール28で構成される。電力モジュール28は、プロセッサ21及びその周辺回路など、ホストデバイス20の機能回路要素を給電するための適切なレギュレータ及び電圧変換器を含む。20

#### 【0023】

これらの実施形態によれば、ホストデバイス20は、U S B T y p e C (U S B - C) インターフェース25を含み、U S B - C インターフェース25において、ホストデバイス20への及びホストデバイス20からの電力の搬送を制御するための回路要素が、或る実施形態に従って実装される。この例において、ホストデバイス20のインターフェース25はU S B - C コネクタ22を含み、U S B - C コネクタ22は、上述した図1A及び図1Bの従来の配置などにおいて、他のU S B - C デバイスへの接続のための適切なU S B T y p e C 規格によって特定された適切な端子を含む。これらの端子には、電力端子V B U S、一対のチャネル構成端子C C 1、C C 2、適切な参照電圧(すなわち、接地)端子、及びS S R X / T X 端子として概して図2に示したデータ端子が含まれる。30

#### 【0024】

この実施形態において、インターフェース25は構成チャネルコントローラ24を含み、構成チャネルコントローラ24は、コネクタ22の構成チャネル端子C C 1、C C 2に結合される。構成チャネルコントローラ24は、U S B - C 接続を介するホストデバイス20の、他のデバイスとのインターフェースを管理するための適切な論理回路要素で構成される。U S B - C 接続の場合、構成チャネルライン(C C 1、C C 2)は、デバイスが、データ及び制御目的に関してホストであるか又はアクセサリであるかを判定するために用いられる。デュアルロールポート(D R P)の場合、この判定は、通常、コントローラ24が、プルアップ抵抗器或いはプルダウン抵抗器をその構成チャネル端子C C 1、C C 2に結合すること、及び、これらの端子の電圧を監視することによって実施される。また、上記で組み込まれたU S B P D 規格において説明されるように、コントローラ24は、そのホストデバイス20が、U S B - C 接続を介するその内部電源(この例では、バッ4050

テリ 2 3 及び電力モジュール 2 8 ) からのアクセサリデバイスに対する電力のプロバイダであるか、又は、外部電源からの電力のコンシューマーであるかを判定するため、及び、その役割において提供又は消費されるべき電流レベルを「ネゴシエート」するために、構成チャネル端子 C C 1、C C 2 を用いる。この動作は、ホストデバイス 2 0 のこれらの 2 つの構成要素間の信号ライン C U R R \_ N E G によって示されるように、プロセッサ 2 1 と組み合わせてコントローラ 2 4 によって実施される。

#### 【 0 0 2 5 】

また、U S B - P D 規格に従って、制御シグナリングが、チャネル構成ライン C C 1、C C 2 を通じて実施され、そのようなシグナリングには、外部 U S B - C ハブからホストデバイス 2 への「ファストロールスワップ」信号の通信が含まれる。上記で組み込まれた U S B - P D 規格において説明されるように、このファストロールスワップ信号は、アクセサリデバイスが電力コンシューマーとして接続されたままである一方で、U S B - C 配置から外部電源を取り外す場合など、ホストデバイス 2 0 がその役割を電力コンシューマーから電力プロバイダに変更すべきときに呼び出される。これらの実施形態に従ってそのようなファストロールスワップを行うことについて、コントローラ 2 4 の動作を下記で更に詳細に説明する。10

#### 【 0 0 2 6 】

U S B - C 接続を介するデータ通信は、インターフェース 2 5 における U S B 3 . 1 S S マルチプレクサ 2 6 によって管理される。概して図 2 に示すように、マルチプレクサ 2 6 は、コネクタ 2 2 の幾つかのデータ端子に接続され、幾つかのデータ端子には、具体的には、U S B - C 規格によって特定される二対の送信端子及び二対の受信端子が含まれる。これらの「S S \_ T X 」導体において通信される信号及びこれらの「S S \_ R X 」導体において受け取られる信号は、従来のように、プロセッサ 2 1 と協働してマルチプレクサ 2 6 によって制御される。「旧式の」U S B 通信(例えば、U S B 2 . 0 )は、適切な U S B \_ T y p e \_ C 規格に記載されるように、コネクタ 2 2 から直接にデータ導体を通じてプロセッサ 2 1 へ、及び、プロセッサ 2 1 から成され得る。20

#### 【 0 0 2 7 】

上記したように、ホストデバイス 2 0 のインターフェース 2 5 もまた、電力ホストデバイス 2 0 への及びホストデバイス 2 0 からの、具体的には、バッテリ 2 3 のその内部電源と電力モジュール 2 8 と外部デバイスとの間の、電力の伝送を制御する。上記で組み込まれた U S B - P D 規格に従って、ホストデバイス 2 0 は電力コンシューマーとして動作し得、この場合、電流は、バッテリ 2 3 を充電するため、コネクタ 2 2 の V B U S 端子において外部電源(例えば、電源 8 )から受け取られる。図 2 のアーキテクチャにおいて、コネクタ 2 2 の V B U S 端子は、インターフェース 2 5 のバッテリ充電器及びスイッチ 2 7 に接続される。ホストデバイス 2 0 が電力コンシューマーの役割で動作しているとき、構成チャネルコントローラ 2 4 は、V B U S 端子において受け取られる電流を、ライン V \_ S N K を介してバッテリ 2 3 に送るため、バッテリ充電器及びスイッチ 2 7 を制御する。30

#### 【 0 0 2 8 】

また、インターフェース 2 5 はパワースイッチ 3 0 を含み、パワースイッチ 3 0 は、電力モジュール 2 8 とコネクタ 2 2 の V B U S 端子との間に接続される。それゆえ、ホストデバイス 2 0 が電力プロバイダの役割で動作しているとき、構成チャネルコントローラ 2 4 は、ライン V \_ S R C をコネクタ 2 2 の V B U S 端子に接続するためにパワースイッチ 3 0 を制御し、そのため、電力モジュール 2 8 は、コネクタ 2 2 及び適切な接続ケーブルを介してホストデバイス 2 0 に接続されるアクセサリデバイスへ、レギュレートされた電圧でバッテリ 2 3 からの電流を提供し得る。構成チャネルコントローラ 2 4 は、ホストデバイス 2 0 が電力プロバイダとして動作しているときにバッテリ充電器及びスイッチ 2 7 を開くように制御する。反対に、コントローラ 2 4 は、ホストデバイスが電力コンシューマーとして動作しているときにパワースイッチ 3 0 を開かせる。40

#### 【 0 0 2 9 】

図 3 は、或る実施形態に従って、バッテリ 2 3 及び電力モジュール 2 8 から電力を提供50

する際のパワースイッチ30の制御に関する、パワースイッチ30の及び構成チャネルコントローラ24の一部の構成を図示する。より具体的には、この実施形態のパワースイッチ30は、二つのnチャネル金属酸化物半導体(MOS)トランジスタ30<sub>1</sub>、30<sub>2</sub>を含み、それらのソース/ドレイン経路は、内部V<sub>SRC</sub>導体及びV<sub>BUS</sub>端子間に直列に接続され、電力モジュール28がパワースイッチトランジスタ30に接続される。パワースイッチトランジスタ30<sub>1</sub>は、内部V<sub>SRC</sub>導体においてそのソースを、及びパワースイッチトランジスタ30<sub>2</sub>のソースに接続されるそのドレインを有する。パワースイッチトランジスタ30<sub>2</sub>のドレインは、V<sub>BUS</sub>端子に接続される。トランジスタ30<sub>1</sub>、30<sub>2</sub>の一方又は両方は、比較的幅広のチャネル幅対チャネル長さ(W/L)比を有することによって電力トランジスタであり得、そうでない場合、USB-PD接続を介して一つ又は複数のアクセサリデバイスを給電するためにホストデバイス20に対して充分な電流の伝導をサポートするため比較的堅牢であり、一層高い電圧外部電源をUSB-Cコネクタ22に結合する際に遭遇し得る比較的大きなソース/ドレイン電圧に耐えることができる。例えば、高電圧及び電流のための可能性を考慮すると、パワースイッチ30におけるトランジスタ30<sub>1</sub>、30<sub>2</sub>の一方又は両方は、横型二重拡散MOSトランジスタ(DMOS、又はLDMOS)として構成され得る。

#### 【0030】

この実施形態において、構成チャネルコントローラ24は、逆電流保護回路33及び電流制限回路35を含む。逆電流保護回路33は、この実装において比較器として機能し、V<sub>BUS</sub>端子の電圧を、V<sub>SRC</sub>導体の電圧からオフセット電圧V<sub>0s</sub>を引いたものと比較し、その比較に従って、パワースイッチトランジスタ30<sub>1</sub>のゲートを駆動する。この実施形態において、V<sub>BUS</sub>端子の電圧が、内部V<sub>SRC</sub>導体の電圧のオフセットV<sub>0s</sub>(例えば、約10mV)内で生じる場合、逆電流保護回路33はパワースイッチトランジスタ30<sub>1</sub>をオフにするように動作し、逆電流がパワースイッチ30を介して導通されないことを保証する。電力がパワースイッチ30を介して受け取られ得るいくつかの実装において、逆電流保護回路33は、外部デバイスからバッテリ23への、制御された量の逆電流を可能にするように動作し得る。

#### 【0031】

同様に、電流制限回路35も比較器として機能し、パワースイッチトランジスタ30<sub>1</sub>のソース/ドレイン経路のいずれかの側の電圧を比較し、それに応じて、パワースイッチトランジスタ30<sub>2</sub>のゲートを制御する。図3の実施形態において、電流制限回路35の一方の入力(負入力)が、パストランジスタ34を介して内部V<sub>SRC</sub>導体の電圧を受け取り、他方の(正)入力が、トランジスタ30<sub>1</sub>、30<sub>2</sub>のソース/ドレイン経路間の中間ノードV<sub>INT</sub>の電圧を受け取る。パストランジスタ34のゲートは、逆電流保護回路33の出力によって制御され、上述したような逆電流の場合にオフにされる。それゆえ、電流制限回路35に印加される差動電圧は、オンのとき、パワースイッチトランジスタ30<sub>1</sub>の電圧降下に対応し、それゆえ、電力モジュール28から、V<sub>BUS</sub>端子に接続される外部アクセサリへ導通されているソース電流I<sub>SOURCE</sub>に対応する。下記で更に詳細に説明されるように、電流制限回路35は、電流I<sub>SOURCE</sub>が、制御論理42から通信される限界I<sub>LIMIT</sub>を超えることに応答して、電流I<sub>SOURCE</sub>がその限界にレギュレートされるように、パワースイッチトランジスタ30<sub>2</sub>を抑えるように動作する。USB-PDの文脈において、この限界I<sub>LIMIT</sub>は、ホストデバイス20と、USB-Cコネクタ22において接続される一つまたは複数のアクセサリとの間でネゴシエートされた電流レベルに対応する。

#### 【0032】

この実施形態に従って、コントローラ24は、チャージポンプノードV<sub>CP</sub>においてチャージポンプ40によってつくられた電流を、それらのそれぞれのゲートに印加することによってトランジスタ30<sub>1</sub>、30<sub>2</sub>をオンにするように動作する。チャージポンプ40は、一層低い電力供給電圧から、高められた電圧をチャージポンプノードV<sub>CP</sub>において生じさせるためのいくつかの従来のアプローチの任意の一つに対して構成される従来のチ

10

20

30

40

50

ヤージポンプ回路である。一般的な意味において、チャージポンプ 40 は、周期信号の交互の位相において充電及び放電する「フライング」キャパシタと共に、印加される周期信号によってクロック制御される一つ又は複数のスイッチングデバイスを含む。単純な 2 位相の例の第 1 の位相において、スイッチングデバイスは、フライングキャパシタを電力供給電圧に接続して、その電圧に向かって充電する。第 2 の位相において、フライングキャパシタは、供給電圧と負荷との間に直列に接続され、これは、負荷における電圧を、電力供給電圧を上回って上昇させる効果を有する。負荷に供給される電流は、チャージポンプに印加される周期信号の周波数と共に増加する。図 3 の実施形態において、チャージポンプ 40 は、例えば信号 NML\_f、FRS\_f によって制御論理 42 から提供されるなどの二つの異なる周波数で動作可能であり、この結果、これらの二つの周波数は、チャージポンプノード VCP から入手可能な異なるレベルの電流となる。例えば、NML\_f 信号、FRS\_f 信号は、直接的に、異なる周波数のクロック信号であり得、又は、チャージポンプ 40 が切り替わる周波数をその他の方で設定する制御信号であり得る。一実装において、FRS\_f クロック信号は、NML\_f 通常モードクロック信号の周波数の 3 ~ 4 倍の周波数である。動作において、下記で更に詳細に説明するように、一層高い周波数 FRS\_f 信号は、チャージポンプ 40 のスイッチング周波数を増加させるため、ファストロールスワップ事象の間イネーブルされ、それゆえ、チャージポンプノード VCP においてソースし得る電流を増加させる。ファストロールスワップに続いて、FRS\_f 信号がデアサー卜され、NML\_f 信号がアサー卜され、インターフェース 25 の電力消費を低減するため、チャージポンプ 40 のスイッチング周波数が減速され、その出力電流が低減される。

10

20

### 【0033】

パワースイッチトランジスタ 30<sub>1</sub> のゲートは、並列に接続される電流源 32<sub>1</sub> 及びスイッチ 33 を介してチャージポンプノード VCP から電流を受け取る。電流源 32<sub>1</sub> は、制御論理 42 からの制御信号 LV\_EN によってイネーブルされるとき、比較的低いレベルの電流  $I_{s_0 f_t}$  をパワースイッチトランジスタ 30<sub>1</sub> のゲートに印加する。電流源 32<sub>1</sub> は、例えば、MOS トランジスタが、所望の電流レベルに対応するレギュレートされたバイアス電圧を受け取ることなどによって、従来のように構成される。本願で説明する他の電流源 32<sub>2</sub>、34 も同様に構成される。下記で更に詳細に説明するように、電流源 32<sub>1</sub> によって導通される電流  $I_{s_0 f_t}$  は、パワースイッチトランジスタ 30<sub>1</sub> を緩やかにオンにし、パワースイッチトランジスタ 30<sub>1</sub> をオン状態に維持するのに充分なレベルである。チャージポンプノード VCP とパワースイッチトランジスタ 30<sub>1</sub> のゲートとの間において電流源 32<sub>1</sub> と並列のスイッチ 33 は、制御論理 42 からの制御信号 FRS\_ON のアクティブルレベルによってオンにされるように制御される。例えば、スイッチ 33 は、適切な駆動能力の MOS トランジスタがそのゲートにおいて制御信号 FRS\_ON を受け取ることによって実現され得る。

30

### 【0034】

この実施形態に従ったパワースイッチトランジスタ 30<sub>2</sub> のゲートは、チャージポンプノード VCP とパワースイッチトランジスタ 30<sub>2</sub> のゲートとの間に並列に接続される制御可能な電流源 32<sub>2</sub> 及び 34 を介して、チャージポンプノード VCP から駆動される。電流源 32<sub>2</sub> は、上述の電流源 32<sub>1</sub> と同様に、制御論理 42 からの制御信号 LV\_EN によってイネーブルされるとき、低レベル電流  $I_{s_0 f_t}$  を導通させる。対照的に、電流源 34 は、制御論理 42 からの制御信号 FRS\_ON によってイネーブルされるとき、チャージポンプノード VCP からパワースイッチトランジスタ 30<sub>2</sub> のゲートにブースト電流  $I_2$  を導通させるように動作する。チャージポンプ 40 によってチャージポンプノード VCP からパワースイッチトランジスタ 30<sub>2</sub> のゲートに導通されるこのブースト電流  $I_2$  は、電流源 32<sub>2</sub> によって導通される電流  $I_{s_0 f_t}$  より著しく高い（例えば、少なくとも 10 倍）。例えば、電流  $I_{s_0 f_t}$  はおよそ 1 μA であり得、ブースト電流  $I_2$  はおよそ 50 ~ 100 μA であり得る。しかし、スイッチ 33 によって導通される電流とは対照的に、この一層高い電流  $I_2$  は、例えば、電流源 34 に印加されるレギュレートされた

40

50

バイアスレベルによって制限されるなど、制御された大きさに制限される。電流源 3 4 の効果は、それゆえ、電流源 3 2<sub>2</sub> から単独で達成し得るよりもパワースイッチトランジスタ 3 0<sub>2</sub> のターンオンを加速することであり、しかし、まずオンにされ、その一過性の突入電流を制限するとき、パワースイッチトランジスタ 3 0<sub>2</sub> によって導通される電流を、制御された方式で抑えることである。

#### 【 0 0 3 5 】

上述したように、スイッチ 3 3 によってチャージポンプノード V C P からパワースイッチトランジスタ 3 0<sub>1</sub> のゲートに印加される電流は、制御又はレギュレートされず、電流源 3 4 によってパワースイッチトランジスタ 3 0<sub>2</sub> のゲートに提供されるブースト電流 I<sub>2</sub> のままである。また、内部 V\_S R C 導体からトランジスタ 3 0<sub>2</sub> における V B U S 端子への電流を抑えることは、トランジスタ 3 0<sub>1</sub> における突入電流を制限し、電流源ではなく、トランジスタ 3 0<sub>1</sub> のゲートにおけるスイッチの一層単純な実装を可能にする。10

#### 【 0 0 3 6 】

図 4 は、或る実施形態に従った電流制限回路 3 5 の構成を図示する。この実施形態において、電流制限回路 3 5 は、従来のように構築され得るオペレーショナルトランスコンダクタンス増幅器 ( O T A ) 5 0 を含む。O T A 5 0 は、一方の入力において V\_S R C 導体の電圧 ( オフセット電圧 V<sub>o s</sub> より低い ) を、及び、他方の入力においてパワースイッチトランジスタ 3 0<sub>1</sub> 及び 3 0<sub>2</sub> 間の V I N T ノードの電圧を受け取り、それらの入力の差動電圧に対応する出力電流を生じさせる。この実施形態において、こうした差動電圧は、パワースイッチトランジスタ 3 0<sub>1</sub> のオン状態電圧降下に対応し、それゆえ、電力モジュール 2 8 から V B U S 端子へ導通されるソース電流 I<sub>S O U R C E</sub> に対応する。したがって、O T A 5 0 の出力は、電力トランジスタ 3 0<sub>1</sub> によって導通されるこうしたソース電流 I<sub>S O U R C E</sub> に対する電流 k × I<sub>S O U R C E</sub> であり、O T A 5 0 の設計に従って、乗法定数 k ( 例えば、k = 0 . 1 ) でスケーリングされる。20

#### 【 0 0 3 7 】

O T A 5 0 によって出力される電流 k × I<sub>S O U R C E</sub> は、ノード N 2 において n チャネル M O S トランジスタ 5 2 のドレン ( 及びゲート ) に印加される。トランジスタ 5 2 のソースは接地である。トランジスタ 5 2 は電流ミラーの一つのレッグを構成し、電流ミラーは、その他のレッグにおいて n チャネル M O S トランジスタ 5 4 を有する。トランジスタ 5 4 は、トランジスタ 5 2 のゲート及びドレンに接続されるゲート、接地であるソース、及び、パワースイッチトランジスタ 3 0<sub>2</sub> のゲートに接続されるドレンを有する。トランジスタ 5 2 及び 5 4 は、通常、互いに対する電流駆動 ( すなわち、W / L 比 ) で、例えば、トランジスタ 5 4 が一層大きい 1 対 4 の比で、スケーリングされる。いずれにせよ、トランジスタ 5 2 、 5 4 は、互いと同じゲート - ソース電圧を有し、それゆえ、トランジスタ 5 2 によって導通される電流はトランジスタ 5 4 においてミラーされる。30

#### 【 0 0 3 8 】

制限電流源 5 1 は、ノード N 2 及び接地間にトランジスタ 5 2 と並列に接続される従来の電流源である。制限電流源 5 1 は、レギュレートされたバイアス電圧を受け取るゲートを備える M O S トランジスタなど、電流源に関する従来のように構築され得る。この実施形態において、電流源 5 1 は、制御された電流 I<sub>l i m i t</sub> を導通させるためにバイアスされる。この電流 I<sub>l i m i t</sub> は、例えば制御論理 4 2 における構成レジスタの内容に従って、プログラム又は調整され得る限界である。電流 I<sub>l i m i t</sub> は、電流制限回路 3 5 がパワースイッチトランジスタ 3 0<sub>2</sub> に対するゲート駆動を低減する電流レベルを確立する。40

#### 【 0 0 3 9 】

また、この実施形態によれば、電流制限回路 3 5 は、プログラム可能補償電流源 5 5 を含み、プログラム可能補償電流源 5 5 は、チャージポンプノード V C P の電圧などの高電圧と、トランジスタ 5 2 のドレン及びゲートにおけるノード N 2 との間に接続される。制御信号 F R S\_O N によってイネーブルされるとき、補償電流源 5 5 は、チャージポンプノード V C P から補償電流 I<sub>2 +</sub> を導通させるためにバイアスされ、補償電流 I<sub>2 +</sub> は50

、ノードN<sub>2</sub>で電流 $k \times I_{SOURC E}$ を加えられ、トランジスタ5<sub>2</sub>及び制限電流源5<sub>1</sub>の並列の組み合わせに印加される。補償電流源5<sub>5</sub>に印加されるバイアス、及びそれゆえ補償電流I<sub>2+</sub>の大きさは、例えば制御論理4<sub>2</sub>における構成レジスタの内容に従って、プログラム又は調整され得る。制御信号FRS\_ONによってイネーブルされないとき、補償電流源5<sub>5</sub>はオフにされ、ノードN<sub>2</sub>に電流を供給しない。

#### 【0040】

動作において、電流制限回路3<sub>5</sub>のOTA5<sub>0</sub>は、パワースイッチトランジスタ3<sub>0\_1</sub>によって導通される電流 $I_{SOURC E}$ に対応する電流 $k \times I_{SOURC E}$ をノードN<sub>2</sub>に印加する。電流 $I_{SOURC E}$ は、そのトランジスタ3<sub>0\_1</sub>のソース/ドレイン経路の電圧降下によって測定されるものである。通常モード（制御信号FRS\_ONがデアサー

トされ、電流源5<sub>5</sub>がディセーブルされる）において、電流 $k \times I_{SOURC E}$ が電流源5<sub>1</sub>の電流 $I_{limit}$ を超える場合、過剰な電流は、トランジスタ5<sub>2</sub>によって導通され、パワースイッチトランジスタ3<sub>0\_2</sub>のゲートから電流を引き込むためにトランジスタ5<sub>4</sub>によってミラーされる。そのため、この通常モードにおいて、内部V\_SNKノードからV\_BUS端子に導通される電流 $I_{SOURC E}$ が、適用可能な限界を超える場合、パワースイッチトランジスタ3<sub>0\_2</sub>によって導通される電流を所望の限界までレギュレートするために、電流制限回路3<sub>5</sub>は、パワースイッチトランジスタ3<sub>0\_2</sub>のゲート電圧を低減させる。

10

#### 【0041】

上述したように、通常モード（制御信号FRS\_ONがデアサーントされる）において、電流源3<sub>2\_2</sub>は、電流 $I_{soft}$ をパワースイッチトランジスタ3<sub>0\_2</sub>のゲートに供給する。この電流 $I_{soft}$ もまた、トランジスタ3<sub>0\_2</sub>のゲートが充電された後、トランジスタ5<sub>4</sub>によって導通されるので、パワースイッチ回路3<sub>5</sub>の動作にエラーが引き起こされる。しかし、この電流 $I_{soft}$ は比較的小さい（例えば~1 μA）ので、通常モードにおけるこのエラーの量は比較的少ない。

20

#### 【0042】

しかし、ファストロールスワップの場合、電流源3<sub>4</sub>もまた、ブースト電流I<sub>2</sub>を用いてパワースイッチトランジスタ3<sub>0\_2</sub>のゲートを駆動している。パワースイッチトランジスタ3<sub>0\_2</sub>のゲートが完全に充電され、トランジスタ3<sub>0\_2</sub>がオンになった後、電流源3<sub>4</sub>からのこのブースト電流I<sub>2</sub>は、トランジスタ5<sub>4</sub>によって導通される。補償されない場合、比較的大きな大きさのブースト電流I<sub>2</sub>（例えば、50~100 μA）が、パワースイッチトランジスタ3<sub>0\_2</sub>をオフにするために必要とされる電流 $I_{SOURC E}$ の大きさを著しく増加させる。しかし、この実施形態によれば、補償電流源5<sub>5</sub>もまた、ファストロールスワップ動作の間、補償電流I<sub>2+</sub>をノードN<sub>2</sub>に印加するために制御信号FRS\_ONによってオンにされる。補償電流I<sub>2+</sub>は、トランジスタ5<sub>2</sub>及び5<sub>4</sub>の互いに対するスケーリングを考慮して、電流源3<sub>4</sub>からの電流I<sub>2</sub>に対応するように選択される。

30

それゆえ、このファストロールスワップモードにおいて、トランジスタ5<sub>2</sub>及び5<sub>4</sub>の電流ミラーは、それぞれ、補償電流I<sub>2+</sub>及びブースト電流I<sub>2</sub>によって平衡される。電流制限 $I_{limit}$ を超える $k \times I_{SOURC E}$ 及びI<sub>2+</sub>の合計が、 $I_{soft}$ 及びI<sub>2</sub>電流のスケールされた合計を或る量超えることに応答して、トランジスタ5<sub>4</sub>は、パワースイッチトランジスタ3<sub>0\_2</sub>のゲートを接地に向かってプルし、デバイスをオフにするため、電流ミラーの作用によって付加的な電流を導通する。したがって、補償電流源5<sub>5</sub>は、ファストロールスワップの間、ファストロールスワップを生じさせるために、パワースイッチトランジスタ3<sub>0\_2</sub>のゲートに印加される付加的な電流I<sub>2</sub>を補償するように動作して、電流制限回路3<sub>5</sub>がパワースイッチ3<sub>0</sub>を介してV\_BUS端子に導通されるソース電流 $I_{SOURC E}$ を適切にレギュレートすることを保証する。結果として、ファストロールスワップの間、回路3<sub>5</sub>によって強化される電流制限は効果的に増加され、これにより、様々なUSB-Cハブ及び潜在的なアクセサリが、ホストデバイス2<sub>0</sub>によってサポートされることが可能となる。

40

#### 【0043】

代替として、電流ミラーへの電流  $I_2$  の付加による結果のエラーが許容し得る場合、補償電流源 55 は、電流制限回路 35 から省かれ得る。この省略は、ファストロールスワップ動作において印加される電流  $I_2$  の規模に依存すると考えられる。

#### 【0044】

図 5 は、その電力搬送役割を電力コンシューマーであることから電力プロバイダであることに変化させる際の、USB Type C (USB-C) インターフェース 25 の動作を図示する。例えば、図 1A 及び図 1B の従来の状況に関して上述したように、外部電源が取り外される一方で、アクセサリデバイスが、バッテリ駆動デバイスの USB-C コネクタに接続されたままである場合に、このロールスワップ事象が生じ得る。それゆえ、図 5 に図示される動作はプロセス 60 で始まり、プロセス 60 において、ホストデバイス 20 は、外部電源から USB-C コネクタ 22 の VBUS ラインを通じて外部電力を受け取っている。この外部電力は、バッテリ充電器及びスイッチ 27 (図 2) を介してバッテリ 23 を充電するのに役立つ。

10

#### 【0045】

プロセス 62 において、USB-C ハブ又は他のデバイス (ホストデバイス 20 それ自体を含む) が、外部電源の取り外しなど、VBUS ライン上の電圧の損失を検出する。例えば、上記で組み込まれた USB-PD 規格に従って、電力コンシューマーのみが VBUS ラインに接続されたままであるので、ホストデバイス 20 の USB-C コネクタ 22 に接続されるハブデバイスが、VBUS ライン上の電圧が安全限界 ( $V_{safe}$ ) を下回って下がることを検出し得る。それに応答して、そのハブデバイス又は他のデバイスは、その規格に従って、USB-C バスのチャネル構成ライン CC1、CC2 を通じて「ファストロールスワップ」信号を生成する (例えば、送出する)。

20

#### 【0046】

ホストデバイス 20 の構成チャネルコントローラ 24 の制御論理 42 は、そのインターフェース 22 のチャネル構成端子 CC1、CC2 でファストロールスワップ信号を検出し、この実施形態に従ってプロセス 64a、64b、64c を実行することによって応答する。これらのプロセス 64a、64b、64c は、各特定の実装に適切なように、同時に又は論理シーケンスで効率的に実行され得る。プロセス 64a において、制御論理 42 は、チャージポンプノード VCP において付加的な電流をソースするため、チャージポンプ 40 を一層高い周波数で動作させるために FRS\_f クロック信号 (又は、適用可能な制御信号) を送出する。また、このとき、制御論理 42 は FRS\_ON 制御信号をアサートし、これは、プロセス 64b において、チャージポンプノード VCP とパワースイッチトランジスタ 30<sub>1</sub> のゲートとの間のスイッチ 33 を閉じ、ブースト電流  $I_2$  をパワースイッチトランジスタ 30<sub>2</sub> のゲートに印加するために電流源 34 をイネーブルする。スイッチ 33 及び電流源 34 を介してチャージポンプノード VCP から印加される付加的な電流は、ファストロールスワップにおいてより一層速いレートで、それぞれパワースイッチトランジスタ 30<sub>1</sub>、30<sub>2</sub> をオンにする効果を有する。このようにして、ホストデバイス 20 の内部電源 (例えば、バッテリ 23) は、最小の中斷で、USB-C コネクタ 22 に取り付けられるアクセサリデバイスに電力を急速に提供する。

30

#### 【0047】

プロセス 64c において、また、制御論理 42 による FRS\_ON 制御信号のアサートは、図 4 に関して上述したように、電流制限回路 35 において補償電流源 55 をイネーブルするよう動作する。その結果、電流制限回路 35 は、ソース電流  $I_{SOURCE}$  が、バッテリ 23 によって、コネクタ 22 の VBUS ラインを通じて電力モジュール 28 を介して外部デバイスに提供されるのを正確に監視し続け、過電流状況の事象においてパワースイッチトランジスタ 30<sub>2</sub> のゲート電圧を低減させる。

40

#### 【0048】

判定 65 において、ホストデバイス 20 それ自体、又は、コネクタ 22 に接続されるハブデバイスが、ホストデバイス 20 がその役割を電力コンシューマーから電力プロバイダに成功裏に変更したかどうかを判定する。例えば、判定 65 は、コネクタ 22 の VBUS 50

端子の電圧を安全限界 ( $V_{safe}$ ) と比較することによって成され得る。V B U S 電圧がこの所望の最小レベルに達していない限り（判定 65 が「no」の結果に戻る）、ファストロールスワップモードにおける動作は維持される（プロセス 66）。しかし、V B U S ラインの電圧が所望のレベルに達した後（判定 65 が「yes」）、ファストロールスワップ動作は終了し得、通常動作モードに入り得る。

#### 【0049】

図 3 及び図 4 を参照すると、この通常動作モードは、プロセス 68aにおいて、制御論理 42 が、F R S \_ f 信号をデアサートすること、及びライン N M L \_ f 上でクロック又は制御信号を送出することを含み、チャージポンプ 40 のスイッチング周波数を低減させ、これが、その電流出力を低減させ、それに応じてホストデバイス 20 の電力消費を低減させる。プロセス 68bにおいて、F R S \_ ON 制御信号はデアサートされ、このデアサートは、パワースイッチトランジスタ 30<sub>1</sub> のゲートにおけるスイッチ 33 を開き、パワースイッチトランジスタ 30<sub>2</sub> のゲートにおける電流源 34 をディセーブルする。電流源 32<sub>1</sub>、32<sub>2</sub> はイネーブルされたままであり、それぞれ、トランジスタ 30<sub>1</sub>、30<sub>2</sub> のゲートに、これらのデバイスをオン状態に維持するために低電流  $I_{soft}$  を提供する。それゆえ、電力モジュール 28 は、U S B - C 接続を通じて外部アクセサリデバイスを給電し続けることができる。また、この実施形態に従ったプロセス 68cにおいて、電流制限スイッチ 35 における補償電流源 55 はディセーブルされて、電流  $I_2$  がもはやパワースイッチトランジスタ 30<sub>2</sub> のゲートに印加されていないことを考慮して、電流制限監視動作の正確性を維持する。代替として、一層低い補償電流（すなわち、電流  $I_{soft}$  に相当）が望まれる場合、プロセス 68c は、この通常動作モードにおいてノード N 2 に印加される付加的な補償電流の大きさを変更し得る。10

#### 【0050】

これらの実施形態によれば、電子デバイス用のインターフェース回路要素は、（例えば、内部バッテリを充電するために）外部電力を受け取ることから、その内部電源（バッテリなど）から外部デバイスに電力を提供することへ、急速に変更し得る。この能力は、パワースイッチトランジスタでの過剰な突入電流を防ぐため制御された方式で提供され、それゆえ、相互接続されたシステムにおいてスイッチング遷移を低減させる。20

#### 【0051】

特許請求の範囲内で、説明した実施形態における改変が可能であり、その他の実施形態が可能である。30

【図1A】

【図1B】

【図1C】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 スジョン クンダプール マノアール

アメリカ合衆国 75252 テキサス州 ダラス, エイピーティー 1215, ハミルトン

アヴェニュー 3320

(72)発明者 アリエル ダリオ モクテツマ

アメリカ合衆国 75043 テキサス州 ガーランド, フォレスト ポイント ドライブ 4

308

審査官 松浦 かおり

(56)参考文献 米国特許出願公開第2006/0261788(US,A1)

米国特許出願公開第2014/0208134(US,A1)

特開2013-025345(JP,A)

(58)調査した分野(Int.Cl., DB名)

G06F 1/26 - 1/3296

H02H 9/00 - 9/08

H02J 1/00 - 1/16