(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-70561

(P2008-70561A)

(43) 公開日 平成20年3月27日(2008.3.27)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/36 (2006.01)</b>  | G09G 3/36 | 2 H093      |

| <b>G09G 3/20 (2006.01)</b>  | G09G 3/20 | 5 C006      |

| <b>G02F 1/133 (2006.01)</b> | G09G 3/20 | 5 C080      |

|                             | G09G 3/20 | 6 2 1 B     |

|                             | G09G 3/20 | 6 2 1 F     |

|                             | G09G 3/20 | 6 3 1 B     |

|                             | G09G 3/20 | 6 4 1 C     |

審査請求 未請求 請求項の数 8 O L (全 18 頁) 最終頁に続く

|           |                              |          |                                            |

|-----------|------------------------------|----------|--------------------------------------------|

| (21) 出願番号 | 特願2006-248573 (P2006-248573) | (71) 出願人 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日  | 平成18年9月13日 (2006. 9. 13)     | (74) 代理人 | 100076428<br>弁理士 大塚 康徳                     |

|           |                              | (74) 代理人 | 100112508<br>弁理士 高柳 司郎                     |

|           |                              | (74) 代理人 | 100115071<br>弁理士 大塚 康弘                     |

|           |                              | (74) 代理人 | 100116894<br>弁理士 木村 秀二                     |

|           |                              | (72) 発明者 | 大内 朗弘<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

最終頁に続く

(54) 【発明の名称】表示装置及びその制御方法

## (57) 【要約】

【課題】 メモリ構成及びその制御を煩雑化せずに液晶応答速度特性を向上することが可能な表示技術を提供する。

【解決手段】 表示装置は、フレームデータを入力する入力手段と、フレームデータを記憶するフレームメモリと、前記入力されたフレームデータと、前記記憶された該入力されたフレームデータの直前のフレームデータと、を比較して補正データを決定する決定手段と、前記補正データを前記入力されたフレームデータに付加する付加手段と、前記補正データが付加されたフレームデータを、前記フレームメモリに記憶制御する記憶制御手段と、前記記憶制御手段により記憶制御されたフレームデータを予め定められたフレームレイヤで読み出し、該フレームデータに付加された前記補正データに基づいて、該フレームデータを補正する補正手段と、補正された前記フレームデータに基づいて前記ディスプレイに画像を表示制御する表示制御手段と、を備える。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

複数のフレームデータを含む映像信号データを入力し、当該映像信号データに基づいてディスプレイに画像を表示する表示装置であって、

フレームデータを入力する入力手段と、

フレームデータを記憶するフレームメモリと、

前記入力手段で入力されたフレームデータと、前記フレームメモリに記憶された該入力されたフレームデータの直前のフレームデータと、を比較して補正データを決定する決定手段と、

決定された前記補正データを、前記入力されたフレームデータに付加する付加手段と、

前記補正データが付加された前記入力されたフレームデータを、前記フレームメモリに記憶制御する記憶制御手段と、

前記記憶制御手段により前記フレームメモリに記憶制御されたフレームデータを予め定められたフレームレイヤで読み出し、該フレームデータに付加された前記補正データに基づいて、該フレームデータを補正する補正手段と、

補正された前記フレームデータに基づいて前記ディスプレイに画像を表示制御する表示制御手段と、

を備えることを特徴とする表示装置。

**【請求項 2】**

前記決定手段は、前記入力手段によるフレームデータの入力に同期して、その直前のフレームデータを前記フレームメモリから読み出し、前記比較を行うことを特徴とする請求項 1 に記載の表示装置。

**【請求項 3】**

前記記憶制御手段は、

前記補正データが付加された前記入力されたフレームデータに含まれるラインデータを一時的に記憶する第 1 ラインメモリを備えることを特徴とする請求項 1 又は 2 に記載の表示装置。

**【請求項 4】**

前記記憶制御手段により前記フレームメモリに記憶されたフレームデータに含まれるラインデータを一時的に記憶する第 2 ラインメモリを更に備え、

前記補正手段は、前記第 2 ラインメモリを介して前記フレームメモリから前記補正データが付加されたフレームデータを読み出す

ことを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載の表示装置。

**【請求項 5】**

前記フレームメモリは、第 1 フレームメモリと第 2 フレームメモリとを備え、

前記記憶制御手段は、

前記補正データが付加された前記入力されたフレームデータを、その直前のフレームデータが、前記第 1 フレームメモリに記憶されている場合は前記第 2 フレームメモリに、前記第 2 フレームメモリに記憶されている場合は前記第 1 フレームメモリに、記憶制御することを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載の表示装置。

**【請求項 6】**

複数のフレームデータを含む映像信号データを入力し、当該映像信号データに基づいてディスプレイに画像を表示する表示装置であって、

フレームデータを入力する入力手段と、

フレームデータを記憶する第 1 フレームメモリと、

前記入力手段で入力されたフレームデータと、前記第 1 フレームメモリに記憶された該入力されたフレームデータの直前のフレームデータと、を比較して補正データを決定する決定手段と、

前記決定手段で決定された補正データを記憶する第 2 フレームメモリと、

前記入力されたフレームデータを、前記第 1 フレームメモリに記憶制御する記憶制御手

10

20

30

40

50

段と、

前記第1フレームメモリよりフレームデータを予め定められたフレームレイヤで読み出し、前記補正データに基づいて、フレームデータを補正する補正手段と、

前記補正手段で補正されたフレームデータに基づいて前記ディスプレイに画像を表示制御する表示制御手段と、

を備えることを特徴とする表示装置。

【請求項7】

前記ディスプレイは液晶パネルであることを特徴とする請求項1乃至6のいずれか1項に記載の表示装置。

【請求項8】

複数のフレームデータを含む映像信号データを入力し、当該映像信号データに基づいてディスプレイに画像を表示する、フレームデータを記憶するフレームメモリを備える表示装置の制御方法であって、

フレームデータを入力する入力工程と、

前記入力工程で入力されたフレームデータと、前記フレームメモリに記憶された該入力されたフレームデータの直前のフレームデータと、を比較して補正データを決定する決定工程と、

決定された前記補正データを、前記入力されたフレームデータに付加する付加工程と、

前記補正データが付加された前記入力されたフレームデータを、前記フレームメモリに記憶制御する記憶制御工程と、

前記記憶制御工程において前記フレームメモリに記憶制御されたフレームデータを予め定められたフレームレイヤで読み出し、該フレームデータに付加された前記補正データに基づいて、該フレームデータを補正する補正工程と、

補正された前記フレームデータに基づいて前記ディスプレイに画像を表示制御する表示制御工程と、

を備えることを特徴とする表示装置の制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は表示装置に関し、特に、入力映像信号の変化に対する液晶応答速度を向上させる液晶表示技術に関する。

【背景技術】

【0002】

近年、T V の受像機やP C の表示装置として液晶表示装置が使用されている。液晶表示装置は、薄型で省スペース、且つ省電力であるため幅広く採用されている。しかしながら、液晶表示装置は、入力される映像信号の変化から実際の表示までの液晶応答速度が長いため、動画を表示した場合に残像が発生する等の問題を有している。そこで、この液晶応答速度を改善するために、次のフレームで表示する映像信号と直前のフレームで表示した映像信号とを比較し、その比較結果に応じて入力映像信号を補正して液晶を駆動する、所謂オーバードライブ駆動が提案されている（特許文献1）。また、オーバードライブ駆動は、短期間に行うことによって液晶応答速度の改善効果がより大きく得られる。このため、例えば入力の1フレームを複数のフィールドに分割して駆動し、最初のフィールドに対してオーバードライブ駆動を行う構成が知られている（特許文献2）。

【0003】

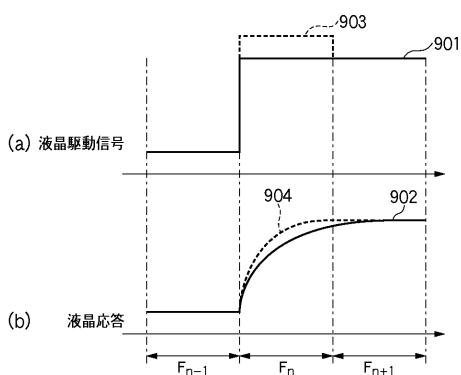

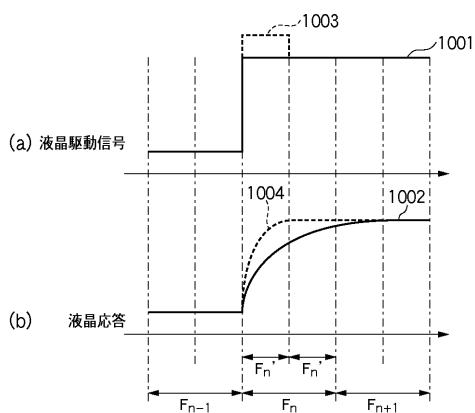

オーバードライブ駆動の原理について、図9，10を参照して簡単に説明する。図9は、入力映像信号と同一のフレームレイヤでオーバードライブ駆動を行った場合の液晶駆動信号と液晶応答特性を例示する模式図である。また、図10は、入力映像信号のフレームレイヤに対して2倍のフレームレイヤに変換し、変換後の初めのフィールドでオーバードライブ駆動を行った場合の液晶駆動信号と液晶応答特性を例示する模式図である。

【0004】

10

20

30

40

50

図9において、横軸は時間を示しており、縦軸は信号及びそれに対する応答のレベルを示している。901は、通常の液晶駆動信号の変化を示しており、902は、液晶駆動信号901に対する液晶応答を示している。903は、オーバードライブ駆動された液晶駆動信号の変化を示しており、904は、液晶駆動信号903に対する液晶応答を示している。液晶応答902, 904を比較して分かるように、オーバードライブ駆動された液晶駆動信号に対する液晶応答は、液晶応答速度が向上している。

#### 【0005】

図10においても、横軸は時間を示しており、縦軸は信号及びそれに対する応答のレベルを示している。1001は通常の液晶駆動信号の変化、1002は液晶駆動信号1001に対する液晶応答、1003はオーバードライブ駆動された液晶駆動信号の変化、1004は液晶駆動信号903に対する液晶応答をそれぞれ示している。液晶応答904, 1004を比較して分かるように、フレームレイトが2倍に変換されている図10においては、液晶応答速度がさらに向上している。10

#### 【0006】

このように1フレームを複数のフィールドに分割し、最初のフィールドに対してオーバードライブ駆動を行う構成は、反射型液晶表示パネル(LCOS: Liquid Crystal On Silicon)の駆動方法と親和性がある。反射型液晶表示パネルは、入力信号のフレームレイトを2倍のフレームレイトに変換し、該倍速のフレーム信号に対して倍速フレーム毎に極性反転を行うためである。

#### 【0007】

ところで入力信号を2倍のフレームレイトに変換(倍速変換)するためには1フレーム分の映像信号をフレームメモリに格納し、2倍速で読み出す必要がある。また、液晶応答速度を改善するためのオーバードライブ駆動を行うためには、現フレームの映像信号と1フレーム前の映像信号とを比較するために1フレーム前の映像信号をフレームメモリに格納する必要がある。つまり、それぞれの処理ブロックでフレームメモリが必要となり、各ブロックでフレームメモリを個別に備えることは、フレームメモリ及びその制御手段の規模が大きく制御が煩雑なものとなってしまう。20

#### 【0008】

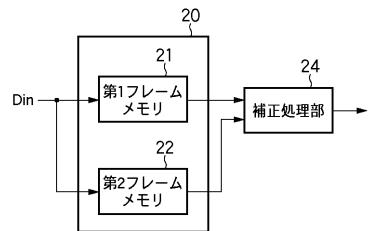

これに対し、倍速変換用のフレームメモリとオーバードライブ駆動用のフレームメモリを共通化した液晶表示装置が提案されている(特許文献3)。以下、図7を参照してこのような構成の従来技術を説明する。図7は、従来の液晶表示装置の倍速変換及びオーバードライブ駆動に関わる処理ブロックである。30

#### 【0009】

入力映像信号データDinは、フレームメモリブロック20を構成する第1フレームメモリ21と第2フレームメモリ22にそれぞれ供給される。フレームメモリ21及び22は、それぞれ独立して書き込みと読み出しの制御が可能な構成となっている。フレームメモリ21及び22の出力は、補正処理部24へ共通に接続されている。補正処理部24は、フレームメモリ21及び22から読み出された映像信号データを基に動画補正処理された表示データを生成し出力する。

#### 【0010】

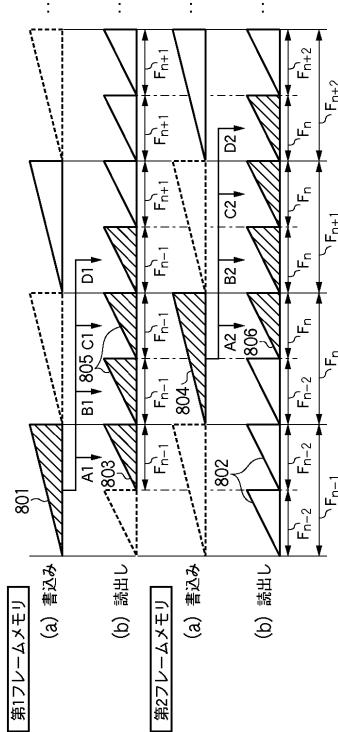

次に、従来例における2つのフレームメモリ21及び22の書き込み、読み出し動作について、図8を参照して詳細に説明する。図8は、2つのフレームメモリ21, 22の書き込み、読み出しに係る動作のタイミングを示す模式図である。

#### 【0011】

フレームFn-1の入力時では第1フレームメモリ21の書き込み制御がアクティブとなり、入力映像信号データDinは、第1フレームメモリ21に図8(a)で示すように書き込まれる(801)。一方、第2フレームメモリ22は書き込み動作を行わず、図8(d)に示すように、前フレームFn-2で格納された映像信号データの読み出しを2倍のレイトで行う(802)。

#### 【0012】

10

20

30

40

50

第1フレームメモリ21では、映像信号データの書き込みがフレームFn-1期間の半ばに達した時点で、図8(b)に示すように読み出しを開始し(803)、フレームFn-1の映像データが2倍のレイトで読み出される。このフレームFn-1の映像信号データ読み出しは、第1フレームメモリ21に格納された映像信号データがフレームFn+1に更新されるまで、図8(b)にA1、B1、C1、D1で表すように4回繰り返される。

#### 【0013】

同様に、次のフレームFnの入力時では第2フレームメモリ21の書き込み制御がアクティブとなり、入力映像信号データDinは、第2フレームメモリ22に図8(c)で示すように書き込まれる(804)。一方、第1フレームメモリ21は書き込み動作を行わず、図8(b)に示すように、前フレームFn-1で格納された映像信号データの読み出しを2倍のレイトで行う(805)。

10

#### 【0014】

第2フレームメモリ22では、映像信号データの書き込みが入力フレームFn期間の半ばに達した時点で、図8(d)に示すように読み出しを開始し(806)、フレームFnの映像信号データが2倍のレイトで読み出される。このフレームFnの映像信号データ読み出しは、第2フレームメモリ22に格納された映像信号データがフレームFn+2に更新されるまで、図8(d)にA2、B2、C2、D2で表すように4回繰り返される。

20

#### 【0015】

ここで、図8(d)に示す第2フレームメモリ22からのフレームFnの映像信号データ読み出し期間に着目する。4回の読み出しサイクルのうちA2、B2で示す期間は、図8(b)に示すように、第1フレームメモリではフレームFn-1の映像信号データのC1、D1で示す期間の読み出しが平行して行われている。

20

#### 【0016】

図7の補正処理部24は、第2フレームメモリ22からA2、B2期間に読み出されるフレームFnの映像信号データを現フレームデータとする。また、第1フレームメモリ21からC1、D1期間に読み出されるフレームFn-1の映像信号データを前フレームデータとする。そして、これらの映像信号データを比較する。比較の結果、信号レベルに差分を生じた映像信号データの組み合わせに基づいて、変化を強調する補正処理を実施した映像信号データを生成して出力する。

30

#### 【0017】

第2フレームメモリ22におけるFnの読み出し期間C2、D2は、フレームFn+1に対する前フレームデータとして補正処理部24で利用される。このときの現フレームデータは、第1フレームメモリ21における4回の読み出しサイクルのうち、前半2回のフレームFn+1に対応する読み出し映像信号データが利用される。

30

#### 【0018】

以上の動作を繰り返すことによって、表示データのフレームレイト変換及び、オーバードライブ駆動を同時に実現している。

#### 【特許文献1】特許第3305240号公報

#### 【特許文献2】特開2001-343956号公報

#### 【特許文献3】特開2005-309326号公報

40

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0019】

しかしながら、上記特許文献3記載の構成においては、データ比較のためにフレームメモリから読み出されて来る現フレーム及び前フレームのデータバスが交互に入れ替わるため、補正処理部の制御が煩雑になる。更に、現フレームと前フレームの映像信号データを平行して読み出すため、2つの独立したフレームメモリが必要である。

#### 【0020】

本発明は上記問題に鑑みなされたものであり、メモリ構成及びその制御を煩雑化せずに液晶応答速度特性を向上することが可能な表示技術を提供することを目的とする。

50

## 【課題を解決するための手段】

## 【0021】

上記目的を達成するため、本発明による表示装置は以下の構成を備える。即ち、複数のフレームデータを含む映像信号データを入力し、当該映像信号データに基づいてディスプレイに画像を表示する表示装置であって、

フレームデータを入力する入力手段と、

フレームデータを記憶するフレームメモリと、

前記入力手段で入力されたフレームデータと、前記フレームメモリに記憶された該入力されたフレームデータの直前のフレームデータと、を比較して補正データを決定する決定手段と、

決定された前記補正データを、前記入力されたフレームデータに付加する付加手段と、

前記補正データが付加された前記入力されたフレームデータを、前記フレームメモリに記憶制御する記憶制御手段と、

前記記憶制御手段により前記フレームメモリに記憶制御されたフレームデータを予め定められたフレームレイヤで読み出し、該フレームデータに付加された前記補正データに基づいて、該フレームデータを補正する補正手段と、

補正された前記フレームデータに基づいて前記ディスプレイに画像を表示制御する表示制御手段と、

を備える。

## 【0022】

また、本発明による表示装置の制御方法は以下の構成を備える。即ち、

複数のフレームデータを含む映像信号データを入力し、当該映像信号データに基づいてディスプレイに画像を表示する、フレームデータを記憶するフレームメモリを備える表示装置の制御方法であって、

フレームデータを入力する入力工程と、

前記入力工程で入力されたフレームデータと、前記フレームメモリに記憶された該入力されたフレームデータの直前のフレームデータと、を比較して補正データを決定する決定工程と、

決定された前記補正データを、前記入力されたフレームデータに付加する付加工程と、

前記補正データが付加された前記入力されたフレームデータを、前記フレームメモリに記憶制御する記憶制御工程と、

前記記憶制御工程において前記フレームメモリに記憶制御されたフレームデータを予め定められたフレームレイヤで読み出し、該フレームデータに付加された前記補正データに基づいて、該フレームデータを補正する補正工程と、

補正された前記フレームデータに基づいて前記ディスプレイに画像を表示制御する表示制御工程と、

を備える。

## 【発明の効果】

## 【0023】

本発明によれば、メモリ構成及びその制御を煩雑化せずに液晶応答速度特性を向上することが可能な表示技術を提供することができる。

## 【発明を実施するための最良の形態】

## 【0024】

以下、添付図面を参照して本発明に係る実施の形態を詳細に説明する。ただし、この実施の形態に記載されている構成要素はあくまでも例示であり、本発明の範囲をそれらのみに限定する趣旨のものではない。

## 【0025】

<<第1の実施形態>>

(液晶表示装置の構成)

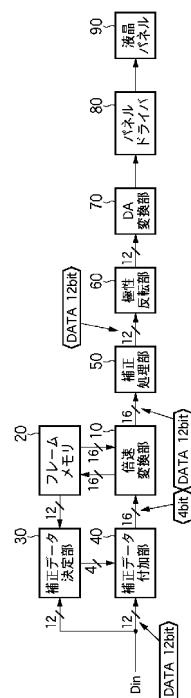

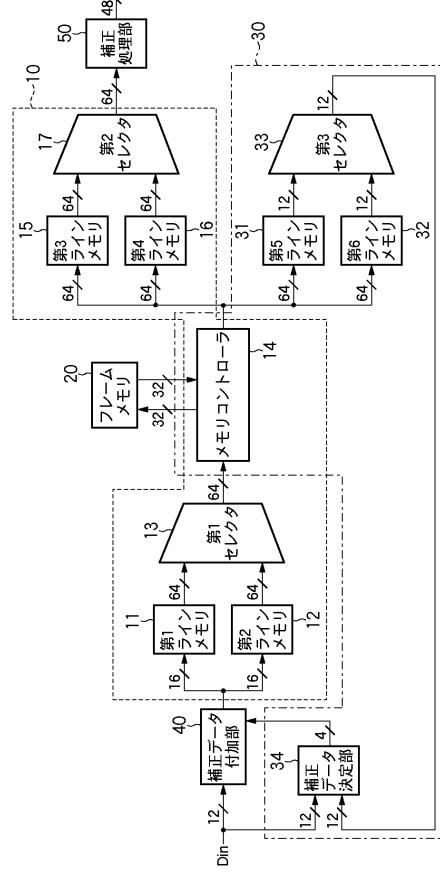

図1は、本実施形態に係る液晶表示装置の概略ブロック図である。10は倍速変換部、

10

20

30

40

50

20はフレームメモリ、30は補正データ決定部、40は補正データ付加部、50は補正処理部、60は極性反転部、70はDA変換部、80はパネルドライバ、90は液晶パネルである。

#### 【0026】

本構成において、倍速変換部10は、補正データ付加部40から入力される映像信号データをフレームメモリ20へ書き込む。更に、倍速変換部10は、フレームメモリ20に格納されている映像信号データを入力映像信号データのフレームレイトに対して倍のレイトで読み出すことによって倍速変換された映像信号データを生成し、補正処理部50へ出力する。

#### 【0027】

補正データ決定部30は、フレームメモリ20に格納されている前フレームの映像信号データを入力のフレームレイトと同一レイトで読み出し、現フレームの映像信号データDinとの信号レベルの比較を行う。そして、その比較結果に基づいて、例えば4ビットの補正データとして補正データ付加部40に出力する。補正データ付加部40は、例えば12ビットで入力される現フレームの映像信号データDinに対して、MSBあるいはLSBに前記4ビットの補正データを付加した16ビットのデータとして倍速変換部10へ出力する。なお、補正データには、オーバードライブ駆動のレベルを示す情報などが含まれる。

#### 【0028】

補正処理部50は、倍速変換されて入力される16ビットのデータから、MSBあるいはLSB4ビットの補正データを参照し、応答速度を更新した12ビットの映像信号データを生成する。ここで、映像信号データの補正是、倍速フレームレイトの映像信号に対して、最初の倍速フレームあるいは後の倍速フレームのいずれか一方のみで行うことが出来る。或いはまた、映像信号データの補正を両方の倍速フレームで行うことも、あるいは行わないことも可能である。

#### 【0029】

極性反転部60は、液晶パネル90に供給される電圧の極性がコモン電圧に対して、倍速フレームの一方がプラス、もう一方がマイナスとなるような映像信号データとしてDA変換部70へ出力する。DA変換部70は、極性反転処理された映像信号データをアナログ信号に変換する。そして、このアナログ信号により、パネルドライバ80を介して液晶パネル90が駆動される。ここで、パネルドライバ80はDA変換部70に含まれても良い。また、液晶パネル90の入力がデジタル入力であった場合、DA変換部70及びパネルドライバ80は不要であることは言うまでもない。

#### 【0030】

(書き込み、読み出しの動作)

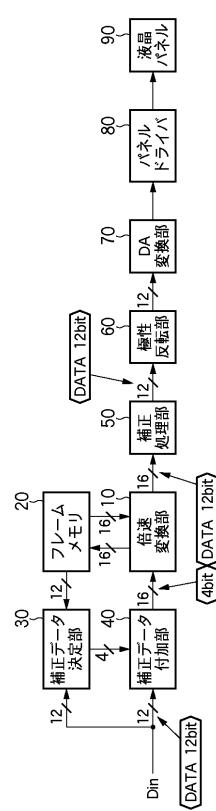

次に、本実施形態におけるフレームメモリ20の書き込み、読み出し動作について図2及び図3を参照して詳細に説明する。図2は、フレーム期間におけるフレームメモリ20の書き込み、読み出し動作を説明するタイミング図である。なお、本実施形態でフレームメモリ20は、図示しない第1フレームメモリ20aと第2フレームメモリ20bとで構成される。

#### 【0031】

DinとしてフレームFnが入力されているときは、第1フレームメモリ20aの書き込み制御がアクティブとなり、映像信号データは、第1フレームメモリ20aに図2(a)で示すように書き込まれる(201)。一方、このとき第2フレームメモリ20bは書き込み動作を行わない。第2フレームメモリ20bは、前フレームFn-1で格納された映像信号データの読み出しを、図2(e)のように入力映像信号Dinと同一レイトで行う(等倍読み出し、202)と共に、図2(f)のように2倍のレイトで行う(倍速読み出し、203)。ここで、図2(e)に示すように入力映像信号Dinと同一レイトで読み出された映像信号データ(202、204)は、前フレームデータとして補正データ決定部30において現フレームデータである入力映像信号データDinとの比較に利用される

10

20

30

40

50

。補正データ決定部30は、現フレームデータと前フレームデータとの間で信号レベルに差分を生じた映像信号データの組み合わせに対して、補正処理部50で補正処理を行うための補正データを決定する。また、第1フレームメモリ20aに書き込まれる映像信号データは、前記補正データ決定部30で決定された補正データがMSBあるいはLSBに付加されたデータである。

#### 【0032】

同様に、次のフレームFn+1では第2フレームメモリ20bの書き込み制御がアクティブとなり、映像信号データは、第2フレームメモリ20bに図2(d)で示すように書き込まれる(205)。一方、第1フレームメモリ20aは書き込み動作を行わず、前フレームFnで格納された映像信号データの読み出しを図2(b)に示すように入力映像信号Dinと同一レイイトで行う(206)と共に図2(c)に示すように2倍のレイイトで行う(207)。

10

#### 【0033】

ここで、図2(b)に示すように入力映像信号Dinと同一レイイトで読み出された映像信号データ(206)は、前フレームデータとして補正データ決定部30において現フレームデータである入力映像信号データDinとの比較に利用される。補正データ決定部30は、現フレームデータと前フレームデータとの間で信号レベルに差分を生じた映像信号データの組み合わせに対して、補正処理部50で補正処理を行うための補正データを決定する。また、第2フレームメモリ20bに書き込まれる映像信号データは、前記補正データ決定部30で決定された補正データをMSBあるいはLSBに付加されたデータである。

20

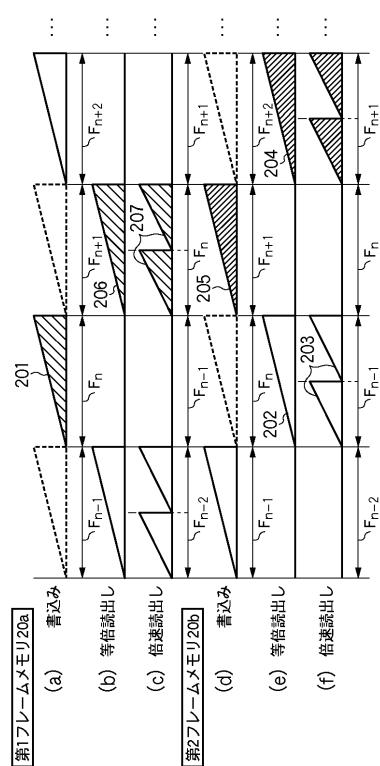

#### 【0034】

映像信号データの書き込み、読み出しの更なる詳細について、図3を参照して説明する。図3は、フレームFnのライン期間におけるフレームメモリ20の書き込み、読み出し動作を説明するタイミング図である。フレームFnでは第1フレームメモリ20aは書き込み制御がアクティブとなっており、映像信号データは、第1フレームメモリ20aに図3(a)で示すようにライン毎に書き込まれる(301)。一方、第2フレームメモリ20bは書き込み動作を行わず、図3(g)で示すように、ラインLnの1/3期間に、前フレームFn-1で格納された映像信号のラインLn+1のデータを読み出す(302)。また、図3(h)で示すように、ラインLnの2/3期間に、前フレームFn-1で格納された映像信号のラインLm及びLn+1のデータを読み出す(303)。

30

#### 【0035】

ここで、第2フレームメモリから読み出される映像信号データは、不図示のラインメモリにそれぞれ一旦格納される。そして、図3(g)で読み出された映像信号データは、現フレームデータである入力映像信号DinのラインLn+1に同期して、図3(d)の304で示すように前フレームFn-1におけるラインLn+1の映像信号データとして再生される。再生されたラインLn+1の映像信号データは、補正データ決定部30において現フレームのラインLn+1における入力映像信号データDinとの比較に利用される。また、図3(h)で読み出された映像信号データ(303)は、現フレームと1/2周期ずれたタイミングで図3(e)の305で示すように前フレームFn-1におけるラインLm及びラインLn+1の映像信号データとして再生される。

40

#### 【0036】

なお、図3(e)で示すように読み出される前フレームFn-1の映像信号データは、現フレームFnの半分の周期で繰り返し読み出されることによって倍速映像信号データとなる。次のフレームFn+1では、第2フレームメモリ20bの書き込み制御がアクティブ、第1フレームメモリ20aの読み出し制御がアクティブとなり、上記と同様の書き込み、読み出し制御が行われる。図1の補正処理部50は、第1フレームメモリ20aあるいは第2フレームメモリ20bから倍速で読み出されるデータのうちMSBあるいはLSBに付加される補正データを参照して応答速度を改善するための補正処理を行う。以上の動作を繰り返すことによって、入力映像信号データのフレームレイイト変換及び、応答速度補正

50

処理を同時に実現している。

【0037】

本実施形態に係る構成拠れば、倍速変換に使用するフレームメモリとオーバードライブ駆動に使用するフレームメモリとを共通にすることが可能である。また、オーバードライブ駆動のための映像信号データの比較を、入力映像信号のフレームレイトに同期して行うことが可能である。従って、メモリ構成及びその制御を煩雑化せずに液晶応答速度特性の向上が可能な表示技術を提供することができる。

【0038】

また、倍速変換後のいずれのフレームにおいてもオーバードライブ駆動のための補正を行うことが可能である。従って、液晶応答速度特性の向上のための補正処理を適正に行うことことが出来る表示技術を提供することができる。

10

【0039】

なお、本実施形態においては、オーバードライブ駆動を行うために倍速でフレームを読み出す構成について例示的に説明したが、読み出し速度は倍速に限らず、用途や目的に応じて適切なレイトで読み出しを行うことができる。

【0040】

<<第2の実施形態>>

第2の実施形態に係る液晶表示装置の基本構成は、図1に示す第1の実施形態と同じである。図4は、倍速変換部10、フレームメモリ20、補正データ決定部30、補正データ付加部40、及び補正処理部50のより詳細なブロック図である。

20

【0041】

倍速変換部10は、第1ラインメモリ11、第2ラインメモリ12、第1セレクタ13、メモリコントローラ14、第3ラインメモリ15、第4ラインメモリ16、及び第2セレクタ17で構成される。また、補正データ決定部30は、メモリコントローラ14、第5ラインメモリ31、第6ラインメモリ32、第3セレクタ33、及び補正データ決定部34で構成される。なお、フレームメモリ20は、少なくとも2フレームデータを格納可能なメモリ容量を備える1個のフレームメモリである。

【0042】

本構成において、補正データ付加部40からの映像信号データは、ライン毎に交互に第1ラインメモリ11及び第2ラインメモリ12に格納される。第1セレクタ13は、第1ラインメモリ11へ映像信号データが書き込まれるラインにおいては第2ラインメモリ12から映像信号データを読み出す。一方、第2ラインメモリ12へ映像信号データが書き込まれるラインにおいては第1ラインメモリ11から映像信号データを読み出すように制御される。第1セレクタ13からの出力は、メモリコントローラ14を介してフレームメモリ20へフレームデータとして格納される。

30

【0043】

ここで、第1ラインメモリ11及び第2ラインメモリ12からの読み出しは、連続する4画素分のデータを同時に読み出すように制御される。映像信号データが1相で入力される場合、例えば、ラインメモリ11及び12をそれぞれ4つのラインメモリで構成することができる。そして、4つのラインメモリに対して同一アドレスに画素順に映像信号データを格納し、読み出しは4つのラインメモリから同時に行うことで、連続する4画素分のデータを同時に読み出すことが出来る。映像信号が2相で入力される場合には、例えば、第1ラインメモリ11及び第2ラインメモリ12をそれぞれ2つのデュアルポートメモリで構成することができる。そして、入力映像信号と同一のクロックレイトで2つのデュアルポートメモリに対して同一アドレスに画素順に映像信号データを格納し、読み出しは倍のクロックレイトで2つのデュアルポートメモリから同時に行うように制御することで実現出来る。

40

【0044】

また、メモリコントローラ14は、4相で入力される映像信号データを2相づつ倍速でフレームメモリ20へ書き込み、倍速で2相づつ読み出して4相に展開して出力するよう

50

に制御する。

【0045】

フレームメモリ20に格納された映像信号データは、メモリコントローラ14を介して、ライン毎に交互に倍速変換部10を構成する第3ラインメモリ15及び第4ラインメモリ16に格納される。第2セレクタ17は、フレームメモリ20から読み出した映像信号データが第3ラインメモリ15へ書き込まれるラインにおいては、第4ラインメモリ16に格納されている映像信号データを読み出すように制御される。一方、第4ラインメモリ16書き込まれるラインにおいては第3ラインメモリ15から映像信号データを読み出すように制御される。第3ラインメモリ15及び第4ラインメモリ16からの読み出しは、10入力フレームレイトに対して倍のフレームレイトとなるクロックレイトで読み出される。

【0046】

ここで、第3ラインメモリ15及び第4ラインメモリ16から読み出される映像信号データは、4画素分並列の4相データとしている。従って、入力映像信号Dinが1相の場合、フレームメモリ20への書き込み／読み出しクロックは入力映像信号と同一レイトであり、入力映像信号のクロックレイトの実質4倍となっている。また、入力映像信号Dinが2相の場合、フレームメモリ20への書き込み／読み出しクロックは入力映像信号の倍のレイトであり、入力映像信号のクロックレイトの実質2倍となっている。

【0047】

従って、入力フレームレイトに対して倍のフレームレイトで読み出しを行うために、例えば、第3ラインメモリ15及び第4ラインメモリ16をそれぞれデュアルポートメモリで構成することができる。そして、入力映像信号Dinが1相の場合には入力映像信号のクロックレイトの1/2のクロックレイトで読み出し、2相の場合には入力映像信号のクロックレイトと同一クロックレイトで読み出すことで、必要なフレームレイトで読み出すことができる。

【0048】

フレームメモリ20に格納された映像信号データは、メモリコントローラ14を介して、ライン交互に補正データ決定部30を構成する第5ラインメモリ31及び第6ラインメモリ32に格納される。第3セレクタ33は、フレームメモリ20から読み出した映像信号データが第5ラインメモリ31へ書き込まれるラインにおいては、第6ラインメモリ32に格納されている映像信号データを読み出すように制御される。一方、第6ラインメモリ32書き込まれるラインにおいては第5ラインメモリ31から映像信号データを読み出すように制御される。ここで、第5ラインメモリ31及び第6ラインメモリ32からの読み出しは、フレームメモリ20から4相で読み出されてくる映像信号データを入力映像信号データと同一タイミングで1相のデータとなるように制御される。これは、例えば、第5ラインメモリ31及び第6ラインメモリ32をそれぞれ4つのデュアルポートメモリで構成し、4つのデュアルポートメモリから順次に入力映像信号データと同一のクロックレイトで読み出すことで実現することが出来る。なお、入力映像信号データDinが2相の場合には、例えば、次のようにして実現することができる。即ち、第5ラインメモリ31及び第6ラインメモリ32をそれぞれ2つのデュアルポートメモリで構成し、2つのデュアルポートメモリから順次に入力映像信号データと同一のクロックレイトで読み出すことで実現することが出来る。

【0049】

第3セレクタ33からの映像信号データは、前フレームデータとして補正データ決定部34へ入力され、現フレームデータDinとの間で信号レベル比較を行い、比較結果を例えば4ビットの補正データとして出力する。補正データ付加部40は、例えば12ビットで入力される現フレームの映像信号データDinに対して、MSBあるいはLSBに前記4ビットの補正データを付加した16ビットのデータとして倍速変換部10へ出力する。

【0050】

補正処理部50は、入力される4相16ビットのデータから、MSBあるいはLSB4ビットの補正データを参照し、応答速度を補正した12ビットの映像信号データを生成す

10

20

30

40

50

る。ここで、映像信号データの補正は、倍速フレームレイトの映像信号に対して、最初の倍速フレームあるいは後の倍速フレームのいずれか一方のみで行うことが出来る。あるいはまた、両方の倍速フレームで映像信号データの補正を行うことも、あるいは行わないことも可能である。

#### 【0051】

なお、フレームメモリ20は、DDR-SDRAMとしてすることで、フレームメモリ20への書き込み、及び読み出しを2相づつ倍速で行い、入力映像信号のクロックレイトの実質4倍で行うように制御することが出来る。ただし、DDR-SDRAMは、Double Data Rate-Synchronous DRAMの略称である。また、フレームメモリ20をSDR-SDRAMとした場合、バス幅を倍にすることでフレームメモリ20への書き込み、及び読み出しを、入力映像信号のクロックレイトの実質4倍で行うように制御することが出来る。ただし、SDR-SDRAMは、Single Data Rate-Synchronous DRAMの略称である。これにより入力フレーム期間の1/4期間で入力映像信号データをフレームメモリに書き込み、2/4期間で倍速フレームデータを生成するための読み出しを行い、残りの1/4期間で応答速度補正データを決定するための参照データを読み出す制御を行っている。また、フレームメモリ20は、最低2フレーム分の容量を備え、書き込むフレームのメモリ空間と読み出すフレームのメモリ空間とを分けることにより1個のフレームメモリで倍速変換とオーバースキヤン駆動を実現可能としている。

#### 【0052】

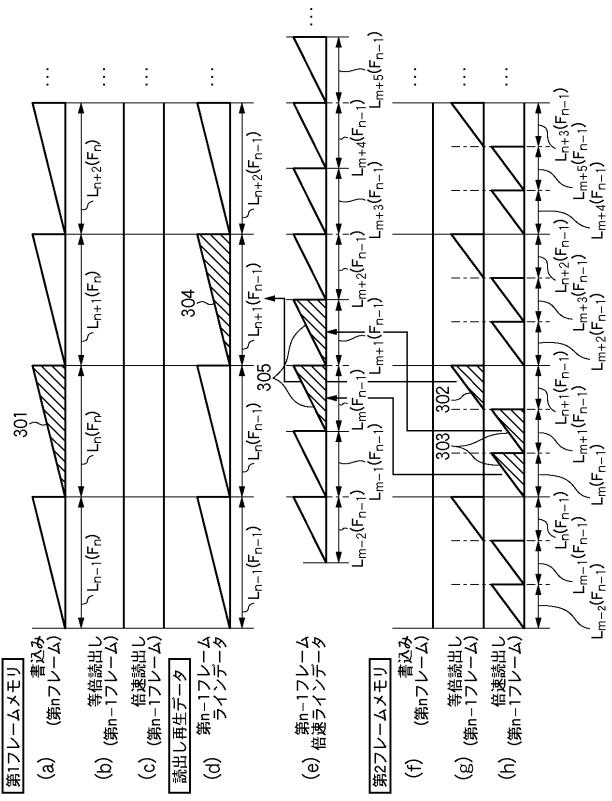

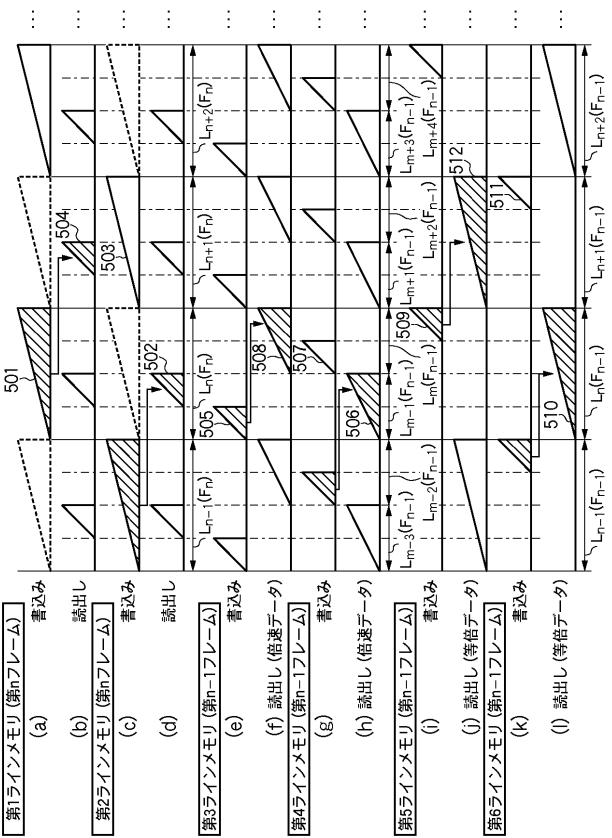

次に、各ラインメモリの動作について図5を参照して説明する。図5は、フレームFnのライン期間におけるラインメモリ11、12、15、16、31、32におけるそれぞれの書き込み、読み出し動作を説明するタイミング図である。

#### 【0053】

フレームFnのラインLn期間では、第1ラインメモリ11の書き込み制御がアクティブとなり、映像信号データは、第1ラインメモリ11に図5(a)で示すように書き込まれる(501)。一方、第2ラインメモリ12は書き込み動作を行わず、図5(d)で示すように、ラインLnの1/4期間に前ラインLn-1期間に格納された映像信号データを読み出す(502)。

#### 【0054】

フレームFnの次のラインLn+1期間では、第2ラインメモリ12の書き込み制御がアクティブとなり、映像信号データは、第2ラインメモリ12に図5(c)で示すように書き込まれる(503)。一方、第1ラインメモリ11は書き込み動作を行わず、図5(b)で示すように、ラインLn+1の1/4期間に前ラインLn期間に格納された映像信号データを読み出す(504)。なお、第1ラインメモリ11及び第2ラインメモリ12へ書き込まれる映像信号データは、補正データが付加されたデータであり、読み出されるデータはフレームメモリ20へ格納される。

#### 【0055】

以上の動作をライン交互に繰り返し、第1セレクタ13で第1ラインメモリ11及び第2ラインメモリ12からの読み出しデータを交互に選択することで入力映像データDinをフレームメモリ20へ書き込む。

#### 【0056】

また、フレームFnのラインLn期間において、最初の1/4期間は、第3ラインメモリ15の書き込み制御がアクティブとなる。そして、図5(e)のようにフレームメモリ20から読み出されるフレームFn-1のラインLmに対応する映像信号データが書き込まれる(505)。一方、第4ラインメモリ16は書き込み動作を行わず、図5(h)で示すように、2番目の1/4期間にかけてラインLn-1期間に格納されたフレームFn-1のラインLm-1に対応する映像信号データを入力フレームレイトの倍のフレームレイトとなるよう読み出す(506)。

#### 【0057】

10

20

30

40

50

フレーム Fn のライン Ln 期間において、3 番目の 1 / 4 期間は、第 4 ラインメモリ 16 の書き込み制御がアクティブとなる。そして、図 5 (g) で示すようにフレームメモリ 20 から読み出されるフレーム Fn-1 のライン Lm+1 に対応する映像信号データが書き込まれる (507)。一方、第 3 ラインメモリ 15 は書き込み動作を行わず、図 5 (f) で示すように、4 番目の 1 / 4 期間にかけてライン Ln 期間に格納されたフレーム Fn-1 のライン Lm に対応する映像信号データを入力フレームレイトの倍のフレームレイトとなるように読み出す (508)。

#### 【0058】

以上の動作をライン交互に繰り返し、第 2 セレクタ 17 で第 3 ラインメモリ 15 及び第 4 ラインメモリ 16 からの読み出しデータを交互に選択することで、連続したフレームデータを生成する。また、この動作を入力フレーム期間に 2 回行うことで入力フレームレイトに対して倍のフレームレイトの映像信号データを生成する。こうして生成された映像信号データは、補正処理部 50 で応答速度補正処理される。10

#### 【0059】

また、フレーム Fn のライン Ln 期間において、4 番目の 1 / 4 期間は、第 5 ラインメモリ 31 の書き込み制御がアクティブとなる。そして、図 5 (i) で示すようにフレームメモリ 20 から読み出されるフレーム Fn-1 のライン Ln+1 に対応する映像信号データが書き込まれる (509)。一方、第 6 ラインメモリ 32 は書き込み動作を行わず、図 5 (l) で示すように、ライン Ln-1 期間に格納されたフレーム Fn-1 のライン Ln に対応する映像信号データを入力フレームレイトと同一のフレームレイトとなるように読み出す (510)。20

#### 【0060】

フレーム Fn の次のライン Ln+1 期間では、第 6 ラインメモリ 32 の書き込み制御がアクティブとなる。そして、図 5 (k) で示すようにフレームメモリ 20 から読み出されるフレーム Fn-1 のライン Ln+2 に対応する映像信号データが書き込まれる (511)。一方、第 5 ラインメモリ 31 は書き込み動作を行わず、図 5 (j) で示すように、ライン Ln 期間に格納されたフレーム Fn-1 のライン Ln+1 に対応する映像信号データを入力フレームレイトと同一のフレームレイトとなるように読み出す (512)。30

#### 【0061】

以上の動作をライン交互に繰り返し、第 3 セレクタ 33 で第 5 ラインメモリ 31 及び第 6 ラインメモリ 32 からの読み出しデータを交互に選択することで、入力フレームレイトに同期する連続したフレームデータを生成する。こうして生成された映像信号データは、補正データ決定部 34 において入力映像信号データ D\_in との間で信号レベル比較が行われ、比較結果を例えば 4 ビットの補正データとして出力する。30

#### 【0062】

上記のように、本実施形態に係る構成に拠れば、1 つのフレームメモリを使用して倍速変換及び液晶応答速度特性の向上のための補正処理を適正に行なうことが可能な表示技術を提供することができる。

#### 【0063】

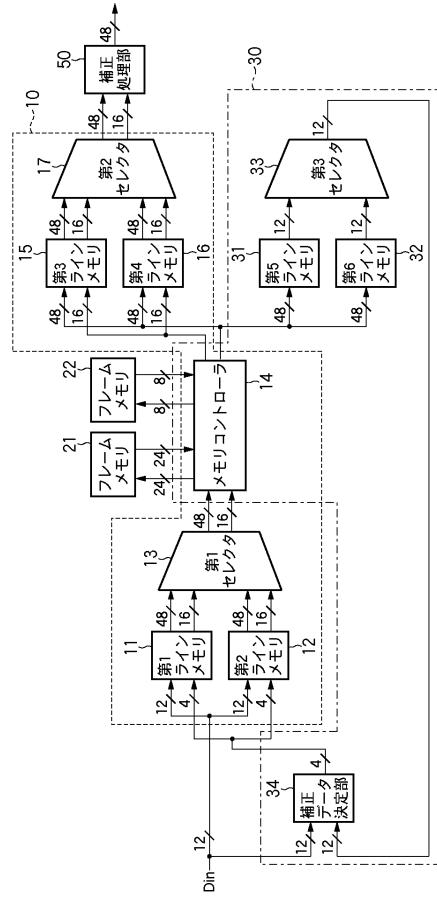

<< 第 3 の実施形態 >>

本実施形態では、映像信号データを格納するフレームメモリと補正データを格納するフレームメモリとが別個に設けられた構成について説明する。40

#### 【0064】

図 6 は、第 3 の実施形態に係る液晶表示装置の概略ブロック図であり、図 4 と同一構成要素に関しては同一符号を付している。図 6 において、21 は少なくとも 2 フレーム分の映像信号データを格納可能なメモリ容量を備える第 1 フレームメモリ、22 は 2 フレーム分の補正データを格納可能なメモリ容量を備える第 2 フレームメモリである。

#### 【0065】

本構成において、映像信号データ及び該映像信号データに対応する補正データは、ライン交互に第 1 ラインメモリ 11 及び第 2 ラインメモリ 12 に格納される。第 1 セレクタ 1

10

20

30

40

50

3は、第1ラインメモリ11へ映像信号データ及び補正データが書き込まれるラインにおいては第2ラインメモリ12から映像信号データ及び補正データを読み出す。第2ラインメモリ12へ映像信号データ及び補正データが書き込まれるラインにおいては第1ラインメモリ11から映像信号データ及び補正データを読み出すように制御される。映像信号データ及び補正データは、メモリコントローラ14を介してそれぞれ第1フレームメモリ21及び第2フレームメモリ22へフレームデータとして格納される。

#### 【0066】

ここで、第1ラインメモリ11及び第2ラインメモリ12からの読み出しは、連続する4画素に対応する映像信号データ及び補正データを同時に読み出すように制御される。映像信号データが1相で入力される場合は、例えば、ラインメモリ11と12をそれぞれ4つのラインメモリで構成し、4つのラインメモリに対して同一アドレスに画素順に映像信号データ及び補正データを格納し、読み出しは4つのラインメモリから同時に行う。映像信号が2相で入力される場合は、例えば、次のように制御する。即ち、ラインメモリ11、12をそれぞれ2つのデュアルポートメモリで構成する。そして、入力映像信号と同一のクロックレイトで2つのデュアルポートメモリに対して同一アドレスに画素順次に映像信号データ及び補正データを格納し、読み出しは倍のクロックレイトで2つのデュアルポートメモリから同時に行うように制御する。

10

#### 【0067】

また、メモリコントローラ14は、4相で入力される映像信号データ及び補正データを2相づつ倍速でそれぞれ第1フレームメモリ21及び第2フレームメモリ22へ書き込み、倍速で2相づつ読み出して4相に展開して出力するように制御する。

20

#### 【0068】

第1フレームメモリ21及び第2フレームメモリ22に格納された映像信号データ及び補正データは、メモリコントローラ14を介して、ライン交互に倍速変換部10を構成する第3ラインメモリ15及び第4ラインメモリ16に格納される。第2セレクタ17は、第1フレームメモリ21及び第2フレームメモリから読み出した映像信号データ及び補正データが第3ラインメモリ15へ書き込まれるラインにおいては、第4ラインメモリ16に格納されている映像信号データを読み出す。第4ラインメモリ16書き込まれるラインにおいては、第3ラインメモリ15から映像信号データ及び補正データを読み出す。第3ラインメモリ15及び第4ラインメモリ16からの読み出しは、入力フレームレイットに対して倍のフレームレイットとなるクロックレイトで読み出される。

30

#### 【0069】

ここで、第3ラインメモリ15及び第4ラインメモリ16から読み出される映像信号データ及び補正データは、4画素分並列の4相データとしている。従って、入力映像信号Dinが1相の場合、第1フレームメモリ21及び第2フレームメモリへの書き込み／読み出しクロックは入力映像信号と同一レイットであり、入力映像信号のクロックレイトの実質4倍となる。また、入力映像信号Dinが2相の場合、第1フレームメモリ21及び第2フレームメモリへの書き込み／読み出しクロックは入力映像信号の倍のレイットであり、入力映像信号のクロックレイトの実質2倍となる。

40

#### 【0070】

従って、例えば、ラインメモリ15、16をそれぞれデュアルポートメモリで構成し、Dinが1相の場合には入力映像信号のクロックレイトの1/2のクロックレイトで読み出すことで入力フレームレイットに対して倍のフレームレイットとすることが出来る。また、入力映像信号Dinが2相の場合には入力映像信号のクロックレイトと同一クロックレイットで読み出すことで入力フレームレイットに対して倍のフレームレイットとすることが出来る。

#### 【0071】

第1フレームメモリ21に格納された映像信号データは、メモリコントローラ14を介して、ライン交互に補正データ決定部30を構成する第5ラインメモリ31及び第6ラインメモリ32に格納される。第3セレクタ33は、第1フレームメモリ21から読み出し

50

た映像信号データが第5ラインメモリ31へ書き込まれるラインにおいては、第6ラインメモリ32に格納されている映像信号データを読み出す。第6ラインメモリ32書き込まれるラインにおいては、第5ラインメモリ31から映像信号データを読み出す。ここで、第5ラインメモリ31及び第6ラインメモリ32からの読み出しは、第1フレームメモリ21から4相で読み出されてくる映像信号データを入力映像信号データと同一タイミングで1相のデータとなるように制御される。これは、例えば、第5ラインメモリ31及び第6ラインメモリ32をそれぞれ4つのデュアルポートメモリで構成し、4つのデュアルポートメモリから順次に入力映像信号データと同一のクロックレイトで読み出すことで実現することが出来る。なお、入力映像信号データDinが2相の場合には、例えば、ラインメモリ31、32をそれぞれ2つのデュアルポートメモリで構成し、2つのデュアルポートメモリから順次に入力映像信号データと同一のクロックレイトで読み出すことで実現することが出来る。

10

## 【0072】

第3セレクタ33からの映像信号データは、前フレームデータとして補正データ決定部34へ入力され、現フレームデータDinとの間で信号レベル比較を行う。比較結果は、例えば4ビットの補正データとして出力され、第1ラインメモリ11及び第2ラインメモリ12へ入力される。

20

## 【0073】

ここまで、映像信号データ及び補正データは、第1ラインメモリ11、第2ラインメモリ12、第3ラインメモリ15及び第4ラインメモリ16に共通に格納される形態として説明してきた。しかし、それぞれのラインメモリを映像信号データと補正データとで分けて格納するように構成しても良い。

20

## 【0074】

補正処理部50は、映像信号データと補正データとから応答速度を補正した12ビットの映像信号データを生成する。ここで、映像信号データの補正是、倍速フレームレイトの映像信号に対して、最初の倍速フレームあるいは後の倍速フレームのいずれか一方のみで行うことが出来る。あるいはまた、両方の倍速フレームで映像信号データの補正を行うことも、あるいは行わないことも可能である。

30

## 【0075】

なお、第1フレームメモリ21及び第2フレームメモリ22は、DDR-SDRAMとすることで、フレームメモリへの書き込み、及び読み出しを2相づつ倍速で行い、入力映像信号のクロックレイトの実質4倍で行うように制御することが出来る。また、第1フレームメモリ21及び第2フレームメモリ22をSDR-SDRAMとした場合、バス幅を倍にすることでフレームメモリへの書き込み、及び読み出しを、入力映像信号のクロックレイトの実質4倍で行うように制御することが出来る。これにより入力フレーム期間の1/4期間で入力映像信号データをフレームメモリに書き込み、2/4期間で倍速フレームデータを生成するための読み出しを行い、残りの1/4期間で応答速度補正データを決定するための参照データを読出す制御を実現している。また、フレームメモリ21、22は、それぞれ最低2フレーム分の映像信号データ及び補正データを格納可能な容量を備え、書き込むフレームのメモリ空間と読み出すフレームのメモリ空間とを分けている。これにより1個のフレームメモリで倍速変換とオーバースキャン駆動を実現可能としている。

40

## 【0076】

上記のように、本実施形態に係る構成に拠れば、倍速変換及び液晶応答速度特性の向上のための補正処理を適正に行うことが出来る表示技術を提供することができる。また、映像信号データを格納するフレームメモリと補正データを格納する補正データを独立している。このため、例えば、システム構成上オーバードライブが必要ない場合、補正データ格納用のフレームメモリを構成要素から容易に外すことが可能となり、コストダウン効果を見込むことが出来る。

## 【図面の簡単な説明】

## 【0077】

50

【図1】第1の実施形態に係る液晶表示装置の概略構成を示すブロック図である。

【図2】フレームメモリの書き込み、読み出しに係る動作のタイミングを示す模式図である。

【図3】フレームメモリの書き込み、読み出しに係る動作のタイミングを示す模式図である。

【図4】第2の実施形態に係る液晶表示装置の概略構成を示すブロック図である。

【図5】フレームメモリの書き込み、読み出しに係る動作のタイミングを示す模式図である。

【図6】第3の実施形態に係る液晶表示装置の概略構成を示すブロック図である。

【図7】従来の液晶表示装置の構成を示すブロック図である。

【図8】フレームメモリの書き込み、読み出しに係る動作のタイミングを示す模式図である。

【図9】液晶駆動信号と液晶応答特性を例示する模式図である。

【図10】液晶駆動信号と液晶応答特性を例示する模式図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

| (51) Int.Cl. | F I     | テーマコード(参考)   |

|--------------|---------|--------------|

|              | G 0 9 G | 3/20 6 4 1 R |

|              | G 0 9 G | 3/20 6 5 0 E |

|              | G 0 9 G | 3/20 6 6 0 V |

|              | G 0 2 F | 1/133 5 0 5  |

|              | G 0 2 F | 1/133 5 7 0  |

(72)発明者 坂下 幸彦

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 水野 良亮

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

F ターム(参考) 2H093 NA16 NA53 NC13 NC15 NC16 NC24 NC25 NC29 NC34 ND32

5C006 AA16 AC26 AF44 AF45 AF83 BF02 BF24 FA14 FA23 FA29

5C080 AA10 BB05 DD06 DD08 EE29 JJ02 JJ04