A1

**DEMANDE

DE BREVET D'INVENTION**

(21)

**N° 79 14997**

(54) Procédé pour décaler les seuils de commutation dans des circuits à opérateurs logiques intégrés à injection.

(51) Classification internationale (Int. Cl. 3). H 03 K 17/30, 3/289, 19/091.

(22) Date de dépôt..... 12 juin 1979, à 15 h 31 mn.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du public de la demande ..... B.O.P.I. — « Listes » n° 1 du 2-1-1981.

(71) Déposant : Société dite : THOMSON-CSF, SA, résidant en France.

(72) Invention de : Maurice Depey.

(73) Titulaire : *Idem* (71)(74) Mandataire : Thomson-CSF, Michel de Beaumont SPI-C, SCPI,

173, bd Haussmann, 75360 Paris Cedex 08.

La présente invention concerne un procédé pour décaler les seuils de commutation dans des circuits à opérateurs logiques intégrés à injection.

Dans le domaine de la réalisation de fonctions logiques sous forme de circuit intégré, une correspondance est supposée entre une grandeur électrique (tension, courant, résistance, etc) et la variable logique.

Selon cette correspondance, à une plage de variation de la grandeur électrique est associée une valeur de la variable logique. Dans le cas de la logique binaire, il y a donc deux plages de valeurs possibles de la grandeur électrique, correspondant aux deux valeurs 0 ou 1 de la variable binaire.

Pour un opérateur logique isolé, on peut définir un seuil ou une frontière de séparation des deux plages, mais en raison de la dispersion des caractéristiques de fabrication ou de différences des conditions de l'environnement, les différents opérateurs que l'on associe pour réaliser une fonction, ne présentent pas, en général, rigoureusement le même seuil. Il en résulte qu'une même valeur de grandeur électrique peut être interprétée comme un "0" par un opérateur, alors qu'elle est interprétée comme un "1" par un autre opérateur. Afin que ce phénomène ne se produise pas, les circuits sont conçus pour qu'en régime statique établi la grandeur électrique prenne une valeur éloignée de cette zone d'incertitude.

Mais en régime transitoire, lorsque l'on passe d'un état à un autre, la grandeur électrique traverse nécessairement cette zone d'incertitude.

Si cette traversée est assez rapide pour que l'opérateur dont on franchit le seuil en premier n'ait pas le temps de réagir avant que le seuil du second opérateur commandé en parallèle ne soit franchi, il n'y a pas, en général, d'effet défavorable. Mais si la transition du signal de commande des deux opérateurs est trop lente, le fonctionnement peut devenir aléatoire, altérant complètement la fonction logique dans le cas de certains circuits séquentiels.

Pour y remédier on introduit, par construction, un décalage volontaire des seuils d'entrée d'opérateurs commandés en parallèle, dans un sens convenable et d'une valeur supérieure à celle des dispersions accidentnelles de ces seuils de sorte que

malgré ces dispersions l'opérateur désiré réagisse le premier lors de la transition.

Ci-après, en se référant aux figures 1 à 4, annexées à la présente demande, on va expliciter le problème général posé.

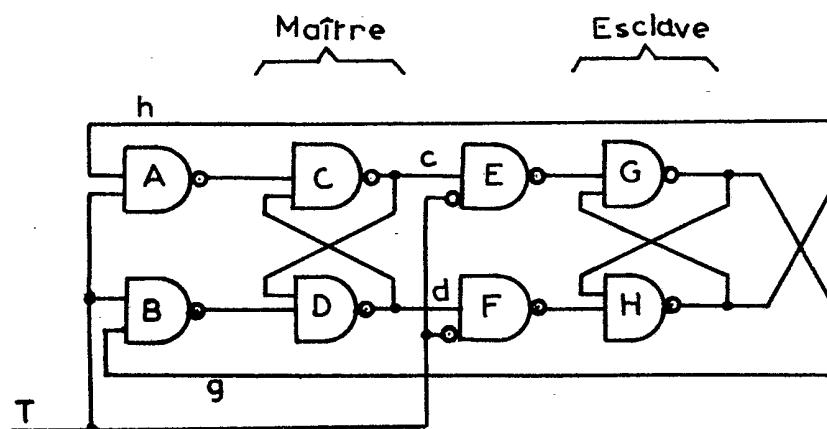

Sur la figure 1, annexée à la présente demande, on a représenté à titre d'exemple une bascule maître-esclave bien connue dans l'art antérieur et fonctionnant en diviseur de fréquence par 2.

Cette bascule maître-esclave comporte deux portes A et B commandant l'arrivée des signaux d'entrée h et g en synchronisme avec un signal d'horloge T, deux portes C et D constituant la bascule maître, deux portes E et F commandant l'attaque de l'esclave par le maître et deux portes G et H constituant la bascule esclave.

En régime statique, lorsque le signal d'horloge T est à l'état "1", les portes A et B sont "ouvertes" et laissent les signaux h et g des connexions de rebouclage commander l'état de la bascule maître formée par les portes C et D. Par contre les portes E et F sont alors "fermées" et les signaux c et d de sortie de la bascule maître n'ont aucun effet sur la bascule esclave formée par les portes G et H. Inversement lorsque le signal d'horloge T est à l'état "0", les portes A et B sont "fermées" et les signaux de sortie g et h de la bascule esclave n'ont aucun effet sur la bascule maître, tandis que les portes E et F sont "ouvertes" et les signaux de sortie c et d de la bascule maître imposent alors l'état de la bascule esclave. Donc en fonctionnement statique normal, soit la bascule esclave commande la bascule maître, soit la bascule maître commande la bascule esclave ; les deux situations sont mutuellement exclusives.

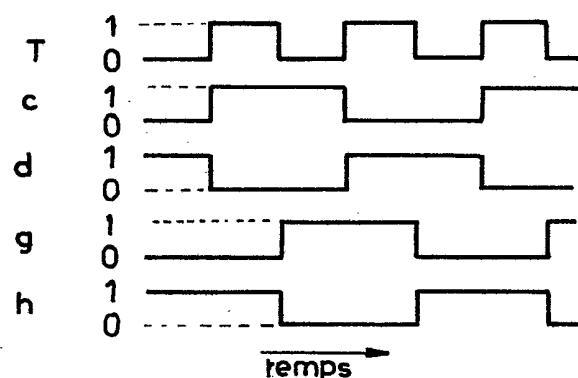

Sur la figure 2, on a représenté des diagrammes temporels des signaux T, c,d,g et h en fonction du temps, illustrant le fonctionnement de la bascule maître-esclave de la figure 1.

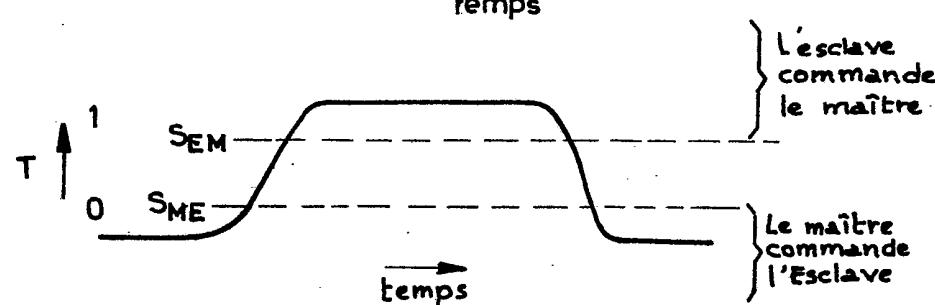

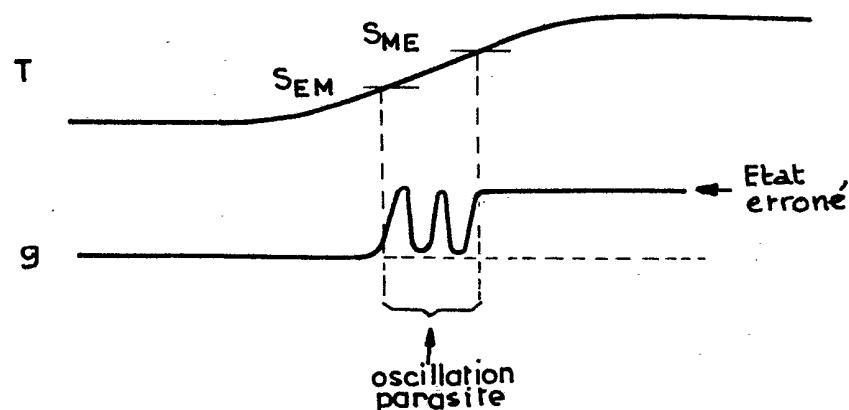

Si alors, en régime transitoire, lors de la transition de l'état "0" vers l'état "1" sur l'entrée T, comme indiqué sur la figure 4, on franchit le seuil  $S_{EM}$  des portes A et B avant d'avoir franchi le seuil  $S_{ME}$  des portes E et F ; alors, au même instant, les portes A et B interprètent le signal en T comme un "1", alors que les portes E et F l'interprètent déjà comme un "0". Il en résulte que les portes A, B, E et F sont alors "ouvertes" simultanément et que simultanément le maître commande l'esclave

et l'esclave commande le maître. Or les connexions sont telles que les ordres sont contradictoires et il y a donc instabilité du circuit. C'est ainsi que les portes E, G, H, A, C forment alors un oscillateur en anneau parasite. Pour éviter ce défaut il faut décaler les seuils de discrimination du 0 et du 1 des portes A et B (SME) d'une part, et des portes E et F (SEM) d'autre part, comme indiqué sur la figure 3, afin que, malgré les dispersions de ces seuils autour de leur valeur nominale, on soit certain dans l'exemple de transition considéré ci-dessus, que les portes E et F coupent 10 l'action des signaux c et d sur l'esclave (G, H) avant que les portes A et B n'autorisent l'action des signaux h et g sur le maître (C et D).

Ce problème est déjà bien connu dans les circuits intégrés logiques classiques, notamment en logique dite TTL. Dans 15 ce cas la solution choisie a consisté à effectuer une transposition de tension pour décaler les seuils, et ce au moyen de l'insertion d'un élément actif (transistor) provoquant le décalage.

Mais dans le domaine des circuits logiques intégrés à injection, dénommés circuits  $I^2L$ , le problème se pose différemment parce que le courant est aussi important à considérer que la tension en tant que grandeur électrique attachée à la variable logique et parce que, également, l'opérateur  $I^2L$  possède la structure d'un transistor NPN multicollecteurs.

Ce problème est résolu conformément à la présente 25 invention dans des circuits à opérateurs logiques intégrés à injection dans lesquels un opérateur à transistor de commutation multicollecteurs commande de façon séquentielle les autres opérateurs, grâce au fait qu'on affecte des surfaces de tailles différentes aux collecteurs du transistor de commutation multicollecteurs effectuant 30 la commande.

Grâce à cette disposition, les différents opérateurs commandés sont déclenchés selon la séquence désirée, et ce de façon absolument fiable. Un domaine particulier d'application est celui d'une bascule de type JK réalisée en structure  $I^2L$ .

35 A titre d'exemple on a décrit ci-dessous et illustré schématiquement aux dessins annexés un mode d'exécution de l'objet selon l'invention.

Les figures 1 à 4, dont il a déjà été fait mention, concernent le système logique d'une bascule maître-esclave et 40 sont destinées à expliciter le problème à la base de l'invention.

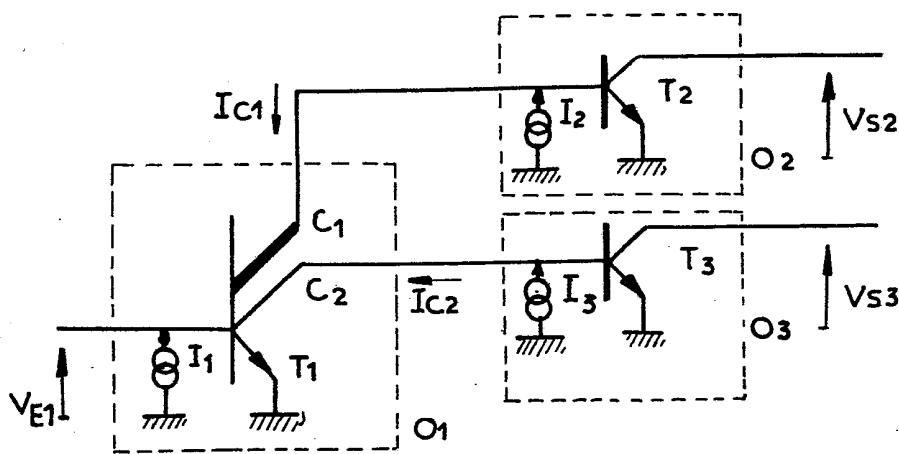

La figure 5 représente le schéma électrique d'un circuit  $I^2L$  auquel s'applique le procédé selon l'invention.

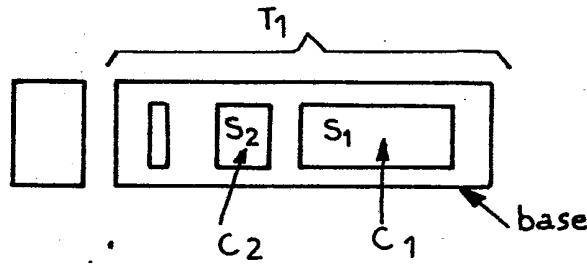

La figure 6 représente la structure conforme à l'invention de l'opérateur de commande  $I^2L$  du circuit de la figure 5.

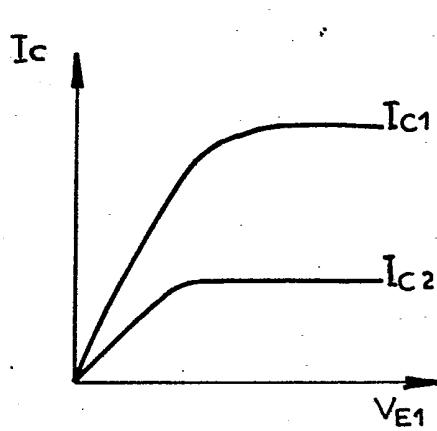

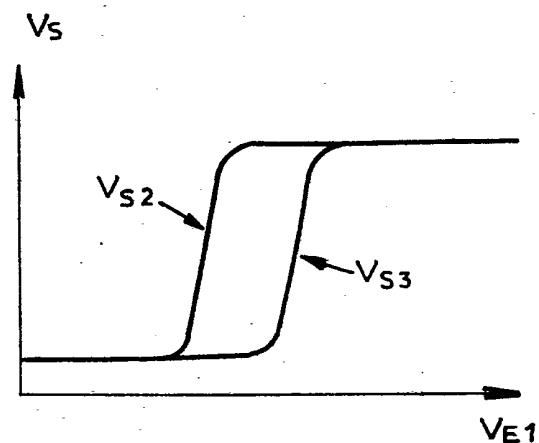

La figure 7 (a,b) montre deux schémas représentant les courbes caractéristiques des opérateurs du circuit de la figure 5.

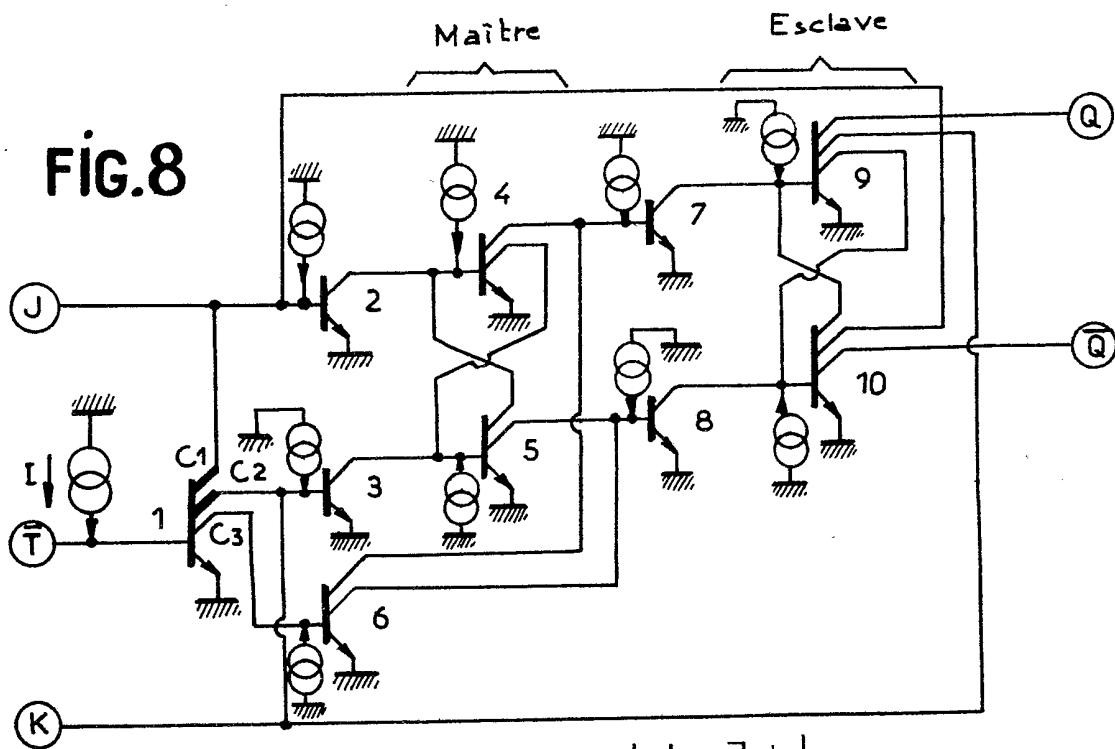

La figure 8 représente le schéma électrique d'une bascule JK utilisant les portes  $I^2L$  et mettant en oeuvre l'objet de la présente invention.

La figure 9 représente la vue en plan schématique de la réalisation technologique du circuit de la figure 8.

Sur la figure 5, on a représenté le schéma électrique d'un circuit dans lequel un opérateur  $I^2L O_1$ , commande deux opérateurs  $I^2L O_2$  et  $O_3$ . Les opérateurs  $O_2$  et  $O_3$  sont formés chacun par un transistor PNP d'injection de courant  $I_2$ ,  $I_3$  et par un transistor de commutation  $T_2$ ,  $T_3$ . L'opérateur de commande  $O_1$  comprend un transistor PNP d'injection de courant  $I_1$  et un transistor NPN de commutation  $T_1$  comportant deux collecteurs  $C_1$ ,  $C_2$ . Conformément à l'invention, (voir la vue en plan de la structure technologique de cet opérateur  $O_1$  sur la figure 6) on affecte aux deux collecteurs  $C_1$  et  $C_2$  du transistor  $T_1$ , des surfaces  $S_1$ ,  $S_2$  de tailles différentes, telles que la surface  $S_1$  du collecteur  $C_1$  est nettement plus grande que la surface  $S_2$  du collecteur  $C_2$ . Cette disposition crée, comme on va l'expliquer ci-après, un net décalage des seuils de commutation pour la commande des opérateurs  $O_2$  et  $O_3$ .

On suppose que les sources de courant  $I_2$  et  $I_3$  des opérateurs  $O_2$  et  $O_3$  sont nominalement identiques. Lorsque la tension  $V_{E1}$  appliquée à l'entrée de l'opérateur  $O_1$ , c'est-à-dire sur la base du transistor  $T_1$ , augmente progressivement, le transistor  $T_2$  se bloque avant le transistor  $T_3$  parce que l'appel de courant est plus grand de la part du collecteur  $C_1$  que du collecteur  $C_2$ , étant donné que la surface  $S_1$  du collecteur  $C_1$  est supérieure à la surface  $S_2$  du collecteur  $C_2$ . (Sur la figure 5, on a représenté le collecteur  $C_1$  par un trait nettement plus épais que le collecteur  $C_2$  pour indiquer que la surface  $S_1$  est supérieure à la surface  $S_2$ ).

Sur la figure 7a, on a en outre représenté la forme des courbes caractéristiques des courants de collecteur  $I_{C1}$  et  $I_{C2}$  en fonction de la tension d'entrée  $V_{E1}$  de l'opérateur  $O_1$ ,

sur lesquelles on voit que l'on a  $I_{C1} > I_{C2}$ .

Sur la figure 7b, on a représenté les caractéristiques de transfert entre la tension d'entrée  $V_{E1}$  de l'opérateur  $O_1$  et les tensions de sortie  $V_{S2}$  et  $V_{S3}$  des opérateurs  $O_2$  et  $O_3$ .

Le procédé conforme à l'invention s'applique notamment à la réalisation d'une bascule du type JK en logique  $I^2L$ , telle que représentée sur la figure 8. Cette figure correspond au schéma logique de la figure 1, si ce n'est qu'ici la commande s'effectue sur le signal d'horloge  $T$  complémenté ( $\bar{T}$ ). Sur cette figure, la référence 1 désigne un opérateur  $I^2L$  à collecteurs multiples, conforme à l'invention (les surfaces des collecteurs  $C1$  et  $C2$  sont égales entre elles et supérieures à la surface du collecteur  $C3$ ), qui commande des opérateurs 2, 3 de transfert des signaux d'entrée aux opérateurs 4, 5 (constituant le "maître") et un opérateur 6 de commande des opérateurs 7, 8 de transfert des signaux du maître 4, 5 aux opérateurs 9, 10 (constituant "l'esclave"), et qui est raccordée en outre par ses collecteurs  $C1$ ,  $C2$  à des collecteurs respectifs des opérateurs 9, 10 de l'esclave.

Par conséquent, et du fait que les surfaces des collecteurs  $C1$  et  $C2$  sont supérieures à la surface du collecteur  $C3$ , lorsque le transistor 1 passe de l'état conducteur à l'état bloqué, le transistor 6 devient conducteur avant les transistors 2 et 3, et donc les transistors 7 et 8 se bloquent avant que les transistors 2 et 3 ne deviennent conducteurs.

Autrement dit, en partant de l'état logique de l'entrée  $\bar{T}$ , pour lequel le maître commande l'esclave, on coupe la commande de l'esclave par le maître avant d'autoriser la commande du maître par l'esclave. Ceci correspond bien, sur la transition montante du signal  $T$  de la figure 3, au franchissement du seuil  $S_{ME}$  avant le franchissement du seuil  $S_{EM}$ .

Sur la figure 9, on a représenté la vue en plan d'une réalisation technologique du circuit à opérateurs  $I^2L$  de la figure 8 sur une microplaquette. Sur cette figure 9, on a repéré les différents transistors de commutation  $T_1, \dots, T_{10}$  des opérateurs  $I^2L$ , ainsi que les différentes bornes J, K, Q, Q, T de la bascule. On remarquera notamment la plus grande surface des collecteurs  $C1$  et  $C2$  du transistor  $T_1$  par rapport à celle du collecteur  $C3$  de ce transistor.

## R E V E N D I C A T I O N S

---

1. Procédé pour décaler les seuils de commutation dans des circuits à opérateurs logiques intégrés à injection dans lesquels un opérateur à transistor de commutation multicollecteurs 5 commande de façon séquentielle les autres opérateurs , caractérisé par le fait qu'on affecte des surfaces de tailles différentes aux collecteurs du transistor de commutation multicollecteurs de commande.

2. Circuit logique à injection intégré réalisé par 10 la mise en oeuvre du procédé selon la revendication 1, comportant trois transistors NPN ( $T_1$ ,  $T_2$ ,  $T_3$ ), le premier transistor ( $T_1$ ) comportant au moins deux collecteurs dont le premier ( $C_1$ ) est relié à la base du deuxième transistor ( $T_2$ ) et la deuxième ( $C_2$ ) est relié à la base du troisième transistor ( $T_3$ ), caractérisé en ce que la 15 surface du premier collecteur est plus grande que celle du deuxième collecteur, d'où il résulte que, lorsque le premier transistor passe progressivement d'un état bloqué à un état conducteur, le deuxième transistor est bloqué avant le troisième.

3. Bascule logique maître-esclave du type JK, 20 réalisée avec des opérateurs logiques intégrés à injection par la mise en oeuvre du procédé suivant la revendication 1, dans laquelle un transistor de commutation à trois collecteurs commande de façon séquentielle les transistors des portes de transfert des signaux d'entrée au maître et le transistor de commande cadencée des transistors des portes de transfert des signaux du maître à l'esclave, 25 caractérisée par le fait que le collecteur ( $C_3$ ) du transistor (1) de commutation à trois collecteurs, qui est relié au transistor (6) de commande cadencée des portes de transfert des signaux du maître à l'esclave, possède une surface plus petite que celles des deux autres collecteurs ( $C_1$ ,  $C_2$ ) raccordés aux transistors des portes (7, 8) de transfert des signaux d'entrée au maître, de sorte 30 que lorsque le transistor multicollecteur (1) passe à l'état conducteur à l'état bloqué, le transistor (6) devient conducteur avant les autres transistors de transfert (2, 3) et que les transistors (7, 8) de transfert des signaux du maître à l'esclave se bloquent avant que les transistors (2,3) ne deviennent conducteurs. 35

FIG.1

FIG.2

FIG.3

FIG.4

FIG.5

FIG.6

FIG.7a

FIG.7b

**FIG.9**