(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7600701号**

**(P7600701)**

(45)発行日 令和6年12月17日(2024.12.17)

(24)登録日 令和6年12月9日(2024.12.9)

(51)国際特許分類

|        |                  |     |        |        |   |

|--------|------------------|-----|--------|--------|---|

| H 01 L | 21/82 (2006.01)  | F I | H 01 L | 21/82  | B |

| H 01 L | 21/822 (2006.01) |     | H 01 L | 21/82  | L |

| H 01 L | 27/04 (2006.01)  |     | H 01 L | 27/04  | D |

| H 01 L | 21/8238(2006.01) |     | H 01 L | 27/092 |   |

| H 01 L | 27/092 (2006.01) |     |        |        |   |

請求項の数 9 (全19頁)

(21)出願番号 特願2021-6441(P2021-6441)

(22)出願日 令和3年1月19日(2021.1.19)

(65)公開番号 特開2022-110807(P2022-110807

A)

(43)公開日 令和4年7月29日(2022.7.29)

審査請求日 令和5年12月22日(2023.12.22)

(73)特許権者 514315159

株式会社ソシオネクスト

神奈川県横浜市港北区新横浜2丁目10

番23

(74)代理人 100107766

弁理士 伊東 忠重

(74)代理人 100070150

弁理士 伊東 忠彦

(72)発明者 岡本 淳

神奈川県横浜市港北区新横浜2丁目10

番23 株式会社ソシオネクスト内

(72)発明者 武野 紘宜

神奈川県横浜市港北区新横浜2丁目10

番23 株式会社ソシオネクスト内

(72)発明者 岩堀 淳司

最終頁に続く

(54)【発明の名称】 半導体装置

**(57)【特許請求の範囲】****【請求項1】**

論理回路が配置される第1領域と、

前記論理回路とは異なる機能回路が配置される第2領域と、

前記第2領域に隣接して設けられ、第1電源線を前記論理回路および前記機能回路に電源を供給する第2電源線に接続する第1電源スイッチ回路と、

を有し、

前記第1電源スイッチ回路は、

前記論理回路に使用されるトランジスタのサイズより大きいサイズを有し、前記第1電源線を前記第2電源線に接続する第1トランジスタと、

前記機能回路に隣接する領域に設けられたエンドキャップと、

前記第1トランジスタが配置される領域と前記エンドキャップとの間に設けられ、前記論理回路に使用されるトランジスタと同じサイズを有し、前記第1電源線を前記第2電源線に接続する第2トランジスタと、

を有する半導体装置。

**【請求項2】**

前記第1領域内に設けられ、前記第1電源線を前記第2電源線に接続する第2電源スイッチ回路を有し、

前記第2電源スイッチ回路は、

前記論理回路に使用されるトランジスタのサイズより大きいサイズを有し、前記第1電

10

20

源線を前記第2電源線に接続する第3トランジスタと、

前記第3トランジスタにおいて前記第3トランジスタのゲート電極の配列方向の端に隣接して設けられ、前記論理回路に使用されるトランジスタと同じサイズを有し、前記第1電源線を前記第2電源線に接続する第4トランジスタと、

を有し、

前記第4トランジスタが配置される領域の大きさは、前記第1電源スイッチ回路の前記第2トランジスタが配置される領域の大きさと同じである

請求項1に記載の半導体装置。

#### 【請求項3】

前記第1電源スイッチ回路は、前記第2トランジスタと同じサイズを有し、前記第1電源線を前記第2電源線に接続する第5トランジスタを有する

10

請求項1または請求項2に記載の半導体装置。

#### 【請求項4】

前記第1トランジスタおよび前記第2トランジスタの各々は、第1方向に配列される複数のゲート電極を有し、

前記第1トランジスタ、前記第2トランジスタおよび前記エンドキャップは、前記第1方向に沿って配置される

請求項1ないし請求項3のいずれか1項に記載の半導体装置。

#### 【請求項5】

前記機能回路は、メモリIP、ハードマクロIPまたはアナログIPである

20

請求項1ないし請求項4のいずれか1項に記載の半導体装置。

#### 【請求項6】

論理回路が配置される第1領域と、

前記第1領域に隣接して設けられ、第1電源線を前記論理回路に電源を供給する第2電源線に接続する複数種の電源スイッチ回路が配置される電源スイッチ領域と、

を有し、

前記複数種の電源スイッチ回路は、前記論理回路に使用されるトランジスタのサイズより大きいサイズを有し、前記第1電源線を前記第2電源線に接続する第1トランジスタを有し、

前記複数種の電源スイッチ回路の少なくとも1種は、さらに、

30

前記第1トランジスタが配置される領域において前記第1トランジスタのゲート電極の配列方向である第1方向の端に隣接して設けられ、前記論理回路に使用されるトランジスタと同じサイズを有し、前記第1電源線を前記第2電源線に接続する第2トランジスタと、

前記第2トランジスタが配置される領域において前記第1トランジスタと反対側に隣接して設けられるエンドキャップと、

を有する半導体装置。

#### 【請求項7】

前記電源スイッチ領域は、前記第1領域の周囲に環状に設けられ、

前記第1領域において前記第1方向の両端に隣接して配置される前記第2トランジスタおよび前記エンドキャップを含む前記電源スイッチ回路は、前記第1トランジスタにおける前記第1方向の両側に設けられた前記第2トランジスタと前記エンドキャップとを有する請求項6に記載の半導体装置。

40

#### 【請求項8】

前記電源スイッチ領域は、前記第1領域において前記第1方向と直交する第2方向に隣接して設けられ、

前記電源スイッチ領域において前記第1方向の両端に配置される前記電源スイッチ回路は、前記第1方向に沿って配置される前記第2トランジスタおよび前記エンドキャップを含み、

前記電源スイッチ領域において前記第1方向の両端に配置される前記電源スイッチ回路を除く前記電源スイッチ回路は、前記第1方向に沿って配置される前記第2トランジスタ

50

および前記エンドキャップを含まない

請求項 6 に記載の半導体装置。

【請求項 9】

前記第 1 トランジスタおよび前記第 2 トランジスタは、f i n F E T である

請求項 1 ないし請求項 8 のいずれか 1 項に記載の半導体装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、半導体装置に関する。

【背景技術】

【0 0 0 2】

半導体装置のリーク電流を削減するために、電源線と複数の回路ブロックの各々の電源線である仮想電源線との間に、回路ブロックの動作時にオンする電源スイッチ回路を設ける手法が知られている。

10

【0 0 0 3】

電源スイッチ回路の電源供給能力を高くするために、電源スイッチ回路で使用されるトランジスタのサイズは、論理回路で使用されるセルトランジスタのサイズに比べて大きく設計される。サイズが異なるトランジスタを隣接して配置する場合、サイズが小さいトランジスタのゲート電極等は、半導体装置の製造時に形状がばらつきやすい。形状のばらつきを抑制するために、サイズが互いに異なるトランジスタは、レイアウトルールにより決められた間隔を空けて配置される。例えば、電源スイッチ回路の端に空き領域を設けることで、電源スイッチ回路のトランジスタと、電源スイッチ回路に隣接する論理回路等のトランジスタとが、レイアウトルールを満足する間隔だけ離れて配置される。例えば、電源スイッチ回路の空き領域には、ダミーゲート電極またはダミートランジスタ等が配置される。

20

【先行技術文献】

【特許文献】

【0 0 0 4】

【文献】米国特許第 1 0 1 4 1 3 3 6 号明細書

【文献】米国特許出願公開第 2 0 1 9 / 0 2 4 4 9 0 0 号明細書

30

【文献】米国特許出願公開第 2 0 1 9 / 0 2 1 4 3 7 7 号明細書

【文献】特開 2 0 1 8 - 1 9 0 7 6 0 号公報

【文献】国際公開第 2 0 1 7 / 2 0 8 8 8 7 号

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 5】

近時、半導体装置の高集積化とリーク電流の抑制とを両立するために、半導体装置に搭載されるトランジスタは、例えば、プレーナ型 F E T (Field Effect Transistor) から立体構造を有する f i n F E T 等に置き換わりつつある。これに伴い、論理回路で使用されるトランジスタのサイズと電源スイッチ回路で使用されるトランジスタのサイズとの差は大きくなる傾向にある。そして、製造時のゲート電極等の形状のばらつきを抑えるために、電源スイッチ回路の端には、より大きな空き領域が設けられる。

40

【0 0 0 6】

空き領域が大きいほど、電源スイッチ回路のサイズは大きくなり、単位サイズ当たりの電源供給能力は低下する。また、通常、半導体装置内には複数の電源スイッチ回路が配置される。このため、電源スイッチ回路のサイズが大きくなると、半導体装置に搭載可能な論理回路の規模は小さくなる。論理回路の規模を維持する場合、半導体装置のチップサイズは大きくなる。

【0 0 0 7】

本発明は、上記の点に鑑みてなされたもので、電源スイッチ回路内に空き領域が必要な

50

場合にも、電源供給能力の低下を抑制することを目的とする。

【課題を解決するための手段】

【0008】

本発明の一態様では、半導体装置は、論理回路が配置される第1領域と、前記論理回路とは異なる機能回路が配置される第2領域と、前記第2領域に隣接して設けられ、第1電源線を前記論理回路および前記機能回路に電源を供給する第2電源線に接続する第1電源スイッチ回路と、を有し、前記第1電源スイッチ回路は、前記論理回路に使用されるトランジスタのサイズより大きいサイズを有し、前記第1電源線を前記第2電源線に接続する第1トランジスタと、前記機能回路に隣接する領域に設けられたエンドキャップと、前記第1トランジスタが配置される領域と前記エンドキャップとの間に設けられ、前記論理回路に使用されるトランジスタと同じサイズを有し、前記第1電源線を前記第2電源線に接続する第2トランジスタと、を有する。

10

【発明の効果】

【0009】

開示の技術によれば、電源スイッチ回路内に空き領域が必要な場合にも、電源供給能力の低下を抑制することができる。

【図面の簡単な説明】

【0010】

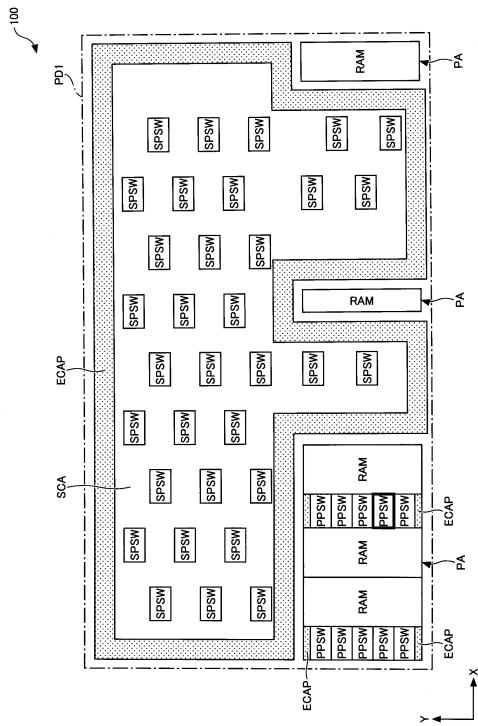

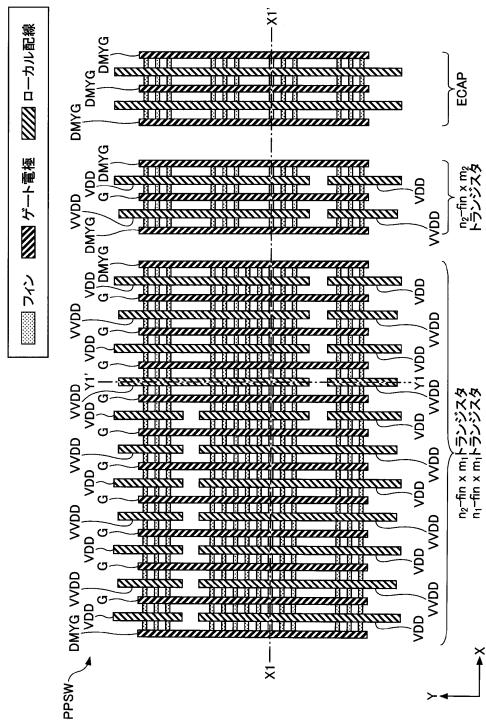

【図1】第1の実施形態の半導体装置のレイアウトの一例を示す図である。

20

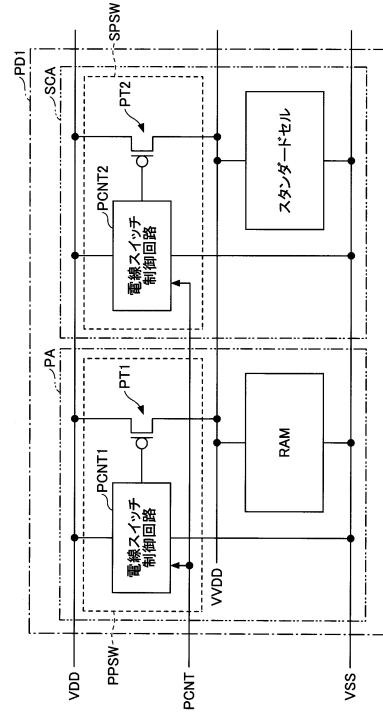

【図2】図1の電源スイッチ回路S P S W、P P S Wの一例を示すブロック図である。

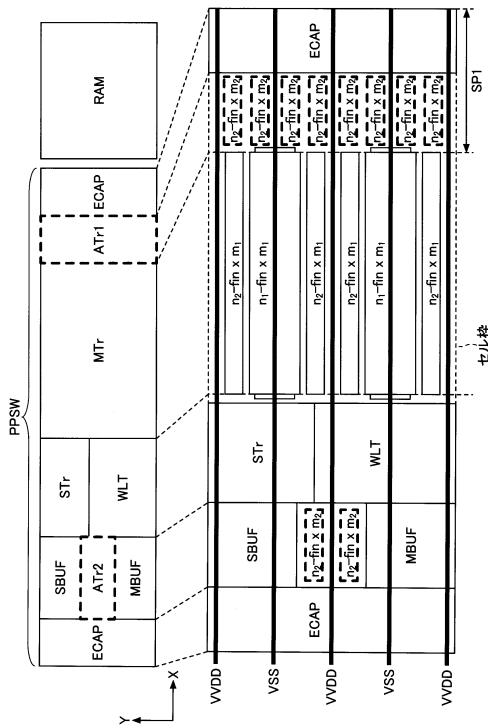

【図3】図1の周辺領域に設けられる電源スイッチ回路のレイアウトの一例を示す図である。

【図4】図3の電源スイッチ回路P P S Wの電源配線のレイアウトの一例を示す図である。

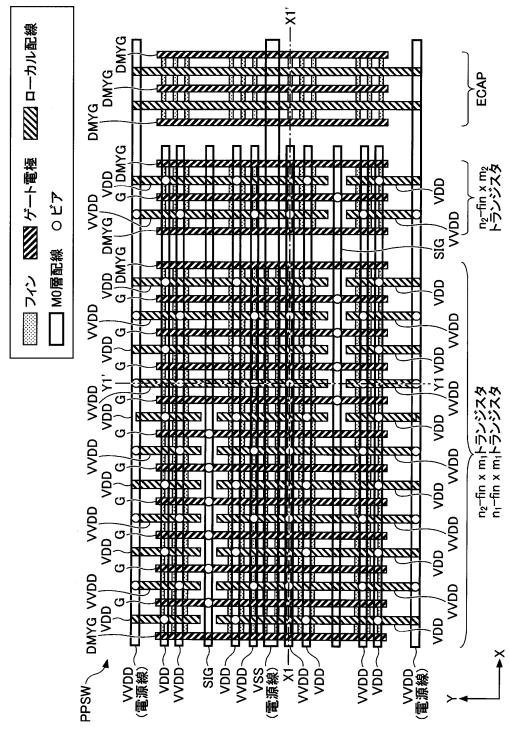

【図5】図4のフィン、ゲート電極およびローカル配線のレイアウトを示す図である。

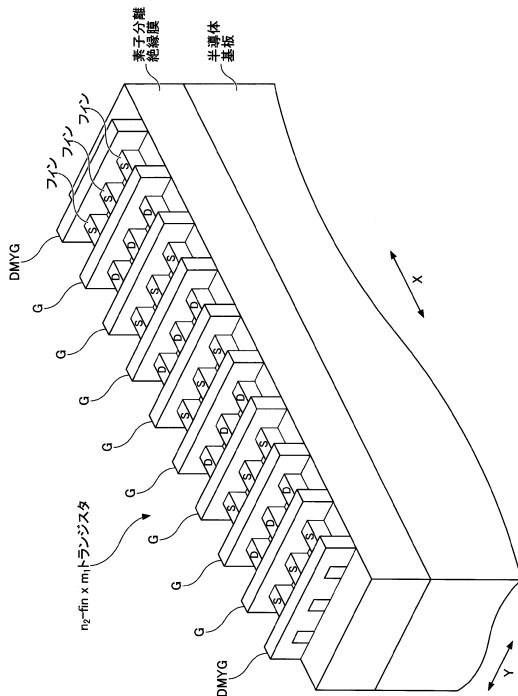

【図6】図3および図4の $n_2 - f_{in} \times m_1$ トランジスタの構造の一例を示す斜視図である。

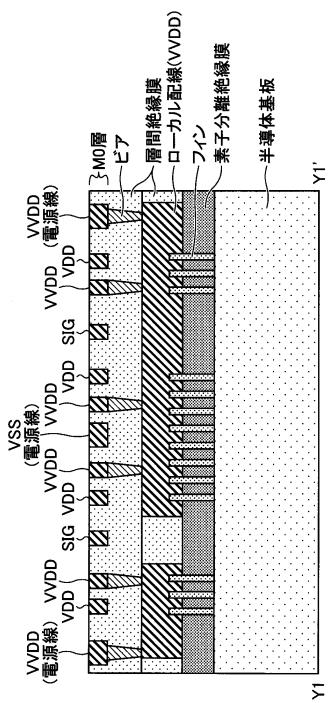

【図7】図4のY1 - Y1'線に沿う断面を示す図である。

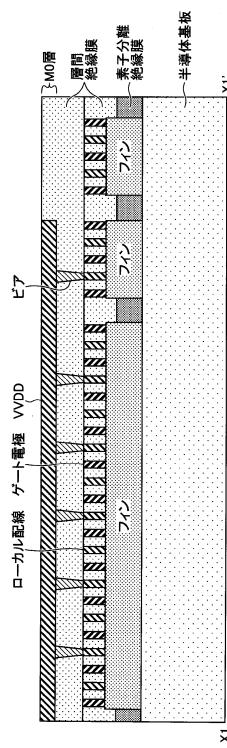

【図8】図4のX1 - X1'線に沿う断面を示す図である。

【図9】図1のスタンダードセル領域に設けられる電源スイッチ回路のレイアウトの一例を示す図である。

30

【図10】他の電源スイッチ回路の回路レイアウトの一例(比較例)を示す図である。

【図11】第2の実施形態における半導体装置のレイアウトの一例を示す図である。

【図12】第3の実施形態における半導体装置のレイアウトの一例を示す図である。

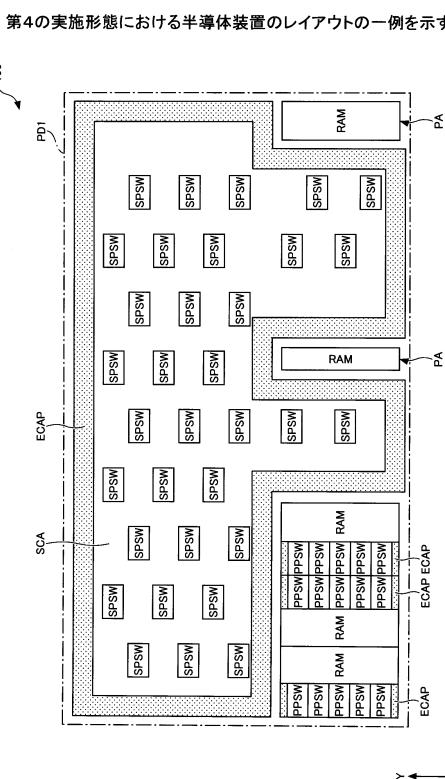

【図13】第4の実施形態における半導体装置のレイアウトの一例を示す図である。

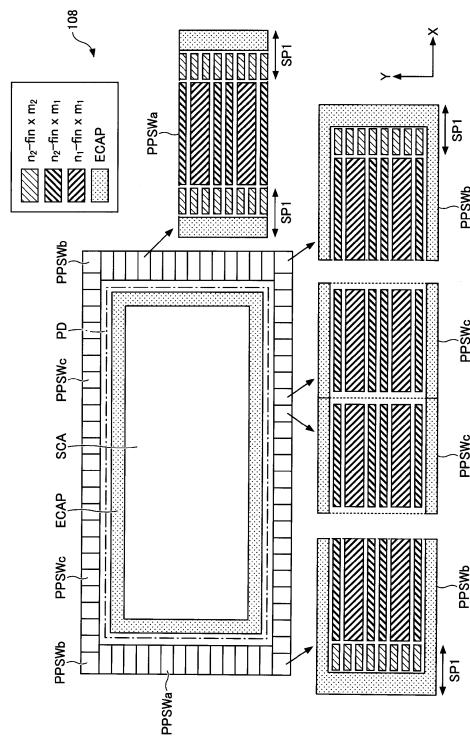

【図14】第5の実施形態における半導体装置のレイアウトの一例を示す図である。

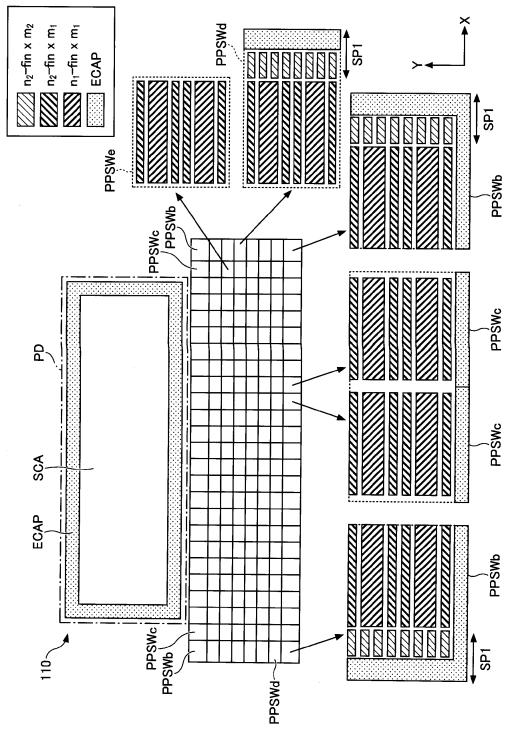

【図15】第6の実施形態における半導体装置のレイアウトの一例を示す図である。

【発明を実施するための形態】

【0011】

以下、図面を用いて実施形態を説明する。以下では、電源が供給される電源線には、電源名と符号が使用される。

40

【0012】

(第1の実施形態)

図1は、第1の実施形態における半導体装置のレイアウトの一例を示す。図1に示す半導体装置100は、例えば、少なくとも1つのパワードメインP D 1を有する。パワードメインP D 1内には、図示しない複数のスタンダードセルが配置されるスタンダードセル領域S C Aと、1つまたは複数のR A M(Random Access Memory)が配置される複数の周辺領域P Aとが設けられる。スタンダードセル領域S C Aは、論理回路が配置される第1領域の一例であり、周辺領域P Aは、論理回路とは異なる機能回路が設けられる第2領域の一例である。

【0013】

50

図1では、1つのパワードメインP D 1のみが示されるが、半導体装置100は、複数のパワードメインを有してもよい。なお、図1においてパワードメインP D 1の左側が、半導体装置100のチップ端であってもよい。特に限定されないが、半導体装置100に搭載されるトランジスタは、finFETである。finFETについては、図6で説明する。

#### 【0014】

スタンダードセル領域S C Aには、複数の電源スイッチ回路S P S Wが間隔を置いて配置される。また、スタンダードセル領域S C Aの周囲には、網掛けのパターンで示されるエンドキャップE C A Pが配置される。エンドキャップE C A Pは、ダミーゲート電極またはダミートランジスタを有する。なお、スタンダードセル領域S C Aに電源スイッチ回路S P S Wを配置せずに、スタンダードセルのみが配置されてもよい。

10

#### 【0015】

各周辺領域P Aには、1つまたは複数のR A Mが配置され、一部の周辺領域P Aには、R A Mに隣接して複数の電源スイッチ回路P P S WとエンドキャップE C A Pとが配置される。R A Mは、ハードマクロであるメモリI P (Intellectual Property)の一例であり、所定の機能を有する機能回路の一例である。電源スイッチ回路P P S Wは、第1電源スイッチ回路の一例である。電源スイッチ回路S P S Wは、第2電源スイッチ回路の一例である。

#### 【0016】

図2は、図1の電源スイッチ回路S P S W、P P S Wの一例を示す。電源スイッチ回路P P S Wは、pチャネルトランジスタP T 1および電源スイッチ制御回路P C N T 1を有する。電源スイッチ回路S P S Wは、pチャネルトランジスタP T 2および電源スイッチ制御回路P C N T 2を有する。なお、pチャネルトランジスタP T 1、P T 2のそれぞれは、実際には、並列接続された複数のトランジスタを含む。なお、電源スイッチ回路S P S Wおよび電源スイッチ回路P P S Wは、それぞれpチャネルトランジスタP T 1およびpチャネルトランジスタP T 2の代わりにnチャネルトランジスタを有してもよい。この場合、nチャネルトランジスタのソースは接地線V S Sに接続され、ドレインはスタンダードセルの各論理回路に接続し、接地電位を供給する仮想接地線に接続される。

20

#### 【0017】

pチャネルトランジスタP T 1のソースは、例えば、外部電源V D Dが供給される電源線V D Dに接続され、pチャネルトランジスタのドレインは、スタンダードセルおよびR A Mの電源端子に接続される仮想電源線V V D Dに接続される。電源線V D Dは、第1電源線の一例であり、仮想電源線V V D Dは、第2電源線の一例である。pチャネルトランジスタP T 1のゲート電極は、電源スイッチ制御回路P C N T 1の出力に接続される。

30

#### 【0018】

pチャネルトランジスタP T 2のソースは、電源線V D Dに接続され、pチャネルトランジスタのドレインは、仮想電源線V V D Dに接続される。pチャネルトランジスタP T 2のゲート電極は、電源スイッチ制御回路P C N T 2の出力に接続される。

#### 【0019】

各電源スイッチ制御回路P C N T 1、P C N T 2は、常時動作するために電源線V D Dおよび接地線V S Sに接続され、電源制御信号P C N Tに基づいて動作する。電源スイッチ制御回路P C N T 1は、電源制御信号P C N TがパワードメインP D 1内の回路を動作させるアクティブモードを示す場合、pチャネルトランジスタP T 1のゲート電極に接地電圧V S Sを供給する。これにより、pチャネルトランジスタP T 1はオンし、電源線V D Dと仮想電源線V V D Dとが相互に接続される。

40

#### 【0020】

電源スイッチ制御回路P C N T 2は、電源制御信号P C N Tがアクティブモードを示す場合、pチャネルトランジスタP T 2のゲート電極に接地電圧V S Sを供給する。これにより、pチャネルトランジスタP T 2はオンし、電源線V D Dと仮想電源線V V D Dとが相互に接続される。

50

**【 0 0 2 1 】**

電源スイッチ制御回路 P C N T 1 は、電源制御信号 P C N T がパワーダウンモードを示す場合、p チャネルトランジスタ P T 1 のゲート電極に電源電圧 V D D を供給する。これにより、p チャネルトランジスタ P T 1 はオフし、電源線 V D D と仮想電源線 V V D D との接続が遮断される。

**【 0 0 2 2 】**

電源スイッチ制御回路 P C N T 2 は、電源制御信号 P C N T がパワーダウンモードを示す場合、p チャネルトランジスタ P T 2 のゲート電極に電源電圧 V D D を供給する。これにより、p チャネルトランジスタ P T 2 はオフし、電源線 V D D と仮想電源線 V V D D との接続が遮断される。このように、p チャネルトランジスタ P T 1、P T 2 は、共通の電源制御信号 P C N T に基づいて動作し、電源線 V D D を仮想電源線 V V D D に接続する電源スイッチとして機能する。

10

**【 0 0 2 3 】**

R A M の電源端子は、仮想電源線 V V D D に接続され、R A M の接地端子は、接地線 V S S に接続される。同様に、スタンダードセルの電源端子は、仮想電源線 V V D D に接続され、スタンダードセルの接地端子は、接地線 V S S に接続される。

**【 0 0 2 4 】**

p チャネルトランジスタ P T 1、P T 2 は、アクティブモード中にオンし、電源線 V D D を仮想電源線 V V D D に接続する。これにより、パワードメイン P D 1 内の R A M およびスタンダードセルは、アクティブモード中、仮想電源線 V V D D を介して電源電圧 V D D を受け、動作する。一方、p チャネルトランジスタ P T 1、P T 2 は、パワーダウンモード中にオフし、電源線 V D D と仮想電源線 V V D D との接続を遮断する。これにより、パワードメイン P D 1 内の R A M およびスタンダードセルは、パワーダウンモード中、電源電圧 V D D の供給が停止され、動作を停止する。

20

**【 0 0 2 5 】**

なお、複数の p チャネルトランジスタ P T 1 は、電源スイッチ制御回路 P C N T 1 からの互いに異なるタイミングの制御信号をゲート電極でそれぞれ受け、順次にオンされ、順次にオフされてもよい。同様に、複数の p チャネルトランジスタ P T 2 は、電源スイッチ制御回路 P C N T 2 からの互いに異なるタイミングの制御信号をゲート電極でそれぞれ受け、順次にオンされ、順次にオフされてもよい。

30

**【 0 0 2 6 】**

p チャネルトランジスタ P T 1 ( または P T 2 ) の動作タイミングをずらすことによって、電源 V D D から仮想電源線 V V D D に電流が急激に流れることが抑止される。これにより、電源スイッチ回路 P P S W、S P S W の動作の開始時に発生する電源ノイズを緩和することができる。

**【 0 0 2 7 】**

図 3 は、図 1 の周辺領域 P A に設けられる電源スイッチ回路 P P S W のレイアウトの一例を示す。図 3 では、電源スイッチ回路 P P S W が、X 方向に延在する 5 本の電源線 ( V V D D、V S S ) の間に設けられる 4 つの領域を使用する 4 ハイトセルである例が示される。なお、電源スイッチ回路 P P S W は、ダブルハイトセル ( 2 ハイトセル ) でもよく、8 ハイトセルでもよい。X 方向は、第 1 方向の一例である。

40

**【 0 0 2 8 】**

電源スイッチ回路 P P S W は、メイントランジスタ M T r 、サブトランジスタ S T r 、付加トランジスタ A T r 1、A T r 2 、ウェルタップ W L T 、メインバッファ部 M B U F 、サブバッファ部 S B U F および 2 つのエンドキャップ E C A P を有する。メイントランジスタ M T r 、サブトランジスタ S T r および付加トランジスタ A T r 1、A T r 2 は、図 2 に示した p チャネルトランジスタ P T 1 に対応する複数の p チャネルトランジスタをそれぞれ有する。メイントランジスタ M T r およびサブトランジスタ S T r は、第 1 トランジスタの一例である。付加トランジスタ A T r 1 は、第 2 トランジスタの一例であり、付加トランジスタ A T r 2 は、第 5 トランジスタの一例である。

50

**【0029】**

メイントランジスタMTrは、 $n_1$ 個のフィンと $m_1$ 本のゲート電極とを有する複数のトランジスタ（以下、 $n_1 - fin \times m_1$ トランジスタとも称する）を有する。また、メイントランジスタMTrは、 $n_2$ 個のフィンと $m_1$ 本のゲート電極とを有する複数のトランジスタ（以下、 $n_2 - fin \times m_1$ トランジスタとも称する）とを有する。付加トランジスタATr1、ATr2は、 $n_2$ 個のフィンと $m_2$ 本のゲート電極とを有する複数のトランジスタ（以下、 $n_2 - fin \times m_2$ トランジスタとも称する）とを有する。ここで、 $n_1$ 、 $n_2$ 、 $m_1$ および $m_2$ は、 $n_1 > n_2$ 、 $m_1 > m_2$ の関係の成り立つ任意の自然数である。

**【0030】**

各トランジスタのサイズは、フィン数とゲート電極の数とに応じて異なる。例えば $n_1 = 8$ 、 $n_2 = 3$ 、 $m_1 = 10$ 、 $m_2 = 1$ である場合、トランジスタのサイズは、大きい順に $n_1 - fin \times m_1 > n_2 - fin \times m_1 > n_2 - fin \times m_2$ である。例えば、 $n_2 - fin \times m_2$ トランジスタのサイズは、図1のスタンダードセル領域SCAの論理回路に使用される複数種のトランジスタのうちのいずれかのトランジスタのサイズと同じである。

**【0031】**

メインバッファ部MBUFおよびサブバッファ部SBUFは、図2に示した電源スイッチ制御回路PCNT1に含まれる。メインバッファ部MBUFは、メイントランジスタMTrおよび付加トランジスタATr1、ATr2の動作を制御し、サブバッファ部SBUFは、サブトランジスタSTRの動作を制御する。なお、付加トランジスタATr1、ATr2は、サブバッファ部SBUFにより制御されてもよい。

10

**【0032】**

ウェルタップWLTは、pチャネルトランジスタが形成されるウェル領域に電源電圧VDDを供給する。2つのエンドキャップECApは、図3の横方向であるX方向の両端に配置される。

**【0033】**

この実施形態では、半導体装置100のレイアウトルールにより、 $n_1 - fin \times m_1$ トランジスタのX方向の端と、電源スイッチ回路PPSWのレイアウト領域の端とは間隔SP1以上離される。間隔SP1のルールは、電源スイッチ回路PPSWに隣接する他の回路といった外部要因からの影響により $n_1 - fin \times m_1$ トランジスタのゲート電極等の形状が、半導体装置100の製造時にばらつくことを抑制し、トランジスタの電気的特性のばらつきを抑制するために設定される。

30

**【0034】**

例えば、エンドキャップECApのX方向の幅は、間隔SP1より小さく、エンドキャップECApと $n_1 - fin \times m_1$ トランジスタとの間には空き領域が発生する。この実施形態では、この空き領域に電源スイッチとして機能する付加トランジスタATr1が配置される。また、電源スイッチ回路PPSWの他の空き領域（この例では、メインバッファ部MBUFとサブバッファ部SBUFとの間）にも電源スイッチとして機能する付加トランジスタATr2が配置される。

40

**【0035】**

このように、メイントランジスタMTr、サブトランジスタSTRおよび付加トランジスタATr1、ATr2は、電源線VDDを仮想電源線VVDDに接続する電源スイッチとして機能する。したがって、電源スイッチ回路PPSWにおいて、レイアウトルールの制約（間隔SP1）により発生する空き領域に配置される付加トランジスタATr1により、電源スイッチ回路PPSWの電源供給能力を向上することができる。

**【0036】**

この際、付加トランジスタATr1は、スタンダードセル領域SCAに配置される論理回路に使用される $n_2 - fin \times m_2$ トランジスタと同じ構造を有する。このため、電源スイッチ回路PPSWに隣接する回路のゲート電極等の形状のばらつきの抑制に寄与することができる。

50

**【 0 0 3 7 】**

また、電源スイッチ回路 P P S Wにおいて、回路レイアウトの都合により発生する空き領域に配置される付加トランジスタ A T r 2により、電源スイッチ回路 P P S Wの電源供給能力を向上することができる。この結果、電源スイッチ回路 P P S Wのレイアウト面積を増加させることなく電源供給能力を向上することができる。

**【 0 0 3 8 】**

すなわち、空き領域に付加トランジスタ A T r 1、A T r 2を配置することで、電源スイッチ回路 P P S Wのレイアウト面積の増大を抑制しつつ、p チャネルトランジスタ P T 1の電源供給能力を向上させることができる。

**【 0 0 3 9 】**

図 4 は、図 3 の電源スイッチ回路 P P S Wの電源配線のレイアウトの一例を示す。図 4 は、図 3 の電源スイッチ回路 P P S Wにおいて、メイントランジスタ M T r から右側のダブルハイセル分のレイアウトを示す。以下では、電源スイッチ回路 P P S Wの外部から配線される仮想電源線 V V D D および接地線 V S S は、電源線 V V D D 、 V S S とも称する。電源スイッチ回路 P P S W内に閉じている仮想電源線 V V D D および電源線 V D D は、それぞれ配線 V V D D 、 V D D とも称する。図 4 の例では、n<sub>1</sub> = 8 、 n<sub>2</sub> = 3 、 m<sub>1</sub> = 10 、 m<sub>2</sub> = 1 である。

**【 0 0 4 0 】**

2 本の電源線 V V D D および 1 本の電源線 V S S は、M 0 層を使用して形成される。M 0 層は、半導体基板に最も近い金属配線層であり、M 0 層の配線は、X 方向（図 4 の横方向）に延在する。各電源線 V V D D と電源線 V S Sとの間には、M 0 層を使用して配線 V D D 、 V V D D および信号線 S I G が形成される。例えば、信号線 S I G は、図 2 に示した p チャネルトランジスタ P T 1 のゲート配線である。

**【 0 0 4 1 】**

Y 方向に延在するローカル配線 V D D は、ビアを介してM 0 層の配線 V D D に接続される。Y 方向は、X 方向と直交する第 2 方向の一例である。M 0 層の配線 V D D は、図示しないビアを介して上層の金属配線層を使用して形成される電源線 V D D に接続される。Y 方向に延在するローカル配線 V V D D は、ビアを介してM 0 層の配線 V V D D およびM 0 層の電源線 V V D D に接続される。なお、M 0 層の配線 V V D D および電源線 V V D D は、上層の金属配線層を使用して形成される電源線 V V D D に接続されてもよい。ローカル配線 V D D 、 V V D D は、Y 方向に延在するゲート電極 G の間に設けられる。

**【 0 0 4 2 】**

フィンは、X 方向に延在し、Y 方向に間隔を置いて配列される。例えば、n<sub>2</sub> - f i n × m<sub>1</sub> トランジスタは、X 方向の両側にダミーゲート電極 D M Y G を有するため、m<sub>1</sub> + 2 本のゲート電極を有する。n<sub>2</sub> - f i n × m<sub>2</sub> トランジスタは、X 方向の両側にダミーゲート電極 D M Y G を有するため、m<sub>2</sub> + 2 本のゲート電極を有する。図 4 に示す例では、エンドキャップ E C A P は、3 本のダミーゲート電極 D M Y G と、ダミーゲート電極 D M Y G の間に配置されるダミーのローカル配線とを有する。

**【 0 0 4 3 】**

n<sub>2</sub> - f i n × m<sub>1</sub> トランジスタおよびn<sub>2</sub> - f i n × m<sub>2</sub> トランジスタにおいて、互いに隣接する 2 本のゲート電極 G の間には、ソース領域 S またはドレイン領域 D が形成される。ソース領域 S およびドレイン領域 D は、ゲート電極 G を挟んで交互に形成され、ソース領域 S には配線 V D D が接続され、ドレイン領域 D には、配線 V V D D が接続される。なお、f i n F E T では、ソース領域 S およびドレイン領域 D は、それぞれフィンに形成される。このため、ローカル配線 V D D は、ソース領域 S として機能するフィンに接続され、ローカル配線 V V D D は、ドレイン領域 D として機能するフィンに接続される。

**【 0 0 4 4 】**

図 5 は、図 4 のフィン、ゲート電極 G およびローカル配線のレイアウトを示す。ゲート電極 G およびローカル配線は、X 方向に延在するフィンを跨いで Y 方向に形成される。

**【 0 0 4 5 】**

10

20

30

40

50

図 6 は、図 3 および図 4 の  $n_2 - fin \times m_1$  トランジスタの構造の一例を示す。 $fin$  トランジスタは、半導体基板上に設けられた X 方向に延在するフィンと、フィンを跨いで Y 方向に延在するゲート電極 G を有する。フィンにおけるゲート電極 G と対向する部分には、ゲート絶縁膜が形成され、ゲート絶縁膜で覆われるフィンの表面部分にトランジスタのチャネルが形成される。

#### 【 0 0 4 6 】

そして、ソース領域 S とドレイン領域 D とが、フィンにおけるゲート電極 G の両側にそれぞれ設けられる。図示を省略しているが、各ソース領域 S および各ドレイン領域 D には、ゲート電極 G の延在方向に沿うローカル配線 VDD およびローカル配線 VVD がそれぞれ設けられる。図 4 に示した電源スイッチ回路 PPSW では、p チャネルトランジスタが形成され、ソース領域 S が配線 VDD に接続され、ドレイン領域 D が配線 VVD に接続される。なお、図 6 において、ソース領域 S とドレイン領域 D とが入れ替えられてもよい。

10

#### 【 0 0 4 7 】

図 7 は、図 4 の Y1 - Y1' 線に沿う断面を示す。フィンは、半導体基板上に形成された STI (Shallow Trench Isolation) 等の素子分離絶縁膜中に形成される。素子分離絶縁膜上に突出するフィンの上部は、図 7 に示す断面では、ローカル配線 VVD で覆われる。図 7 に示す断面では、各ローカル配線 VVD は、ビアを介して、M0 層に形成された電源線 VVD および配線 VVD に接続される。各ローカル配線 VVD 、各ビアおよび M0 層に形成される各配線 VVD 、 VD は、層間絶縁膜によりそれぞれ電気的に分離される。

20

#### 【 0 0 4 8 】

図 8 は、図 4 の X1 - X1' 線に沿う断面を示す。図 8 に示す断面では、フィンの上にローカル配線およびゲート電極が交互に形成される。また、ローカル配線のうち、図示しないトランジスタのドレイン領域に接続されるローカル配線は、M0 層に形成される配線 VVD に接続される。

#### 【 0 0 4 9 】

図 9 は、図 1 のスタンダードセル領域 SCA に設けられる電源スイッチ回路 SPSW のレイアウトの一例を示す。図 3 と同様の要素については、同じ符号を付し、詳細な説明は省略する。スタンダードセル領域 SCA に設けられる電源スイッチ回路 SPSW は、エンドキャップ ECAP を持たず、レイアウトルールで定義される間隔 SP1 が不要となる。

30

#### 【 0 0 5 0 】

ただし、例えば、電源スイッチ回路 SPSW がスタンダードセル領域 SCA を囲んで配置されるエンドキャップ ECAP と隣接する場合、電源スイッチ回路 SPSW とエンドキャップ ECAP との間に間隔 SP1 を設ける必要が生じる。このような場合、図 9 の例に示すように、間隔 SP1 に付加トランジスタ AT r1 ( $n_2 - fin \times m_2$  トランジスタ) を配置する。なお、電源スイッチ回路 SPSW がスタンダードセル領域 SCA を囲んで配置されるエンドキャップ ECAP と離れて配置される場合、間隔 SP1 および間隔 SP1 に配置される付加トランジスタ AT r1 の配置を省略してもよい。

40

#### 【 0 0 5 1 】

電源スイッチ回路 SPSW のその他の構成は、図 3 の電源スイッチ回路 PPSW の構成と同様である。電源スイッチ回路 SPSW の他の空き領域（この例では、メインバッファ部 MBUF とサブバッファ部 SBUF との間）に電源スイッチとして機能する付加トランジスタ AT r2 ( $n_2 - fin \times m_2$  トランジスタ) が配置される。

#### 【 0 0 5 2 】

電源スイッチ回路 SPSW に設けられるメイントランジスタ MTr およびサブトランジスタ STr は、第 3 トランジスタの一例である。電源スイッチ回路 SPSW に設けられる付加トランジスタ AT r1 は、第 4 トランジスタの一例であり、付加トランジスタ AT r2 は、第 5 トランジスタの一例である。

#### 【 0 0 5 3 】

50

図3に示す電源スイッチ回路PPSWと同様に、電源スイッチ回路SPSWのメイントランジスタMTr、サブトランジスタSTrおよび付加トランジスタATr1、ATr2は、電源線VDDを仮想電源線VVDDに接続する電源スイッチとして機能する。したがって、電源スイッチ回路SPSWにおいて、レイアウトルールの制約(間隔SP1)により発生する空き領域に配置される付加トランジスタATr1により、電源スイッチ回路SPSWの電源供給能力を向上することができる。

#### 【0054】

この際、付加トランジスタATr1は、スタンダードセル領域SCAに配置される論理回路に使用される $n_2 - fin \times m_2$ トランジスタと同じ構造を有する。このため、エンドキャップECAと隣接する電源スイッチ回路SPSWは、スタンダードセル領域SCAの外部に配置される他の回路やその他パターンなどに起因するゲート電極等の形状のばらつきを抑制することができる。

10

#### 【0055】

また、電源スイッチ回路SPSWにおいて、回路レイアウトの都合により発生する空き領域に配置される付加トランジスタATr2により、電源スイッチ回路SPSWの電源供給能力を向上することができる。この結果、電源スイッチ回路SPSWのレイアウト面積を増加させることなく電源供給能力を向上することができる。

#### 【0056】

すなわち、空き領域に付加トランジスタATr1、ATr2を配置することで、電源スイッチ回路SPSWのレイアウト面積の増大を抑制しつつ、pチャネルトランジスタPT2の電源供給能力を向上させることができる。

20

#### 【0057】

図10は、他の電源スイッチ回路PSWの回路レイアウトの一例(比較例)を示す。図3と同様の要素については、同じ符号を付し、詳細な説明は省略する。図10に示す電源スイッチ回路PSWは、図3の電源スイッチ回路PPSWの付加トランジスタATr1、ATr2の配置領域にトランジスタが配置されず、空き領域E1、E2になっている。この場合、電源スイッチ回路PSWの電源供給能力は、図3の電源スイッチ回路PPSWおよび図9の電源スイッチ回路SPSWより低下する。

#### 【0058】

以上、この実施形態では、電源スイッチ回路PPSW、SPSWの各々において、レイアウトルールの制約(間隔SP1)により発生する空き領域に付加トランジスタATr1が配置される。これにより、電源スイッチ回路PPSW、SPSWのレイアウト面積を増加させることなく電源供給能力を向上することができる。換言すれば、レイアウトルールの制約により、電源スイッチ回路内PPSW、SPSWに空き領域が必要な場合にも、電源供給能力の低下を抑制することができる。

30

#### 【0059】

付加トランジスタATr1は、スタンダードセル領域SCAに配置される論理回路に使用される $3fin \times 1$ トランジスタと同じ構造を有する。このため、電源スイッチ回路PPSW、SPSWに隣接する回路のゲート電極等の形状のばらつきの抑制に寄与することができる。

40

#### 【0060】

また、電源スイッチ回路PPSW、SPSWにおいて、回路レイアウトの都合により発生する空き領域に配置される付加トランジスタATr2により、電源スイッチ回路PPSW、SPSWの電源供給能力を向上することができる。これにより、電源スイッチ回路PPSW、SPSWのレイアウト面積を増加させることなく電源供給能力を向上することができる。

#### 【0061】

(第2の実施形態)

図11は、第2の実施形態における半導体装置のレイアウトの一例を示す。図1と同様の要素については、同じ符号を付し、詳細な説明は省略する。図10に示す半導体装置1

50

02は、例えば、図1に示したパワードメインPD1におけるX方向の左側に、パワードメインPD2、PD3を有する。

#### 【0062】

パワードメインPD2は、パワードメインPD1と同様の回路がレイアウトされる。パワードメインPD3は、半導体装置102に電源が供給されている間に常時動作する回路がレイアウトされるため、電源スイッチ回路PPSW、SPSWは配置されない。

#### 【0063】

以上、この実施形態では、複数のパワードメインPD1、PD2、PD3が互いに隣接する場合にも、上述した実施形態と同様に、電源スイッチ回路PPSW、SPSWのレイアウト面積を増加させることなく電源供給能力を向上することができる。

10

#### 【0064】

##### (第3の実施形態)

図12は、第3の実施形態における半導体装置のレイアウトの一例を示す。図1と同様の要素については、同じ符号を付し、詳細な説明は省略する。図11に示す半導体装置104は、周辺領域PAにRAMとアナログIPとが配置される。

#### 【0065】

半導体装置104において、アナログIP以外の回路は、半導体装置104に電源が供給されている間に常時動作する。このため、アナログIPのX方向の両側に電源スイッチ回路PPSWが配置され、アナログIPと電源スイッチ回路PPSWとは、パワードメインPD4に属する。

20

#### 【0066】

以上、この実施形態においても、上述した実施形態と同様に、電源スイッチ回路PPSWのレイアウト面積を増加させることなく電源供給能力を向上することができる。

#### 【0067】

##### (第4の実施形態)

図13は、第4の実施形態における半導体装置のレイアウトの一例を示す。図1と同様の要素については、同じ符号を付し、詳細な説明は省略する。図13に示す半導体装置106は、RAMに隣接する領域に、Y方向にそれぞれ配列される複数の電源スイッチ回路PPSWを含む2つの電源スイッチ回路列が設けられる。すなわち、半導体装置106は、図1の半導体装置100に比べて、電源スイッチ回路PPSWの数が増えている。半導体装置106のその他の構成は、図1の半導体装置100の構成と同様である。

30

#### 【0068】

以上、この実施形態においても、上述した実施形態と同様に、電源スイッチ回路PPSWのレイアウト面積を増加させることなく電源供給能力を向上することができる。さらに、この実施形態では、半導体装置106のパワードメインPD1内に空き領域がある場合、空き領域を利用して電源スイッチ回路PPSWを追加することで、パワードメインPD1での電源供給能力をさらに向上することができる。

#### 【0069】

##### (第5の実施形態)

図14は、第5の実施形態における半導体装置のレイアウトの一例を示す。図1と同様の要素については、同じ符号を付し、詳細な説明は省略する。図14に示す半導体装置108は、スタンダードセル領域SCAの周囲に設けられる電源スイッチ領域に配置される複数種の電源スイッチ回路PPSW(PPSWa、PPSWb、PPSWc)を有する。スタンダードセル領域SCAには、図1に示した電源スイッチ回路SPSWが配置されない。このため、スタンダードセル領域SCAに配置される回路の動作電源である電源VVDDは、図示しない上層の配線層を介して電源スイッチ回路PPSWから供給される。

40

#### 【0070】

電源スイッチ回路PPSWaは、スタンダードセル領域SCAにおけるX方向の両側に配置される。電源スイッチ回路PPSWaは、X方向の中央部に配置される $n_2 - fin \times m_1$ トランジスタおよび $n_1 - fin \times m_1$ トランジスタを有する。また、電源スイッチ

50

回路 P P S W a は、 $n_2 - f_{in} \times m_1$  トランジスタおよび $n_1 - f_{in} \times m_1$  トランジスタのゲート電極の配列方向である X 方向の両側に配置された $n_2 - f_{in} \times m_2$  トランジスタとエンドキャップ E C A P を有する。

#### 【 0 0 7 1 】

$n_2 - f_{in} \times m_2$  トランジスタは、 $n_2 - f_{in} \times m_1$  トランジスタおよび $n_1 - f_{in} \times m_1$  トランジスタに隣接して設けられる。エンドキャップ E C A P は、 $n_2 - f_{in} \times m_2$  トランジスタにおける $n_2 - f_{in} \times m_1$  トランジスタおよび $n_1 - f_{in} \times m_1$  トランジスタと反対側に配置される。そして、エンドキャップ E C A P と、エンドキャップ E C A P に隣接する $n_2 - f_{in} \times m_2$  トランジスタとにより、レイアウトルールで定義される間隔 S P 1 が確保される。

10

#### 【 0 0 7 2 】

電源スイッチ回路 P P S W b は、スタンダードセル領域 S C A の周囲の角部に配置される。電源スイッチ回路 P P S W b の周辺部には、電源スイッチ回路 P P S W c 側の端部を除いて、エンドキャップ E C A P が配置される。そして、電源スイッチ回路 P P S W b は、X 方向の端に配置されたエンドキャップ E C A P に隣接する $n_2 - f_{in} \times m_2$  トランジスタと、 $n_2 - f_{in} \times m_2$  トランジスタの列に隣接して配置された $n_1 - f_{in} \times m_1$  トランジスタおよび $n_2 - f_{in} \times m_1$  トランジスタとを有する。電源スイッチ回路 P P S W b においても、エンドキャップ E C A P と、エンドキャップ E C A P に隣接する $n_2 - f_{in} \times m_2$  トランジスタとにより間隔 S P 1 が確保される。

#### 【 0 0 7 3 】

電源スイッチ回路 P P S W c は、スタンダードセル領域 S C A における Y 方向の両側に配置される。電源スイッチ回路 P P S W c は、電源スイッチ回路 P P S W b から、 $n_2 - f_{in} \times m_2$  トランジスタと、 $n_2 - f_{in} \times m_2$  トランジスタの X 方向に隣接するエンドキャップ E C A P とを取り除いた構成を有する。

20

#### 【 0 0 7 4 】

なお、各電源スイッチ回路 P P S W a、P P S W b、P P S W c は、メインバッファ部 M B U F およびサブバッファ部 S B U F を持たなくてもよい。この場合、図 2 に示した電源スイッチ制御回路 P C N T 1 は、各電源スイッチ回路 P P S W a、P P S W b、P P S W c の外部に設けられる。

#### 【 0 0 7 5 】

30

以上、この実施形態においても、上述した実施形態と同様に、電源スイッチ回路 P P S W のレイアウト面積を増加させることなく電源供給能力を向上することができる。さらに、この実施形態では、スタンダードセル領域 S C A の周囲に電源スイッチ回路 P P S W a、P P S W b、P P S W c を配置することで、スタンダードセル領域 S C A 内の電源スイッチ回路 S P S W を不要にすることできる。したがって、スタンダードセル領域 S C A 内の論理回路間を、電源スイッチ回路 S P S W に影響されることなく接続することができ、信号の伝搬遅延時間を最小限にすることができる。この結果、半導体装置 1 0 8 の性能向上に寄与することができる。

#### 【 0 0 7 6 】

( 第 6 の実施形態 )

40

図 1 5 は、第 6 の実施形態における半導体装置のレイアウトの一例を示す。図 1 および図 1 4 と同様の要素については、同じ符号を付し、詳細な説明は省略する。図 1 5 に示す半導体装置 1 1 0 は、スタンダードセル領域 S C A の Y 方向の一方に隣接して設けられる電源スイッチ領域に配置される複数種の電源スイッチ回路 P P S W ( P P S W b、P P S W c、P P S W d、P P S W e ) を有する。図 1 4 と同様に、スタンダードセル領域 S C A には、図 1 に示した電源スイッチ回路 S P S W が配置されない。このため、スタンダードセル領域 S C A に配置される回路の動作電源である電源 V V D D は、図示しない上層の配線層を介して電源スイッチ回路 P P S W から供給される。

#### 【 0 0 7 7 】

この実施形態では、環状に配置される電源スイッチ回路 P P S W b、P P S W c、P P

50

$S_{Wd}$  の内側に電源スイッチ回路  $PPSW_e$  が配置される。電源スイッチ回路  $PPSW_b$ 、 $PPSW_c$  は、図 14 の電源スイッチ回路  $PPSW_b$ 、 $PPSW_c$  と同じ構成を有する。

#### 【0078】

電源スイッチ回路  $PPSW_d$  は、X 方向の左側に配置される  $n_2 - fin \times m_1$  トランジスタおよび  $n_1 - fin \times m_1$  トランジスタを有する。また、電源スイッチ回路  $PPSW_d$  は、X 方向において電源スイッチ回路  $PPSW_e$  の反対側に順次に配置された  $n_2 - fin \times m_2$  トランジスタとエンドキャップ  $ECAp$  を有する。

#### 【0079】

そして、 $n_2 - fin \times m_2$  トランジスタと、 $n_2 - fin \times m_2$  トランジスタに隣接するエンドキャップ  $ECAp$  により間隔  $SP_1$  が確保される。電源スイッチ回路  $PPSW_d$  は、図 14 の電源スイッチ回路  $PPSW_a$  から、 $n_2 - fin \times m_2$  トランジスタの 1 つ列と、1 つのエンドキャップ  $ECAp$  を削除した構成を有する。これは、電源スイッチ回路  $PPSW_d$  の X 方向の一端がスタンダードセル領域  $SCA$  に隣接しないためである。

#### 【0080】

電源スイッチ回路  $PPSW_e$  は、電源スイッチ回路  $PPSW_b$ 、 $PPSW_c$ 、 $PPSW_d$  の内側に配置されるため、間隔  $SP_1$  を確保するための  $n_2 - fin \times m_2$  トランジスタとエンドキャップ  $ECAp$  とは配置されない。このため、電源スイッチ回路  $PPSW_e$  は、 $n_2 - fin \times m_1$  トランジスタおよび  $n_2 - fin \times m_1$  トランジスタのみを有する。

#### 【0081】

以上、この実施形態においても、上述した実施形態と同様に、電源スイッチ回路  $PPSW$  のレイアウト面積を増加させることなく電源供給能力を向上することができる。

#### 【0082】

なお、上述した実施形態は、 $finFET$  を有する電源スイッチ回路  $PSW_1$ 、 $PSW_2$  に適用する例を述べたが、プレーナ型トランジスタ、ナノワイヤトランジスタ、ナノシートトランジスタ、フォークシートトランジスタ、 $CFeT$  (Complementary FET)、縦型ナノワイヤトランジスタなどを有する電源スイッチ回路に適用されてもよい。

#### 【0083】

以上、各実施形態に基づき本発明の説明を行ってきたが、上記実施形態に示した要件に本発明が限定されるものではない。これらの点に関しては、本発明の主旨をそこなわない範囲で変更することができ、その応用形態に応じて適切に定めることができる。

#### 【符号の説明】

#### 【0084】

100、102、104、106、108、110 半導体装置

A Tr 1、A Tr 2 付加トランジスタ

D ドレイン領域

E 1、E 2 領域

ECAp エンドキャップ

G ゲート電極

MBUF メインバッファ部

MTr メイントランジスタ

PA 周辺領域

PCNT 電源制御信号

PCNT 1、PCNT 2 電源スイッチ制御回路

PD、PD 1、PD 2、PD 3、PD 4 パワードメイン

PPSW、PPSWa、PPSWb 電源スイッチ回路

PPSWc、PPSWd、PPSWe 電源スイッチ回路

PT 1、PT 2 p チャネルトランジスタ

S ソース領域

SBUF サブバッファ部

10

20

30

40

50

S C A スタンダードセル領域

S I G 信号線

S P 1 間隔

S P S W 電源スイッチ回路

S T r サブトランジスタ

V D D 電源線

V S S 電源線（接地線）

V V D D 仮想電源線

W L T ウェルタップ

【図面】

【図 1】

第1の実施形態の半導体装置のレイアウトの一例を示す図

【図 2】

図1の電源スイッチ回路SPSW、PPSWの一例を示すブロック図

10

20

30

40

50

【図3】

図1の周辺領域に設けられる電源スイッチ回路のレイアウトの一例を示す図

【図4】

図3の電源スイッチ回路PPSWの電源配線のレイアウトの一例を示す図

【図5】

図4のFin、ゲート電極およびローカル配線のレイアウトを示す図

【図6】

図3および図4のn<sub>2</sub>-fin x m<sub>1</sub>トランジスタの構造の一例を示す斜視図

10

20

30

40

50

【 四 7 】

【 四 8 】

図4のY1-Y1'線に沿う断面を示す図

図4のX1-X1' 線に沿う断面を示す図

10

20

【図9】

【 図 1 0 】

図1のスタンダードセル領域に設けられる電源スイッチ回路のレイアウトの一例を示す図

他の電源スイッチ回路の回路レイアウトの一例(比較例)を示す図

30

40

【図 1 1】

第2の実施形態における半導体装置のレイアウトの一例を示す図

【図 1 2】

第3の実施形態における半導体装置のレイアウトの一例を示す図

10

20

【図 1 3】

【図 1 4】

30

40

50

【図15】

10

20

30

40

50

---

フロントページの続き

神奈川県横浜市港北区新横浜二丁目10番23 株式会社ソシオネクスト内

審査官 石川 雄太郎

(56)参考文献 特開2008-251835 (JP, A)

特開2009-289797 (JP, A)

特開2020-004763 (JP, A)

特開2008-103569 (JP, A)

米国特許出願公開第2016/0189759 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

H01L 21/82

H01L 21/822

H01L 21/8238

H01L 27/04

H01L 27/092