(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4568595号

(P4568595)

(45) 発行日 平成22年10月27日(2010.10.27)

(24) 登録日 平成22年8月13日(2010.8.13)

(51) Int.Cl.

F 1

H03K 3/03 (2006.01)

H03K 3/354 (2006.01)H03K 3/03

H03K 3/354

Z

請求項の数 6 (全 24 頁)

(21) 出願番号 特願2004-357869 (P2004-357869)

(22) 出願日 平成16年12月10日 (2004.12.10)

(65) 公開番号 特開2006-166305 (P2006-166305A)

(43) 公開日 平成18年6月22日 (2006.6.22)

審査請求日 平成18年12月13日 (2006.12.13)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100101454

弁理士 山田 卓二

(74) 代理人 100081422

弁理士 田中 光雄

(74) 代理人 100125874

弁理士 川端 純市

(74) 代理人 100098280

弁理士 石野 正弘

(72) 発明者 神戸 伸介

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体回路

## (57) 【特許請求の範囲】

## 【請求項 1】

電源電圧で駆動され、上記電源電圧に依存した電流を出力するとともに、上記電源電圧から所定の低下電圧だけ低下してなる基準電圧を出力し、互いに所定の時間間隔だけ遅延されて動作が開始される3以上の整数N個の電流源と、

上記N個の電流源からそれぞれ出力される電流により充電されるN個のコンデンサと、

セット信号に応答してセットされ、リセット信号に応答してリセットされ、上記リセットされた後上記セットされるまで出力信号を出力するN個のセットリセット型フリップフロップと、

N個のしきい値素子であって、上記N個のコンデンサから出力される信号電圧が所定のしきい値以上となったときそれぞれ、上記N個のしきい値素子のうち各1対のしきい値素子からのしきい値結果信号が互いに同時に出力されるしきい値結果信号を出力する上記N個のしきい値素子と、

上記N個のしきい値素子のうち、各1対のしきい値素子からのしきい値結果信号が互いに同時に出力されることを示す同時出力信号を、上記N個のセットリセット型フリップフロップのうちの対応する各1対のセットリセット型フリップフロップのセット信号とリセット信号として出力するN個のゲート素子と、

上記N個のセットリセット型フリップフロップから出力される出力信号に応答してそれぞれ上記N個のコンデンサを放電するN個の放電回路とを備え、

上記リセット信号に応答して、上記各コンデンサの電圧が上記各コンデンサの充電によ

り経過時間に実質的に比例して上昇し上記基準電圧に到達した後、上記セット信号に応答して、上記各コンデンサの放電により上記基準電圧から経過時間につれて下降する動作を上記各コンデンサにおいて上記時間間隔だけずれて繰り返すことにより、上記各セットリセット型フリップフロップからの出力信号をそれぞれ、所定の周期を有する発振信号として出力する発振回路を構成し、

上記各しきい値素子はインバータであり、上記各ゲート素子はノアゲートであることを特徴とする半導体回路。

【請求項 2】

電源電圧で駆動され、上記電源電圧に依存した電流を出力するとともに、上記電源電圧から所定の低下電圧だけ低下してなる基準電圧を出力し、互いに所定の時間間隔だけ遅延されて動作が開始される 3 以上の整数 N 個の電流源と、

上記 N 個の電流源からそれぞれ出力される電流により充電される N 個のコンデンサと、

セット信号に応答してセットされ、リセット信号に応答してリセットされ、上記リセットされた後上記セットされるまで出力信号を出力する N 個のセットリセット型フリップフロップと、

N 個のしきい値素子であって、上記 N 個のコンデンサから出力される信号電圧が所定のしきい値以上となったときそれぞれ、上記 N 個のしきい値素子のうち各 1 対のしきい値素子からのしきい値結果信号が互いに同時に出力されるしきい値結果信号を出力する上記 N 個のしきい値素子と、

上記 N 個のしきい値素子のうち、各 1 対のしきい値素子からのしきい値結果信号が互いに同時に出力されることを示す同時出力信号を、上記 N 個のセットリセット型フリップフロップのうちの対応する各 1 対のセットリセット型フリップフロップのセット信号とリセット信号として出力する N 個のゲート素子と、

上記 N 個のセットリセット型フリップフロップから出力される出力信号に応答してそれぞれ上記 N 個のコンデンサを放電する N 個の放電回路とを備え、

上記リセット信号に応答して、上記各コンデンサの電圧が上記各コンデンサの充電により経過時間に実質的に比例して上昇し上記基準電圧に到達した後、上記セット信号に応答して、上記各コンデンサの放電により上記基準電圧から経過時間につれて下降する動作を上記各コンデンサにおいて上記時間間隔だけずれて繰り返すことにより、上記各セットリセット型フリップフロップからの出力信号をそれぞれ、所定の周期を有する発振信号として出力する発振回路を構成し、

上記各しきい値素子はしきい値バッファであり、上記各ゲート素子は反転入力端子付きオアゲートであることを特徴とする半導体回路。

【請求項 3】

上記各電流源は、

第 1 と第 2 の P チャンネル M O S F E T を含むカレントミラー回路と、

第 1 の抵抗と、

第 2 の抵抗とを備え、

上記電源電圧と接地との間に、上記第 1 の P チャンネル M O S F E T と上記第 1 の抵抗が挿入され、

上記各電流源は上記電源電圧から上記第 1 の P チャンネル M O S F E T のしきい値電圧だけ低下した電圧値である上記第 1 の抵抗の両端の電圧を基準電圧として出力し、

上記各電流源は、上記電源電圧から上記第 2 の P チャンネル M O S F E T 及び上記第 2 の抵抗を介して電流を上記コンデンサに出力することを特徴とする請求項 1 又は 2 記載の半導体回路。

【請求項 4】

上記各電流源は、

第 1 と第 2 の N チャンネル M O S F E T を含む第 1 のカレントミラー回路と、

第 1 と第 2 の P チャンネル M O S F E T を含む第 2 のカレントミラー回路と、

第 1 の抵抗と、

10

20

30

40

50

第 2 の抵抗とを備え、

上記第 1 のカレントミラー回路と、上記第 2 のカレントミラー回路とが縦続に接続され、

上記電源電圧と接地との間に、上記第 1 の抵抗と上記第 1 の N チャンネル M O S F E T が挿入され、

上記各電流源は、上記電源電圧から上記第 1 の抵抗を介して低下した電圧値である上記第 1 の N チャンネル M O S F E T の両端の電圧を、上記第 2 の N チャンネル M O S F E T を介して出力した電圧を基準電圧として出力し、

上記各電流源は、上記電源電圧から上記第 2 の P チャンネル M O S F E T 及び上記第 2 の抵抗を介して電流を上記コンデンサに出力することを特徴とする請求項 1 又は 2 記載の半導体回路。

#### 【請求項 5】

上記各電流源は、

第 1 と第 2 の P チャンネル M O S F E T を含む第 1 のカレントミラー回路と、

第 1 と第 2 の N チャンネル M O S F E T を含む第 2 のカレントミラー回路と、

第 3 と第 4 の P チャンネル M O S F E T を含む第 3 のカレントミラー回路と、

第 1 の抵抗と、

第 2 の抵抗とを備え、

上記第 1 のカレントミラー回路と、上記第 2 のカレントミラー回路と、上記第 3 のカレントミラー回路とが縦続に接続され、

上記電源電圧と接地との間に、上記第 1 の P チャンネル M O S F E T と上記第 1 の抵抗が挿入され、

上記各電流源は、上記電源電圧から上記第 1 の P チャンネル M O S F E T のしきい値電圧だけ低下した値である上記第 1 の抵抗の両端の電圧を、上記第 2 の P チャンネル M O S F E T 及び上記第 2 のカレントミラー回路を介して出力した電圧を基準電圧として出力し、

上記各電流源は、上記電源電圧から上記第 4 の P チャンネル M O S F E T 及び上記第 2 の抵抗を介して電流を上記コンデンサに出力することを特徴とする請求項 1 又は 2 記載の半導体回路。

#### 【請求項 6】

上記各放電回路は、N チャンネル M O S F E T で構成されたことを特徴とする請求項 1 乃至 5 のうちいずれか 1 つに記載の半導体回路。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、例えば C M O S 回路などで形成された、例えばタイマー回路や発振回路などの半導体回路に関する。

##### 【背景技術】

##### 【0002】

例えば、特許文献 1 において、タイマー回路及び当該タイマー回路を内蔵した半導体記憶装置が開示されている。当該タイマー回路では、温度の上昇に伴ってタイマー周期が減少する傾向を示し、温度の低下に伴ってタイマー周期が増加する傾向を示すタイマー回路を提供するために、以下の構成を有している。ダイオードは、温度に依存した電流特性を有し、この順方向電流は、カレントミラーの一次側を構成する n 型 M O S トランジスタ N 1 を流れる。この n 型 M O S トランジスタ N 1 を流れる電流に応じて、カレントミラーの二次側を構成する p 型 M O S トランジスタ P 2 及び n 型 M O S トランジスタ N 3 を流れる電流が定まる。これら p 型 M O S トランジスタ P 2 及び n 型 M O S トランジスタ N 3 を流れる電流は、インバータ I 1 乃至 I 3 からなるリングオシレータの動作電流として供給される。従って、このリングオシレータから出力されるクロック信号 C L K の周期（タイマー周期）には、ダイオード D の温度特性が反映され、温度の上昇に伴ってタイマー周期が

10

20

30

40

50

減少する。

【0003】

【特許文献1】特開2002-117671号公報。

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、従来技術の発振回路では、電源電圧が低下したときは、所定の周期を保持して安定に動作することができないという問題点があった。

【0005】

本発明の目的は以上の問題点を解決し、より低い電圧から広範囲の電源電圧範囲で安定に動作することができる、発振回路である半導体回路を提供することにある。

10

【課題を解決するための手段】

【0006】

本発明に係る半導体回路は、電源電圧で駆動され、上記電源電圧に依存した電流を出力するとともに、上記電源電圧から所定の低下電圧だけ低下してなる基準電圧を出力し、互いに所定の時間間隔だけ遅延されて動作が開始される3以上の整数N個の電流源と、

上記N個の電流源からそれぞれ出力される電流により充電されるN個のコンデンサと、

セット信号に応答してセットされ、リセット信号に応答してリセットされ、上記リセットされた後上記セットされるまで出力信号を出力するN個のセットリセット型フリップフロップと、

20

N個のしきい値素子であって、上記N個のコンデンサから出力される信号電圧が所定のしきい値以上となったときそれぞれ、上記N個のしきい値素子のうち各1対のしきい値素子からのしきい値結果信号が互いに同時に出力されるしきい値結果信号を出力する上記N個のしきい値素子と、

上記N個のしきい値素子のうち、各1対のしきい値素子からのしきい値結果信号が同時に出力されることを示す同時出力信号を、上記N個のセットリセット型フリップフロップのうちの対応する各1対のセットリセット型フリップフロップのセット信号とリセット信号として出力するN個のゲート素子と、

上記N個のセットリセット型フリップフロップから出力される出力信号に応答してそれぞれ上記N個のコンデンサを放電するN個の放電回路とを備え、

30

上記リセット信号に応答して、上記各コンデンサの電圧が上記各コンデンサの充電により経過時間に実質的に比例して上昇し上記基準電圧に到達した後、上記セット信号に応答して、上記各コンデンサの放電により上記基準電圧から経過時間につれて下降する動作を上記各コンデンサにおいて上記時間間隔だけずれて繰り返すことにより、上記各セットリセット型フリップフロップからの出力信号をそれぞれ、所定の周期を有する発振信号として出力する発振回路を構成し、

上記各しきい値素子はインバータであり、上記各ゲート素子はノアゲートであることを特徴とする。

また、本発明に係る半導体回路は、電源電圧で駆動され、上記電源電圧に依存した電流を出力するとともに、上記電源電圧から所定の低下電圧だけ低下してなる基準電圧を出力し、互いに所定の時間間隔だけ遅延されて動作が開始される3以上の整数N個の電流源と

40

上記N個の電流源からそれぞれ出力される電流により充電されるN個のコンデンサと、

セット信号に応答してセットされ、リセット信号に応答してリセットされ、上記リセットされた後上記セットされるまで出力信号を出力するN個のセットリセット型フリップフロップと、

N個のしきい値素子であって、上記N個のコンデンサから出力される信号電圧が所定のしきい値以上となったときそれぞれ、上記N個のしきい値素子のうち各1対のしきい値素子からのしきい値結果信号が互いに同時に出力されるしきい値結果信号を出力する上記N個のしきい値素子と、

50

上記N個のしきい値素子のうち、各1対のしきい値素子からのしきい値結果信号が同時に

出力されることを示す同時出力信号を、上記N個のセットリセット型フリップフロップの

うちの対応する各1対のセットリセット型フリップフロップのセット信号とリセット信

号として出力するN個のゲート素子と、

上記N個のセットリセット型フリップフロップから出力される出力信号に応答してそれ

ぞれ上記N個のコンデンサを放電するN個の放電回路とを備え、

上記リセット信号に応答して、上記各コンデンサの電圧が上記各コンデンサの充電によ

り経過時間に実質的に比例して上昇し上記基準電圧に到達した後、上記セット信号に応答

して、上記各コンデンサの放電により上記基準電圧から経過時間につれて下降する動作を

上記各コンデンサにおいて上記時間間隔だけずれて繰り返すことにより、上記各セットリ

セット型フリップフロップからの出力信号をそれぞれ、所定の周期を有する発振信号とし

て出力する発振回路を構成し、

上記各しきい値素子はしきい値バッファであり、上記各ゲート素子は反転入力端子付き

オアゲートであることを特徴とする。

**【発明の効果】**

**【0007】**

従って、本発明に係る半導体回路によれば、各電流源からの充電電流と、各電流源からの基準電圧を用いて、タイマー回路の動作を含む発振回路の動作を実行しているので、電源電圧が低下しても、電源電圧に依存した充電電流も小さくなる一方、電源電圧から低下電圧だけ低下してなる基準電圧も小さくなる。それ故、各コンデンサの各電圧がそれら充電により経過時間に実質的に比例して上昇し基準電圧に到達するまでの時間はほとんど変化しない。すなわち、電源電圧が低下しても発振回路の発振周期を保持しつつ動作できる。従って、より低い電圧から広範囲の電源電圧範囲で安定に動作することができる発振回路を提供できる。

10

**【発明を実施するための最良の形態】**

**【0008】**

以下、本発明に係る実施の形態について図面を参照して説明する。なお、同様の構成要素については同一の符号を付している。

**【0009】**

実施の形態1。

20

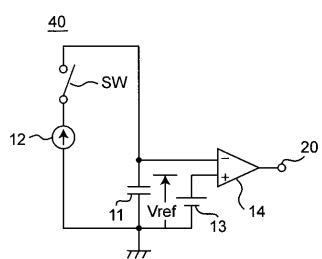

図1は本発明の実施の形態1に係る半導体回路であるタイマー回路40の構成を示す回路図である。

**【0010】**

図1において、タイマー回路40は、電流源12と、電流源12からの電流の供給をオン／オフするスイッチSWと、当該電流により電荷を充電するコンデンサ11と、基準電圧源13と、コンパレータ14とを備えて構成される。ここで、電流源12は、電源電圧Vccで駆動され、電源電圧Vccに依存した電流を出力するとともに、電源電圧Vccから所定の低下電圧だけ低下してなる基準電圧Vrefを出力する。電流源12の一端はスイッチSWを介してコンデンサ11の一端に接続され、電流源12の他端は接地される。また、コンデンサ11の一端はコンパレータ14の反転入力端子に接続され、コンデンサ11の他端は接地される。さらに、電流源12から供給される基準電圧Vrefを有する基準電圧源13の正極はコンパレータ14の非反転入力端子に接続され、基準電圧源13の負極は接地される。コンパレータ14において、反転入力端子に入力される電圧が基準電圧源13の基準電圧Vref以上となると、コンパレータ14からの出力信号は、例えば+5Vのハイレベルから、例えば0Vのローレベルに立ち下がる。なお、スイッチSWは、タイマー回路40に電源電圧Vccが供給されたときにオンとなる仮想的なスイッチである。

30

**【0011】**

以上のように構成されたタイマー回路40において、コンデンサ11に電荷が蓄積されていない状態で、タイマー回路40の電源電圧Vccが供給されてスイッチSWがオンさ

40

50

れたとき、電流源 12 から電流がコンデンサ 11 に流れ、コンデンサ 11 に電荷が蓄積される。そして、時間経過につれてコンデンサ 11 の両端電圧が経過時間に実質的に比例して上昇し、その電圧が基準電圧  $V_{ref}$  以上となったとき、コンパレータ 14 からの出力信号はハイレベルからローレベルに立ち下がる。すなわち、電源電圧  $V_{cc}$  の供給によるスイッチ SW のオン時から所定の時間だけ遅延した時刻でコンパレータ 14 からの出力信号はハイレベルからローレベルに立ち下がり、タイマー回路 40 として動作することになる。

#### 【0012】

すなわち、タイマー回路 40 においては、電源電圧  $V_{cc}$  で駆動され、電源電圧  $V_{cc}$  に依存した電流を出力するとともに、電源電圧  $V_{cc}$  から所定の低下電圧だけ低下してなる基準電圧  $V_{ref}$  を出力する電流源 12 を用いてコンデンサ 11 を充電し、コンデンサ 11 の電圧を、電流源 12 から出力される基準電圧  $V_{ref}$  と比較して、基準電圧  $V_{ref}$  以上となったとき、出力信号を出力するコンパレータ 14 を備え、電源電圧  $V_{cc}$  の供給開始から、コンデンサ 11 の電圧がその充電により経過時間に実質的に比例して上昇し基準電圧  $V_{ref}$  に到達するまでの遅延時間後に、出力信号を出力するタイマー回路 40 を構成している。それ故、電源電圧  $V_{cc}$  が低下しても、電源電圧  $V_{cc}$  に依存した充電電流も小さくなる一方、電源電圧  $V_{cc}$  から低下電圧だけ低下してなる基準電圧  $V_{ref}$  も小さくなるので、コンデンサ 11 の電圧がその充電により経過時間に実質的に比例して上昇し基準電圧  $V_{ref}$  に到達するまでの遅延時間はほとんど変化しない。すなわち、電源電圧  $V_{cc}$  が低下してもタイマー回路 40 の遅延時間を保持しつつ動作できる。従って、より低い電圧から広範囲の電源電圧範囲で安定に動作することができるタイマー回路 40 を提供できる。

#### 【0013】

なお、例えば、電流源 12 は電源電圧  $V_{cc}$  に依存しない一定電流を供給する回路が用いられる場合は、電流源 12 を半導体回路内に構成するためには最低でも 2 段のトランジスタ直列回路と抵抗又はダイオードといった能動素子のカスケード接続が必要であり、最低動作電圧を低く設定することはきわめて難しく、より広い電源電圧範囲で動作するタイマー回路を作成することは難しい。この問題点を解決するために、本発明者らは、図 1 のタイマー回路 40 の具体例を提案する。

#### 【0014】

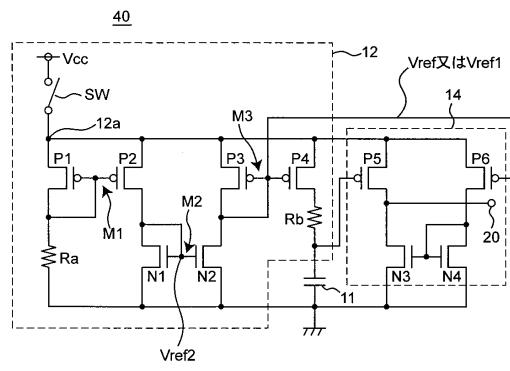

図 2 は図 1 のタイマー回路 40 の具体例を示す回路図である。図 2 において、タイマー回路 40 は、3 個のカレントミラー回路 M1, M2, M3 と抵抗 Ra, Rb を備えた電流源 12 と、コンデンサ 11 と、コンパレータ 14 とを備えて構成され、電流源 12 及びコンパレータ 14 は CMOS 回路で形成される。

#### 【0015】

図 2 において、電流源 12 は、スイッチ SW と、4 個の P チャンネル MOSFET P1 乃至 P4 と、2 個の N チャンネル MOSFET N1, N2 と、2 個の抵抗 Ra, Rb とを備えて構成される。ここで、1 対の P チャンネル MOSFET P1, P2 によりカレントミラー回路 M1 を構成し、1 対の N チャンネル MOSFET N1, N2 によりカレントミラー回路 M2 を構成し、1 対の P チャンネル MOSFET P3, P4 によりカレントミラー回路 M3 を構成し、これら 3 個のカレントミラー回路 M1, M2, M3 が縦続に接続されている。また、コンパレータ 14 は、2 個の P チャンネル MOSFET P5, P6 と、2 個の N チャンネル MOSFET N3, N4 とを備えて構成される。

#### 【0016】

電源電圧  $V_{cc}$  はスイッチ SW を介して電源接続点 12a に接続される。電源接続点 12a は、6 個の P チャンネル MOSFET P1 乃至 P6 の各ソースに接続される。また、4 個の N チャンネル MOSFET N1 乃至 N4 の各ソースは接地される。P チャンネル MOSFET P1, P2 の各ゲートは互いに接続されるとともに、P チャンネル MOSFET P1 のドレインに接続され、さらに、抵抗 Ra を介して接地される。また、P チャンネル MOSFET P2 のドレインは、N チャンネル MOSFET N1 のドレイン及びゲート

10

20

30

40

50

、並びにNチャンネルMOSFETN2のゲートに接続される。さらに、3個のPチャンネルMOSFETP3、P4、P6の各ゲートは互いに接続されるとともに、PチャンネルMOSFETP3のドレインに接続され、さらに、NチャンネルMOSFETN2のドレインに接続される。PチャンネルMOSFETP4のドレインは抵抗Rbを介してPチャンネルMOSFETP5のゲートに接続されるとともに、コンデンサ11を介して接地される。また、PチャンネルMOSFETP5のドレインはNチャンネルMOSFETN3のドレインに接続されるとともに、出力端子20に接続される。さらに、PチャンネルMOSFETP6のドレインはNチャンネルMOSFETN4のドレイン及びゲート、並びにNチャンネルMOSFETN3のゲートに接続される。

## 【0017】

10

以上のように構成された図2のタイマー回路40において、2個のPチャンネルMOSFETP1、P2からなるカレントミラー回路M1と、2個のPチャンネルMOSFETP3、P4からなるカレントミラー回路M2と、2個のNチャンネルMOSFETN1、N2からなる第3のカレントミラー回路M3と、2個の抵抗Ra、Rbとにより、電流源12の回路を構成している。また、2個のPチャンネルMOSFETP5、P6と、2個のNチャンネルMOSFETN3、N4とにより、コンパレータ14を構成している。

## 【0018】

図2のタイマー回路12において、電源電圧Vccが投入されてスイッチSWがオンされると、電源電圧VccからPチャンネルMOSFETP1と抵抗Raを介して接地に向けて電流が流れる。このとき、抵抗Raの両端に誘起される電圧は、電源電圧Vccから、ダイオード接続しているPチャンネルMOSFETP1のしきい値電圧分だけ減じた電圧値となり、上記抵抗Raに流れる電流は電源電圧Vccに実質的に比例して、すなわち電源電圧Vccに依存した電流となる。この電流を用いて、1対のPチャンネルMOSFETP1、P2で構成されるカレントミラー回路M1と、1対のNチャンネルMOSFETN1、N2で構成されるカレントミラー回路M2と、1対のPチャンネルMOSFETP3、P4で構成されるカレントミラー回路M3とを介して、電源電圧VccからPチャンネルMOSFETP4及び抵抗Rbを介してコンデンサ11に流れる充電電流を得る。従って、充電電流は、電源電圧Vccに依存して、電源電圧Vccに実質的に比例する電流となる。ここで、各カレントミラー回路M1、M2、M3のMOSFETの各ゲート幅を調整することにより、ユーザーが所望する充電電流を得ることができる。

20

## 【0019】

30

また、基準電圧Vrefは、カレントミラー回路M3における1対のPチャンネルMOSFETP3、P4のゲート電位から得ている。当該基準電圧VrefはPチャンネルMOSFETP3、P4のしきい値電圧分だけ低下してなる電圧値であり、電源電圧Vccの低下により低下する。なお、後述する実施の形態において、上記基準電圧Vrefを第1の基準電圧Vref1として用い、カレントミラー回路M2の1対のNチャンネルMOSFETN1、N2のゲート電位（当該MOSFETのしきい値電圧値である。）を、第1の基準電圧Vref1よりも低い第2の基準電圧Vref2として用いることができる。

## 【0020】

40

上述のように得られた電源電圧Vccに依存する電流にて、コンデンサ11の充電が進み、コンパレータ14の反転入力端子（PチャンネルMOSFETP5のゲート）の電位が基準電圧Vref以上になると出力端子20の電圧値が、電源電圧レベルであるハイレベルから接地電位であるローレベルまで反転する。

## 【0021】

このときの基準電圧Vrefの電位（PチャンネルMOSFETP3、P4のゲート電位）と、PチャンネルMOSFETP1のゲート電位とは、トランジスタのドレイン・ソース間電圧の変化によって実効チャネル長が変化するチャネル長変調効果を無視できるトランジスタ構成とすれば同じ電位となる。従って、この回路構成では、出力端子20における電圧の反転は、電源電圧Vccに依存した充電電流にて充電されたコンデンサ11が

50

、電源電圧  $V_{cc}$  から P チャンネル MOSFET P1 のしきい値電圧を減じた電圧値である基準電圧  $V_{ref}$  に到達することによって発生する。各 MOSFET のしきい値電圧が一定であれば、電源電圧  $V_{cc}$  が低下しても、電源電圧  $V_{cc}$  に依存した充電電流も小さくなる一方、電源電圧  $V_{cc}$  から低下電圧だけ低下してなる基準電圧  $V_{ref}$  も小さくなるので、コンデンサ 11 の電圧がその充電により経過時間に実質的に比例して上昇し基準電圧  $V_{ref}$  に到達するまでの遅延時間はほとんど変化しない。すなわち、電源投入から出力端子 20 の論理反転が発生するまでの遅延時間は、電源電圧  $V_{cc}$  の変動の影響を受けにくく、さらに、充電電流の発生源は、1つの P チャンネル MOSFET P1 と1つの抵抗  $R_a$  で構成されるため、比較的低い電圧での始動が可能となる。すなわち、電源電圧  $V_{cc}$  が低下してもタイマー回路 40 の遅延時間を保持しつつ動作でき、より低い電圧から広範囲の電源電圧範囲で安定に動作することができるタイマー回路 40 を提供できる。

10

#### 【0022】

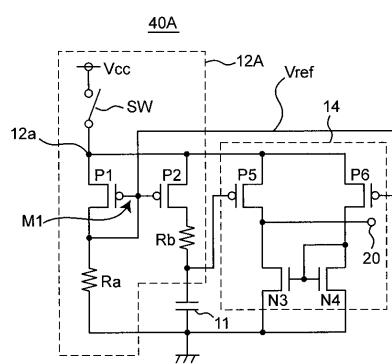

図 3 は図 2 のタイマー回路 40 の変形例 40A を示す回路図である。図 3 のタイマー回路 40A は、図 2 のタイマー回路 40 に比較して、電流源 12 においてカレントミラー回路 M2, M3 を省略したことを特徴としている。図 3 において、相違点について説明すると、充電電流は、電源電圧  $V_{cc}$  から P チャンネル MOSFET P2 及び抵抗  $R_b$  を介してコンデンサ 11 に流れる。以上のように構成しても、図 3 のタイマー回路 40A は、図 2 のタイマー回路 40 と同様に動作する。

#### 【0023】

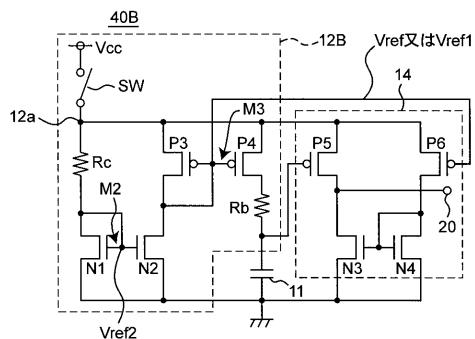

図 4 は図 1 のタイマー回路 40 の別の具体例 40B を示す回路図である。図 4 のタイマー回路 40B は、図 2 のタイマー回路 40 に比較して、2 個の P チャンネル MOSFET P1, P2 と、1 個の抵抗  $R_a$  からなる回路を、1 個の抵抗  $R_c$  で構成したことを特徴としている。以上のように構成しても、図 4 のタイマー回路 40B は、図 2 のタイマー回路 40 と同様に動作する。

20

#### 【0024】

以上説明したように、本発明の実施の形態 1 に係る半導体回路によれば、電源電圧  $V_{cc}$  が低下しても、電源電圧  $V_{cc}$  に依存した充電電流も小さくなる一方、電源電圧  $V_{cc}$  から低下電圧だけ低下してなる基準電圧  $V_{ref}$  も小さくなるので、コンデンサ 11 の電圧がその充電により経過時間に実質的に比例して上昇し基準電圧  $V_{ref}$  に到達するまでの遅延時間はほとんど変化しない。すなわち、電源電圧  $V_{cc}$  が低下してもタイマー回路 40 の遅延時間を保持しつつ動作できる。従って、より低い電圧から広範囲の電源電圧範囲で安定に動作することができるタイマー回路 40, 40A, 40B を提供できる。

30

#### 【0025】

実施の形態 2 。

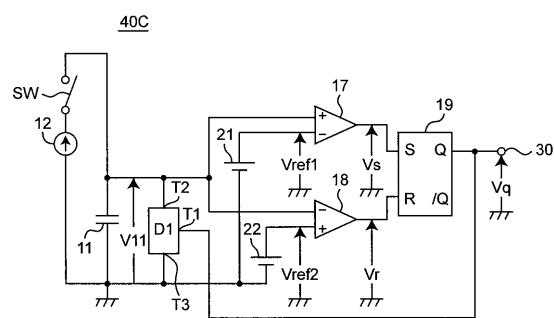

図 5 は本発明の実施の形態 2 に係る半導体回路である発振回路 40C の構成を示す回路図である。本実施の形態 2 に係る発振回路 40C は、図 1 のタイマー回路 40 を基礎とした CMOS 回路で形成された発振回路であって（実施の形態 3 乃至 5 も、同様に形成される CMOS 回路の発振回路である。）、図 1 のタイマー回路 40 に比較して、基準電圧源 13 を有するコンパレータ 14 に代えて、第 1 の基準電圧  $V_{ref1}$  を有する基準電圧源 21 を有するコンパレータ 17 と、第 2 の基準電圧  $V_{ref2}$  を有する基準電圧源 22 を有するコンパレータ 18 と、セットリセット型フリップフロップ 19 と、放電回路 D1 を備えて構成したことを特徴としている。なお、コンパレータ 17, 18 及びセットリセット型フリップフロップ 19 は例えば CMOS 回路で形成される。また、基準電圧源 21, 22 も、実施の形態 1 と同様に CMOS 回路で形成された電流源 12 又は 12B で発生され、具体的には、図 2 及び図 4 において図示された 2 個の基準電圧  $V_{ref1}$ ,  $V_{ref2}$  を用いる。

40

#### 【0026】

図 5 において、コンデンサ 11 の両端電圧を電圧  $V_{11}$  とし、その両端にそれぞれ放電回路 D1 の端子 T2, T3 が接続される。コンデンサ 11 の一端は、コンパレータ 17 の非反転入力端子及びコンパレータ 18 の反転入力端子に接続される。基準電圧源 21 から

50

の基準電圧  $V_{ref1}$  はコンパレータ 17 の反転入力端子に印加され、基準電圧源 22 からの基準電圧  $V_{ref2}$  はコンパレータ 18 の非反転入力端子に印加される。また、コンパレータ 17 からの出力信号の電圧  $V_s$  はセットリセット型フリップフロップ 19 のセット端子 S に入力され、コンパレータ 18 からの出力信号の電圧  $V_r$  はセットリセット型フリップフロップ 19 のリセット端子 R に入力される。ここで、セットリセット型フリップフロップ 19 は、非反転出力端子 Q と、反転出力端子 /Q (本願明細書及び図面において、/Q のうちの / は上側バーを示し、ローアクティブを示す。) とを有し、セット信号に応答してセットされ、リセット信号に応答してリセットされ、上記セットされた後上記リセットされるまで非反転出力端子 Q から出力信号  $V_q$  を出力するとともに、その反転信号を反転出力端子 /Q から出力する。ここで、セットリセット型フリップフロップ 19 の非反転出力端子 Q からの出力信号の電圧  $V_q$  は出力端子 30 に出力されるとともに、放電回路 D1 の制御端子 T1 に対して放電開始信号として印加される。

10

#### 【0027】

ここで、コンパレータ 17 は、非反転入力端子に入力される電圧  $V_{11}$  が基準電圧  $V_{ref1}$  以上となったとき、ハイレベルのパルス信号を出力し、また、コンパレータ 18 は、非反転入力端子に入力される電圧  $V_{11}$  が基準電圧  $V_{ref2}$  以下となったとき、ハイレベルのパルス信号を出力する。

#### 【0028】

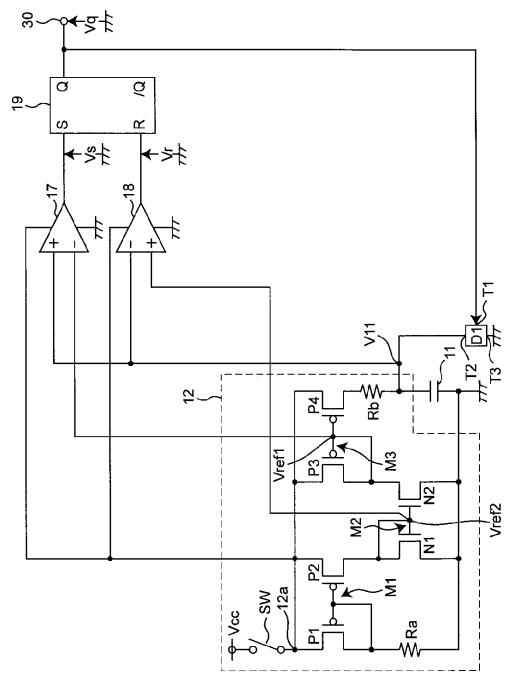

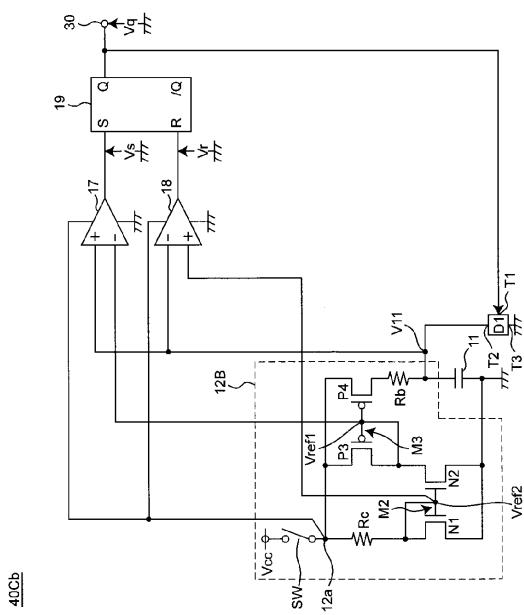

図 6 は、図 5 の発振回路 40C の第 1 の具体例 40Ca の構成を示す回路図である。図 6において、発振回路 40Ca は、図 2 の電流源 12 と、図 2 のコンパレータ 14 と同様の構成を有する 2 個のコンパレータ 17, 18 とを用いて構成したことを特徴としている。

20

#### 【0029】

図 6において、電流源 12 の電源接続点 12a はコンパレータ 17 の電源端子に接続されて電源電圧  $V_{cc}$  が供給され、また、コンパレータ 18 の電源端子にも接続されて電源電圧  $V_{cc}$  が供給される。電流源 12 の P チャンネル MOSFET P3, P4 の各ゲート電圧は基準電圧  $V_{ref1}$  としてコンパレータ 17 の反転入力端子に印加され、電流源 12 の N チャンネル MOSFET N1, N2 の各ゲート電圧は基準電圧  $V_{ref2}$  としてコンパレータ 18 の非反転入力端子に印加される。さらに、電流源 12 の P チャンネル MOSFET P4 のソースは抵抗 Rb 及びコンデンサ 11 を介して接地され、コンデンサ 11 の両端電圧  $V_{11}$  は、コンパレータ 17 の非反転入力端子に印加され、コンパレータ 18 の反転入力端子に印加され、放電回路 D1 の端子 T2 に印加される。コンパレータ 17 からの出力信号は、セットリセット型フリップフロップ 19 のセット端子 S に入力される。また、コンパレータ 18 からの出力信号は、セットリセット型フリップフロップ 19 のリセット端子 R に入力される。さらに、セットリセット型フリップフロップ 19 の非反転出力端子 Q からの出力信号は放電回路 D1 の制御端子 T1 に入力される。

30

#### 【0030】

図 7 は、図 5 の発振回路 40C の第 2 の具体例 40Cb の構成を示す回路図である。図 7において、発振回路 40Cb は、図 4 の電流源 12B と、図 4 のコンパレータ 14 と同様の構成を有する 2 個のコンパレータ 17, 18 とを用いて構成したことを特徴としている。すなわち、発振回路 40Cb は、図 6 の発振回路 40Ca に比較して、図 2 の電流源 12 に代えて、図 4 の電流源 12B を備えたことであり、その他の構成は、図 6 と同様である。

40

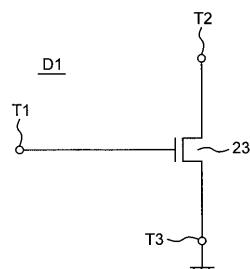

#### 【0031】

図 8 は図 5 乃至図 7 の放電回路 D1 の構成を示す回路図である。放電回路 D1 は、例えば、図 8 に示すように、CMOS 回路のうちの 1 個の N チャンネル MOSFET 23 で構成され、そのゲートは制御端子 T1 に接続され、ドレインは端子 T2 に接続され、ソースは接地された端子 T3 に接続される。以上のように構成された放電回路 D1 において、ハイレベル信号が制御端子 T1 を介して N チャンネル MOSFET 23 のゲートに印加されると、N チャンネル MOSFET 23 がオンとなり、端子 T2 と端子 T3 間で所定の抵

50

抗値を有する放電回路を構成する。

【0032】

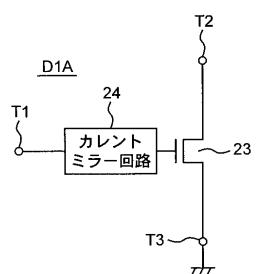

図9は図5乃至図7の放電回路D1の変形例D1Aの構成を示す回路図である。図9の放電回路D1Aは、図8の放電回路D1に比較して、制御端子T1と、NチャンネルMOSFET23のゲートとの間にカレントミラーリード回路24を挿入し、制御端子T1に入力される電圧信号に基づいて電流を発生してNチャンネルMOSFET23を電流で駆動するように構成したことを特徴としている。

【0033】

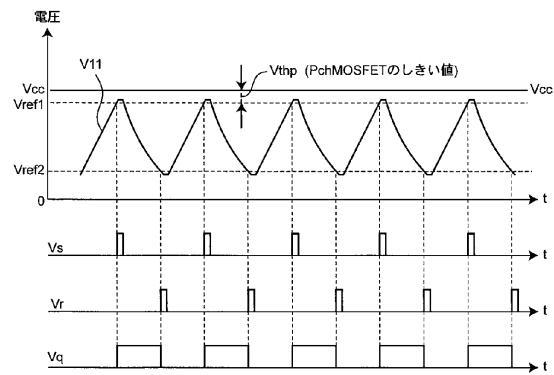

図10は、図5の発振回路40Cの動作を示すタイミングチャートである。なお、図5の発振回路40Cにおいて、図10に示すように、基準電圧Vref1は、電源電圧VccからPチャンネルMOSFETのしきい値電圧Vthpを減じた電圧に設定され、基準電圧Vref2は、基準電圧Vref1よりも低い電圧に設定される。

10

【0034】

図10から明らかなように、スイッチSWがオンされた後、コンデンサ11が充電され、コンデンサ11の両端電圧V11が基準電圧Vref1以上となったとき、コンパレータ17はハイレベルのパルス信号を出力し、これにより、セットリセット型フリップフロップ19はセットされ、非反転出力端子Qからハイレベル信号Vqが出力される。そのとき、当該ハイレベル信号に応答して、放電回路D1がオンされ、コンデンサ11に蓄積された電荷が、コンデンサ11と放電回路D1のNチャンネルMOSFET23の抵抗分とで決定される時定数で放電される。そして、コンデンサ11の両端電圧が基準電圧Vref2以下となったとき、コンパレータ18はハイレベルのパルス信号をセットリセット型フリップフロップ19のリセット端子Sに出力する。これに応答して、セットリセット型フリップフロップ19はリセットされ、非反転出力端子Qから信号Vqはローレベルとなる。これにより、放電回路D1への信号がローレベルになるので、放電回路D1がオフされ、放電回路D1の放電が終了する。次いで、また、コンデンサ11に対する充電が開始され、上述の動作が繰り返される。従って、図10から明らかなように、出力端子30からは、所定のパルス幅を有するハイレベル信号が所定の周期で出力され、すなわち、所定の発振信号が出力される。

20

【0035】

以上のように構成された図5の発振回路40Cにおいては、リセット信号に応答して、コンデンサ11の電圧がその充電により第2の基準電圧Vref2から経過時間に実質的に比例して上昇し第1の基準電圧Vref1に到達した後、セット信号に応答して、コンデンサ11の放電により第1の基準電圧Vref1から経過時間につれて下降して第2の基準電圧Vref2に到達する動作を繰り返すことにより、セットリセット型フリップフロップ19からの出力信号を、所定の周期を有する発振信号として出力することができる。

30

【0036】

以上説明したように、本発明の実施の形態2に係る半導体回路の発振回路40Cにおいても、実施の形態1の電流源12又は12Bからの充電電流と、電流源12又は12Bからの基準電圧Vref1を用いて、実施の形態1のタイマーリード回路の動作を含む発振回路の動作を実行しているので、電源電圧Vccが低下しても、電源電圧Vccに依存した充電電流も小さくなる一方、電源電圧Vccから低下電圧だけ低下してなる基準電圧Vref1も小さくなる。それ故、コンデンサ11の電圧がその充電により基準電圧Vref2から経過時間に実質的に比例して上昇し基準電圧Vref1に到達するまでの時間はほとんど変化しない。すなわち、電源電圧Vccが低下しても発振回路の発振周期を保持しつつ動作できる。従って、より低い電圧から広範囲の電源電圧範囲で安定に動作することができる発振回路を提供できる。

40

【0037】

実施の形態3.

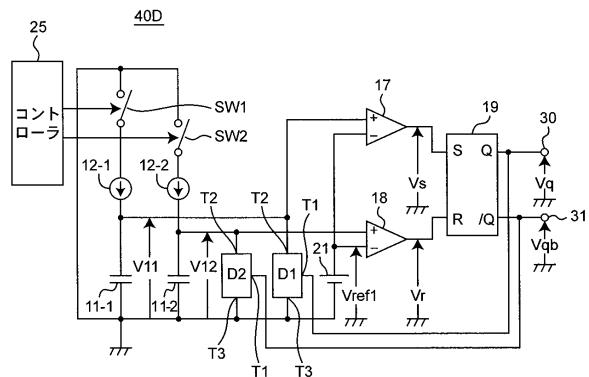

図11は本発明の実施の形態3に係る半導体回路である発振回路40Dの構成を示す回

50

路図である。図11の発振回路40Dは、図5の発振回路40Cに比較して、2個の電流源12-1, 12-2にそれぞれ対応するコンデンサ11-1, 11-2及び放電回路D1, D2を備え、また、上記2個の電流源12-1, 12-2の動作をそれぞれオン/オフする2個のスイッチSW1, SW2を備え、これら2個のスイッチSW1, SW2のオン/オフを制御するコントローラ25を備えたことを特徴としている。上述した図5の発振回路40Cでは、図10から明らかなように、基準電圧Vref1と基準電圧Vref2が実質的に同一の電圧に設定されたときは、発振動作が停止されることになるが、図11の発振回路40Dではこの問題点を解決する。なお、基準電圧源21は、実施の形態1と同様にCMOS回路で形成された電流源12, 12A又は12Bで発生され、具体的には、図2乃至図4において図示された基準電圧Vrefを用いる。また、放電回路D1, D2もそれぞれ上述の放電回路D1と同様に構成される。

### 【0038】

図11において、電流源12-1の一端はスイッチSW1を介して接地され、電流源12-1の他端はコンデンサ11-1を介して接地される。また、電流源12-2の一端はスイッチSW2を介して接地され、電流源12-2の他端はコンデンサ11-2を介して接地される。コンデンサ11-1の両端電圧V11は放電回路D1及びコンパレータ17の非反転入力端子に印加される。また、コンデンサ11-2の両端電圧V12は放電回路D2及びコンパレータ18の非反転入力端子に印加される。さらに、2個のコンパレータ17, 18の各反転入力端子には、基準電圧源21からの基準電圧Vrefが印加される。ここで、コンパレータ17, 18はそれぞれ、各非反転入力端子に印加される電圧V11, V12が基準電圧Vref以上となったとき、ハイレベルのパルス信号を出力する。コンパレータ17からの出力信号は電圧Vsでセットリセット型フリップフロップ19のセット端子Sに出力され、コンパレータ18からの出力信号は電圧Vrでセットリセット型フリップフロップ19のリセット端子Rに出力される。さらに、セットリセット型フリップフロップ19の非反転出力端子Qから出力される信号は電圧Vqで出力端子30に出力されるとともに、放電回路D1の制御端子T1に出力される。また、セットリセット型フリップフロップ19の反転出力端子/Qから出力される信号は電圧Vqbで出力端子31に出力されるとともに、放電回路D2の制御端子T1に出力される。なお、コントローラ25は、当該発振回路40Dの動作の開始後、スイッチSW1をオンした後、所定の時間間隔だけ遅延してスイッチSW2をオンする。

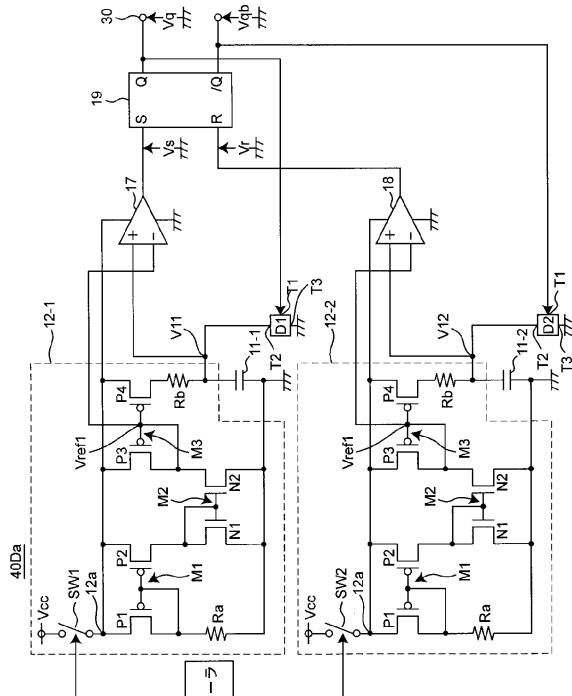

### 【0039】

図12は図11の発振回路40Dの第1の具体例40Daの構成を示す回路図である。図12において、発振回路40Daは、図2の電流源12と同様の構成を有する電流源12-1, 12-2と、図2のコンパレータ14と同様の構成を有する2個のコンパレータ17, 18とを用いて構成したことを特徴としている。

### 【0040】

図12において、電流源12-1はコントローラ25により制御されるスイッチSW1を有し、電流源12-2はコントローラ25により制御されるスイッチSW2を有する。電流源12-1の電源接続点12aはコンパレータ17の電源端子に接続されて電源電圧Vccが供給される。また、電流源12-2の電源接続点12aはコンパレータ18の電源端子にも接続されて電源電圧Vccが供給される。電流源12-1のPチャンネルMOSFETP3, P4の各ゲート電圧は基準電圧Vref1としてコンパレータ17の反転入力端子に印加され、また、電流源12-2のPチャンネルMOSFETP3, P4の各ゲート電圧は基準電圧Vref1としてコンパレータ18の反転入力端子に印加される。さらに、電流源12-1のPチャンネルMOSFETP4のソースは抵抗Rb及びコンデンサ11-1を介して接地され、コンデンサ11-1の両端電圧V11は、コンパレータ17の非反転入力端子に印加され、放電回路D1の端子T2に印加される。電流源12-2のPチャンネルMOSFETP4のソースは抵抗Rb及びコンデンサ11-2を介して接地され、コンデンサ11-2の両端電圧V12は、コンパレータ18の非反転入力端子に印加され、放電回路D2の端子T2に印加される。コンパレータ17からの出力信号は

、セットリセット型フリップフロップ19のセット端子Sに入力される。また、コンパレータ18からの出力信号は、セットリセット型フリップフロップ19のリセット端子Rに入力される。さらに、セットリセット型フリップフロップ19の非反転出力端子Qからの出力信号は放電回路D1の制御端子T1に入力され、セットリセット型フリップフロップ19の反転出力端子/Qからの出力信号は放電回路D2の制御端子T1に入力される。

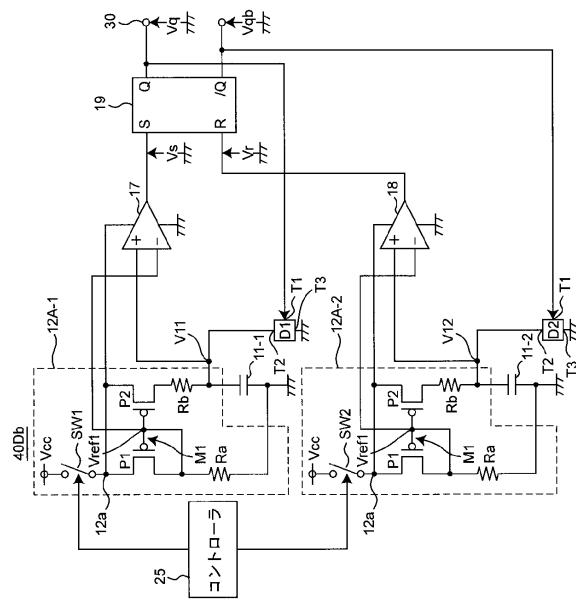

#### 【0041】

図13は図11の発振回路40Dの第2の具体例40Dbの構成を示す回路図である。図13において、発振回路40Dbは、図3の電流源12Aと同様の構成を有する電流源12A-1, 12A-2と、図3のコンパレータ14と同様の構成を有する2個のコンパレータ17, 18とを用いて構成したことを特徴としている。すなわち、発振回路40D 10 bは、図12の発振回路40Daに比較して、図2の電流源12に代えて、図3の電流源12Aを備えたことであり、その他の構成は、以下の点を除いて図12と同様である。電流源12A-1はコントローラ25により制御されるスイッチSW1を有し、電流源12A-2はコントローラ25により制御されるスイッチSW2を有する。また、電流源12A-1のPチャンネルMOSFETP1, P2の各ゲート電圧は基準電圧Vref1としてコンパレータ17の反転入力端子に印加され、また、電流源12A-2のPチャンネルMOSFETP1, P2の各ゲート電圧は基準電圧Vref1としてコンパレータ18の反転入力端子に印加される。

#### 【0042】

図14は図11の発振回路40Dの第3の具体例40Dcの構成を示す回路図である。図14において、発振回路40Dcは、図4の電流源12Bと同様の構成を有する電流源12B-1, 12B-2と、図4のコンパレータ14と同様の構成を有する2個のコンパレータ17, 18とを用いて構成したことを特徴としている。すなわち、発振回路40D 20 cは、図12の発振回路40Daに比較して、図2の電流源12に代えて、図4の電流源12Bを備えたことであり、その他の構成は、以下の点を除いて図12と同様である。電流源12B-1はコントローラ25により制御されるスイッチSW1を有し、電流源12B-2はコントローラ25により制御されるスイッチSW2を有する。

#### 【0043】

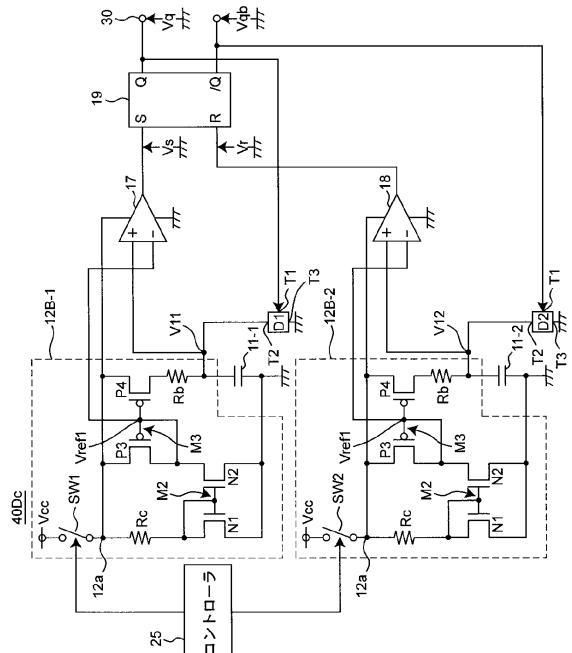

図15は図11の発振回路40Dの動作を示すタイミングチャートである。図15において、コントローラ25は、当該発振回路40Dの動作の開始後、スイッチSW1をオンした後、所定の時間間隔だけ遅延してスイッチSW2をオンする。これにより、まず、コンデンサ11-1が充電し、その両端電圧V11が基準電圧Vref以上となったとき、コンパレータ17はハイレベルのパルス信号をセットリセット型フリップフロップ19のセット端子Sに出力し、これにより、セットリセット型フリップフロップ19はセットされ、その非反転出力端子Qから所定のハイレベル信号Vqが出力端子30及び放電回路D1の制御端子T1に出力されるとともに、その反転出力端子/Qから所定のローレベル信号Vqbが出力端子31及び放電回路D2の制御端子T1に出力される。このとき、放電回路D1はオンとされ、コンデンサ11-1に蓄積された電荷は放電される一方、放電回路D2はオフとされ、コンデンサ11-2に電流源12-2からの電流が流れ、電荷の蓄積が行われる。

#### 【0044】

そして、コンデンサ11-2が充電し、その両端電圧V12が基準電圧Vref以上となったとき、コンパレータ18はハイレベルのパルス信号をセットリセット型フリップフロップ19のリセット端子Rに出力し、これにより、セットリセット型フリップフロップ19はリセットされ、その非反転出力端子Qから所定のローレベル信号Vqが出力端子30及び放電回路D1の制御端子T1に出力されるとともに、その反転出力端子/Qから所定のハイレベル信号Vqbが出力端子31及び放電回路D2の制御端子T1に出力される。このとき、放電回路D1はオフとされて充電が再び開始される一方、放電回路D2はオンとされ、コンデンサ11-2に蓄積された電荷が放電される。以上の動作が繰り返され、出力端子30から出力される信号Vqとして、所定のパルス幅を有するハイレベル信号

10

20

30

40

50

が所定の周期で出力され、すなわち、所定の発振信号が出力される。

【0045】

以上のように構成された発振回路においては、リセット信号に応答して、コンデンサ11-1の電圧がその充電により経過時間に実質的に比例して上昇し基準電圧Vrefに到達した後、セット信号に応答して、コンデンサ11-1の放電により基準電圧Vrefから経過時間につれて下降するとともに、セット信号に応答して、コンデンサ11-2の電圧がその充電により経過時間に実質的に比例して上昇し基準電圧Vrefに到達した後、リセット信号に応答して、コンデンサ11-2の放電により基準電圧Vrefから経過時間につれて下降する動作を繰り返すことにより、セットリセット型フリップフロップ19からの2個の出力信号Vq, Vqbをそれぞれ、所定の周期を有する発振信号として出力することができる。 10

【0046】

以上説明したように、本発明の実施の形態3に係る半導体回路の発振回路においても、実施の形態1の電流源12, 12又は12Bからの充電電流と、電流源12, 12又は12Bからの基準電圧Vrefを用いて、実施の形態1のタイマー回路の動作を含む発振回路の動作を実行しているので、電源電圧Vccが低下しても、電源電圧Vccに依存した充電電流も小さくなる一方、電源電圧Vccから低下電圧だけ低下してなる基準電圧Vrefも小さくなる。それ故、コンデンサ11-1, 11-2の各電圧がその充電により経過時間に実質的に比例して上昇し基準電圧Vrefに到達するまでの時間はほとんど変化しない。すなわち、電源電圧Vccが低下しても発振回路の発振周期を保持しつつ動作できる。従って、より低い電圧から広範囲の電源電圧範囲で安定に動作することができる発振回路を提供できる。 20

【0047】

実施の形態4。

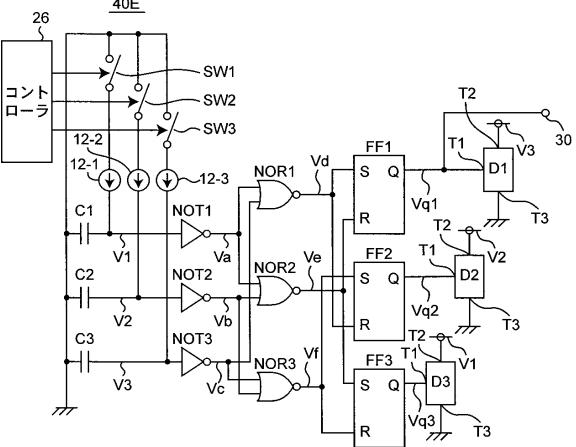

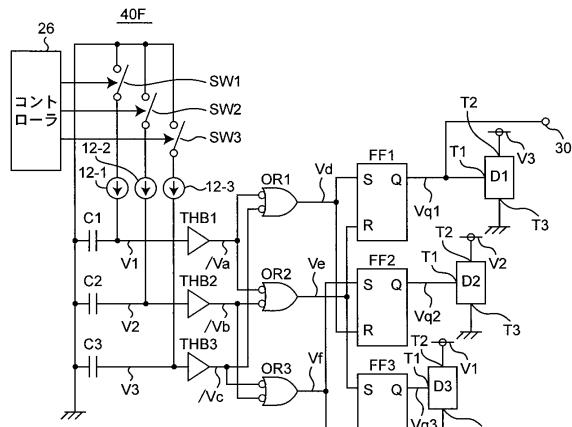

図16は本発明の実施の形態4に係る半導体回路である発振回路40Eの構成を示す回路図である。図16の発振回路40Eは、図11の発振回路40Dに比較して、3個の電流源12-1, 12-2, 12-3と、3個のインバータNOT1, NOT2, NOT3と、3個のセットリセット型フリップフロップFF1, FF2, FF3と、3個の放電回路D1, D2, D3とを備えて構成したことを特徴としている。なお、電流源12-1, 12-2, 12-3は、上述の電流源12と同様にCMOS回路で構成され、放電回路D1, D2, D3もそれぞれ上述の放電回路D1と同様に構成される。 30

【0048】

図16において、電流源12-1の一端はスイッチSW1を介して接地され、電流源12-1の他端はコンデンサC1を介して接地される。また、電流源12-2の一端はスイッチSW2を介して接地され、電流源12-2の他端はコンデンサC2を介して接地される。さらに、電流源12-3の一端はスイッチSW3を介して接地され、電流源12-3の他端はコンデンサC3を介して接地される。コンデンサC1の両端電圧V1は放電回路D3に印加されるとともに、インバータNOT1を介して電圧VaとしてノアゲートNOR1の第1の入力端子及びノアゲートNOR2の第1の入力端子に入力される。また、コンデンサC2の両端電圧V2は放電回路D2に印加されるとともに、インバータNOT2を介して電圧VbとしてノアゲートNOR2の第2の入力端子及びノアゲートNOR3の第2の入力端子に出力される。さらに、コンデンサC3の両端電圧V3は放電回路D1に印加されるとともに、インバータNOT3を介して電圧VcとしてノアゲートNOR1の第2の入力端子及びノアゲートNOR3の第1の入力端子に入力される。なお、各インバータNOT1, NOT2, NOT3はそれぞれ、入力信号が所定のしきい値電圧以上となつたとき、反転されたローレベル信号を出力する。ここで、各インバータNOT1, NOT2, NOT3のしきい値電圧は、好ましくは、上述の実施の形態と同様に、電源電圧VccからPチャンネルMOSFETのしきい値電圧Vthpだけ減じた値に設定される。 40

【0049】

ノアゲートNOR1からの出力信号は電圧Vdとしてセットリセット型フリップフロッ 50

FF1のセット端子S及びセットリセット型フリップフロップFF2のリセット端子Rに出力される。また、ノアゲートNOR2からの出力信号は電圧Veとしてセットリセット型フリップフロップFF1のリセット端子R及びセットリセット型フリップフロップFF3のセット端子Sに出力される。さらに、ノアゲートNOR3からの出力信号は電圧Vfとしてセットリセット型フリップフロップFF2のセット端子S及びセットリセット型フリップフロップFF3のリセット端子Rに出力される。セットリセット型フリップフロップFF1の非反転出力端子Qからの出力信号は電圧Vq1として出力端子30に出力されるとともに、放電回路D1の制御端子T1に出力される。また、セットリセット型フリップフロップFF2の非反転出力端子Qからの出力信号は電圧Vq2として放電回路D2の制御端子T1に出力される。さらに、セットリセット型フリップフロップFF3の非反転出力端子Qからの出力信号は電圧Vq3として放電回路D3の制御端子T1に出力される。なお、コントローラ26は、当該発振回路40Eの動作の開始後、スイッチSW1をオンした後、所定の時間間隔だけ遅延してスイッチSW2をオンし、さらに、上記同じ時間間隔だけ遅延してスイッチSW3をオンする。

10

#### 【0050】

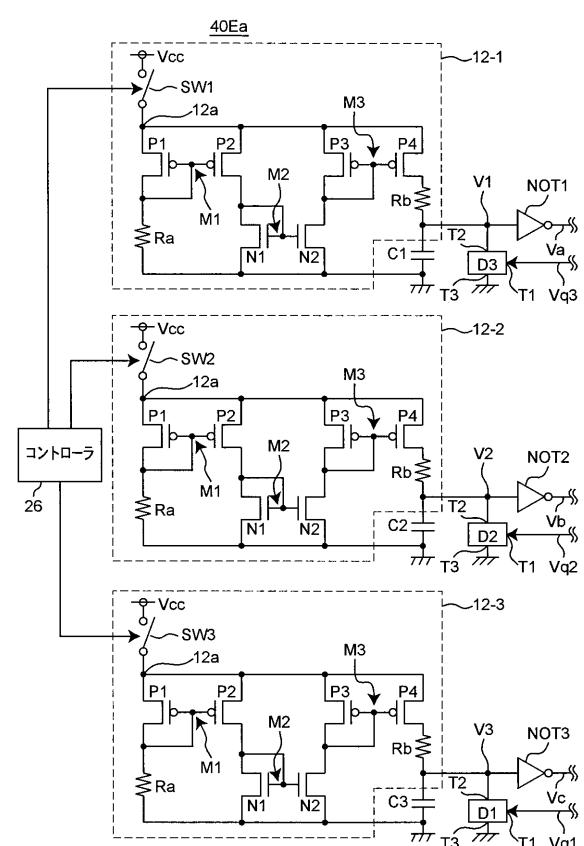

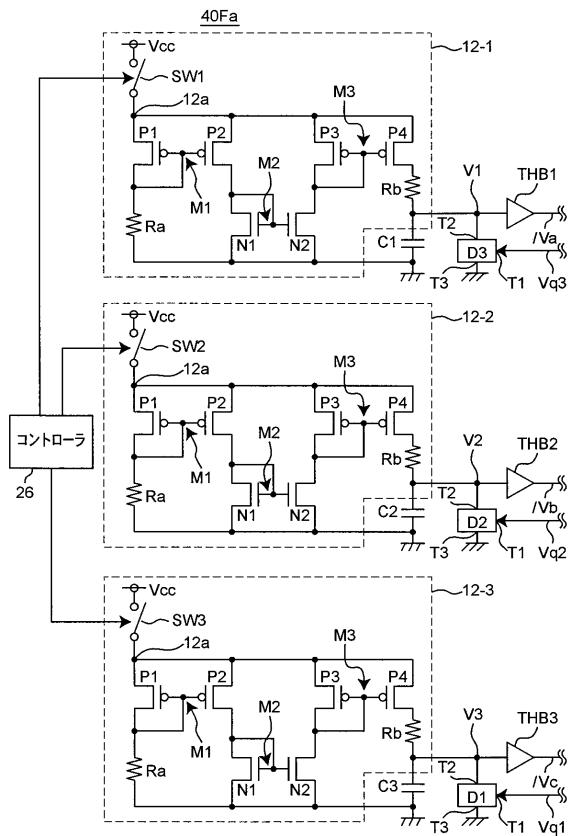

図17は図16の発振回路40Eの第1の具体例40Eaの構成を示す回路図である。なお、図17は、発振回路40Eのコントローラ26からインバータNOT1, NOT2, NOT3及び放電回路D1, D2, D3までの回路のみを示している。図17の発振回路40Eaは、図2の電流源12と同様の構成を有する3個の電流源12-1, 12-2, 12-3を用いて構成したことを特徴としている。

20

#### 【0051】

図17において、電流源12-1はコントローラ26により制御されるスイッチSW1を有し、電流源12-2はコントローラ26により制御されるスイッチSW2を有し、電流源12-3はコントローラ26により制御されるスイッチSW3を有する。電流源12-1のPチャンネルMOSFETP4のソースは抵抗Rb及びコンデンサC1を介して接地され、コンデンサC1の両端電圧V1はインバータNOT1及び放電回路D3の端子T2に印加される。また、電流源12-2のPチャンネルMOSFETP4のソースは抵抗Rb及びコンデンサC2を介して接地され、コンデンサC2の両端電圧V2はインバータNOT2及び放電回路D2の端子T2に印加される。さらに、電流源12-3のPチャンネルMOSFETP4のソースは抵抗Rb及びコンデンサC3を介して接地され、コンデンサC3の両端電圧V3はインバータNOT3及び放電回路D1の端子T2に印加される。

30

#### 【0052】

図18は図16の発振回路40Eの第2の具体例40Ebの構成を示す回路図である。なお、図18は、発振回路40Eのコントローラ26からインバータNOT1, NOT2, NOT3及び放電回路D1, D2, D3までの回路のみを示している。図18の発振回路40Ebは、図3の電流源12Aと同様の構成を有する3個の電流源12A-1, 12A-2, 12A-3を用いて構成したことを特徴としている。図18において、電流源12A-1はコントローラ26により制御されるスイッチSW1を有し、電流源12A-2はコントローラ26により制御されるスイッチSW2を有し、電流源12A-3はコントローラ26により制御されるスイッチSW3を有する。その他の構成は、図17と同様である。

40

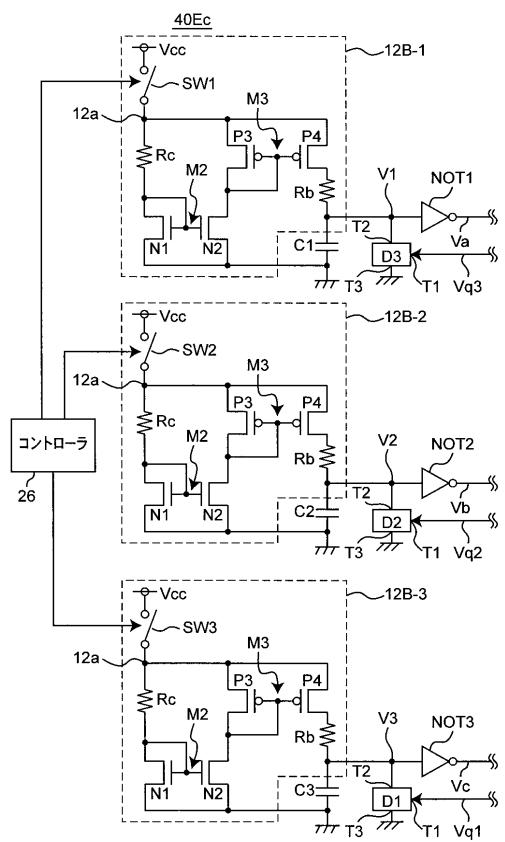

#### 【0053】

図19は図16の発振回路40Eの第3の具体例40Ecの構成を示す回路図である。なお、図19は、発振回路40Eのコントローラ26からインバータNOT1, NOT2, NOT3及び放電回路D1, D2, D3までの回路のみを示している。図19の発振回路40Ecは、図4の電流源12Bと同様の構成を有する3個の電流源12B-1, 12B-2, 12B-3を用いて構成したことを特徴としている。図19において、電流源12B-1はコントローラ26により制御されるスイッチSW1を有し、電流源12B-2はコントローラ26により制御されるスイッチSW2を有し、電流源12B-3はコントローラ26により制御されるスイッチSW3を有する。

50

ローラ26により制御されるスイッチSW3を有する。その他の構成は、図17及び図18と同様である。

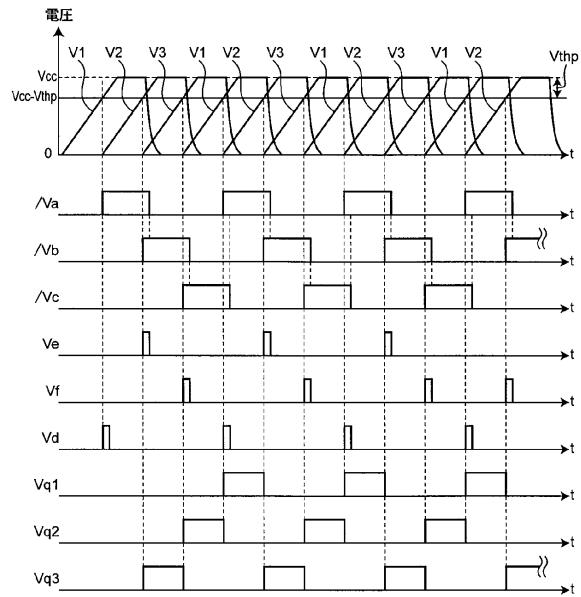

【0054】

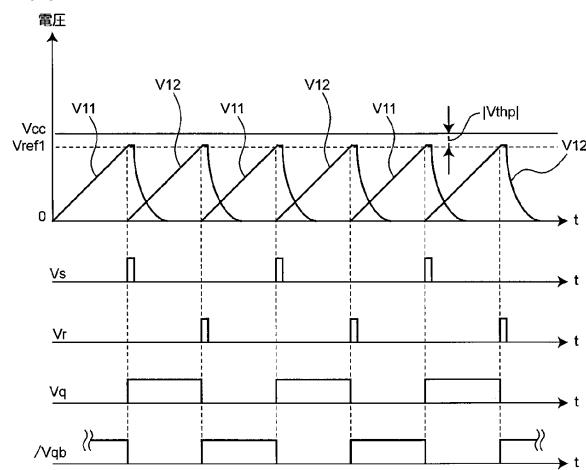

図20は図16の発振回路40Eの動作を示すタイミングチャートである。図20において、コントローラ26は、当該発振回路40Eの動作の開始後、スイッチSW1をオンした後、所定の時間間隔だけ遅延してスイッチSW2をオンし、さらに、上記同じ時間間隔だけ遅延してスイッチSW3をオンする。これにより、まず、コンデンサC1が充電し、その両端電圧V1がインバータNOT1のしきい値電圧以上となったとき、ローレベル信号VaがインバータNOT1から出力される。次いで、コンデンサC2が充電し、その両端電圧V2がインバータNOT2のしきい値電圧以上となったとき、ローレベル信号VbがインバータNOT2から出力される。そして、コンデンサC3が充電し、その両端電圧V3がインバータNOT3のしきい値電圧以上となったとき、ローレベル信号VcがインバータNOT3から出力される。ここで、ローレベル信号Vaとローレベル信号Vbとが所定の時間期間で重なるように、また、ローレベル信号Vbとローレベル信号Vcとが所定の時間期間で重なるように、ローレベル信号Vcと、次のサイクルのローレベル信号Vaが所定の時間期間で重なるように、コントローラ26による起動時（電源投入時）の制御が実行される。なお、図20において、ローレベル信号Va, Vb, Vcについては、図示の簡単化のために、ローアクティブ信号の形式/Va, /Vb, /Vcで図示している。

【0055】

以上説明したように、ローレベル信号Va, Vb, Vcが順次互いに重なるように出力されるので、ノアゲートNOR2, NOR3, NOR1の順序で、順次同一の周期でハイパルス信号Ve, Vf, Vdが順次出力され、これに応答して、セットリセット型フリップフロップFF3からのハイレベル出力信号Vq3と、セットリセット型フリップフロップFF2からのハイレベル出力信号Vq2と、セットリセット型フリップフロップFF1からのハイレベル出力信号Vq1とが順次出力される。ここで、放電回路D3, D2, D1も順次、放電のオフ/オンが繰り返される。従って、図20に示すように、以上の動作が繰り返され、出力端子30から出力される信号Vq1として、所定のパルス幅を有するハイレベル信号が所定の周期で出力され、すなわち、所定の発振信号が出力される。

【0056】

以上の実施の形態4に係る図16の発振回路40Eでは、3個の電流源12-1, 12-2, 12-3を用いる例を示しているが、4個以上の電流源とそれに対応した素子回路を用いて同様の発振回路を構成してもよい。

【0057】

当該発振回路においては、リセット信号に応答して、各コンデンサC1, C2, C3の電圧がそれぞれそれらの充電により経過時間に実質的に比例して上昇し基準電圧Vrefに到達した後、セット信号に応答して、各コンデンサC1, C2, C3の放電により基準電圧Vrefから経過時間につれて下降する動作を各コンデンサC1, C2, C3において時間間隔だけずれて繰り返すことにより、各セットリセット型フリップフロップFF1, FF2, FF3からの出力信号をそれぞれ、所定の周期を有する発振信号として出力することができる。

【0058】

以上説明したように、本発明の実施の形態4に係る半導体回路の発振回路においても、実施の形態1の電流源12、12又は12Bからの充電電流と、電流源12、12又は12Bからの基準電圧Vrefを用いて、実施の形態1のタイマー回路の動作を含む発振回路の動作を実行しているので、電源電圧Vccが低下しても、電源電圧Vccに依存した充電電流も小さくなる一方、電源電圧Vccから低下電圧だけ低下してなる基準電圧Vrefも小さくなる。それ故、コンデンサC1, C2, C3の各電圧がそれら充電により経過時間に実質的に比例して上昇し基準電圧Vrefに到達するまでの時間はほとんど変化しない。すなわち、電源電圧Vccが低下しても発振回路の発振周期を保持しつつ動作で

10

20

30

40

50

きる。従って、より低い電圧から広範囲の電源電圧範囲で安定に動作することができる発振回路を提供できる。

【0059】

実施の形態5.

図21は本発明の実施の形態5に係る半導体回路である発振回路40Fの構成を示す回路図である。図21の発振回路40Fは、図16の発振回路40Eと比較して、インバータNOT1, NOT2, NOT3に代えて、しきい値バッファTHB1, THB2, THB3を備え、また、ノアゲートNOR1, NOR2, NOR3に代えて、2つの反転入力端子付きオアゲートOR1, OR2, OR3を備えたことを特徴としている。以上のように構成された発振回路40Fにおいては、出力信号Va, Vb, Vcが図16の発振回路40Eに比較して反転されることを除いて、発振回路40Eと同様に動作する。

10

【0060】

以上の実施の形態5に係る図21の発振回路40Fでは、3個の電流源12-1, 12-2, 12-3を用いる例を示しているが、4個以上の電流源とそれに対応した素子回路を用いて同様の発振回路を構成してもよい。

【0061】

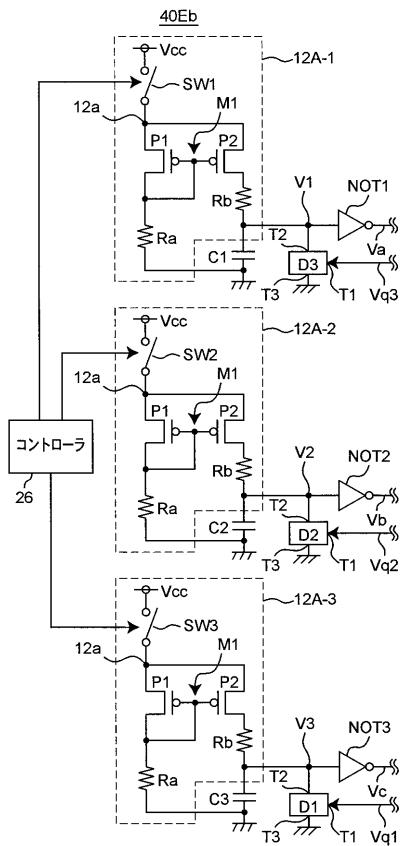

図22は図21の発振回路40Fの第1の具体例40Faの構成を示す回路図である。なお、図22は、発振回路40Fのコントローラ26からしきい値バッファTHB1, THB2, THB3及び放電回路D1, D2, D3までの回路のみを示している。図22の発振回路40Faは、図2の電流源12と同様の構成を有する3個の電流源12-1, 12-2, 12-3を用いて構成したことを特徴としている。ここで、図22の発振回路40Faは、図17の発振回路40Eaに比較して、インバータNOT1, NOT2, NO3に代えてそれぞれ、しきい値バッファTHB1, THB2, THB3を備えたことが異なる。

20

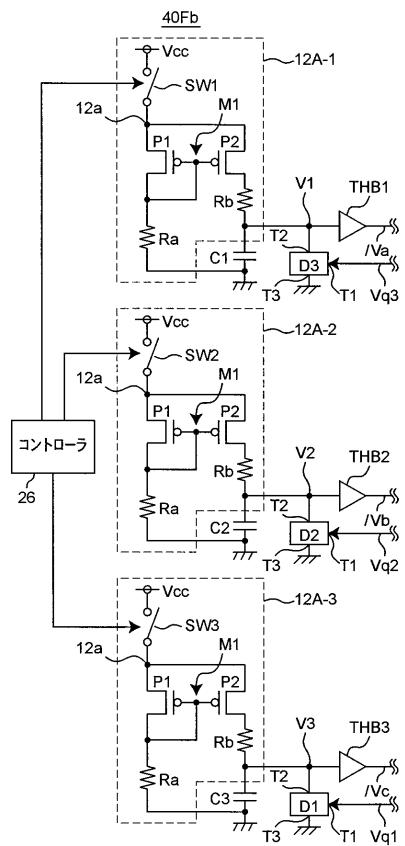

【0062】

図23は図21の発振回路40Fの第2の具体例40Fbの構成を示す回路図である。なお、図23は、発振回路40Fのコントローラ26からしきい値バッファTHB1, THB2, THB3及び放電回路D1, D2, D3までの回路のみを示している。図23の発振回路40Fbは、図3の電流源12Aと同様の構成を有する3個の電流源12A-1, 12A-2, 12A-3を用いて構成したことを特徴としている。ここで、図23の発振回路40Fbは、図18の発振回路40Ebに比較して、インバータNOT1, NOT2, NO3に代えてそれぞれ、しきい値バッファTHB1, THB2, THB3を備えたことが異なる。

30

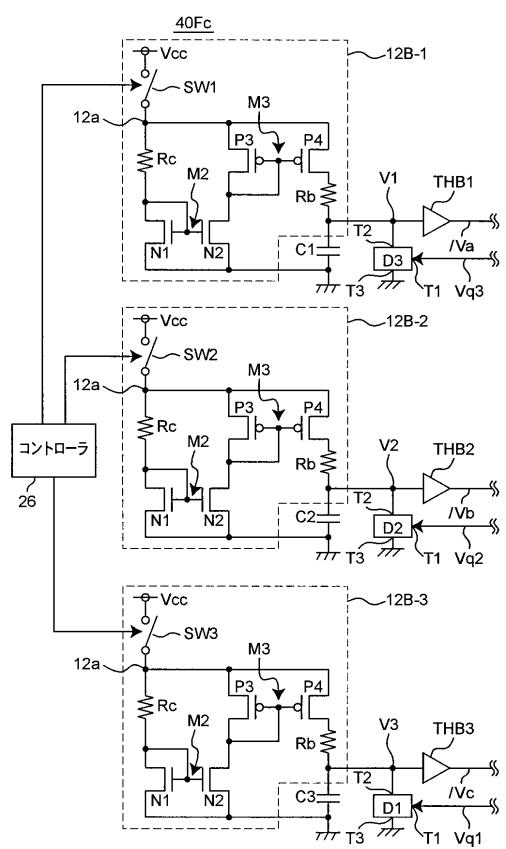

【0063】

図24は図21の発振回路40Fの第3の具体例40Fcの構成を示す回路図である。図24は、発振回路40Fのコントローラ26からしきい値バッファTHB1, THB2, THB3及び放電回路D1, D2, D3までの回路のみを示している。図24の発振回路40Fcは、図4の電流源12Bと同様の構成を有する3個の電流源12B-1, 12B-2, 12B-3を用いて構成したことを特徴としている。ここで、図24の発振回路40Fcは、図19の発振回路40Ecに比較して、インバータNOT1, NOT2, NO3に代えてそれぞれ、しきい値バッファTHB1, THB2, THB3を備えたことが異なる。

40

【0064】

以上説明したように、本発明の実施の形態5に係る半導体回路の発振回路において、実施の形態4と同様の作用効果を有し、電源電圧Vccが低下しても発振回路の発振周期を保持しつつ動作でき、より低い電圧から広範囲の電源電圧範囲で安定に動作することができる発振回路を提供できる。

【産業上の利用可能性】

【0065】

以上詳述したように、本発明に係る半導体回路によれば、各電流源からの充電電流と、

50

各電流源からの基準電圧を用いて、タイマー回路の動作を含む発振回路の動作を実行しているので、電源電圧が低下しても、電源電圧に依存した充電電流も小さくなる一方、電源電圧から低下電圧だけ低下してなる基準電圧も小さくなる。それ故、各コンデンサの各電圧がそれら充電により経過時間に実質的に比例して上昇し基準電圧に到達するまでの時間はほとんど変化しない。すなわち、電源電圧が低下しても発振回路の発振周期を保持しつつ動作できる。従って、より低い電圧から広範囲の電源電圧範囲で安定に動作することができる発振回路を提供できる。

【図面の簡単な説明】

【0066】

【図1】本発明の実施の形態1に係る半導体回路であるタイマー回路40の構成を示す回路図である。

10

【図2】図1のタイマー回路40の具体例を示す回路図である。

【図3】図2のタイマー回路40の変形例40Aを示す回路図である。

【図4】図1のタイマー回路40の別の具体例40Bを示す回路図である。

【図5】本発明の実施の形態2に係る半導体回路である発振回路40Cの構成を示す回路図である。

【図6】図5の発振回路40Cの第1の具体例40Caの構成を示す回路図である。

【図7】図5の発振回路40Cの第2の具体例40Cbの構成を示す回路図である。

【図8】図5乃至図7の放電回路D1の構成を示す回路図である。

【図9】図5乃至図7の放電回路D1の変形例D1Aの構成を示す回路図である。

20

【図10】図5の発振回路40Cの動作を示すタイミングチャートである。

【図11】本発明の実施の形態3に係る半導体回路である発振回路40Dの構成を示す回路図である。

【図12】図11の発振回路40Dの第1の具体例40Daの構成を示す回路図である。

【図13】図11の発振回路40Dの第2の具体例40Dbの構成を示す回路図である。

【図14】図11の発振回路40Dの第3の具体例40Dcの構成を示す回路図である。

【図15】図11の発振回路40Dの動作を示すタイミングチャートである。

【図16】本発明の実施の形態4に係る半導体回路である発振回路40Eの構成を示す回路図である。

【図17】図16の発振回路40Eの第1の具体例40Eaの構成を示す回路図である。

30

【図18】図16の発振回路40Eの第2の具体例40Ebの構成を示す回路図である。

【図19】図16の発振回路40Eの第3の具体例40Ecの構成を示す回路図である。

【図20】図16の発振回路40Eの動作を示すタイミングチャートである。

【図21】本発明の実施の形態5に係る半導体回路である発振回路40Fの構成を示す回路図である。

【図22】図21の発振回路40Fの第1の具体例40Faの構成を示す回路図である。

【図23】図21の発振回路40Fの第2の具体例40Fbの構成を示す回路図である。

【図24】図21の発振回路40Fの第3の具体例40Fcの構成を示す回路図である。

【符号の説明】

【0067】

11, 11-1, 11-2 コンデンサ、12, 12A, 12B, 12-1, 12-2

, 12-3, 12A-1, 12A-2, 12A-3, 12B-1, 12B-2, 12B-3

電流源、13 基準電圧源、14, 17, 18 コンパレータ、19, FF1, FF2, FF3

セットリセット型フリップフロップ、20, 30, 31 出力端子、21, 22

基準電圧源、23 NチャンネルMOSFET、24 カレントミラー回路、25

, 26 コントローラ、40, 40A, 40B タイマー回路、40C, 40Ca, 40Cb, 40D, 40Da, 40Db, 40Dc, 40E, 40Ea, 40Eb, 40Ec, 40F, 40Fa, 40Fb, 40Fc 発振回路、C1, C2, C3 コンデンサ、

D1, D2, D3 放電回路、P1乃至P6 PチャンネルMOSFET、N1乃至N4

NチャンネルMOSFET、NOR1, NOR2, NOR3 ノアゲート、NOT1,

40

50

NOT 2, NOT 3 インバータ、M1, M2, M3 カレントミラー回路、R<sub>a</sub>, R<sub>b</sub>, R<sub>c</sub> 抵抗、T1 制御端子、T2, T3 端子、SW, SW1, SW2, SW3 スイッチ、V<sub>ref</sub>, V<sub>ref1</sub>, V<sub>ref2</sub> 基準電圧。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図11】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

---

フロントページの続き

審査官 石田 勝

(56)参考文献 特開平11-298299 (JP, A)

特開平6-177719 (JP, A)

特開平11-120782 (JP, A)

特開平11-103239 (JP, A)

特開2003-332893 (JP, A)

米国特許第04868525 (US, A)

特開平8-204527 (JP, A)

特開昭62-152217 (JP, A)

特開平11-145808 (JP, A)

特開昭61-39718 (JP, A)

W.J.Dally/J.W.Poulton著, 「Digital Systems Engineering」, 米国, The Press Syndicate of The University of Cambridge, 1998年, 195頁~199頁, カレントミラー、カスコード接続

(58)調査した分野(Int.Cl., DB名)

H03K 3/03

H03K 3/354