(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6509909号

(P6509909)

(45) 発行日 令和1年5月8日(2019.5.8)

(24) 登録日 平成31年4月12日(2019.4.12)

|                      |            |

|----------------------|------------|

| (51) Int.Cl.         | F 1        |

| HO3F 3/45 (2006.01)  | HO3F 3/45  |

| HO3F 3/189 (2006.01) | HO3F 3/189 |

| HO3F 3/72 (2006.01)  | HO3F 3/72  |

| HO3F 1/22 (2006.01)  | HO3F 1/22  |

請求項の数 11 (全 22 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-563827 (P2016-563827)  |

| (86) (22) 出願日 | 平成27年4月14日 (2015.4.14)        |

| (65) 公表番号     | 特表2017-514395 (P2017-514395A) |

| (43) 公表日      | 平成29年6月1日 (2017.6.1)          |

| (86) 国際出願番号   | PCT/US2015/025770             |

| (87) 国際公開番号   | W02015/164125                 |

| (87) 国際公開日    | 平成27年10月29日 (2015.10.29)      |

| 審査請求日         | 平成30年3月19日 (2018.3.19)        |

| (31) 優先権主張番号  | 14/258,669                    |

| (32) 優先日      | 平成26年4月22日 (2014.4.22)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595020643<br>クアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                        |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                        |

| (74) 代理人  | 100158805<br>弁理士 井関 守三                                                                                        |

| (74) 代理人  | 100112807<br>弁理士 岡田 貴志                                                                                        |

最終頁に続く

(54) 【発明の名称】選択的に結合されるゲート端子を有する差動カスコード増幅器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタと第2のトランジスタとを備える差動カスコード増幅器と、

トランジスタであって、

前記差動カスコード増幅器の前記第1のトランジスタのゲート端子に結合されたソース端子と、

前記差動カスコード増幅器の前記第2のトランジスタのゲート端子に結合されたドレイン端子と、

前記第1のトランジスタの前記ゲート端子に、および前記トランジスタの前記ソース端子に結合された第1のパッシブな高インピーダンス要素と、

前記第2のトランジスタの前記ゲート端子に、および前記ドレイン端子に結合された第2のパッシブな高インピーダンス要素と

を含むトランジスタと

を備え、ここにおいて、

前記トランジスタは、前記ソース端子を、前記差動カスコード増幅器の前記第1のトランジスタの前記ゲート端子に選択的に結合するために、および前記ドレイン端子を、前記差動カスコード増幅器の前記第2のトランジスタの前記ゲート端子に選択的に結合するために、第1のモードにおいてアクティベートされるように構成され、

前記トランジスタは、前記差動カスコード増幅器の前記第1のトランジスタの前記ゲート端子が、前記第1のパッシブな高インピーダンス要素および前記第2のパッシブな高イ

ンピーダンス要素を介して、前記差動力スコード増幅器の前記第2のトランジスタの前記ゲート端子に結合されるように、第2のモードにおいてデアクティベートされるように構成され、ここにおいて、前記第1のパッシブな高インピーダンス要素および前記第2のパッシブな高インピーダンス要素は、共通の制御ノードに共に結合される、

装置。

【請求項2】

前記第2のパッシブな高インピーダンス要素は、前記第1のパッシブな高インピーダンス要素に結合される、請求項1に記載の装置。

【請求項3】

前記第1のパッシブな高インピーダンス要素は第1の抵抗器を備え、ここにおいて、前記第2のパッシブな高インピーダンス要素は第2の抵抗器を備える、請求項2に記載の装置。 10

【請求項4】

前記第1のパッシブな高インピーダンス要素は第1のインダクタを備え、ここにおいて、前記第2のパッシブな高インピーダンス要素は第2のインダクタを備える、請求項2に記載の装置。

【請求項5】

前記差動力スコード増幅器は、

前記第1のトランジスタに結合された第3のトランジスタと、

前記第2のトランジスタに結合された第4のトランジスタと、ここにおいて、前記第1のトランジスタと前記第3のトランジスタは第1のカスコードトランジスタ対を形成し、ここにおいて、前記第2のトランジスタと前記第4のトランジスタは第2のカスコードトランジスタ対を形成する、

20

をさらに備える、請求項1に記載の装置。

【請求項6】

前記第3のトランジスタのゲートは第1の差動入力信号を受信するように構成され、ここにおいて、前記第4のトランジスタのゲートは第2の差動入力信号を受信するように構成される、請求項5に記載の装置。

【請求項7】

前記差動力スコード増幅器に結合された変圧器をさらに備え、ここにおいて、前記変圧器は、前記差動力スコード増幅器の出力をアンテナに与えるように構成される、請求項1に記載の装置。 30

【請求項8】

電力増幅器または駆動増幅器をさらに備え、ここにおいて、前記トランジスタおよび前記差動力スコード増幅器は前記電力増幅器または前記駆動増幅器内に含められる、請求項1に記載の装置。

【請求項9】

前記差動力スコード増幅器は増幅器段のユニットセルに含められ、ここにおいて、前記第1のトランジスタのドレイン端子は前記増幅器段の少なくとも1つの他のユニットセルに結合される、請求項1に記載の装置。 40

【請求項10】

第1のゲート端子を有する第1のトランジスタを含み、第2のゲート端子を有する第2のトランジスタをさらに含む差動力スコード増幅器において、差動信号を増幅することと、

第1のモードの間に、前記第1のゲート端子と前記第2のゲート端子との間に結合されたトランジスタを介して、前記第1のゲート端子を前記第2のゲート端子に結合するため、前記トランジスタをアクティベートすることと、

第2のモードの間に、前記差動力スコード増幅器の前記第1のトランジスタの前記ゲート端子が、第1のパッシブな高インピーダンス要素および第2のパッシブな高インピーダンス要素を介して、前記差動力スコード増幅器の前記第2のトランジスタの前記ゲート端

子に結合するように、前記第1のゲート端子を前記第1のパッシブな高インピーダンス要素に結合するために、および前記第2のゲート端子を前記第2のパッシブな高インピーダンス要素に結合するために、前記トランジスタをデアクティベートすることと、ここにおいて、前記第1のパッシブな高インピーダンス要素および前記第2のパッシブな高インピーダンス要素は、共通の制御ノードに共に結合される、

を備える、方法。

【請求項11】

前記第2のモードの間に、前記第1のゲート端子における電圧が前記第1のトランジスタのドレイン電圧を追跡し、前記第2のゲート端子における電圧が前記第2のトランジスタのドレイン電圧を追跡する、請求項10に記載の方法。 10

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

[0001]本出願は、その内容全体が参照により本明細書に明確に組み込まれる、2014年4月22日に出願された、同一出願人が所有する米国非仮特許出願第14/258,669号の優先権を主張する。 20

【0002】

[0002]本開示は一般に、オフ状態にある1つまたは複数のゲインセルを有する差動カスコード増幅器に関する。 20

【背景技術】

【0003】

[0003]技術の進歩により、コンピューティングデバイスは、より小型でより強力になった。たとえば、現在、小型で、軽量で、ユーザが容易に持ち運べる、ポータブルワイヤレス電話、携帯情報端末(PDA)、およびペーディングデバイスなど、ワイヤレスコンピューティングデバイスを含む、様々なポータブルパーソナルコンピューティングデバイスが存在する。より具体的には、セルラー電話およびインターネットプロトコル(IP)電話などのポータブルワイヤレス電話は、ワイヤレスネットワークを介して音声とデータパケットとを通信し得る。さらに、多くのそのようなワイヤレス電話は、その中に組み込まれた他のタイプのデバイスを含む。たとえば、ワイヤレス電話は、デジタルスチルカメラ、デジタルビデオカメラ、デジタルレコーダ、およびオーディオファイルプレーヤをも含み得る。また、そのようなワイヤレス電話は、インターネットにアクセスするために使用され得る、ウェブブラウザアプリケーションなど、ソフトウェアアプリケーションを含む、実行可能な命令を処理し得る。したがって、これらのワイヤレス電話はかなりの計算能力を含み得る。 30

【発明の概要】

【0004】

[0004]ワイヤレス電話または他のワイヤレスデバイスは、アンテナを介して信号を送る送信機を含み得る。信号は、アンテナによって送られるより前に、ワイヤレスデバイスの電力増幅器(PA)段または駆動増幅器(DA)段などにおいて増幅され得る。PA段(またはDA段)は、変圧器などを介して、アンテナに磁気的に結合され得、また、PA段(またはDA段)が変圧器を介してアンテナに差動増幅された信号を供給することを可能にする差動カスコード構成(たとえば、カスコードトランジスタの差動対を含み得る)を有し得る。動作の間、ワイヤレスデバイスは、差動増幅された信号の利得を調節するために、PA段(またはDA段)の一部分(たとえば「セル」)を選択的にアクティベートし得る。たとえば、セル内のトランジスタのゲート端子は、バイアス電圧が論理高の電圧レベルを有するときにアクティベートされ得るか、またはバイアス電圧が論理低の電圧レベル(たとえば、ほぼ0ボルト)を有するときにデアクティベートされ得る。 40

【0005】

[0005]セルをデアクティベートするためにバイアス電圧を論理低の電圧レベル(たとえ

50

ば、ほぼ 0 ボルト) に調節することは、トランジスタに「ストレス」を与える。たとえば、P A 段 (または D A 段) の利得を調節する間、デアクティベートされたセルのカスコードデバイスのトランジスタは、バイアス電圧よりもかなり大きいドレイン電圧を有し、トランジスタに電圧「ストレス」を引き起こし得る。この電圧「ストレス」は、(たとえばトランジスタのゲート酸化物領域に損害を与えることによって) トランジスタに損害を与えるものであり、また增幅器段の信頼性を低下させ得る。論理低の電圧レベルであるバイアス電圧は、デアクティベートされたトランジスタのドレインゲート間電圧差を低減するように増大され得るが、この技法はカスコードデバイスを通じた漏れ電流 (たとえば信号漏れ) を増加させ、それによって、カスコードデバイスの増幅された出力とカスコードデバイスの入力との間の線形性を低減する。

10

【図面の簡単な説明】

【0006】

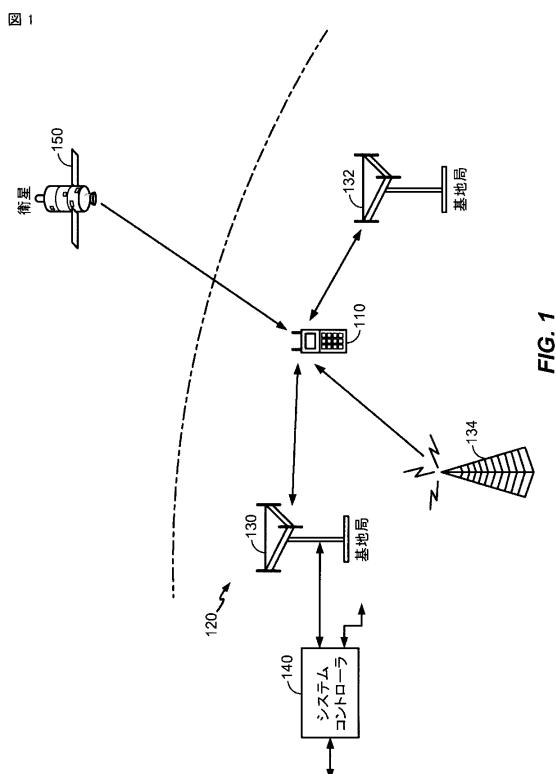

【図 1】[0006] ワイヤレスシステムと通信するワイヤレスデバイスを示す図。

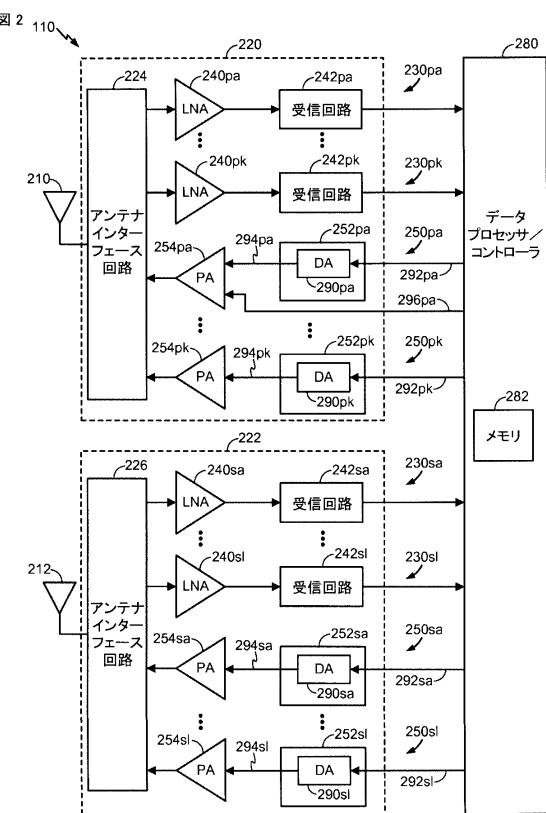

【図 2】[0007] 図 1 のワイヤレスデバイスのブロック図。

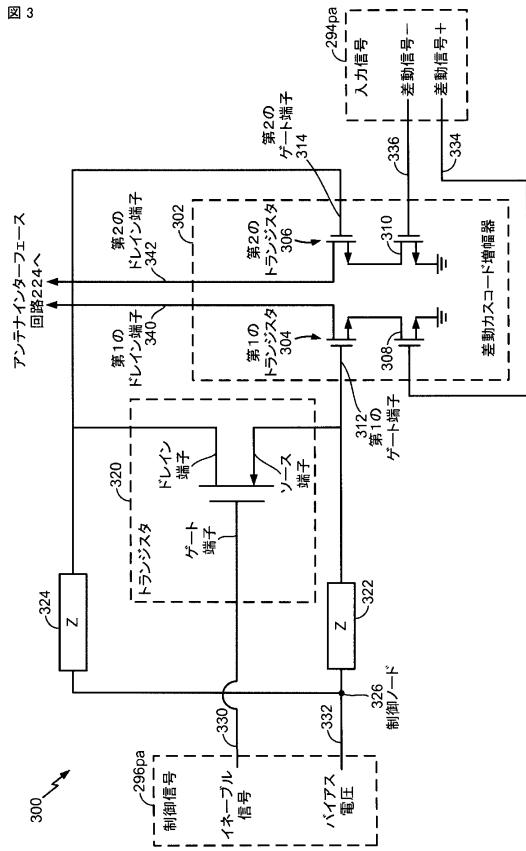

【図 3】[0008] 図 2 のワイヤレスデバイスの構成要素内にある增幅器の例示的な実施形態を示すブロック図。

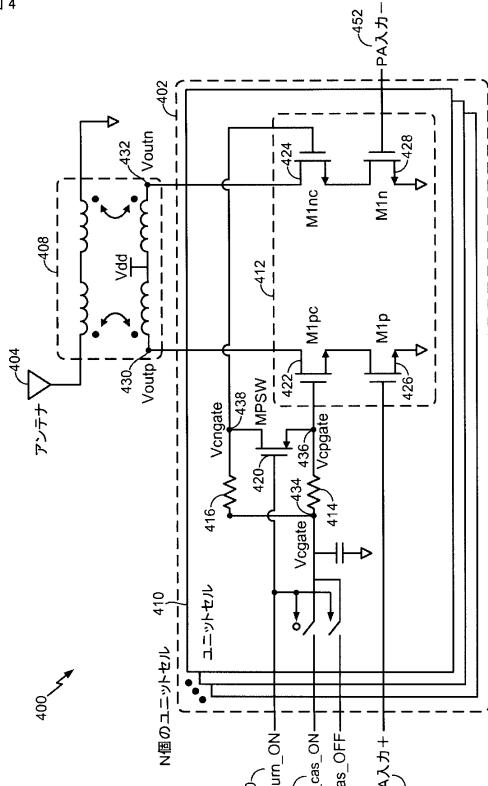

【図 4】[0009] 図 2 のワイヤレスデバイスの増幅器内に組み込まれた要素を含む回路の例示的な実施形態を示す図。

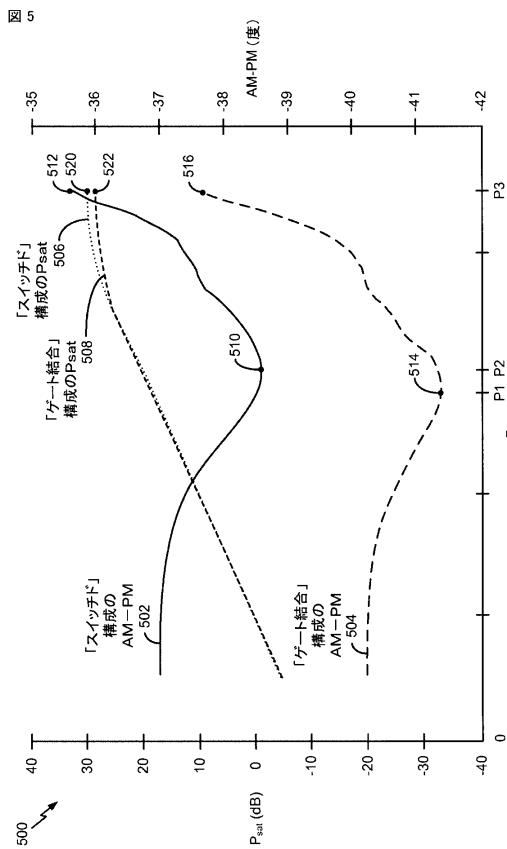

【図 5】[0010] 差動カスコード増幅器内にあるトランジスタのゲート端子を選択的に分離する方法の例示的な実施形態を示すフローチャート。

20

【図 6】

【図 7】

【発明を実施するための形態】

【0007】

[0011] 下で示される詳細な説明は、本開示の例示的な設計の説明として意図され、本開示を実践できる唯一の設計を表すことは意図されていない。「例示的」という用語は、本明細書では、「例、実例、または例示として働くこと」を意味するのに使用される。本明細書で「例示的」として説明されるすべての設計は、必ずしも、他の設計より好ましいまたは有利と解釈されるべきではない。この「発明を実施するための形態」は、本開示の例示的な設計の完全な理解を提供するために、特定の詳細を含む。本明細書で説明される例示的な設計が、これらの特定の詳細なしで実践され得ることは、当業者には明白である。いくつかの場合には、周知の構造およびデバイスは、本明細書で提示される例示的な設計の新規性を不明瞭にすることを避けるために、ブロック図の形で示される。

30

【0008】

[0012] 図 1 に、ワイヤレス通信システム 120 と通信するワイヤレスデバイス 110 を示す。ワイヤレス通信システム 120 は、ロングタームエボリューション (LTE (登録商標) : Long Term Evolution) システム、符号分割多元接続 (CDMA) システム、モバイル通信用グローバルシステム (GSM (登録商標) : Global System for Mobile Communications) システム、ワイヤレスローカルエリアネットワーク (WLAN: wireless local area network) システム、または何らかの他のワイヤレスシステムであり得る。CDMA システムは、広帯域 CDMA (WCDMA (登録商標) )、CDMA 1X (CDMA2000 1xRTT)、エボリューションデータオプティマイズド (EV-DO: Evolution-Data Optimized)、時分割同期 CDMA (TD-SCDMA: Time Division Synchronous CDMA)、または CDMA の何らかの他のバージョンを実装し得る。簡単のために、図 1 は、2 つの基地局 130 および 132 と 1 つのシステムコントローラ 140 を含むワイヤレス通信システム 120 を示している。概して、ワイヤレスシステムは、任意の数の基地局と、ネットワークエンティティの任意のセットとを含み得る。

40

【0009】

[0013] ワイヤレスデバイス 110 は、ユーザ機器 (UE)、移動局、端末、アクセス端末、加入者ユニット、局などと呼ばれることもある。ワイヤレスデバイス 110 は、セル

50

ラー電話、スマートフォン、タブレット、ワイヤレスモデム、携帯情報端末（PDA）、ハンドヘルドデバイス、ラップトップコンピュータ、スマートブック、ネットブック、コードレス電話、ワイヤレスローカルループ（WLL）ステーション、Blue tooth（登録商標）デバイスなどとされ得る。ワイヤレスデバイス110はワイヤレス通信システム120と通信し得る。ワイヤレスデバイス110はまた、放送局（たとえば、放送局134）からの信号、1つまたは複数のグローバルナビゲーション衛星システム（GNSS：global navigation satellite systems）中の衛星（たとえば、衛星150）からの信号などを受信し得る。ワイヤレスデバイス110は、LTE、WCDMA、CDMA1X、EV-DO、TD-SCDMA、GSM、802.11など、ワイヤレス通信のための1つまたは複数の無線技術をサポートし得る。

10

#### 【0010】

[0014]図2は、図1のワイヤレスデバイス110の例示的な設計のブロック図を示す。この例示的な設計では、ワイヤレスデバイス110は、1次アンテナ210に結合されたトランシーバ220と、2次アンテナ212に結合されたトランシーバ222と、データプロセッサ／コントローラ280とを含む。トランシーバ220は、複数の周波数帯域、複数の無線技術、キャリアアグリゲーションなどをサポートするために、複数（K個）の受信機230pa～230pkと複数（K個）の送信機250pa～250pkとを含む。トランシーバ222は、複数の周波数帯域、複数の無線技術、キャリアアグリゲーション、受信ダイバーシティ、複数の送信アンテナから複数の受信アンテナへの多入力多出力（MIMO）送信などをサポートするために、複数（L個）の受信機230sa～230s1と複数（L個）の送信機250sa～250s1とを含む。

20

#### 【0011】

[0015]図2に示す例示的な設計では、各受信機230pa～230pk、230sa～230s1はそれぞれ、LNA240pa～240pk、240sa～240s1と、受信回路242pa～242pk、242sa～242s1を含む。データ受信では、アンテナ210は、基地局および／または他の送信機局から信号を受信し、受信RF信号を与える。その受信RF信号は、アンテナインターフェース回路224を介してルーティングされ、選択された受信機に入力RF信号として提示される。アンテナインターフェース回路224は、スイッチ、デュプレクサ、送信フィルタ、受信フィルタ、整合回路などを含み得る。以下の説明では、受信機230paが選択された受信機である例が提示される。受信機230pa内で、LNA240paが、入力RF信号を増幅し、出力RF信号を与える。受信回路242paは、出力RF信号をRFからベースバンドにダウンコンバートし、ダウンコンバートされた信号を増幅およびフィルタ処理し、データプロセッサ／コントローラ280にアナログ入力信号を与える。受信回路242paは、ミキサ、フィルタ、増幅器、整合回路、発振器、局部発振器（LO）生成器、位相ロックループ（PLL：phase locked loop）などを含み得る。トランシーバ220および222中の各残りの受信機は、受信機230paと同様の方法で動作し得る。

30

#### 【0012】

[0016]図2に示す例示的な設計では、各送信機250pa～250pk、250sa～250s1はそれぞれ、送信回路252pa～252pk、252sa～252s1と、電力増幅器（PA）254pa～254pk、254sa～254s1とを含んでいる。データ送信では、データプロセッサ／コントローラ280は、送信されるべきデータを処理（たとえば、符号化および変調）し、選択された送信機にアナログ出力信号を与える。以下の説明では、送信機250paが選択された送信機である例が提示される。送信機250pa内で、送信回路252paは、アナログ出力信号を増幅し、フィルタ処理し、ベースバンドからRFにアップコンバートし、被変調RF信号を与える。送信回路252paは、増幅器、フィルタ、ミキサ、整合回路、発振器、LO生成器、PLLなどを含み得る。PA254paは、被変調RF信号を受信し、増幅し、適切な出力電力レベルを有する送信RF信号を与える。送信RF信号は、アンテナインターフェース回路224を介してルーティングされ、アンテナ210を介して送信される。トランシーバ220および2

40

50

22中の各残りの送信機は、送信機 250pa と同様の方法で動作し得る。

【0013】

[0017]図2は、受信機 230pa～230pk および 230sa～230s1 ならびに送信機 250pa～250pk および 250sa～250s1 の例示的な設計を示す。受信機および送信機はまた、フィルタ、整合回路など、図2に示されていない他の回路を含み得る。トランシーバ 220 および 222 の全部または一部分が、1つまたは複数のアナログ集積回路 (IC)、RF IC (RFIC)、混合信号 IC などの上に実装され得る。たとえば、LNA 240pa～240pk および 240sa～240s1、ならびに受信回路 242pa～242pk および 242sa～242s1 は、RFIC などであり得る1つのモジュール上に実装され得る。トランシーバ 220 および 222 中の回路は他の様式でも実装され得る。 10

【0014】

[0018]例示的な実施形態では、送信回路 252pa～252pk、252sa～252s1 はそれぞれ、駆動増幅器 290pa～290pk、290sa～290s1 を含み得る。駆動増幅器 290pa～290pk、290sa～290s1 は、データプロセッサ / コントローラ 280 から第1の送信信号 292pa～292pk、292sa～292s1 (たとえば入力信号) を受信し得る。例示的な実施形態では、電力増幅器 254pa～254pk、254sa～254s1 はそれぞれ、駆動増幅器 290pa～290pk、290sa～290s1 から第2の送信信号 294pa～294pk、294sa～294s1 を受信し得る。例示的な実施形態では、第1の送信信号 292pa～292pk、292sa～292s1 および / または第2の送信信号 294pa～294pk、294sa～294s1 は、差動信号 (たとえば、図3の第1の差動信号 334 および第2の差動信号 336 または図4の第1の差動信号 (PA入力+) 450 および第2の差動信号 (PA入力-) 452) を含み得る。 20

【0015】

[0019]電力増幅器 254pa～254pk、254sa～254s1 のうちの1つもしくは複数および / または駆動増幅器 290pa～290pk、290sa～290s1 のうちの1つもしくは複数は、図3～4 および 7 に関連してさらに詳細に説明するように、差動カスコード増幅器 (たとえば、第1のゲート端子 312 を有する第1のトランジスタ 304 と第2のゲート端子 314 を有する第2のトランジスタ 306 とを含む図3の差動カスコード増幅器 302) と、トランジスタ (たとえば、図3のトランジスタ 320) と、第1のゲート端子 312 と制御ノード (たとえば、図3の制御ノード 326) とに結合された第1の高インピーダンス要素 (たとえば、図3の第1の高インピーダンス要素 322) と、第2のゲート端子 314 と制御ノードとに結合された第2の高インピーダンス要素 (たとえば、図3の第2の高インピーダンス要素 324) とを含み得る。 30

【0016】

[0020]たとえば、駆動増幅器 290pa～290pk、290sa～290s1 のうちの1つまたは複数が、データプロセッサ / コントローラ 280 から第1の送信信号 (たとえば、それぞれ 292pa～292pk、292sa～292s1 のうちの1つ) を受信し増幅するように動作可能である、図3の差動カスコード増幅器 302 を含み得る。別の例として、電力増幅器 254pa～254pk、254sa～254s1 のうちの1つまたは複数が、駆動増幅器 290pa～290pk、290sa～290s1 のうちの1つまたは複数から第2の送信信号 (たとえば、それぞれ 294pa～294pk、294sa～294s1) を受信し増幅するように動作可能である、図3の差動カスコード増幅器 302 を含み得る。追加または代替として、図4のシステム 400 は、PA 254pa～254pk、254sa～254s1 のうちの1つもしくは複数および / または DA 290pa～290pk、290sa～290s1 のうちの1つもしくは複数に含められ得るか、あるいはそれらを実装するために使用され得る。 40

【0017】

[0021]図3～7をさらに参照しながら説明するように、電力増幅器 254pa～254s1 を含む。 50

p k、254sa～254s1のうちの1つもしくは複数および／または駆動増幅器290pa～290pk、290sa～290s1のうちの1つもしくは複数の信頼性、電力消費量、および応答線形性は、トランジスタ320が差動カスコード増幅器302のそれぞれ2つのトランジスタ304、306の2つのゲート端子312、314に結合される、図3の差動カスコード増幅器302を使用して改善され得る。

#### 【0018】

[0022]データプロセッサ／コントローラ280は、ワイヤレスデバイス110のための様々な機能を実施し得る。たとえば、データプロセッサ／コントローラ280は、受信機230pa～230pk、230sa～230s1を介して受信されているデータおよび送信機250pa～250pk、250sa～250s1を介して送信されているデータのための処理を実施し得る。データプロセッサ／コントローラ280は、トランシーバ220および222内の様々な回路の動作を制御し得る。たとえば、データプロセッサ／コントローラ280は、PA 254paに制御信号296paを与え得る。制御信号296paは、イネーブル信号（たとえば、図3のイネーブル信号330または図4のイネーブル信号（TURN\_ON）440）と、バイアス電圧（たとえば、図3のバイアス電圧332または図4の第1のバイアス信号（Vdc\_cas\_ON）442および第2のバイアス信号（Vdc\_cas\_OF\_F）444）とを含み得る。データプロセッサ／コントローラ280は、PA 254pa～254pk、254sa～254s1および／またはDA 290pa～290pk、290sa～290s1に、同様の制御信号を与え得る。メモリ282は、データプロセッサ／コントローラ280のためのプログラムコードとデータとを記憶し得る。データプロセッサ／コントローラ280は、1つまたは複数の特定用途向け集積回路（ASIC）および／または他のIC上に実装され得る。

10

#### 【0019】

[0023]ワイヤレスデバイス110は、複数のバンドグループ、複数の無線技術、および／または複数のアンテナをサポートし得る。ワイヤレスデバイス110は、複数のバンドグループ、複数の無線技術、および／または複数のアンテナを介した受信をサポートするために、いくつかのLNAを含み得る。図1および図2のワイヤレスデバイス110は、図3～図4および図7に関連してさらに説明するように、差動カスコード増幅器の1つまたは複数のトランジスタに損傷を与える可能性を低減する例示的なデバイス（差動カスコード増幅器、トランジスタ、第1の高インピーダンス要素、および第2の高インピーダンス要素を含む）を示している。

20

#### 【0020】

[0024]図3を参照すると、増幅システム300の例示的な実施形態が示されている。増幅システム300は、電力増幅器または駆動増幅器に含められ得る。例として本明細書で説明するように、増幅システム300は、PA 254paに含められても、PA 254paを実装するために使用されてもよい。他の例示的な実施形態では、増幅システム300は、図2の電力増幅器254pa～254pk、254sa～254s1のうちの1つもしくは複数、または駆動増幅器290pa～290pk、290sa～290s1のうちの1つもしくは複数に含められるか、またはそれらを実装するために使用され得る。

30

#### 【0021】

[0025]増幅システム300は、第1のゲート端子312を有する第1のトランジスタ304と第2のゲート端子314を有する第2のトランジスタ306とを含む差動カスコード増幅器302を含み得る。差動カスコード増幅器302はまた、第1のトランジスタ304に結合された第3のトランジスタ308と、第2のトランジスタ306に結合された第4のトランジスタ310とを含み得る。第1のトランジスタ304と第3のトランジスタ308は第1のカスコードトランジスタ対を形成し得、第2のトランジスタ306と第4のトランジスタ310は第2のカスコードトランジスタ対を形成し得る。第3のトランジスタ308は第1の差動信号334を受信するように構成され得、第4のトランジスタ310は第2の差動信号336を受信するように構成され得る。例示的な実施形態では、差動信号334、336は、図2のDA 290paから受信された第2の送信信号29

40

50

4 p a に対応し得る。他の例示的な実施形態では、差動信号は、図 2 の第 1 の送信信号 2 9 2 p a ~ 2 9 2 p k、2 9 2 s a ~ 2 9 2 s l のうちの 1 つもしくは複数および / または第 2 の送信信号 2 9 4 p a ~ 2 9 4 p k、2 9 4 s a ~ 2 9 4 s l のうちの 1 つもしくは複数に対応し得る。

【 0 0 2 2 】

[0026] 増幅システム 3 0 0 はまた、第 1 のゲート端子 3 1 2 と第 2 のゲート端子 3 1 4 とに結合されたトランジスタ 3 2 0 (たとえばメイントランジスタ) を含み得る。図 3 に示す例示的な実施形態では、トランジスタ 3 2 0 は、p 形金属酸化物半導体 (PMOS) トランジスタであってもよい。代替的に、トランジスタ 3 2 0 は、他の例示的な実施形態では n 形金属酸化物半導体 (NMOS) トランジスタであってもよい。トランジスタ 3 2 0 は、スイッチとして動作し得る。トランジスタ 3 2 0 のゲート端子は、第 1 のゲート端子 3 1 2 を第 2 のゲート端子 3 1 4 に選択的に結合するために、イネーブル信号 3 3 0 に応答し得る。たとえば、トランジスタ 3 2 0 のドレイン端子は第 2 のゲート端子 3 1 4 に結合され得、トランジスタ 3 2 0 のソース端子は第 1 のゲート端子 3 1 2 に結合され得る。例示的な実施形態では、イネーブル信号 3 3 0 およびバイアス電圧 3 3 2 は、図 2 における制御信号 2 9 6 p a としてデータプロセッサ / コントローラ 2 8 0 から受信され得る。トランジスタ 3 2 0 が伝導するとき (たとえば、電流がソース端子とドレイン端子との間で伝搬するとき)、第 1 のゲート端子 3 1 2 はトランジスタ 3 2 0 を介して第 2 のゲート端子 3 1 4 に結合される。

【 0 0 2 3 】

[0027] 加えて、増幅システム 3 0 0 は、第 1 のゲート端子 3 1 2 と制御ノード 3 2 6 とに結合された第 1 の高インピーダンス要素 (Z) 3 2 2 と、第 2 のゲート端子 3 1 4 と制御ノード 3 2 6 とに結合された第 2 の高インピーダンス要素 (Z) 3 2 4 とを含み得る。高インピーダンス要素 3 2 2 および 3 2 4 はそれぞれ、制御ノード 3 2 6 とゲート端子 3 1 2、3 1 4 との間に高インピーダンスをもたらし得る。高インピーダンス要素 3 2 2 および 3 2 4 の各々は高インピーダンス値を有し得、トランジスタ 3 2 0 ならびに高インピーダンス要素 3 2 2 および 3 2 4 は、制御ノード 3 2 6 に与えられるバイアス電圧 3 3 2 に基づいて付勢されるように、第 1 のゲート端子 3 1 2 および第 2 のゲート端子 3 1 4 の各々をイネーブルし得る。第 1 の例示的な実施形態では、第 1 の高インピーダンス要素 3 2 2 および第 2 の高インピーダンス要素 3 2 4 は抵抗器であってもよい。たとえば、高インピーダンス要素 3 2 2 および 3 2 4 はそれぞれ、少なくとも 10 キロオームの抵抗を有し得る。第 2 の例示的な実施形態では、第 1 の高インピーダンス要素 3 2 2 および第 2 の高インピーダンス要素 3 2 4 はインダクタであってもよい。たとえば、高インピーダンス要素 3 2 2 および 3 2 4 は、周波数依存の高インピーダンス値をもたらすインダクタであってもよい。

【 0 0 2 4 】

[0028] 動作の間、増幅システム 3 0 0 は、DA 2 9 0 p a から差動信号 3 3 4 および 3 3 6 を受信する。差動カスコード増幅器 3 0 2 の第 1 の動作モード (たとえば、イネーブルまたはアクティブモード) の間、イネーブル信号 3 3 0 がアサートされ、トランジスタ 3 2 0 は、第 1 のゲート端子 3 1 2 を第 2 のゲート端子 3 1 4 に結合するようにアクティベートされる。差動カスコード増幅器 3 0 2 に、受信された差動信号 3 3 4、3 3 6 を増幅させ、図 2 のアンテナインターフェース回路 2 2 4 へその増幅された差動出力信号 3 4 0、3 4 2 を供給させるため、第 1 のゲート端子 3 1 2 および第 2 のゲート端子 3 1 4 は、第 1 の動作モードの間にトランジスタ 3 0 4、3 0 6 をイネーブルする (たとえばオンにする) のに十分な特定の電圧レベル (たとえば 1 ボルト) にあるバイアス電圧 3 3 2 によって付勢され得る。

【 0 0 2 5 】

[0029] 第 2 の動作モード (たとえば、ディスエーブルまたは非アクティブモード) の間、イーンブル信号 3 3 0 はデアサートされ、トランジスタ 3 2 0 はデアクティベートされ、バイアス電圧 3 3 2 は、論理低の電圧レベル (たとえば 0 ボルト) に設定される。トランジ

10

20

30

40

50

ンジスタ 320 をデアクティベートすることにより、第 1 のゲート端子 312 から第 2 のゲート端子 314 までのインピーダンスが増加する（たとえばインピーダンス増加が促進される）。インピーダンス増加は、第 1 の高インピーダンス要素 322 および第 2 の高インピーダンス要素 324 上で少なくとも部分的に付勢され得る。インピーダンスを増加することは、第 1 のゲート端子 312 を第 2 のゲート端子 314 から分離するかまたは実質的に分離することになり、ゲート端子 312、314 におけるゲート電圧が独立に「浮動する」ことが可能となり得る。ゲート電圧は「浮動する」ため、各ゲート電圧は、トランジスタ 304、306 のドレインゲート間寄生キャパシタンスに起因するそれぞれのドレイン電圧に応答し得る。たとえば、第 1 のゲート端子 312 における第 1 のゲート電圧は、第 1 のトランジスタ 304 の第 1 のドレイン端子における第 1 のドレイン電圧を「追跡する」ことが可能である（たとえば、その第 1 のドレイン電圧に応答して電圧を変化させ得る）。同様に、第 2 のゲート端子 314 における第 2 のゲート電圧は、第 2 のトランジスタ 306 の第 2 のドレイン端子における第 2 のドレイン電圧を「追跡する」ことが可能である。したがって、ゲート電圧が第 2 の動作モードの間に変化しない（たとえば、論理低の電圧値に固定される）他の差動カスコード増幅器と比較して、ゲート端子 312、314 におけるゲート電圧は、それぞれのドレイン電圧に応答して電圧を変化させるため、トランジスタ 304、306 のドレインゲート間電圧は、第 2 の動作モードの間に低減され得る。10

#### 【0026】

[0030] ドレインゲート間電圧を低減することは、図 4 を参照しながらより詳細に説明するシステム 400 など、オフ状態にある複数のユニットセル（たとえば、ゲインセル）を含む増幅器内のトランジスタにかかる電圧「ストレス」を低減することになり得る。複数のユニットセルを含み、トランジスタ 320 と高インピーダンス要素 322、324 とを含まない特定の増幅器では、ドレイン端子における電圧は、トランジスタに対して電圧「ストレス」を引き起こすように十分に高いレベルに到達し得る。たとえば、トランジスタ 320 と高インピーダンス要素 322 および 324 とを含まない他の差動カスコード増幅器では、ゲート電圧は、差動カスコード増幅器がディスエーブルされているとき、論理低の電圧レベル（たとえば 0 ボルト）に「強制される」。しかしながら、そのような他の差動カスコード増幅器内にあるトランジスタのドレイン端子は、同じトランシーバの他のユニットセル内にある他のトランジスタの他のドレイン端子に結合され得る。複数の他のユニットセルはアクティブとなり、それぞれのゲート電圧が論理低の電圧レベルに「強制されて」いる間に他の差動カスコード増幅器のトランジスタのドレイン端子における電圧を高電圧レベルに到達させ得る。したがって、他の差動カスコード増幅器のトランジスタは、他の差動カスコード増幅器がディスエーブルされているとき、高いドレインゲート間電圧を経験する。高いドレインゲート間電圧は、トランジスタに電圧「ストレス」を引き起こし得るが、この電圧「ストレス」は、トランジスタに損傷を引き起こし、他の差動カスコード増幅器の信頼性を低減し得る。30

#### 【0027】

[0031] 対照的に、トランジスタ 320 は、増幅システム 300 がトランジスタ 304 および 306 への損傷を防止または低減することを可能にする。たとえば、トランジスタ 320 がデアクティベートされているとき、ゲート端子 312 および 314 のゲート電圧は、論理低の電圧レベルに強制される代わりに、それぞれのドレイン電圧を「追跡する」。したがって、トランジスタ 304 および 306 のドレインゲート間電圧は、トランジスタ 304 および 306 に対する電圧「ストレス」を低減する。電圧「ストレス」を低減することは、差動カスコード増幅器 302 がディスエーブルされているときに、トランジスタ 304 および 306 への損傷を防止または低減することになり得る。40

#### 【0028】

[0032] 加えて、トランジスタ 320 は、差動カスコード増幅器 302 の線形性（たとえば、増幅された差動出力信号 340、342 と受信された差動信号 334、336 との間の線形性）を増大させ得る。本明細書で使用するとき、「スイッチド」構成で構成された

10

20

30

40

50

差動力スコード増幅器は、図3に示すように、トランジスタのゲート端子をトランジスタ320および高インピーダンス要素322、324に結合された差動力スコード増幅器を指す。対照的に、「ゲート結合」構成で構成された差動力スコード増幅器は、トランジスタのゲート端子が互いに直接結合された差動力スコード増幅器（たとえば、トランジスタ320および高インピーダンス要素322、324を含まない差動力スコード増幅器）を指す。それぞれのドレイン電圧を「追跡する」ために、ゲート端子312、314におけるゲート電圧をイネーブルすることによって、「スイッチド」構成をなす差動力スコード増幅器302は、「ゲート結合」構成をなす差動力スコード増幅器と比較して、増幅された差動出力信号340、342と受信された差動信号334、336との間の線形性を改善している。たとえば、「ゲート結合」構成では、トランジスタのドレイン電圧は、それぞれのゲート電圧を下回り、それによって第2の動作モード（たとえば非アクティブモード）の間にトランジスタをオンにし得る。非アクティブモードの間にトランジスタをオンにすることは、漏れ電流を増加させ、「ゲート結合」構成をなす差動力スコード増幅器の線形性を低減することになる。10

#### 【0029】

[0033]「スイッチド」構成では、ゲート端子312、314のゲート電圧は、ドレイン電圧がそれぞれのゲート電圧を下回らないように、トランジスタ304、306のドレイン電圧に応答して変化する。したがって、トランジスタ304、306は、非アクティブモードの間にイネーブルされず（たとえばオンにされず）、差動出力信号340、342の線形性は、「ゲート結合」構成をなす差動力スコード増幅器と比較して増大される。改善された線形性に関係するさらなる詳細について、図4～図6を参照しながら説明する。20

#### 【0030】

[0034]図4を参照すると、トランジスタに対する電圧「ストレス」を低減した差動増幅をもたらすシステム400の例示的な実施形態が示されている。例示的な実施形態では、システム400は、電力増幅器または駆動増幅器に含められ得る。たとえば、本明細書で説明するように、システム400は、図2の電力増幅器254paを含んでも、それを実装するために使用されてもよい。他の例示的な実施形態では、システム400は、図2の電力増幅器254pa～254pk、254sa～254s1のうちの1つもしくは複数および/または駆動増幅器290pa～290pk、290sa～290s1のうちの1つもしくは複数に含められ得るか、またはそれらを実装するために使用され得る。30

#### 【0031】

[0035]システム400は、増幅器段402とアンテナ404とを含み得る。増幅器段402は、各々が電力増幅器を形成する複数のN個の「ユニットセル」（たとえば部分）を含み得、ここでNは正の整数である。たとえば、アンテナ404はアンテナ210に対応し得、各ユニットセルは、図2のPA 254pa～254pk、254sa～254s1のうちの1つまたは複数に含められても、それらを実装するために使用されてもよい。増幅器段402およびアンテナ404は、変圧器408を介するなど、出力負荷を介して磁気的に結合され得る。たとえば、変圧器408は、図2のアンテナインターフェース回路224に対応し得る。システム400の構成要素は、送信機（たとえば図2の送信機250pa）に対応してもよく、または送信機の中に組み込まれてもよい。40

#### 【0032】

[0036]増幅器段402（たとえば複数のユニットセル）は、差動力スコード増幅器412を有し、さらにトランジスタ（MPSW）420（たとえばメイントランジスタ）を有する例示的なユニットセル410を含み得る。差動力スコード増幅器412は、第1のトランジスタ（M1pc）422と、第2のトランジスタ（M1nc）424と、第1のトランジスタ（M1pc）422に結合された第3のトランジスタ（M1p）426と、第2のトランジスタ（M1nc）424に結合された第4のトランジスタ（M1n）428とを含み得る。第1のトランジスタ（M1pc）422と第3のトランジスタ（M1p）426は第1のカスコードトランジスタ対を形成し得、第2のトランジスタ（M1nc）424と第4のトランジスタ（M1n）428は第2のカスコードトランジスタ対を形成50

し得る。

【0033】

[0037]トランジスタ(MPSW)420は、第1のトランジスタ(M1pc)422の第1のゲート端子436と、第2のトランジスタ(M1nc)424の第2のゲート端子438とに結合され得る。例示的な実施形態では、トランジスタ(MPSW)420はPMOSトランジスタであってもよく、またスイッチとして動作し得る。トランジスタ(MPSW)420は、イネーブル信号(Turn\_ON)440に応答する入力端子を含み得る。例示的な実施形態では、イネーブル信号(Turn\_ON)440、第1のバイアス電圧(Vdc\_cas\_ON)442、および第2のバイアス電圧(Vdc\_cas\_OFF)444は、図2の制御信号296paとしてコントローラ280から受信され得る。ユニットセル410は、制御ノード434と、トランジスタ(MPSW)420の第1の端子にさらに結合される第1のゲート端子436とに結合される第1の抵抗器414(たとえば第1の高インピーダンス要素)をさらに含み得る。ユニットセル410は、制御ノード434と第2のゲート端子438とに結合され、トランジスタ(MPSW)420の第2の端子にさらに結合される第2の抵抗器416(たとえば第2の高インピーダンス要素)をさらに含み得る。抵抗器414および416の各々は、少なくとも10キロオームの抵抗を有し得る。

【0034】

[0038]差動力スコード増幅器412は変圧器408に結合され得る。たとえば、第1のトランジスタ(M1pc)422の第1のドレイン端子は第1のノード430を介して変圧器408に結合され得、第2のトランジスタ(M1nc)424の第2のドレイン端子は第2のノード432を介して変圧器408に結合され得る。複数のユニットセルのうちの他のユニットセルが、同様の様式で、第1のノード430と第2のノード432とに結合され得る(たとえば、ノード430および432の各々が、複数のユニットセルのうちの各々に結合され得る)。変圧器408は、N個のユニットセルの増幅された差動出力(たとえば、VoutpおよびVoutn)をアンテナ404に与えるように構成され得る。たとえば、ノード430および432において受信された増幅された差動出力は、各アクティブなユニットセルの差動力スコード増幅器の出力に基づき得るものであり、変圧器408とアンテナ404との間で上述の磁気結合を介してアンテナ404に与えられ得る。したがって、増幅器段402の各ユニットセルは、アクティベートされると、増幅された差動出力(VoutpおよびVoutn)に寄与する。

【0035】

[0039]増幅器段402の各ユニットセルは、例示的なユニットセル410と同様の構成を有し得る。たとえば、各ユニットセルは、対応する差動力スコード増幅器と、対応するトランジスタ(たとえば、トランジスタ(MPSW)420に対応するトランジスタ)と、対応する抵抗器(たとえば高インピーダンス要素)とを含み得、各ユニットセルは、ノード430および432を介して変圧器408に結合され得る。各ユニットセルは、対応するイネーブル信号に基づいて選択的にアクティベートされ得る。たとえば、スイッチの対応するサブセットをデアクティベートすることによって(たとえば、イネーブル信号の対応するサブセットをアサートすることを介して)、ユニットセルのサブセットがデアクティベートされ得る。N個のユニットセルの選択的なアクティベーションにより、増幅器段402の利得が調節され得る。

【0036】

[0040]動作の間、増幅器段402は、差動信号(PA入力+450およびPA入力-452)に応答し得る。例示的な実施形態では、差動信号(PA入力+)450および(PA入力-)452は、第2の送信信号294paとしてDA290paから受信され得る。差動力スコード増幅器412の第3のトランジスタ(M1P)426および第4のトランジスタ(M1n)428は、差動信号(PA入力+)450および(PA入力-)452に応答し得る。差動力スコード増幅器412は、イネーブル信号(Turn\_ON)440に基づいて種々の動作モードで動作し得る。イネーブル信号(Turn\_ON)440

40 およびスイッチのペアが制御ノード434を付勢するために使用され得る。たとえば、イネーブル信号(Turn\_ON)440がアサートされるとき、制御ノード434は、第1のバイアス信号(Vdc\_cas\_ON)442によって付勢され得、イネーブル信号(Turn\_ON)440がデアサートされるとき、制御ノード434は第2のバイアス信号(Vdc\_cas\_OFF)444によって付勢され得る。例示的な実施形態では、第1のバイアス信号(Vdc\_cas\_ON)442は、特定の電圧レベル(たとえば、ほぼ1ボルトまたはトランジスタ422、424をイネーブルするのに十分な任意の電圧)において実質的に一定の電圧を与え得、第2のバイアス信号(Vdc\_cas\_OFF)444は、論理低の電圧レベル(たとえば、ほぼ0ボルト)において実質的に一定の電圧を与え得る。

10

### 【0037】

[0041]差動力スコード増幅器412の第1の動作モード(たとえば、「オン」モードまたはアクティベートモード)の間、第1のトランジスタ(M1pc)422および第2のトランジスタ(M1nc)424は、変圧器408を介してアンテナ404に与えられる増幅差動出力(たとえばVoutpおよびVoutn)に寄与するように、第1のバイアス信号(Vdc\_cas\_ON)442に基づいてアクティベートされ得る。第1のモードの間、トランジスタ(MPSW)420は、第1のゲート端子436を第2のゲート端子438に結合するために、イネーブル信号(Turn\_ON)440の第1の値(たとえば論理低の電圧レベル)に基づいてアクティベートされ得る。第1のゲート端子436および第2のゲート端子438は、第1のバイアス信号(Vdc\_cas\_ON)442に基づいて、抵抗器414および416を介して付勢され得る。

20

### 【0038】

[0042]差動力スコード増幅器412の第2の動作モード(たとえば、「オフ」モードまたはデアクティベートモード)の間、イネーブル信号(Turn\_ON)440は、第2の値(たとえば、特定の電圧レベル)にアサートされ得る。抵抗器414および416を介した第1のゲート端子436から第2のゲート端子438へのインピーダンスを増大させるために、イネーブル信号(Turn\_ON)440をデアサートすることにより、トランジスタ(MPSW)420がデアクティベートされる。第1のゲート端子436から第2のゲート端子438へのインピーダンスを増大させることは、第1のゲート端子436を第2のゲート端子438から分離するか、または実質的に分離することになり得る。たとえば、抵抗器414および416と組み合わせて、第1のゲート端子436における第1のゲート電圧(Vcgate)が第2のゲート端子438における第2のゲート電圧(Vcngate)から実質的に独立し得るように、デアクティベートされたトランジスタ(MPSW)420のインピーダンスは、十分に高くなり得る。

30

### 【0039】

[0043]ゲート端子436と438とを分離するかまたは実質的に分離することは、第1のゲート電圧(Vcgate)および第2のゲート電圧(Vcngate)がそれぞれ第1のトランジスタ(M1pc)422および第2のトランジスタ(M1nc)424のドレイン電圧に応答する(たとえば、それを「追跡する」)ことを可能にし得る。たとえば、第1のゲート端子436は、トランジスタ(MPSW)420がデアクティベートされているときに第2のゲート端子438に対して分離されるか、または実質的に分離されるため、第1のゲート電圧(Vcgate)は、第1のトランジスタ(M1pc)422の第1のドレイン電圧(Voutp)に基づいて第1の電圧へと「浮動する」ことがある。第1のゲート電圧(Vcgate)は、第1のトランジスタ(M1pc)422の第1のゲート端子436と第1のドレイン端子との間の容量結合が原因で「浮動する」ことがある。この例では、第1のゲート電圧(Vcgate)は、第1のドレイン電圧(Voutp)の電圧変化(たとえば「スイング」)に比例する電圧変化(たとえば「スイング」)を有し得るが、第1のトランジスタ(M1pc)422がオンにならないような十分に低い電圧レベルに依然としてある。第2のゲート電圧(Vcngate)は、第2のトランジスタ(M1nc)424の第2のドレイン電圧(Voutn)に基づいて

40

50

、（たとえば、第2のトランジスタ（M1nC）424の第2のゲート端子438と第2のドレイン端子との間の容量性結合が原因で）同様に第2の電圧に「浮動する」ことがある。

#### 【0040】

[0044]したがって、第1のトランジスタ（M1pC）422に関連付けられる第1のドレインゲート間電圧差および第2のトランジスタ（M1nC）424に関連付けられる第2のドレインゲート間電圧差は、増幅器のトランジスタのゲート端子がバイアス信号を介して共通の論理低の電圧レベルに「強制される」デバイス（たとえば、他の差動カスコード増幅器）と比較して低減され得る。図3に関して上記で説明したように、高いドレインゲート間電圧は、トランジスタに損傷を与えることがあり、また増幅器の信頼性を減じることもある電圧「ストレス」を、トランジスタに対して引き起こす。ドレインゲート間電圧を低減することは、トランジスタ422および424に損傷を与える可能性を低減することになり、それによって差動カスコード増幅器412の信頼性が向上する。10

#### 【0041】

[0045]差動カスコード増幅器のトランジスタのゲート端子が、「ゲート結合」構成で互いに直接結合されるデバイス（たとえば、トランジスタ（MPSW）420ならびに抵抗器414および416のないデバイス）では、ゲート端子は、差動カスコード増幅器がデアクティベートされるときに論理低の電圧レベル（たとえば0ボルト）で付勢される。しかしながら、トランジスタのドレイン電圧は、デバイスの他のアクティベートされたユニットセルに少なくとも部分的に基づいて、 $2 * V_{dd}$ （たとえばレール電圧）の値に到達し得る。したがって、トランジスタのドレインゲート間電圧は、1つのユニットセルがデアクティベートされているとき、 $2 * V_{dd}$ 程度の大きさになり得る。そのような大きなドレインゲート間電圧は、トランジスタに「ストレス」を引き起こし、「ゲート結合」構成で構成された差動カスコード増幅器のトランジスタに損傷を与える（たとえば、トランジスタのゲート酸化物領域に損傷を与える）可能性が増大する。20

#### 【0042】

[0046]システム400（たとえば、「スイッチド」構成で構成されたシステム）では、第2の動作モードの間に第1のゲート端子436を第2のゲート端子438から分離するかまたは実質的に分離するために、トランジスタ（MPSW）420と抵抗器414および416とを使用することにより、トランジスタ422および424にかかる電圧「ストレス」は、第1のゲート電圧（ $V_{cp gate}$ ）と第2のゲート電圧（ $V_{cn gate}$ ）とを論理低の電圧レベル（たとえば、ほぼ0ボルト）に「強制する」とことと比較して低減される。たとえば、第1のゲート電圧（ $V_{cp gate}$ ）は第1のドレイン電圧を「追跡する」ことが可能であり、したがって、ドレインゲート間電圧が低減され、第1のトランジスタ（M1pC）422に損傷を与える可能性が低減される。30

#### 【0043】

[0047]追加的に、トランジスタ（MPSW）420を使用して、第1のゲート電圧（ $V_{cp gate}$ ）および第2のゲート電圧（ $V_{cn gate}$ ）がそれぞれのドレイン電圧に応答するようにすることは、「ゲート結合」構成で構成された差動カスコード増幅器と比較して、差動カスコード増幅器412の線形性（たとえば、増幅された差動出力（たとえば $V_{out p}$ および $V_{out n}$ ）と差動信号（PA入力+）450および（PA入力-）452との間の関係の線形性）を増大させることになり得る。たとえば、第1のゲート電圧（ $V_{cp gate}$ ）および第2のゲート電圧（ $V_{cn gate}$ ）がそれぞれのドレイン電圧に応答するようにすることは、ゲート電圧がそれぞれのドレイン電圧を超えることを防止するか、またはその可能性を低減することになる。したがって、トランジスタは第2の動作モード（たとえばデアクティベートモード）の間、オフのままであるため、第1のトランジスタ（M1pC）422および第2のトランジスタ（M1nC）424における漏れ電流が回避または低減され得る。対照的に、「ゲート結合」構成で構成された差動カスコード増幅器では、トランジスタは、第2の動作モードの間、オンになるかまたは部分的にオンになり得、それによって対応する差動カスコード増幅器の線形性が低減する（た4050

とえば低下する)。

【0044】

[0048]「スイッチド」構成で構成された差動カスコード増幅器412を含む(たとえば、トランジスタ(MPSW)420と抵抗器414、416とを含む)システム400は、「ゲート結合」構成で構成された差動カスコード増幅器と比較して、付加的な性能上の利点をもたらし得る。図5を参照すると、「スイッチド」構成で構成された差動カスコード増幅器(本明細書では「スイッチド構成DCA」と呼ぶ)および「ゲート結合」構成で構成された差動カスコード増幅器(本明細書では「ゲート結合構成DCA」と呼ぶ)の飽和時電力出力(Psat)および振幅変調ごとの位相変調(AM-PM)のグラフが示されており、全体として500で示されている。例示的な実施形態では、スイッチド構成DCAは、図3の増幅システム300の差動カスコード増幅器302または図4のシステム400の差動カスコード増幅器412に対応し得る。グラフ500は、例示的な非限定的な値を表している。他の実施形態では、PsatおよびAM-PMの他の値が達成され得る。

10

【0045】

[0049]グラフ500は、スイッチド構成DCAに関連付けられる第1のAM-PM曲線502と、ゲート結合構成DCAに関連付けられる第2のAM-PM曲線504とを含んでいる。AM-PM曲線502、504は、2つの差動カスコード増幅器に対するAM-PMと無線周波数電力(Prf)との間の関係を示す。図5に示すように、スイッチド構成DCAに関連付けられるAM-PM変動は、ゲート結合構成DCAに関連付けられるAM-PM変動と比較して低減されている(たとえばより小さくなっている)。たとえば、「スイッチド」構成のAM-PM値は、P2における第1のAM-PM値510とP3における第2のAM-PM値512との間のAM-PM差によって示されるように、0とP3との間のPrf値に対して3度以内で変動し得る。「ゲート結合」構成のAM-PM値は、P1における第3のAM-PM値514とP3における第4のAM-PM値516との間のAM-PM差によって示されるように、0とP3との間のPrf値に対して4度以内で変動し得る。したがって、「スイッチド」構成は、「ゲート結合」構成と比較して、0とP3との間のPrf値に対する少なくとも1度のAM-PM変動の低減に関連付けられる。

20

【0046】

30

[0050]グラフ500はまた、スイッチド構成DCAに関連付けられる第1のPsat曲線506と、ゲート結合構成DCAに関連付けられる第2のPsat曲線508とを含んでいる。Psat曲線506、508は、2つの差動カスコード増幅器に対するPsatとPrfとの間の関係を示す。図5に示すように、スイッチド構成DCAのPsatは、ゲート結合構成DCAのPsatと比較して増大されている。たとえば、第1のPrf値P1において、スイッチド構成DCAに関連付けられる第1のPsat値520は約29.4デジベル(dB)であり、ゲート結合構成DCAに関連付けられる第2のPsat値522は約28.9dBである。したがって、「スイッチド」構成は、「ゲート結合」構成と比較して、Psatにおける増大(たとえば約0.5dBの増大)に関連付けられる。

40

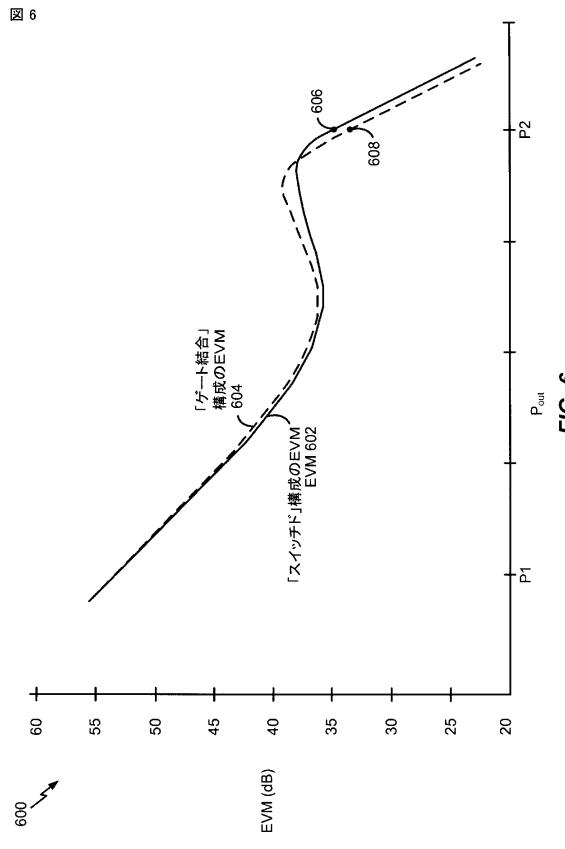

【0047】

[0051]付加的な性能上の改善が図6に示されており、ここにおいて、スイッチド構成DCAおよびゲート結合構成DCAのエラーベクトル振幅(EVM)のグラフが示されており、全体として600で示されている。グラフ600は、例示的な非限定的な値を表している。他の実施形態では、EVMの他の値が達成され得る。グラフ600は、スイッチド構成DCAに関連付けられる第1のEVM曲線602と、ゲート結合構成DCAに関連付けられる第2のEVM曲線604とを含んでいる。EVM曲線602、604は、2つの差動カスコード増幅器に対するEVMと出力電力(Pout)との間の関係を示す。図6に示すように、スイッチド構成DCAのEVMは、低い値のPoutにおいてはゲート結合構成DCAのEVMと実質的に同様であり、また高い値のPoutにおいては増大され

50

ている。たとえば、第1のPout値P1において、スイッチド構成DCAに関連付けられるEVMは、ゲート結合構成DCAに関連付けられるEVMと実質的に同様である。P1よりも大きい(たとえば高い)第2のPout値P2において、スイッチド構成DCAに関連付けられる第1のEVM値606は約34.9dBであり、ゲート結合構成DCAに関連付けられる第2のEVM値608は約33.3dBである。したがって、「スイッチド」構成は、「ゲート結合」構成と比較して、P2以上のPout値におけるEVMの増大(たとえば1.5dBを越える増大)に関連付けられる。

#### 【0048】

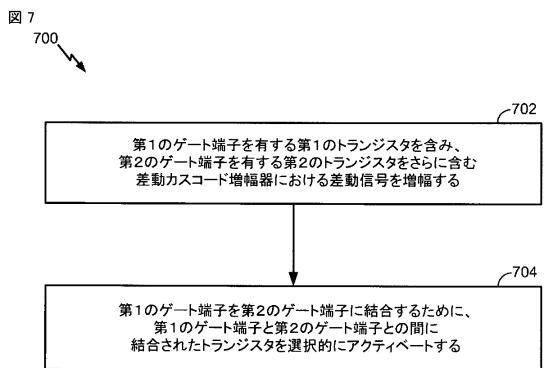

[0052]図7を参照すると、差動カスコード増幅器内のトランジスタのゲート端子を選択的に分離する方法の例示的な実施形態を示すフローチャートが示されており、全体として10 700で示されている。例示的な一実施形態では、方法700は、図1～図2のワイヤレスデバイス110、図3の増幅システム300、図4のシステム400、またはそれらの組合せにおいて実施され得る。

#### 【0049】

[0053]方法700は、702で、第1のゲート端子を有する第1のトランジスタを含み、第2のゲート端子を有する第2のトランジスタをさらに含む差動カスコード増幅器において、差動信号を増幅することを含み得る。差動カスコード増幅器は、図3の差動カスコード増幅器302もしくは図4の差動カスコード増幅器412を含むか、またはそれに対応し得る。第1のトランジスタは、図3の第1のトランジスタ304もしくは図4の第1のトランジスタ(M1pc)422を含むか、またはそれに対応し得る。第2のトランジスタは、図3の第2のトランジスタ306もしくは図4の第2のトランジスタ(M1nc)424を含むか、またはそれに対応し得る。20

#### 【0050】

[0054]方法700はまた、第1のゲート端子を第2のゲート端子に結合するために、第1のゲート端子と第2のゲート端子との間に結合されたトランジスタを選択的にアクティベートすることを含み得る。たとえば、トランジスタはそれぞれ、図3のトランジスタ320もしくは図4のトランジスタ(MPSW)420を含むかまたはそれに対応し得、またイネーブル信号(たとえば、図3のイネーブル信号330または図4のイネーブル信号(Turn\_ON)440)に応答し得る。

#### 【0051】

[0055]例示的な実施形態では、方法700は、第1の高インピーダンス要素および第2の高インピーダンス要素に少なくとも部分的に基づいて、第1のゲート端子から第2のゲート端子へのインピーダンスを増大させるために、トランジスタをデアクティベートすることを含む。第1の高インピーダンス要素は、第1のゲート端子および制御ノードに結合され得、第2の高インピーダンス要素は、第2のゲート端子および制御ノードに結合され得る。たとえば、トランジスタ320は、第1の高インピーダンス要素322および第2の高インピーダンス要素324に少なくとも部分的に基づいて、第1のゲート端子312から第2のゲート端子314へのインピーダンスを増大させるために、デアクティベートされ得る。別の例として、トランジスタ(MPSW)420は、第1の抵抗器414および第2の抵抗器416に少なくとも部分的に基づいて、第1のゲート端子436から第2のゲート端子438へのインピーダンスを増大させるために、デアクティベートされ得る。トランジスタをデアクティベートすることは、第1のゲート端子における第1の電圧が第1のトランジスタの第1のドレイン端子における第1のドレイン電圧に応答する(たとえば、第1のドレイン電圧を「追跡する」)ことを引き起こし得、また、第2のゲート端子における第2の電圧が第2のトランジスタの第2のドレイン端子における第2のドレイン電圧に応答する(たとえば、第2のドレイン電圧を「追跡する」)ことを引き起こし得る。たとえば、トランジスタ320をデアクティベートすることは、第1のゲート端子312における第1のゲート電圧が第1のトランジスタ304の第1のドレイン端子における第1のドレイン電圧に応答することを引き起こし得、また、第2のゲート端子314における第2のゲート電圧が第2のトランジスタ306の第2のドレイン端子における第2のドレイン電圧に応答することを引き起こし得る。40

10

20

30

40

50

のドレイン電圧に応答することを引き起こし得る。別の例として、トランジスタ (M P S W) 4 2 0 をデアクティベートすることは、第 1 のゲート端子 4 3 6 における第 1 のゲート電圧 (V c p g a t e) が第 1 のトランジスタ (M 1 p c) 4 2 2 の第 1 のドレイン端子における第 1 のドレイン電圧 (V o u t p) に応答することを引き起こし得、また、第 2 のゲート端子 4 3 8 における第 2 のゲート電圧 (V c n g a t e) が第 2 のトランジスタ (M 1 n c) 4 2 4 の第 2 のドレイン端子における第 2 のドレイン電圧 (V o u t n) に応答することを引き起こし得る。

#### 【 0 0 5 2 】

[0056]方法 7 0 0 は、増幅器段の利得制御を可能にする一方で、1つまたは複数のトランジスタにかかる電圧「ストレス」を低減する。たとえば、増幅器段の利得は、増幅器段の1つまたは複数のユニットセルをオンまたはオフにすることによって調節され得る。差動カスコード増幅器がオフにされているときに第 1 のゲート端子を第 2 のゲート端子から分離するかまたは実質的に分離するために、トランジスタおよび高インピーダンス要素を使用することにより、方法 7 0 0 は、差動カスコード増幅器がオフにされているとき、論理低の電圧レベル（たとえば、ほぼ 0 ボルト）に「強制された」ゲート端子を有するトランジスタと比較して、トランジスタのドレインゲート間電圧の低減を可能にする。ドレインゲート間電圧を低減することは、トランジスタに損傷を与える可能性を低減することになり、また差動カスコード増幅器の信頼性を向上させることになる。加えて、それぞれのドレイン電圧を追跡するためにゲート電圧をイネーブルすることは、差動カスコード増幅器の線形性（たとえば、増幅された差動出力と受信された差動入力との関係の線形性）を増大させることになる。10

#### 【 0 0 5 3 】

[0057]説明した実施形態とともに、ある装置が、差動信号を増幅するための手段を含む。増幅するための手段は、図 3 の差動カスコード増幅器 3 0 2、図 4 の差動カスコード増幅器 4 1 2、差動信号を増幅するための1つもしくは複数の他のデバイス、回路、モジュール、もしくは命令、またはそれらの任意の組合せを含み得るか、またはそれらに応答し得る。増幅するための手段は、第 1 のゲート端子を有する第 1 のトランジスタと、第 2 のゲート端子を有する第 2 のトランジスタとを含み得る。第 1 のトランジスタは、図 3 の第 1 のゲート端子 3 1 2 を有する第 1 のトランジスタ 3 0 4 または図 4 の第 1 のゲート端子 4 3 6 を有する第 1 のトランジスタ (M 1 p c) 4 2 2 を含み得るか、またはそれに対応し得、第 2 のトランジスタは、図 3 の第 2 のゲート端子 3 1 4 を有する第 2 のトランジスタ 3 0 6 または図 4 の第 2 のゲート端子 4 3 8 を有する第 2 のトランジスタ (M 1 n c) 4 2 4 を含み得るか、またはそれに対応し得る。20

#### 【 0 0 5 4 】

[0058]この装置は、第 1 のゲート端子を第 2 のゲート端子に選択的に結合するための手段を含み得る。選択的に結合するための手段は、図 3 のトランジスタ 3 2 0、図 4 のトランジスタ (M P S W) 4 2 0、第 1 のゲート端子を第 2 のゲート端子に選択的に結合するための1つもしくは複数の他のデバイス、回路、モジュール、もしくは命令、またはそれらの任意の組合せを含み得るか、またはそれらに応答し得る。30

#### 【 0 0 5 5 】

[0059]例示的な実施形態では、この装置は、第 1 のゲート端子と制御ノードとに結合された第 1 の高インピーダンス要素と、第 2 のゲート端子と制御ノードとに結合された第 2 の高インピーダンス要素とをさらに含み得る。第 1 の高インピーダンス要素および第 2 の高インピーダンス要素はそれぞれ、図 3 の第 1 の高インピーダンス要素 3 2 2 および第 2 の高インピーダンス要素 3 2 4、または図 4 の第 1 の抵抗器 4 1 4 および第 2 の抵抗器 4 1 6 を含み得るか、またはそれに対応し得る。制御ノードは、図 3 の制御ノード 3 2 6 または図 4 の制御ノード 4 3 4 を含むか、またはそれに対応し得る。40

#### 【 0 0 5 6 】

[0060]例示的な実施形態では、第 1 の高インピーダンス要素および第 2 の高インピーダンス要素は、抵抗器、インダクタ、またはそれらの組合せを含み得る。選択的に結合す50

るための手段は、第1のゲート端子を第2のゲート端子に結合するように増幅するための手段の第1の動作モードの間にアクティベートされ得、第1の高インピーダンス要素および第2の高インピーダンス要素を介して第1のゲート端子から第2のゲート端子へのインピーダンスを増大させるように増幅するための手段の第2の動作モードの間にデアクティベートされ得る。たとえば、選択的に結合するための手段は、図3～図4および図7を参照しながら説明したように、ドレイン電圧に応答する（たとえばドレイン電圧を「追跡する」）ためにゲート電圧をイネーブルするために、第1のゲート端子を第2のゲート端子から分離し得るか、または実質的に分離し得る。

#### 【0057】

[0061] 本明細書で開示した実施形態に関して説明した様々な例示的な論理ブロック、構成、モジュール、回路、およびアルゴリズムステップは、電子ハードウェア、プロセッサによって実行されるコンピュータソフトウェア、または両方の組合せとして実装され得ることを、当業者はさらに諒解されよう。たとえば、図2の制御信号296p a、図3のイネーブル信号330、図4のイネーブル信号（Turn\_ON）440、またはそれらの組合せは、命令を実行するプロセッサによって生成され得る。様々な例示的な構成要素、ブロック、構成、モジュール、回路、およびステップが、上記では概して、それらの機能に関して説明された。そのような機能がハードウェアとして実装されるか、プロセッサ実行可能命令として実装されるかは、特定の適用例および全体的なシステムに課された設計制約に依存する。当業者は、説明された機能を特定の適用例ごとに様々な方法で実装し得るが、そのような実装の決定は、本開示の範囲からの逸脱を生じるものと解釈されるべきではない。 10

#### 【0058】

[0062] 本明細書で開示する実施形態に関して説明した方法またはアルゴリズムのステップは、直接ハードウェアで実施され得るか、プロセッサによって実行されるソフトウェアモジュールで実施され得るか、またはその2つの組合せで実施され得る。例示すると、プロセッサは、図3のイネーブル信号330または図4のイネーブル信号（Turn\_ON）440を生成することを含む方法またはアルゴリズムを実施するための命令を実行し得る。ソフトウェアモジュールは、ランダムアクセスメモリ（RAM）、フラッシュメモリ、読み取り専用メモリ（ROM）、プログラマブル読み取り専用メモリ（PROM）、消去可能なプログラマブル読み取り専用メモリ（EPROM）、電気消去可能なプログラマブル読み取り専用メモリ（EEPROM（登録商標））、レジスタ、ハードディスク、リムーバブルディスク、コンパクトディスク読み取り専用メモリ（CD-ROM）、または当技術分野で知られている任意の他の形態の非一時的記憶媒体中に常駐し得る。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り、記憶媒体に情報を書き込むことができるようプロセッサに結合される。代替として、記憶媒体は、プロセッサと一体化され得る。プロセッサおよび記憶媒体は、特定用途向け集積回路（ASIC）に存在することができる。ASICは、コンピューティングデバイスまたはユーザ端末に存在することができる。代替では、プロセッサおよび記憶媒体は、コンピューティングデバイスまたはユーザ端末に個別の構成要素として存在することができる。 30

#### 【0059】

[0063] 開示されている実施形態の上記の説明は、当業者が開示されている実施形態を製作または使用することを可能にするために提供されている。これらの実施形態に対する種々の変更は、当業者には容易に明らかになり、本明細書において規定される原理は、本開示の範囲から逸脱することなく、他の実施形態に適用され得る。たとえば、特定の例示的な回路が説明されてきたが、他の回路も実装され得る。したがって、本開示は、本明細書に示した実施形態に限定されるものではなく、以下の特許請求の範囲によって定義される原理および新規の特徴と一致することが可能な最も広い範囲が与えられるべきものである。

以下に本願の出願当初の特許請求の範囲に記載された発明を付記する。

[C1] 第1のトランジスタと第2のトランジスタとを備える差動カスコード増幅器と、 50

前記差動力スコード増幅器の前記第1のトランジスタのゲート端子に結合されたソース端子と、

前記差動力スコード増幅器の前記第2のトランジスタのゲート端子に結合されたドレイン端子と

を含むトランジスタとを備える装置。

[C 2] 前記ソース端子に結合された第1の高インピーダンス要素と、

前記第1の高インピーダンス要素と前記ドレイン端子とに結合された第2の高インピーダンス要素とをさらに備える、C 1に記載の装置。

[C 3] 前記第1の高インピーダンス要素は第1の抵抗器を備え、ここにおいて、前記第2の高インピーダンス要素は第2の抵抗器を備える、C 2に記載の装置。

10

[C 4] 前記第1の高インピーダンス要素は第1のインダクタを備え、ここにおいて、前記第2の高インピーダンス要素は第2のインダクタを備える、C 2に記載の装置。

[C 5] 前記差動力スコード増幅器は、

前記第1のトランジスタに結合された第3のトランジスタと、

前記第2のトランジスタに結合された第4のトランジスタと、ここにおいて、前記第1のトランジスタと前記第3のトランジスタは第1のカスコードトランジスタ対を形成し、ここにおいて、前記第2のトランジスタと前記第4のトランジスタは第2のカスコードトランジスタ対を形成する、をさらに備える、C 1に記載の装置。

[C 6] 前記第3のトランジスタのゲートは第1の差動入力信号を受信するように構成され、ここにおいて、前記第4のトランジスタのゲートは第2の差動入力信号を受信するように構成される、C 1に記載の装置。

20

[C 7] 前記差動力スコード増幅器に結合された変圧器をさらに備え、ここにおいて、前記変圧器は、前記差動力スコード増幅器の出力をアンテナに与えるように構成される、C 1に記載の装置。

[C 8] 電力増幅器をさらに備え、ここにおいて、前記トランジスタおよび前記差動力スコード増幅器は前記電力増幅器内に含められる、C 1に記載の装置。

[C 9] 駆動増幅器をさらに備え、ここにおいて、前記トランジスタおよび前記差動力スコード増幅器は前記駆動増幅器内に含められる、C 1に記載の装置。

[C 10] 差動信号を増幅するための手段と、増幅するための前記手段は、第1のゲート端子を有する第1のトランジスタと、第2のゲート端子を有する第2のトランジスタとを含む、

30

前記第1のゲート端子を前記第2のゲート端子に選択的に結合するための手段とを備える装置。

[C 11] 前記第1のゲート端子を前記第2のゲート端子に選択的に結合するための前記手段はトランジスタを含む、C 10に記載の装置。

[C 12] 前記差動信号を増幅するための前記手段は、

前記第1のトランジスタに結合された第3のトランジスタと、

前記第2のトランジスタに結合された第4のトランジスタと、ここにおいて、前記第1のトランジスタと前記第3のトランジスタは第1のカスコードトランジスタ対を形成し、ここにおいて、前記第2のトランジスタと前記第4のトランジスタは第2のカスコードトランジスタ対を形成する、をさらに備える、C 10に記載の装置。

40

[C 13] 前記第3のトランジスタのゲートは第1の差動入力信号を受信するように構成され、ここにおいて、前記第4のトランジスタのゲートは第2の差動入力信号を受信するように構成される、C 12に記載の装置。

[C 14] 前記差動入力信号を増幅するための前記手段の出力をアンテナに与えるための手段をさらに備える、C 10に記載の装置。

[C 15] 電力増幅器をさらに備え、ここにおいて、前記差動入力信号を増幅するための前記手段および前記第1のゲートを前記第2のゲートに選択的に結合するための前記手段は、前記電力増幅器内に含められる、C 10に記載の装置。

[C 16] 駆動増幅器をさらに備え、ここにおいて、前記差動入力信号を増幅するための

50

前記手段および前記第1のゲートを前記第2のゲートに選択的に結合するための前記手段は、前記駆動増幅器内に含められる、C 1 0 に記載の装置。

[C 1 7] 前記差動信号を増幅するための前記手段は差動カスコード増幅器を含む、C 1 0 に記載の装置。

[C 1 8] 第1のゲート端子を有する第1のトランジスタを含み、第2のゲート端子を有する第2のトランジスタをさらに含む差動カスコード増幅器において、差動信号を増幅することと、

第1のモードの間に、前記第1のゲート端子と前記第2のゲート端子との間に結合されたトランジスタを介して、前記第1のゲート端子を前記第2のゲート端子に結合するために、前記トランジスタをアクティベートすることとを備える方法。

10

[C 1 9] 第2のモードの間に、第1の高インピーダンス要素および第2の高インピーダンス要素を介して前記第1のゲート端子を前記第2のゲート端子に結合するために、前記トランジスタをデアクティベートすることをさらに備える、C 1 8 に記載の方法。

[C 2 0] 前記第2のモードの間に、前記第1のゲート端子における電圧が前記第1のトランジスタのドレイン電圧を追跡し、前記第2のゲート端子における電圧が前記第2のトランジスタのドレイン電圧を追跡する、C 1 9 に記載の方法。

【図1】

FIG. 1

【図2】

FIG. 2

### 【 义 3 】

图 3

FIG. 3

【図5】

5

FIG. 5

【 四 4 】

图 4

FIG. 4

【 図 6 】

6

P<sub>out</sub>

【図7】

FIG. 7

---

フロントページの続き

(72)発明者 チャン、アラン・ナガー・ロン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 イエオ、ガレス・セン・タイ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

審査官 工藤 一光

(56)参考文献 特開2010-141753(JP, A)

特開2010-147992(JP, A)

米国特許第6377120(US, B1)

米国特許出願公開第2006/0097792(US, A1)

米国特許出願公開第2009/0231041(US, A1)

米国特許出願公開第2009/0289721(US, A1)

(58)調査した分野(Int.Cl., DB名)

H03F3/72

H03F3/45

H03F3/189

H03F1/22