(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-169398

(P2009-169398A)

(43) 公開日 平成21年7月30日(2009.7.30)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/36 (2006.01)</b>  | G09G 3/36 | 2 H 09 3    |

| <b>G09G 3/20 (2006.01)</b>  | G09G 3/20 | 2 H 19 3    |

| <b>G02F 1/133 (2006.01)</b> | G09G 3/20 | 5 C 00 6    |

|                             | G09G 3/20 | 5 C 08 0    |

|                             | G09G 3/20 | 5 C 08 P    |

審査請求 未請求 請求項の数 19 O L (全 16 頁) 最終頁に続く

(21) 出願番号 特願2008-293344 (P2008-293344)

(22) 出願日 平成20年11月17日 (2008.11.17)

(31) 優先権主張番号 10-2008-0005080

(32) 優先日 平成20年1月16日 (2008.1.16)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

SAMSUNG ELECTRONICS

CO., LTD.

大韓民国京畿道水原市靈通区梅灘洞 416

416, Maetan-dong, Yeongtong-gu, Suwon-si,

Gyeonggi-do 442-742

(KR)

(74) 代理人 110000051

特許業務法人共生国際特許事務所

(72) 発明者 文 檜 植

大韓民国忠清南道天安市佛堂洞 7

80 湖畔 リージェンシービルアパート

108棟 1103号

最終頁に続く

(54) 【発明の名称】表示装置及びその駆動方法

## (57) 【要約】

【課題】表示品質を向上させることができる表示装置及びその駆動方法を提供する。

【解決手段】複数の画素を含み画像を表示する表示パネルであって、前記各画素はデータラインと、第1及び第2ゲートラインと、前記データライン及び前記第1ゲートラインに接続される第1サブ画素と、前記データライン及び前記第2ゲートラインに接続される第2サブ画素とを含む表示パネルと、画像信号の入力を受け、前記画像信号を第1サブ画像信号と第2サブ画像信号に変換し、第1サブデータ電圧を前記データラインを通して前記第1サブ画素に供給し、前記第1サブデータ電圧を供給した後に第2サブデータ電圧を前記データラインを通して前記第2サブ画素に供給する表示駆動部とを有し、前記第1サブデータ電圧は前記第1サブ画像信号に対応し、前記第2サブデータ電圧は前記第2サブ画像信号に対応する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

複数の画素を含み画像を表示する表示パネルであって、前記各画素はデータラインと、第1及び第2ゲートラインと、前記データライン及び前記第1ゲートラインに接続される第1サブ画素と、前記データライン及び前記第2ゲートラインに接続される第2サブ画素とを含む表示パネルと、

画像信号の入力を受け、前記画像信号を第1サブ画像信号と第2サブ画像信号に変換し、第1サブデータ電圧を前記データラインを通して前記第1サブ画素に供給し、前記第1サブデータ電圧を供給した後に第2サブデータ電圧を前記データラインを通して前記第2サブ画素に供給する表示駆動部とを有し、

前記第1サブデータ電圧は前記第1サブ画像信号に対応し、前記第2サブデータ電圧は前記第2サブ画像信号に対応することを特徴とする表示装置。

**【請求項 2】**

前記第1サブ画像信号と第2サブ画像信号は互いに異なる階調 (gray scale) を有し、前記第1サブデータ電圧と前記第2サブデータ電圧は互いに異なる電圧レベルを有することを特徴とする請求項1に記載の表示装置。

**【請求項 3】**

前記第1サブ画像信号の階調レベルは前記画像信号の階調レベルより大きいか又は同じであり、前記第2サブ画像信号の階調レベルは前記画像信号の階調レベルより小さいか又は同じであることを特徴とする請求項2に記載の表示装置。

**【請求項 4】**

前記第1サブ画像信号及び前記第2サブ画像信号を保存するルックアップテーブルをさらに有することを特徴とする請求項1に記載の表示装置。

**【請求項 5】**

前記表示駆動部は、前記画像信号に対応する前記第1及び第2サブ画像信号を前記ルックアップテーブルから読み出して、順次に出力するタイミングコントローラと、

読み出された前記第1及び第2サブ画像信号に対応する前記第1及び第2サブデータ電圧を供給するデータドライバとを含むことを特徴とする請求項4に記載の表示装置。

**【請求項 6】**

ゲートオン電圧が前記第1及び第2ゲートラインに順次に印加されて、前記第1及び第2サブ画素に順次に前記第1及び第2サブデータ電圧が供給されることを特徴とする請求項1に記載の表示装置。

**【請求項 7】**

第1画素行乃至第n (nは1より大きい整数) 画素行を含む表示パネルであって、第i (1 i n) 画素行は複数の画素を含み、前記各画素は第1サブ画素と第2サブ画素とを含む表示パネルと、

複数の画像信号の入力を受け、前記各画像信号を複数の第1サブ画像信号と第2サブ画像信号に変換し、前記複数の第1サブ画像信号に対応する複数の第1サブデータ電圧を前記第i画素行の前記複数の第1サブ画素に供給し、前記複数の第1サブデータ電圧を供給した後に前記複数の第2サブ画像信号に対応する複数の第2サブデータ電圧を前記第i画素行の前記複数の第2サブ画素に供給する表示駆動部とを有することを特徴とする表示装置。

**【請求項 8】**

前記第1サブ画像信号及び前記第2サブ画像信号を保存するルックアップテーブルをさらに有することを特徴とする請求項7に記載の表示装置。

**【請求項 9】**

前記表示駆動部は、前記複数の画像信号に対応する前記複数の第1及び第2サブ画像信号をルックアップテーブルから読み出し、

前記複数の第1サブ画像信号を出力し、

前記複数の第1サブ画像信号を出力した後に前記複数の第2サブ画像信号を出力するこ

10

20

30

40

50

とを特徴とする請求項 8 に記載の表示装置。

【請求項 10】

前記表示駆動部は、前記複数の画像信号に対応する複数の前記第 1 及び第 2 サブ画像信号を前記ルックアップテーブルから読み出すメモリコントローラと、

読み出された複数の第 1 及び第 2 サブ画像信号を保存する保存部と、

前記保存部に保存された複数の第 1 サブ画像信号を出力し、前記複数の第 1 サブ画像信号を出力した後に前記保存部に保存された複数の第 2 サブ画像信号を出力する出力部と、

前記出力部から出力された複数の第 1 サブ画像信号及び前記複数の第 2 サブ画像信号を前記複数の第 1 サブデータ電圧及び前記複数の第 2 サブデータ電圧に変換して、各々前記複数の第 1 サブ画素及び第 2 サブ画素に供給するデータドライバとを含むことを特徴とする請求項 9 に記載の表示装置。 10

【請求項 11】

前記表示駆動部は、前記複数の画像信号に対応する前記複数の第 1 サブ画像信号を前記ルックアップテーブルから読み出して出力し、

前記第 1 サブ画像信号を読み出して出力した後に前記複数の画像信号に対応する前記複数の第 2 サブ画像信号を前記ルックアップテーブルから読み出して出力することを特徴とする請求項 8 に記載の表示装置。

【請求項 12】

前記表示駆動部は、前記複数の画像信号を保存する保存部と、

前記保存部に保存された複数の画像信号に対応する前記複数の第 1 サブ画像信号を前記ルックアップテーブルから読み出して出力し、前記複数の第 1 サブ画像信号を出力した後に前記保存部に保存された複数の画像信号に対応する前記複数の第 2 サブ画像信号を前記ルックアップテーブルから読み出して出力するメモリコントローラと、 20

前記メモリコントローラから出力された複数の第 1 サブ画像信号及び前記複数の第 2 サブ画像信号を前記複数の第 1 サブデータ電圧及び前記複数の第 2 サブデータ電圧に変換して各々前記複数の第 1 サブ画素及び第 2 サブ画素に供給するデータドライバとを含むことを特徴とする請求項 11 に記載の表示装置。

【請求項 13】

前記各画素行は、前記各第 1 サブ画素と接続される第 1 ゲートラインと、

前記各第 2 サブ画素と接続される第 2 ゲートラインと、 30

前記各第 1 サブ画素及び前記各第 2 サブ画素と接続される複数のデータラインとを含むことを特徴とする請求項 7 に記載の表示装置。

【請求項 14】

前記第 1 サブ画像信号と第 2 サブ画像信号は互いに異なる階調 (gray scale) を有し、前記第 1 サブデータ電圧と前記第 2 サブデータ電圧は互いに異なる電圧レベルを有することを特徴とする請求項 7 に記載の表示装置。

【請求項 15】

前記第 1 サブ画像信号の階調レベルは前記画像信号の階調レベルより大きいか又は同じであり、前記第 2 サブ画像信号の階調レベルは前記画像信号の階調レベルより小さいか又は同じであることを特徴とする請求項 14 に記載の表示装置。 40

【請求項 16】

第 1 画素行乃至第 n (n は 1 より大きい整数) 画素行を含み、第 i (1 ≤ i ≤ n) 画素行は複数の画素を含み、該各画素は第 1 サブ画素と第 2 サブ画素とを含む表示装置の駆動方法であって、

複数の画像信号の入力を受信する段階と、

前記複数の画像信号を複数の第 1 サブ画像信号と第 2 サブ画像信号に変換する段階と、

前記複数の第 1 サブ画像信号に対応する複数の第 1 サブデータ電圧を前記第 i 画素行の前記複数の第 1 サブ画素に供給する段階と、

前記複数の第 1 サブデータ電圧を供給した後に前記複数の第 2 サブ画像信号に対応する複数の第 2 サブデータ電圧を前記第 i 画素行の前記複数の第 2 サブ画素に供給する段階と 50

を有することを特徴とする表示装置の駆動方法。

【請求項 17】

前記第1及び第2サブ画像信号に変換する段階は、前記複数の画像信号に対応する前記複数の第1及び第2サブ画像信号をルックアップテーブルから読み出す段階と、

前記複数の第1サブ画像信号を出力する段階と、

前記複数の第1サブ画像信号を出力した後に前記複数の第2サブ画像信号を出力する段階とを含むことを特徴とする請求項16に記載の表示装置の駆動方法。

【請求項 18】

前記第1及び第2サブ画像信号に変換する段階は、前記複数の画像信号に対応する複数の前記第1サブ画像信号をルックアップテーブルから読み出して出力する段階と、

前記第1サブ画像信号を読み出して出力した後に前記複数の画像信号に対応する複数の前記第2サブ画像信号を前記ルックアップテーブルから読み出して出力する段階とを含むことを特徴とする請求項16に記載の表示装置の駆動方法。

【請求項 19】

前記第1サブ画像信号の階調レベルは前記画像信号の階調レベルより大きいか又は同じであり、前記第2サブ画像信号の階調レベルは前記画像信号の階調レベルより小さいか又は同じであることを特徴とする請求項16に記載の表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は表示装置及びその駆動方法に関し、さらに詳細には表示品質を向上させることができるものである。

【背景技術】

【0002】

フラットパネル表示装置の一例である液晶表示装置は視野角（viewing angle）が狭いという短所を有するが、これを改善するため、広視野角特性を有するPVA（Patterned Vertical Alignment）モード、MVA（Multi-domain Vertical Alignment）モード及びS-PVA（Super-Patterned Vertical Alignment）モードの液晶表示装置が開発されている。

【0003】

特にS-PVAモード液晶表示装置は二つのサブ画素から成る画素を具備する（例えば、特許文献1参照）。各サブ画素には互いに異なるサブデータ電圧が印加されて各サブ画素ごとに光の透過率が異なるようになり、二つのサブ画素を含む一つの画素は互いに異なる二つの透過率の中間値と見られる。このようなS-PVAモードによって液晶表示装置の側面視野角を広げることができる。

【0004】

しかし従来では二つのサブ画素に提供されるサブデータ電圧を各々個別的に制御することができなかった。それによって表示品質をより一層向上させることができなかつたという問題点がある。

【0005】

【特許文献1】大韓民国特許出願公開第10-2006-116443号明細書

【発明の開示】

【発明が解決しようとする課題】

【0006】

そこで、本発明は上記従来の液晶表示装置における問題点に鑑みてなされたものであって、本発明の目的は、表示品質を向上させることができる表示装置を提供することにある。

【0007】

10

20

30

40

50

また、本発明の他の目的は、表示品質を向上させることができる表示装置の駆動方法を提供することにある。

**【課題を解決するための手段】**

**【0008】**

上記目的を達成するためになされた本発明による表示装置は、複数の画素を含み画像を表示する表示パネルであって、前記各画素はデータラインと、第1及び第2ゲートラインと、前記データライン及び前記第1ゲートラインに接続される第1サブ画素と、前記データライン及び前記第2ゲートラインに接続される第2サブ画素とを含む表示パネルと、画像信号の入を受け、前記画像信号を第1サブ画像信号と第2サブ画像信号に変換し、第1サブデータ電圧を前記データラインを通して前記第1サブ画素に供給し、前記第1サブデータ電圧を供給した後に第2サブデータ電圧を前記データラインを通して前記第2サブ画素に供給する表示駆動部とを有し、前記第1サブデータ電圧は前記第1サブ画像信号に対応し、前記第2サブデータ電圧は前記第2サブ画像信号に対応することを特徴とする。

10

**【0009】**

また、上記目的を達成するためになされた本発明による表示装置は、第1画素行乃至第n(nは1より大きい整数)画素行を含む表示パネルであって、第i(1 i n)画素行は複数の画素を含み、前記各画素は第1サブ画素と第2サブ画素とを含む表示パネルと、複数の画像信号の入を受け、前記各画像信号を複数の第1サブ画像信号と第2サブ画像信号に変換し、前記複数の第1サブ画像信号に対応する複数の第1サブデータ電圧を前記第i画素行の前記複数の第1サブ画素に供給し、前記複数の第1サブデータ電圧を供給した後に前記複数の第2サブ画像信号に対応する複数の第2サブデータ電圧を前記第i画素行の前記複数の第2サブ画素に供給する表示駆動部とを有することを特徴とする。

20

**【0010】**

上記目的を達成するためになされた本発明による表示装置の駆動方法は、第1画素行乃至第n(nは1より大きい整数)画素行を含み、第i(1 i n)画素行は複数の画素を含み、該各画素は第1サブ画素と第2サブ画素とを含む表示装置の駆動方法であって、複数の画像信号の入力を受信する段階と、前記複数の画像信号を複数の第1サブ画像信号と第2サブ画像信号に変換する段階と、前記複数の第1サブ画像信号に対応する複数の第1サブデータ電圧を前記第i画素行の前記複数の第1サブ画素に供給する段階と、前記複数の第1サブデータ電圧を供給した後に前記複数の第2サブ画像信号に対応する複数の第2サブデータ電圧を前記第i画素行の前記複数の第2サブ画素に供給する段階とを有することを特徴とする。

30

**【発明の効果】**

**【0011】**

本発明に係る表示装置及びその駆動方法によれば表示品質が向上され得るという効果がある。

**【発明を実施するための最良の形態】**

**【0012】**

次に、本発明に係る表示装置及びその駆動方法を実施するための最良の形態の具体例を図面を参照しながら説明する。

**【0013】**

一つの素子(elements)が他の素子と“接続された(connected to)”あるいは“カップリングされた(coupled to)”と指称されるものは、他の素子と直接接続あるいはカップリングされた場合、あるいは中間に他の素子を介在した場合をすべて含む。反面、一つの素子が他の素子と“直接接続された(directly connected to)”あるいは“直接カップリングされた(directly coupled to)”と指称されるものは、中間に他の素子を介在しないことを表す。明細書全体にかけて同一参照符号は同一構成要素を指称する。“及び／又は”は言及されたアイテムの各々および一つ以上のすべての組合せを含む。

40

**【0014】**

第1、第2等が多様な素子、構成要素及び／又はセクションを叙述するために使用されるが、これら素子、構成要素及び／又はセクションはこれら用語によって制限されないことはもちろんである。これら用語は単に一つの素子、構成要素あるいはセクションを他の素子、構成要素あるいはセクションと区別するために使用するものである。したがって、以下で言及される第1素子、第1構成要素あるいは第1セクションは本発明の技術的思想内で第2素子、第2構成要素あるいは第2セクションであり得ることはもちろんである。

#### 【0015】

本明細書で使用された用語は実施形態を説明するためのものであり、本発明を制限しようとするものではない。本明細書で单数型は文句に特別に言及しない限り複数型も含む。明細書で使用される“有する（comprises）”及び／又は“含む（comprising）”は言及された構成要素、段階、動作及び／又は素子は一つ以上の他の構成要素、段階、動作及び／又は素子の存在又は追加を排除しない。

10

#### 【0016】

他の定義がなければ、本明細書で使用されるすべての用語（技術および科学的用語を含む）は本発明が属する技術分野で通常の知識を有する者に共通に理解され得る意味として使用され得るものである。また一般的に使用される辞典に定義されている用語は明白に特別に定義されていない限り理想的にまたは過度に解釈されない。

#### 【0017】

図1～図7を参照して本発明の一実施形態による表示装置及びその駆動方法を説明する。

20

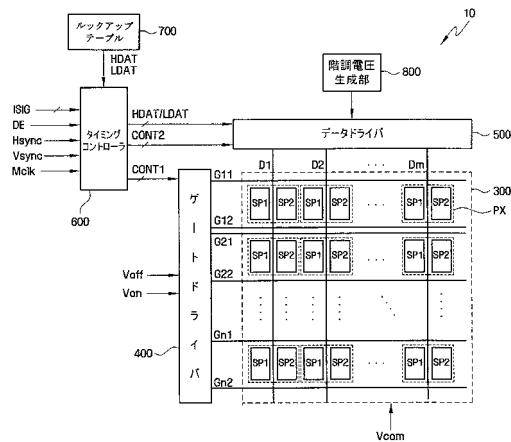

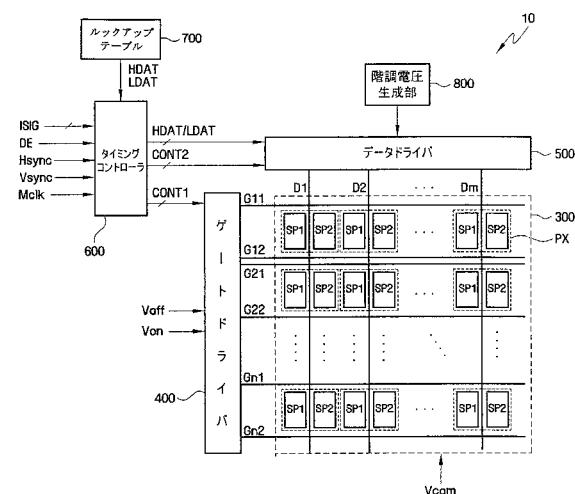

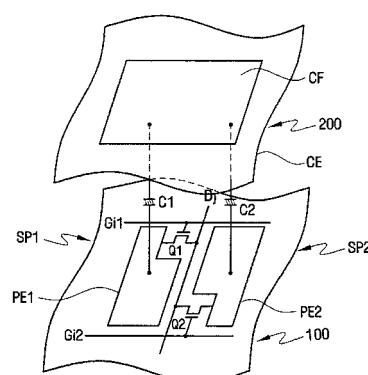

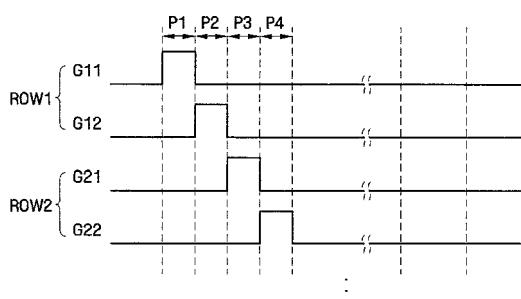

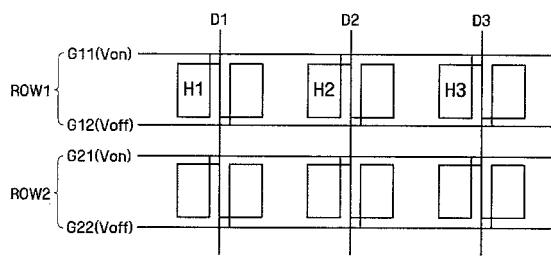

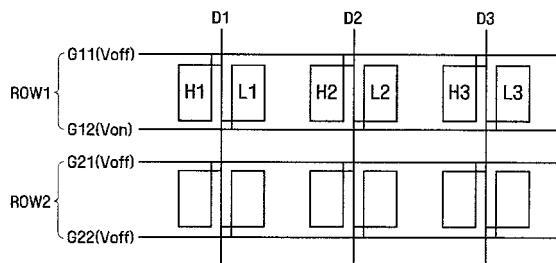

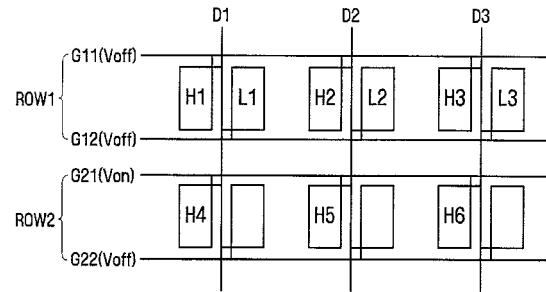

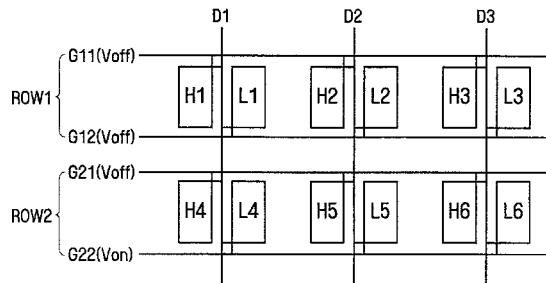

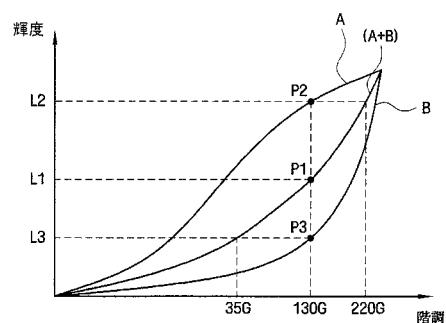

図1は本発明の一実施形態による表示装置の概略構成ブロック図であり、図2は図1の一画素の等価回路図であり、図3は本発明の一実施形態による表示装置の表示駆動部の動作を説明するための信号波形図であり、図4～図7は本発明の一実施形態による表示装置の表示駆動部の動作を説明するための概念図であり、図8は図1のルックアップテーブルに保存された第1サブ画像信号及び第2サブ画像信号を説明するためのグラフである。

#### 【0018】

図1を参照すると、本発明の一実施形態による液晶表示装置10は液晶パネル300、表示駆動部、ルックアップテーブル700および階調電圧生成部800を含む。表示駆動部はゲートドライバ400、データドライバ500、これらを制御するタイミングコントローラ600を含む。

30

#### 【0019】

液晶パネル300は第1～第n画素行を含み、各画素行は複数の画素PXを含み、各画素PXは第1サブ画素SP1と第2サブ画素SP2を含む。一つの画素行ごとに2個のゲートラインG11、G12～Gn1、Gn2が形成されている。データラインD1～Dmは第1サブ画素SP1と第2サブ画素SP2の間に形成されて概ね列方向に延長されお互いがほとんど平行する。

#### 【0020】

図2を参照すれば、一つの画素PXは第1サブ画素SP1と第2サブ画素SP2を含む。第1サブ画素SP1は第1ゲートラインGi1及びデータラインDjと接続され、第2サブ画素SP2は第2ゲートラインGi2及びデータラインDjと接続される。すなわち、第1サブ画素SP1及び第2サブ画素SP2はデータラインを共有する。

40

#### 【0021】

第1サブ画素SP1と第2サブ画素SP2は第1基板100と第2基板200の間に形成される。第1サブ画素SP1は第1液晶キャパシタC1と第1スイッチング素子Q1を含み、第2サブ画素SP2は第2液晶キャパシタC2と第2スイッチング素子Q2を含む。

#### 【0022】

第1液晶キャパシタC1は第1基板100上に形成された第1画素電極PE1と第2基板200上に形成された共通電極CE及びこれらの間に介在する液晶層（未図示）からなる。第2液晶キャパシタC2は第1基板100上に形成された第2画素電極PE2と第2

50

基板 120 上に形成された共通電極 C E 及びこれらの間に介在する液晶層（未図示）から成る。第 2 基板 200 上にはカラーフィルタ C F がさらに形成され得る。

#### 【0023】

一つの画素 P X には各々互いに異なる電圧レベルの第 1 サブデータ電圧と第 2 サブデータ電圧がデータライン D j を通し順次に印加され得る。例えば、先に第 1 サブデータ電圧は第 1 サブ画素 S P 1 に印加されて次に第 2 サブデータ電圧は第 2 サブ画素 S P 2 に印加され得る。

第 1 サブ画素 S P 1 に第 1 サブデータ電圧が印加されれば、バックライトアセンブリ（未図示）から供給される光が第 1 サブ画素 S P 1 を第 1 サブデータ電圧に対応する第 1 透過率で透過し、第 2 サブ画素 S P 2 に第 2 サブデータ電圧が印加されれば、光は第 2 サブ画素 S P 2 を第 2 サブデータ電圧に対応する第 2 透過率で透過する。したがって一つの画素 P X で表示される画像は、第 1 透過率と第 2 透過率との間の所定の透過率に対応する明るさで表示される。10

#### 【0024】

表示駆動部はタイミングコントローラ 600、ゲートドライバ 400 及びデータドライバ 500 を含む。

表示駆動部は複数の画像信号 I S I G の入力を受けて、各画像信号 I S I G を複数の第 1 サブ画像信号 H D A T と複数の第 2 サブ画像信号 L D A T に変換し、複数の第 1 サブ画像信号 H D A T に対応する複数の第 1 サブデータ電圧を第 i (1 ≤ i ≤ n) 画素行の複数の第 1 サブ画素 S P 1 に供給し、複数の第 1 サブデータ電圧を提供した後に複数の第 2 サブ画像信号 L D A T に対応する複数の第 2 サブデータ電圧を第 i 画素 P X 行の複数の第 2 サブ画素 S P 2 に供給する。以下にて、表示駆動部の各ブロックに対してさらに具体的に説明する。20

#### 【0025】

タイミングコントローラ 600 は外部のグラフィック制御器（未図示）から入力制御信号を受信してこれに基づいてゲート制御信号 C O N T 1 とデータ制御信号 C O N T 2 を生成し、ゲート制御信号 C O N T 1 をゲートドライバ 400 に、データ制御信号 C O N T 2 をデータドライバ 500 に送る。

ここで入力制御信号は、垂直同期信号（V s y n c）と水平同期信号（H s y n c）、メインクロック（M c l k）、データイネーブル信号（D E）等である。ゲート制御信号 C O N T 1 はゲートドライバ 400 の動作を制御するための信号であって、ゲートドライバ 400 の動作を開示する垂直開始信号、ゲートオン電圧の出力時期を決定するゲートクロック信号及びゲートオン電圧のパルス幅を決定する出力イネーブル信号などを含む。データ制御信号 C O N T 2 はデータドライバ 500 の動作を制御する信号であって、データドライバ 500 の動作を開示する水平開示信号、二つのデータ電圧の出力を指示する出力指示信号などを含む。30

#### 【0026】

また、タイミングコントローラ 600 は、画像信号 I S I G の入力を受けこれに対応する第 1 サブ画像信号 H D A T 及び第 2 サブ画像信号 L D A T をルックアップテーブル 700 から読み出し、順次に出力する。さらに具体的には、タイミングコントローラ 600 は一画素 P X 行に供給される画像信号 I S I G の入力を受け一画素行の各第 1 サブ画素 S P 1 に供給される複数の第 1 サブ画像信号 H D A T を先に出力し、次に一画素行の各第 2 サブ画素 S P 2 にされる複数の第 2 サブ画像信号 L D A T を出力する。40

#### 【0027】

ゲートドライバ 400 はタイミングコントローラ 600 から供給されたゲート制御信号 C O N T 1 に応答して、外部から入力されるゲートオン／オフ電圧（V o n、V o f f）を図 3 に示すように複数のゲートライン G 1 1 ~ G n 2 に順次に出力する。

#### 【0028】

図 3 を参照すると、一つの画素 P X 行が活性化され、データ電圧の入力を受ける時間を 1 水平周期（以下“1 H”という）とすると、“1 H”の間、各画素行の第 1 及び第 2 ゲ

ートラインが順次に活性化される。すなわち、最初の“1H”で第1区間P1の間、第1画素行ROW1の第1ゲートラインG11が活性化されて、第2区間P2の間、第1画素行ROW1の第2ゲートラインG12が活性化される。2番目の“1H”で第3区間P3の間、第2画素行ROW2の第1ゲートラインG21が活性化されて、第4区間P4の間、第2画素行ROW2の第2ゲートラインG22が活性化される。

#### 【0029】

一方、図1のデータドライバ500はタイミングコントローラ600から供給されたデータ制御信号CONT2に応答し、先に複数の第1サブ画像信号HDATに対応する複数の第1サブデータ電圧を各データラインD1～Dmに印加し、次に複数の第2サブ画像信号LDATに対応する複数の第2サブデータ電圧を各データラインに印加する。データドライバ500は階調電圧生成部800から複数の第1サブ画像信号HDATに対応する複数の第1サブデータ電圧及び、複数の第2サブ画像信号LDATに対応する複数の第2サブデータ電圧の入力を受ける。

10

#### 【0030】

図3、図4～図7をさらに参照してより一層具体的に説明する。

第1区間P1の間、第1画素行ROW1の第1ゲートラインG11にゲートオン電圧(Von)が印加されて、残りゲートラインG12、G21、G22にゲートオフ電圧(Voff)が印加される。データドライバ500が先に複数の第1サブデータ電圧H1、H2、H3を各データラインD1、D2、D3に印加する。したがって図4に示すように第1画素行ROW1の複数の第1サブ画素SP1に各第1サブデータ電圧H1、H2、H3が供給される。

20

#### 【0031】

第2区間P2の間、第1画素行ROW1の第2ゲートラインG12にゲートオン電圧(Von)が印加されて、残りゲートラインG11、G21、G22にゲートオフ電圧(Voff)が印加される。データドライバ500が複数の第2サブデータ電圧L1、L2、L3を各データラインD1、D2、D3に印加する。したがって図5に示すように第1画素行ROW1の複数の第2サブ画素SP2に各第2サブデータ電圧L1、L2、L3が供給される。

20

#### 【0032】

第3区間P3の間、第2画素行ROW2の第1ゲートラインG21にゲートオン電圧(Von)が印加されて、残りゲートラインG11、G12、G22にゲートオフ電圧(Voff)が印加される。データドライバ500が複数の第1サブデータ電圧H4、H5、H6を各データラインD1、D2、D3に印加する。したがって図6に示すように第2画素行ROW2の複数の第1サブ画素SP1に各第1サブデータ電圧H4、H5、H6が供給される。

30

#### 【0033】

第4区間P4の間、第2画素行ROW2の第2ゲートラインG22にゲートオン電圧(Von)が印加されて、残りゲートラインG11、G12、G21にゲートオフ電圧(Voff)が印加される。データドライバ500が複数の第2サブデータ電圧L4、L5、L6を各データラインD1、D2、D3に印加する。したがって図7に示すように第2画素行ROW2の複数の第2サブ画素SP2に各第2サブデータ電圧L4、L5、L6が供給される。

40

#### 【0034】

図8を参照してルックアップテーブル700に保存された第1サブ画像信号HDAT及び第2サブ画像信号LDATを説明する。

#### 【0035】

図8を参照すると、液晶パネル300に印加される階調レベル(gray scale levels)に従った輝度特性を表すガンマ曲線を示す。

液晶表示装置10の製造段階で液晶パネル300の側面視認性が最適となる第1サブ画素SP1のガンマ曲線Aと第2サブ画素PXのガンマ曲線Bを設定する。第1サブ画素P

50

X のガンマ曲線 A と第 2 サブ画素 P X のガンマ曲線 B は液晶表示装置 10 の特性及び機能に大いに依存する。

【0036】

液晶パネル 300 の第 1 サブ画素 P X と第 2 サブ画素 P X に同一の階調レベルに該当するデータ電圧を印加した後、液晶パネル 300 の正面での輝度特性を検知して、液晶パネル 300 の正面でのガンマ曲線 (A + B) を求める。液晶パネル 300 の正面でのガンマ曲線 (A + B) と既に設定された第 1 サブ画素 P X のガンマ曲線 A と第 2 サブ画素 P X のガンマ曲線 B を利用してロックアップテーブル 700 に第 1 サブ画像信号 H D A T 及び第 2 サブ画像信号 L D A T を保存する。

【0037】

例えば、液晶パネル 300 の第 1 サブ画素 S P 1 と第 2 サブ画素 S P 2 に同一の第 1 階調レベル 130 G に該当するサブデータ電圧を印加すれば、液晶パネル 300 の正面では第 1 輝度 L 1 値を有する。液晶パネル 300 に印加された第 1 階調レベル 130 G と液晶パネル 300 から感知された第 1 輝度 L 1 値が接する第 1 接点 P 1 を輝度軸の方向に直線に延長して、第 1 サブ画素 S P 1 のガンマ曲線 A と接する第 2 接点 P 2 と第 2 サブ画素 S P 2 のガンマ曲線 B と接する第 3 接点 P 3 を求める。

【0038】

第 1 サブ画素 S P 1 のガンマ曲線 A 上で第 2 接点 P 2 は第 2 輝度 L 2 値を有する。液晶パネル 300 の正面ガンマ曲線 (A + B) 上で第 2 輝度 L 2 に該当する階調値は第 2 階調レベル 220 G となる。同様に、第 2 サブ画素 S P 2 のガンマ曲線 B 上で第 3 接点 P 3 は第 3 輝度 L 3 値を有する。液晶パネル 300 の正面ガンマ曲線 (A + B) 上で第 3 輝度 L 3 に該当する階調値は第 3 階調レベル 35 G となる。

【0039】

すなわち、液晶パネル 300 の正面でガンマ特性が第 1 接点 P 1 として表現されるためには、第 1 サブ画素 S P 1 には第 2 階調レベル 220 G に該当するサブデータ電圧が印加されなければならず、第 2 サブ画素 S P 2 には第 3 階調レベル 35 G に該当するサブデータ電圧が印加されなければならない。

【0040】

上述した方法で、外部から入力される画像信号 I S I G の各階調レベルに対応して、第 1 及び第 2 サブ画素 S P 1 、 S P 2 に印加する第 1 サブデータ電圧及び第 2 サブデータ電圧に対応する第 1 サブ画像信号 H D A T 及び第 2 サブ画像信号 L D A T をロックアップテーブル 700 に保存することができる。

【0041】

上述したように、側面視認性を最適化することができるよう画像信号 I S I G を第 1 及び第 2 サブ画像信号 H D A T 、 L D A T に変換し、各第 1 及び第 2 サブ画素 S P 1 、 S P 2 に第 1 及び第 2 サブデータ電圧を供給することにより表示品質が向上される。

【0042】

一方、第 1 及び第 2 サブ画素 S P 1 、 S P 2 は一つのデータラインを共有するため、表示駆動部は複数の第 1 サブデータ電圧を先に各データライン D 1 ~ D m に印加し、次に複数の第 2 サブデータ電圧を各データライン D 1 ~ D m に印加しなければならない。

【0043】

このため、表示駆動部が駆動動作を実行する一番目の方法としては、タイミングコントローラ 600 が先に複数の第 1 サブ画像信号 H D A T を各データライン D 1 ~ D m に供給し、その後、複数の第 2 サブ画像信号 L D A T を各データライン D 1 ~ D m に供給する方法がある。この時、データドライバ 500 はタイミングコントローラ 600 から順次に出力される複数の第 1 サブ画像信号 H D A T を先に複数の第 1 サブデータ電圧に変換して出力し、その次に複数の第 2 サブ画像信号 L D A T を複数の第 2 サブデータ電圧に変換して出力するものである。

【0044】

2 番目方法としては、タイミングコントローラ 600 が入力される画像信号 I S I G に

10

20

30

40

50

対応する第1サブ画像信号H D A Tと第2サブ画像信号L D A Tを出力し、データドライバ500が出力された複数の第1及び第2サブ画像信号(H D A T、L D A T)のうち先に複数の第1サブ画像信号H D A Tを複数の第1サブデータ電圧に変換して出力し、その次に複数の第2サブ画像信号L D A Tを複数の第2サブデータ電圧に変換して出力するものである。

#### 【0045】

本発明による表示装置は上記2種類の方法に限定されず、多様な方法で動作され得るが、以下では上述した1番目 の方法で動作する表示装置を具体的な実施形態を通して説明する。

#### 【0046】

10

図9及び図10を参照して本発明の一実施形態による表示装置を説明する。

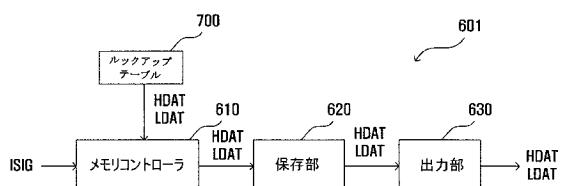

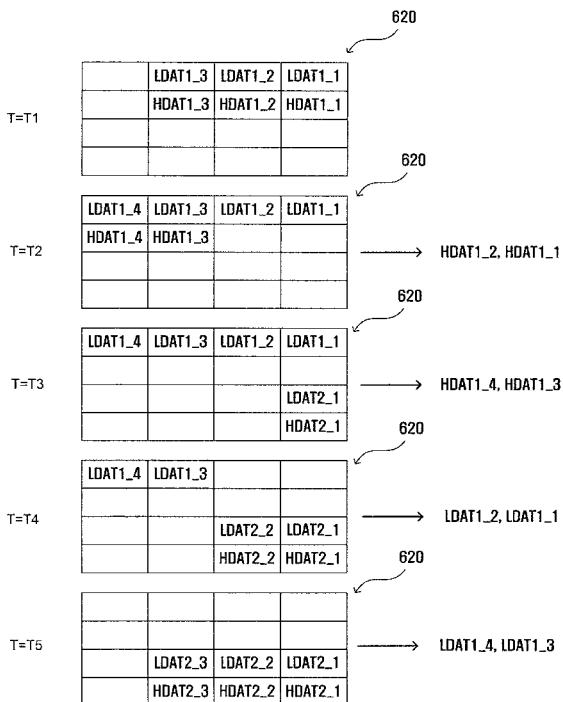

図9は、本発明の一実施形態による表示装置のタイミングコントローラの概略プロック図であり、図10は、図9のタイミングコントローラの動作を説明するための概念図である。

#### 【0047】

図9を参照すると、タイミングコントローラ601はメモリコントローラ610と、保存部620と出力部630を含む。

#### 【0048】

20

先ず、メモリコントローラ610は、画像信号I S I Gの入力を受けこれに対応する第1サブ画像信号H D A T及び第2サブ画像信号L D A Tをルックアップテーブル700から読み出す。ここでメモリコントローラ610は第1サブ画像信号H D A T及び第2サブ画像信号L D A Tを同時に読み出すことができ、あるいは順次に読み出すことができる。

#### 【0049】

保存部620は、メモリコントローラ610から出力された第1サブ画像信号H D A T及び第2サブ画像信号L D A Tを保存する。保存部620は一画素行の複数の第1サブ画素S P 1に提供される複数の第1サブ画像信号H D A Tを複数の第2サブ画像信号L D A Tより先に出力するために複数の第1サブ画像信号H D A T及び第2サブ画像信号L D A Tを保存する。出力部630はメモリに保存されている複数の第1サブ画像信号H D A Tを先に出力し、次に複数の第2サブ画像信号L D A Tを出力する。

#### 【0050】

30

ここで図10をさらに参照して保存部620と出力部630の動作をさらに詳細に説明する。

以下では一画素行に4個の画素P Xを含む場合を例にあげて説明する。一画素P X行は4個の第1サブ画素S P 1と4個の第2サブ画素S P 2を含む。

#### 【0051】

先ず、時間T1において保存部620は、第1画素行の3個の第1サブ画素S P 1に供給される3個の第1サブ画像信号(H D A T 1\_1、H D A T 1\_2、H D A T 1\_3)と3個の第2サブ画素S P 2に供給される3個の第2サブ画像信号(L D A T 1\_1、L D A T 1\_2、L D A T 1\_3)を保存する。

#### 【0052】

40

次に、メモリコントローラ610が第1画素行の4番目の画素P Xに供給される第1サブ画像信号(H D A T 1\_4)及び第2サブ画像信号(L D A T 1\_4)を供給するとき、時間T2において、保存部620は第1サブ画像信号(H D A T 1\_4)及び第2サブ画像信号(L D A T 1\_4)を保存する。この時、出力部630は保存部620から第1画素行の1番目の画素P Xと2番目の画素P Xに供給される第1サブ画像信号(H D A T 1\_1、H D A T 1\_2)を出力する。

#### 【0053】

次に、メモリコントローラ610が第2画素行の1番目の画素P Xに供給される第1サブ画像信号(H D A T 2\_1)及び第2サブ画像信号(L D A T 2\_1)を供給するとき、時間T3において、保存部620は第1サブ画像信号(H D A T 2\_1)及び第2サブ

50

画像信号（L D A T 2 \_ 1）を保存する。この時、出力部630は保存部620から第1画素行の3番目の画素P Xと4番目の画素P Xに供給される第1サブ画像信号（H D A T 1 \_ 3、H D A T 1 \_ 4）を出力する。

**【0054】**

次に、メモリコントローラ610が第2画素行の2番目の画素P Xに供給される第1サブ画像信号（H D A T 2 \_ 2）及び第2サブ画像信号（L D A T 2 \_ 2）を供給するとき、時間T4において、保存部620は第1サブ画像信号H D A T（H D A T 2 \_ 2）及び第2サブ画像信号（L D A T 2 \_ 2）を保存する。この時、出力部630は保存部620から第1画素行の一番目の画素P Xと2番目の画素P Xに供給される第2サブ画像信号（L D A T 1 \_ 2、L D A T 1 \_ 1）を出力する。10

**【0055】**

次に、メモリコントローラ610が第2画素行の3番目の画素P Xに供給される第1サブ画像信号（H D A T 2 \_ 3）及び第2サブ画像信号（L D A T 2 \_ 3）を供給するとき、時間T5において、保存部620は第1サブ画像信号（H D A T 2 \_ 3）及び第2サブ画像信号（L D A T 2 \_ 3）を保存する。この時、出力部630は保存部620から第1画素行の3番目の画素P Xと4番目の画素P Xに供給される第2サブ画像信号（L D A T 1 \_ 3、L D A T 1 \_ 4）を出力する。

**【0056】**

整理して説明すれば、保存部620はメモリコントローラ610から出力された複数の第1サブ画像信号H D A T及び複数の第2サブ画像信号L D A Tを保存し、出力部630が保存部620から一画素P X行に対する複数の第1サブ画像信号H D A Tを先に出力し、次に一画素P X行に対する複数の第2サブ画像信号L D A Tを出力する。20

**【0057】**

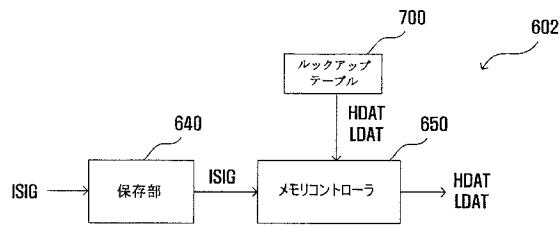

図11及び図12を参照し、本発明の他の実施形態による表示装置及びその駆動方法を説明する。

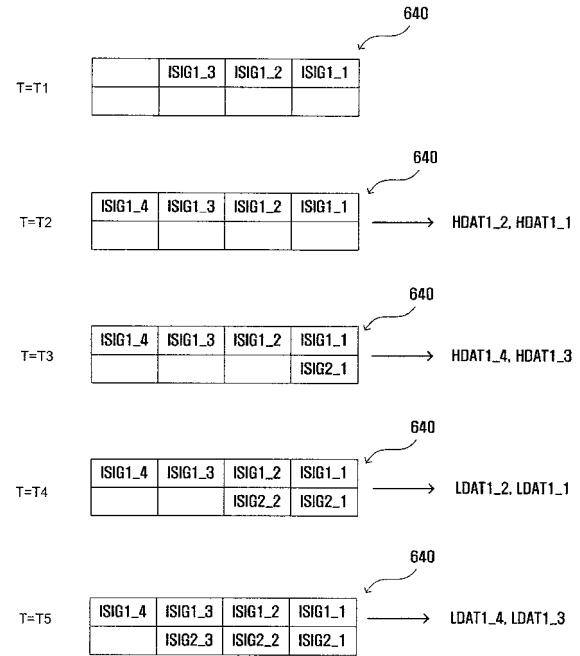

図11は、本発明の他の実施形態による表示装置のタイミングコントローラのブロック図であり、図12は、図11のタイミングコントローラの動作を説明するための概念図である。

図9に示した構成要素と同一の機能をする構成要素に対しては同一の図面符号を使用し、説明の便宜上、該当構成要素の詳細な説明は省略する。30

**【0058】**

図11を参照すると、タイミングコントローラ602は保存部640とメモリコントローラ650を含む。

**【0059】**

保存部640は画像信号I S I Gの入力を受け保存する。メモリコントローラ650は保存部640に保存された画像信号I S I Gの入力を受けこれに対応する複数の第1サブ画像信号H D A Tを先に読み出して出力し、次に複数の第2サブ画像信号L D A Tを読み出して出力する。

**【0060】**

図12をさらに参照して保存部640とメモリコントローラ650の動作をさらに詳細に説明する。40

以下では一画素行に4個の画素P Xを含む場合を例にあげて説明する。一画素行は4個の第1サブ画素S P 1と4個の第2サブ画素S P 2を含む。

**【0061】**

まず、時間T1において、保存部640は第1画素行の3個の画素P Xに供給される3個の画像信号（I S I G 1 \_ 1、I S I G 1 \_ 2、I S I G 1 \_ 3）を保存する。

**【0062】**

時間T2において、保存部640は第1画素行の4番目の画素P Xに供給される画像信号（I S I G 1 \_ 4）を保存する。この時、メモリコントローラ650は先に第1画素行の一番目の画素P Xに供給される画像信号（I S I G 1 \_ 1）の入力を受けこれに対応す50

る第1サブ画像信号( H D A T 1 \_ 1 )をルックアップテーブル700から読み出して出力する。次に、第1画素行の2番目の画素P Xに供給される画像信号( I S I G 1 \_ 2 )の入力を受けこれに対応する第1サブ画像信号( H D A T 1 \_ 2 )をルックアップテーブル700から読み出して出力する。

#### 【 0 0 6 3 】

時間T3において、保存部640が第2画素行の一番目の画素P Xに供給される画像信号( I S I G 2 \_ 1 )を保存する。この時、メモリコントローラ650は先に第1画素行の3番目の画素P Xに供給される画像信号( I S I G 1 \_ 3 )の入力を受けこれに対応する第1サブ画像信号( H D A T 1 \_ 3 )をルックアップテーブル700から読み出して出力する。次に、第1画素行の4番目の画素P Xに供給される画像信号( I S I G 1 \_ 4 )の入力を受けこれに対応する第1サブ画像信号( H D A T 1 \_ 4 )をルックアップテーブル700から読み出して出力する

10

#### 【 0 0 6 4 】

時間T4において、保存部640が第2画素行の2番目の画素P Xに供給される画像信号( I S I G 2 \_ 2 )を保存する。この時、メモリコントローラ650は先に第1画素行の一番目の画素P Xに供給される画像信号( I S I G 1 \_ 1 )の入力を受けこれに対応する第2サブ画像信号( L D A T 1 \_ 1 )をルックアップテーブル700から読み出して出力する。次に、第1画素行の2番目の画素P Xに供給される画像信号( I S I G 1 \_ 2 )の入力を受けこれに対応する第2サブ画像信号( L D A T 1 \_ 2 )をルックアップテーブル700から読み出して出力する。

20

#### 【 0 0 6 5 】

時間T5において、保存部640が第2画素行の3番目の画素P Xに供給される画像信号( I S I G 2 \_ 3 )を保存する。この時、メモリコントローラ650は先に第1画素行の3番目の画素P Xに供給される画像信号( I S I G 1 \_ 3 )の入力を受けこれに対応する第2サブ画像信号( L D A T 1 \_ 3 )をルックアップテーブル700から読み出して出力する。次に、第1画素行の4番目の画素P Xに供給される画像信号( I S I G 1 \_ 4 )の入力を受けこれに対応する第2サブ画像信号( L D A T 1 \_ 4 )をルックアップテーブル700から読み出して出力する。

20

#### 【 0 0 6 6 】

以上を整理して説明すれば、保存部640は画像信号I S I Gを保存して、メモリコントローラ650が一画素行に対する画像信号I S I Gに対応する複数の第1サブ画像信号H D A Tを先に読み出して出力し、次に一画素行に対する複数の第2サブ画像信号L D A Tを読み出して出力する。

30

#### 【 0 0 6 7 】

尚、本発明は、上述の実施例に限られるものではない。本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

#### 【 産業上の利用可能性 】

#### 【 0 0 6 8 】

本発明は、液晶表示装置などのフラットパネル表示装置に利用される。

40

#### 【 図面の簡単な説明 】

#### 【 0 0 6 9 】

【 図1 】本発明の一実施形態による表示装置の概略構成ブロック図である。

【 図2 】図1の一画素の等価回路図である。

【 図3 】本発明の一実施形態による表示装置の表示駆動部の動作を説明するための信号波形図である。

【 図4 】本発明の一実施形態による表示装置の表示駆動部の動作を説明するための概念図である。

【 図5 】本発明の一実施形態による表示装置の表示駆動部の動作を説明するための概念図である。

【 図6 】本発明の一実施形態による表示装置の表示駆動部の動作を説明するための概念図

50

である。

【図7】本発明の一実施形態による表示装置の表示駆動部の動作を説明するための概念図である。

【図8】図1のルックアップテーブルに保存された第1サブ画像信号及び第2サブ画像信号を説明するためのグラフである。

【図9】本発明の一実施形態による表示装置のタイミングコントローラの概略ブロック図である。

【図10】図9のタイミングコントローラの動作を説明するための概念図である。

【図11】本発明の他の実施形態による表示装置のタイミングコントローラのブロック図である。

【図12】図11のタイミングコントローラの動作を説明するための概念図である。

【符号の説明】

【0070】

- |                   |             |

|-------------------|-------------|

| 1 0               | 液晶表示装置      |

| 1 0 0             | 第1基板        |

| 2 0 0             | 第2基板        |

| 3 0 0             | 液晶パネル       |

| 4 0 0             | ゲートドライバ     |

| 5 0 0             | データドライバ     |

| 6 0 0、6 0 1、6 0 2 | タイミングコントローラ |

| 6 1 0、6 5 0       | メモリコントローラ   |

| 6 2 0、6 4 0       | 保存部         |

| 6 3 0             | 出力部         |

| 7 0 0             | ルックアップテーブル  |

| 8 0 0             | 階調電圧生成部     |

【図1】

【図2】

【図3】

10

20

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

## フロントページの続き

| (51) Int.Cl. | F I     | テーマコード(参考)   |

|--------------|---------|--------------|

|              | G 0 9 G | 3/20 6 2 3 W |

|              | G 0 9 G | 3/20 6 4 1 P |

|              | G 0 9 G | 3/20 6 8 0 H |

|              | G 0 9 G | 3/20 6 4 1 K |

|              | G 0 2 F | 1/133 5 7 5  |

|              | G 0 2 F | 1/133 5 5 0  |

F ターム(参考) 2H093 NA16 NA43 NA53 NC10 NC12 NC13 NC23 NC28 NC34 ND01

2H193 ZA04 ZD23 ZF22 ZF36

5C006 AA12 AA16 AA17 AA22 AB03 AC17 AC21 AF45 AF46 BA15

BB16 BC16 BC23 BF08 FA55 FA56

5C080 AA10 BB05 CC03 DD01 EE29 FF11 JJ02