【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成22年11月25日(2010.11.25)

【公開番号】特開2008-21782(P2008-21782A)

【公開日】平成20年1月31日(2008.1.31)

【年通号数】公開・登録公報2008-004

【出願番号】特願2006-191470(P2006-191470)

【国際特許分類】

H 01 L 27/115 (2006.01)

H 01 L 21/8247 (2006.01)

H 01 L 29/788 (2006.01)

H 01 L 29/792 (2006.01)

【F I】

H 01 L 27/10 4 3 4

H 01 L 29/78 3 7 1

【手続補正書】

【提出日】平成22年10月8日(2010.10.8)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

行方向に配置されたメモリトランジスタのゲートに接続する各行ごとにメモリトランジスタ選択線が配置され、列方向に配置されたメモリトランジスタのソースに接続する各列ごとに第1次ソース線が配置され、複数の第1次ソース線に接続する行方向に配置される第2次ソース線がメタルであることを特徴とする不揮発性メモリ。

【請求項2】

ソース領域、チャネル領域及びドレイン領域が基板側からこの順に形成され、前記チャネル領域の外側に電荷蓄積層を有する不揮発性メモリトランジスタが前記基板上に行列状に配置され、行方向に配置されたメモリトランジスタのゲートに接続する各行ごとにメモリトランジスタ選択線が配置され、列方向に配置されたメモリトランジスタのソースに接続する各列ごとに第1次ソース線が配置され、複数の第1次ソース線に接続する行方向に配置される第2次ソース線がメタルであることを特徴とする不揮発性メモリ。

【請求項3】

少なくとも、請求項1の不揮発性メモリが列方向に複数配列した不揮発性メモリ。

【請求項4】

少なくとも、請求項1の不揮発性メモリが行方向に複数配列した不揮発性メモリ。

【請求項5】

少なくとも、請求項1の不揮発性メモリが列方向及び行方向に複数配列した不揮発性メモリ。

【請求項6】

少なくとも、請求項2の不揮発性メモリが列方向に複数配列した不揮発性メモリ。

【請求項7】

少なくとも、請求項2の不揮発性メモリが行方向に複数配列した不揮発性メモリ。

【請求項8】

少なくとも、請求項2の不揮発性メモリが列方向及び行方向に複数配列した不揮発性メモリ。

モリ。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【発明の詳細な説明】

【発明の名称】不揮発性半導体メモリ及びその駆動方法

【技術分野】

【0001】

この発明は、不揮発性半導体メモリ及びその駆動方法に関するものである。

【背景技術】

【0002】

小さな基板占有面積で電荷蓄積層とゲートの間の容量を十分大きく確保することができ、優れた書き込み、消去効率を持つ、半導体基板の表面に形成された島状半導体層の側壁に島状半導体層を取り囲むように形成された電荷蓄積層及びゲートを有するメモリトランジスタからなるフラッシュメモリが提案されている（例えば、特許文献1および非特許文献1参照）。

【0003】

上記フラッシュメモリでは、ホット・エレクトロンを利用して電荷蓄積層への電荷の注入が行われる。この電荷蓄積層の電荷蓄積状態の相違によるしきい値電圧の相違をデータ“0”、“1”として記憶する。例えば、電荷蓄積層に浮遊ゲートを用いたNチャネルのメモリトランジスタの場合、浮遊ゲートに電荷を注入するには、ゲートとドレイン拡散層に高電圧を与え、ソース拡散層と、半導体基板とを接地する。このとき、ソース・ドレイン間の電圧によって、半導体基板の電子のエネルギーを高め、トンネル酸化膜のエネルギー障壁を乗り越えさせて電気蓄積層に注入する。この電荷注入によりメモリトランジスタのしきい値電圧は正方向に移動する。ソース・ドレイン間を流れる電流のうち、電荷蓄積層に注入される比率は小さい。そのため、書き込みに必要な電流がセル当たり $100\mu\text{A}$ オーダーとなる。また、NOR型フラッシュメモリでは、読み出し時に流れる電流は、 $30\mu\text{A}$ 程度である。

【0004】

上記島状半導体層の側壁を利用したメモリトランジスタからなるフラッシュメモリセルアレイは、ソース線もしくはソース面に拡散層を用いている。拡散層は、金属と比べて高抵抗である。抵抗に電流が流れると、電位差が生じる。そのため、書き込み時にメモリトランジスタのソース拡散層の電圧は、 $0\text{V}$ より高い電圧となり、ソース・ドレイン間の電圧は低下し、ソース・ドレイン間に流れる電流は減少し、書き込み速度が低下する。また、読み出し時においても、メモリトランジスタのソース拡散層の電圧は、 $0\text{V}$ より高い電圧となり、ソース・ドレイン間の電圧は低下し、ソース・ドレイン間に流れる電流は減少し、読み出し速度は低下する。

【0005】

【特許文献1】特開平8-148587号公報

【非特許文献1】Howard Pein他 IEEE Electron Device Letters, Vol.14, No.8, pp.415-pp.417, 1993年

【発明の開示】

【発明が解決しようとする課題】

【0006】

そこで、書き込み速度と読み出し速度の低下を回避する島状半導体層の側壁を利用したメモリトランジスタからなる不揮発性半導体メモリを提供することを目的とする。

【課題を解決するための手段】

【0007】

上記の課題を解決するために本発明では以下の構成を有する。本発明の一つの特徴によれば、ソース領域、チャネル領域及びドレイン領域が基板側からこの順に形成され、さらに、前記チャネル領域の外側にゲート絶縁膜を介して形成された電荷蓄積層と、当該電荷蓄積層の外側に絶縁層を介して当該電荷蓄積層を覆うように形成されたゲートとを有するメモリトランジスタが、前記基板上にn行m列の行列状に配置された不揮発性半導体メモリであって、

前記行列の列方向に整列したメモリトランジスタのソース領域を相互に接続するよう列方向に配線された複数の第1次ソース線と、

前記列方向に整列したメモリトランジスタのドレイン領域を相互に接続するよう、前記第1次ソース線とは異なる層において列方向に配線された複数の平行なビット線と、

前記列方向に実質的に直交する行方向に整列したメモリトランジスタのゲートを相互に接続するよう行方向に配線された線をゲート線とし、

前記行列のp行( $p < n$ )置きに1行ずつ配線される第2次ソース線であって、前記第1次ソース線を相互に接続するメタルで形成された第2次ソース線と、

を含んでいる不揮発性半導体メモリが提供される。

#### 【0008】

また、本発明のさらなる別の特徴によると、ソース領域、チャネル領域及びドレイン領域が基板側からこの順に形成され、さらに、前記チャネル領域の外側にゲート絶縁膜を介して形成された電荷蓄積層と、当該電荷蓄積層の外側に絶縁層を介して当該電荷蓄積層を覆うように形成されたゲートとを有するメモリトランジスタが、前記基板上にn行m列の行列状に配置された不揮発性半導体メモリであって、

前記行列の行および列の方向にそれぞれ整列したメモリトランジスタのソース領域を相互に接続するよう配線された第1の共通拡散ソース線と、

前記列方向に整列したメモリトランジスタのドレイン領域を相互に接続するよう、前記第1の共通拡散ソース線とは異なる層において列方向に配線された複数の平行なビット線と、

前記列方向に実質的に直交する行方向に整列したメモリトランジスタのゲートを相互に接続するよう行方向に配線された線をゲート線とし、

前記ソース面に接続されるメタルで形成された第2次ソース線であって、前記行列のp行( $p < n$ )置きに1行ずつ配線される第2次ソース線と、

を含んでいる不揮発性半導体メモリが提供される。

#### 【0009】

また、本発明に係る不揮発性半導体メモリの駆動方法の特徴によれば、不揮発性半導体メモリへの書き込み方法であって、

選択したビット線に0Vまたは正の第一電圧を印加し、非選択のビット線に0Vを印加し、選択したゲート線に正の第二電圧を印加し、非選択のゲート線に0Vを印加し、第1次ソース線または第1の共通拡散ソース線と第2次ソース線に0Vを印加することで、選択したメモリトランジスタにホット・エレクトロンを利用して電荷蓄積層へ電荷の注入を行う、不揮発性半導体メモリへの書き込み方法が提供される。

#### 【0010】

また、本発明に係る不揮発性半導体メモリの駆動方法の別の特徴によれば、不揮発性半導体メモリからの読み出し方法であって、

選択したゲート線に正の第一電圧を印加し、非選択のゲート線に、0Vを印加し、第1次ソース線または第1の共通拡散ソース線と第2次ソース線に0Vを印加し、選択したビット線に正の第二電圧を印加することで、選択したメモリトランジスタを読み出す、不揮発性半導体メモリからの読み出し方法が提供される。

#### 【0011】

また、本発明に係る不揮発性半導体メモリの駆動方法のさらなる別の特徴によれば、不揮発性半導体メモリの消去方法であって、

ビット線と第1次ソース線または第1の共通拡散ソース線と第2次ソース線に正の第一

電圧を印加し、ゲート線に0Vを印加することで、FN (Fowler-Nordheim) トンネル電流を利用して全メモリトランジスタの電荷蓄積層から電荷を放出する、不揮発性半導体メモリの消去方法が提供される。

#### 【0012】

また、本発明に係る不揮発性半導体メモリの駆動方法のさらなる別の特徴によれば、不揮発性半導体メモリの消去方法であって、

ビット線と第1次ソース線または第1の共通拡散ソース線と第2次ソース線に正の第一電圧を印加し、選択したゲート線に0Vを印加し、非選択のゲート線に正の第二電圧を印加することで、FNトンネル電流を利用して選択したゲート線に接続されたメモリトランジスタの電荷蓄積層から電荷を放出する、不揮発性半導体メモリの消去方法が提供される。

#### 【発明の効果】

#### 【0013】

この発明によれば、所定数のゲート線毎に、メタルを用いて形成された第2次ソース線を持つため、ソース線を低抵抗化することができ、書き込み時にメモリトランジスタのソース拡散層に0Vを与えることができ、ソース・ドレイン間に十分な電圧を与えることができ、ソース・ドレイン間に十分な電流を流すことができ、書き込み速度の低下を回避することができる。また、読み出し時においても、メモリトランジスタのソース拡散層に0Vを与えることができ、ソース・ドレイン間に十分な電圧を与えることができ、ソース・ドレイン間に十分な電流を流すことができ、読み出し速度の低下を回避することができる。

#### 【発明を実施するための最良の形態】

#### 【0014】

この発明に係る不揮発性半導体メモリは、半導体基板上に形成された多数の島状半導体層を含む。島状半導体層は、その上部に形成されたドレイン拡散層と、その下部に形成されたソース拡散層と、ドレイン拡散層とソース拡散層に挟まれた側壁のチャネル領域上にゲート絶縁膜を介して形成された電荷蓄積層と、電荷蓄積層上に形成されたゲートを有する不揮発性半導体メモリトランジスタからなる。そして、不揮発性半導体メモリは、この不揮発性半導体メモリトランジスタを行列状に配列するとともに、ドレイン拡散層に接続されたビット線を列方向に配線し、ゲート線を行方向に配線し、ソース拡散層に接続された第1次ソース線を列方向に配線した構造とし、所定数（例えば64本）のゲート線毎に1本ずつ、メタルで形成された第2次ソース線を行方向に配線し、このとき、この第2次ソース線を第1次ソース線に接続することもできる。

#### 【0015】

また、この不揮発性半導体メモリにおいて、この不揮発性半導体メモリトランジスタを拡散層で形成された第1の共通拡散ソース線上に行列状に配列するとともに、ドレイン拡散層に接続されたビット線を列方向に配線し、ゲート線を行方向に配線した構造とすることもできる。さらに、この不揮発性半導体メモリにおいて、所定数（例えば64本）のゲート線毎に1本ずつ、メタルで形成された第2次ソース線を行方向に配線し、このとき、この第2次ソース線を第1の共通拡散ソース線に接続することもできる。

#### 【0016】

この発明の駆動方法は、選択したビット線に0Vまたは正の第一電圧を印加し、非選択のビット線に0Vを印加し、選択したゲート線に正の第二電圧を印加し、非選択のゲート線に0Vを印加し、第1次ソース線または第1の共通拡散ソース線と第2次ソース線に0Vを印加することで、選択したメモリトランジスタにホット・エレクトロンを利用して電荷蓄積層へ電荷の注入を行うことができる。

#### 【0017】

この発明の駆動方法は、選択したゲート線に正の第一電圧を印加し、非選択のゲート線に、0Vを印加し、第1次ソース線または第1の共通拡散ソース線と第2次ソース線に0Vを印加し、選択したビット線に正の第二電圧を印加することで、選択したメモリトランジスタを読み出すことができる。

#### 【0018】

この発明の駆動方法は、ビット線と第1次ソース線または第1の共通拡散ソース線と第2次ソース線に正の第一電圧を印加し、ゲート線に0Vを印加することで、FNトンネル電流を利用して全メモリトランジスタの電荷蓄積層から電荷を放出することができる。

#### 【0019】

この発明の駆動方法は、ビット線と第1次ソース線または第1の共通拡散ソース線と第2次ソース線に正の第一電圧を印加し、選択したゲート線に0Vを印加し、非選択のゲート線に正の第二電圧を印加することで、FNトンネル電流を利用して選択したゲート線に接続されたメモリトランジスタの電荷蓄積層から電荷を放出することができる。

#### 【実施例】

#### 【0020】

以下、図面に示す実施形態に基づいてこの発明を記述する。なお、この発明は、これによって限定されるものではない。

#### 【0021】

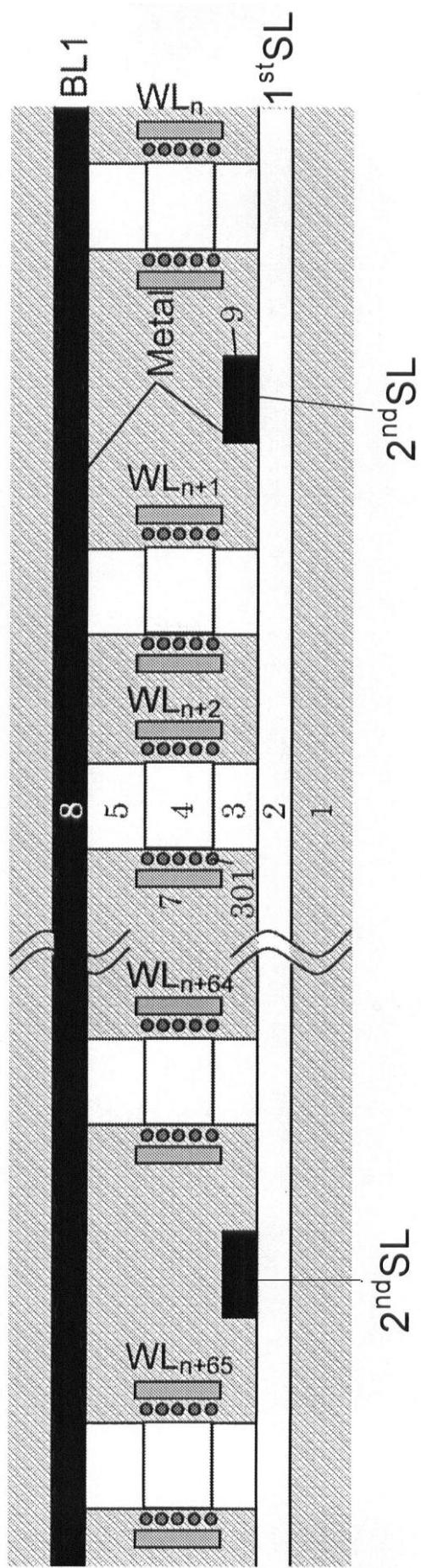

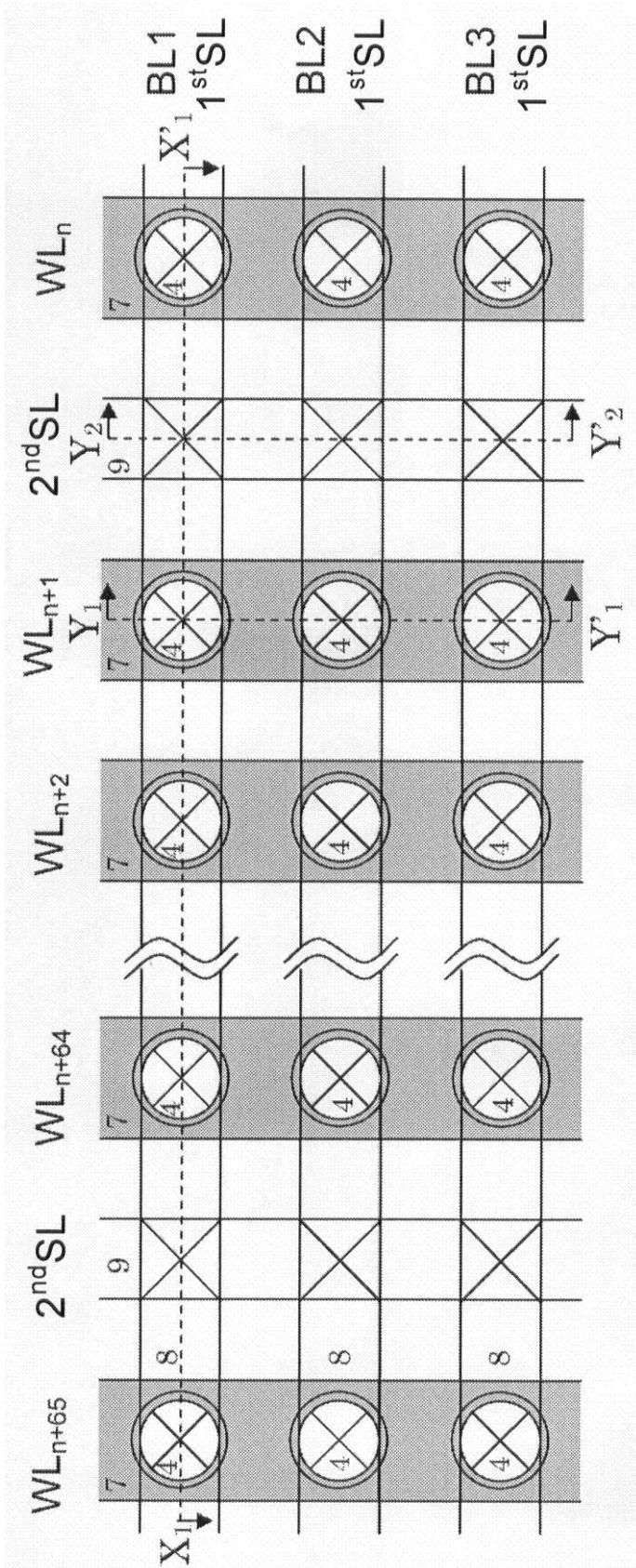

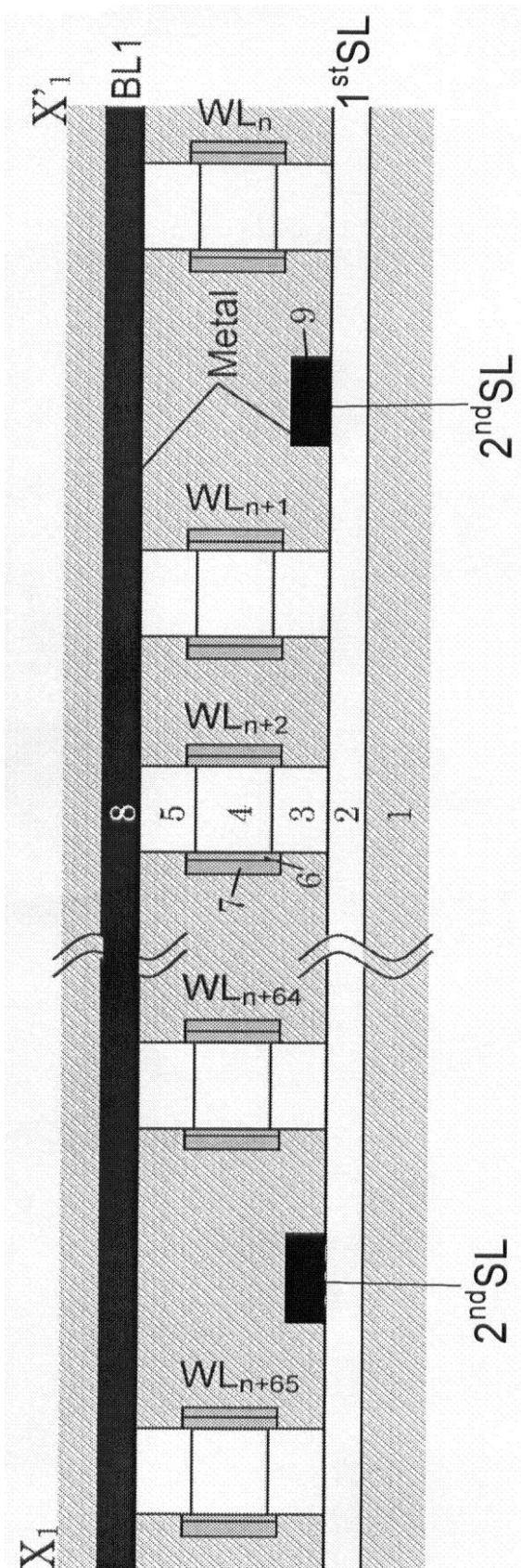

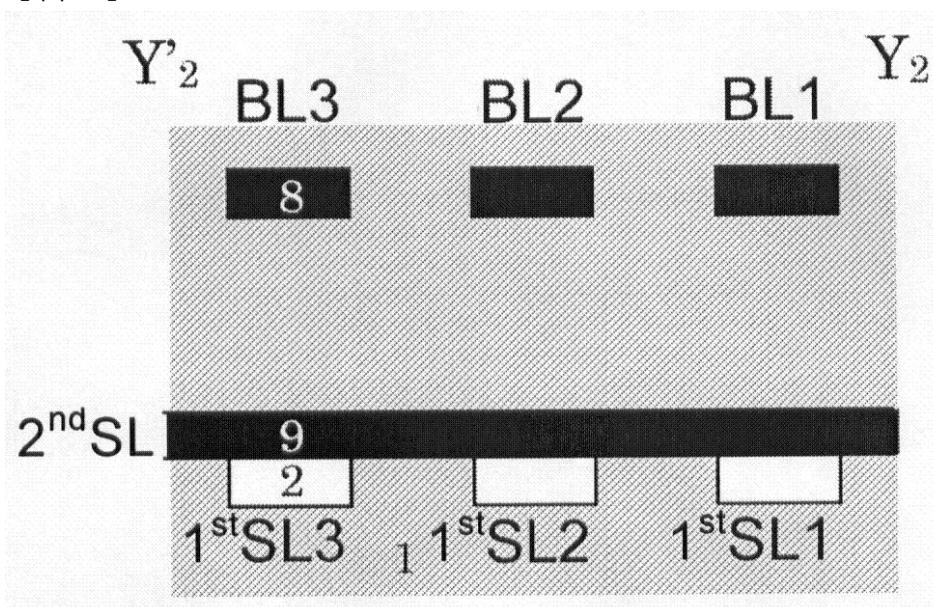

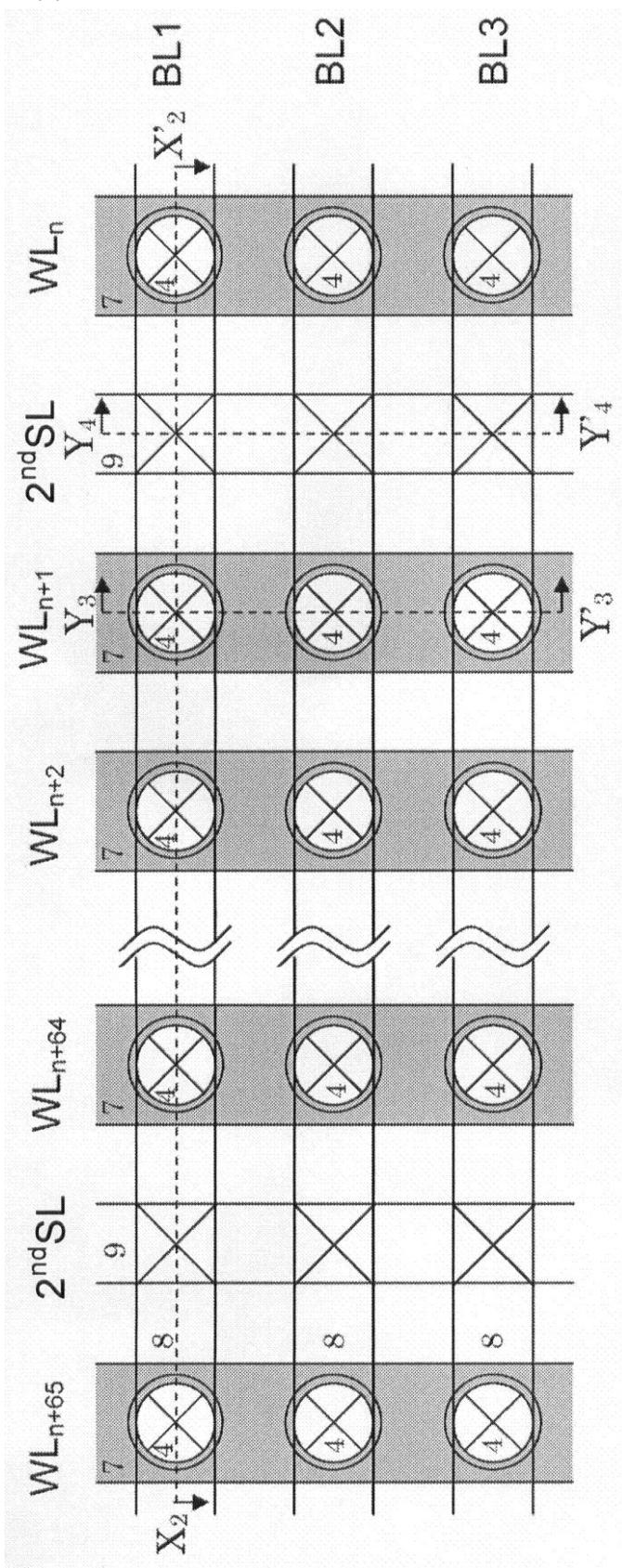

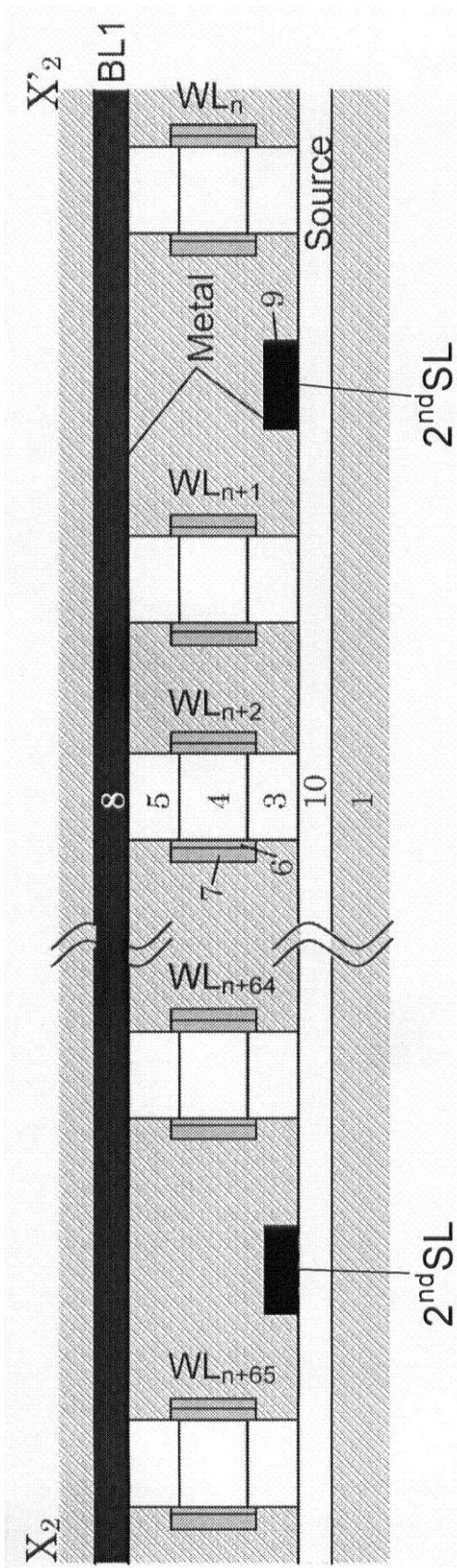

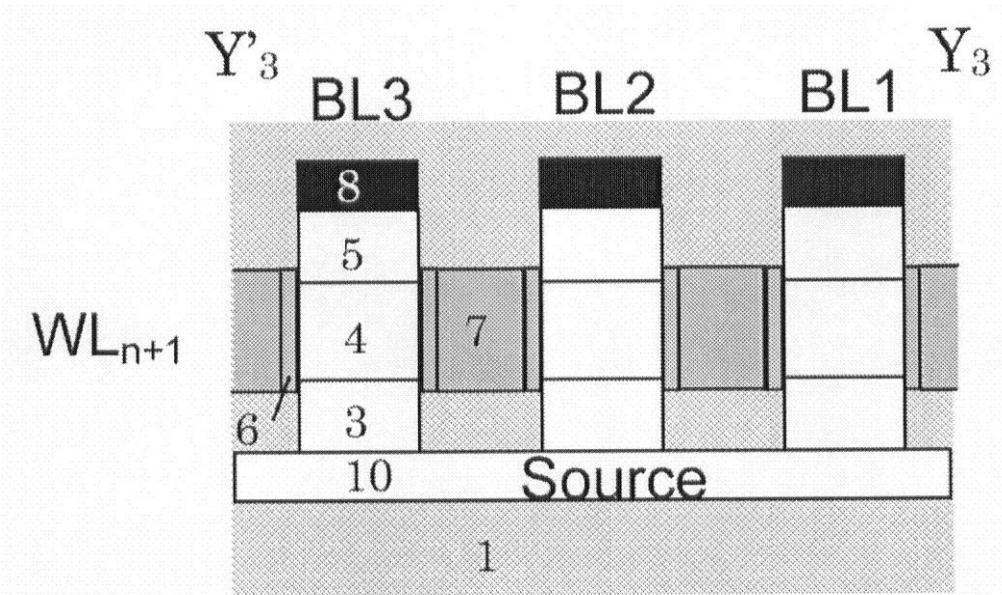

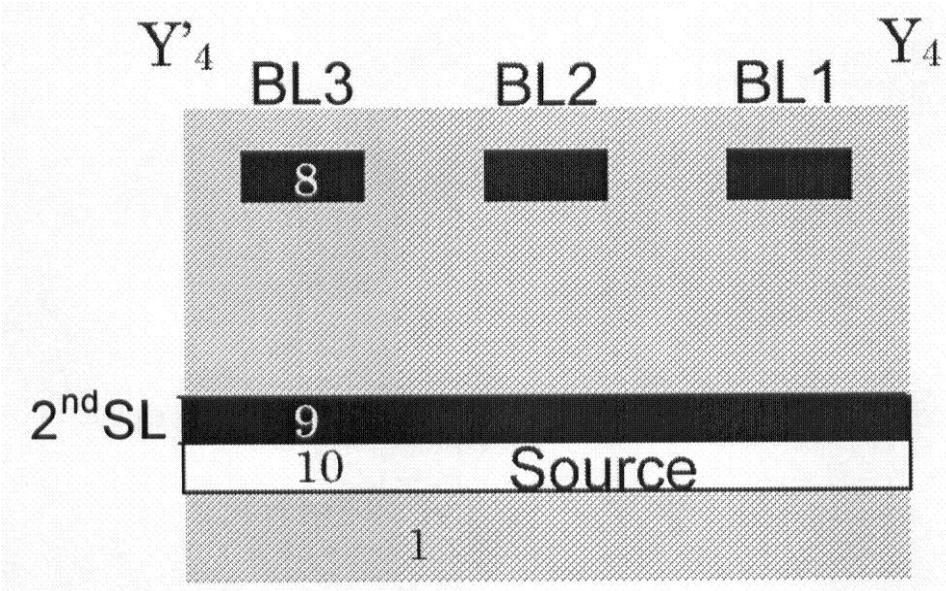

この発明に係る不揮発性半導体メモリのレイアウトと断面構造を、それぞれ図1、図2、図3、図4に示す。この実施例では、シリコン酸化膜1上に、第1次ソース線2とソース拡散層3が形成され、その上に島状半導体層4が形成され、該当島状半導体層4の上部にドレイン拡散層5が形成され、ドレイン拡散層5とソース拡散層3に挟まれた側壁のチャネル領域上にゲート絶縁膜を介して形成された電荷蓄積層6が形成され、電荷蓄積層6上にゲートが形成され、メモリトランジスタを形成する。メモリトランジスタのゲートを相互に接続するよう行方向に配線された線をゲート線7とする。ドレイン拡散層上に、ビット線8が形成される。また、所定数のゲート線毎（ここでは64本毎）に、第1次ソース線上に、行に配属するメタルからなる第2次ソース線9が形成される。

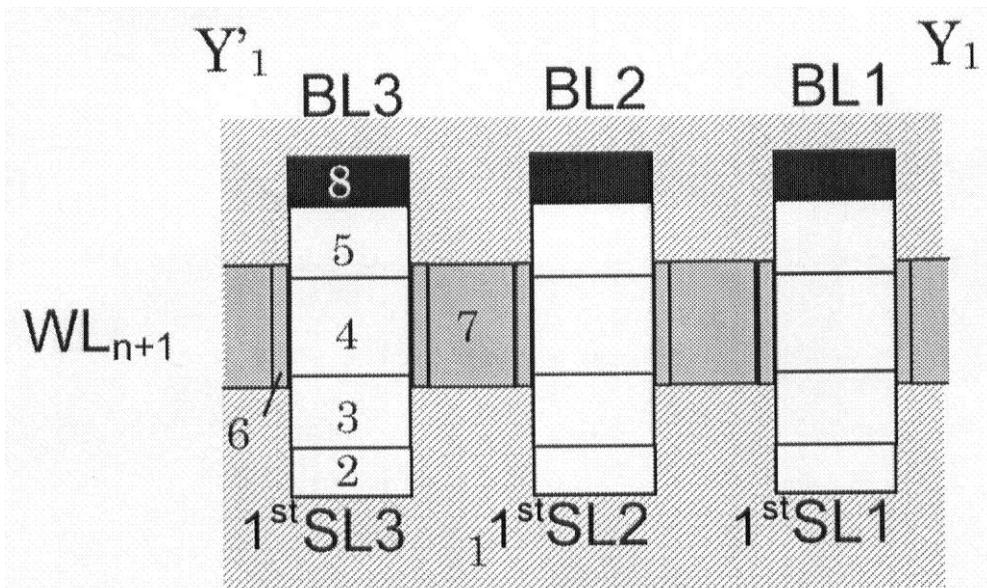

#### 【0022】

また、この発明に係る不揮発性半導体メモリのレイアウトと断面構造を、それぞれ図5、図6、図7、図8に示す。この実施例では、シリコン酸化膜1上に、第1の共通拡散ソース線10とソース拡散層3が形成され、その上に島状半導体層4が形成され、該当島状半導体層4の上部にドレイン拡散層5が形成され、ドレイン拡散層5とソース拡散層3に挟まれた側壁のチャネル領域上にゲート絶縁膜を介して形成された電荷蓄積層6が形成され、電荷蓄積層6上にゲートが形成され、メモリトランジスタを形成する。メモリトランジスタのゲートを相互に接続するよう行方向に配線された線をゲート線7とする。ドレイン拡散層上に、ビット線8が形成される。また、所定数のゲート線毎（ここでは64本毎）に、第1の共通拡散ソース線上に、行に配属するメタルからなる第2次ソース線9が形成される。

#### 【0023】

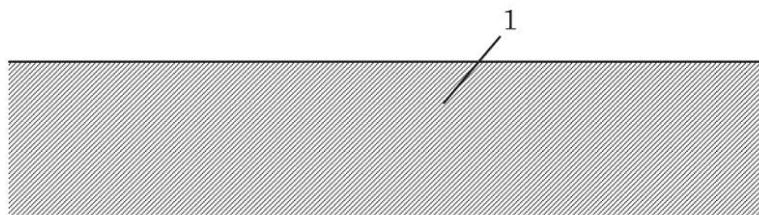

以下に、この発明に係る不揮発性半導体メモリが備えるメモリトランジスタアレイの構造を形成するための製造工程の一例を図9～図65を参照して説明する。図9は、シリコン酸化膜1上に、P型シリコン100が形成されているSOI基板のX<sub>1</sub>-X<sub>1'</sub>断面図である。また、図10は、Y<sub>1</sub>-Y<sub>1'</sub>断面図、図11は、Y<sub>2</sub>-Y<sub>2'</sub>断面図である。X<sub>1</sub>-X<sub>1'</sub>断面は図2に対応し、Y<sub>1</sub>-Y<sub>1'</sub>断面は図3に対応し、Y<sub>2</sub>-Y<sub>2'</sub>断面は図3に対応する断面である。

#### 【0024】

レジストをマスクとして、反応性イオンエッティングによりP型シリコン100をエッティングして、第1次ソース線2を形成する（図12（X<sub>1</sub>-X<sub>1'</sub>）、図13（Y<sub>1</sub>-Y<sub>1'</sub>）、図14（Y<sub>2</sub>-Y<sub>2'</sub>））。

#### 【0025】

酸化膜を堆積し、CMPにより平坦化を行い、反応性イオンエッティングを用いてエッチバックを行う（図15（X<sub>1</sub>-X<sub>1'</sub>）、図16（Y<sub>1</sub>-Y<sub>1'</sub>）、図17（Y<sub>2</sub>-Y<sub>2'</sub>））。

#### 【0026】

レジストをマスクとして用いて、反応性イオンエッティングによりP型シリコン100をエッティングして、島状半導体層101を形成する（図18（X<sub>1</sub>-X<sub>1'</sub>）、図19（Y<sub>1</sub>-Y<sub>1'</sub>）、図20（Y<sub>2</sub>-Y<sub>2'</sub>））。島状半導体層101の下部は、第1次ソース線となる。

#### 【0027】

続いて、酸化を行い、トンネル絶縁膜102を形成する（図21（ $X_1-X'_1$ ）、図22（ $Y_1-Y'_1$ ）、図23（ $Y_2-Y'_2$ ））。

【0028】

続いて、多結晶シリコン膜103を堆積する（図24（ $X_1-X'_1$ ）、図25（ $Y_1-Y'_1$ ）、図26（ $Y_2-Y'_2$ ））。

【0029】

続いて、多結晶シリコン膜を、反応性イオンエッティングによりエッティングし、島状半導体側壁に、サイドウォールスペーサ状に残存させ、電荷蓄積層6を形成する（図27（ $X_1-X'_1$ ）、図28（ $Y_1-Y'_1$ ）、図29（ $Y_2-Y'_2$ ））。

【0030】

続いて、酸化を行い、インターポリ絶縁膜104を形成する（図30（ $X_1-X'_1$ ）、図31（ $Y_1-Y'_1$ ）、図32（ $Y_2-Y'_2$ ））。CVDにより絶縁膜を堆積させてもよい。

【0031】

続いて、多結晶シリコン膜105を堆積する（図33（ $X_1-X'_1$ ）、図34（ $Y_1-Y'_1$ ）、図35（ $Y_2-Y'_2$ ））。

【0032】

続いて、多結晶シリコン膜をCMPにより平坦化した後、エッチバックする（図36（ $X_1-X'_1$ ）、図37（ $Y_1-Y'_1$ ）、図38（ $Y_2-Y'_2$ ））。

【0033】

続いて、公知のフォトリソグラフィ技術によりパターニングされたレジスト106を形成する（図39（ $X_1-X'_1$ ）、図40（ $Y_1-Y'_1$ ）、図41（ $Y_2-Y'_2$ ））。

【0034】

続いて、レジストをマスクとして用いて、多結晶シリコン膜105を反応性イオンエッティングによりエッティングし、電荷蓄積層側壁にサイドウォールスペーサ状に残存させ、ゲート線7を形成する（図42（ $X_1-X'_1$ ）、図43（ $Y_1-Y'_1$ ）、図44（ $Y_2-Y'_2$ ））。

【0035】

続いて、イオン注入法などにより第1次ソース線2及びソース拡散層3及びドレイン拡散層5を形成する（図45（ $X_1-X'_1$ ）、図46（ $Y_1-Y'_1$ ）、図47（ $Y_2-Y'_2$ ））。

【0036】

続いて、シリコン酸化膜といった層間絶縁膜107を堆積し、CMPなどを用いて平坦化を行った後、レジストをマスクとして用いて、層間絶縁膜を反応性イオンエッティングによりエッティングする（図48（ $X_1-X'_1$ ）、図49（ $Y_1-Y'_1$ ）、図50（ $Y_2-Y'_2$ ））。

【0037】

続いて、メタル108をスパッタなどにより堆積する（図51（ $X_1-X'_1$ ）、図52（ $Y_1-Y'_1$ ）、図53（ $Y_2-Y'_2$ ））。

【0038】

続いて、メタルを反応性イオンエッティングによりエッティングを行い、第2次ソース線9を形成する（図54（ $X_1-X'_1$ ）、図55（ $Y_1-Y'_1$ ）、図56（ $Y_2-Y'_2$ ））。

【0039】

続いて、層間絶縁膜109を堆積する（図57（ $X_1-X'_1$ ）、図58（ $Y_1-Y'_1$ ）、図59（ $Y_2-Y'_2$ ））。

【0040】

続いて、CMPなどを用いてドレイン拡散層を露出させる（図60（ $X_1-X'_1$ ）、図61（ $Y_1-Y'_1$ ）、図62（ $Y_2-Y'_2$ ））。

【0041】

続いて、メタルをスパッタなどにより堆積し、レジストをマスクとして用いてメタルをエッティングし、ビット線8を形成する（図63（ $X_1-X'_1$ ）、図64（ $Y_1-Y'_1$ ）、図65（ $Y_2-Y'_2$ ））。

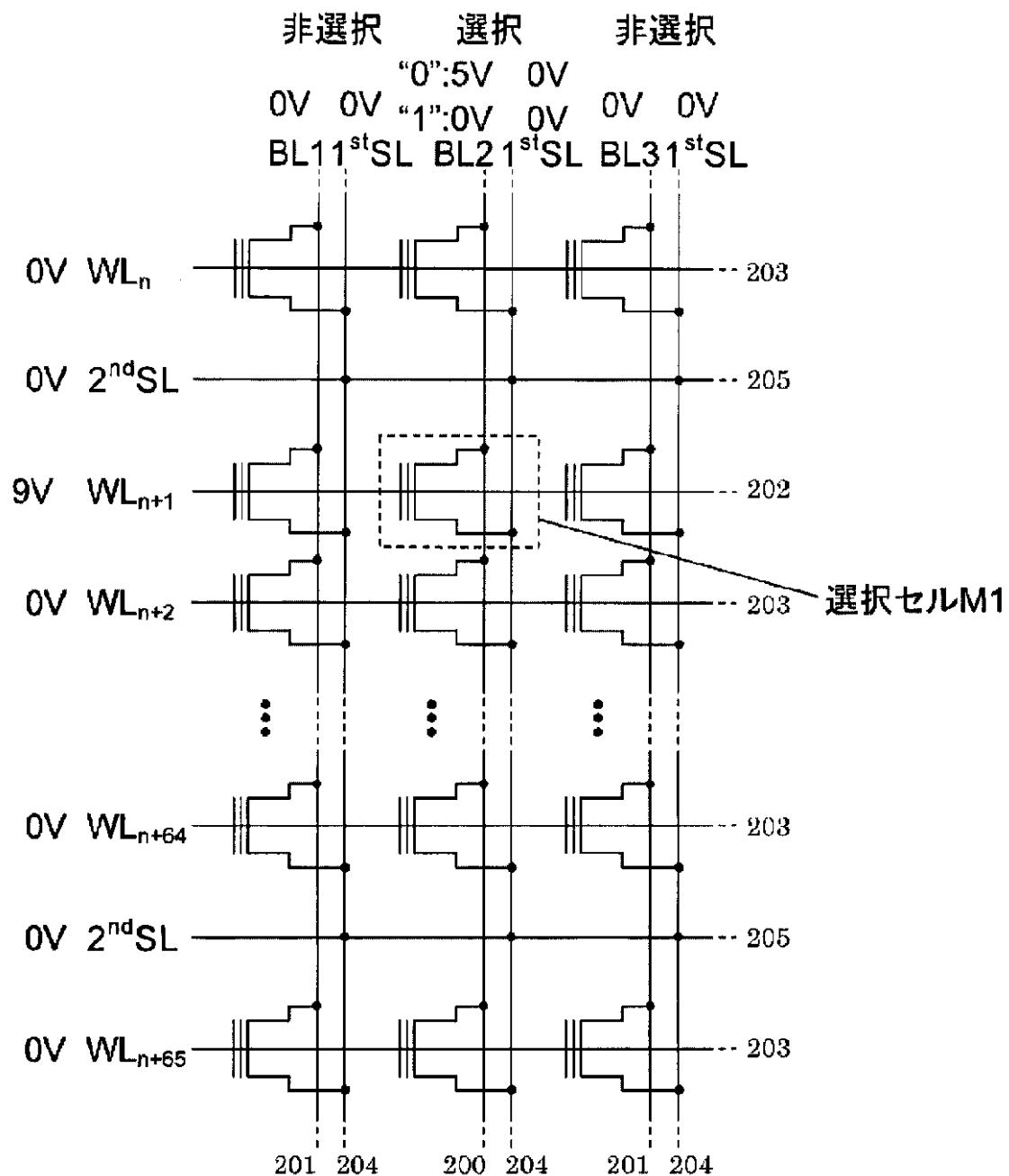

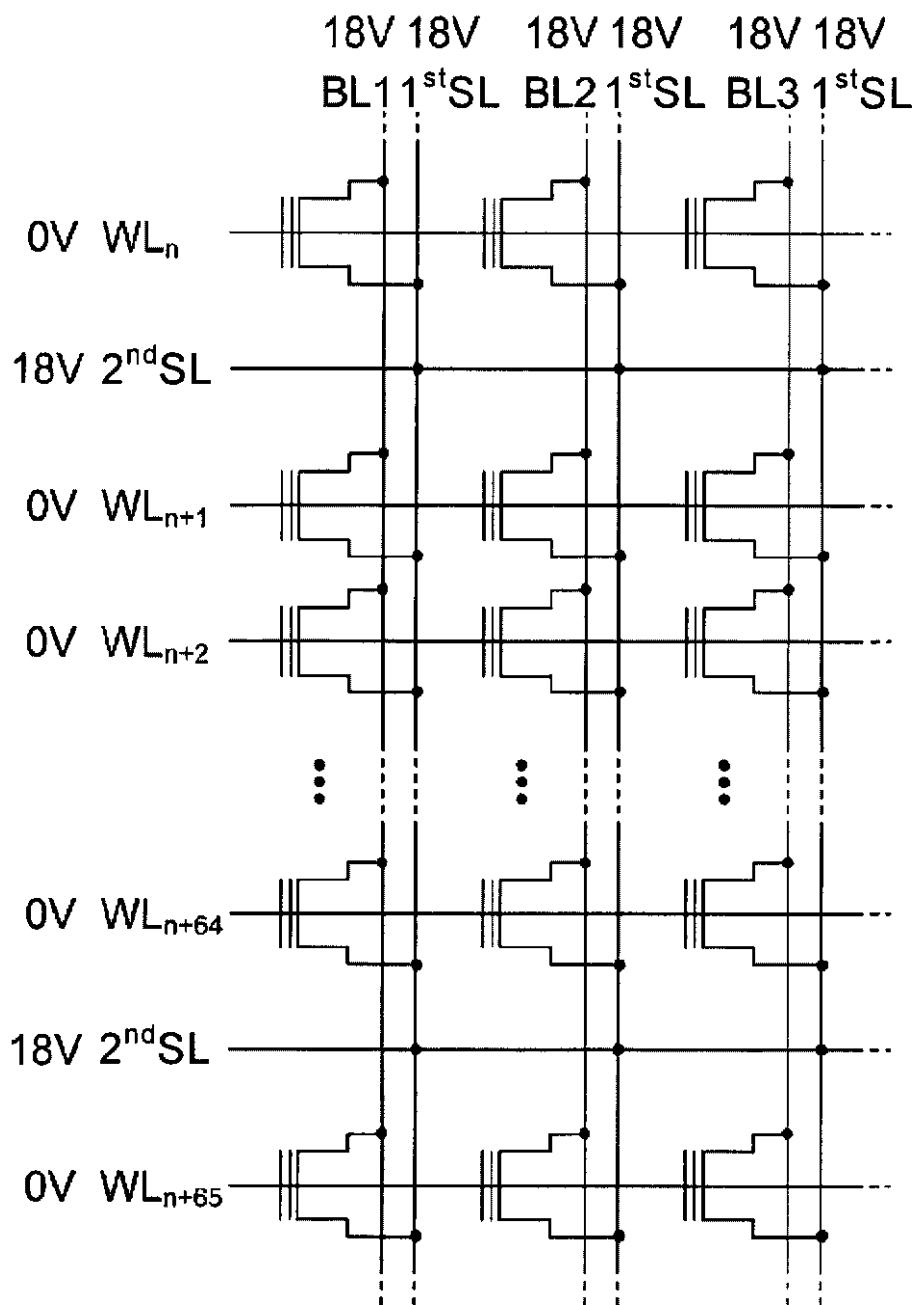

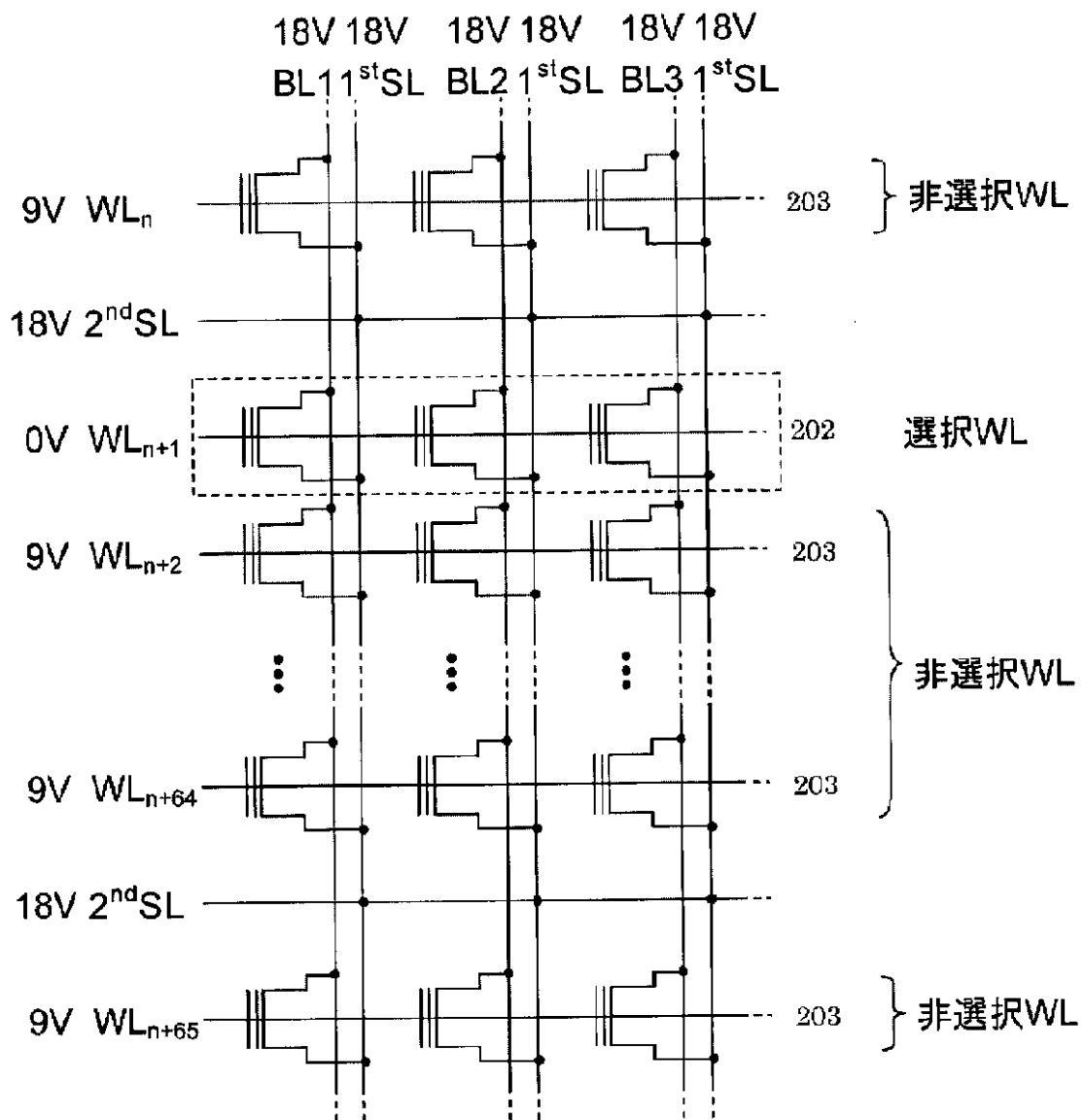

【0042】

以下に、この発明の不揮発性半導体メモリトランジスタアレイの駆動方法を図66～図69

を参照して説明する。

【0043】

選択したメモリトランジスタM1の電荷蓄積層へ、ホット・エレクトロンにより電荷を注入する（書き込む）動作は、図66に示すように行う。選択したビット線200に0Vもしくはホット・エレクトロンが発生する程度の電圧（5V）を印加し、非選択のビット線201に、0Vを印加し、選択したゲート線202に、高電圧（9V）を印加し、非選択のゲート線203に、0Vを印加し、第1次ソース線204と第2次ソース線205に0Vを印加する。以上の動作で、ホット・エレクトロンを用いて電荷を電荷蓄積層に注入することができる。

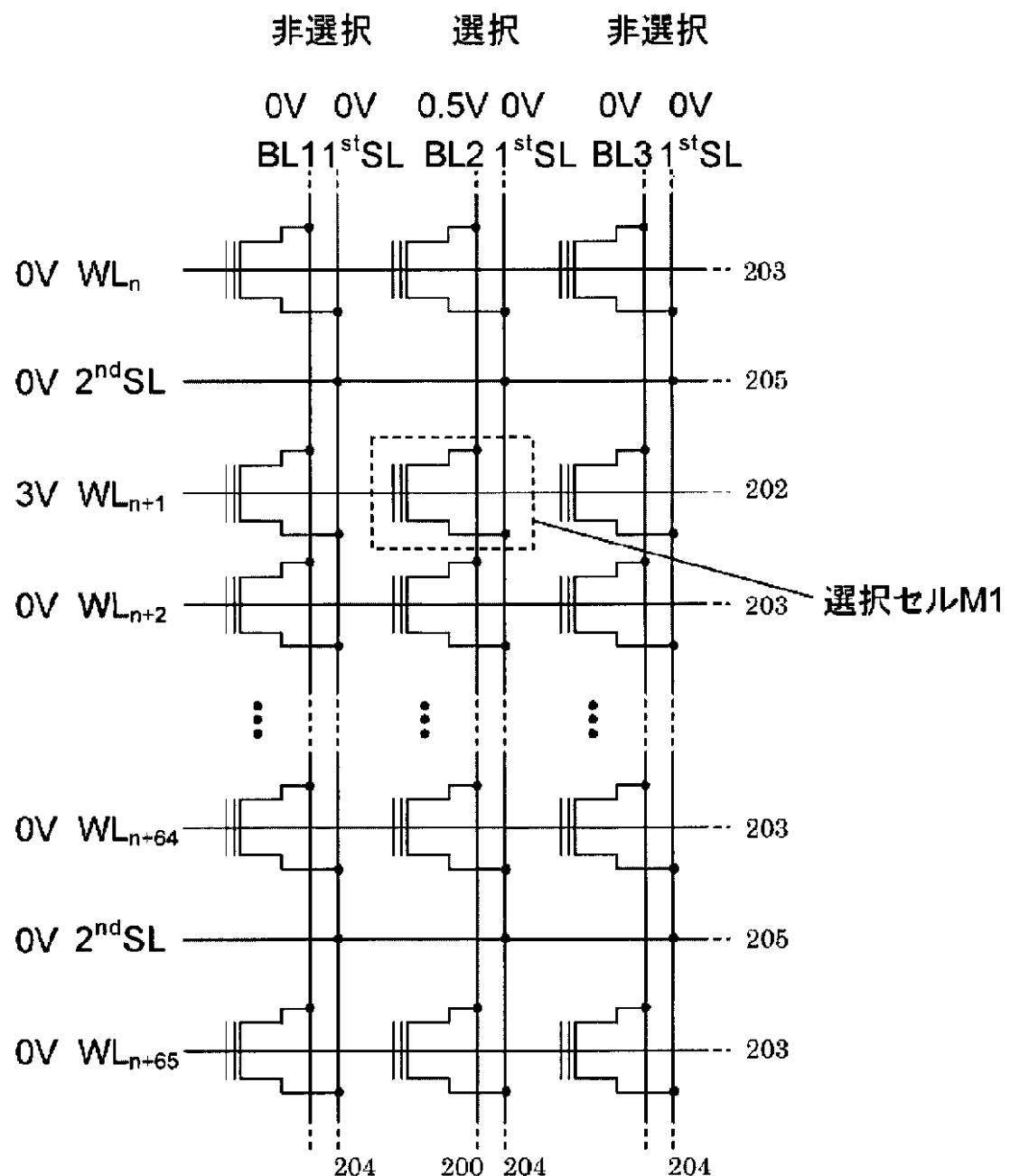

【0044】

選択したメモリトランジスタM1のデータの読み出し動作は、図67に示すように行う。選択したゲート線202に電圧（3V）を印加し、非選択のゲート線203に0Vを印加し、第1次ソース線204と第2次ソース線205に0Vを印加し、選択したビット線200に電圧（0.5V）を印加することで、選択したメモリトランジスタを読み出すことができる。

【0045】

メモリトランジスタアレイの全メモリトランジスタの電荷蓄積層から、FNトンネル電流により電荷を放出する（消去）動作は、図68に示すように行う。全ビット線と全第1次ソース線と第2次ソース線に消去電圧（18V）を印加し、全ゲート線に0Vを印加することで、FNトンネル電流を利用して全メモリトランジスタの電荷蓄積層から電荷を放出することができる。

【0046】

メモリトランジスタアレイの選択したゲート線に接続されたメモリトランジスタの電荷蓄積層から、FNトンネル電流により電荷を放出する（消去）動作は、図69に示すように行う。全ビット線と第1次ソース線と第2次ソース線に消去電圧（18V）を印加し、選択したゲート線202に0Vを印加し、非選択のゲート線203に消去を阻止できる程度の電圧（9V）を印加することで、FNトンネル電流を利用して選択したゲート線に接続されたメモリトランジスタの電荷蓄積層から電荷を放出することができる。

【0047】

また、実施例では、島状半導体層のドレイン拡散層とソース拡散層に挟まれた側壁のチャネル領域上にゲート絶縁膜を介して、島状半導体を取り囲む単一の電荷蓄積層の構造のメモリトランジスタを用いたが、電荷蓄積層は必ずしも単一の電荷蓄積層である必要はなく、図70に示すように、島状半導体の側壁のチャネル領域上の一部を一または複数個の電荷蓄積層300が取り囲んでいてもよい。また、ゲートと島状半導体層の間に、一または複数個の粒子状の電荷蓄積層301あるいは電荷蓄積可能な領域を持つホット・エレクトロンを利用して書き込み可能な構造の不揮発性半導体メモリトランジスタ（図71）を用いてもよい（図72）。

【0048】

上述したように、この発明によれば、所定数のゲート線毎に、メタルを用いて形成された第2次ソース線を持つため、ソース線を低抵抗化することができ、書き込み時にメモリトランジスタのソース拡散層に0Vを与えることができ、ソース・ドレイン間に十分な電圧を与えることができ、ソース・ドレイン間に十分な電流を流すことができ、書き込み速度の低下を回避することができる。また、読み出し時においても、メモリトランジスタのソース拡散層に0Vを与えることができ、ソース・ドレイン間に十分な電圧を与えることができ、ソース・ドレイン間に十分な電流を流すことができ、読み出し速度の低下を回避することができる。

【図面の簡単な説明】

【0049】

【図1】この発明に係る不揮発性半導体メモリのレイアウトである。

【図2】この発明に係る不揮発性半導体メモリの図1におけるX<sub>1</sub>-X<sub>1</sub>'断面図に対応する断面図である。

【図3】この発明に係る不揮発性半導体メモリの図1におけるY<sub>1</sub>-Y<sub>1</sub>'断面図に対応する断

面図である。

【図4】この発明に係る不揮発性半導体メモリの図1におけるY<sub>2</sub>-Y'2断面図に対応する断面図である。

【図5】この発明に係る不揮発性半導体メモリのレイアウトである。

【図6】この発明に係る不揮発性半導体メモリの図1におけるX<sub>1</sub>-X'1断面図に対応する断面図である。

【図7】この発明に係る不揮発性半導体メモリの図1におけるY<sub>1</sub>-Y'1断面図に対応する断面図である。

【図8】この発明に係る不揮発性半導体メモリの図1におけるY<sub>2</sub>-Y'2断面図に対応する断面図である。

【図9】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X'1断面工程図である。

【図10】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y'1断面工程図である。

【図11】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図12】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X'1断面工程図である。

【図13】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y'1断面工程図である。

【図14】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図15】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X'1断面工程図である。

【図16】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y'1断面工程図である。

【図17】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図18】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X'1断面工程図である。

【図19】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y'1断面工程図である。

【図20】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図21】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X'1断面工程図である。

【図22】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y'1断面工程図である。

【図23】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図24】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X'1断面工程図である。

【図25】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y'1断面工程図である。

【図26】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図27】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X'1断面工程図である。

【図28】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y'1断面工程図である。

【図29】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図30】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X<sub>1</sub>断面工程図である。

【図31】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y<sub>1</sub>'断面工程図である。

【図32】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図33】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X<sub>1</sub>断面工程図である。

【図34】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y<sub>1</sub>断面工程図である。

【図35】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図36】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X<sub>1</sub>断面工程図である。

【図37】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y<sub>1</sub>'断面工程図である。

【図38】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図39】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X<sub>1</sub>'断面工程図である。

【図40】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y<sub>1</sub>断面工程図である。

【図41】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図42】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X<sub>1</sub>断面工程図である。

【図43】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y<sub>1</sub>'断面工程図である。

【図44】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図45】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X<sub>1</sub>'断面工程図である。

【図46】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y'、<sub>1</sub>断面工程図である。

【図47】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図48】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X<sub>1</sub>'断面工程図である。

【図49】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y'、<sub>1</sub>断面工程図である。

【図50】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y' <sub>2</sub>断面工程図である

【図51】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X<sub>1</sub>'断面工程図である。

【図52】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y<sub>1</sub>断面工程図である。

【図53】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y'2断面工程図である。

【図 5 4】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X<sub>1</sub>'<sub>1</sub>断面工程図である。

【図 5 5】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y<sub>1</sub>'<sub>1</sub>断面工程図である。

【図 5 6】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y<sub>2</sub>'<sub>2</sub>断面工程図である。

【図 5 7】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X<sub>1</sub>'<sub>1</sub>断面工程図である。

【図 5 8】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y<sub>1</sub>'<sub>1</sub>断面工程図である。

【図 5 9】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y<sub>2</sub>'<sub>2</sub>断面工程図である。

【図 6 0】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X<sub>1</sub>'<sub>1</sub>断面工程図である。

【図 6 1】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y<sub>1</sub>'<sub>1</sub>断面工程図である。

【図 6 2】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y<sub>2</sub>'<sub>2</sub>断面工程図である。

【図 6 3】この発明に係るメモリトランジスタアレイの製造例を示すX<sub>1</sub>-X<sub>1</sub>'<sub>1</sub>断面工程図である。

【図 6 4】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>1</sub>-Y<sub>1</sub>'<sub>1</sub>断面工程図である。

【図 6 5】この発明に係るメモリトランジスタアレイの製造例を示すY<sub>2</sub>-Y<sub>2</sub>'<sub>2</sub>断面工程図である。

【図 6 6】データ書き込み時の電位関係を示す図である。

【図 6 7】データ読み出し時の電位関係を示す図である。

【図 6 8】全メモリトランジスタ消去時の電位関係を示す図である。

【図 6 9】選択されたゲート線に接続されたメモリトランジスタ消去時の電位関係を示す図である。

【図 7 0】この発明に係る他の実施例を示す鳥瞰図である。

【図 7 1】この発明に係る他の実施例を示す鳥瞰図である。

【図 7 2】この発明に係る他の実施例を示す断面図である。

【符号の説明】

【0 0 5 0】

- 1 シリコン酸化膜

- 2 第1次ソース線 (1st S L)

- 3 ソース拡散層

- 4 島状半導体層

- 5 ドレイン拡散層

- 6 電荷蓄積層

- 7 ゲート線 (W L)

- 8 ビット線

- 9 第2次ソース線 (2nd S L)

10 第1の共通拡散ソース線

- 100 P型シリコン

- 101 島状半導体層

- 102 トンネル絶縁膜

- 103 多結晶シリコン膜

- 104 インターポリ絶縁膜

- 105 多結晶シリコン膜

1 0 6 レジスト

1 0 7 層間絶縁膜

1 0 8 メタル

1 0 9 層間絶縁膜

2 0 0 選択したビット線

2 0 1 非選択のビット線

2 0 2 選択したゲート線

2 0 3 非選択のゲート線

2 0 4 第1次ソース線

2 0 5 第2次ソース線

3 0 0 電荷蓄積層

3 0 1 粒子状電荷蓄積層

【手続補正3】

【補正対象書類名】図面

【補正対象項目名】図1

【補正方法】変更

【補正の内容】

【図 1】

【手続補正 4】

【補正対象書類名】図面

【補正対象項目名】図 2

【補正方法】変更

【補正の内容】

【図2】

【手続補正5】

【補正対象書類名】図面

【補正対象項目名】図3

【補正方法】変更

【補正の内容】

【図3】

【手続補正6】

【補正対象書類名】図面

【補正対象項目名】図4

【補正方法】変更

【補正の内容】

【図4】

【手続補正7】

【補正対象書類名】図面

【補正対象項目名】図5

【補正方法】変更

【補正の内容】

【図 5】

【手続補正 8】

【補正対象書類名】図面

【補正対象項目名】図 6

【補正方法】変更

【補正の内容】

【図 6】

【手続補正 9】

【補正対象書類名】図面

【補正対象項目名】図 7

【補正方法】変更

【補正の内容】

【図 7】

【手続補正 1 0】

【補正対象書類名】図面

【補正対象項目名】図 8

【補正方法】変更

【補正の内容】

【図 8】

【手続補正 1 1】

【補正対象書類名】図面

【補正対象項目名】図 9

【補正方法】変更

【補正の内容】

【図 9】

X<sub>1</sub> \_\_\_\_\_ X'<sub>1</sub>

100

【手続補正 1 2】

【補正対象書類名】図面

【補正対象項目名】図 6 6

【補正方法】変更

【補正の内容】

【図 6 6】

【手続補正 1 3】

【補正対象書類名】図面

【補正対象項目名】図 6 7

【補正方法】変更

【補正の内容】

【図 6 7】

【手続補正 1 4】

【補正対象書類名】図面

【補正対象項目名】図 6 8

【補正方法】変更

【補正の内容】

【図 6.8】

【手続補正 1.5】

【補正対象書類名】図面

【補正対象項目名】図 6.9

【補正方法】変更

【補正の内容】

【図 6 9】

【手続補正 1 6】

【補正対象書類名】図面

【補正対象項目名】図 7 2

【補正方法】変更

【補正の内容】

【図 7-2】