(12)

## EUROPÄISCHE PATENTSCHRIFT

(45) Veröffentlichungstag der Patentschrift :

**17.06.92 Patentblatt 92/25**

(51) Int. Cl.<sup>5</sup> : **G04F 10/10**

(21) Anmeldenummer : **89911553.9**

(22) Anmeldetag : **12.10.89**

(86) Internationale Anmeldenummer :

**PCT/EP89/01209**

(87) Internationale Veröffentlichungsnummer :

**WO 90/04219 19.04.90 Gazette 90/09**

(54) **SCHALTUNGSAORDNUNG ZUR DIGITALEN ERFASSUNG EINER ANALOGEN INFORMATION IN DER FORM DES ZEITABSTANDES ZWEITERAUFENANDERFOLGENDER ZUSTÄNDE EINES SIGNALS.**

(30) Priorität : **13.10.88 DE 3834938**

(73) Patentinhaber : **Ziegler, Horst Prof. Dr. Steinhauser Weg 13 W-4790 Paderborn (DE)**

(43) Veröffentlichungstag der Anmeldung :

**31.07.91 Patentblatt 91/31**

(72) Erfinder : **ZIEGLER, Horst Steinhauser Weg 13 W-4790 Paderborn (DE)**

Erfinder : **RIEMER, Gerald Friedenseiche 7 W-4782 Erwitte (DE)**

(45) Bekanntmachung des Hinweises auf die Patenterteilung :

**17.06.92 Patentblatt 92/25**

(74) Vertreter : **Liska, Horst, Dr.-Ing. et al Patentanwälte H. Weickmann, Dr. K. Fincke, F.A. Weickmann, B. Huber, Dr. H. Liska, Dr. J. Prechtel Kopernikusstrasse 9 Postfach 86 08 20 W-8000 München 86 (DE)**

(84) Benannte Vertragsstaaten :

**AT BE CH DE FR GB IT LI LU NL SE**

(56) Entgegenhaltungen :

**FR-A- 2 468 153**

**US-A- 3 735 261**

**US-A- 3 790 890**

**US-A- 4 613 950**

**US-A- 4 772 843**

**EP 0 438 469 B1**

Anmerkung : Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelegt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99(1) Europäisches Patentübereinkommen).

## Beschreibung

Die Erfindung betrifft eine Schaltungsanordnung zur digitalen Erfassung einer analogen Information in der Form des Zeitabstandes zweier aufeinanderfolgender Zustände wenigstens eines Signals oder der Amplitude des Signals, gemäß dem Oberbegriff des Anspruchs 1.

Eine Schaltungsanordnung zur Erfassung von Zeitabständen, insbesondere zur Messung von kleinen Zeitabständen, im Submillisekundenbereich, die mit konventionellen digitalen Zeitabstandsmeßeinrichtungen nicht oder nur mit unzureichender Auflösung bestimmt werden können, umfaßt einen Integrationskondensator, der über eine Ladeschaltung auf eine die analoge Information repräsentierende Spannung ladbar ist, und eine Ladungsänderungsschaltung, die die Spannung des Integrationskondensators mit einer Änderungsrate kleiner als die der Ladeschaltung ändert. Ein Komparator vergleicht die Spannung an dem Integrationskondensator mit einem vorbestimmten Schwellenwert. Ferner ist ein Zähler vorgesehen, welcher während der Änderung der Spannung des Integrationskondensators mittels der Ladungsänderungsschaltung bis zum Erreichen des vorbestimmten Schwellenwertes periodische Taktpulse zählt.

Nachdem der Integrationskondensator über die Ladeschaltung auf eine die analoge Information repräsentierende Spannung geladen worden ist, ändert die Ladungsänderungsschaltung die Spannung am Integrationskondensator bis zum Erreichen des durch den Komparator überwachten Schwellenwertes. Die Dauer dieser Spannungsänderung des Integrationskondensators mittels der Ladungsänderungsschaltung hängt einerseits von vorbestimmten Parametern der Schaltungsanordnung und andererseits von dem Wert der die analoge Information repräsentierenden Integrationskondensatorspannung ab. Nach Ablauf der Spannungsänderung am Integrationskondensator stellt das Zählereignis des Zählers eine digitale Information über die Dauer der Spannungsänderung und damit auch über den Wert der analogen Information dar.

Bei der konventionellen digitalen Messung von Zeitintervallen auf der Grundlage des Auszählens von Flanken periodischer Taktpulse eines Referenztaktsignals bekannter Periodendauer stellt sich das Problem, daß der Beginn bzw. das Ende des Zeitintervalls im allgemeinen nicht mit einer Flanke des Referenztaktsignals zusammenfällt. Der Zeitabstand zwischen dem Beginn des Meßzeitintervalls und dem Auftreten der ersten, ein Zählereignis auslösenden Flanke des Referenztaktsignals wird nicht richtig erfaßt, da keine vollständige Referenztaktperiode auf diesen Zeitabstand entfällt. Eine entsprechende Situation ergibt sich am Ende des Meßzeitintervalls. Der dadurch entstehende Fehler des digitalen Meßergebnisses wird als +/- 1-Digitalisierungsunsicherheit bezeichnet. Die +/- 1-Digitalisierungsunsicherheit begrenzt die relative Auflösung einer Zeitabstandsmessung um so stärker, je größer das Verhältnis von Periodendauer des Referenztaktsignals zur Dauer des zu messenden Zeitabstands ist. Zur Erzielung einer hohen Auflösung einer konventionellen Zeitabstandsmessung ist daher eine hohe Referenztaktfrequenz erforderlich. Ein Referenztaktsignal mit sehr hoher konstanter Frequenz erfordert jedoch aufwendige Oszillatorschaltungen und ist störanfällig.

Eine Möglichkeit der Auflösungsverbesserung bei der Zeitintervallmessung ohne Erhöhung der Referenztaktfrequenz besteht darin, die aufgrund der Asynchronität von Meß- und Referenztaktsignal nicht genau erfaßbaren Zeitabstände am Beginn und am Ende des Meßzeitintervalls mit einer Schaltungsanordnung der oben bezeichneten Art zu bestimmen.

Eine solche Anwendung einer Schaltungsanordnung zur digitalen Erfassung des Zeitabstandes zweier aufeinanderfolgender Zustände wenigstens eines Signals ist aus der Zeitschrift "Elektronik" Jahrgang 7-1988, Heft 14 Seiten 65 bis 68 bekannt. Die bekannte Schaltungsanordnung arbeitet als Analog-Interpolator eines Zeitintervall-Meßsystems und erfaßt den Zeitabstand  $T_1$  zwischen dem Beginn eines zu messenden Zeitintervalls  $T_x$  und einer darauffolgenden vorbestimmten Flanke eines periodischen Referenztaktsignals. Ein weiterer Analog-Interpolator erfaßt den Zeitabstand  $T'_1$  zwischen dem Ende des zu messenden Zeitintervalls und einer darauffolgenden vorbestimmten Flanke des Referenztaktsignals. Die oben genannten vorbestimmten Flanken des Referenztaktsignals schließen ein Zeitintervall  $T_m$  ein, dessen Länge einem ganzzahligen Vielfachen der Periodendauer des Referenztaktsignals entspricht und somit durch Auszählen der in dieses taktsynchrone Zeitintervall fallenden Taktperioden mit einer Zähleinrichtung exakt bestimmbar ist. Aus den mit den Analoginterpolatoren und der Zähleinrichtung ermittelten Informationen über die Zeitabschnitte  $T_1$ ,  $T'_1$  und  $T_m$  berechnet eine Auswerteeinrichtung einen digitalen Meßwert für das zu bestimmende Meßzeitintervall  $T_x$ , wodurch eine hohe Zeitauflösung erzielt wird. Die bekannte Schaltungseinrichtung umfaßt einen in einer Integratorschaltung angeordneten Integrationskondensator, eine Ladeschaltung zum Laden des Integrationskondensators mit einem konstanten Strom einer ersten Ladungsquelle während des zu erfassenden Zeitabstandes  $T_1$  bzw.  $T'_1$ , eine Ladungsänderungsschaltung zum Entladen des Integrationskondensators mit dem Strom einer zweiten Ladungsquelle, und einen Komparator, der die Spannung am Kondensator mit einem dem Entladezustand des Kondensators entsprechenden Schwellenwert vergleicht. Die erste und zweite Ladungsquelle haben einander entgegengesetzte Polarität. Die erste Ladungsquelle liefert einen konstanten Strom, der um den Faktor tausend größer ist als der konstante Strom der zweiten Ladungsquelle. Die Spannungsänderungen am Integra-

tionskondensator während der Lade- und Entladephase verlaufen linear, jedoch mit unterschiedlichen Vorzeichen. Während der Entladephase zählt ein Zähler periodische Taktimpulse des Referenztaktsignals. Nach Ablauf der Entladephase stellt das Zählergebnis des Zählers eine Information über den zu erfassenden Zeitabstand  $T_1$  bzw.  $T'_1$  dar.

5 Die bekannte Schaltungsanordnung hat insbesondere den Nachteil, daß zum Laden und Entladen des Integrationskondensators Ladungsquellen mit entgegengesetzter Polarität erforderlich sind. Darüberhinaus benötigt der Komparator zum Einstellen des Schwellenwertes OV eine negative Gleichspannung. Für den Ladestrom und für den Entladestrom ist eine gute Konstanz zu fordern. Bei Schwankungen des Ladestroms repräsentiert die Integrationskondensatorspannung nach Ablauf der Ladephase das zu erfassende Zeitintervall nur fehlerhaft, während Schwankungen des Entladestroms einen störenden Einfluß auf die Entladezeit und somit auf das Zählergebnis des Zählers haben. Die erforderliche Stabilisierung der Ströme unterschiedlicher Vorzeichen auf jeweils vorbestimmte Werte, die sich darüberhinaus noch wesentlich unterscheiden, ist mit einem hohen Schaltungsaufwand verbunden, der die Schaltungsanordnung kompliziert und teuer macht. Zur Erzielung einer hohen Meßgenauigkeit des bekannten Analog-Interpolators ist eine aufwendige statistische Kalibrierung zur Bestimmung des Verhältnisses von Ladestrom zu Entladestrom nach jedem Meßvorgang erforderlich. Dabei wird jeder der Interpolatoren mit Hilfe von Referenzimpulsen kalibriert, die den Eingängen der Interpolatoren über einen Präzisionsphasenschieber zugeführt werden. Diese Kalibriermethode erfordert neben einem zusätzlichen Schaltungsaufwand einen vergleichsweise großen Rechenaufwand der Auswerteinrichtung.

20 Aus dem Fachbuch: Halbleiterschaltungstechnik, Verfasser: Tietze-Schenk, Dritte Auflage, Springer-Verlag, Heidelberg New York 1980, Seite 662, ist eine Schaltungsanordnung zur digitalen Erfassung der Spannungsamplitude eines analogen Signals bekannt. Diese bekannte Schaltungsanordnung arbeitet nach dem "dual-slope"-Analog-Digital-Wandler-Verfahren und umfaßt einen Integrationskondensator in einer Integratororschaltung mit Operationsverstärker. Der Eingang der Integratororschaltung ist während eines vorbestimmten 25 Integrationszeitintervalls über eine Ladeschaltung mit der Signalquelle elektrisch verbunden, wodurch der Integrationskondensator auf eine der zu messenden Signalspannung proportionale Spannung geladen wird. Nach Ablauf des Integrationszeitintervalls wird der Eingang der Integratororschaltung an eine Referenzspannungsquelle mit konstanter Referenzspannung angeschlossen, um den Integrationskondensator zu entladen. Dabei ändert sich die Kondensatorspannung linear mit der Zeit. Während des Entladevorgangs zählt ein Zähler periodische Taktpulse einer Referenztaktquelle. Ein Komparator beendet den Zählvorgang, wenn die Spannung am Kondensator auf den Wert OV abgesunken ist. Nach Ablauf der Entladephase stellt das Zählergebnis des Zählers eine digitale Information über die zu messende Signalspannung dar.

30 Ein Nachteil dieses bekannten Analog-Digital-Wandlers liegt darin, daß für den kontrollierten Entladevorgang des Integrationskondensators und damit für eine hohe Genauigkeit der Spannungsmessung eine sehr gut konstante Referenzspannung erforderlich ist, deren Vorzeichen entgegengesetzt zum Vorzeichen der Meßspannung ist. Die bekannte Schaltungsanordnung erfordert daher wenigstens eine positive und eine negative Spannungsquelle mit jeweils sehr gut konstanter Ausgangsspannung, und eine Schalteinrichtung, die die Referenzspannung umpolst.

35 Der Erfindung liegt die Aufgabe zugrunde, eine Schaltungsanordnung zur digitalen Erfassung einer analogen Information in der Form des Zeitabstandes zweier aufeinanderfolgender Zustände wenigstens eines Signals oder der Amplitude des Signals anzugeben, deren Schaltungsaufwand und Störanfälligkeit gering ist.

40 Diese Aufgabe wird erfindungsgemäß dadurch gelöst, daß die Ladeschaltung und die Ladungsänderungsschaltung die Spannung des Integrationskondensators in gleicher Richtung ändern und an eine gemeinsame Ladungsquelle angeschlossen sind.

45 Die erfindungsgemäße Schaltungsanordnung ist mit geringem Schaltungsaufwand realisierbar und arbeitet nahezu störungsunanfällig. Insbesondere ist zum Betrieb der Schaltung nur eine Ladungsquelle, zum Beispiel eine Gleichspannungsquelle erforderlich. Ein weiterer Vorteil liegt darin, daß die Schaltungsanordnung ohne Einschränkung ihrer Zuverlässigkeit aus vergleichsweise preiswerten Bauelementen aufgebaut werden kann.

50 Mit einer Weiterbildung der Erfindung zur digitalen Erfassung des Zeitabstandes zweier aufeinanderfolgender Zustände wenigstens eines Signals, gemäß Anspruch 2, wird sichergestellt, daß die Ladeschaltung nur während des zu erfassenden Zeitabstandes wirksam geschaltet ist, um den Integrationskondensator auf eine den zu messenden Zeitabstand repräsentierende Spannung zu laden. Ferner ist sichergestellt, daß die Spannungsänderung des Integrationskondensators mittels der Ladungsänderungsschaltung unmittelbar im Anschluß an den zu erfassenden Zeitabstand erfolgt, wodurch die den Zeitabstand repräsentierende Spannung am Integrationskondensator ohne Verfälschung durch Leckströme, störungssicher und vergleichsweise schnell ausgewertet werden kann.

55 Gemäß der Weiterbildung der Erfindung nach Anspruch 3 lassen sich verschiedene Signalzustände eines

Signals als Begrenzungsmarken eines zu messenden Zeitabstandes auswählen. Die Signalzustände können beispielsweise steigende oder fallende Flanken eines Meßsignals sein.

Gemäß der Weiterbildung der Erfindung nach Anspruch 4 lassen sich Zeitabstände zwischen Signalzuständen von Signalen aus verschiedenen Quellen erfassen.

5 Durch Verwendung einer Gleichspannungsquelle als Ladungsquelle, insbesondere einer Versorgungsgleichspannungsquelle der Schaltungsanordnung wird der Schaltungsaufwand zur Stromversorgung minimal gehalten.

Die Weiterbildung der Erfindung gemäß Anspruch 6, zur Messung der Amplitude des Signals, gewährleistet ein konstantes Integrationszeitintervall zum Laden des Integrationskondensators auf eine die Amplitude 10 des analogen Signals repräsentierende Spannung. Durch Auszählen von periodischen Taktpulsen, die in die sich an das Integrationszeitintervall anschließende Ladungsänderungsphase fallen, wird eine digitale Information über die zu erfassende analoge Signalspannung erhalten.

Eine Abtast-Halte-Schaltung zur Zwischenspeicherung von Signalamplitudenwerten ermöglicht die digitale Erfassung von Amplitudenwerten zeitveränderlicher Signale.

15 Die Ladeschaltung lässt sich durch Einstellen eines ersten Widerstandswertes und die Ladungsänderungsschaltung durch Einstellen eines zweiten Widerstandswertes der Widerstandsschaltung nach Anspruch 8 einfacher realisieren, wobei Lade und Ladungsänderungsschaltung mit einer gemeinsamen Ladungsquelle auskommen.

20 Im Anspruch 9 wird eine sehr einfache Möglichkeit zur Änderung des Widerstandswertes der Widerstandsschaltung angegeben. Ein besonderer Vorteil der Widerstandsschaltung nach Anspruch 9 besteht darin, daß der Ladungsfluß zum Kondensator während der Ladephase und während der Ladungsänderungsphase im wesentlichen von störungensfälligen passiven Bauelementen, nämlich Ohm'schen Widerständen, abhängt. Die vorgeschlagene Widerstandsschaltung gewährleistet bei sehr einfacherem Aufbau eine nahezu störungensfällige 25 Erfassung der analogen Information. Hinzukommt, daß Widerstände mit hoher Präzision, Temperaturunabhängigkeit und Langzeitstabilität ihrer Widerstandswerte mit den heutzutage vorhandenen Technologien ohne Schwierigkeiten bei gleichzeitig geringen Kosten herstellbar sind, was zur preiswerten Realisierung der Schaltungsanordnung beiträgt.

25 Dadurch, daß der zweite Widerstand der Widerstandsschaltung nach Anspruch 9 einen wesentlich größeren Widerstandswert als der erste Widerstand hat, ist die Änderungsrate der Spannung des Integrationskondensators während der Spannungsänderung mittels der Ladungsänderungsschaltung wesentlich kleiner als die Änderungsrate der Spannungsänderung am Integrationskondensator während der Ladephase mittels der Ladeschaltung. Dies ist insbesondere von Bedeutung, wenn Zeitabstände digital erfaßt werden sollen, die etwa gleich lang oder kürzer als die Periodendauer des periodischen Taktsignals sind. Die von der Dauer der Ladephase abhängige Dauer der Ladungsänderungsphase kann durch Wahl des Widerstandsverhältnisses des ersten und zweiten Widerstandes immer so lang gewählt werden, daß mehrere periodische Taktpulse während der Ladungsänderungsphase auftreten, so daß durch Zählen dieser Taktpulse eine digitale Information über die Dauer der Ladephase erhalten wird.

30 Entsprechend der Weiterbildung der Erfindung nach Anspruch 11 kann der Integrationskondensator durch einen zweiten Schalter der Steuereinrichtung kurzgeschlossen werden, um die Anfangsbedingungen für einen neuen Meßvorgang herzustellen.

35 Ausführungsbeispiele der Erfindung sind in den Zeichnungen dargestellt und werden im folgenden näher beschrieben.

Es zeigen

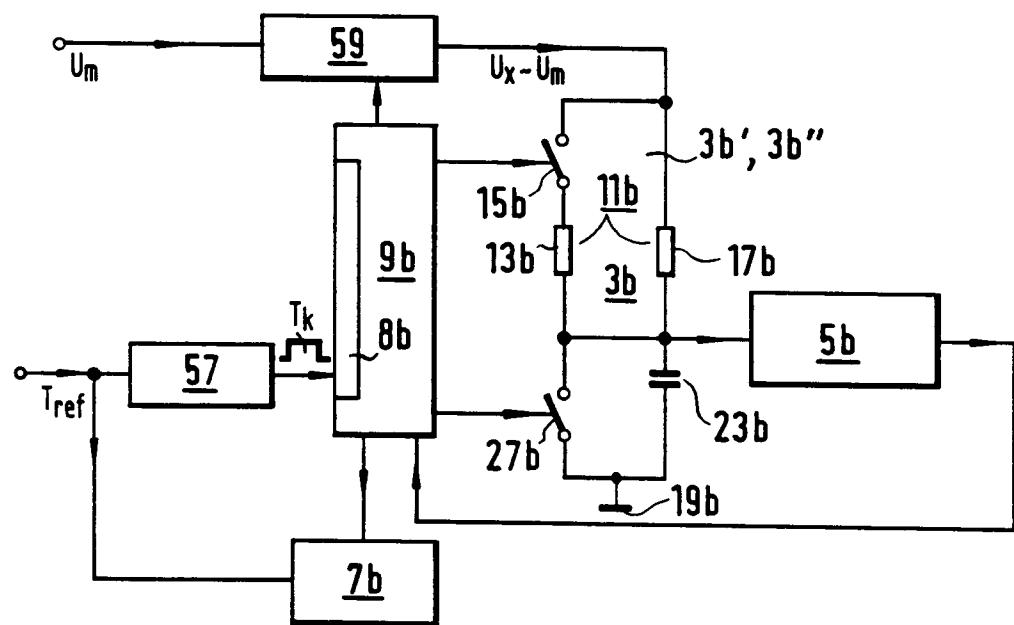

40 Fig. 1 eine schematische Darstellung einer Schaltungsanordnung nach der Erfindung zur digitalen Erfassung eines Zeitabstandes zwischen aufeinanderfolgenden Zuständen wenigstens eines Signals,

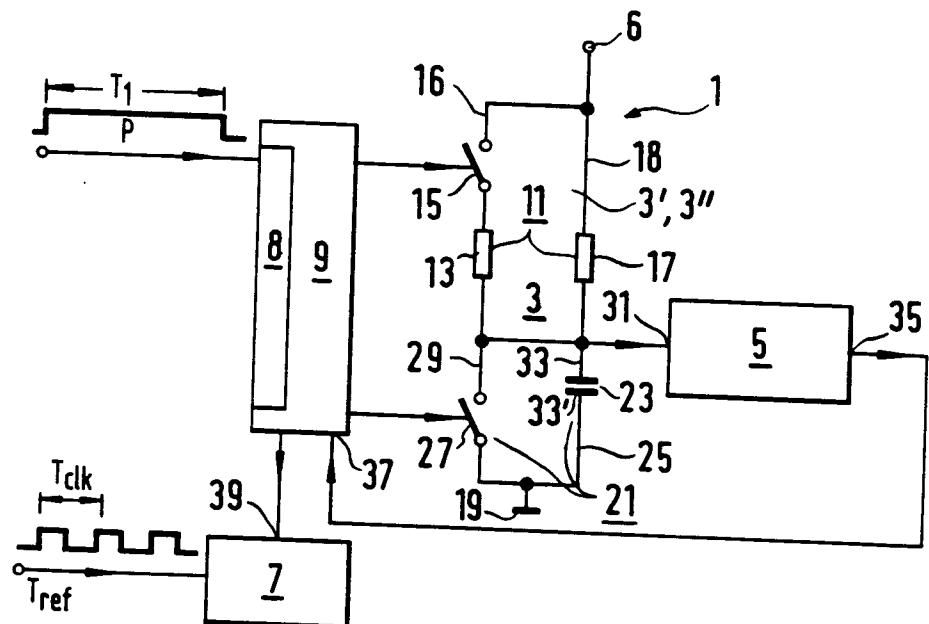

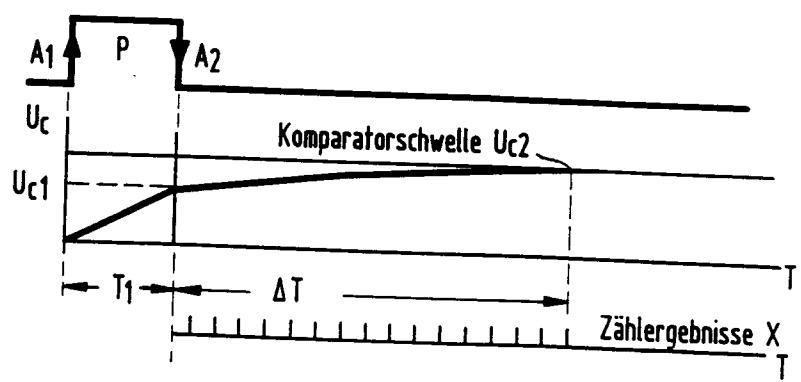

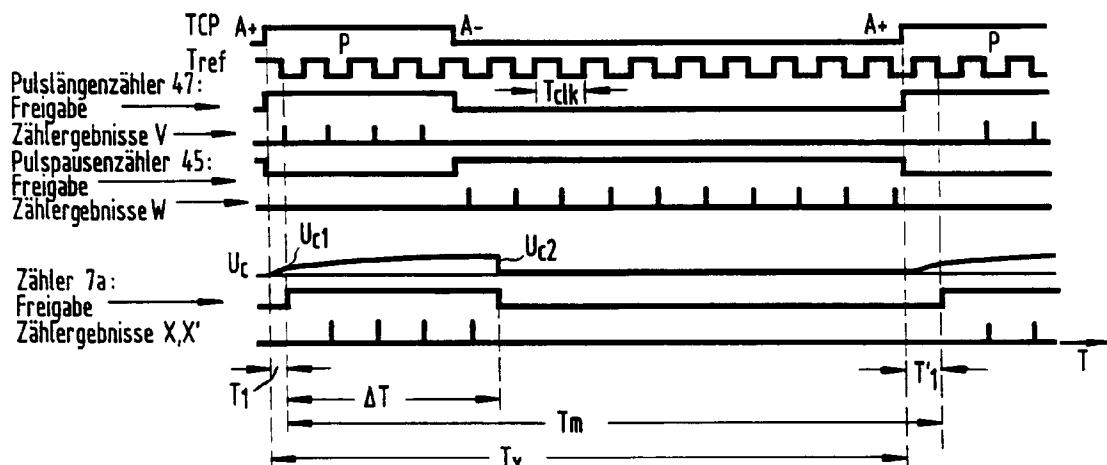

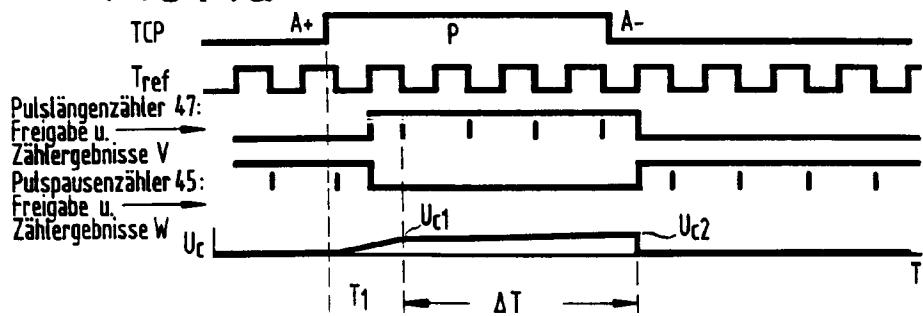

Fig. 2 ein Signalablaufdiagramm zur Erläuterung der Arbeitsweise der Schaltungsanordnung nach Fig. 1, Fig. 3 eine schematische Darstellung einer Zeitintervall-Meßeinrichtung mit einem Ausführungsbeispiel der Erfindung,

Fig. 4 und Fig. 4a ein Signalablaufdiagramm zur Erläuterung der Arbeitsweise der Zeitintervall-Meßeinrichtung nach Fig. 3 und

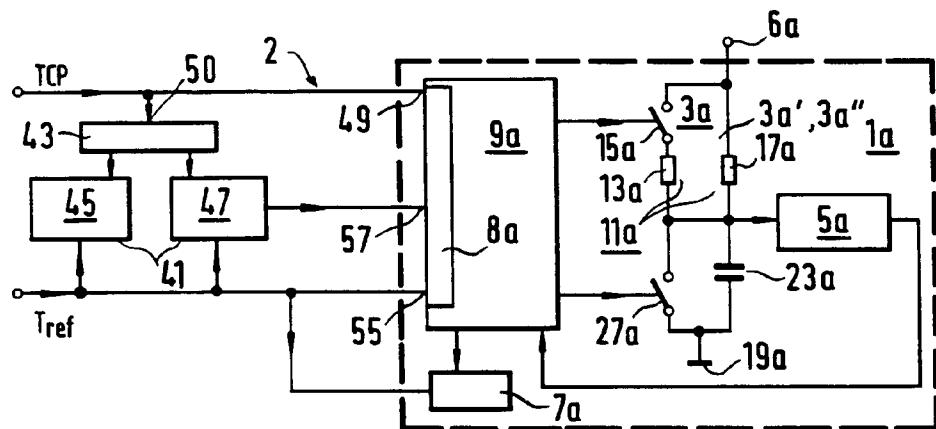

Fig. 5 eine schematische Darstellung eines Ausführungsbeispiels der Erfindung zur digitalen Erfassung der Amplitude eines Signals.

45 Die in Fig. 1 mit 1 bezeichnete Schaltungsanordnung nach der Erfindung umfaßt einen analogen Schaltungsteil 3, einen Komparator 5, einen Zähler 7 und eine Steuereinrichtung 9. Der analoge Schaltungsteil 3 umfaßt eine an den Pluspol 6 einer positiven Gleichspannungsquelle angeschlossene Widerstandsschaltung 11 mit einem ersten Widerstand 13 in Serie zu einem ersten Schalter 15 in einem ersten Zweig 16 und mit einem zweiten Widerstand 17 parallel zum ersten Widerstand 13 und zum ersten Schalter 15 in einem zweiten Zweig 18, ferner in Serie zur Widerstandsschaltung 11 eine an das Bezugspotential 19 (Masse) der Gleichspannungs-

quelle angeschlossene Parallelschaltung 21 aus einem Integrationskondensator 23 in einem dritten Zweig 25 und einem zweiten Schalter 27 in einem vierten Zweig 29.

Der erste Schalter 15 und der zweite Schalter 27 werden von der Steuereinrichtung 9 gesteuert und schalten je nach Schaltzustand einen Strom durch den ersten Zweig 16 bzw. durch den vierten Zweig 29 ein oder aus. Ein Eingang 31 des Komparators 5 ist mit einem ersten Anschluß 33 des Integrationskondensators 23 elektrisch verbunden. Der Komparator 5 vergleicht die Spannung  $U_c$  am Integrationskondensator 23 mit einem vorbestimmten Schwellenwert  $U_{c2}$  und ändert den Zustand seines Komparatorausgangssignals, wenn die Kondensatorspannung  $U_c$  den Schwellenwert  $U_{c2}$  erreicht. Ein das Komparatorausgangssignal führender Ausgang 35 des Komparators 5 ist mit einem Eingang 37 der Steuereinrichtung 9 elektrisch verbunden. Ein Signalzustandsdetektor 8 der Steuereinrichtung 9 detektiert vorbestimmte aufeinanderfolgende Zustandsänderungen wenigstens eines Meß-, beispielsweise die positive und negative Flanke eines Rechteckpulses eines Meßsignals, und die Steuereinrichtung 9 steuert den ersten Schalter 15 bzw. zweiten Schalter 27 in Abhängigkeit vom Auftreten der vorbestimmten Zustandsänderungen wenigstens eines Meßsignals bzw. in Abhängigkeit vom Auftreten einer Zustandsänderung des Komparatorausgangssignals. Die Steuereinrichtung 9 ist ferner mit einem Zählfreigabeingang 39 des Zählers 7 elektrisch verbunden, um die Zählbereitschaft des Zählers 7 in Abhängigkeit vom Auftreten einer vorbestimmten Zustandsänderung wenigstens eines Meßsignals bzw. des Komparatorausgangssignals ein- bzw. auszuschalten. Bei eingeschalteter Zählbereitschaft zählt der Zähler 7 Taktpulse eines periodischen Taktsignals Tref konstanter Taktperiode Tclk.

Anhand eines Beispiels einer Pulslängenmessung mit dem Ausführungsbeispiel der Erfindung wird nachstehend die zeitliche Folge verschiedener Schritte bei der digitalen Erfassung des Zeitabstandes  $T_1$  zwischen der positiven und der darauffolgenden negativen Flanke eines Rechtecksignalpulses P beschrieben. Dazu wird auf Fig. 1 und Fig. 2 Bezug genommen. Vor dem Auftreten des Pulses P ist der zweite Schalter 27 eingeschaltet und damit der Integrationskondensator 23 über den vierten Zweig 29 kurzgeschlossen und entladen (Ausgangszustand der Schaltung). Bei Auftreten der positiven Flanke  $A_1$  des Rechteckpulses P detektiert der Signalzustandsdetektor 8 der Steuereinrichtung 9 die positive Flanke  $A_1$  als Startsignal einer Messung, und die Steuereinrichtung 9 schaltet durch Ausgabe eines Steuersignals gleichzeitig den zweiten Schalter 27 aus, so daß kein Strom über den vierten Zweig 29 an dem Integrationskondensator 23 vorbeifließen kann. Damit setzt eine Ladephase zum Laden des Integrationskondensators 23 auf eine den Zeitabstand  $T_1$  zwischen den Pulsflanken  $A_1, A_2$  des Rechteckpulses P repräsentierende Spannung  $U_{c1}$  ein. Während der Ladephase ist der erste Schalter 15 eingeschaltet, so daß der Integrationskondensator 23 über den ersten und zweiten Widerstand 13, 17 geladen wird. In der Konfiguration, daß der erste Schalter 15 eingeschaltet und der zweite Schalter 27 ausgeschaltet ist, arbeitet die Analogschaltung 3 als Ladeschaltung 3' mit einer Ladezeitkonstante  $\tau_1$ .

Bei Auftreten der negativen Flanke  $A_2$  des Rechteckpulses P detektiert der Signalzustandsdetektor 8 der Steuereinrichtung 9 die negative Flanke  $A_2$  als Stoppsignal für die Ladephase, und die Steuereinrichtung 9 beendet die Ladephase durch Ausschalten des ersten Schalters 15. Ferner gibt die Steuereinrichtung 9 mit Beendigung der Ladephase ein Signal an den Zähler 7 aus, um die Zählbereitschaft des Zählers 7 einzuschalten, so daß dieser Taktpulse des periodischen Taktsignals Tref zählt. Unmittelbar an die Ladephase schließt sich eine Ladungsänderungsphase  $\Delta T$  an, in der der Integrationskondensator 23 nur noch über den zweiten Widerstand 17 geladen wird. In der während der Ladungsänderungsphase  $\Delta T$  vorliegenden Konfiguration, daß erster und zweiter Schalter 15, 27 ausgeschaltet sind, arbeitet die Analogschaltung 3 als Ladungsänderungsschaltung 3" zur Linderung der Spannung  $U_c$  am Integrationskondensator 23 bis zum Erreichen des von dem Komparator 5 überwachten Schwellenwertes  $U_{c2}$ . Die Ladezeitkonstante  $\tau_2$  der Ladungsänderungsschaltung ist wesentlich größer als die Ladezeitkonstante  $\tau_1$  der Ladeschaltung, so daß die Spannung  $U_c$  am Integrationskondensator 23 während der Ladungsänderungsphase  $\Delta T$  mit einer wesentlich kleineren Änderungsrate als während der Ladephase  $T_1$  geändert wird. Die Zeitkonstante  $\tau_2$  der Ladungsänderungsschaltung ist größer als die Zeitkonstante  $\tau_1$  der Ladeschaltung, da der Gesamtwiderstand der Widerstandsschaltung 11 während der Ladungsänderungsphase (Ladung des Integrationskondensators 23 über den zweiten Widerstand 17) größer ist als während der Ladephase (Ladung des Integrationskondensators 23 über eine Parallelschaltung aus erstem und zweitem Widerstand 13, 17).

Lade- und Ladungsänderungsschaltung 3', 3" ändern die Spannung  $U_c$  am Integrationskondensator 23 in gleicher Richtung. Wenn die Spannung  $U_c$  am Integrationskondensator 23 den vorbestimmten Schwellenwert  $U_{c2}$  erreicht, ändert der Komparator 5 den Zustand des Komparatorausgangssignals, woraufhin die Steuereinrichtung 9 die Zählbereitschaft des Zählers 7 ausschaltet und den zweiten Schalter 27 einschaltet. Der Integrationskondensator 23 wird danach über den zweiten Schalter 27 kurzgeschlossen und entladen, wodurch die Schaltungsanordnung nach der Erfundung in ihren Ausgangszustand zurückgesetzt wird. Das Zählergebnis X des Zählers 7 wird nach Ablauf der Ladungsänderungsphase von einer Auswerteeinrichtung (nicht gezeigt) ausgelesen und als digitale Information zur Berechnung eines Meßwertes für den Zeitabstand  $T_1$  zwischen den Flanken  $A_1, A_2$  des Meßsignals ausgewertet.

Das wesentliche Arbeitsprinzip des Ausführungsbeispiels der Erfindung wurde vorstehend anhand der Erläuterung einer Pulslängenmessung beschrieben. Das Ausführungsbeispiel ist jedoch nicht auf die Messung von Rechteckpulsdauern beschränkt.

Der Signalzustandsdetektor 8 der Steuereinrichtung 9 kann wahlweise ebenso auf andere vorbestimmte 5 Signalzustände als die oben beschriebenen reagieren. Insbesondere können die Signalzustände zum Starten und Stoppen der Ladephase des Integrationskondensators und damit des Meßzeitintervalls von verschiedenen Signalquellen stammen.

Die Schaltungsanordnung nach der Erfindung ist in der Lage, Selbstkalibriermessungen auszuführen. Vor 10 Beginn der Kalibriermessung ist der erste Schalter 15 ausgeschaltet und der zweite Schalter 27 eingeschaltet (Ausgangsschaltzustand), so daß der Integrationskondensator 23 entladen ist. Die Steuereinrichtung 9 startet die Kalibriermessung durch Ausschalten des zweiten Schalters 27 und Einschalten der Zählbereitschaft des Zählers 7. Der Integrationskondensator 23 wird daraufhin nur über den zweiten Widerstand 17 von seinem Entladezustand bis zum Erreichen des Schwellenwertes  $U_{c2}$  geladen. Bei Erreichen des Schwellenwertes  $U_{c2}$  ändert der Komparator 5 den Zustand seines Ausgangssignals, woraufhin die Steuereinrichtung 9 die Kalibriermessung durch Ausschalten der Zählbereitschaft des Zählers 7 und Einschalten des zweiten Schalters 27 15 beendet. Während der Kalibriermessung zählt der Zähler 7 die Taktpulse des periodischen Taktsignals Tref. Das Zählergebnis XT des Zählers 7 wird nach Ablauf der Kalibriermessung von der Auswerteeinrichtung ausgelesen und zwischengespeichert. Dieses Zählergebnis XT der Kalibriermessung wird von der Auswerteeinrichtung in die Auswertung eines oder mehrerer zu messender Zeitabstände  $T_1$  einbezogen.

20 Nachstehend werden mathematische Grundlagen zur Ermittlung eines gesuchten Zeitabstandes  $T_1$  zwischen aufeinanderfolgenden Zuständen wenigstens eines Signals dargelegt.

Bei Beendigung der Ladephase hat die Spannung  $U_c$  am Integrationskondensator 23 den durch nachstehende Gleichung (1) beschriebenen Wert:

$$U_{c1} = U_o (1 - \exp(-T_1/\tau_1)) \quad (1),$$

25 worin  $U_o$  die Spannung der Gleichspannungsquelle,  $T_1$  die Dauer der Ladephase und  $\tau_1$  die Zeitkonstante der Ladeschaltung 3' bezeichnet.

Die Zeitkonstante  $\tau_1$  der Ladeschaltung 3a lässt sich durch die Beziehung:

$$\tau_1 = C R_1 R_2 / (R_1 + R_2) \quad (2)$$

beschreiben, worin  $R_1$  bzw.  $R_2$  den Widerstandswert des ersten bzw. zweiten Widerstandes 13, 17 und  $C$  die 30 Kapazität des Integrationskondensators 23 bezeichnet.

Die Dauer  $\Delta T$  der Ladungsänderungsphase kann durch nachstehende Gleichung (3) beschrieben werden:

$$\Delta T = \tau_2 \ln ((U_o - U_{c1}) / (U_o - U_{c2})) \quad (3),$$

worin

35  $\tau_2 = R_2 \cdot C$  die Ladezeitkonstante der Ladungsänderungsschaltung und  $U_{c2}$  den vom Komparator 5 überwachten Schwellenwert der Integrationskondensatorspannung bezeichnet.

Auflösen der Gleichung (3) nach  $U_{c1}$  führt zu:

$$U_{c1} = U_o - (U_o - U_{c2}) \exp(\Delta T / \tau_2) \quad (4)$$

Gleichsetzen der Gleichungen (1) und (4) und Auflösen des Ergebnisses nach  $T_1$  führt zu einer von der unbekannten Spannung  $U_{c1}$  unabhängigen mathematischen Beschreibung der Dauer der Ladephase bzw. des 40 zu erfassenden Zeitabstandes zwischen zwei aufeinanderfolgenden Zuständen wenigstens eines Signals:

$$T_1 = -R_1 R_2 C / (R_1 + R_2) \ln ((U_o - U_{c2}) / U_o) - R_1 / (R_1 + R_2) X Tclk \quad (5)$$

In Gleichung (5) sind die Zeitkonstanten  $\tau_1$  und  $\tau_2$  durch die Widerstandswerte  $R_1$  und  $R_2$  und durch die 45 Kapazität  $C$  des Integrationskondensators 23 ausgedrückt. Das Symbol  $\Delta T$  für die Dauer der Ladungsänderungsphase ist in Gleichung (5) durch den äquivalenten Ausdruck:  $X Tclk$  ersetzt worden.  $X$  bezeichnet das Zählergebnis des Zählers 7 nach Ablauf der Ladungsänderungsphase und  $Tclk$  die Periodendauer des periodischen Taktsignals Tref. Mit Gleichung (5) kann der zu erfassende Zeitabstand  $T_1$  aus dem Zählergebnis  $X$  und den ansonsten bekannten Parametern der Gleichung (5) bestimmt werden.

Die Gleichung (5) lässt sich durch Einbeziehen des Zählergebnisses XT einer Kalibriermessung noch wesentlich vereinfachen. Die Spannungsänderung  $U_c$  des Integrationskondensators 23 von seinem Entladezustand bis zum Erreichen des Schwellenwertes  $U_{c2}$  erfolgt bei einer Kalibriermessung in der Zeit  $T_3$ , die durch das Produkt aus Zählergebnis XT und Periodendauer  $Tclk$  des periodischen Taktsignals Tref beschrieben werden kann:

$$T_3 = XT \cdot Tclk \quad (3)$$

Unter Verwendung der Gleichung (6) und der exponentiellen Ladefunktion des Integrationskondensators 55 23 entsprechend Gleichung (1) wird der Schwellenwert  $U_{c2}$  in Abhängigkeit vom Zählerstand einer Kalibriermessung angegeben:

$$U_{c2} = U_o (1 - \exp(-XT \cdot Tclk / (R_2 C))) \quad (7)$$

Ersetzt man in Gleichung (5)  $U_{c2}$  durch den Ausdruck der rechten Seite von Gleichung (7), so führt dies

zu Gleichung (8):

$$T_1 = R_1 / (R_1 + R_2) \cdot T_{clk} \cdot (X_T - X) \quad (8)$$

Nach Gleichung (8) wird die Auswertung des Zählergebnisses X zur Bestimmung eines Zeitabstandes  $T_1$  zweier aufeinanderfolgender Zustände wenigstens eines Signals durch Einbeziehung des Zählergebnisses  $X_T$  einer Kalibriermessung wesentlich vereinfacht.

In die Auswertungsgleichung (8) für die digitale Erfassung des Zeitabstandes  $T_1$  zweier aufeinanderfolgender Zustände wenigstens eines Signals geht weder der Wert der Versorgungsspannung  $U_o$  noch der Schwellenwert  $U_{c2}$  des Komparators 5, noch der Kapazitätswert C des Integrationskondensators 23 ein. Eine Langzeitstabilität der vorstehend genannten Größen ist daher nicht erforderlich, wenn eine Zeitabstandsmessung oder eine Meßreihe von Zeitabstandsmessungen mit der Schaltungsanordnung nach der Erfindung jeweils im Zusammenhang mit einer Kalibriermessung durchgeführt wird. Es ist dann lediglich eine leicht zu erfüllende Kurzzeitstabilität der oben genannten Größen für jeweils einen Meßvorgang zu fordern. Auf teure Präzisionsbauelemente mit hoher Langzeitstabilität oder auf aufwendige Stabilisierungsschaltungen kann daher verzichtet werden. Da der Kapazitätswert C des Integrationskondensators 23 nicht in die Gleichung (8) eingeht, spielen auch größere Abweichungen vom Nennkapazitätswert, beispielsweise durch Fertigungstoleranzen, keine Rolle. Die einzigen in die Auswertung eingehenden Geräteparameter sind die Widerstandswerte  $R_1$  und  $R_2$  und die Periodendauer  $T_{clk}$  des Taktsignals. Diese Werte sind sehr einfach zu ermitteln und haben eine gute Konstanz.

Zu diesen ganz wesentlichen Vorteilen der Schaltungsanordnung nach der Erfindung kommt hinzu, daß die Kalibriermessung sehr einfach durchzuführen ist und, statt zusätzlichen Rechenaufwand zu erfordern, die rechnerische Auswertung zur Ermittlung eines Meßzeitintervalls wesentlich vereinfacht.

Die Steuereinrichtung kann aus an sich bekannten elektronischen Bauteilen wie Flipflops, digitale Gatter usw. aufgebaut werden.

Die Gleichspannungsquelle ist vorzugsweise eine Versorgungsgleichspannungsquelle für alle Komponenten der Schalteinrichtung, insbesondere eine 5-V-Gleichspannungsquelle. Durch die Verwendung nur einer Spannungsquelle für alle Komponenten der Schaltungseinrichtung nach der Erfindung ist der Schaltungsaufwand für die Stromversorgung gering. Als erster und zweiter Schalter 15, 27 werden bevorzugt MOS-Feldefekttransistoren mit kurzen Schaltzeiten verwendet. Der Komparator 5 sollte einen Eingangswiderstandswert haben, der wesentlich größer ist als die Widerstandswerte  $R_1$ ,  $R_2$  des ersten und zweiten Widerstandes 13, 17, um die Belastung der Analogschaltung 3 durch den Komparator vernachlässigbar klein zu halten.

In einem bevorzugten Ausführungsbeispiel ist die Komparatorschwelle  $U_{c2}$  auf einen Wert von näherungsweise 2/3 der Versorgungsspannung  $U_o$  der Gleichspannungsquelle eingestellt. Dadurch wird erreicht, daß die Integrationskondensatorspannung  $U_c$  während einer Messung nicht bis in den flachauslaufenden asymptotischen Bereich der exponentiellen Ladefunktion ansteigt. Für die Erfassung kleiner Zeitabstände sollte der Widerstand  $R_2$  mindestens um einen Faktor der Größenordnung 100 größer sein als der Widerstandswert  $R_1$  des ersten Widerstandes 13, so daß die Zeitkonstante  $\tau_2$  der Ladungsänderungsschaltung 3" ebenfalls groß gegenüber der Zeitkonstante  $\tau_1$  der Ladeschaltung 3' ist.

Nachstehend wird eine Zeitintervallmeßeinrichtung 2 mit einer Schaltungsanordnung nach der Erfindung zu digitalen Erfassung eines Zeitabstandes beschrieben.

Mit der Zeitintervallmeßeinrichtung 2 sollen beispielsweise Zeitintervalle  $T_x$  zwischen positiven Flanken  $A_+$  eines Meßsignals TCP mit mehreren aufeinanderfolgenden Pulsen P bestimmt werden (Fig. 4). Die zu bestimmenden Zeitintervalle  $T_x$  sind länger als die Periodendauer  $T_{clk}$  eines Referenztaktsignals Tref, so daß mehrere Taktpulse des Referenztaktsignals zeitlich in ein Zeitintervall  $T_x$  fallen. Wie aus Fig. 4 zu ersehen ist, kann die Länge  $T_x$  des zu ermittelnden Zeitintervalls durch die Beziehung:

$$T_x = T_m + T_1 - T'_1 \quad (9)$$

beschrieben werden. Darin bezeichnet  $T_m$  ein Zeitintervall, das sich aus einem ganzzahligen Vielfachen der Periodendauer  $T_{clk}$  des Referenztaktsignals Tref zusammensetzt,  $T_1$  das Fehlerzeitintervall am Anfang des Meßzeitintervalls  $T_x$  und  $T'_1$  das Fehlerzeitintervall am Anfang des mit der nächsten positiven Flanke des Meßsignals TCP beginnenden Meßzeitintervalls. Das taktsynchrone Zeitintervall  $T_m$  wird durch Auszählen der in das Zeitintervall  $T_m$  fallenden Referenztaktperioden mit einer Zähleinrichtung 41 bestimmt, wogegen die Fehlerzeitintervalle  $T_1$ ,  $T'_1$  mit der Schaltungsanordnung 1a erfaßt werden.

Die Zeitintervallmeßeinrichtung 2 umfaßt neben einer Schaltungsanordnung nach der Erfindung 1a eine Zähleinrichtung 41 und eine Zählerfreigabeschaltung 43. Die Schaltungsanordnung 1a ist im wesentlichen wie die Schaltungsanordnung 1 des vorher beschriebenen Ausführungsbeispiels aufgebaut. Bereits beschriebene Komponenten sind mit dem Buchstaben a hinter der Bezugsziffer gekennzeichnet. Abweichungen vom vorhergehenden Ausführungsbeispiel werden nachstehend erläutert.

Die Zähleinrichtung 41 umfaßt einen Pulspausenzähler 45 zur Zählung von Taktpulsen des Referenztakts.

signals Tref während einer Pulspause zwischen den Pulsen P des Meßsignals TCP und einen Pulslängenzähler 47 zur Zählung von Taktpulsen des Referenztaktsignals während der Dauer eines Pulses P. Eine derartige Zähleinrichtung 41 mit Pulspausen- und Pulslängenzähler 45, 47 ist dann von Vorteil, wenn sowohl Pulsdauern als auch Pulspausen länger sind, als die Periodentauer Tclk des Referenztaktsignals. Der Vorteil liegt darin, daß der Pulslängenzähler 47 bzw. der Pulspausenzähler 45 abwechselnd von einer Auswerteeinrichtung (nicht gezeigt) ausgelesen werden können, während der jeweils andere Zähler 45, 47 Taktpulse zählt. An die Auswerteeinrichtung brauchen dann keine sehr hohen Geschwindigkeitsanforderungen bezüglich des Auslesens der Zählergebnisse der Zähler 45, 47 gestellt werden, um alle in ein Zeitintervall  $T_m$  fallende Zählergebnisse bzw. Taktpulse des Referenztaktsignals Tref zu registrieren.

Das Meßsignal liegt an einem Eingang 49 der Steuereinrichtung 9a und an einem Eingang 50 der Zählerfreigabeschaltung 43 an. Die Zählerfreigabeschaltung 43 steuert die Zählbereitschaft der Zähler 45, 47 in Abhängigkeit vom Auftreten von Pulsflanken des Meßsignals TCP.

Das periodische Referenztaktsignal Tref liegt an den Zähleingängen des Pulslängenzählers 47, des Pulspausenzählers 45 und des Zählers 7a der Schalteinrichtung 1a an. Ferner ist das Referenztaktsignal Tref einem Eingang 55 der Steuereinrichtung 9a zugeführt. Ein Übernahmesignal des Pulslängenzählers 47 ist einem Kontrolleingang 57 der Steuereinrichtung 9a zugeführt.

Tritt eine positive Flanke  $A_+$  des Meßsignals TCP auf, so wird der erste Schalter 15a der Schaltungsanordnung 1a durch die Steuereinrichtung 9a eingeschaltet und der zweite Schalter 27a ausgeschaltet. Damit beginnt die Ladephase, während der der Integrationskondensator 23a über den ersten Widerstand 13a und über zweiten Widerstand 17a geladen wird. Mit Auftreten der positiven Flanke  $A_+$  des Meßsignals TCP sperrt die Zählerfreigabeschaltung 43 die Zählbereitschaft des Pulspausenzählers 45 und schaltet die Zählbereitschaft des Pulslängenzählers 47 ein. Die Ladephase des Integrationskondensators 23a endet mit dem Auftreten einer ersten von dem Pulslängenzähler 47 gezählten negativen Flanke des Referenztaktsignals Tref und entspricht einem zu bestimmenden Fehlerzeitintervall  $T_1$  bzw.  $T'_1$ . Die Steuereinrichtung 9a schaltet mit Beendigung der Ladephase  $T_1$  den ersten Schalter 15a aus, so daß der Integrationskondensator 23a während der Ladungsänderungsphase  $\Delta T$  über den zweiten Widerstand 17a bis zu einem von dem Komparator 5a überwachten Spannungsschwellenwert  $U_{c2}$  weitergeladen wird. Die Steuereinrichtung 9a überwacht das Übernahmesignal vom Pulslängenzähler 47, um festzustellen, ob der Pulslängenzähler 47 die erste negative Flanke des periodischen Taktsignals Tref nach Beginn des Meßzeitintervalls  $T_1$  tatsächlich gezählt hat, und beendet die Ladephase  $T_1$  mit dem Auftreten einer negativen Flanke des Referenztaktsignals erst dann, wenn die Flanke von dem Zähler 47 registriert wurde. Während der Ladungsänderungsphase  $\Delta T$  zählt der Zähler 7a Taktpulse bzw. negative Flanken des periodischen Referenztaktsignals Tref.

Das Zusammenwirken der Steuereinheit 9a mit dem Zähler 7a und dem Komparator 5a zur Beendigung der Ladungsänderungsphase und zur Steuerung der Zählbereitschaft (Freigabe) des Zählers 7a ist bereits in Zusammenhang mit dem vorher beschriebenen Ausführungsbeispiel der Erfindung erläutert worden.

Nach Ablauf der Ladungsänderungsphase befindet sich die Schaltungsanordnung 1a in ihrem Ausgangszustand und ist damit für die Erfassung eines nächsten Fehlerzeitintervalls  $T_1$  bzw.  $T'_1$  bereit. Die Zählbereitschaft (Freigabe) des Pulslängenzählers 47 wird bei Auftreten einer negativen Flanke  $A_-$  des Meßsignals TCP ausgeschaltet und die des Pulspausenzählers 45 wird eingeschaltet. Die Zählergebnisse der Zähler 7a, 45 und 47 werden jeweils nach dem Stillstand des entsprechenden Zählers von der Auswerteeinrichtung ausgelesen und zwischengespeichert. Die Auswerteeinrichtung berechnet aus den zwischengespeicherten Zählergebnissen einen digitalen Wert für das zu bestimmende Meßzeitintervall  $T_x$ .

In einer vorteilhaften Variante des vorstehend beschriebenen Ausführungsbeispiels überwacht die Zählerfreigabeschaltung (43) sowohl das Meßsignal TCP als auch das Referenzsignal Tref und schaltet die Zählbereitschaft des Pulslängenzählers 47 bzw. des Pulspausenzählers 45 erst dann ein bzw. aus, wenn die erste positive Flanke des Referenzsignals Tref auf die positive bzw. negative Flanke  $A_+$  des Meßsignals TCP folgt (Fig. 4a). Die ein erstes Zählergebnis des Pulslängenzählers auslösende negative Flanke des Referenztaktsignals Tref, die gleichzeitig die Ladephase  $T_1$  des Integrationskondensators 23a beendet, tritt dann frühestens nach Ablauf einer halben Taktperiode des Referenztaktsignals Tref nach Beginn des Meßzeitintervalls  $T_x$  auf. Der mit der Schaltungsanordnung 1a zu erfassende Zeitabstand  $T_1$  bzw.  $T'_1$  kann dann minimal eine halbe und maximal drei halbe Periodendauern Tclk des Referenzsignals Tref lang sein. Das Problem, daß eine erste vom Pulslängenzähler 47 zu zählende Flanke des Referenztaktsignals Tref zu dicht auf die positive Flanke  $A_+$  des Meßsignals TCP folgt, um vom Zähler 47 registriert zu werden, ist auf diese Weise beseitigt.

Nachstehend wird anhand von Beispielswerten für die Widerstände  $R_1$ ,  $R_2$ , für die Kapazität C des Integrationskondensators 23a, für die Periodendauer Tclk des Referenztaktsignals Tref und für die Komparatorschwelle  $U_{c2}$  ein typisches Zeitverhalten der Schaltungsanordnung 1a zu diskutiert.

Es sei:

5       $T_{clk} = 200 \text{ ns}$ ,

$R_1 = 820 \text{ Ohm}$ ,

$R_2 = 100 \text{ kOhm}$ ,

$C = 1 \text{ nF}$  und

$U_{c2} = 2/3 U_o$ , wobei  $U_o$  die Spannung der Gleichspannungsquelle bezeichnet.

Entsprechend der oben erwähnten Variante der Zeitintervall-Meßeinrichtung nach der Erfindung kann die Dauer eines Fehlerzeitintervalls  $T_1$  zwischen 100 ns und 300 ns liegen, wenn die Referenztaktperiodendauer  $T_{clk} = 200 \text{ ns}$  zugrunde gelegt wird. Mit den obigen Werten für  $R_1$ ,  $R_2$  und  $C$  ergibt sich für die Ladeschaltung 10 3a' die Zeitkonstante  $\tau_1 = 813 \text{ ns}$ . Während der Minimaldauer des Zeitabstandes  $T_1 = 100 \text{ ns}$  wird der Integrationskondensator 23a mit einer Ladezeitkonstante  $\tau_1 = 813 \text{ ns}$  auf die Spannung  $U_{c1} = 0,11 U_o$  geladen. Die Ladungsänderungsschaltung 3a'' benötigt dann eine Zeit von  $\Delta T_{max} = 98 \mu\text{s}$  zum Weiterladen des Integrationskondensators 23a bis zum Erreichen der Komparatorschwelle  $2/3 U_o$ . Während der Ladungsänderungsphase  $\Delta T_{max} = 98 \mu\text{s}$  summiert der Zähler 7a  $X_{max} = 487$  Zählereignisse auf. Während der Maximaldauer des Zeitabstandes  $T_1 = 300 \text{ ns}$  wird der Integrationskondensator 23a mit der Kapazität 1 nF auf  $U_{c1} = 0,3 U_o$  geladen. Die Ladungsänderungsphase dauert dann  $\Delta T_{min} = 73 \mu\text{s}$  lang. Dem entspricht ein Zählerstand von 364 Zählereignissen des Zählers 7a, bei einer Referenztaktperiodendauer von 200 ns.

Die Auswertungsgleichung zur Berechnung von  $T_x$  geht auf Gleichung (9) zurück.

Ersetzt man in Gleichung (9)  $T_1$  und  $T'_1$  durch entsprechende Ausdrücke der Gleichung (8) und ferner  $T_m$  durch  $T_{clk}$  ( $V+W$ ), so ergibt sich:

$$T_x = T_{clk} \cdot (V + W) + R_1 / (R_1 + R_2) \cdot T_{clk} \cdot (X' - X) \quad (10)$$

Darin bezeichnet  $T_x$  das zu bestimmende Meßzeitintervall zwischen aufeinanderfolgenden positiven Flanken des Meßsignals,

V das Zählergebnis des Pulslängenzählers nach Ablauf der Pulsdauer,

25 W das Zählergebnis des Pausenzählers nach Ablauf einer Pauspause,

X das Zählergebnis des Zählers 7a nach Ablauf des Fehlerzeitintervalls  $T_1$ ,

X' das Zählergebnis des Zählers 7a nach Ablauf des Fehlerzeitintervalls  $T'_1$  und  $T_{clk}$  die Periodendauer des periodischen Taktsignals Tref.

Gleichung (10) ist eine einfache Berechnungsvorschrift zur Bestimmung des Meßwertes  $T_x$  aus den Zählergebnissen des Pulslängenzählers 47, des Pausenzählers 45 und des Zählers 7a der Schaltungsanordnung 1a.

Da in die Gleichung (10) nur die Zählergebnisse der Zähler 7a, 45, 47, die bekannten Widerstandswerte  $R_1$  bzw.  $R_2$  und der bekannte Periodendauerwert  $T_{clk}$  des periodischen Taktsignals eingehen, erübrigt sich bei der Zeitintervallmessung aufeinanderfolgender Zeitintervalle mit der Schaltungseinrichtung 1a nach der Erfindung sogar eine Kalibriermessung.

Auch bei diesem Anwendungsbeispiel einer Schaltungsanordnung nach der Erfindung sind keine hohen Anforderungen an die Kurzzeitstabilität der Versorgungsspannung  $U_o$  oder der Komparatorschwelle  $U_{c2}$  zu stellen.

Die rechte Seite der Gleichung (10) umfaßt den Summanden  $T_{clk} \cdot (V+W)$ , der als ganzzahliges Vielfaches der Referenztaktperiode  $T_{clk}$  abgemessen wird, und den Summanden  $R_1 / (R_1 + R_2) \cdot T_{clk} \cdot (X' - X)$ , der die Erfassung der Fehlerzeitintervalle  $T_1$  bzw.  $T'_1$  beschreibt. Die Fehlerzeitintervalle können als Vielfaches einer "virtuellen Taktperiode"  $T_{clkvirtuell}$  dargestellt werden, mit:

$$T_{clkvirtuell} = R_1 / (R_1 + R_2) \cdot T_{clk} \quad (1)$$

Je nach den Widerstandswerten  $R_1$  und  $R_2$  erscheinen die Fehlerzeitintervalle  $T_1$ ,  $T'_1$  in wesentlich kleinere Zeitquanten als  $T_{clk}$  unterteilt, wie an nachstehendem Beispiel veranschaulicht wird:

Es sei:

50       $T_{clk} = 200 \text{ ns}$ ,

$R_1 = 1 \text{ kOhm}$ ,

$R_2 = 100 \text{ kOhm}$

Mit diesen Werten für die Taktperiodendauer  $T_{clk}$  und für die Widerstände  $R_1$ ,  $R_2$  werden die Fehlerzeitintervalle mit einem Zeitraster von 200 ns/101 abgetastet, d.h., die virtuelle Taktperiodendauer beträgt bei diesem Beispiel etwa 2 ns bei einer realen Taktperiodendauer von 200 ns.

Aus den vorstehenden Betrachtungen geht hervor, daß mit einer Schaltungsanordnung nach der Erfindung zur digitalen Erfassung von Zeitabständen zweier aufeinanderfolgender Zustände wenigstens eines Signals eine extrem hochauflösende digitale Zeitabstandmessung möglich ist, auch wenn das Referenztaktsignal Tref eine Periodendauer  $T_{clk}$  von lediglich 200 ns hat. Das Referenztaktsignal Tref kann beispielsweise von einer Systemtaktquelle stammen, die auch eine Mikroprozessoreinheit der Auswerteeinrichtung taktet.

Eine Zeitintervallmeßeinrichtung mit einer Schalteinrichtung nach der Erfindung erfordert nur eine einzige Versorgungsgleichspannungsquelle und ebenfalls nur eine einzige Referenztaktquelle.

Die zur Erläuterung des Arbeitsprinzips der Zeitintervallmeßeinrichtung 2 vorausgesetzte Form des Meßsignals ist nicht zwingend. Auch bei diesem Ausführungsbeispiel der Erfindung können andere vorbestimmte Signalzustände als die beschriebenen als Begrenzungsmarken von Zeitabständen gewählt werden.

Nachstehend wird bezugnehmend auf die Fig. 5 ein weiteres Ausführungsbeispiel der Erfindung beschrieben. Dieses weitere Ausführungsbeispiel ist eine Schaltungsanordnung zur digitalen Erfassung der Amplitude eines Signals und umfaßt einen analogen Schaltungsteil 3b, einen Komparator 5b, einen Zähler 7b, eine Steuereinrichtung 9b, ferner eine Zeitsteuerschaltung 57 und eine Abtast-Halteschaltung 59. Das wesentliche Prinzip des analogen Schaltungsteils 3b, des Komparators 5b, des Zählers 7b und der Steuereinrichtung 9b geht im wesentlichen aus der Beschreibung der vorhergehenden Ausführungsbeispiele hervor; Abweichungen dazu sind nachstehend beschrieben. Die bereits in den vorhergehenden Ausführungsbeispielen beschriebenen Komponenten, die mit gleicher oder ähnlicher Funktion auch in der Schaltungsanordnung 1b zur digitalen Erfassung der Amplitude eines Signals verwendet werden, sind mit einem b hinter der entsprechenden Bezugsziffer gekennzeichnet.

Der analoge Schaltungsteil 3b ist an eine die Ladungsquelle für den Integrationskondensator 23b darstellende Abtast-Halteschaltung 59 angeschlossen. Die Abtast-Halteschaltung 59 tastet das unbekannte Signal  $U_m$ , z.B. ein Spannungssignal, ab und gibt eine einem jeweils aktuellen Abtast- bzw. Haltewert proportionale Spannung  $U_x$  an die Analogschaltung 3b aus. Die Zeitsteuerschaltung 57 wird mit dem Referenztaktsignal Tref getaktet und gibt ein Zeitsteuersignal mit in einem vorbestimmten Zeitabstand  $T_k$  aufeinanderfolgenden Signalflanken an die Steuereinrichtung 9b aus.

Bei Beginn des vorbestimmten Zeitabstandes  $T_k$ , zum Beispiel bei Auftreten einer positiven Flanke des Zeitsteuersignals, schaltet die Steuereinrichtung 9b den ersten Schalter 15b ein und den zweiten Schalter 27b aus und startet damit die Ladephase des Integrationskondensators 23b. Der Integrationskondensator 23b wird während der Ladephase über den ersten und zweiten Widerstand 13b, 17b auf eine Spannung  $U_{c1}$  geladen, die den an der Analogschaltung anliegenden Abtast-Haltewert der Abtast-Halteschaltung repräsentiert. Bei Beendigung des vorbestimmten Zeitabstandes  $T_k$ , z.B. bei Auftreten einer negativen Flanke des Zeitsteuersignals, schaltet die Steuereinrichtung den ersten Schalter 15b aus und die Zählbereitschaft des Zählers 7b zur Zählung periodischer Referenztaktpulse ein, womit die Ladungsänderungsphase zur Änderung der Spannung am Integrationskondensator 23b bis zum Erreichen eines vorbestimmten, durch den Komparator 5b überwachten Schwellenwertes  $U_{c2}$  beginnt. Der Komparator 5b ändert bei Erreichen der Spannung  $U_{c2}$  am Integrationskondensator 23b sein Ausgangssignal, woraufhin die Steuereinrichtung 9b den zweiten Schalter 27b einschaltet und die Zählbereitschaft des Zählers 7b ausschaltet. Über ein Bereitschaftssignal teilt die Steuereinrichtung 9b der Abtast-Halteschaltung 59 die Bereitschaft zu einem neuen Meßzyklus mit, so daß die Abtast-Halteschaltung 59 einen neuen Abtastwert  $U_x$  für einen nächsten Meßzyklus ausgibt.

Nach dem Meßzyklus liest eine Auswerteeinrichtung (nicht gezeigt) das Zählergebnis des Zählers 7b aus, um damit einen digitalen Meßwert für die zu erfassende Signalspannung  $U_x$  bzw.  $U_m$  zu berechnen.

Eine Ausgangsgleichung für die Berechnung eines Wertes  $U_x$  läßt sich aus Gleichung (5) ableiten, indem die Gleichung (5) nach  $U_o$  aufgelöst und  $U_o$  durch  $U_x$  und  $T_1$  durch  $T_k$  ersetzt wird.

Durch das vorstehend beschriebene Ausführungsbeispiel der Erfindung wird ein neuer Weg der Analog-Digital-Wandlung aufgezeigt. Auch dieses Ausführungsbeispiel ist wenig störanfällig und läßt sich mit geringem Schaltungsaufwand preiswert realisieren.

Die Erfindung ist nicht auf die beschriebenen Ausführungsbeispiele beschränkt sondern umfaßt auch Abwandlungen mit geänderten oder zusätzlichen technischen Details, wenn der Erfindungsgedanke dadurch nicht verlassen wird. So kann beispielsweise die Steuereinrichtung mit Laufzeitausgleichschaltungen versehen sein, die unterschiedliche Signallaufzeiten und Schaltzeiten bzw. Vorbereitungszeiten von Bauelementen berücksichtigen. Darüberhinaus kann die Steuereinrichtung, insbesondere Kontrollschaltungen umfassen, die dafür sorgen, daß ein neuer Meßzyklus erst dann beginnen kann, wenn der vorherige Meßzyklus abgeschlossen ist. Die Dimensionierung des ersten und zweiten Widerstandes, des Integrationskondensators, und der Periodendauer  $T_{clk}$  des Referenztaktsignals hängt im wesentlichen von der gewünschten digitalen Auflösung einer zu erfassenden analogen Information und von der tolerierten Maximaldauer eines Meßzyklus ab.

Die Analogschaltung 3, 3a, 3b zur Realisierung der Ladeschaltung und der Ladungsänderungsschaltung kann durch äquivalente Schaltungen ersetzt werden, zum Beispiel durch eine von einer Konstantstromquelle gespeiste Parallelschaltung aus einem Integrationskondensator, einem ersten und einem zweiten Widerstand mit einem ersten Schalter in Reihe zum ersten Widerstand und einen zweiten Schalter in Reihe zum zweiten Widerstand.

**Patentansprüche**

1. Schaltungsanordnung zur digitalen Erfassung einer analogen Information in der Form des Zeitabstandes zweier aufeinanderfolgender Zustände wenigstens eines Signals oder der Amplitude des Signals, mit einem Integrationskondensator (23; 23a; 23b), der über eine Ladeschaltung (3'; 3a'; 3b') auf eine die analoge Information repräsentierende Spannung ladbar ist, mit einer Ladungsänderungsschaltung (3"; 3a"; 3b"), die die Spannung des Integrationskondensators (23; 23a; 23b) mit einer Änderungsrate kleiner als die der Ladeschaltung (3'; 3a'; 3b') ändert, mit einem die Spannung an dem Integrationskondensator (23; 23a; 23b) mit einem vorbestimmten Schwellenwert vergleichenden komparator (5; 5a; 5b) und mit einem Zähler (7; 7a; 7b), welcher während der Änderung der Spannung des Integrationskondensators (23; 23a; 23b) mittels der Ladungsänderungsschaltung (3"; 3a"; 3b") bis zum Erreichen des vorbestimmten Schwellenwertes periodische Taktpulse zählt, dadurch gekennzeichnet, daß die Ladeschaltung (3'; 3a'; 3b') und die Ladungsänderungsschaltung (3"; 3a"; 3b") die Spannung des Integrationskondensators (23; 23a; 23b) in gleicher Richtung ändern und an eine gemeinsame Ladungsquelle angeschlossen sind.

2. Schaltungsanordnung nach Anspruch 1, dadurch gekennzeichnet, daß zur digitalen Erfassung des Zeitabstandes zweier aufeinanderfolgender Zustände wenigstens eines Signals ein Signalzustandsdetektor (8, 8a) einer Steuereinrichtung (9, 9a), insbesondere ein Flankendetektor die aufeinanderfolgenden Zustände detektiert, und daß die Steuereinrichtung bei Auftreten des zeitlich ersten Zustandes die Ladeschaltung (3', 3a') wirksam schaltet und bei Auftreten des zweiten Zustandes die Ladungsänderungsschaltung (3"; 3a") wirksam schaltet.

3. Schaltungsanordnung nach Anspruch 2, dadurch gekennzeichnet, daß der zeitlich erste und der zweite Signalzustand jeweils wahlweise dem Überschreiten oder dem Unterschreiten vorbestimmter Amplitudenpegel eines Signals entspricht.

4. Schaltungsanordnung nach Anspruch 2 oder 3, dadurch gekennzeichnet, daß der zeitlich erste Signalzustand wahlweise dem Überschreiten oder dem Unterschreiten vorbestimmter Amplitudenpegel eines ersten Signals entspricht und daß der zweite Zustand wahlweise dem Überschreiten oder dem Unterschreiten vorbestimmter Amplitudenpegel eines zweiten Signals entspricht.

5. Schaltungsanordnung nach Anspruch 2, 3 oder 4, dadurch gekennzeichnet, daß die Ladungsquelle eine Gleichspannungsquelle, insbesondere eine Versorgungsgleichspannungsquelle der Schaltungsanordnung ist.

6. Schaltungsanordnung nach Anspruch 1, dadurch gekennzeichnet, daß zur Messung der Amplitude eines Signals eine ein Integrationszeitintervall vorbestimmter Länge erzeugende Zeitsteuerschaltung (57) mit einer Steuereinrichtung (9b) zusammenwirkt, welche bei Beginn des Integrationszeitintervalls die Ladeschaltung (3b') wirksam schaltet und bei Ende des Integrationszeitintervalls die Ladungsänderungsschaltung (3b") wirksam schaltet, und daß die Ladungsquelle die quelle des analogen Signals oder eine Schaltung ist, die eine der Amplitude des analogen Signals proportionale Spannung abgibt.

7. Schaltungsanordnung nach Anspruch 6, dadurch gekennzeichnet, daß die Ladungsquelle eine das Signal abtastende und Abtastwerte der Signalamplitude analog zwischenspeichernde Abtast-Halte-Schaltung (59) ist, welche während des Integrationszeitintervalls eine einem Abtastwert der Signalamplitude proportionale Ausgangsspannung erzeugt.

8. Schaltungsanordnung nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, daß der Integrationskondensator (23; 23a; 23b) über eine in Serie zum Integrationskondensator (23; 23a; 23b) geschaltete Widerstandsschaltung (11; 11a; 11b) mit steuerbarem Gesamtwiderstandswert an die Ladungsquelle angeschlossen ist.

9. Schaltungsanordnung nach Anspruch 8, dadurch gekennzeichnet, daß die Widerstandsschaltung (11; 11a; 11b) eine Parallelschaltung aus einem ersten Widerstand (13; 13a; 13b) und einem zweiten Widerstand (17; 17a; 17b) umfaßt und daß der Strom durch den ersten Widerstand (13; 13a; 13b) mit einem ersten Schalter (15; 15a; 15b) der Steuereinrichtung (9; 9a; 9b) ein- und ausschaltbar ist.

10. Schaltungsanordnung nach Anspruch 9, dadurch gekennzeichnet, daß der Wert ( $R_2$ ) des zweiten Widerstandes (17; 17a) den Wert ( $R_1$ ) des ersten Widerstandes (13; 13a) um ein Vielfaches des wertes des ersten Widerstandes überschreitet.

11. Schaltungsanordnung nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, daß zum Entladen des Integrationskondensators (23; 23a; 23b) die Anschlüsse des Integrationskondensators (23; 23a; 23b) über einen zweiten Schalter (27; 27a; 27b) der Steuereinrichtung (9; 9a; 9b) kurzschließbar sind.

12. Schaltungsanordnung nach einem der Ansprüche 1, 2, 4, 5, 8, 9, und 11, dadurch gekennzeichnet, daß die Schaltungsanordnung (1a) Teil einer Zeitintervall-Meßeinrichtung (2) zur digitalen Erfassung von Zeitintervallen (Tx), deren Dauer die Dauer der periodischen Taktpulse um ein Mehrfaches überschreitet, ist, daß eine

5 Zähleinrichtung (41) während eines Zeitabschnittes (Tm) der Dauer eines ganzzahligen Vielfachen der Takt-periodendauer (Tclk) die periodischen Taktpulse zählt, und daß die Schaltungsanordnung (1a) die Zeitabstände (T<sub>1</sub>, T'<sub>1</sub>) zwischen Beginn eines Meßzeitintervalls (Tx) und dem Beginn des taktsynchronen Zeitabschnittes (Tm) sowie zwischen dem Ende des Meßzeitintervalls (Tx) und dem Ende des taktsynchronen Zeitabschnittes (Tm) erfaßt und daß eine Auswerteeinrichtung die Zählergebnisse der Zähleinrichtung (41) und des Zählers (7a) zur Berechnung eines digitalen Meßwertes für das Zeitintervall (Tx) weiterverarbeitet.

10 13. Schaltungsanordnung nach Anspruch 12, dadurch gekennzeichnet, daß die Zähleinrichtung (41) einen Pulslängenzähler (47) und einen Pulspausenzähler (45) umfaßt, wobei der Pulslängenzähler (47) und der Pulspausenzähler (45) bei der Zählung der in den taktsynchronen Zeitabschnitt (Tm) fallenden periodischen Takt-pulse einander ablösen.

## Claims

15 1. Circuit arrangement for the digital monitoring of analog information in the form of the interval between two successive conditions of at least one signal or the amplitude of the signal, with an integration capacitor (23; 23a; 23b), which can be charged by a charging circuit (3'; 3a'; 3b') to a voltage representing the analog information, with a charge variation circuit (3"; 3a"; 3b"), which varies the voltage of the integration capacitor (23; 23a; 23b) with a variation rate less than that of the charging circuit (3'; 3a'; 3b'), 20 with a comparator (5; 5a; 5b) comparing the voltage at the integration capacitor (23; 23a; 23b) with a predetermined threshold value and with a counter (7; 7a; 7b), which counts periodic clock pulses during the variation of the voltage of the integration capacitor (23; 23a; 23b) by means of the charge variation circuit (3"; 3a"; 3b") until the predetermined threshold value is reached,

25 characterised in that the charging circuit (3'; 3a'; 3b') and the charge variation circuit (3"; 3a"; 3b") vary the voltage of the integration capacitor (23; 23a; 23b) in the same direction and are connected to a common source of charge.

30 2. Circuit arrangement according to Claim 1, characterised in that for the digital monitoring of the interval between two successive conditions of at least one signal, a signal condition detector (8, 8a) of a control device (9, 9a), in particular an edge detector detects the successive conditions and that upon the occurrence of the first condition with regard to time, the control device effectively switches the charging circuit (3', 3a') and upon the occurrence of the second condition effectively switches the charge variation circuit (3", 3a").

35 3. Circuit arrangement according to Claim 2, characterised in that the first and second signal condition with regard to time corresponds respectively optionally to exceeding or falling below the predetermined amplitude level of a signal.

40 4. Circuit arrangement according to Claim 2 or 3, characterised in that the first signal condition with regard to time corresponds optionally to exceeding or falling below the predetermined amplitude level of a first signal and that the second condition corresponds optionally to exceeding or falling below the predetermined amplitude level of a second signal.

45 5. Circuit arrangement according to Claim 2, 3 or 4, characterised in that the source of charge is a d.c. source, in particular a d.c. supply source of the circuit arrangement.

6. Circuit arrangement according to Claim 1, characterised in that for measuring the amplitude of a signal, a time control circuit (57) producing an integration time interval of predetermined length cooperates with a control device (9b), which at the beginning of the integration time interval effectively switches the charging circuit (3b') and at the end of the integration time interval effectively switches the charge variation circuit (3b") and that the source of charge is the source of the analog signal or a circuit, which emits a voltage proportional to the amplitude of the analog signal.

50 7. Circuit arrangement according to Claim 6, characterised in that the source of charge is a scanning holding circuit (59) scanning the signal and providing temporary storage in an analog manner of the scanning values of the signal amplitude, which circuit (59), during the integration time interval, produces an output voltage proportional to a scanning value of the signal amplitude.

8. Circuit arrangement according to one of the preceding Claims, characterised in that the integration capacitor (23; 23a; 23b) is connected to the source of charge by way of a resistance circuit (11; 11a; 11b) connected in series with the integration capacitor (23; 23a; 23b) and having a controllable total resistance value.

55 9. Circuit arrangement according to Claim 8, characterised in that the resistance circuit (11; 11a; 11b) comprises a parallel circuit consisting of a first resistor (13; 13a; 13b) and a second resistor (17; 17a; 17b) and that the current through the first resistor (13; 13a; 13b) can be switched on and off by a first switch (15; 15a; 15b) of the control device (9; 9a; 9b).

10. Circuit arrangement according to Claim 9, characterised in that the value of the second resistor (17; 17a) exceeds the value of the first resistor (13; 13a) by a multiple of the value of the first resistor.

11. Circuit arrangement according to one of the preceding Claims, characterised in that for discharging the integration capacitor (23; 23a; 23b), the connections of the integration capacitor (23; 23a; 23b) can be short-circuited by way of a second switch (27; 27a; 27b) of the control device (9; 9a; 9b).

12. Circuit arrangement according to one of Claims 1, 2, 4, 5, 8, 9 and 11, characterised in that the circuit arrangement (1a) is part of a time interval measuring device (2) for the digital monitoring of time intervals (Tx), whereof the duration exceeds the duration of the periodic timing pulses by a multiple, that during a period (Tm) of the duration of an integral multiple of the clock period duration (Tclk), a counting device (41) counts the periodic clock pulses, and that the circuit arrangement (1a) monitors the periods (T<sub>1</sub>, T'<sub>1</sub>) between the beginning of a measuring time interval (Tx) and the beginning of the timing synchronous period (Tm) as well as between the end of the measuring time interval (Tx) and the end of the timing synchronous period (Tm) and that an evaluation device processes the counting results of the counting device (41) and of the counter (7a) for calculating a digital measured value for the time interval (Tx).

13. Circuit arrangement according to Claim 12, characterised in that the counting device (41) comprises a pulse length counter (47) and a pulse interval counter (45), in which case the pulse length counter (47) and the pulse interval counter (45) alternate in the counting of the periodic clock pulses occurring in the timing synchronous period (Tm).

20

## Revendications

1. Circuit pour l'enregistrement numérique d'une information analogique sous la forme de l'intervalle de temps séparant deux états successifs d'au moins un signal ou de l'amplitude du signal,

comportant un condensateur d'intégration (23; 23a; 23b) qui peut être chargé, par l'intermédiaire d'un circuit de charge (3'; 3a'; 3b'), sur une tension représentant l'information analogique, avec un circuit de variation de charge (3"; 3a"; 3b")

qui fait varier la tension du condensateur d'intégration (23; 23a; 23b) avec un taux de variation inférieur à celui du circuit de charge (3'; 3a'; 3b'),

comportant un comparateur (5; 5a; 5b) comparant la tension du condensateur d'intégration (23; 23a; 23b) à une valeur de seuil prédéterminée et comportant un compteur (7; 7a; 7b) qui, pendant la variation de la tension du condensateur d'intégration (23; 23a; 23b), compte des impulsions périodiques de rythme jusqu'à ce que la valeur de seuil prédéterminée soit atteinte,

caractérisé en ce que le circuit de charge (3'; 3a'; 3b') et le circuit de variation de charge (3"; 3a"; 3b") font varier dans le même sens la tension du condensateur d'intégration (23; 23a; 23b) et sont connectés à une source de charge commune.

2. Circuit selon la revendication 1, caractérisé en ce que pour l'enregistrement numérique de l'intervalle de temps séparant deux états successifs d'au moins un signal, un détecteur d'état de signal (8, 8a) d'un dispositif de commande (9, 9a), en particulier un détecteur de fronts, détecte les états successifs et en ce que le dispositif de commande rend opérant le circuit de charge (3', 3a') à l'apparition du premier état dans le temps et rend opérant le circuit de variation de charge (3", 3a"), à l'apparition du deuxième état.

3. Circuit selon la revendication 2, caractérisé en ce que le premier état de signal dans le temps et le deuxième correspondent chacun, au choix, au dépassement ou à des valeurs inférieures à des niveaux d'amplitude prédéterminés d'un signal.

4. Circuit selon la revendication 2 ou 3, caractérisé en ce que le premier état de signal dans le temps correspond, au choix, au dépassement ou à des valeurs inférieures à des niveaux d'amplitude prédéterminés d'un premier signal et en ce que le deuxième état correspond, au choix, au dépassement ou à des valeurs inférieures à des niveaux d'amplitude prédéterminés d'un deuxième signal.

5. Circuit selon la revendication 2, 3 ou 4, caractérisé en ce que la source de charge est une source de tension continue, en particulier une source de tension continue d'alimentation du circuit.

6. Circuit selon la revendication 1, caractérisé en ce que pour mesurer l'amplitude d'un signal un circuit de commande de temps (57), produisant un intervalle de temps d'intégration de longueur prédéterminée, coopère avec un dispositif de commande (9b) qui, au début de l'intervalle de temps d'intégration, rend opérant le circuit de charge (3b") et, à la fin de l'intervalle de temps d'intégration, rend opérant le circuit de variation de charge (3b") et en ce que la source de charge est la source du signal analogique ou un circuit qui délivre une tension proportionnelle à l'amplitude du signal analogique.

7. Circuit selon la revendication 6, caractérisé en ce que la source de charge est un circuit de détection et de maintien (59) détectant le signal et stockant de manière intermédiaire et analogique des valeurs détectées

de l'amplitude du signal, lequel circuit produit, pendant l'intervalle de temps d'intégration, une tension de sortie proportionnelle à une valeur détectée de l'amplitude du signal.

8. Circuit selon l'une des revendications précédentes, caractérisé en ce que le condensateur d'intégration (23; 23a; 23b) est connecté à la source de charge, par un circuit résistant (11; 11a; 11b) avec valeur de résistance globale commandable, monté en série avec le condensateur d'intégration (23; 23a; 23b).

5 9. Circuit selon la revendication 8, caractérisé en ce que le circuit résistant (11; 11a; 11b) comporte un circuit parallèle constitué d'une première résistance (13; 13a; 13b) et d'une deuxième résistance (17; 17a; 17b) et en ce que le courant, passant à travers la première résistance (13; 13a; 13b), peut être alimenté et coupé par un premier interrupteur (15; 15a; 15b) du dispositif de commande (9; 9a; 9b).

10 10. Circuit selon la revendication 9, caractérisé en ce que la valeur ( $R_2$ ) de la deuxième résistance (17; 17a) dépasse la valeur ( $R_1$ ) de la première résistance (13; 13a), d'un multiple de la valeur de la première résistance.

15 11. Circuit selon l'une des revendications précédentes, caractérisé en ce que, pour décharger le condensateur d'intégration (23; 23a; 23b), les branchements du condensateur d'intégration (23; 23a; 23b) peuvent être court-circuités par un deuxième interrupteur (27; 27a; 27b) du dispositif de commande (9; 9a; 9b).

12. Circuit selon l'une des revendications 1, 2, 3, 4, 5, 8, 9 et 11, caractérisé en ce que le circuit (1a) fait partie d'un dispositif de mesure d'intervalle de temps (2) pour l'enregistrement numérique d'intervalles de temps (Tx) dont la durée dépasse, d'un multiple, celle des impulsions périodiques de rythme, en ce qu'un dispositif de comptage (41) compte les impulsions périodiques de rythme pendant un intervalle de temps (Tm) d'une durée correspondant à un multiple entier de la durée de la période de rythme (Tclk) et en ce que le circuit (1a) enregistre les intervalles de temps (T<sub>1</sub>, T'<sub>1</sub>) entre le début d'un intervalle de temps de mesure (Tx) et le début de l'intervalle de temps (Tm) de rythme synchrone ainsi qu'entre la fin de l'intervalle de temps de mesure (Tx) et la fin de l'intervalle de temps (Tm) de rythme synchrone et en ce qu'un dispositif d'exploitation traite les résultats de comptage du dispositif de comptage (41) et du compteur (7a) afin de calculer une valeur de mesure numérique pour l'intervalle de temps (Tx).

20 13. Circuit selon la revendication 12, caractérisé en ce que le dispositif de comptage (41) comprend un compteur de longueur d'impulsions (47) et un compteur de pause d'impulsions (45), le compteur de longueur d'impulsions (47) et le compteur de pause d'impulsions (45) se déclenchant l'un l'autre lors du comptage des impulsions périodiques de rythme, tombant pendant la période de temps (Tm) de rythme synchrone.

25 30

35

40

45

50

55

FIG. 1

FIG. 2

FIG.3

FIG.4

FIG.4a

FIG.5