(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-111479

(P2004-111479A)

(43) 公開日 平成16年4月8日(2004.4.8)

(51) Int.Cl.<sup>7</sup>

H01L 21/336

H01L 21/28

H01L 21/8234

H01L 27/088

H01L 29/423

F 1

H01L 29/78

H01L 21/28

H01L 21/28

H01L 29/78

H01L 29/58

301P

301D

301S

301G

G

テーマコード(参考)

4M104

5F048

5F140

審査請求 未請求 請求項の数 14 O L (全 12 頁) 最終頁に続く

(21) 出願番号

特願2002-268970 (P2002-268970)

(22) 出願日

平成14年9月13日 (2002. 9. 13)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100084618

弁理士 村松 貞男

(74) 代理人 100068814

弁理士 坪井 淳

(74) 代理人 100092196

弁理士 橋本 良郎

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【要約】

【課題】後熱工程によるシート抵抗の上昇を抑制でき、トランジスタの寄生抵抗の低減によるスイッチング速度の高速化が図れる半導体装置を提供する。

【解決手段】半導体装置は、Ge / (Si + Ge) 組成比が  $x$  ( $0 < x < 0.2$ 、より好ましくは  $0.04 < x < 0.16$ ) の poly-Si<sub>1-x</sub>Ge<sub>x</sub> 層を含むゲート電極 5 と、このゲート電極上に形成され、NiSi<sub>1-y</sub>Ge<sub>y</sub> からなる第1の金属シリサイド膜 10b と、ソース/ドレイン領域 SO, DR 上にそれぞれ形成され、NiSi からなる第2, 第3の金属シリサイド膜 10a, 10a とを有するMOSFETを備えることを特徴としている。後熱工程によるシート抵抗の上昇を抑制し、トランジスタの寄生抵抗の低減によるスイッチング速度の高速化が図れる。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

半導体基板と、

前記半導体基板の主表面領域中に形成されるソース／ドレイン領域と、

前記ソース／ドレイン領域間のチャネル領域上に形成されるゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、 $Ge / (Si + Ge)$ 組成比が $x (0 < x < 0.2)$ の $polycrystalline-Si_{1-x}Ge_x$ 層を含むゲート電極と、

前記ゲート電極上に形成され、 $NiSi_{1-y}Ge_y$ からなる第1の金属シリサイド膜と、

前記ソース／ドレイン領域上にそれぞれ形成され、 $NiSi$ からなる第2，第3の金属シリサイド膜と

を有するMOSFETを備えることを特徴とする半導体装置。

## 【請求項 2】

$Ge / (Si + Ge)$ 組成比は、より好ましくは $0.04 \times 0.16$ の範囲内であることを特徴とする請求項1に記載の半導体装置。

## 【請求項 3】

前記MOSFET上に形成される層間絶縁膜と、前記層間絶縁膜の前記ゲート電極上に形成された第1のコンタクトホール内に形成される第1の金属プラグと、前記第1の金属プラグと前記第1の金属シリサイド膜との間に介在される第1のバリアメタル層と、前記層間絶縁膜の前記ソース／ドレイン領域上にそれぞれ形成された第2，第3のコンタクトホール内に形成される第2，第3の金属プラグと、前記第2，第3の金属プラグと前記第2の金属シリサイド膜との間に介在される第2，第3のバリアメタル層とを更に具備することを特徴とする請求項1または2に記載の半導体装置。

## 【請求項 4】

前記第1乃至第3の金属プラグはタンクステンであり、前記第1乃至第3のバリアメタル層はTiNを含むことを特徴とする請求項3に記載の半導体装置。

## 【請求項 5】

前記ゲート電極における $polycrystalline-Si_{1-x}Ge_x$ 層の膜厚は、前記第1の金属シリサイド膜の膜厚の少なくとも2倍であることを特徴とする請求項1乃至4いずれか1つの項に記載の半導体装置。

## 【請求項 6】

前記半導体基板中に形成されるウェル領域を更に具備し、前記ソース／ドレイン領域は前記ウェル領域中に形成され、且つ前記ソース／ドレイン領域は、ソース／ドレイン・エクステンションを有する構造であり、高濃度の第1，第2の不純物拡散領域と、これら第1，第2の不純物拡散領域におけるチャンネル領域の近傍に設けられる低濃度の第3，第4の不純物拡散領域とを有することを特徴とする請求項1乃至5いずれか1つの項に記載の半導体装置。

## 【請求項 7】

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に $Ge / (Si + Ge)$ 組成比が $x (0 < x < 0.2)$ の $polycrystalline-Si_{1-x}Ge_x$ 層を含むゲート電極を形成する工程と、

前記半導体基板の主表面領域中に不純物を導入してソース／ドレイン領域を形成する工程と、

前記ゲート電極上及び前記ソース／ドレイン領域上にNi膜を形成する工程と、熱処理を行って、前記ゲート電極上のNi膜を $NiSi_{1-y}Ge_y$ 膜に置換し、且つ前記ソース／ドレイン領域上のNi膜をNiSi膜に置換する工程とを具備することを特徴とする半導体装置の製造方法。

## 【請求項 8】

$Ge / (Si + Ge)$ 組成比は、より好ましくは $0.04 \times 0.16$ の範囲内であることを特徴とする請求項7に記載の半導体装置の製造方法。

10

20

30

40

50

**【請求項 9】**

前記  $NiSi_{1-y}Ge_y$  膜上、及び前記  $NiSi$  膜上に層間絶縁膜を形成する工程と、前記層間絶縁膜における前記ゲート電極上及び前記ソース／ドレイン領域上に対応する位置にそれぞれ第1乃至第3のコンタクトホールを形成する工程と、前記第1乃至第3のコンタクトホール内に第1乃至第3のバリアメタル層を形成する工程と、前記第1乃至第3のコンタクトホール内の前記第1乃至第3のバリアメタル層上に第1乃至第3の金属プラグを埋め込み形成する工程とを更に具備することを特徴とする請求項7または8に記載の半導体装置の製造方法。

**【請求項 10】**

前記ゲート絶縁膜を形成する工程の前に、前記半導体基板の主表面に素子分離構造を形成する工程と、前記素子分離構造で区画された能動素子領域にウェル領域を形成する工程とを更に具備することを特徴とする請求項7乃至9いずれか1つの項に記載の半導体装置の製造方法。 10

**【請求項 11】**

前記ソース／ドレイン領域を形成する工程は、前記ゲート電極をマスクにして前記半導体基板の主表面領域中に不純物をイオン注入して低濃度の第1，第2の不純物拡散領域を形成する工程と、前記ゲート電極の側壁部に側壁絶縁膜を形成する工程と、前記ゲート電極及び前記側壁絶縁膜をマスクにして前記半導体基板の主表面領域中に不純物をイオン注入して高濃度の第3，第4の不純物拡散領域を形成する工程とを含むことを特徴とする請求項7乃至10いずれか1つの項に記載の半導体装置の製造方法。 20

**【請求項 12】**

前記層間絶縁膜を形成する工程は、前記半導体基板の主表面上及び前記ゲート電極の上面及び側壁部にシリコン窒化膜を堆積形成する工程と、前記シリコン窒化膜上にシリコン酸化膜を堆積形成する工程とを含むことを特徴とする請求項9乃至11いずれか1つの項に記載の半導体装置の製造方法。

**【請求項 13】**

前記第1乃至第3のバリアメタル層を形成する工程は、前記層間絶縁膜上及び前記第1乃至第3のコンタクトホール内に  $Ti$  膜を形成する工程と、前記  $Ti$  膜を窒化することにより少なくとも一部を  $TiN$  膜にする工程とを含むことを特徴とする請求項9乃至12いずれか1つの項に記載の半導体装置の製造方法。 30

**【請求項 14】**

第1乃至第3の金属プラグを埋め込み形成する工程は、前記層間絶縁膜上及び前記第1乃至第3のコンタクトホール内に、CVD法によりタングステンを形成する工程と、CMPを行って平坦化し、前記タングステンを前記第1乃至第3のコンタクトホール内に残存させることにより、第1乃至第3の金属プラグを形成する工程とを含むことを特徴とする請求項9乃至13いずれか1つの項に記載の半導体装置の製造方法。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、半導体装置及びその製造方法に関し、特にサリサイドプロセスを用いて形成したトランジスタ(MOSFET)とその製造方法に係り、ゲート電極及びソース／ドレイン領域とこれらの引き出し電極とのコンタクト部に適用されるものである。 40

**【0002】****【従来の技術】**

近年、MOSFETにおけるゲート電極の材料として、空乏化を抑制するために  $p_{0.1}y-SiGe$  を導入する検討が進められている。しかし、現在、コンタクト材料として主に用いられている  $CoSi_2$  は、第1の低温RTA(400程度)では  $Co(Si_{1-y}Ge_y)$  を形成するが、第2の高温RTA(700程度)では  $Ge$  を吐き出して  $Ge-rich$  なアイランドの  $SiGe$  層と  $CoSi_2$  を形成する。その結果、シート抵抗の著しい上昇が見られる(例えば、非特許文献1参照)。このため、ゲート電極に  $p_{0.1}y-$  50

SiGeを用いる場合には、CoSi<sub>2</sub>との界面にpoly-Siキャップ層を導入する必要があることが知られている。

【0003】

また、ゲート長が50nm世代以降のMOSFETにおいては、サリサイドプロセスを適用するためのコンタクト材料としてNiSiが検討されている。このNiSiの欠点としては、これまで用いられてきたTiSi<sub>2</sub>やCoSi<sub>2</sub>に比べて耐熱性が低いことがあげられる。しかしながら、poly-SiGe上にNiSiをコンタクト材として用いる場合、上述のCoSi<sub>2</sub>で見られたようなpoly-SiGeとの激しい不整合は生じないが、より耐熱性を向上させるために「引き出し電極28の下層側にSi<sub>x</sub>(Ge<sub>y</sub>C<sub>1-y</sub>)<sub>1-x</sub>化合物層28aを用いる」という提案がされている（例えば、特許文献1参照）。 10

【0004】

この特許文献1の要旨は、ゲート電極またはソース/ドレイン拡散層との界面不整合を小さくすることによって、後熱工程後のショットキー障壁変化と、それに伴うコンタクト抵抗の変化を抑制する、というものである。

【0005】

ところで、上記耐熱性とは別に、高温の熱工程後にNiシリサイドのシート抵抗が増加してしまうという問題が知られている。この原因としては、高比抵抗のNiSi<sub>2</sub>の形成（相転移）や凝集が考えられている。 20

【0006】

その対策として、Ni/Si及びNi/SiGe界面にCo中間層を導入する報告がされている（例えば、非特許文献2参照）。しかしながら、製造プロセスが増加する等の集積化するまでの課題が増えることになる。

【0007】

【特許文献1】

特開平11-214680号公報（段落番号[0019]、図1）

【0008】

【非特許文献1】

Z. Wang, D. B. Aldrich, Y. L. Chen, D. E. Sayers and R. J. Nemanich, Thin Solid Films, Vol. 270 (1995) 555-560. 30

【0009】

【非特許文献2】

J. S. Maa, D. J. Tweett, Y. Ono, L. Stecker and S. T. Hsu, Mat. Res. Soc. Symp. Proc. Vol. 670, K6. 9. 1 (2001).

【0010】

【発明が解決しようとする課題】

上記のように従来の半導体装置及びその製造方法は、サリサイドプロセスを適用する際に、コンタクト材料としてNiSiを用いた場合、高温の後熱工程によりソース/ドレイン領域やゲート電極との界面抵抗の上昇、シート抵抗の上昇といった耐熱性の問題があった。

【0011】

本発明は上記のような事情に鑑みてなされたもので、その目的とするところは、コンタクト材料としてNiSiを用いる場合に、高温の後熱工程によりソース/ドレイン領域やゲート電極との界面抵抗の上昇やシート抵抗の上昇などの耐熱性の問題を回避してトランジスタのスイッチング速度を高速化できる半導体装置を提供することにある。

【0012】

また、本発明の他の目的は、製造歩留まりと信頼性を向上できる半導体装置の製造方法を提供することにある。

## 【0013】

## 【課題を解決するための手段】

本発明の半導体装置は、半導体基板と、前記半導体基板の主表面領域中に形成されるソース／ドレイン領域と、前記ソース／ドレイン領域間のチャネル領域上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成され、 $Ge / (Si + Ge)$ 組成比が $x (0 < x < 0.2)$ の $poly-Si_{1-x}Ge_x$ 層を含むゲート電極と、前記ゲート電極上に形成され、 $NiSi_{1-y}Ge_y$ からなる第1の金属シリサイド膜と、前記ソース／ドレイン領域上にそれぞれ形成され、 $NiSi$ からなる第2、第3の金属シリサイド膜とを有するMOSFETを備えることを特徴としている。

## 【0014】

上記のような構成によれば、コンタクト材料として $NiSi$ を用いる場合に、高温の後熱工程によりソース／ドレイン領域やゲート電極との界面抵抗の上昇やシート抵抗の上昇などの耐熱性の問題を回避してトランジスタのスイッチング速度を高速化できる。

## 【0015】

また、本発明の半導体装置の製造方法は、半導体基板上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上に $Ge / (Si + Ge)$ 組成比が $x (0 < x < 0.2)$ の $poly-Si_{1-x}Ge_x$ 層を含むゲート電極を形成する工程と、前記半導体基板の主表面領域中に不純物を導入してソース／ドレイン領域を形成する工程と、前記ゲート電極上及び前記ソース／ドレイン領域上に $Ni$ 膜を形成する工程と、熱処理を行って、前記ゲート電極上の $Ni$ 膜を $NiSi_{1-y}Ge_y$ 膜に置換し、且つ前記ソース／ドレイン領域上の $Ni$ 膜を $NiSi$ 膜に置換する工程とを具備することを特徴としている。

## 【0016】

上記のような製造方法によれば、種々のパターン部でのシート抵抗の上昇を抑制できるので、製造歩留まりと信頼性を向上できる。

## 【0017】

## 【発明の実施の形態】

以下、本発明の実施の形態について図面を参照して説明する。

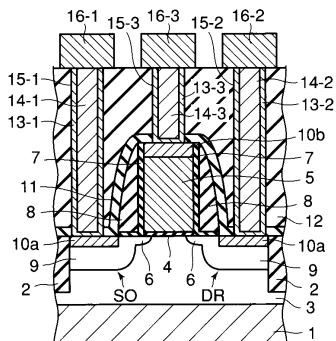

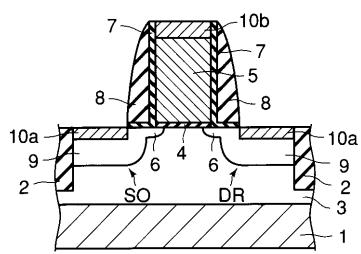

図1は、本発明の実施の形態に係る半導体装置について説明するためのもので、MOSFETの断面図である。

## 【0018】

基板1は、N型シリコン基板またはP型シリコン基板であり、この基板1の主表面には例えば埋め込み素子分離法等により素子分離構造2が形成されている。また、この素子分離構造2で区画された基板1の能動素子領域中には、P型またはN型のウェル領域3が形成されている。このウェル領域3内には、チャンネル領域を挟むようにソース／ドレイン領域SO, DRが形成されている。このソース／ドレイン領域SO, DRは、ソース／ドレイン・エクステンションを有する構造であり、高濃度の不純物拡散領域9, 9と、これらの領域9, 9におけるチャンネル領域の近傍に設けられた低濃度の不純物拡散領域6, 6とで形成される。このソース／ドレイン領域SO, DRにおける、上記高濃度の不純物拡散領域9, 9上には、サリサイドプロセスにより金属シリサイド膜( $NiSi$ )10aが形成されている。

## 【0019】

上記ソース／ドレイン領域SO, DR間のチャネル領域上には、ゲート絶縁膜4が形成されている。このゲート絶縁膜4の材料は、シリコン酸化膜でも良いが、シリコン窒化膜を含んでいる方が好ましい。上記ゲート絶縁膜4上には、ゲート電極5が形成されている。このゲート電極5は、 $poly-Si_{0.88}Ge_{0.12}$ 層の一層構造、あるいは $poly-Si$ 層上に $poly-Si_{0.88}Ge_{0.12}$ 層が積層された二層構造になっている。この $poly-Si_{0.88}Ge_{0.12}$ 層は、 $Ge / (Si + Ge)$ 組成比が $x (0 < x < 0.2)$ 、より好ましくは $0.04 < x < 0.16$ の $poly-Si_{1-x}Ge_x$ が好適であり、ここではその一例として $poly-Si_{0.88}Ge_{0.12}$ を用いている。

10

20

30

40

50

【 0 0 2 0 】

上記ゲート電極 5 上には、サリサイドプロセスにより金属シリサイド膜 (NiSi<sub>1-y</sub>Ge<sub>y</sub> (y は x とほぼ等しい)、例えば NiSi<sub>0.88</sub>Ge<sub>0.12</sub>) 10 b が形成されている。上記ゲート電極 5 の側壁部には、後酸化膜 7, 7 としてのシリコン酸化膜と、側壁絶縁膜 8, 8 が設けられている。上記側壁絶縁膜 8, 8 は、上記したようなソース / ドレイン領域 S / D を形成するために製造プロセス上で必要な構造であり、例えばシリコン窒化膜及びシリコン酸化膜からなる。なお、上記ゲート電極 5 の側壁部には、オフセットスペーサが設けられていても良い。

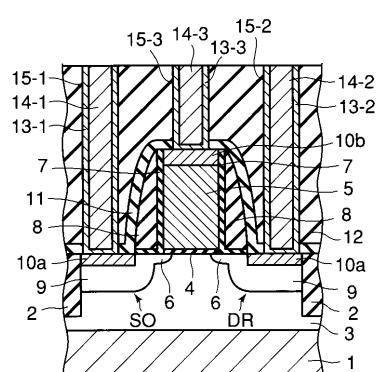

【 0 0 2 1 】

上記MOSFET上には、例えばシリコン窒化膜11とシリコン酸化膜12とからなる層間絶縁膜が形成されている。この層間絶縁膜の上記ソース／ドレイン領域S0, DR(金属シリサイド10a, 10a)に対応する位置、及びゲート電極5(金属シリサイド10b)に対応する位置には、コンタクトホール15-1, 15-2, 15-3が形成されている。これらコンタクトホール15-1, 15-2, 15-3内には、TiNまたはTiNとTiが積層されたバリアメタル層13-1, 13-2, 13-3を介在してタンゲステン(W)プラグ14-1, 14-2, 14-3が埋め込み形成されている。

【 0 0 2 2 】

そして、上記層間絶縁膜上に、上記Wプラグ14-1, 14-2, 14-3とそれぞれ電気的に接続された状態で、ソース配線16-1、ドレイン配線16-2及びゲート配線16-3等の引き出し電極が形成されている。

[ 0 0 2 3 ]

本実施の形態で示したように、MOSFETのゲート電極材料として、 $x$  ( $0 < x < 0.2$ 、より好ましくは $0.04 \leq x \leq 0.16$ ) の poly-Si<sub>1-x</sub>Ge<sub>x</sub>層を用いることにより、ゲート電極5上の金属シリサイド10bのシート抵抗の上昇を抑制することができる。これによって、トランジスタの寄生抵抗を低減でき、スイッチング速度を高速化できる。

[ 0 0 2 4 ]

ところで、上述したようにゲート電極 5 としては、poly-Si<sub>1-x</sub>Ge<sub>x</sub>の一層構造や、poly-Si<sub>1-x</sub>Ge<sub>x</sub>/poly-Siといった二層構造 (poly-Si がゲート絶縁膜との界面側) が用いられるが、このときの poly-Si<sub>1-x</sub>Ge<sub>x</sub> 層の膜厚が薄いと、Ni が Si<sub>1-x</sub>Ge<sub>x</sub> を突き抜けて Si と優先的に反応してしまう。Ni の場合、反応によって消費する下地 Si<sub>1-x</sub>Ge<sub>x</sub> の膜厚は、反応前の Ni 膜厚と同程度である。また、NiSi<sub>1-y</sub>Ge<sub>y</sub>/Si<sub>1-x</sub>Ge<sub>x</sub> 界面のモフォロジ荒れによるマージンを考慮すると、反応前の Ni 膜厚の少なくとも 2 倍程度の膜厚が好ましい。

【 0 0 2 5 】

なお、実験によれば、 $Si_{1-x}Ge_x$  の膜厚が薄いときには、シート抵抗の上昇が見られ、断面 TEM 観察を行ったところ Ni シリサイドが  $Si_{1-x}Ge_x$  を突き抜けて Si と反応して凝集していた。これは、Ni - Ge の結合より Ni - Si の結合の方がエネルギー的に安定なために、 $NiSi_{1-y}Ge_y$  よりも NiSi へ進んだためと考えられる。

【 0 0 2 6 】

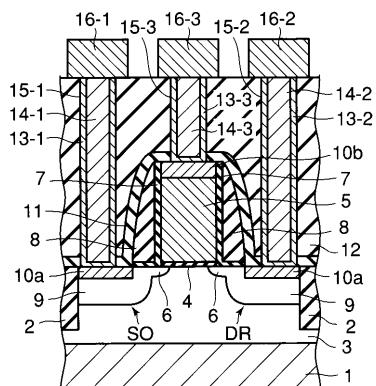

次に、上記図1に示したMOSFETの製造方法について説明する。図2乃至図6はそれぞれ、上記図1に示したMOSFETの製造方法を工程順に示す断面図である。

( 0 0 2 7 )

まず、図2に示すように、P型シリコン基板あるいはN型シリコン基板1に、例えば埋め込み素子分離法等により、深さ300nm程度の素子分離構造2を形成する。その後、熱酸化を行って能動素子領域上に10nm程度のシリコン酸化膜を形成し、この酸化膜越しに上記基板1中に不純物をイオン注入し、ウェル領域3及びチャンネルストップを形成する。この時の、典型的なイオン注入条件としては、例えばPウェル領域を形成する場合にはボロン(B)を加速エネルギー-260KeV、ドーズ量 $2.0 \times 10^{13} \text{ cm}^{-2}$ の条件、Nウェル領域ではリン(P)を加速エネルギー-500KeV、ドーズ量 $2.5 \times 10^{13} \text{ cm}^{-2}$ の条件

$10^3 \text{ cm}^{-2}$  の条件である。

【0028】

その後、図3に示すように、能動素子領域上にゲート絶縁膜4 ( $\text{Si}_3\text{N}_4$ 、 $\text{SiO}_2 + \text{Si}_3\text{N}_4$ 、または $\text{SiO}_x\text{N}_y + \text{Si}_3\text{N}_4$ )を $1 \sim 5 \text{ nm}$ の厚さに形成した後、このゲート絶縁膜4上に例えばpoly-Si<sub>0.88</sub>Ge<sub>0.12</sub>(またはpoly-Si、poly-Si<sub>0.88</sub>Ge<sub>0.12</sub>の順に)を成膜してパターニングすることによりゲート電極5を形成する。引き続き、後酸化工程を行って上記基板1の主表面上、上記ゲート電極5の上面と側壁にそれぞれ後酸化膜7を形成する。次に、必要に応じて上記ゲート電極5の側壁にオフセットスペーサを形成した後(図示せず)、上記ゲート電極5をマスクにして、基板1の主表面領域中にイオン注入を行って、ソース/ドレイン・エクステンション(低濃度の不純物拡散領域6, 6)を形成する。上記エクステンションを形成するための典型的なイオン注入条件は、N型では砒素(As)を加速エネルギー $10 \text{ keV}$ 、ドーズ量 $5 \times 10^{14} \text{ cm}^{-2}$ の条件、P型ではBF<sub>2</sub>を加速エネルギー $7 \text{ keV}$ 、ドーズ量 $5 \times 10^{14} \text{ cm}^{-2}$ の条件である。

10

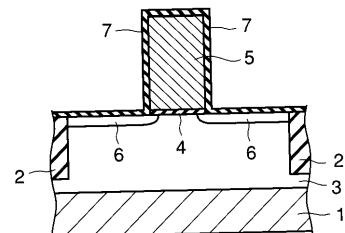

【0029】

次に、図4に示すように、800程度の活性化RTA(急速熱アニール処理)を施した後、CVD法、異方性エッチング法等の技術によりシリコン窒化膜及びシリコン酸化膜からなる側壁絶縁膜8, 8を形成する。その後、上記ゲート電極5及び側壁絶縁膜8, 8をマスクにして、基板1の主表面領域中にイオン注入を行うことによって、深い接合部(高濃度の不純物拡散領域9, 9)を形成する。この深い接合部を形成するための典型的なイオン注入条件は、N型ではAsを加速エネルギー $50 \text{ keV}$ 、ドーズ量 $7 \times 10^{15} \text{ cm}^{-2}$ の条件、P型ではBを加速エネルギー $5 \text{ keV}$ 、ドーズ量 $4 \times 10^{15} \text{ cm}^{-2}$ の条件である。その後、約1000程度の活性化RTAを行うことによって、ソース/ドレイン領域SO, DRとして働く不純物拡散層のドーパントの活性化を行う。

20

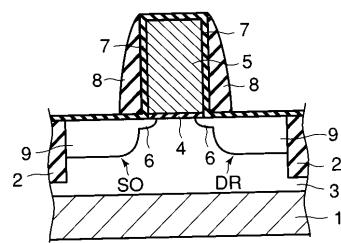

【0030】

次に、上記後酸化膜7がソース/ドレイン領域SO, DR上及びゲート電極5上に残存していれば薬液処理により剥離する。その後、スパッタ法(あるいはCVD法)を用いて全面にNi膜を成膜する。このNi膜の膜厚は、 $10 \sim 15 \text{ nm}$ 程度とする。Ni膜の膜厚を厚くすればするほど、凝集によるシート抵抗の上昇は抑制できるが、逆に接合リードレベルが上昇するので、上記 $10 \sim 15 \text{ nm}$ 程度が好ましい。次に、500のRTAによりソース/ドレイン領域SO, DR上及びゲート電極5上のNi膜を、それぞれ金属シリサイド膜(NiSi)<sub>10a</sub>及び金属シリサイド膜(NiSi<sub>0.88</sub>Ge<sub>0.12</sub>)<sub>10b</sub>に置換する。RTA温度が450以下のように低い場合には、反応が十分進まずにNi<sub>2</sub>Si<sub>0.88</sub>Ge<sub>0.12</sub>がNiSi<sub>0.88</sub>Ge<sub>0.12</sub>表面に残存していた。このNi<sub>2</sub>Si<sub>0.88</sub>Ge<sub>0.12</sub>が残存した状態で、HC1とH<sub>2</sub>O<sub>2</sub>やO<sub>3</sub>を含んだ薬液処理を行うと、過剰なNiと薬液が反応して膜剥がれを生じていた。また、剥がれ部を分析するとその箇所のNiは消失し、SiO<sub>2</sub>層が観察された。次いで、未反応の金属(Ni膜)を選択エッチングにより除去すると、図5に示すようになる。

30

【0031】

その後、図6に示すように、全面にシリコン窒化膜11及びシリコン酸化膜12を層間絶縁膜として堆積形成後、CMP処理により表面の平坦化を行う。次いで、RIEにより、ソース/ドレイン領域SO, DR及びゲート電極5の引き出し電極形成のためのコンタクトホール15-1, 15-2, 15-3を開口する。そして、TiをCVD成膜した後、N<sub>2</sub>雰囲気(あるいはNH<sub>3</sub>雰囲気、またはFG(3%のH<sub>2</sub>を含むN<sub>2</sub>)雰囲気)中で550程度の温度により60分間のアニールを施して窒化することにより、少なくとも一部をTiNとしたバリアメタル層13-1, 13-2, 13-3を形成する。このアニールは、金属シリサイド10a, 10b形成後の最高温度熱工程となっている。更に、CVD法によりタンゲステン(W)プラグ14-1, 14-2, 14-3を埋め込み形成し、CMPを行うことにより層間絶縁膜の表面を平坦化する。

40

【0032】

50

その後、アルミニウム等の金属を蒸着した後、パターニングしてソース配線16-1、ドレイン配線16-2及びゲート配線16-3等の引き出し電極を形成し、図1に示したようなMOSFETを形成する。

### 【0033】

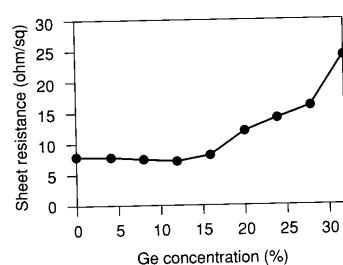

本実施の形態で重要なのは、ゲート電極材料である $\text{poly-Si}_{1-x}\text{Ge}_x$ のGe/(Si+Ge)組成比である。図7は、pチャネル型MOSFETのボロン(B)がドープされたゲート電極( $\text{poly-Si}_{1-x}\text{Ge}_x$ )上に形成された金属シリサイド( $\text{NiSi}_{1-y}\text{Ge}_y$ )膜のGe濃度(Ge concentration)とゲート電極上の金属シリサイドのシート抵抗(Sheet resistance)との関係を示している。換言すれば、Ge/(Si+Ge)組成比に対するシート抵抗の依存性を示している。図7から明らかなように、組成比Ge/(Si+Ge)が0~0.16(0~16%)の範囲ではシート抵抗はほとんど変化しないが、0.2(20%)以上においてシート抵抗の急激な上昇が見られる。

### 【0034】

この傾向は、nチャネル型MOSFETのリン(P)または砒素(As)をドープしたゲート電極 $\text{poly-Si}_{1-x}\text{Ge}_x$ 上の金属シリサイド( $\text{NiSi}_{1-y}\text{Ge}_y$ )膜においても同様であった。

### 【0035】

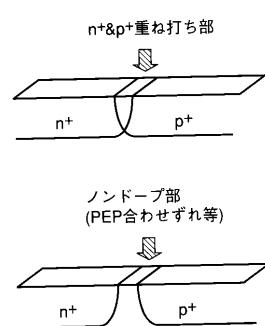

ところで、実際のデバイスでは、図8(a)に示すようなp型及びn型の不純物の重ね打ち部や、図8(b)に示すようなPEPの合わせずれ等によるノンドープ部が存在する。

### 【0036】

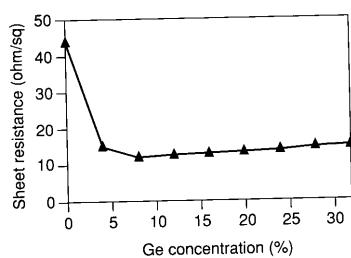

図9は、上記図8(b)に相当するノンドープ部を持つゲート電極( $\text{poly-Si}_{1-x}\text{Ge}_x$ )上の金属シリサイド( $\text{NiSi}_{1-y}\text{Ge}_y$ )膜におけるGe濃度(Ge concentration)とシート抵抗(Sheet resistance)との関係を示している。すなわち、シート抵抗のGe/(Si+Ge)組成比に対する依存性を示している。この場合は、図7に示した場合とは傾向が全く異なり、ゲート電極( $\text{poly-Si}_{1-x}\text{Ge}_x$ )のGe/(Si+Ge)組成比が0に対応するゲート電極( $\text{poly-Si}$ )でシート抵抗の上昇が見られた。物理解析として、断面SEM観察及びEDX分析を行ったところ、 $\text{poly-Si}$ 層を含むゲート電極上の $\text{NiSi}$ 膜では $\text{NiSi}_2$ 膜への相転移を伴って凝集が生じていることが観測された。一方、本実施の形態に用いた $\text{poly-Si}_{0.88}\text{Ge}_{0.12}$ 層を含むゲート電極上の $\text{NiSi}_{0.88}\text{Ge}_{0.12}$ 膜では相転移は観測されなかった。

### 【0037】

ここで、図9に示した $\text{poly-Si}$ と $\text{Si}_{1-x}\text{Ge}_x$ の結晶粒径は、ほぼ同じものを用いた。耐熱性の傾向としては、この結晶粒径が大きくなるほど凝集が進み易く、シート抵抗も上昇する。また、結晶粒径が小さい場合には凝集は進みにくいが、 $\text{NiSi}_2$ への相転移が起こりやすく、これに伴うシート抵抗上昇が見られた。

### 【0038】

上記実施の形態で示したように、Ge/(Si+Ge)組成比が $x(0 < x < 0.2)$ 、より好ましくは $0.04 < x < 0.16$ の $\text{poly-Si}_{1-x}\text{Ge}_x$ 層を含むゲート電極材料を選択することにより、上記不純物をドープした $\text{poly-Si}_{1-x}\text{Ge}_x$ 層を含むゲート電極と、ノンドープの $\text{poly-Si}_{1-x}\text{Ge}_x$ からなるゲート電極の双方のシート抵抗の上昇を抑制することができる。

### 【0039】

従って、金属シリサイド形成後に熱工程を施したMOSFETにおいて、ゲート電極上の金属シリサイドのシート抵抗の上昇を抑制できる。このシート抵抗の上昇の抑制によって、それに伴うトランジスタの寄生抵抗の低減によるスイッチング速度の高速化が可能となる。しかも、種々のパターン部、例えばPEPの合わせずれによるノンドープ部でのシート抵抗の上昇も抑制できるので、製造歩留まりと信頼性を向上できる。

### 【0040】

10

20

30

40

50

なお、上述した実施の形態では、NiとSiGeの組み合わせを、ゲート電極について説明した。しかしながら、これとは別に、ソース／ドレイン領域のSi基板上にSiやSiGeをエピタキシャル成長させて、接合深さを稼ぐ試みが検討されている。この場合についても、ゲート電極上と同様Ge濃度を上述したような低濃度にすることにより、Niシリサイドの凝集、及びNiSi<sub>2</sub>への相転移抑制が可能である。

#### 【0041】

以上実施の形態を用いて本発明の説明を行ったが、本発明は上記実施の形態に限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で種々に変形することが可能である。また、上記実施の形態には種々の段階の発明が含まれており、開示される複数の構成要件の適宜な組み合わせにより種々の発明が抽出され得る。例えば実施の形態に示される全構成要件からいくつかの構成要件が削除されても、発明が解決しようとする課題の欄で述べた課題の少なくとも1つが解決でき、発明の効果の欄で述べられている効果の少なくとも1つが得られる場合には、この構成要件が削除された構成が発明として抽出され得る。

10

#### 【0042】

##### 【発明の効果】

以上説明したように、本発明によれば、コンタクト材料としてNiSiを用いる場合に、高温の後熱工程によるゲート電極のシート抵抗の上昇といった耐熱性の問題を回避してトランジスタのスイッチング速度を高速化できる半導体装置が得られる。

#### 【0043】

また、製造歩留まりと信頼性を向上できる半導体装置の製造方法が得られる。

20

##### 【図面の簡単な説明】

【図1】本発明の実施の形態に係る半導体装置について説明するためのもので、MOSFETの断面構成図。

【図2】本発明の実施の形態に係る半導体装置の製造方法について説明するためのもので、図1のMOSFETの製造方法を工程順に示しており、第1の工程の断面図。

【図3】本発明の実施の形態に係る半導体装置の製造方法について説明するためのもので、図1のMOSFETの製造方法を工程順に示しており、図2に続く第2の工程の断面図。

30

【図4】本発明の実施の形態に係る半導体装置の製造方法について説明するためのもので、図1のMOSFETの製造方法を工程順に示しており、図3に続く第3の工程の断面図。

【図5】本発明の実施の形態に係る半導体装置の製造方法について説明するためのもので、図1のMOSFETの製造方法を工程順に示しており、図4に続く第4の工程の断面図。

【図6】本発明の実施の形態に係る半導体装置の製造方法について説明するためのもので、図1のMOSFETの製造方法を工程順に示しており、図5に続く第5の工程の断面図。

40

【図7】pチャネル型MOSFETのボロンがドープされたゲート電極上に形成された金属シリサイド膜のGe濃度とシート抵抗との関係を示す図。

【図8】実際のデバイスにおけるp型及びn型の不純物の重ね打ち部と、PDPの合わせずれ等によるノンドープ部の概念について説明するための図。

【図9】ノンドープ部を持つゲート電極上の金属シリサイド膜におけるGe濃度とシート抵抗との関係を示す図。

##### 【符号の説明】

- 1 ... 基板 (N型シリコン基板またはP型シリコン基板)

- 2 ... 素子分離構造

- 3 ... ウェル領域

- 4 ... ゲート絶縁膜

- 5 ... ゲート電極

50

6 ... 低濃度の不純物拡散領域

7 ... 後酸化膜(シリコン酸化膜)

8 ... 側壁絶縁膜(シリコン窒化膜及びシリコン酸化膜)

9 ... 高濃度の不純物拡散領域

10a, 10b ... 金属シリサイド膜

11 ... シリコン窒化膜

12 ... シリコン酸化膜

13-1, 13-2, 13-3 ... バリアメタル層

14-1, 14-2, 14-3 ... 第1乃至第3の金属(タンゲステン)プラグ

15-1, 15-2, 15-3 ... 第1乃至第3のコンタクトホール

16-1, 16-2, 16-3 ... 配線

S O, D R ... ソース/ドレイン領域

10

【図1】

【図3】

【図4】

【図2】

【図5】

【図6】

【図7】

【図8】

【図9】

## フロントページの続き

(51) Int.Cl.<sup>7</sup> F I テーマコード(参考)

H 01 L 29/49 H 01 L 27/08 102C

H 01 L 29/78 H 01 L 27/08 102D

(74)代理人 100070437

弁理士 河井 将次

(72)発明者 出羽 光明

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72)発明者 飯沼 俊彦

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72)発明者 須黒 恭一

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

F ターム(参考) 4M104 AA01 BB01 BB02 BB14 BB19 BB21 BB30 BB36 BB38 BB40

CC01 CC05 DD04 DD08 DD16 DD17 DD37 DD43 DD55 DD64

DD65 DD75 DD78 DD80 DD84 FF13 FF14 FF22 GG09 GG10

GG14 HH12 HH16

5F048 AA07 AC03 BA14 BB04 BB05 BB06 BB07 BB08 BB09 BB13

BC06 BF01 BF06 BF07 BF11 BF15 BF16 BG11 DA25 DA27

5F140 AA00 AA01 AA10 BA01 BD01 BD05 BD07 BD09 BD10 BF04

BF11 BF14 BF18 BF21 BF28 BF31 BF59 BF60 BG09 BG12

BG14 BG34 BG35 BG45 BG46 BG50 BG52 BG53 BG56 BH14

BH15 BJ01 BJ08 BJ11 BJ17 BJ20 BJ27 BK02 BK13 BK21

BK29 BK30 BK33 BK34 BK35 CA03 CB02 CB04 CB08 CC01

CC03 CC08 CE07 CE08 CF04 CF05