(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5479915号

(P5479915)

(45) 発行日 平成26年4月23日(2014.4.23)

(24) 登録日 平成26年2月21日(2014.2.21)

(51) Int.Cl.

F 1

H01L 29/868 (2006.01)

H01L 29/91

D

H01L 29/861 (2006.01)

H01L 29/06

301D

H01L 29/06 (2006.01)

請求項の数 24 (全 28 頁)

(21) 出願番号 特願2009-545646 (P2009-545646)

(86) (22) 出願日 平成20年1月8日 (2008.1.8)

(65) 公表番号 特表2010-516060 (P2010-516060A)

(43) 公表日 平成22年5月13日 (2010.5.13)

(86) 國際出願番号 PCT/US2008/050532

(87) 國際公開番号 WO2008/086366

(87) 國際公開日 平成20年7月17日 (2008.7.17)

審査請求日 平成22年12月20日 (2010.12.20)

(31) 優先権主張番号 60/879,434

(32) 優先日 平成19年1月9日 (2007.1.9)

(33) 優先権主張国 米国(US)

(73) 特許権者 509084024

マックスパワー・セミコンダクター・イン

コーポレイテッド

MAX POWER SEMICONDUCTOR INC.

アメリカ合衆国、95008 カリフォル

ニア州、キャンベル、リガス・ドライブ、

675

(74) 代理人 110000578

名古屋国際特許業務法人

(72) 発明者 ダーウィッシュ モハメド エヌ.

アメリカ合衆国 カリフォルニア州 95

008 キャンベル リガス ドライブ

375

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体構造体であって、

前記半導体構造体の第1の端子に結合された第1の領域と、

前記半導体構造体の第2の端子に結合された第2の領域と、

前記第1の領域と第2の領域との間に配置された第3の領域と、

前記第3の領域の深さに沿って第1の距離だけ延在する、少なくとも第1および第2の誘電体領域と、

を備え、前記第1および第2の領域は、相反する導電型であり、前記少なくとも第1および第2の誘電体領域、または前記少なくとも第1および第2の誘電体領域のそれぞれと、前記第3の領域との間の界面領域は、意図的に導入された電荷を含み、

前記意図的に導入された電荷は、二酸化シリコン層に注入された正の電荷である、

半導体構造体。

## 【請求項 2】

前記少なくとも第1および第2の誘電体領域は、前記第1および第2の領域内に延在する、請求項1に記載の半導体構造体。

## 【請求項 3】

前記少なくとも第1および第2の誘電体領域の表面に平行な線に沿った、前記第3の領域内の不純物の集積ドープ密度は、 $1 \times 10^{12} / \text{cm}^2$  から  $5 \times 10^{12} / \text{cm}^2$  までの範囲である、請求項1に記載の半導体構造体。

## 【請求項 4】

前記少なくとも第 1 および第 2 の誘電体領域のそれぞれは、第 1 および第 2 の材料をさらに含む、請求項 1 に記載の半導体構造体。

## 【請求項 5】

前記第 1 および第 2 の領域は、それぞれ  $p^+$  型および  $n^+$  型領域であり、前記第 1 および第 2 の端子は、それぞれアノードおよびカソード端子であり、前記第 3 の領域は、 $p$  型領域である、請求項 1 に記載の半導体構造体。

## 【請求項 6】

前記第 3 の領域は、前記第 2 の領域の上方に形成され、前記第 1 の領域は、前記第 3 の領域の上方に形成される、請求項 5 に記載の半導体構造体。

10

## 【請求項 7】

前記第 1 および第 2 の領域は、それぞれ  $p^+$  型および  $n^+$  型領域であり、前記第 1 および第 2 の端子は、それぞれアノードおよびカソード端子であり、前記第 3 の領域は、 $n$  型領域である、請求項 1 に記載の半導体構造体。

## 【請求項 8】

前記第 3 の領域は、前記第 2 の領域の上方に形成され、前記第 1 の領域は、前記第 3 の領域の上方に形成される、請求項 7 に記載の半導体構造体。

20

## 【請求項 9】

前記少なくとも第 1 および第 2 の誘電体領域は、互いに隔離される、請求項 1 に記載の半導体構造体。

## 【請求項 10】

前記第 1 および第 2 の領域は、それぞれ  $n^+$  型および  $p^+$  型領域であり、前記第 1 および第 2 の端子は、それぞれカソードおよびアノード端子であり、前記第 3 の領域は、 $p$  型領域である、請求項 1 に記載の半導体構造体。

## 【請求項 11】

前記第 1 および第 2 の領域は、それぞれ  $n^+$  型および  $p^+$  型領域であり、前記第 1 および第 2 の端子は、それぞれカソードおよびアノード端子であり、前記第 3 の領域は、 $n$  型領域である、請求項 1 に記載の半導体構造体。

## 【請求項 12】

前記第 1 、第 2 、および第 3 の領域は、前記半導体構造体が形成される半導体基板の同じ表面に沿って形成される、請求項 5 に記載の半導体構造体。

30

## 【請求項 13】

半導体構造体であって、

前記半導体構造体の第 1 の端子に結合された第 1 の領域と、

前記半導体構造体の第 2 の端子に結合された第 2 の領域と、

前記第 1 の領域と第 2 の領域との間に配置された第 3 の領域と、

前記第 3 の領域の深さに沿って第 1 の距離だけ延在し、前記第 3 の領域の導電型とは相反する導電型を有する第 4 の領域であって、前記第 1 および第 2 の領域に隣接する第 4 の領域と、

前記第 3 の領域の深さに沿って第 2 の距離だけ延在する少なくとも第 1 および第 2 の誘電体領域と、

を備え、前記第 1 および第 2 の領域は、相反する導電型であり、前記第 4 の領域は、前記少なくとも第 1 および第 2 の誘電体領域の一部を囲み、前記少なくとも第 1 および第 2 の誘電体領域、または前記少なくとも第 1 および第 2 の誘電体領域のそれぞれと、前記第 4 の領域との間の界面領域は、意図的に導入された電荷を含み、

前記意図的に導入された電荷は、二酸化シリコン層に注入された正の電荷である、

半導体構造体。

## 【請求項 14】

前記少なくとも第 1 および第 2 の誘電体領域は、前記第 1 および第 2 の領域内に延在する、請求項 13 に記載の半導体構造体。

50

**【請求項 15】**

前記第1および第2の領域は、それぞれp+型およびn+型領域であり、前記第1および第2の端子は、それぞれアノードおよびカソード端子であり、前記第3の領域は、p型領域である、請求項1\_3に記載の半導体構造体。

**【請求項 16】**

前記第3の領域は、前記第2の領域の上方に形成され、前記第1の領域は、前記第3の領域の上方に形成される、請求項1\_5に記載の半導体構造体。

**【請求項 17】**

前記第1および第2の領域は、それぞれp+型およびn+型領域であり、前記第1および第2の端子は、それぞれアノードおよびカソード端子であり、前記第3の領域は、n型領域である、請求項1\_3に記載の半導体構造体。10

**【請求項 18】**

前記第3の領域は、前記第2の領域の上方に形成され、前記第1の領域は、前記第3の領域の上方に形成される、請求項1\_7に記載の半導体構造体。

**【請求項 19】**

前記少なくとも第1および第2の誘電体領域は、互いに隔離される、請求項1\_3に記載の半導体構造体。

**【請求項 20】**

前記第1および第2の領域は、それぞれn+型およびp+型領域であり、前記第1および第2の端子は、それぞれカソードおよびアノード端子であり、前記第3の領域は、p型領域である、請求項1\_3に記載の半導体構造体。20

**【請求項 21】**

前記第1および第2の領域は、それぞれn+型およびp+型領域であり、前記第1および第2の端子は、それぞれカソードおよびアノード端子であり、前記第3の領域は、n型領域である、請求項1\_3に記載の半導体構造体。

**【請求項 22】**

前記第1、第2、および第3の領域は、前記半導体構造体が形成される半導体基板の同じ表面に沿って形成される、請求項1\_3に記載の半導体構造体。

**【請求項 23】**

前記第1の領域は、p+型領域であり、前記第2の領域は、n+型領域であり、前記第3の領域は、p型領域であり、前記第4の領域は、n型領域である、請求項1\_3に記載の半導体構造体。30

**【請求項 24】**

前記第1の領域は、p+型領域であり、前記第2の領域は、n+型領域であり、前記第3の領域は、n型領域であり、前記第4の領域は、p型領域である、請求項1\_3に記載の半導体構造体。

**【発明の詳細な説明】****【発明の詳細な説明】****【0001】****【関連出願の相互参照】**

本出願は、合衆国法典第35巻第119(e)の下で、2007年1月9日に出願された米国暫定特許出願60/879,434号、名称「Power MOS Transistor」の利益を主張するものであり、参照することによりその全体の内容が本願明細書に組み込まれる。40

**【背景技術】**

本発明は、電子装置に関し、より具体的には、高電圧を維持するように適合された半導体装置に関する。

**【0002】**

電子システムでは、しばしば、一対のノードの間で比較的高い電圧を維持する必要がある。半導体p-n接合ダイオードは、高電圧を維持するように逆バイアスモードで広く使50

用されている。p - n 接合の間の高降伏電圧を維持するために、比較的厚く、また電圧維持層を形成する、低濃度ドープ領域が必要である。このような p - n 接合は、MOSFET、IGBT、およびJFET 等の多くの半導体装置に比較的高い降伏電圧を提供する。さらに、このような半導体装置は、一般的に、オン状態で比較的低いオン抵抗 ( $R_{on}$ ) を有すること、および逆バイアス条件下において比較的高い降伏電圧  $V_B$  を有することが必要である。既知のように、高降伏  $V_B$  と低  $R_{on}$  の両方を達成するには、多くの困難な課題がある。従来の装置では、降伏電圧を増加させるのに使用することができる、ドープ密度または層厚さ等の設計パラメータによって、オン抵抗の増加が生じ、その逆も生じる。

## 【0003】

10

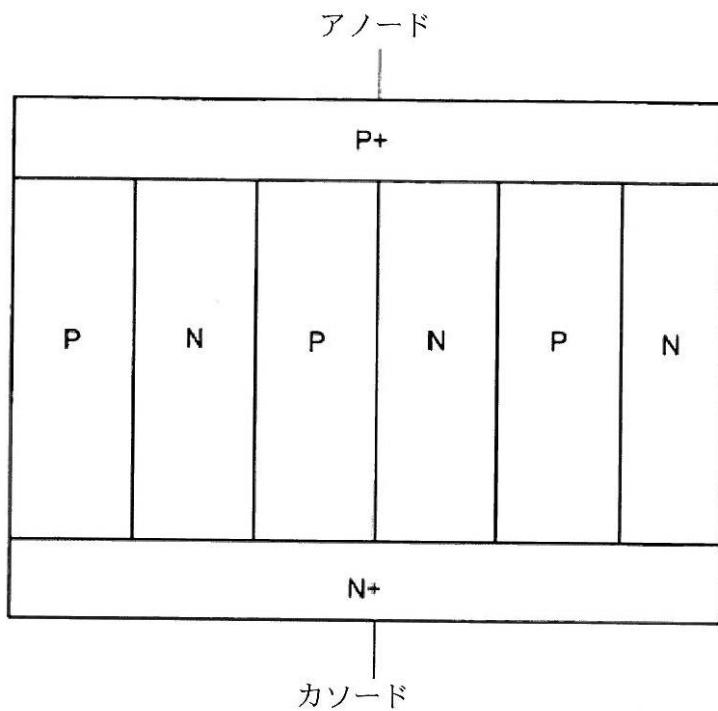

低オン抵抗および高降伏電圧の両方を達成するのに使用される 1 つの既知の装置は、一般に超接合 (SJ) 装置と称される。図 1 に示されるように、SJ 装置 (構造体) は、しばしば、電荷が平衡化された、多数の p 型および n 型を交互にした層またはピラーを含む。SJ 構造体では、固有オン抵抗  $R_{sp}$  を低くするように、所与の単位面積内に多くのピラーまたはセルを詰め込むことが望ましく、ここで、 $R_{sp}$  は、 $R_{on} \times A$  で定義され、式中、A は、装置の面積である。

## 【0004】

20

SJ 構造体では、n 型および p 型ピラーの幅によって、セルのピッチおよび構造体の小型化が制限される。また、複数のエピタキシャル層を成長させるための要件、および多くの注入および拡散ステップを実行するための要件等の、SJ 構造体の製造に関連する多くの欠点もある。高降伏電圧、低  $R_{sp}$ 、低静電容量、および低逆回復電荷 ( $Q_{rr}$ ) を有し、容易に小型化され、かつ製造が容易な半導体装置の必要性が依然として存在する。

## 【発明の概要】

半導体構造体は、本発明の一実施形態によれば、部分的に、多数の半導体領域と、少なくとも一対の誘電体領域と、一対の端子とを含む。半導体構造体の第 1 および第 2 の領域は、それぞれ第 1 および第 2 の端子に結合される。半導体構造体の第 3 の領域は、单一の導電型であり、第 1 および第 2 の領域間に配置される。誘電体領域は、第 3 の領域内に延在する。第 3 の領域内に存在する不純物のドープ濃度、および誘電体領域間の距離は、半導体構造体の電気的特性を画定する。半導体構造体の電気的特性は、誘電体領域の幅に依存しない。第 1 および第 2 の領域は、反対の導電型である。

30

## 【0005】

一実施形態では、誘電体領域は、第 1 および第 2 の領域内に延在する。一実施形態では、誘電体領域の表面に平行な線に沿った、第 3 の領域内の不純物の集積中ドープ密度は、約  $1 \times 10^{12} / \text{cm}^2$  から約  $5 \times 10^{12} / \text{cm}^2$  までの範囲である。一実施形態では、各誘電体領域は、第 2 の材料をさらに含む。一実施形態では、各誘電体領域内の第 2 の材料は、部分的に、フッ化アルミニウムを含む。一実施形態では、各誘電体領域は、部分的に、誘電体材料である第 3 の材料をさらに含む。一実施形態では、各誘電体領域内の第 2 および第 3 の材料は、同じ材料である。

## 【0006】

40

一実施形態では、第 1 および第 2 の領域は、それぞれ p + 型および n + 型領域であり、第 1 および第 2 の端子は、それぞれアノードおよびカソード端子である。一実施形態では、第 3 の領域は、p 型領域である。別の実施形態では、第 3 の領域は、n 型領域である。一実施形態では、第 3 の領域は、第 2 の領域の上方に形成され、前記第 1 の領域は、第 3 の領域の上方に形成される。一実施形態では、誘電体領域は、互いに単離される。

## 【0007】

一実施形態では、半導体構造体は、部分的に、第 2 および第 3 の領域間に配置された第 4 の領域をさらに含む。第 2 のおよび第 4 の領域は、同じ導電型である。

一実施形態では、第 1 および第 2 の領域は、それぞれ n + 型および p + 型領域であり、第 1 および第 2 の端子は、それぞれカソードおよびアノード端子である。一実施形態では、第 3 の領域は、p 型領域である。別の実施形態では、第 3 の領域は、n 型領域である。

50

一実施形態では、第3の領域は、第2の領域の上方に形成され、第1の領域は、第3の領域の上方に形成される。一実施形態では、第3の領域は、第2の領域の上方に形成され、第1の領域は、第3の領域の上方に形成される。一実施形態では、誘電体領域のそれぞれは、誘電体領域の一端の近くの幅が、誘電体領域の他端よりも広くなるようにテーパ状である。

#### 【0008】

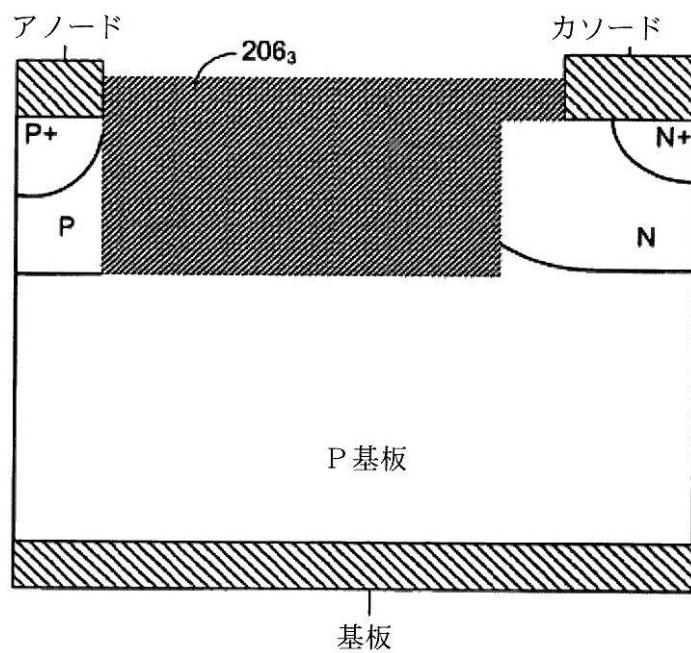

一実施形態では、第1、第2、および第3の領域は、半導体構造体が形成される半導体基板の同じ表面に沿って形成される。このような一実施形態では、半導体構造体は、第2の領域が形成される第4の領域を含む。このような一実施形態では、第3の領域は、第1および第4の領域に隣接する。このような一実施形態では、第1の領域は、p+型領域であり、第2の領域は、n+型領域であり、第3の領域は、p型領域であり、第4の領域は、n型領域である。別のこのような実施形態では、第1の領域は、p+型領域であり、第2の領域は、n+型領域であり、第3の領域は、n型領域であり、第4の領域は、p型領域である。

10

#### 【0009】

半導体構造体は、本発明の別の実施形態によれば、部分的に、多数の半導体領域と、少なくとも一対の誘電体領域と、一対の端子とを含む。半導体構造体の第1および第2の領域は、第1および第2の端子にそれぞれ結合される。第3および第4の領域は、第1および第2の領域間に隣接して配置される。誘電体領域は、第3の領域内に延在する。第4の領域は、第3の領域内に延在し、第3の領域の導電型とは反対の導電型を有し、少なくとも第1および第2の誘電体領域の一部を囲む。第3の領域内に存在する不純物のドープ濃度、および誘電体領域間の距離は、半導体構造体の電気的特性を画定する。半導体構造体の電気的特性は、誘電体領域の幅に依存しない。第1および第2の領域は、相反する導電型である。誘電体領域と第4の領域との間の界面領域は、意図的に誘起された電荷を含む。

20

#### 【0010】

一実施形態では、誘電体領域は、第1および第2の領域内に延在する。一実施形態では、誘電体領域の表面に平行な線に沿った、第3の領域内の不純物の集積ドープ密度は、約 $1 \times 10^{12} / \text{cm}^2$ から約 $5 \times 10^{12} / \text{cm}^2$ までの範囲である。一実施形態では、各誘電体領域は、第2の材料をさらに含む。一実施形態では、各誘電体領域内の第2の材料は、部分的に、フッ化アルミニウムを含む。一実施形態では、各誘電体領域は、部分的に、誘電体材料である第3の材料をさらに含む。一実施形態では、各誘電体領域内の第2および第3の材料は、同じ材料である。

30

#### 【0011】

一実施形態では、第1および第2の領域は、それぞれp+型およびn+型領域であり、第1および第2の端子は、それぞれアノードおよびカソード端子である。一実施形態では、第3の領域は、p型領域である。別の実施形態では、第3の領域は、n型領域である。一実施形態では、第3の領域は、第2の領域の上方に形成され、該第1の領域は、第3の領域の上方に形成される。一実施形態では、誘電体領域は、互いに単離される。

#### 【0012】

40

一実施形態では、半導体構造体は、部分的に、第2および第3の領域間に配置された第4の領域をさらに含む。第2のおよび第4の領域は、同じ導電型である。

一実施形態では、第1および第2の領域は、それぞれn+型およびp+型領域であり、第1および第2の端子は、それぞれカソードおよびアノード端子である。一実施形態では、第3の領域は、p型領域である。一実施形態では、第3の領域は、p型領域である。別の実施形態では、第3の領域は、n型領域である。一実施形態では、第3の領域は、第2の領域の上方に形成され、第1の領域は、第3の領域の上方に形成される。一実施形態では、第3の領域は、第2の領域の上方に形成され、第1の領域は、第3の領域の上方に形成される。一実施形態では、誘電体領域のそれぞれは、誘電体領域の一端の近くの幅が、誘電体領域の他端よりも広くなるようにテーパ状である。

50

## 【0013】

一実施形態では、第1、第2、および第3の領域は、半導体構造体が形成される半導体基板の同じ表面に沿って形成される。このような一実施形態では、半導体構造体は、第2の領域が形成される第4の領域を含む。このような一実施形態では、第3の領域は、第1および第4の領域に隣接する。このような一実施形態では、第1の領域は、p+型領域であり、第2の領域は、n+型領域であり、第3の領域は、p型領域であり、第4の領域は、n型領域である。別のこのような実施形態では、第1の領域は、p+型領域であり、第2の領域は、n+型領域であり、第3の領域は、n型領域であり、第4の領域は、p型領域である。

## 【図面の簡単な説明】

10

## 【0014】

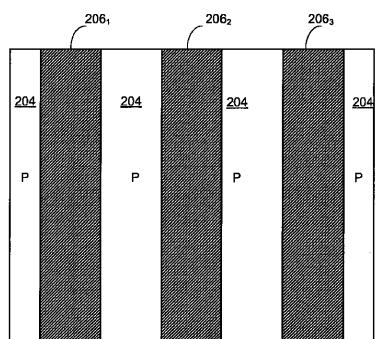

【図1】従来技術で既知の超接合装置の断面図である。

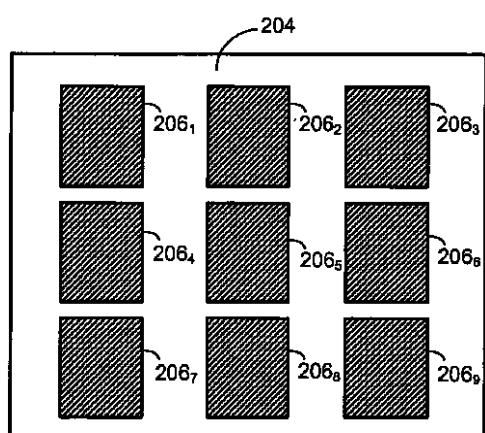

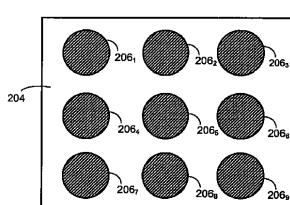

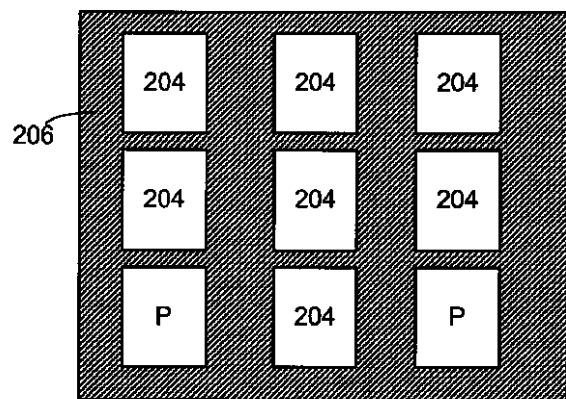

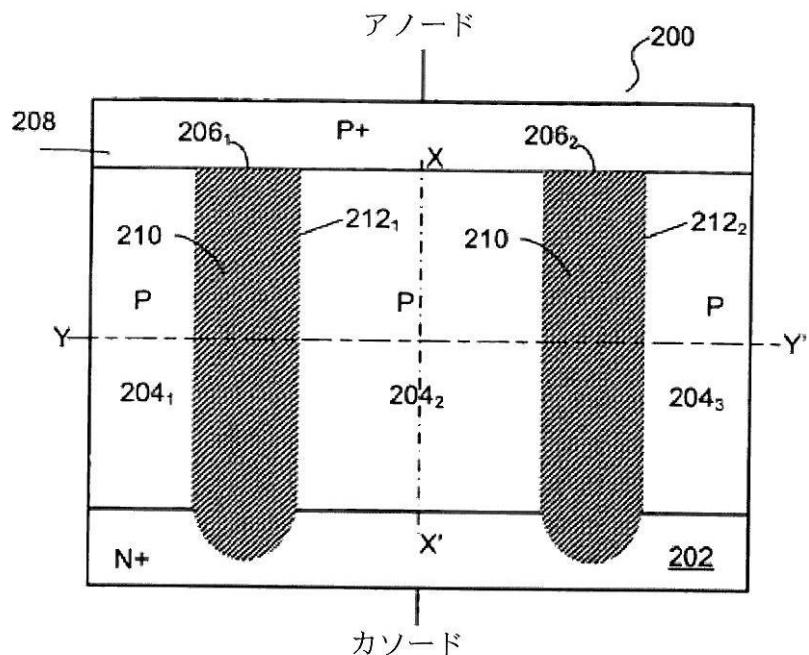

【図2A】本発明の一実施形態による、例示的な電圧維持半導体構造体の断面図である。

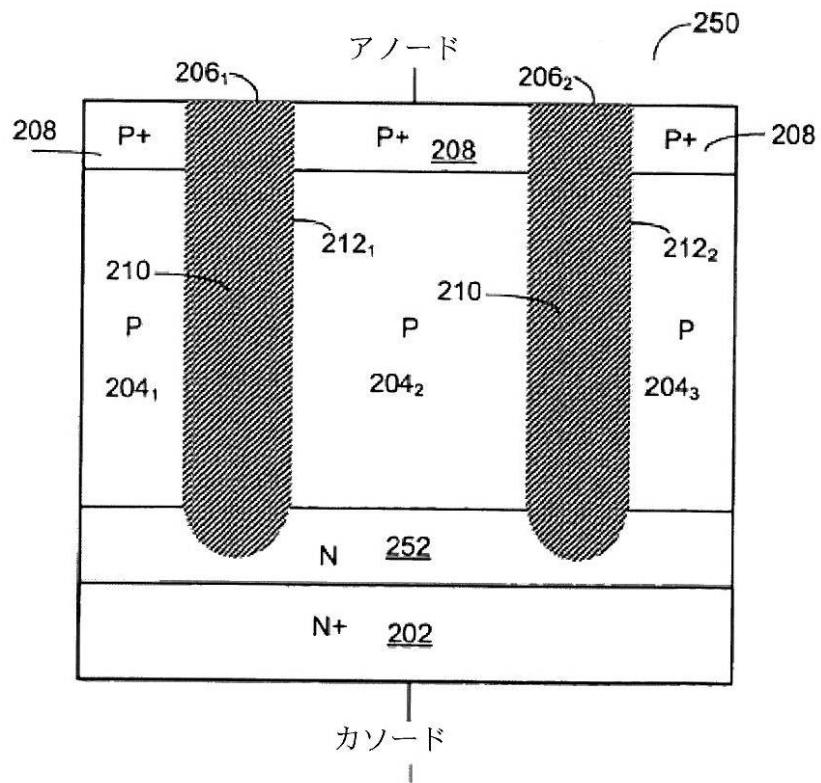

【図2B】本発明の一実施形態による、例示的な電圧維持半導体構造体の断面図である。

【図2C-2F】本発明の一実施形態による、図2Aの装置の例示的な上面図である。

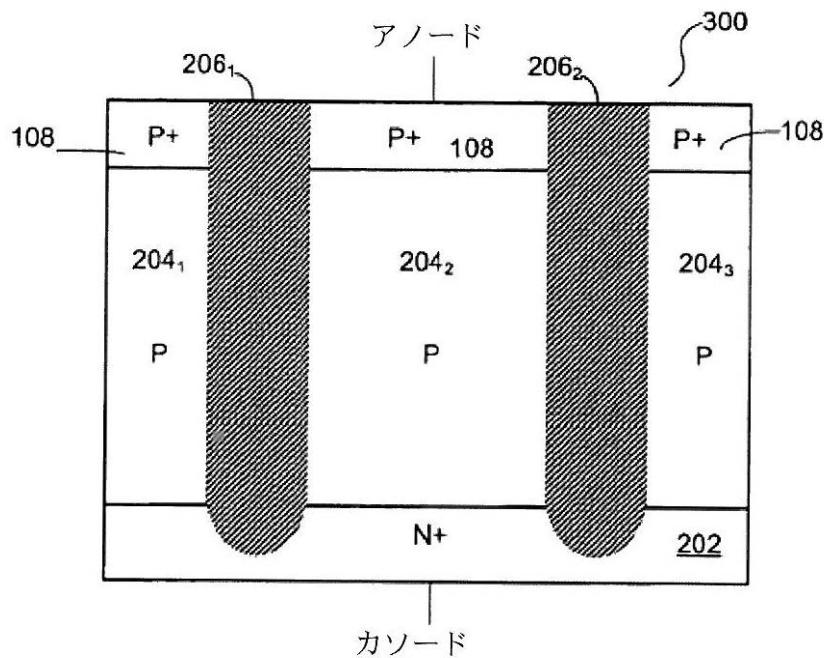

【図3】本発明の別の実施形態による、例示的な電圧維持半導体構造体の断面図である。

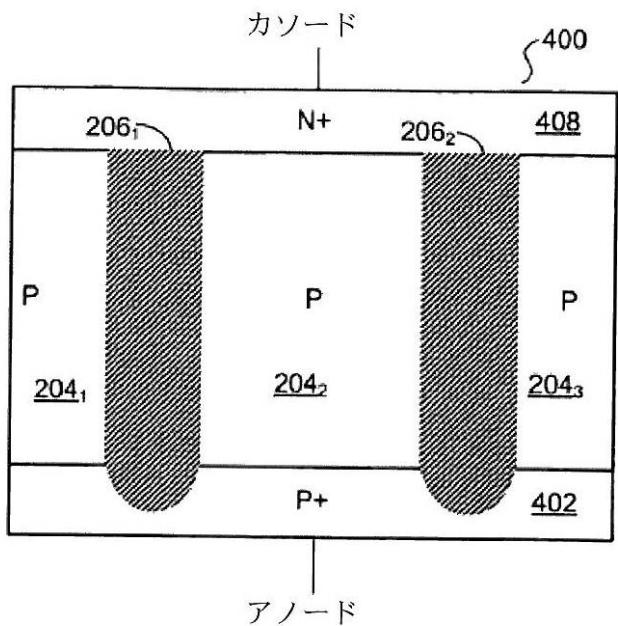

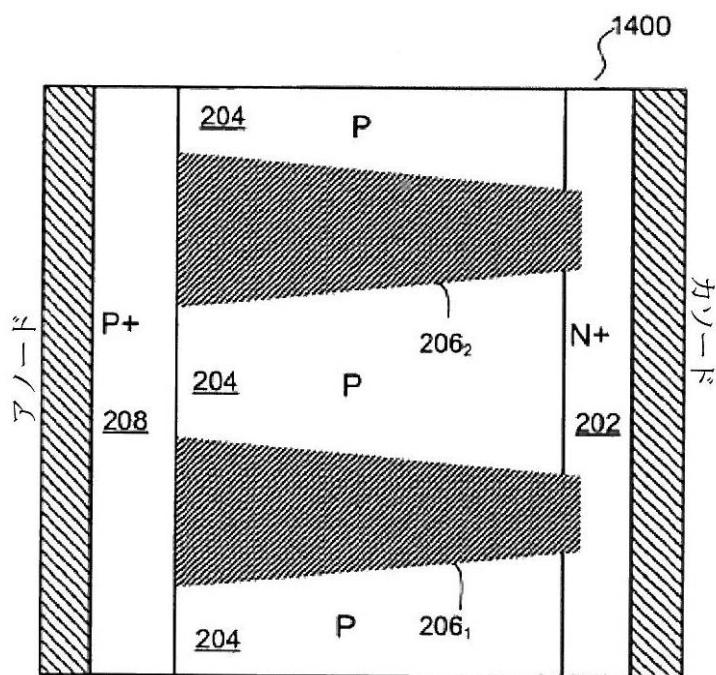

【図4】本発明の別の実施形態による、例示的な電圧維持半導体構造体の断面図である。

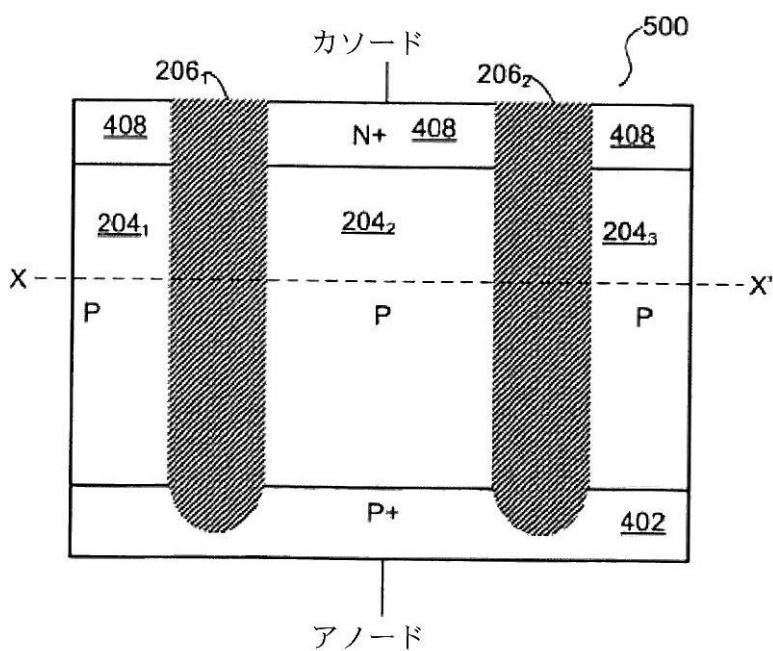

【図5】本発明の別の実施形態による、例示的な電圧維持半導体構造体の断面図である。

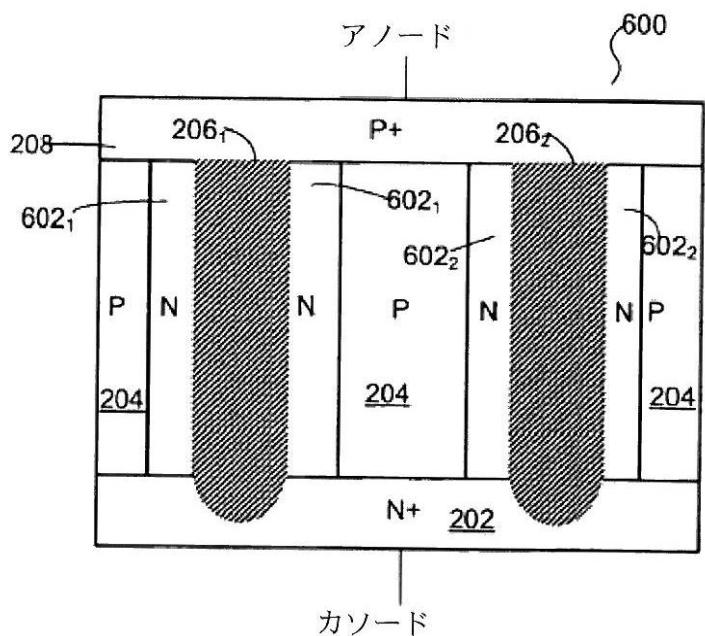

【図6A】本発明の別の実施形態による、例示的な電圧維持半導体構造体の断面図である。

20

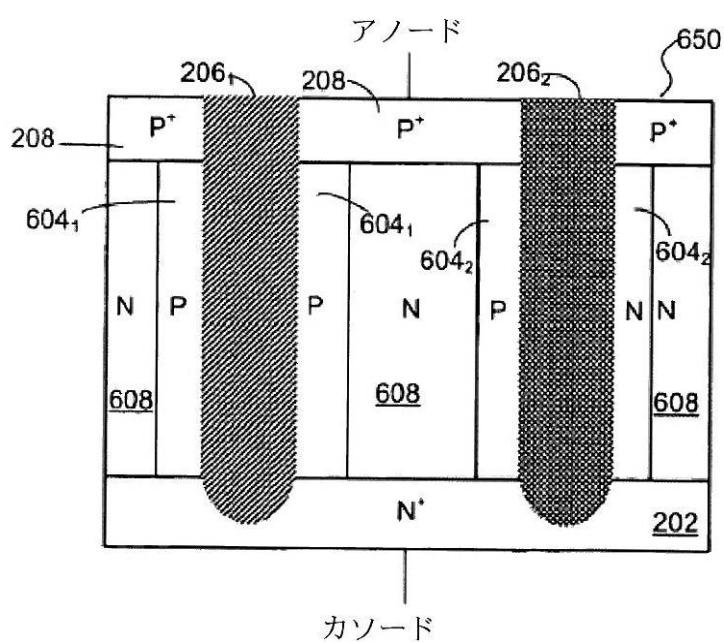

【図6B】本発明の別の実施形態による、例示的な電圧維持半導体構造体の断面図である。

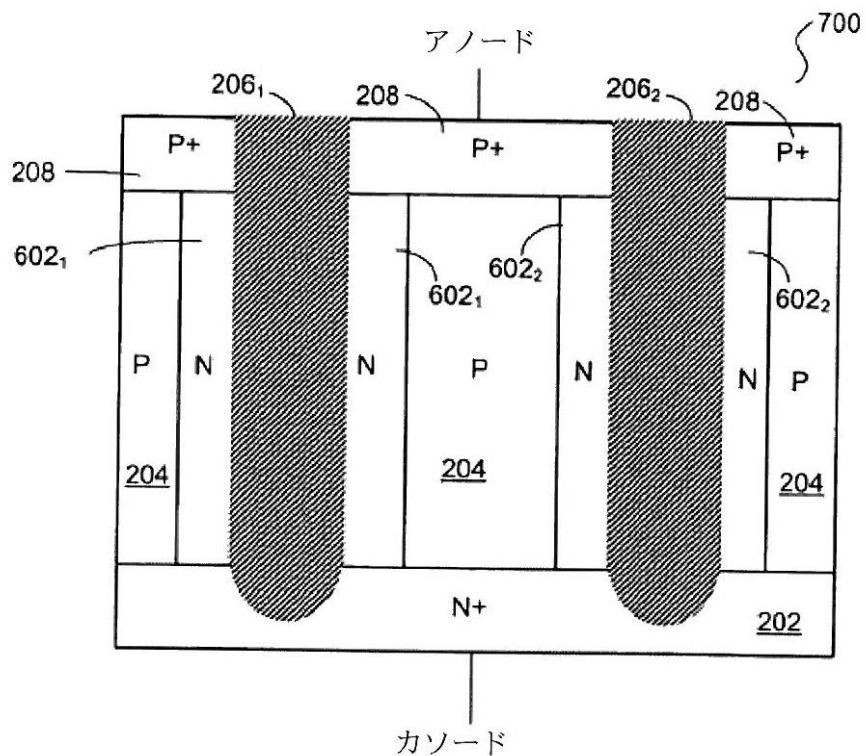

【図7】本発明の別の実施形態による、例示的な電圧維持半導体構造体の断面図である。

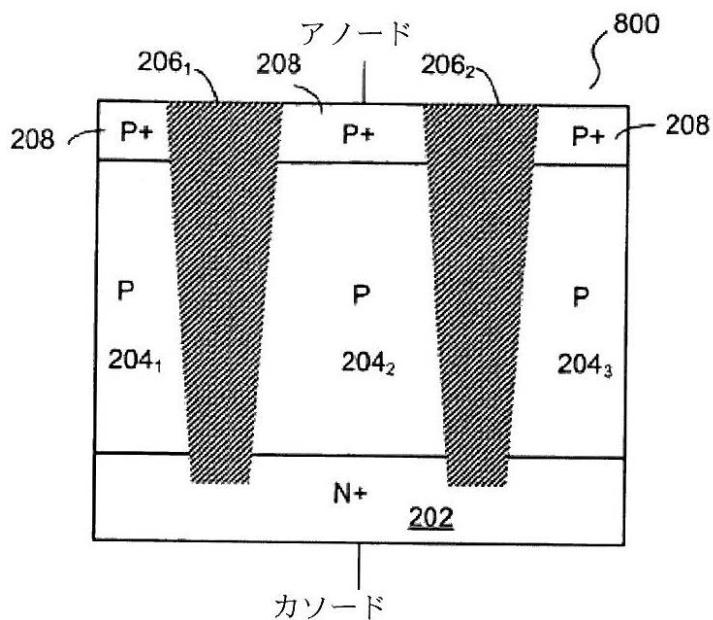

【図8】本発明の別の実施形態による、例示的な電圧維持半導体構造体の断面図である。

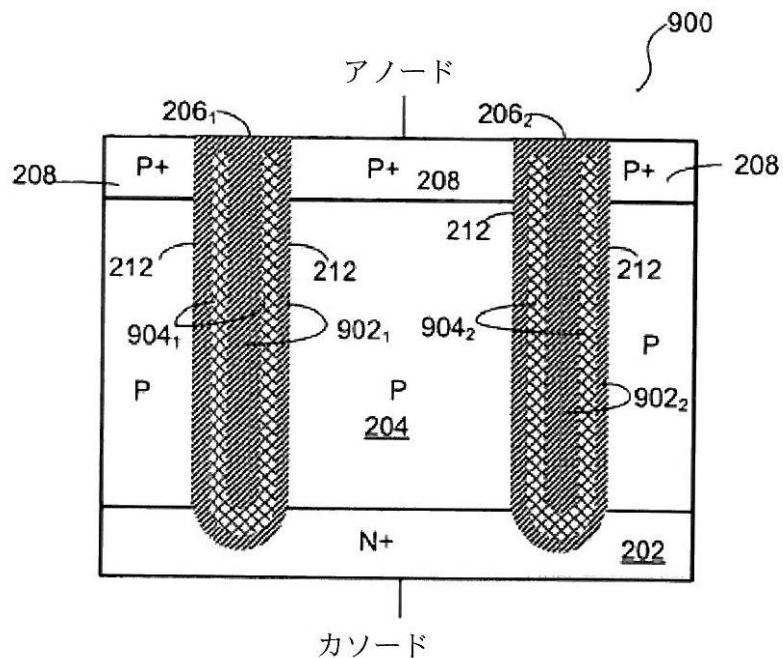

【図9】本発明の別の実施形態による、例示的な電圧維持半導体構造体の断面図である。

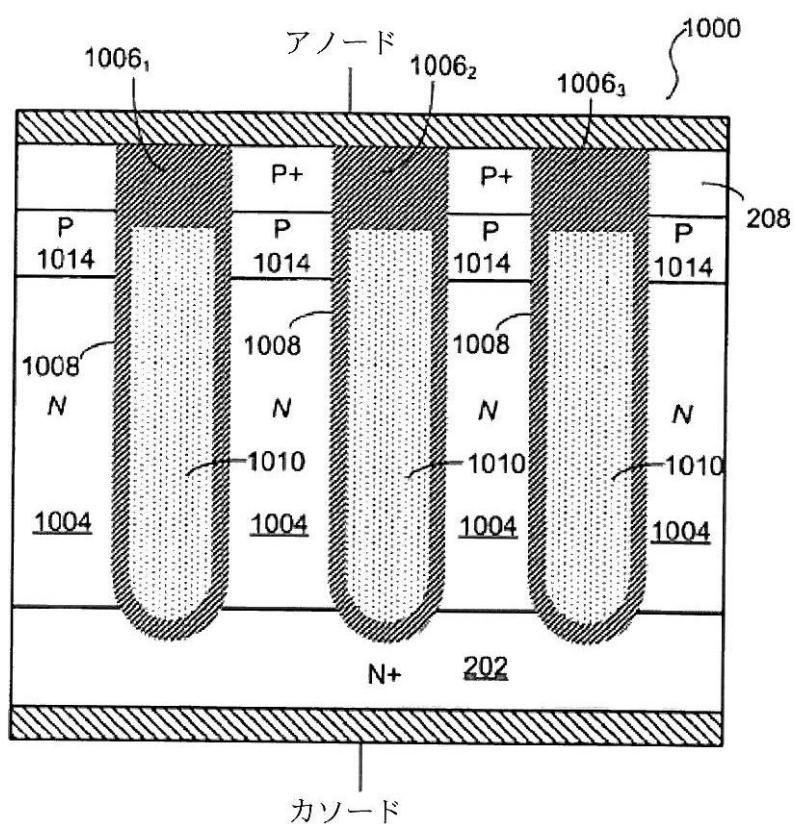

【図10】本発明の別の実施形態による、例示的な電圧維持構造体の構成要素の断面図である。

【図11】本発明の別の実施形態による、例示的な電圧維持半導体構造体の断面図である。

【図12A】本発明の別の実施形態による、横型電圧維持半導体構造体の上面図である。

30

【図12B-12C】図12Aに示される装置の種々の断面図である。

【図13A】本発明の別の実施形態による、横型電圧維持半導体構造体の上面図である。

【図13B-13D】図13Aに示される装置の種々の断面図である。

【図14】本発明の別の実施形態による、横型電圧維持半導体構造体の上面図である。

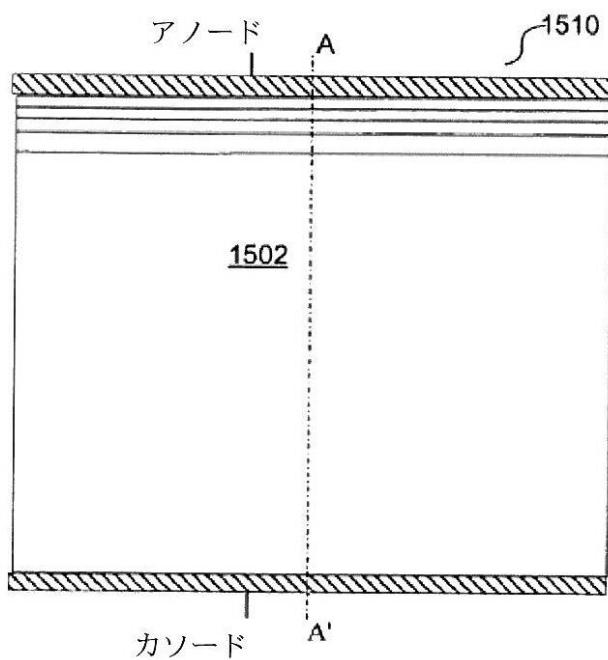

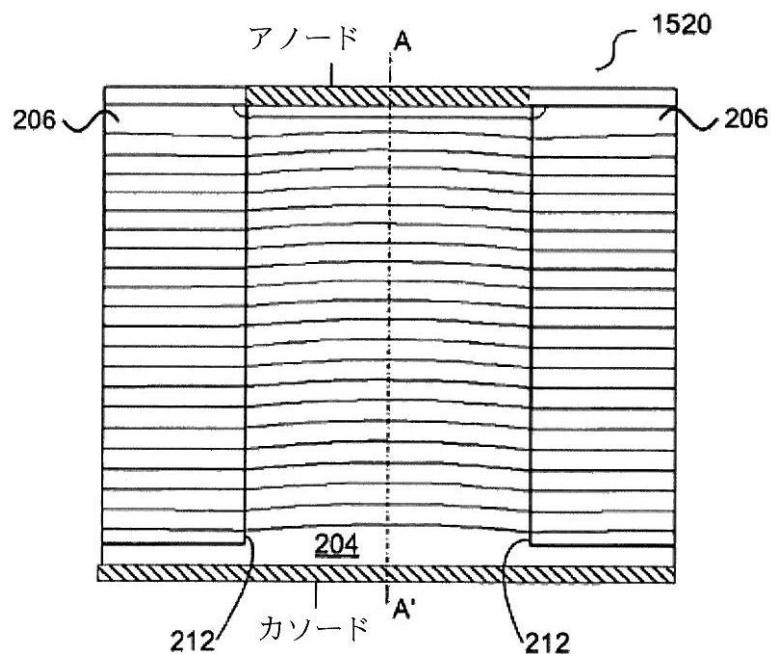

【図15A-15B】従来の構造体、および本発明の例示的な一実施形態による構造体の、それぞれの降伏電圧における等電位線を示す、コンピュータシミュレーションの図である。

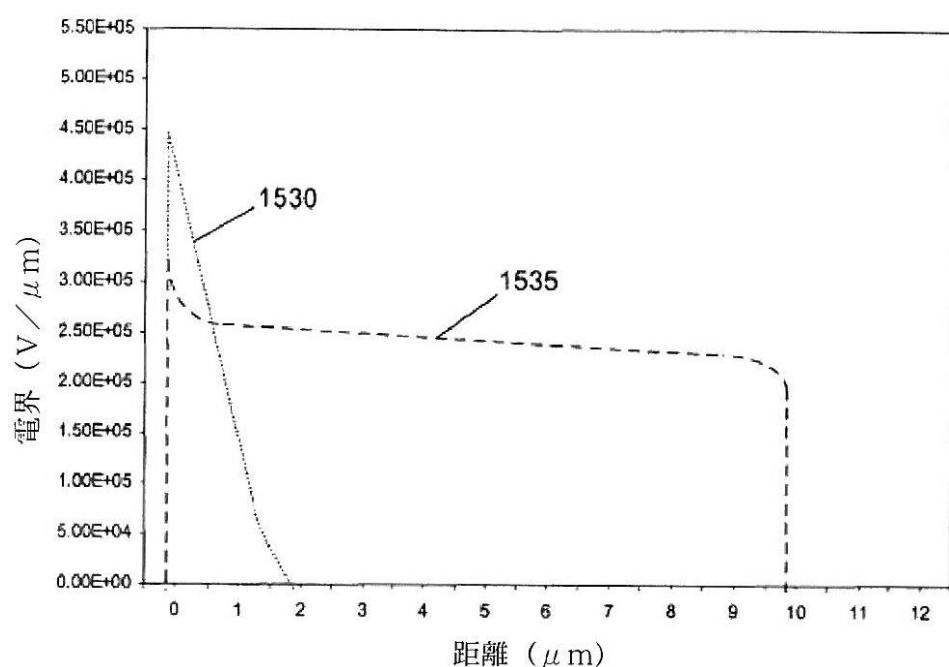

【図15C】図15A～Bに示される構造体の、断面線A A'に沿った電界を示す図である。

【図15D】図15A～Bに示される構造体の、逆バイアス電流対電圧特性を示す図である。

40

## 【発明を実施するための形態】

## 【0015】

半導体構造体は、本発明の例示的な一実施形態によれば、部分的に、比較的高い降伏電圧  $V_B$  を特徴とする。半導体構造体は、意図的に導入された電荷 ( $Q_f$ ) を有する誘電体層を含む。電荷が平衡化された誘電体およびシリコン層を交互にすることによって、該構造体は、所与の電圧維持領域のドープ濃度および/または厚さに対して、従来の装置よりも高い降伏電圧を維持する。いくつかの実施形態では、誘電体層間に配置されたシリコン層は、エピタキシャル成長、注入、または低濃度ドープのエピタキシャル成長とこれに続く注入、等を使用して形成される。本発明の実施形態によって提供された装置の性能は、工

50

ピタキシャル層または電圧維持層の同じドープおよび厚さに対する一次元シリコンの降伏電圧限度を超えるものである。

【0016】

以下の説明では、固定電荷とは、製作工程の副生物として生じる電荷に加えて、イオン注入、拡散、蒸着等の工程を使用して意図的に導入される電荷を指す。さらに、以下に、界面電荷一般、すなわち、誘電体領域と半導体領域との間の界面領域内の電荷に関して言及するが、そのような電荷はまた、誘電体領域、および誘電体領域が形成される半導体領域の両方に存在し得るものと理解される。

【0017】

逆バイアスで、誘電体層の電荷は、空乏領域内の電荷によって平衡化される。ゼロバイアスで、誘電体層の電荷は、部分的に、半導体 - 誘電体層間の界面に形成する反転層内に存在する電荷によって平衡化される。誘電体層内の電荷は、一実施形態では、最高の効率のために、半導体 - 誘電体層間の界面に、またはその近くに位置する。一実施形態では、電荷は、代表的な装置の動作温度において不動である。半導体層のイオン化不純物の空乏電荷を平衡化するのに必要な電荷を提供するために、負または正電荷の両方を使用することができる。これによって、電圧維持領域に沿ってより均一な電界がもたらされ、したがって、より高い降伏電圧がもたらされる。

【0018】

本発明は、主に半導体領域に隣接する誘電体層の誘電率および幅に依存する、従来の半導体構造体を上回る、多くの利点を提供する。本発明によれば、電荷平衡に提供される固定電荷は、トレンチ幅の関数ではない。したがって、より高い降伏電圧を達成するために、誘電体層の幅は、固定電荷を導入し、また、トレンチを再充填するのに必要なステップによってのみ制限され、これによって、従来のSJまたは非SJ型構造体によって得ることができるものよりも小さいセルピッチが可能となる。さらに、p - n接合または電界板内ではなく誘電体層内の電荷を使用して電荷平衡を行うことによって、より低い静電容量が達成される。本願明細書に記載の本発明の構造体は、製作がより容易で、かつ費用効率がより高いものである。

【0019】

所要の電荷平衡を提供するためには、負または正電荷の両方を使用し得る。本発明による、誘電体層の電荷を使用して達成される電荷平衡は、他の電荷平衡手法よりも低い静電容量値を提供する。本発明による構造体は、製作がより容易で、かつ費用効率がより高いものである。

【0020】

いくつかの実施形態では、トレンチの半導体 - 誘電体間の界面近くの負電荷は、より高い電圧を維持するように、n型半導体層の正の空乏電荷を平衡化する。負の誘電体電荷は、例えば二酸化シリコンおよびフッ化アルミニウム(A1F<sub>3</sub>またはA1F<sub>x</sub>)等の、化合物絶縁層を使用して、またはヨウ素、臭素、塩素、クロミウム、アルミニウム、または他の好適なイオン等のイオンを注入することによって生成し得る。二酸化シリコンおよびフッ化アルミニウム(A1F<sub>3</sub>またはA1F<sub>x</sub>)の化合物絶縁層を使用した負電荷生成効果は、実験的に検証され、負の界面電荷が、分率xの強い関数であることが見出された。さらに他の実施形態では、トレンチの半導体 - 誘電体間の界面近くの正電荷は、より高い電圧を維持するように、p型半導体層の負の空乏電荷を平衡化する。正電荷は、例えば、セシウムまたはカリウム等の正イオンを、トレンチの壁または底部に沿って形成された誘電体層内に注入することによって生成し得る。代替的に、窒化シリコンまたは酸窒化シリコン等の正電荷を含有する別の誘電体層が、トレンチの壁または底部に沿って形成される誘電体層上に蒸着される。例えば酸化物等の、誘電体層内に正または負電荷を生成する別の手法は、不純物を酸化物層上に蒸着し、その後にドライブインまたはアニーリングステップを行う、等の技術を使用した、酸化物内への不純物の拡散である。

【0021】

図2Aは、本発明の一実施形態による、半導体構造体(本願明細書では、装置と同意で

10

20

30

40

50

称される) 200 の断面図である。装置 200 は、n+領域 202 に結合されたカソード端子、p+領域 208 に結合されたアノード端子、p+領域 208 と n+領域 202 との間に配置された p 領域 204、および p 領域 204 内に形成された、以下、本願明細書では集合的かつ代替的にトレンチ 206 と称する、多数のトレンチ 206<sub>1</sub>、206<sub>2</sub>、…、206<sub>N</sub>を含むように示されている。簡潔にするため、トレンチ 206<sub>1</sub>の左側に位置する p 領域は、参考番号 204<sub>1</sub>で識別され、トレンチ 206<sub>2</sub>の右側に位置する p 領域は、参考番号 204<sub>3</sub>で識別され、トレンチ 206<sub>1</sub>と 206<sub>2</sub>との間に位置する p 領域は、参考番号 204<sub>2</sub>で識別される。図 2 には 2 つのトレンチ 206<sub>1</sub>、206<sub>2</sub>のみが示されているが、本発明による高降伏電圧装置は、任意の数のトレンチ 206 を含み得ることが理解される。さらに、トレンチ 206 は、n+領域 202 内に延在するように示されている。

#### 【0022】

図 2B は、本発明の別の実施形態による、半導体 250 の断面図である。装置 250 は、装置 250 においては、n 型領域 252 が、n+領域 202 と p 領域 204 との間に配置されていることを除いて、装置 200 に類似したものである。このような実施形態では、トレンチ 206 は、n 型領域 252 内に延在する。以下では、同様な要素の異なる事例は、代替的に、異なる添字を有する同様な参考番号によって識別され、添字は、参考番号に対する下付数字として示される。例えば、トレンチ 206 の 2 つの示された事例は、206<sub>1</sub>および 206<sub>2</sub>として代替的に識別される。

#### 【0023】

一実施形態では、各トレンチ 206 は、1 つ以上の誘電体層 210 を含む。本発明によれば、各誘電体充填トレンチ 206 と p 領域 204 との間に配置された界面領域は、正電荷を含む。正電荷は、トレンチ 206 の内側、トレンチと p 型領域 204 との間の遷移領域(図示せず)内、p 領域 204 内、またはそれらの組み合わせ内に存在し得るものと理解される。本発明によれば、トレンチ 206<sub>1</sub>、206<sub>2</sub>の対向する面である 212<sub>1</sub>と 212<sub>2</sub>との間に存在する正の界面電荷は、これらの 2 つのトレンチの間に配置された p 領域 204<sub>2</sub>を、逆バイアスの下で部分的に、または完全に空乏化させるのに十分である。p 領域 204<sub>2</sub>の部分的な、または完全な空乏化によって、図 2B に示される線 × ×' に沿った電界は、これらの 2 つの端子間に外部から印加された逆バイアスの下で、比較的均一なままとなる。

#### 【0024】

逆バイアスで、正電荷は、空乏化された半導体の電圧維持領域内の電荷によって平衡化される。上述のように、正電荷は、一実施形態では、代表的な装置の動作温度で不動である。半導体構造体は、本発明によれば、多くの従来の SJ 構造体よりも小さく、より薄い電圧維持層を備えたセルピッチを達成する。さらに、従来の p-n 接合とは対照的に、誘電体層内で電荷を使用することによって、より低い静電容量が達成され、逆回復条件下で貯蔵される電荷がより少ない。本発明の構造体は、製作がより容易で、かつ費用効率がより高いものである。

#### 【0025】

図 2A を参照すると、p 領域 204<sub>2</sub>は、トレンチ 206 と p 領域 204<sub>2</sub>との間の界面領域内に存在する正電荷によって空乏化される。線 × ×' は、p 領域 204<sub>2</sub>の中央を横断するものと仮定する。したがって、表面 212<sub>1</sub>の近くに存在する正電荷は、p 領域 204<sub>2</sub>内の線 × ×' の左側に存在する負電荷によって平衡化される。同様に、表面 212<sub>2</sub>の近くに存在する正電荷は、p 領域 204<sub>2</sub>内の線 × ×' の右側に存在する負電荷によって平衡化される。したがって、線 × ×' に沿った電界は、ほぼ均一である。結果的に、p+領域 208、p 領域 204<sub>2</sub>、および n+領域 206<sub>2</sub>は、集合的に構造体を画定し、該構造体は、装置 200 のカソードとアノード端子との間に印加された逆電圧から p 領域 204<sub>2</sub>内への電界線の終端を抑制または低減する。正電荷は、例えば、セシウムまたはカリウム等の正イオンを、トレンチの壁または底部を覆う酸化物層内に注入することによって実現し得る。一実施例では、装置 200 は、それぞれ幅が 1 μm、深さ 10 μm である

10

20

30

40

50

トレンチを特徴とする。このような実施例では、隣接するトレンチ間の距離は、 $2 \mu m$ となり得、p型領域204のドープ濃度は、 $10^{16} atoms/cm^3$ となり得、また、トレンチ-半導体間の界面での電荷は、 $10^{12} cm^{-2}$ の密度( $Q_f/q$ )となり得、ここで、 $q$ は、電子電荷である。このような実施形態では、220ボルトの逆降伏電圧が達成され得る。トレンチ-半導体間の界面の電荷が無ければ、降伏電圧は、わずか34ボルトである。

【0026】

図2Cは、図2Aに示される線yy'に沿って示された、装置200の例示的な上面図である。206<sub>1</sub>、206<sub>2</sub>、および206<sub>3</sub>の3つのトレンチが、p領域204内に形成されているように示されているが、装置200は、本図に示されていない多数のトレンチを含み得るものと理解される。図2Dは、図2Aに示される線yy'に沿って示された、装置200の例示的な上面図である。本実施例によれば、p領域204は、上面が長方形である9つのトレンチ206を含むように示されている。図2Eは、トレンチ206が円形の上面を有するように示されている、装置200の別の例示的な上面図である。トレンチ206は、六角形等のような他のあらゆる上面を有し得るものと理解される。

【0027】

図2Fは、線yy'に沿って示された、装置200の別の例示的な上面図である。本実施例によれば、図2Fに示されるように、トレンチは、p領域204を複数の分離された領域に分割する。

【0028】

図3は、本発明の別の実施形態による、例示的な半導体装置300の断面図である。装置300は、装置300においては、トレンチ206がp+領域208の上面に延在していることを除いて、装置200に類似したものである。装置300は、その他の点では装置200の降伏特性に類似する、降伏特性を有する。

【0029】

図4は、本発明の別の実施形態による、例示的な半導体装置400の断面図である。装置400は、装置400においては、カソード端子がn+型領域408に結合され、アノード端子がp+領域402に結合されていることを除いて、装置200に類似したものである。装置400は、その他の点では装置200の降伏特性に類似する、降伏特性を有する。

【0030】

図5は、本発明の別の実施形態による、例示的な半導体装置500の断面図である。装置500は、装置500においては、トレンチ206がn+領域408の上面に延在していることを除いて、装置400に類似したものである。装置500は、その他の点では装置400の降伏およびオン抵抗特性に類似する、降伏およびオン抵抗特性を有する。

【0031】

図6Aは、本発明の別の実施形態による、例示的な半導体装置600の断面図である。装置600では、複数のトレンチ206は、複数のn型領域(ピラー)602内に形成され、次いで、これらはP型領域(ピラー)204内に形成される。例えば、示されるように、トレンチ206<sub>1</sub>がn型ピラー602<sub>1</sub>内に形成されているように示され、トレンチ206<sub>2</sub>がn型ピラー602<sub>2</sub>内に形成されているように示されている。交互するPおよびNピラー204、602は、隣接するトレンチの対向面内、およびそれらの空乏化されたN領域内の電荷の合計が、空乏化されたP領域内の負電荷に等しくなるように、超接合構造体を形成する。例えば、トレンチ206<sub>1</sub>および206<sub>2</sub>の対向面内、およびN領域602<sub>1</sub>および602<sub>2</sub>の空乏領域内の正電荷の合計は、これら2つのN領域間に配置されたP領域204の空乏領域内の負電荷の合計に実質的に等しい。装置600では、多量の正電荷が、固定トレンチ-半導体間の界面電荷によって供給され、したがって、従来のSJ装置と比較して、nピラーを使用することにより、装置600内の電荷平衡の達成が容易である。nピラーは、イオン注入または気相ドープを使用して形成し得る。また、装置600は、既存の構造体よりも改善されたキャリア移動度を提供し得る。図6Aに示されるよう

10

20

30

40

50

に、トレンチは、N領域602内に形成され、次いでP領域204内に形成される。図6Bは、本発明の別の実施形態による、例示的な半導体装置650の断面図である。実施形態650では、トレンチは、P型領域604内に形成され、次いでN型領域608内に形成される。

【0032】

図7は、本発明の別の実施形態による、例示的な半導体装置700の断面図である。装置700は、装置700においては、トレンチ206がp+領域208の上面に延在していることを除いて、装置600に類似したものである。装置700は、その他の点では装置600の降伏およびオン抵抗特性に類似する、降伏およびオン抵抗特性を有する。

【0033】

図8は、本発明の別の実施形態による、例示的な半導体装置800の断面図である。装置800は、装置800においては、トレンチの上部近くの幅がトレンチの底部よりも広くなるようにテーパ状であることを除いて、装置300に類似したものである。トレンチは、設計により、またはトレンチの形成に使用され得る処理ステップもしくはエッチング等のような機器の結果として、のいずれかによってテーパ状にされる。したがって、装置800では、半導体内の不純物のドーププロファイルがこの影響を排除するように調節されない限りは、電界は、トレンチ206の上部近くよりも、トレンチ206の底部近くの方が高くなる。

【0034】

図9は、本発明の別の実施形態による、例示的な半導体装置900の断面図である。装置900では、各トレンチ206は、2つの異なる層、すなわち、第1の層902および第2の層904を含むように示されている。第2の層904は、固定電荷を生成するために使用されるか、またはp領域204の空乏化に使用される電荷が、装置の製作中に、表面212の近くに確実に保持されるように、キャップ層として使用されるか、のいずれかである。

【0035】

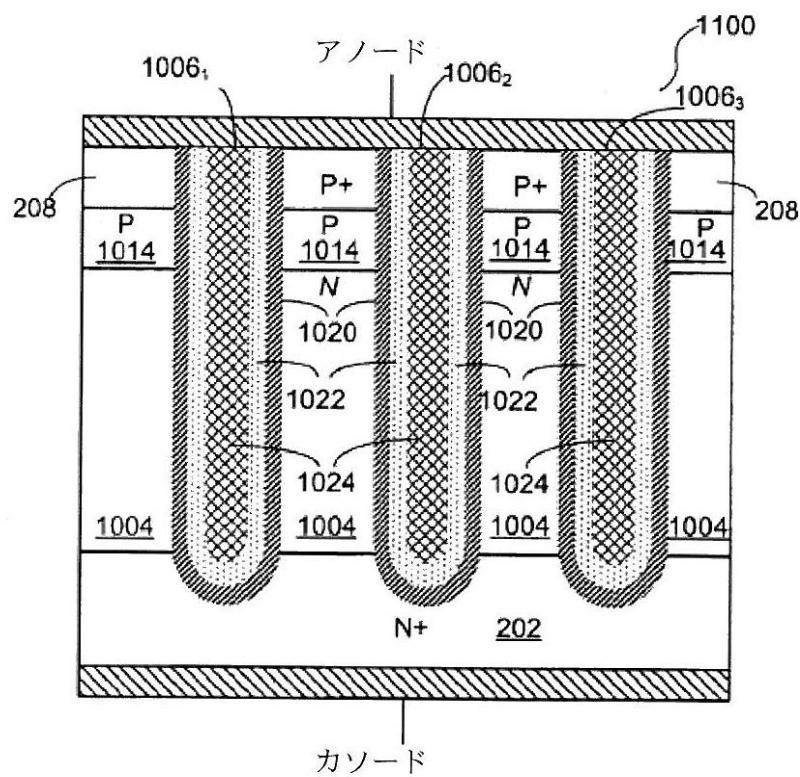

本発明のいくつかの実施形態によれば、トレンチは、トレンチが部分的に形成されたN領域を空乏化するように適合された負電荷を含む材料を含む。図10は、本発明の一実施形態による、半導体装置1000の断面図である。装置1000は、n+領域202に結合されたカソード端子と、p領域1014を覆うp+領域208に結合されたアノード端子と、N+領域202を覆うN領域1004内に形成された、以下、本願明細書では集合的かつ代替的にトレンチ1006と称する、多数のトレンチ1006<sub>1</sub>、1006<sub>2</sub>、…、1006<sub>N</sub>とを含むように示されている。図10には3つのトレンチ1006<sub>1</sub>、1006<sub>2</sub>、および1006<sub>3</sub>のみが示されているが、本発明による高降伏電圧装置は、任意の数のトレンチ1006を含み得るものと理解される。さらに、トレンチ1006は、n+領域202内に延在しているように示されているが、他の実施形態では、トレンチ1006は、n+領域202内に延在しない場合もあるものと理解される。

【0036】

図10に示された例示的な実施形態では、各トレンチ1006は、第1の誘電体層1008と、第2の層1010とを含むように示されている。一実施形態では、第2の層1010は、誘電体材料を含む場合も含まない場合もある多くの材料を含む。図10に示しているように、各トレンチ1006と、隣接するN領域1004との間に配置された界面領域は、負電荷を含む。さらに、本発明によれば、隣接するトレンチの対向する面の間に存在する負の界面電荷は、このような隣接するトレンチ間に配置されたN領域1004を、逆バイアスの下で完全に、または部分的に空乏化させるのに十分である。例えば、隣接するトレンチ1006<sub>1</sub>および1006<sub>2</sub>内に存在する負電荷は、これら2つのトレンチの間に配置されたN領域1004を、逆バイアスで空乏化させるのに十分である。N領域1004<sub>2</sub>の空乏化は、アノード端子とカソード端子との間に、有効な半導体-絶縁体-半導体構造体を提供することによって、電界線を制限する。制限しなければ、電界線は、これらの2つの端子間に外部から印加された逆電圧から空乏化されたN領域1004内へ終端す

10

20

30

40

50

るであろう。

【0037】

一実施形態では、n型領域1004は、高濃度ドープのn+基板202全面上に成長したエピタキシャル層である。一実施形態では、n型エピタキシャル層1004は、均一にドープされる。別の実施形態では、n型エピタキシャル層1004は、不均一にドープされる。例えば、ドーピングプロファイルは、表面と比較して基板において高濃度ドープを有するように、またはその逆になるように傾斜させることができる。

【0038】

図10に示された実施形態では、第1の誘電体材料1008、例えば熱成長した酸化物層は、トレンチの底部または壁に沿って形成される。一実施形態では、第1の誘電体材料は、厚さが、約2nmから約200nmまでの範囲である。例えば、第1の誘電体材料の厚さは、約30nmでもよい。トレンチ1006は、トレンチの内側領域内にあり、第1の誘電体材料1008内に封入された、1つ以上の材料/化合物層であってもよい、第2の材料1010を含むように示されている。フッ化アルミニウムであってもよい第2の材料1010は、AlFx層と第1の誘電体材料1008との間の界面で負電荷を提供する。

【0039】

図11は、本発明の別の実施形態による、半導体装置1100の断面図である。装置1100は、装置1100においては、各トレンチ1006が、第1の誘電体層1020と、第2の層1022と、第3の層1024とを含むように示されていることを除いて、装置1100に類似したものである。一実施形態では、各第3の層1024は、誘電体材料を含む場合も含まない場合もある多くの材料を含む。実施形態1100は、その他の点では実施形態1000に類似している。

【0040】

装置1100では、各トレンチ1006は、誘電体層である第1の層1020と、第2の層1022と、誘電体層である第3の層1024とを含む。第1の層1020は、トレンチの壁および底部上に形成される。第2の層1022は、2つ以上の材料を含んでも良く、第1の層1020内に封入されるように形成される。第3の層1024は、第2の層1022内に封入されるように形成される。一実施形態では、第3の層1024は、第1の層1020と同じ材料から形成される。別の実施形態では、第1および第2の誘電体層は、異なる材料を使用して形成される。2つの誘電体層1020と1024との間に、例えばフッ化アルミニウムを含み得る層1022を配置することで、誘電体層1020、1024と層1022との間の界面に負電荷を提供する。装置1100の種々のn+、p+、n、およびp型層は、注入、拡散、アニーリング等の従来の製作工程を使用して形成される。

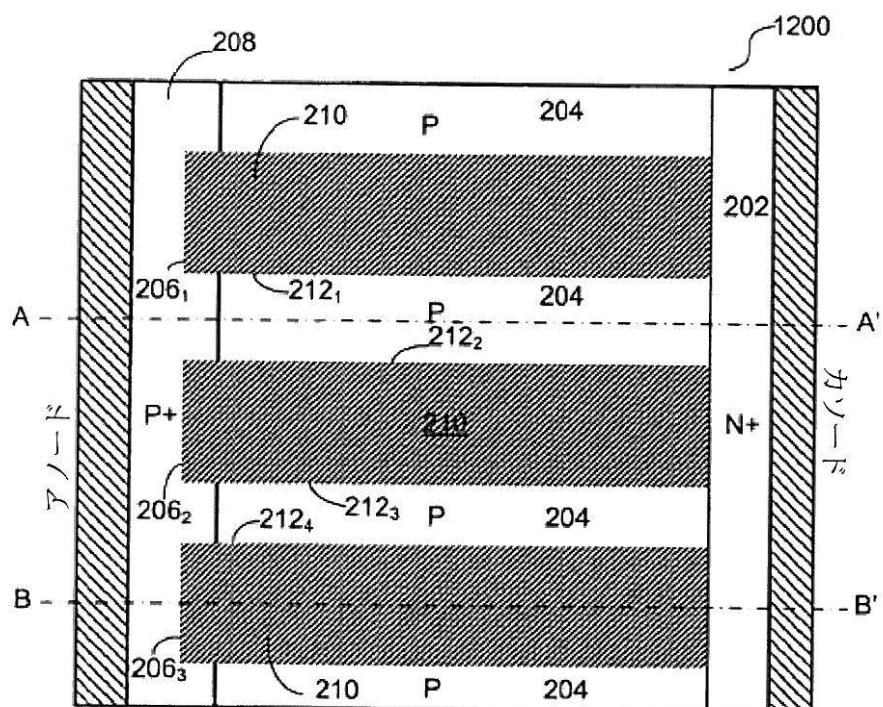

【0041】

図12Aは、本発明の別の実施形態による、横型高電圧半導体装置1200の簡素化した上面図である。装置1200は、n+領域202に結合されたカソード端子と、p+領域208に結合されたアノード端子と、p+領域208とn+領域202との間に配置されたp型領域204と、p領域204内に形成された、以下、本願明細書では集合的かつ代替的にトレンチ206と称する、多数のトレンチ206<sub>1</sub>、206<sub>2</sub>、…、206<sub>N</sub>とを含むように示されている。図12Aには3つのトレンチ206<sub>1</sub>、206<sub>2</sub>、および206<sub>3</sub>のみが示されているが、本発明による高降伏電圧装置は、任意の数のトレンチ206を含み得るものと理解される。

【0042】

一実施形態では、各トレンチ206は、1つ以上の誘電体層210を含む。本発明によれば、正電荷は、トレンチ206内に意図的に導入される。このような電荷は、トレンチ内、トレンチとp型領域204との間の遷移領域内、P領域204内、またはそれらの組み合わせで存在しても良く、これらは、集合的かつ代替的に界面電荷と称する。トレンチの対向する面の間に存在するこのような正の界面電荷は、このような2つのトレンチの間

10

20

30

40

50

に配置されたp領域204を、逆バイアスで部分的に、または完全に空乏化させるのに十分である。例えば、トレンチ206<sub>1</sub>、206<sub>2</sub>の対向する面212<sub>1</sub>および212<sub>2</sub>の近くに存在する電荷は、これらの2つのトレンチの間に配置されたp型領域2042を、逆バイアスで部分的に、または完全に空乏化させるのに十分である。同様に、トレンチ206<sub>2</sub>、206<sub>3</sub>の対向する面212<sub>3</sub>および212<sub>4</sub>の近くに存在する電荷は、これらの2つのトレンチの間に配置されたp型領域204を、逆バイアスで部分的に、または完全に空乏化させるのに十分である。逆バイアスでのp型領域204の部分的な、または完全な空乏化によって、例えば対向面212<sub>1</sub>と212<sub>2</sub>との間に位置する線AA'に垂直な平面に沿った電界は、カソードとアノード端子との間に外部から印加された逆バイアスの下で、比較的均一なまとなる。逆バイアスで、正の界面電荷は、P型領域204の空乏電荷内の電荷によって平衡化される。上述のように、正電荷は、一実施形態では、代表的な装置の動作温度で不動である。

#### 【0043】

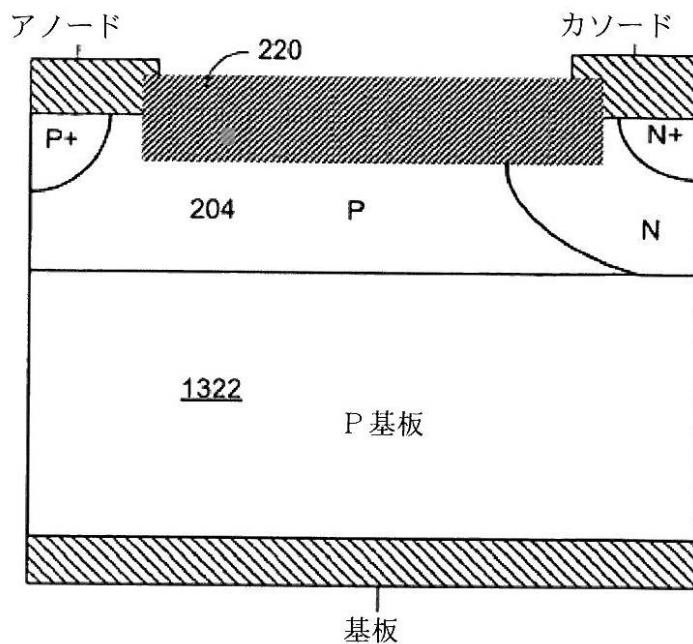

図12Bは、線AA'に沿った構造体1200の簡素化した断面図である。図12Bを参照すると、p型領域204は、逆バイアスの下で、完全に、または部分的に空乏化される。誘電体層220は、構造体全体を覆い、半導体装置の不動態化に使用される。図12Cは、トレンチ206<sub>3</sub>および装置1200の種々の他の領域を示す、線BB'に沿った構造体1200の簡素化した断面図である。

#### 【0044】

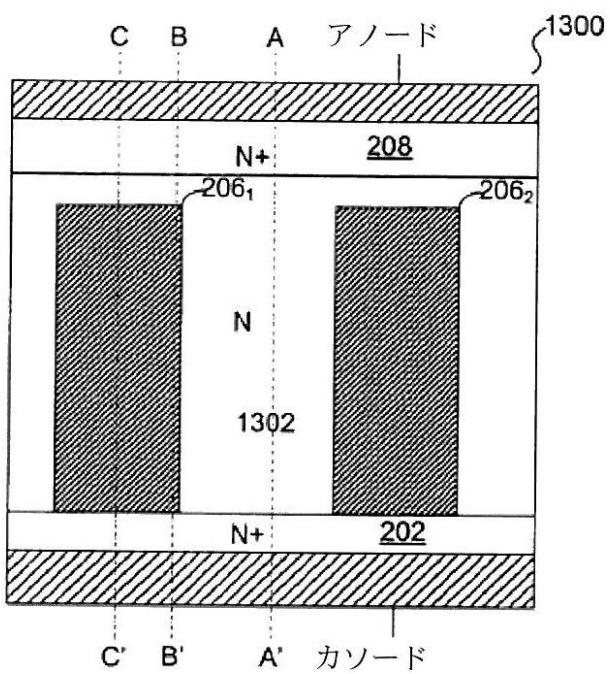

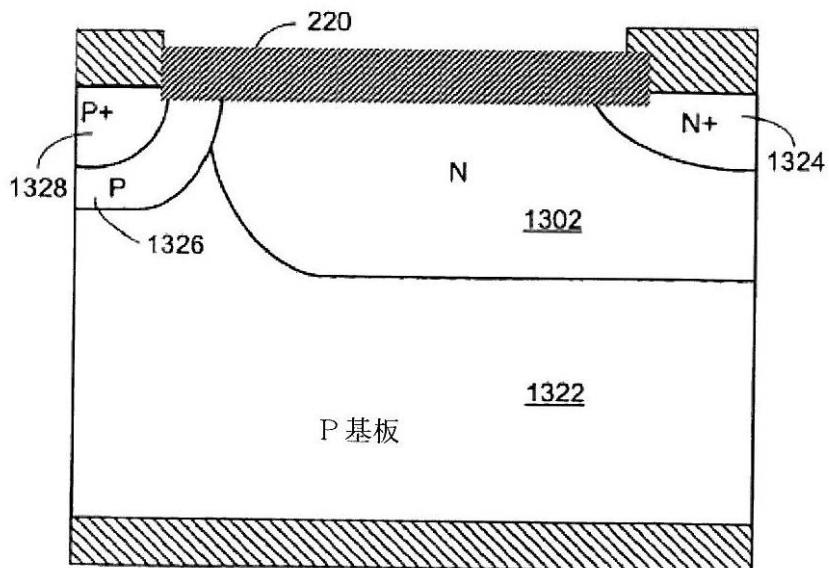

図13Aは、本発明の別の実施形態による、横型高電圧半導体装置1300の簡素化した上面図である。装置1300は、n+領域202に結合されたカソード端子と、n+領域208に結合されたアノード端子と、n+領域208、202の間に配置されたn型領域1302と、n型領域1302内に形成された、以下、本願明細書では集合的かつ代替的にトレンチ206と称する、多数のトレンチ206<sub>1</sub>、206<sub>2</sub>、…、206<sub>N</sub>とを含むように示されている。図13Aには2つのトレンチ206<sub>1</sub>、206<sub>2</sub>のみが示されているが、本発明による高降伏電圧装置は、任意の数のトレンチ206を含み得るものと理解される。図13Bは、線AA'に沿った構造体1300の断面図である。図13Bを参照すると、n型領域1302は、逆バイアスの下で、完全に、または部分的に空乏化される。誘電体層220は、構造体全体を覆い、半導体装置の不動態化に使用される。

#### 【0045】

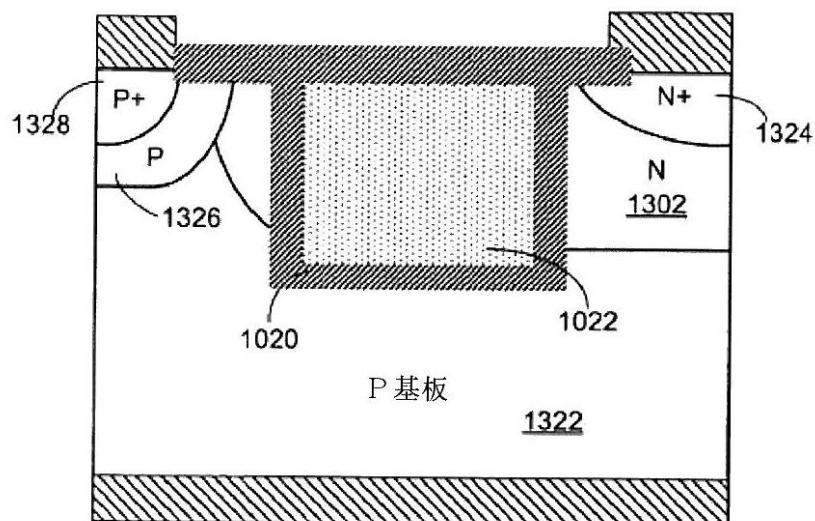

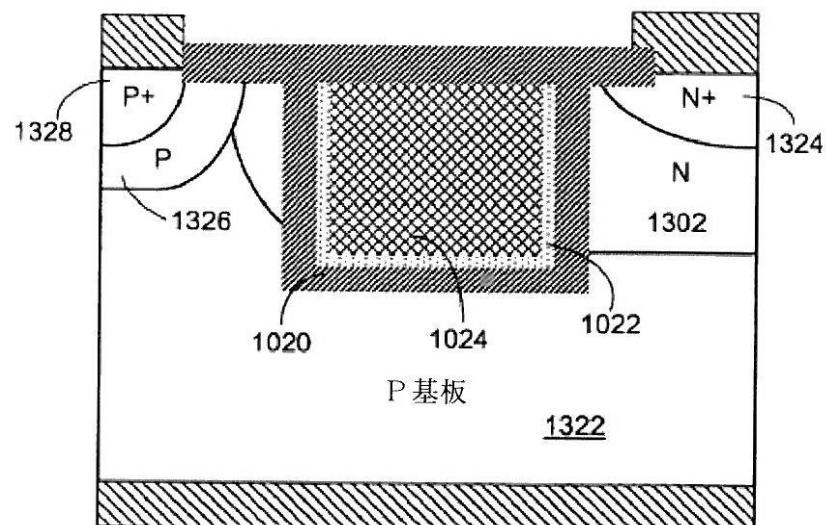

図13Cおよび13Dは、線BB'およびCC'に沿った半導体装置1300の断面図である。装置1300は、装置1300においては、各トレンチ1006が、第1の誘電体層1020と、第2の層1022と、第3の層1024とを含むように示されていることを除いて(図13D)、装置1200に類似したものである。さらに、装置1200とは異なり、装置1300では、トレンチは、N領域1302を空乏化するために負電荷を含むように形成される。一実施形態では、各第3の層1024は、誘電体材料を含む場合も含まない場合もある多くの材料を含む。

#### 【0046】

装置1300では、また、上述のように、各トレンチ1006は、誘電体層である第1の層1020と、第2の層1022と、誘電体層である第3の層1024とを含む。第1の層1020は、トレンチの壁および底部上に形成される。第2の層1022は、2つ以上の材料を含んでも良く、第1の層1020内に封入されるように形成される。第3の層1024は、第2の層1022内に封入されるように形成される。一実施形態では、第3の層1024は、第1の層1020と同じ材料から形成される。別の実施形態では、第1および第2の誘電体層は、異なる材料を使用して形成される。2つの誘電体層1020と1024との間に、例えばフッ化アルミニウムを含み得る層1022を配置することで、誘電体層1020、1024と層1022との間の界面に負電荷を提供する。装置1300の種々の層は、注入、拡散、アニーリング等の従来の製作工程を使用して形成される。

#### 【0047】

図14は、本発明の別の実施形態による、横型高電圧半導体装置1400の簡素化した

10

20

30

40

50

上面図である。装置 1400 は、装置 1400 においては、p 基板内で生成された空乏電荷を補うように、アノード端子近くの幅が、カソード端子近くよりも広くなるようにテープ状であることを除いて、装置 1200 に類似したものである。

【 0048 】

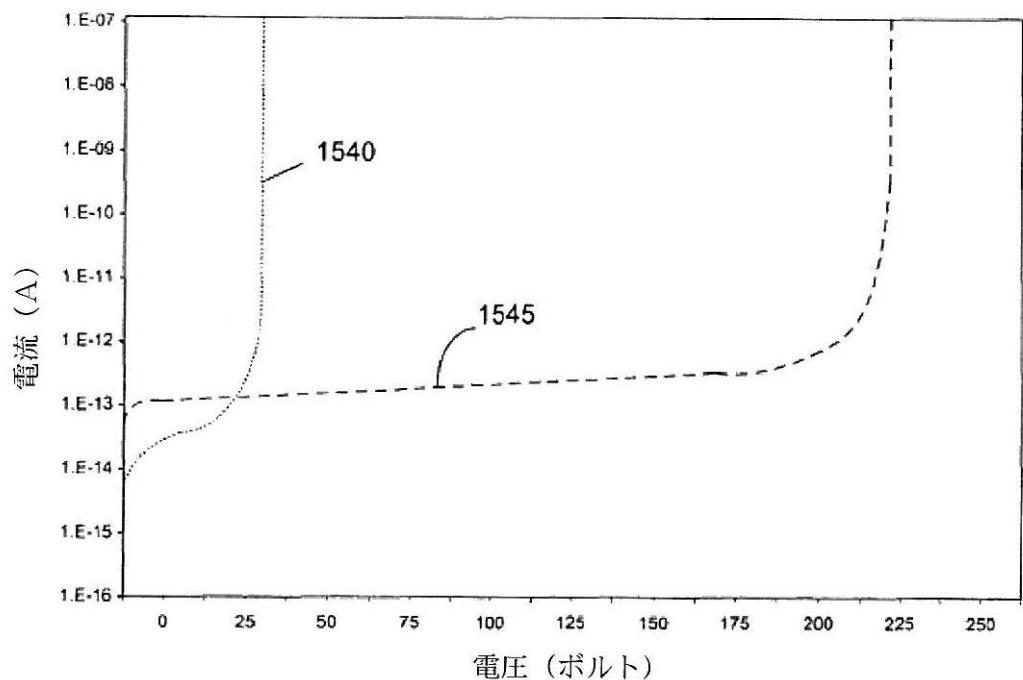

図 15A および 15B は、それぞれ、従来の構造体 1510、および本発明の例示的な一実施形態による構造体 1520 の、降伏電圧での等電位線を示している。各等値線は、このシミュレーションでは 10 ボルトを表す。構造体 1510 は、ダイオードの関連するアノード端子とカソード端子との間に配置された半導体領域 1502 を含む。構造体 1520 は、トレンチ 206 を含むように示されている。本発明によれば、電荷密度 ( $Q_f / q$ ) ( $q$  は、電子電荷である) が  $1 \times 10^{12} \text{ cm}^{-2}$  である正の界面電荷は、トレンチ 206 および P 領域 204 の界面に存在する。本シミュレーションには、トレンチ 206 の幅  $1 \mu\text{m}$  と、アノードからカソードまでの距離  $10 \mu\text{m}$  を使用した。半導体領域 1502 および 204 のドープレベルは、 $2 \times 10^{16} \text{ cm}^{-3}$  とした。本シミュレーションによれば、従来の構造体 1510 の降伏電圧は約 34 ボルトであるが、一方で、本発明の構造体 1520 の降伏電圧は 220 ボルトである。

【 0049 】

図 15C は、図 15A ~ 図 15B に示される構造体の断面線 AA' に沿った電界を示している。構造体 1510 の電界分布は、線図 1530 を使用して示されている。構造体 1520 の大幅に改善された電界分布は、線図 1535 を使用して示されている。逆バイアスでの p 型領域 204 の部分的な、または完全な空乏化によって、互いに対向する面 212 と 212 との間に位置する線 AA' に沿った電界は、カソード端子とアノード端子との間に外部から印加された逆バイアスの下で、比較的均一なままとなる。構造体 1510 の場合、逆バイアスの下で、領域 1502 内のイオン化したドーパントからの電界は、アノードで終端し、それによって、電界は三角形のプロファイルを生じる。

【 0050 】

図 15D は、構造体 1510 (線図 1540) および 1520 (線図 1545) の逆バイアス電流対電圧特性を示している。示されるように、構造体 1510 の降伏電圧は 34 ボルトであり、構造体 1520 の降伏電圧は 220 ボルトである。

【 0051 】

上述の本発明の実施形態は、例示的なものであり、制限するものではない。種々の代替案および均等物が生じ得る。本発明は、本開示を配置し得る装置または集積回路の種類によって制限されるものではない。また、本開示は、本開示の製造に使用され得る、例えば CMOS、バイポーラ、または BICMOS 等の、いかなる特定の種類の工程技術にも制限されない。他の追加、除去、または変更は、本開示に照らして明らかであり、また、添付の特許請求の範囲内にあるように意図されている。

【図 2 C】

FIG. 2C

【図 2 D】

FIG. 2D

【図 2 E】

FIG. 2E

【図 2 F】

FIG. 2F

【図1】

【図2A】

【図2B】

【図3】

【図4】

【図5】

【図 6 A】

【図 6 B】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12A】

【図 1 2 B】

【図 1 2 C】

【図 1 3 A】

【図 1 3 B】

【図 1 3 C】

【図 1 3 D】

【図14】

【図15A】

【図 1 5 B】

【図 1 5 C】

【図 15 D】

---

フロントページの続き

審査官 小川 将之

(56)参考文献 国際公開第03/065459 (WO, A1)

特開2004-047599 (JP, A)

特開平02-156552 (JP, A)

特開2005-064429 (JP, A)

特開2003-282892 (JP, A)

特表2003-523087 (JP, A)

特開2004-146689 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/861

H01L 29/868

H01L 29/06