(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3930644号

(P3930644)

(45) 発行日 平成19年6月13日(2007.6.13)

(24) 登録日 平成19年3月16日(2007.3.16)

(51) Int.C1.

F 1

G O 1 T 1/20 (2006.01)

G O 1 T 1/00 (2006.01)G O 1 T 1/20

G O 1 T 1/00

Z

B

請求項の数 4 (全 9 頁)

(21) 出願番号

特願平10-199171

(22) 出願日

平成10年7月14日(1998.7.14)

(65) 公開番号

特開2000-28736 (P2000-28736A)

(43) 公開日

平成12年1月28日(2000.1.28)

審査請求日

平成17年3月14日(2005.3.14)

(73) 特許権者 000236436

浜松ホトニクス株式会社

静岡県浜松市市野町1126番地の1

(74) 代理人 100088155

弁理士 長谷川 芳樹

(74) 代理人 100089978

弁理士 塩田 辰也

(74) 代理人 100092657

弁理士 寺崎 史朗

(72) 発明者 久嶋 龍次

静岡県浜松市市野町1126番地の1 浜

松ホトニクス株式会社内

(72) 発明者 森 治通

静岡県浜松市市野町1126番地の1 浜

松ホトニクス株式会社内

最終頁に続く

(54) 【発明の名称】 X線パネルセンサ

## (57) 【特許請求の範囲】

## 【請求項 1】

入射したX線像を蛍光像に変換するシンチレータ及び前記シンチレータにより変換された蛍光像を撮像するMOS型イメージセンサを備えたX線パネルセンサにおいて、前記MOS型イメージセンサがその上側に固定される第1配線基板と、グランド電位を有する第1金属薄膜をその上下面間に有し、前記第1配線基板の下側に対向すると共に前記第1配線基板に電気的に接続されるように配置された第2配線基板と、前記第1及び第2配線基板間に介在しグランド電位を有するX線遮蔽板と、前記第2配線基板の上面側に設けられ前記MOS型イメージセンサからの出力信号をアナログ処理するアナログ回路と、前記第2配線基板の下面側に設けられ前記MOS型イメージセンサの駆動信号のタイミングを生成するデジタル回路と、を備え、

前記第2配線基板はグランド電位を有する第2金属薄膜をその上下面間に有し、前記第1及び第2金属薄膜はそれぞれ前記アナログ回路及び前記デジタル回路のグランドにそれぞれ電気的に接続されていることを特徴とするX線パネルセンサ。

## 【請求項 2】

前記第1及び第2配線基板間に介在して前記第1配線基板を前記第2配線基板上に支持すると共に、前記MOS型イメージセンサの出力信号を前記アナログ回路に伝送し、前記デジタル回路の出力信号を前記MOS型イメージセンサに伝送するコネクタを更に備えることを特徴とする請求項1に記載のX線パネルセンサ。

## 【請求項 3】

10

前記シンチレータと前記MOS型イメージセンサとの間に介在し、鉛を含有するファイバオプティカルプレートを更に備えることを特徴とする請求項1に記載のX線パネルセンサ。

#### 【請求項4】

前記第1配線基板上に配置される前記MOS型イメージセンサのための電子素子と、前記ファイバオプティカルプレートの周囲に配置され、前記電子素子を入射X線像のX線から遮蔽する枠体を更に備えることを特徴とする請求項3に記載のX線パネルセンサ。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

10

本発明は、X線イメージを撮像するX線パネルセンサに関する。

##### 【0002】

##### 【従来の技術】

従来のX線パネルセンサは、特開平9-288184号公報に記載されている。このセンサは、半導体イメージセンサをシンチレータの下に設けてX線検出を行っている。

##### 【0003】

##### 【発明が解決しようとする課題】

しかしながら、上記従来のX線パネルセンサでは良質な画像を得ることができない。すなわち、半導体イメージセンサの出力信号には、蛍光体を透過したX線によるノイズ及び半導体イメージセンサの高周波駆動信号及び外部からのノイズが重畠される場合がある。特に、半導体イメージセンサが大型のMOS型イメージセンサである場合には、出力信号を伝送するビデオラインが長くなるため、出力信号にノイズが重畠しやすくなり、このようなノイズは画像の劣化を招く。本発明はかかる課題に鑑みてなされたものであり、従来に比して更に良質の画像を得ることができるX線パネルセンサを提供することを目的とする。

20

##### 【0004】

##### 【課題を解決するための手段】

上記課題を解決するため、本発明に係るX線パネルセンサは、入射したX線像を蛍光像に変換するシンチレータ及びシンチレータにより変換された蛍光像を撮像するMOS型イメージセンサを備えたX線パネルセンサにおいて、MOS型イメージセンサがその上側に固定される第1配線基板と、グランド電位を有する第1金属薄膜をその上下面間に有し、第1配線基板の下側に対向すると共に第1配線基板に電気的に接続されるように配置された第2配線基板と、第1及び第2配線基板間に介在しグランド電位を有するX線遮蔽板と、第2配線基板の上面側に設けられMOS型イメージセンサからの出力信号をアナログ処理するアナログ回路と、第2配線基板の下面側に設けられ前記MOS型イメージセンサの駆動信号のタイミングを生成するデジタル回路とを備え、第2配線基板はグランド電位を有する第2金属薄膜をその上下面間に有し、第1及び第2金属薄膜はそれぞれアナログ回路及びデジタル回路のグランドにそれぞれ電気的に接続されていることを特徴とする。

30

##### 【0005】

本発明のX線パネルセンサによれば、MOS型イメージセンサからの出力信号をアナログ処理するアナログ回路は、第2配線基板の上面側に配置され、また、共にグランド電位を有する第2配線基板の第1金属薄膜とX線遮蔽板との間に配置される。

40

##### 【0006】

本発明のX線パネルセンサによれば、アナログ回路を介して出力されるMOS型イメージセンサの出力信号に重畠されるべきノイズ、すなわち、上側からアナログ回路に入射するX線のノイズ及び下側からアナログ回路に伝搬してくるデジタル回路及び外部からのノイズは、それぞれX線遮蔽板及び第1金属薄膜によって抑制される。

##### 【0007】

従来、MOS型イメージセンサの大型化に伴うノイズの増加が、画像劣化を引き起こしていたため、良質な画像を得ることができる大型のMOS型イメージセンサを搭載したX線

50

パネルセンサを実現することができなかった。

【0008】

一方、本発明によれば、そのノイズを低下させることにより、大型のMOS型イメージセンサ（例えば縦横寸法 = 50 mm × 50 mm）を搭載したX線パネルセンサを実現することができ、しかも、第1配線基板と第2配線基板とを対向させて配置し、第2配線基板の上下面にアナログ及びデジタル回路を搭載することとしたので、X線パネルセンサ全体の寸法は小型化することができる。なお、本発明は小型のMOS型イメージセンサを搭載したX線パネルセンサにも適用することが可能である。

【0009】

なお、上述のように、第2配線基板はグランド電位を有する第2金属薄膜をその上下面間に有し、第1及び第2金属薄膜はそれぞれアナログ回路及びデジタル回路のグランドにそれぞれ電気的に接続されていることが望ましい。第1及び第2金属薄膜は、上述のノイズ遮蔽機能を達成すると共に、これらがアナログ回路及びデジタル回路に対応してそれぞれ設けられていることにより、双方の回路の安定化を達成することができる。

10

【0010】

更に、本発明のX線パネルセンサは、第1及び第2配線基板間に介在して第1配線基板を第2配線基板上に支持すると共に、MOS型イメージセンサの出力信号をアナログ回路に伝送し、デジタル回路の出力信号をMOS型イメージセンサに伝送するコネクタを更に備えることが望ましい。この場合、上記機能を果たすコネクタ自体が、第1配線基板を第2配線基板上に支持するので、構造上の強度が増加すると共に部品点数を減少させることができる。

20

【0011】

また、X線パネルセンサが、シンチレータとMOS型イメージセンサとの間に介在し、鉛を含有するファイバオプティカルプレートを更に備えることとすると、シンチレータで変換されなかったX線をMOS型イメージセンサの受光面に到達する前に遮蔽することができる。

【0012】

さらに、X線パネルセンサが、第1配線基板上に配置されるMOS型イメージセンサのための電子素子と、ファイバオプティカルプレートの周囲に配置され、電子素子を入射X線像のX線から遮蔽する枠体を更に備えることとすれば、この電子素子は、ファイバオプティカルプレートの周囲に配置された枠体によりX線から遮蔽することができる。

30

【0013】

【発明の実施の形態】

以下、実施の形態に係るX線パネルセンサについて説明する。同一要素又は同一機能を有する要素には同一符号を用いるものとし、重複する説明は省略する。

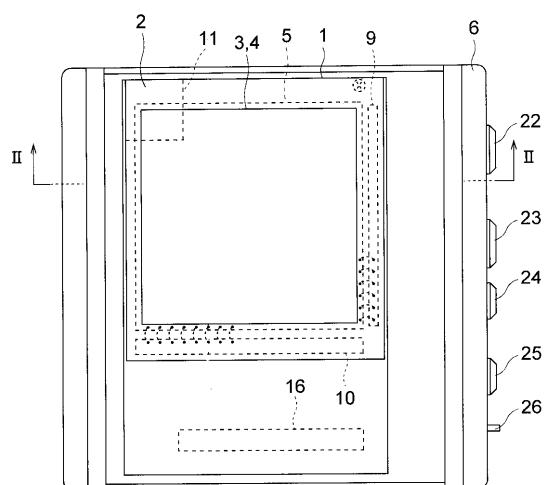

【0014】

図1はX線パネルセンサの平面図であり、図2は図1に示したX線パネルセンサのI-I'矢印断面図である。

【0015】

本X線パネルセンサは、Cu/Ni/Auからなる配線が形成された配線基板1上に固定された枠体2と、枠体2の内縁にその外縁が接着され、鉛をシリカガラス中に含むファイバオプティカルプレート3と、ファイバオプティカルプレート3の一方の表面に設けられ入射したX線を蛍光に変換するシンチレータ（蛍光体）4と、ファイバオプティカルプレート3の他方の表面に対向して配線基板1上に設けられた半導体イメージセンサ5（MOS型イメージセンサ）とを備えている。枠体2は、その内縁でファイバオプティカルプレート3を固定するために、ファイバオプティカルプレート3と略同じ、若しくは若干大きな面積を有する矩形状の開口を有している。また、ファイバオプティカルプレート3の光軸はMOS型イメージセンサ5の受光面に垂直である。

40

【0016】

上記部材は鉄製の筐体6内部に配置され、筐体6の上面にはX線入射領域を規定する矩形

50

開口を有する蓋部材 7 が設けられ、この蓋部材 7 には X 線入射領域に設けられた窓材 8 が内面側から固定されている。すなわち、蓋部材 7 は X 線を遮蔽する厚さ約 1 mm の金属 (Fe) から形成され、窓材 8 は X 線を透過させる厚さ約 0.5 mm の樹脂 (ポリカーボネイト) から形成されている。なお、配線基板 1 を透過する X 線が低減されるように、基板裏面側には Cu / Ni / Au からなる遮蔽膜が形成されている。

#### 【0017】

MOS型イメージセンサ 5 は、2次元状に配置された複数のフォトダイオードと、光の入射に応答してそれぞれのフォトダイオードで発生した電荷の読み出しを制御するための複数の MOSFET (電界効果トランジスタ) とからなる受光領域と、その周辺部に配置された電極パッドとを備えている。配線基板 1 上には MOSFET の駆動制御を行うためのシフトレジスタ 9 と、MOS型イメージセンサ 5 の出力を増幅する電子素子としての増幅素子 (アンプアレイ) 10 がペアチップの状態で設けられ、それぞれボンディングワイヤにより MOS イメージセンサの電極パッドに電気的に接続されている。ここで、MOS型イメージセンサ 5 、シフトレジスタ 9 、アンプアレイ 10 と配線基板 1 との間には導電性フィラーを含む熱硬化性樹脂 (エポキシ系樹脂) が介在しており、これらは配線基板 1 上の配線と電気的に接続されると同時に物理的に固定されている。

#### 【0018】

配線基板 1 は、A 1 からなる複数のスペーサ 11, 12 及び信号処理基板 (第 2 配線基板) 13 上から上方に立設したコネクタ 16 を介して信号処理基板 13 に固定されている。信号処理基板 13 は A 1 からなる複数のスペーサ 14, 15 を介して筐体 6 の底面に固定されている。コネクタ 16 は、配線基板 1 と信号処理基板 13 とを電気的に接続するものである。なお、装置全体の小型化のために、MOS イメージセンサ 5 は、その 1 つの角部が配線基板 1 の角部の近傍に位置するように配置されている。したがって、この位置には、ネジ止めの必要なスペーサを設けることはできないため、この位置において配線基板 1 と信号処理基板 13 との間に介在するスペーサ 11 は、ブロック形状とした。

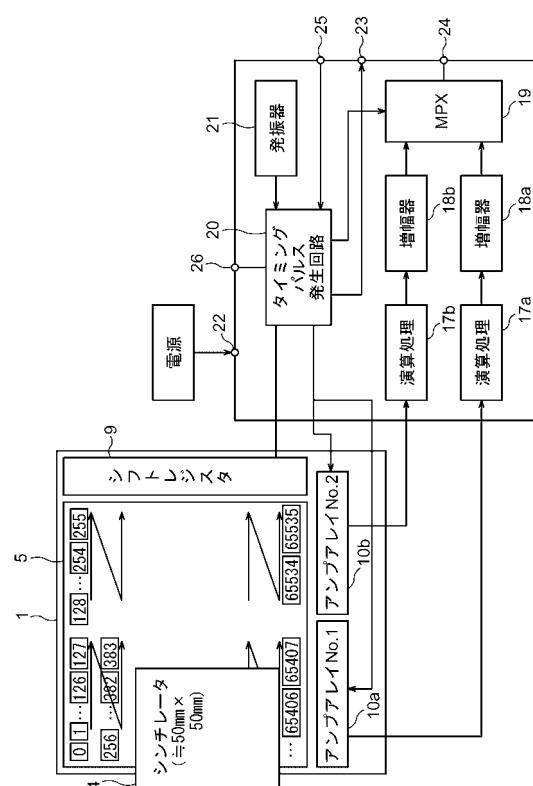

#### 【0019】

図 3 は、図 1 に示した X 線パネルセンサの回路構成図である。以下、図 1 及び図 2 を参照しつつ、X 線パネルセンサの回路構成について説明する。信号処理基板 13 の一方面上には、アンプアレイ 10 から出力された映像信号に所定の演算処理を行う演算処理回路 17a, 17b、演算処理回路 17a, 17b の出力を増幅する増幅器 18a, 18b、及び増幅器 18a, 18b の出力を 2 分の 1 周期ずらして合成するマルチプレクサ 19 等のアナログ回路が設けられている。

#### 【0020】

MOS型イメージセンサ 5 の受光面は、水平方向のアドレス 0 番地から 127 番地までの行とこれに垂直な列で規定される第 1 受光領域と、水平方向のアドレス 128 番地から 255 番地までの行とこれに垂直な列で規定される第 2 受光領域とから構成されている。なお、それぞれのアドレスには信号電荷を読み出すための MOSFET が配置されている。それぞれの受光領域内のフォトダイオードからの信号の読み出しは、シフトレジスタ 9 によって MOSFET を制御することにより同時進行で行われ、フォトダイオードからの信号読み出しは高速化されている。

#### 【0021】

アンプアレイ 10 は、MOS型イメージセンサ 5 の第 1 及び第 2 受光領域からの出力信号をタイミングパルス発生回路 20 からの同期信号に基づいてそれぞれ増幅する第 1 アンプアレイ 10a 及び第 2 アンプアレイ 10b から構成されている。演算処理回路 17a, 17b 及び増幅器 18a, 18b は、アンプアレイ 10a, 10b にそれぞれ対応して設けられている。アンプアレイ 10a, 10b は配線基板 1 上に設けられているので、MOS型イメージセンサ 5 とアンプアレイ 10a, 10b とを近接させることができ、これらの接続配線に重畠されるノイズを低減させ、良質な画像を得ることができる。アンプアレイ 10a, 10b を近接させた場合においても、入射 X 線の影響は撮像時に低減されることが望ましい。そこで、枠体 2 は、X 線を遮蔽する金属 (A 1 又は原子量の大きな金属) で

10

20

30

40

50

作製されることとし、アンプアレイ 10 は金属によって X 線の入射が遮蔽される位置に設けられている。

【 0 0 2 2 】

同時に、枠体 2 は、MOS 型イメージセンサ 5 の電極パッド、アンプアレイ 10a, 10b、シフトレジスタ 9 を覆っているため、電極パッドとアンプアレイ 10a, 10b、及び電極パッドとシフトレジスタとを接続するボンディングワイヤを外的負荷から保護している。

【 0 0 2 3 】

信号処理基板 13 の他方面には、シフトレジスタ 9 及びアンプアレイ 10a, 10b に信号の読み出しタイミング及び信号増幅タイミングをそれぞれ与え、これらから構成される駆動信号を発生するタイミングパルス発生回路 20、及びタイミングパルス発生回路 20 の基準クロックを生成する発振器 21 等のデジタル回路が設けられている。

10

【 0 0 2 4 】

マルチブレクサ 19 は、タイミングパルス発生回路 20 から出力される同期信号に同期して増幅器 18a, 18b の出力を 2 分の 1 周期ずらして合成する。マルチブレクサ 19 から出力された映像信号は、映像信号出力端子 24 から出力される。なお、筐体 6 には、この他にタイミングパルス発生回路 20 駆動のためのトリガ信号を装置内部で発生するか、外部で発生するかを切り換える切換スイッチ 26、外部からトリガ信号を入力する場合の外部トリガ信号入力端子 25、タイミングパルス発生回路 20 から出力された同期信号を出力する同期信号出力端子 23、及び装置全体に電源を供給するための電源コネクタ 22 が設けられている。

20

【 0 0 2 5 】

本実施の形態に係る X 線パネルセンサによれば、窓材 8 を介してセンサ内に X 線が入射すると、シンチレータ 4 が X 線の入射に応答して蛍光発光する。この蛍光は、複数の光ファイバの集合体であるファイバオプティカルプレート 3 内を、隣接光ファイバ間を通過する光と混合することなく、その光軸方向に沿って伝搬し、MOS 型イメージセンサ 5 の受光面に入射する。MOS 型イメージセンサ 5 から出力された信号は、アンプアレイ 10 に入力されることによって増幅され、コネクタ 16 を介して信号処理基板 13 上の回路に入力され、映像信号出力端子 24 から出力される。

【 0 0 2 6 】

30

ここで、コネクタ 16 は、第 1 配線基板 1 及び信号処理基板 13 間に介在して第 1 配線基板 1 を信号処理基板 13 上に支持すると共に、MOS 型イメージセンサ 5 の出力信号をアナログ回路 17a, 17b, 18a, 18b, 19 に伝送し、デジタル回路 20, 21 の出力信号を MOS 型イメージセンサ 5 に伝送する。本実施の形態においては、コネクタ 16 自体が、第 1 配線基板 1 を信号処理基板 13 上に支持するので、構造上の強度が増加すると共に部品点数を減少させることができる。

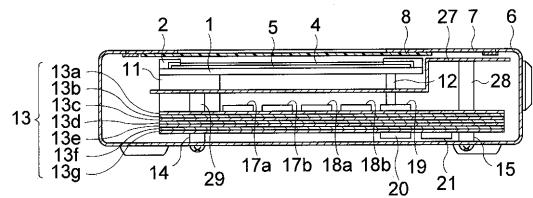

【 0 0 2 7 】

本実施の形態においては、信号処理基板 13 は、金属薄膜 13a, 13c, 13e, 13g 及びガラス纖維を含む絶縁性薄膜 13b, 13d, 13f とが交互に積層されてなる 4 層配線基板である。露出した金属薄膜 13a 及び 13g は、Cu / Ni / Au からなり、内部の金属薄膜 13c, 13e は Cu からなる。

40

【 0 0 2 8 】

この中で、信号処理基板 13 の上面側に形成された回路に最も近い内部金属薄膜 13c は、信号処理基板 13 の上面側に形成された回路のグランド電位に接続されており、信号処理基板 13 の裏面側に形成された回路に最も近い内部金属薄膜 13e は、信号処理基板 13 の裏面側に形成された回路のグランド電位に接続されている。また、これらの内部金属薄膜 13c, 13e は、一カ所のみで電気的に接続されている。

【 0 0 2 9 】

すなわち、信号処理基板 13 はグランド電位を有する第 2 金属薄膜 13e をその上下面間に有し、第 1 及び第 2 金属薄膜 13c, 13e はそれぞれアナログ回路 17a, 17b,

50

18a, 18b, 19及びデジタル回路20, 21のグランドにそれぞれ電気的に接続されている。第1及び第2金属薄膜13c, 13eは、アナログ回路17a, 17b, 18a, 18b, 19へのデジタル回路20, 21側からのノイズを遮蔽する。また、これがアナログ回路17a, 17b, 18a, 18b, 19及びデジタル回路20, 21に対応してそれぞれ設けられることにより、双方の回路の安定化が達成される。

#### 【0030】

信号処理基板13へのX線の入射を抑制するために、配線基板1と信号処理基板13との間には段部を有する遮蔽板27が介在し、遮蔽板27の上段部はスペーサ28によって、下段部はスペーサ29によって信号処理基板13に固定されている。遮蔽板27は、表面にNiメッキが施された真鍮からなり、グランド電位に接続されている。

10

#### 【0031】

上述のように、本実施の形態に係るX線パネルセンサは、入射したX線像を蛍光像に変換するシンチレータ4及びシンチレータ4により変換された蛍光像を撮像するMOS型イメージセンサ5を備えたX線パネルセンサにおいて、MOS型イメージセンサ5がその上側に固定される第1配線基板1と、グランド電位を有する第1金属薄膜13cをその上下面間に有し、第1配線基板1の下側に対向すると共に第1配線基板1に電気的に接続されるように配置された信号処理基板13と、第1配線基板1及び信号処理基板13間に介在しグランド電位を有するX線遮蔽板27と、信号処理基板13の上面側に設けられMOS型イメージセンサ5からの出力信号をアナログ処理するアナログ回路17a, 17b, 18a, 18b, 19と、信号処理基板13の下面側に設けられMOS型イメージセンサ5の駆動信号のタイミングを生成するデジタル回路20, 21とを備えている。

20

#### 【0032】

本実施の形態のX線パネルセンサによれば、MOS型イメージセンサ5からの出力信号を増幅処理するアンプアレイ10は、MOS型イメージセンサ5とアナログ回路との接続距離が短くなるように第1配線基板の上面側に配置され、また、アンプアレイ10からの出力を更にアナログ処理するアナログ回路17a, 17b, 18a, 18b, 19は、共にグランド電位を有する第2配線基板13の第1金属薄膜13cとX線遮蔽板27との間に配置されている。

#### 【0033】

したがって、この接続距離の短縮によって出力信号のノイズ耐性が向上すると共に、アナログ回路17a, 17b, 18a, 18b, 19を介して出力されるMOS型イメージセンサ5の出力信号に重畠されるべきノイズ、すなわち、上側からシンチレータ4及び筐体6を透過し、MOS型イメージセンサ5、アンプアレイ10、アナログ回路に入射するX線、及び下側からアナログ回路17a, 17b, 18a, 18b, 19、MOS型イメージセンサ5、アンプアレイ10に伝搬してくるデジタル回路20, 21及び外部からのノイズは、それぞれ鉛入りファイバオプティカルプレート3及び枠体2と、X線遮蔽板27及び第1金属薄膜13cによって抑制される。

30

#### 【0034】

また、本実施の形態においては、MOS型イメージセンサ5とアンプアレイ10とが別体の例について説明したが、これらは同一半導体基板上にモノリシックに形成されたものであってもよい。また、図4に示すように、MOS型イメージセンサ5上に、直接シンチレータ4を形成することもできる。

40

#### 【0035】

したがって、上記実施の形態によれば、出力信号に重畠されるノイズを低下させることにより、大型のMOS型イメージセンサ(縦横寸法=50mm×50mm)5を搭載したX線パネルセンサを実現することができる。信号処理基板13の上下面にはアナログ回路17a, 17b, 18a, 18b, 19及びデジタル回路20, 21を搭載することとしたので、X線パネルセンサ全体の寸法は小型化することができる。

#### 【0036】

以上、説明したように、本実施の形態に係るX線パネルセンサは、良質の画像を得ること

50

ができるので、医療機器や宇宙観測機器等の高性能測定機器に適用することができる。

【0037】

【発明の効果】

以上、説明したように、本発明に係るX線パネルセンサによれば、MOS型イメージセンサを第1配線基板上に形成し、X線遮蔽板と、金属薄膜を上下面間に有する第2配線基板との間となる第2配線基板の上面側にアナログ回路を配置し、これと逆側にデジタル回路を配置することとしたので、更に良質の画像を得ることができる。

【図面の簡単な説明】

【図1】X線パネルセンサの平面図。

【図2】図1に示したX線パネルセンサのI I - I I 矢印断面図。

10

【図3】図1に示したX線パネルセンサの回路構成図。

【図4】別の形態に係るX線パネルセンサの断面図。

【符号の説明】

1...配線基板、2...枠体、3...ファイバオプティカルプレート、4...シンチレータ、5...半導体イメージセンサ、10...增幅素子、17a, 17b, 18a, 18b, 19...アナログ回路、20, 21...デジタル回路。

【図1】

【図3】

【図2】

【図4】

---

フロントページの続き

(72)発明者 山本 晃永

静岡県浜松市市野町1126番地の1 浜松ホトニクス株式会社内

審査官 青木 洋平

(56)参考文献 特開平09-288184 (JP, A)

特開平10-032323 (JP, A)

特開平02-021285 (JP, A)

特開平02-276996 (JP, A)

特開平05-060871 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G01T 1/00-7/12