(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4149377号

(P4149377)

(45) 発行日 平成20年9月10日(2008.9.10)

(24) 登録日 平成20年7月4日(2008.7.4)

(51) Int.Cl.

H01L 25/065 (2006.01)

H01L 25/07 (2006.01)

H01L 25/18 (2006.01)

F 1

H01L 25/08

Z

請求項の数 5 (全 30 頁)

(21) 出願番号 特願2003-506004 (P2003-506004)

(86) (22) 出願日 平成14年4月5日 (2002.4.5)

(86) 国際出願番号 PCT/JP2002/003434

(87) 国際公開番号 WO2002/103793

(87) 国際公開日 平成14年12月27日 (2002.12.27)

審査請求日 平成16年10月1日 (2004.10.1)

(31) 優先権主張番号 特願2001-172503 (P2001-172503)

(32) 優先日 平成13年6月7日 (2001.6.7)

(33) 優先権主張国 日本国 (JP)

前置審査

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 角 義之

東京都小平市上水本町五丁目20番1号

株式会社日立製作所 半導体グループ内

(72) 発明者 内藤 孝洋

東京都小平市上水本町五丁目20番1号

株式会社日立製作所 半導体グループ内

(72) 発明者 佐藤 俊彦

東京都小平市上水本町五丁目20番1号

株式会社日立製作所 半導体グループ内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

(a) 第1主面、前記第1主面上に形成された複数の第1電極、前記複数の第1電極上有する第1半導体チップと、第2主面、前記第2主面上に形成された複数の第2電極、前記複数の第2電極上有する第2半導体チップと、第3主面、前記第3主面上に形成された複数の第3電極、及び前記第3主面と反対側の第3裏面を有する第3半導体チップとを準備する工程、

(b) 表面、前記表面に形成された複数の配線、前記複数の配線の周囲に形成された複数のボンディングパッド、前記表面と反対側の裏面、及び前記裏面に形成された複数の電極パッドを有する配線基板を準備し、前記配線基板の前記複数の配線上に樹脂テープを貼り付ける工程、

(c) 前記(b)工程の後、前記第1半導体チップの前記第1主面及び前記第2半導体チップの前記第2主面のそれぞれが前記配線基板の前記表面と対向し、前記第1半導体チップと前記第2半導体チップが互いに隣り合うように、前記配線基板の前記表面に貼り付けられた前記樹脂テープ上に前記複数の第1バンプ電極を介して前記第1半導体チップ及び前記複数の第2バンプ電極を介して前記第2半導体チップのそれぞれを搭載する工程、

(d) 前記(c)工程の後、前記第1半導体チップの前記第1裏面及び前記第2半導体チップの前記第2裏面にツールを押し当て、前記複数の第1バンプ電極及び前記複数の第2

10

20

バンプ電極のそれを前記複数の配線と電気的に接続し、前記複数の第1バンプ電極及び前記複数の第2バンプ電極を前記樹脂テープで封止し、前記第1半導体チップと前記第2半導体チップとの間に前記樹脂テープを充填させる工程、

(e) 前記(d)工程の後、前記第3半導体チップの前記第3裏面が前記第1半導体チップの前記第1裏面及び前記第2半導体チップの前記第2裏面とそれ対向するように、前記第1半導体チップの前記第1裏面上及び前記第2半導体チップの前記第2裏面上に前記第3半導体チップを積層する工程、

(f) 前記(e)工程の後、前記第3半導体チップの前記複数の第3電極と前記配線基板の前記複数のボンディングパッドとを複数のワイヤを介してそれぞれ電気的に接続する工程、

(g) 前記(f)工程の後、前記第1半導体チップ、前記第2半導体チップ、前記第3半導体チップ、及び前記複数のワイヤをモールド樹脂で封止する工程、

(h) 前記(g)工程の後、前記配線基板の前記複数の電極パッドに複数の半田バンプをそれぞれ接続する工程、

を含むことを特徴とする半導体装置の製造方法。

#### 【請求項2】

前記(b)工程において、前記樹脂テープは、前記第1半導体チップと前記第2半導体チップとの間よりも小さい粒径サイズから成る第1フィラーを有し、

前記(g)工程において、前記モールド樹脂は、前記第1半導体チップと前記第2半導体チップとの間及び前記第1フィラーの径よりも大きい粒径サイズから成る第2フィラーを有することを特徴とする請求項1記載の半導体装置の製造方法。

#### 【請求項3】

前記(d)工程では、前記ツールを加熱した状態で押し当てる特徴とする請求項2記載の半導体装置の製造方法。

#### 【請求項4】

前記樹脂テープは、前記配線基板をベークしてから貼り付ける特徴とする請求項3記載の半導体装置の製造方法。

#### 【請求項5】

前記樹脂テープは、前記配線基板をベークし、さらにプラズマ処理を施してから貼り付ける特徴とする請求項4記載の半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

##### 【0002】

本発明は、半導体装置およびその製造技術に関し、特に、複数の半導体チップを同一の配線基板上に搭載したマルチチップモジュール(Multi-Chip Module; M C M)またはマルチチップパッケージ(Multi-Chip Package; M C P)に適用して有効な技術に関する。

##### 【従来の技術】

##### 【0003】

フラッシュメモリやD R A M(Dynamic Random Access Memory)などのメモリL S Iを大容量化する対策の一つとして、これらのメモリL S Iが形成された半導体チップ(メモリチップ)を積層して単一のパッケージに封止したメモリ・モジュール構造が種々提案されている。

##### 【0004】

例えば特開平4-302164号公報は、一つのパッケージ内に同一機能、同一サイズの複数の半導体チップを絶縁層を介して階段状に積層し、それぞれの半導体チップの階段状部分に露出したボンディングパッドとパッケージのインナーリードとをワイヤを介して電気的に接続したパッケージ構造を開示している。

##### 【0005】

また、特開平11-204720号公報は、絶縁性基板上に熱圧着シートを介して第1の

半導体チップを搭載し、この第1の半導体チップ上に熱圧着シートを介して、外形寸法が第1の半導体チップよりも小さい第2の半導体チップを搭載し、第1および第2の半導体チップのボンディングパッドと絶縁性基板上の配線層とをワイヤを介して電気的に接続し、第1および第2の半導体チップとワイヤとを樹脂により封止したパッケージ構造を開示している。

【発明が解決しようとする課題】

【0006】

本発明者らは、一つのパッケージ内に複数個の半導体チップ（以下、単にチップという）を搭載したマルチチップモジュールを開発している。

【0007】

本発明者らが開発中のマルチチップモジュールは、DRAM (Dynamic Random Access Memory) が形成されたチップと、フラッシュメモリが形成されたチップと、高速マイクロプロセッサ (MPU: 超小型演算処理装置) が形成されたチップとを单一の樹脂パッケージ内に封止することによって、複数個のメモリチップを樹脂封止した従来のメモリ・モジュールよりも汎用性が高いシステムを実現しようとするものである。また、このマルチチップモジュールは、実装面積を縮小するために、3個のチップのうち、DRAM が形成されたチップとフラッシュメモリが形成されたチップとをパッケージ基板の主面上に並べて配置し、フリップチップ方式によって実装する。また、マイクロプロセッサが形成された第3のチップは、上記2個のメモリチップの上に積層し、ワイヤボンディング方式によって実装する。

10

20

【0008】

ところが、上記のような構造のマルチチップモジュールは、高密度実装の観点から、並べて配置した2個のメモリチップの間隔が数10 μm 程度と極めて狭く、しかもこれら2個のメモリチップの上に第3のチップが積層されるため、これら3個のチップをモールド樹脂で封止しようとすると、2個のメモリチップの隙間にモールド樹脂が入り難いという問題がある。

【0009】

一般に、モールド樹脂中には、モールド樹脂の熱膨張係数をシリコンチップのそれに近づけるために、シリカフィラーが混入されている。しかし、このシリカフィラーの粒径（例えば70 ~ 100 μm）は、上記した2個のメモリチップの間隔（数10 μm）よりも大きいため、これがメモリチップの隙間にモールド樹脂が充填され難いという原因の一つになっている。

30

【0010】

2個のメモリチップの隙間がモールド樹脂で充填されないと、そこに空気溜まり（ボイド）が生じるため、ボイド内の空気の熱膨張が繰り返されることに起因して、ボイドを中心にモールド樹脂とチップの剥離が広がり、例えば、MCP を実装基板に半田リフロー技術を用いて実装する時に、パッケージクラックを引き起こす虞れがある。

【0011】

本発明の目的は、複数個のチップを配線基板に搭載してその正面を樹脂封止したマルチチップモジュールの信頼性、高密度実装化、低コスト化を促進させる技術を提供することにある。

40

【0012】

本発明の他の目的は、複数個のチップの上に他のチップを積層して樹脂封止したマルチチップモジュールの信頼性を向上させる技術を提供することにある。

【0013】

本発明の他の目的は、複数個のチップの上に他のチップを積層して樹脂封止したマルチチップモジュールの製造コストを低減することのできる技術を提供することにある。

【0014】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

50

【課題を解決するための手段】

【0015】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0017】

本願発明による半導体装置の製造方法は、以下の工程を含んでいる。

(a) 第1主面、前記第1主面上に形成された複数の第1電極、前記複数の第1電極上にそれぞれ形成された複数の第1バンプ電極、及び前記第1主面と反対側の第1裏面を有する第1半導体チップと、第2主面、前記第2主面上に形成された複数の第2電極、前記複数の第2電極上にそれぞれ形成された複数の第2バンプ電極、及び前記第2主面と反対側の第2裏面を有する第2半導体チップと、第3主面、前記第3主面上に形成された複数の第3電極、及び前記第3主面と反対側の第3裏面を有する第3半導体チップとを準備する工程、10

(b) 表面、前記表面に形成された複数の配線、前記複数の配線の周囲に形成された複数のボンディングパッド、前記表面と反対側の裏面、及び前記裏面に形成された複数の電極パッドを有する配線基板を準備し、前記配線基板の前記複数の配線上に樹脂テープを貼り付ける工程、

(c) 前記(b)工程の後、前記第1半導体チップの前記第1主面及び前記第2半導体チップの前記第2主面のそれぞれが前記配線基板の前記表面と対向し、前記第1半導体チップと前記第2半導体チップが互いに隣り合うように、前記配線基板の前記表面に貼り付けられた前記樹脂テープ上に前記複数の第1バンプ電極を介して前記第1半導体チップ及び前記複数の第2バンプ電極を介して前記第2半導体チップのそれぞれを搭載する工程、20

(d) 前記(c)工程の後、前記第1半導体チップの前記第1裏面及び前記第2半導体チップの前記第2裏面にツールを押し当て、前記複数の第1バンプ電極及び前記複数の第2バンプ電極のそれぞれを前記複数の配線と電気的に接続し、前記複数の第1バンプ電極及び前記複数の第2バンプ電極を前記樹脂テープで封止し、前記第1半導体チップと前記第2半導体チップとの間に前記樹脂テープを充填させる工程、

(e) 前記(d)工程の後、前記第3半導体チップの前記第3裏面が前記第1半導体チップの前記第1裏面及び前記第2半導体チップの前記第2裏面とそれぞれ対向するように、前記第1半導体チップの前記第1裏面上及び前記第2半導体チップの前記第2裏面上に前記第3半導体チップを積層する工程、30

(f) 前記(e)工程の後、前記第3半導体チップの前記複数の第3電極と前記配線基板の前記複数のボンディングパッドとを複数のワイヤを介してそれぞれ電気的に接続する工程、

(g) 前記(f)工程の後、前記第1半導体チップ、前記第2半導体チップ、前記第3半導体チップ、及び前記複数のワイヤをモールド樹脂で封止する工程、

(h) 前記(g)工程の後、前記配線基板の前記複数の電極パッドに複数の半田バンプをそれぞれ接続する工程。

【発明の実施の形態】

【0018】

以下、本発明の実施形態を図面に基づいて詳細に説明する。なお、実施形態を説明するための全図において、同一の機能を有するものには同一の符号を付し、その繰り返しの説明は省略する。

【0019】

(実施の形態1)

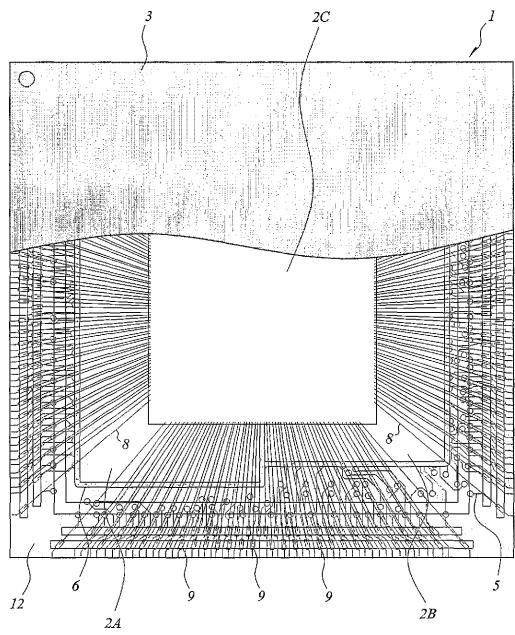

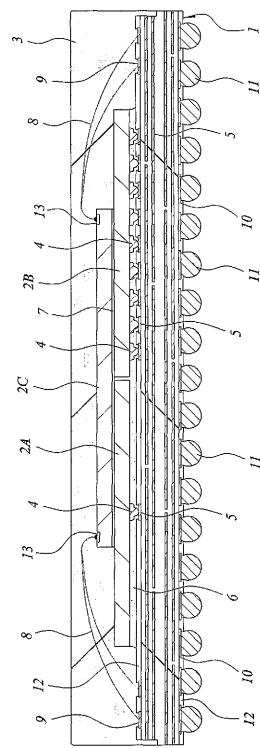

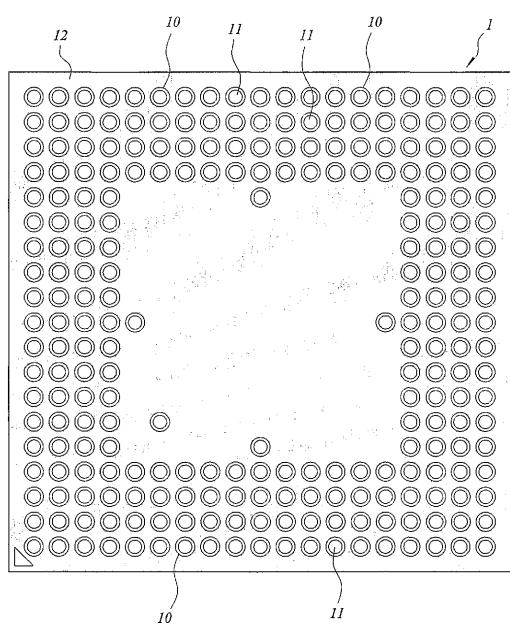

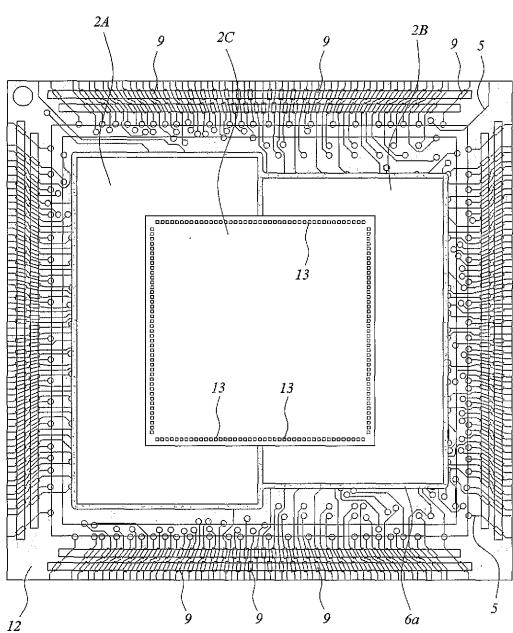

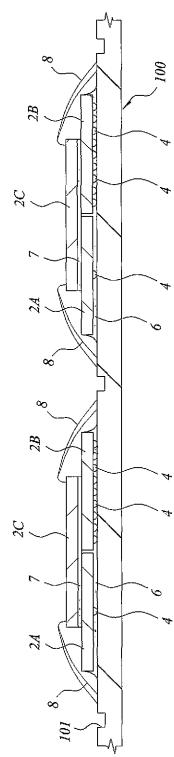

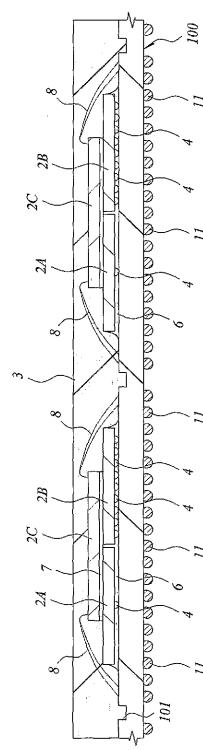

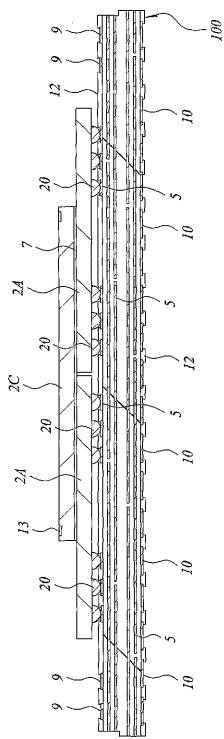

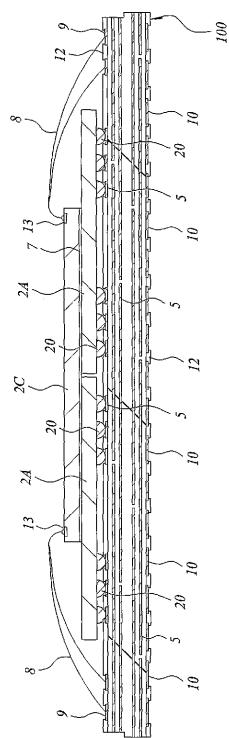

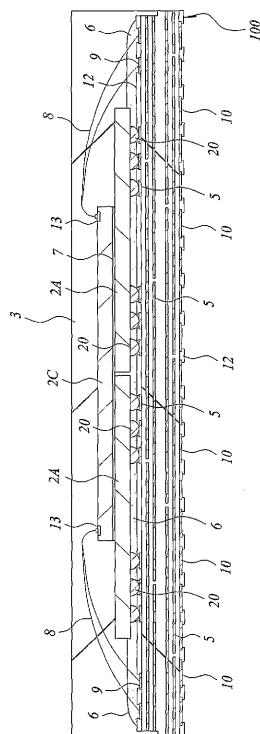

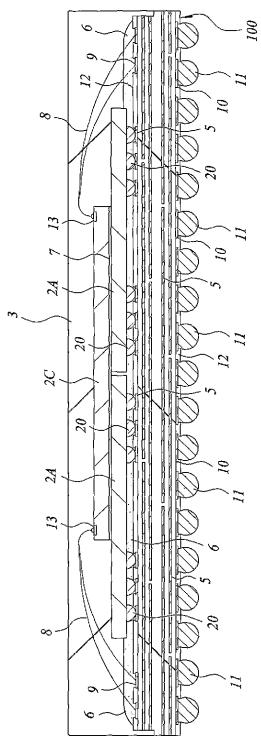

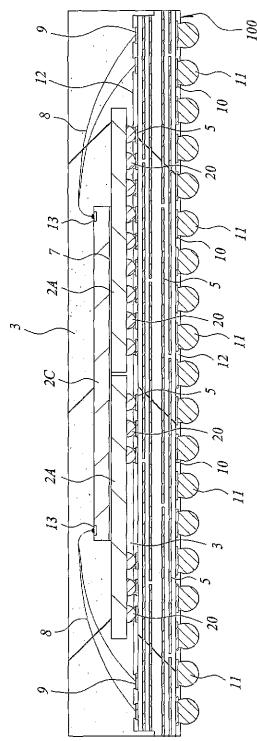

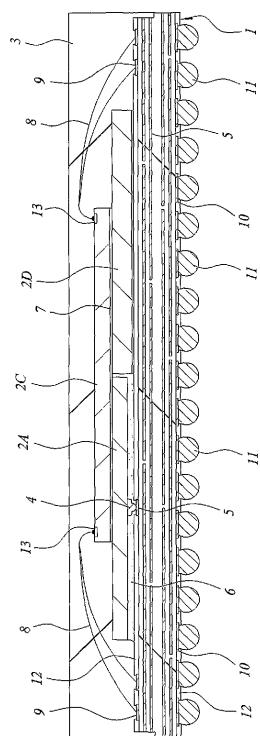

図1は、本実施形態の半導体装置の上面を示す平面図、図2は、この半導体装置の断面図、図3は、この半導体装置の下面を示す平面図である。

【0020】

本実施形態の半導体装置は、パッケージ基板1の主面上に3個のチップ2A、2B、2Cを実装し、これらのチップ2A、2B、2Cをモールド樹脂3で封止したマルチチップモ

10

20

30

40

50

ジユール( M C M )である。3個のチップ2A～2Cのうち、2個のチップ2A、2Bは、パッケージ基板1の主面上に並べて配置され、それらの正面に形成された複数個のA u バンプ4を介してパッケージ基板1の配線5と電気的に接続されている。すなわち、チップ2A、2Bのそれぞれは、フリップチップ方式によって実装されている。

#### 【 0 0 2 1 】

チップ2A、2Bの正面(下面)とパッケージ基板1の正面との隙間には、アンダーフィル樹脂(封止樹脂)6が充填されている。チップ2Aは、例えば複数の記憶素子を有する記憶回路を含むD R A Mが形成されたシリコンチップであり、チップ2Bは、例えばフラッシュメモリが形成されたシリコンチップである。

#### 【 0 0 2 2 】

チップ2Cは、2個のチップ2A、2Bを跨ぐように配置され、接着剤7によってチップ2A、2Bの上面に接着されている。チップ2Cの正面に形成されたボンディングパッド13は複数本のA u ワイヤ8によってパッケージ基板1のボンディングパッド9と電気的に接続されている。すなわち、チップ2Cは、ワイヤボンディング方式によって実装されている。チップ2Cは、例えばプログラムで動作するプロセッサ回路を含む高速マイクロプロセッサ( M P U : 超小型演算処理装置)が形成されたシリコンチップである。

#### 【 0 0 2 3 】

上記3個のチップ2A、2B、2Cを実装するパッケージ基板1は、ガラス繊維を含んだエポキシ樹脂(ガラス・エポキシ樹脂)のような汎用樹脂を主体として構成された多層配線基板であり、その正面(上面)、下面および内部に4～6層程度の配線5が形成されている。

#### 【 0 0 2 4 】

パッケージ基板1の下面には、上記配線5と電気的に接続された複数の電極パッド10がアレイ状に配置されており、それぞれの電極パッド10には、マルチチップモジュール( M C M )の外部接続端子を構成する半田バンプ11が接続されている。マルチチップモジュール( M C M )は、これらの半田バンプ11を介して電子機器の配線基板などに実装される。パッケージ基板1の正面および下面には、配線5とチップ2A、2Bとの接続部、ボンディングパッド9、電極パッド10などの表面を除き、エポキシ系樹脂やアクリル系樹脂などからなるソルダレジスト(絶縁膜)12がコーティングされている。

#### 【 0 0 2 5 】

上記マルチチップモジュール( M C M )の寸法の一例を説明すると、パッケージ基板1の外形寸法は、縦×横 = 13 mm × 13 mm、厚さ0.3 mmである。パッケージ基板1に実装されたチップ2A、2B、2Cの厚さは、それぞれ0.15 mm、並んで配置された2個のチップ2A、2Bの間隔は、20 μm～100 μmである。チップ2A、2B、2Cを封止するモールド樹脂3の厚さは、0.66 mm、モールド樹脂3の上面から半田バンプ11の下端までの距離、すなわちマルチチップモジュール( M C M )の実装高さは、1.468 mmである。

#### 【 0 0 2 6 】

次に、上記のように構成された本実施形態の半導体装置の製造方法を図4～図26を用いて工程順に説明する。

#### 【 0 0 2 7 】

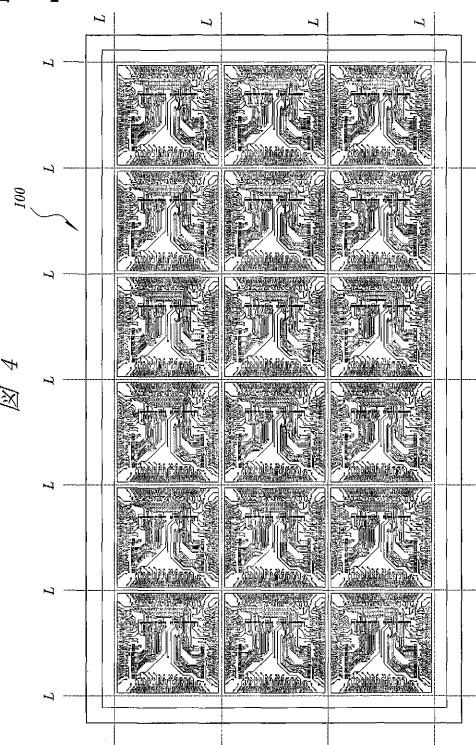

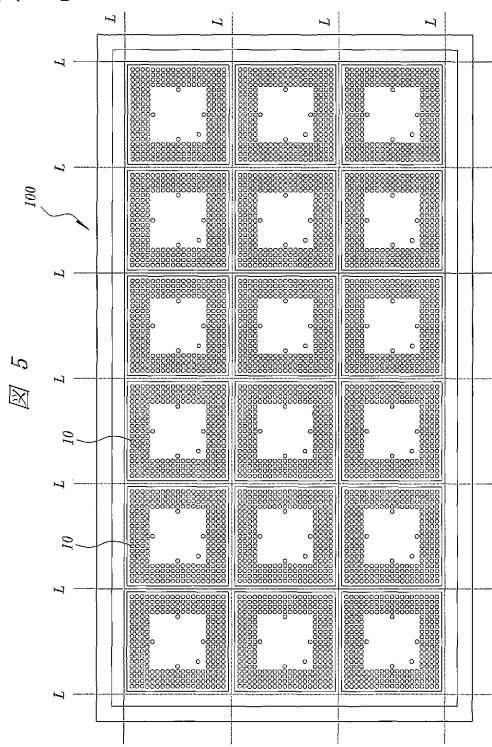

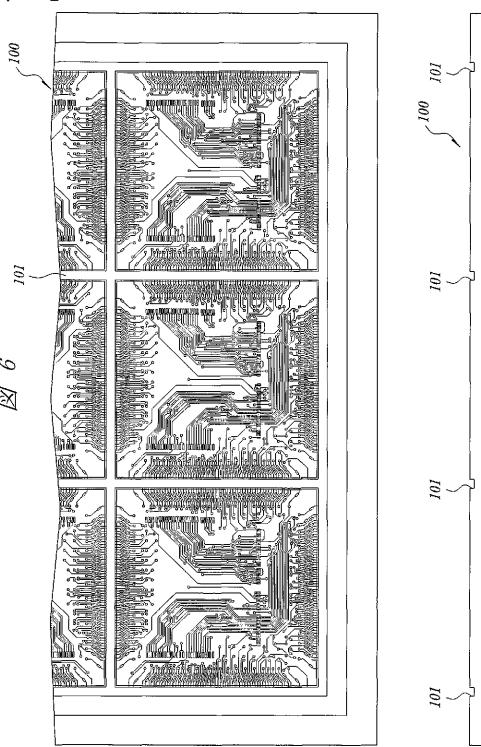

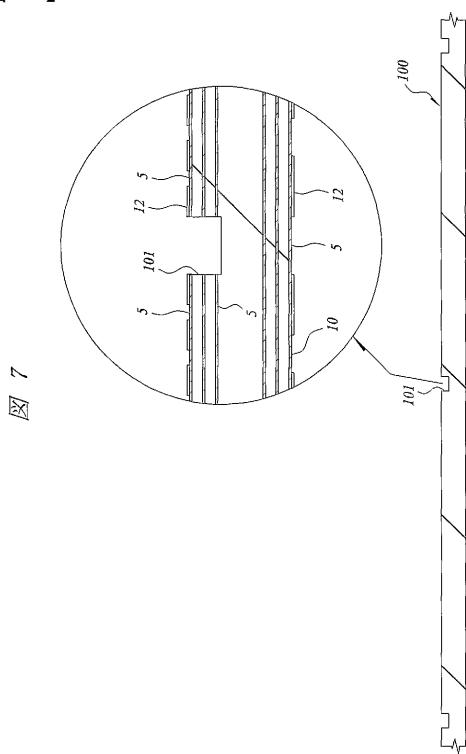

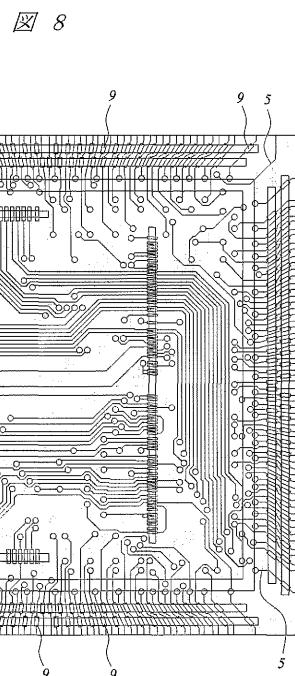

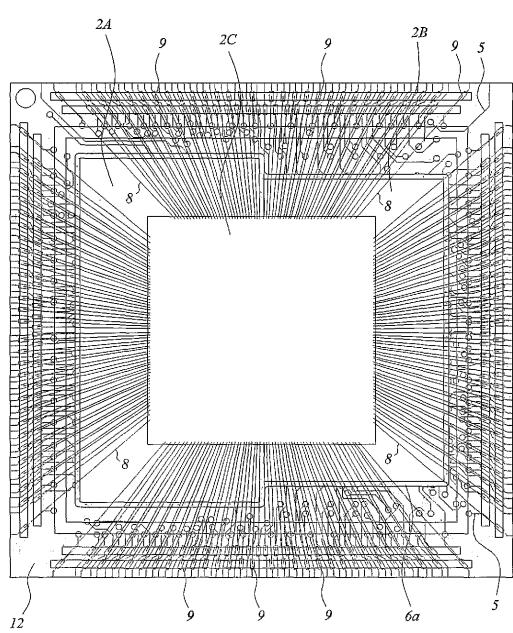

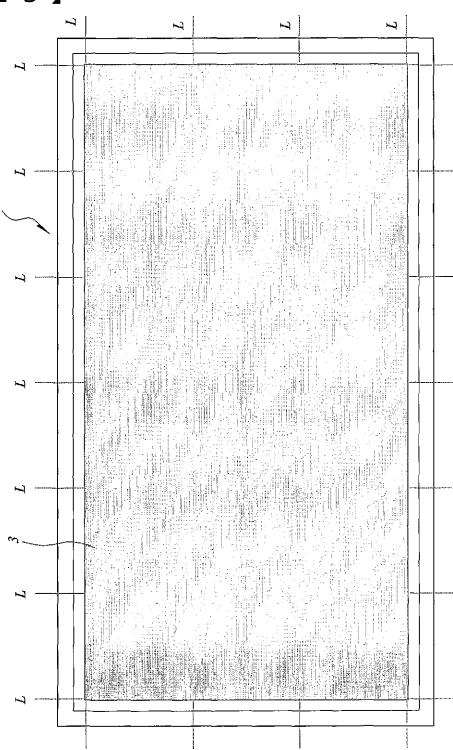

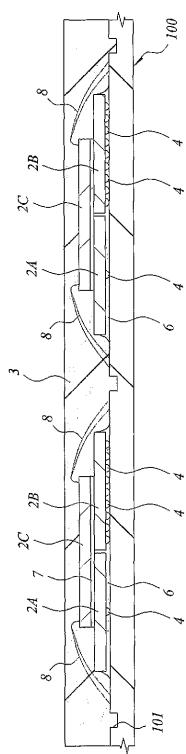

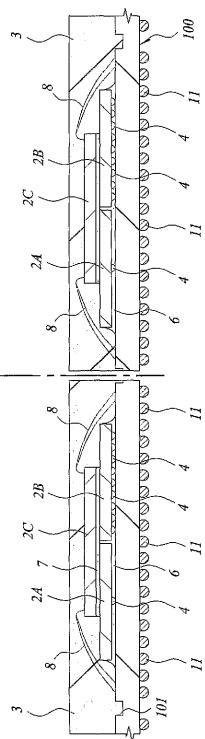

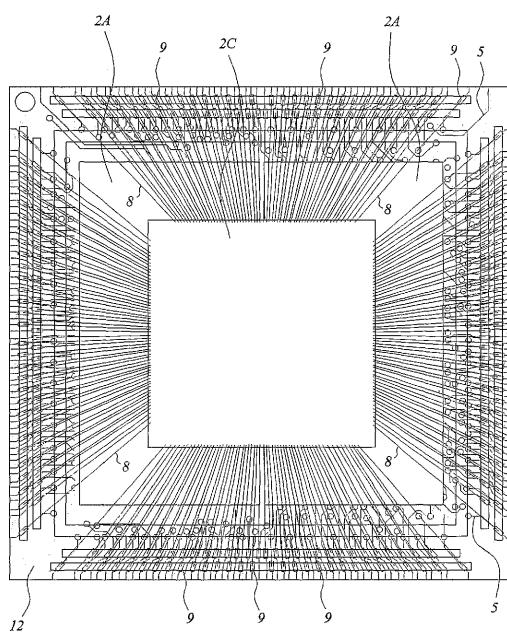

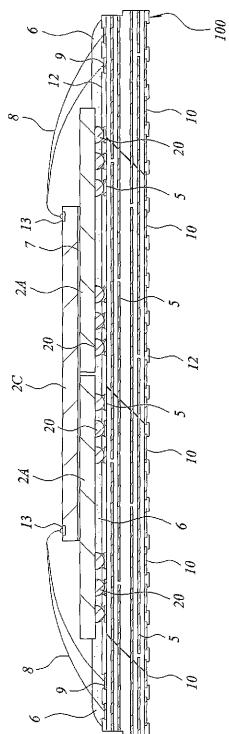

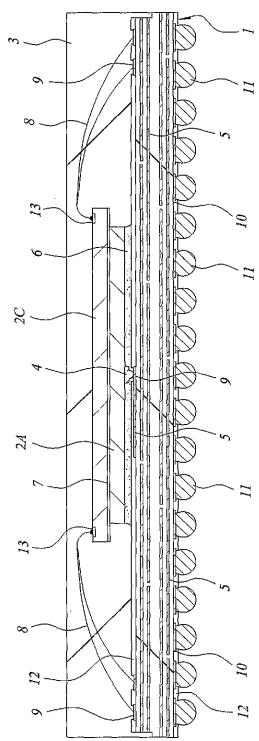

図4～図8は、マルチチップモジュール( M C M )の製造に使用する長方形の基板(以下、マルチ配線基板またはマルチ配線基板100という)を示している。図4は、このマルチ配線基板100の正面(チップ実装面)を示す全体平面図、図5は、裏面を示す全体平面図である。また、図6は、マルチ配線基板100の一部を示す平面図と側面図、図7は、マルチ配線基板100の一部を示す断面図、図8は、マルチ配線基板100の一部(パッケージ基板1個分の領域)を示す拡大平面図である。

#### 【 0 0 2 8 】

マルチ配線基板100は、前記パッケージ基板1の母体となる基板である。このマルチ配線基板100を図4、図5に示すダイシングラインLに沿って格子状に切断(ダイシング

10

20

30

40

50

)、個片化することにより、複数個のパッケージ基板1が得られる。図に示すマルチ配線基板(マルチ配線基板)100の場合は、その長辺方向が6ブロックのパッケージ基板形成領域に区画され、短辺方向が3ブロックのパッケージ基板形成領域に区画されているので、 $3 \times 6 = 18$ 個のパッケージ基板1が得られる。

#### 【0029】

上記マルチ配線基板100は、ガラス・エポキシ樹脂のような汎用樹脂を主体として構成された多層配線基板である。マルチ配線基板100の正面には、配線5およびボンディングパッド9が形成されており、裏面には、電極パッド10が形成されている。また、マルチ配線基板100の内層には、複数層の配線5が形成されている。パッケージ基板1を、安価な汎用樹脂を使って製造することにより、マルチチップモジュール(MCM)の製造原価を低減することができる。10

#### 【0030】

マルチ配線基板100の正面の配線5およびボンディングパッド9と、裏面の電極パッド10は、マルチ配線基板100の両面に貼り付けたCu箔をエッチングすることによって形成される。マルチ配線基板100の正面の配線5のうち、ソルダレジスト12で覆われていない領域、すなわちチップ2A、2BのAuバンプ4が接続される領域の表面には、NiおよびAuのメッキが施されている。また、ボンディングパッド9の表面および電極パッド10の表面にも、NiおよびAuのメッキが施されている。これらのメッキは、無電解メッキ法で形成することもできるが、無電解メッキ法で形成したメッキ層は膜厚が薄く、ボンディングパッド9上にAuワイヤ4を接続したときに十分な接着強度が確保し難いので、上記NiおよびAuのメッキは、無電解メッキ法よりも膜厚を厚くすることができる電解メッキ法で形成される。20

#### 【0031】

配線5、ボンディングパッド9および電極パッド10の表面に電解メッキ法でNiおよびAuのメッキを施す場合は、配線5、ボンディングパッド9および電極パッド10がマルチ配線基板100の全域で導通した状態でメッキ処理を行い、次いで、ダイシングライン上に配線5をルータで切断した後、各パッケージ基板形成領域の導通試験を行う。そのため、図6および図7に示したように、マルチ配線基板100の正面のダイシングライン上には、この領域の配線5をルータで切断したときの溝101が残っている。前記ルータ加工により、導通試験を行うための各パッケージ基板間の連続して形成された配線が切断されるので、導通試験が個別にでき、また、マルチ配線基板100を完全に切り離さないので、一括モールド工程やその後の基板搬送処理が容易にできる。切断された配線の端部が溝101の側面から露出している。30

#### 【0032】

図8に示すように、パッケージ基板形成領域の周辺部には、チップ実装領域を囲むように複数のボンディングパッド13が形成されている。ボンディングパッド13は、パッケージ基板形成領域の4辺に沿って2列に配置されている。ボンディングパッド13とチップ実装領域との間には、チップ実装領域を囲むようにダム領域16が設けられている。このダム領域16は、ソルダレジスト12が形成されていない領域であり、その内側および外側のソルダレジスト12が形成された領域よりも表面の高さが低くなっているため、チップ2A、2Bの下部にアンダーフィル樹脂6を充填する際、このアンダーフィル樹脂6がパッケージ基板形成領域の周辺部、すなわちボンディングパッド13が形成された領域に流れのを防ぐ機能を持っている。40

#### 【0033】

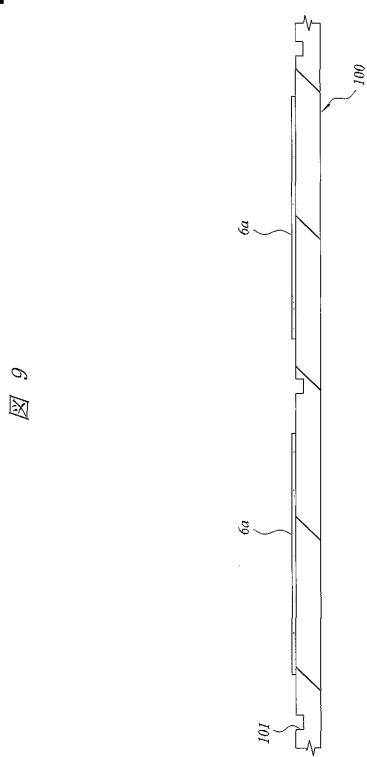

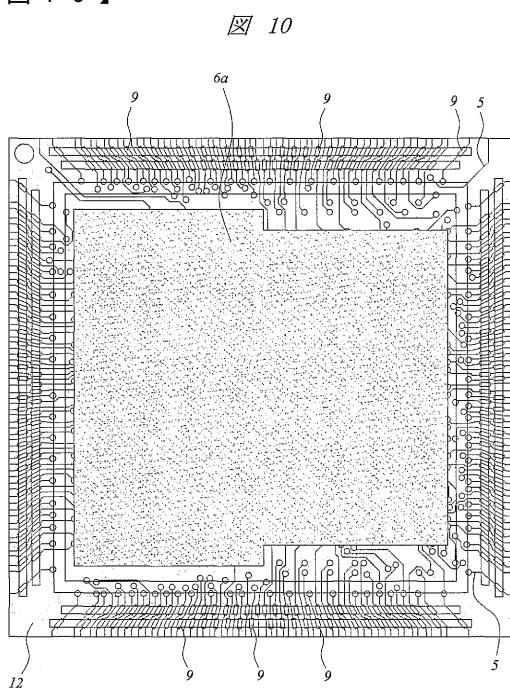

上記マルチ配線基板100を使ってマルチチップモジュール(MCM)を製造するには、図9(パッケージ基板2個分の領域を示す断面図)および図10(パッケージ基板1個分の領域を示す拡大平面図)に示すように、マルチ配線基板100の正面のチップ実装領域に樹脂テープ6aを貼り付ける。樹脂テープ6aは、例えば粒径3μm程度のシリカを分散させた熱硬化型エポキシ系樹脂からなるもので、あらかじめ2個のチップ(チップ2A、2B)とほぼ同じ寸法となるように裁断しておく。樹脂テープ6aは、樹脂中に導電性50

の微粉末を分散させた異方性導電性樹脂( A C F )などで構成することもできる。樹脂テープ 6 a は、各半導体チップ 2 A、2 B とほぼ同じ寸法の 2 枚の分割されたテープを用いてよい。

#### 【 0 0 3 4 】

なお、大気中に放置したマルチ配線基板 1 0 0 には大気中の水分が浸入しているため、そのまま樹脂テープ 6 a を貼り付けると、両者の接着性が低下する虞れがある。従って、マルチ配線基板 1 0 0 の正面に樹脂テープ 6 a を貼り付ける際には、その直前にマルチ配線基板 1 0 0 をベークして水分を除去しておくことが望ましい。ベーク条件は、例えば 125℃、2 時間程度である。また、上記ベーク処理に続いてマルチ配線基板 1 0 0 をプラズマ処理し、その表面を活性化することにより、樹脂テープ 6 a とマルチ配線基板 1 0 0 との接着性をさらに向上させることができる。10

#### 【 0 0 3 5 】

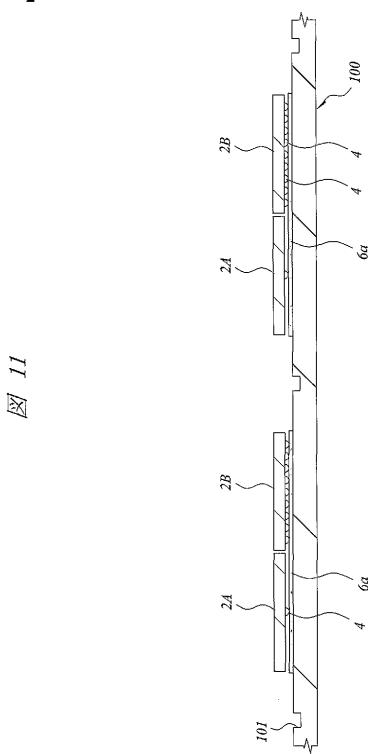

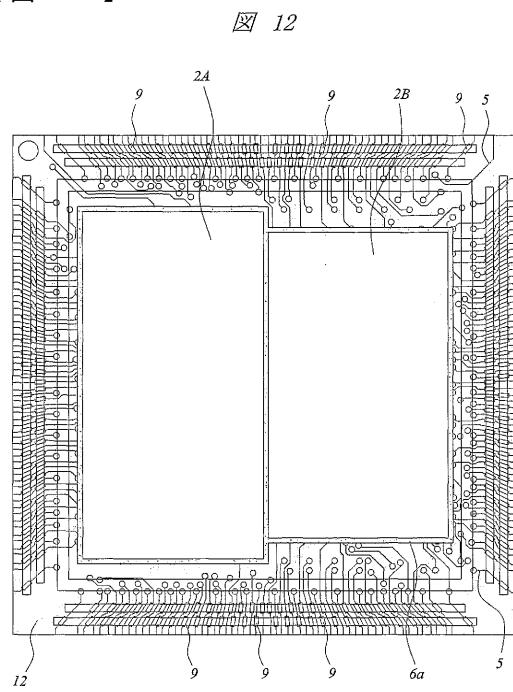

次に、図 1 1 および図 1 2 に示すように、マルチ配線基板 1 0 0 の正面に貼り付けた樹脂テープ 6 a の上に 2 個のチップ 2 A、2 B をフェイスダウン方式で搭載する。このとき、チップ 2 A とチップ 2 B の隙間を 20 μm ~ 100 μm 程度に設定する。樹脂テープ 6 a に含まれるシリカの粒径は 3 μm 程度であるため、チップ 2 A とチップ 2 B の隙間を 20 μm まで狭くしても、この隙間にアンダーフィル樹脂 6 を充填させることができる。他方、チップ 2 A とチップ 2 B の隙間が広すぎると、この隙間がアンダーフィル樹脂 6 で完全に充填されなくなり、後のモールド工程でこの隙間に空気溜まり(ボイド)が生じることがある。また、チップ 2 A とチップ 2 B の隙間を広くすることは個々の配線基板の面積を大きくすることを意味し、高密度実装を阻害するものである。20

#### 【 0 0 3 6 】

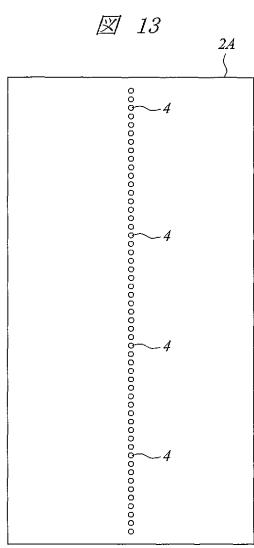

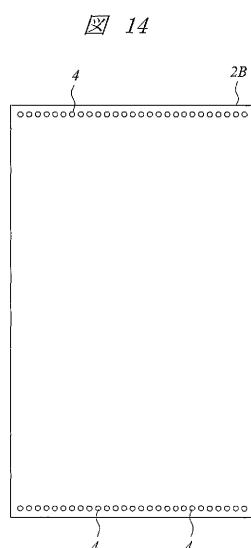

図 1 3 に示すように、D R A M が形成されたチップ 2 A の正面には、あらかじめホールボンディング法を用いて Au バンプ 4 を形成しておく。また、図 1 4 に示すように、フラッシュメモリが形成されたチップ 2 B の正面にも、同様の方法で Au バンプ 4 を形成しておく。これらの Au バンプ 4 は、ウエハプロセスの最終工程で形成する。すなわち、通常のウエハプロセスが完了した後、ウエハのボンディングパッド上にホールボンディング法を用いて Au バンプ 4 を形成し、その後、ウエハをダイシングすることによって、個片化されたチップ 2 A、2 B を得る。30

#### 【 0 0 3 7 】

通常、D R A M のボンディングパッドは、チップの中央に一列に配置されるが、フラッシュメモリのボンディングパッドは、チップの短辺に沿って 2 列に配置される。そのため、D R A M のボンディングパッドは、フラッシュメモリのそれに比べてパッドのピッチが狭くなり、それに伴ってパッドの径も小さくなる(例えばフラッシュメモリの端子ピッチが 150 μm の場合、D R A M のそれは 85 μm 程度である)。従って、D R A M のボンディングパッド上に Au バンプ 4 を形成するときは、径の細い(例えば直径 20 μm) の Au 線を使用し、フラッシュメモリのボンディングパッド上に Au バンプ 4 を形成するときは、径の太い(例えば直径 30 μm) の Au 線を使用するのが通常である。

#### 【 0 0 3 8 】

しかし、本実施形態のマルチチップモジュール( M C M )は、2 個のチップ 2 A、2 B の上に第 3 のチップ 2 C を積層するので、チップの厚さおよび Au バンプ 4 の径を 2 個のチップ 2 A、2 B で同じにすることによって、両者の実装高さを揃える必要がある。従って、本実施形態では、フラッシュメモリのボンディングパッド上に Au バンプ 4 を形成するときに使用する Au 線は、D R A M のボンディングパッド上に Au バンプ 4 を形成するときに使用する Au 線と同じ径(例えば直径 20 μm) のものを使用する。この場合、ソルダレジスト 1 2 の厚さ(例えば 25 μm) を考慮すると、細い Au 線を使って形成した Au バンプ 4 は、ボンディングパッドとの接触面積が少なり、接触不良を起こす可能性がある。そこで本実施形態では、Au バンプ 4 とボンディングパッドとの接触面積を確保するために、Au バンプ 4 の上に Au バンプ 4 を重ねてボンディングする多段バンプ構造を採用する。4050

## 【0039】

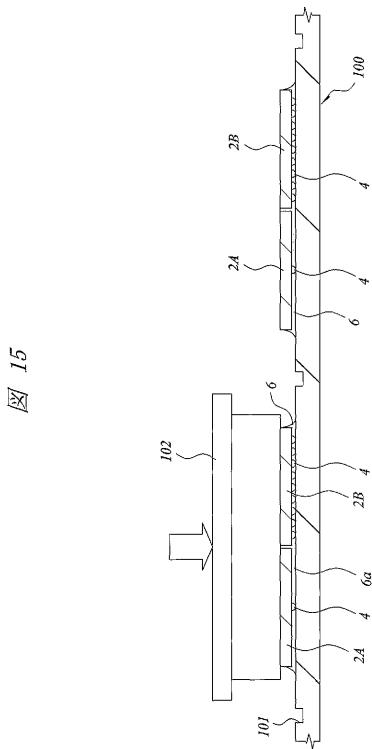

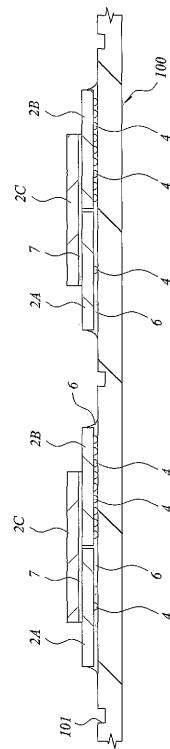

次に、図15に示すように、2個のチップ2A、2Bの上に底面が平坦なヒートツール（ヒートブロックとも言う）102を押し当てる。ヒートツール102の加圧圧力は、例えば15kg/10mm<sup>2</sup>、温度は例えば235である。これにより、樹脂テープ6aが溶融し、チップ2A、2Bとマルチ配線基板100の隙間、およびチップ2Aとチップ2Bの隙間にアンダーフィル樹脂6が充填されると共に、チップ2A、2BのAuバンプ4とマルチ配線基板100の配線5（図15には示さない）とが電気的に接続される。アンダーフィル樹脂6は、チップ2A、2Bの主面（半導体素子および電極（ボンディングパッド）形成面）の保護する、チップ2A、2Bをマルチ配線基板100に接着する、バンプ電極4とマルチ配線基板100の電極パッドの接続強度を確保する等の目的で形成される。10

## 【0040】

このように、本実施形態では、チップ2A、2Bとほぼ同じ寸法に加工した樹脂テープ6aを溶融させることによって、チップ2A、2Bとマルチ配線基板100の隙間、およびチップ2Aとチップ2Bの隙間にアンダーフィル樹脂6を充填する。この方法によれば、例えばチップ2A、2Bの周辺にディスペンサを使って液状のアンダーフィル樹脂を供給する充填方法に比べた場合、アンダーフィル樹脂6がチップ2A、2Bの周囲にはみ出す量を少なくすることができるので、チップ2A、2Bを囲むように配置されたマルチ配線基板100上のボンディングパッド9がアンダーフィル樹脂6で覆われることはない。20

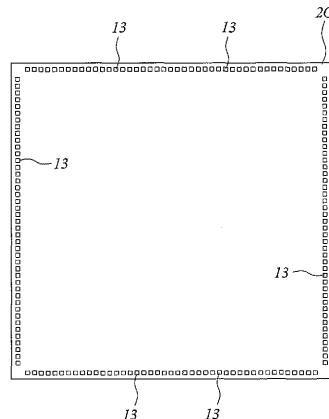

## 【0041】

次に、図16および図17に示すように、2個のチップ2A、2Bの上にチップ2Cを搭載する。図18に示すように、マイクロプロセッサが形成されたチップ2Cの主面には、その4辺に沿ってボンディングパッド13が形成されている。ボンディングパッド13の数は、チップ2Aやチップ2Bに形成されたボンディングパッドの数よりも多い。このようにボンディングパッド数が比較的少ないチップをバンプ電極によってフェースダウン実装し、ボンディングパッド数が比較的多いチップをワイヤボンディングによりフェースアップ実装することによって、配線基板の配線密度（配線ピッチ）や配線引き回しを低減し、低コストで高密度実装されたパッケージを提供できる。20

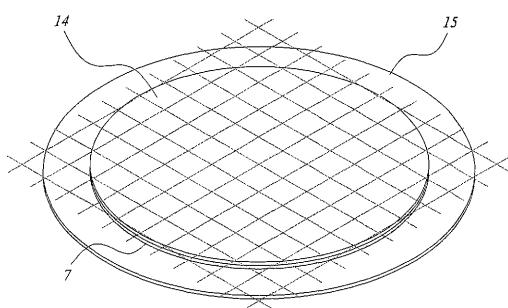

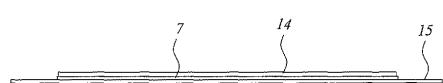

## 【0042】

チップ2Cは、マルチ配線基板100とチップ2Cとを接続するAuワイヤ8の長さが出来るだけ均一になるよう、各パッケージ基板形成領域の中央に配置する。また、チップ2Cの裏面には、あらかじめチップ2Cと同じ寸法に裁断されたテープ状の接着剤7を貼り付けておく。チップ2Cの裏面にテープ状の接着剤7を貼り付けるには、例えば図19および図20に示すように、通常のウエハプロセスが完了したウエハ14の裏面にダイシングテープ15を貼り付ける際、ウエハ14とダイシングテープ15との間にテープ状の接着剤7を挟み込み、この状態でウエハ14をダイシングすることによってチップ2Cを得る。その後、チップ2Cの裏面のダイシングテープ15を除去すると、チップ2Cの裏面にチップ2Cと同寸法の接着剤7が残る。接着剤7は、例えばポリイミド樹脂系の接着剤を使用する。30

## 【0043】

次に、マルチ配線基板100を加熱炉内で180、1時間程度加熱する。この加熱処理により、接着剤7が軟化し、チップ2A、2Bの上にチップ2Cが接着される。40

## 【0044】

次に、図21および図22に示すように、マルチ配線基板100のボンディングパッド9とチップ2Cのボンディングパッド13（図21、22には示さない）とをAuワイヤ8で接続する。Auワイヤ8の接続は、例えば超音波振動と熱圧着とを併用したワイヤボンダを使用して行う。

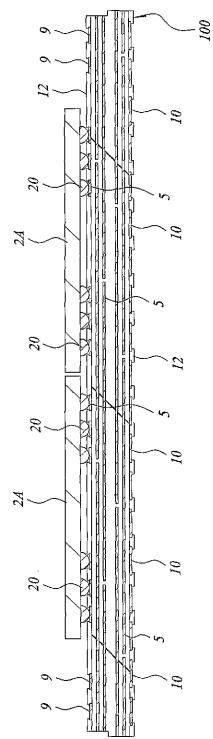

## 【0045】

次に、図23および図24に示すように、マルチ配線基板100をモールド金型（図示せず）に装着し、マルチ配線基板100の主面全体を一括して樹脂封止する。モールド樹脂50

3は、例えば粒径 $70\text{ }\mu\text{m} \sim 100\text{ }\mu\text{m}$ 程度のシリカを分散させた熱硬化型エポキシ系樹脂からなる。前述したように、チップ2A、2Bとマルチ配線基板100の隙間、およびチップ2Aとチップ2Bの隙間には、あらかじめアンダーフィル樹脂6が充填されているので、マルチ配線基板100の主面を樹脂封止したときに、これらの隙間に空気溜まり(ボイド)が生じることはない。

#### 【0046】

次に、図25に示すように、マルチ配線基板100の裏面の電極パッド9(図25には示さない)に半田バンプ11を接続する。半田バンプ11の接続は、例えば低融点のPb-Sn共晶合金からなる半田ボールを電極パッド9の表面に供給した後、半田ボールをリフローさせることによって行う。

10

#### 【0047】

次に、図26に示すように、マルチ配線基板100を前記図4、図5に示すダイシングラインLに沿って切断、個片化することにより、前記図1～図3に示した本実施形態のマルチチップモジュール(MCM)が完成する。マルチ配線基板100を切断するときには、マルチ配線基板100のダイシングラインLに形成された溝101(図6および図7参照)の幅よりも狭い幅のダイシングブレードを使用する。このようにすると、パッケージ基板1の側面の一部がモールド樹脂3で覆われる(図2参照)ので、パッケージ基板1の側面から内部に浸入する水分の量が低減され、マルチチップモジュール(MCM)の信頼性が向上する。個片化されたマルチチップモジュール(MCM)は、例えば、プリント配線基板(PCB)等の実装用意基板に、半田バンプ11を介して実装される。

20

#### 【0048】

##### (実施の形態2)

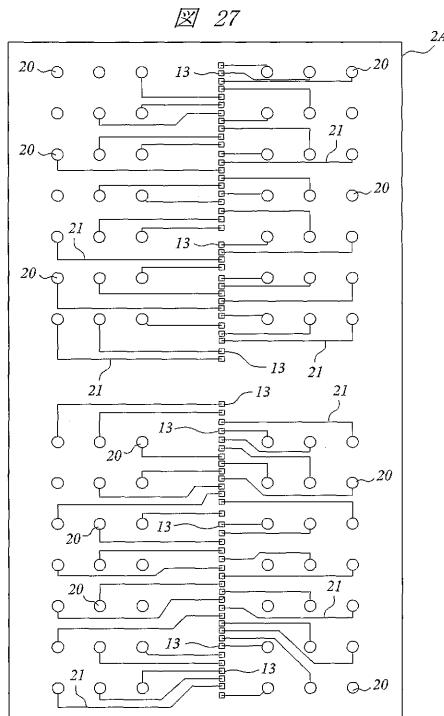

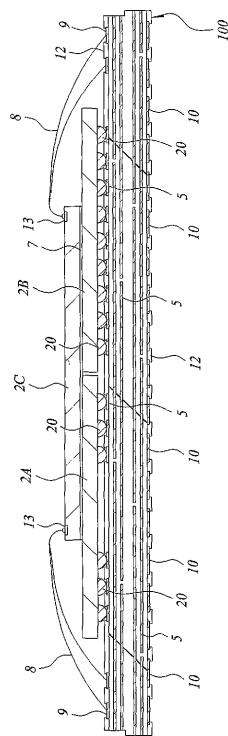

本実施形態の半導体装置の製造方法を図27～図34を用いて工程順に説明する。

#### 【0049】

前記実施の形態1では、DRAMが形成されたチップ2Aの主面およびフラッシュメモリが形成されたチップ2Bの主面にそれぞれAuバンプ4を形成したが、本実施形態では、Auバンプ4に代えて半田バンプ20を使用する。

#### 【0050】

図27は、DRAMが形成されたチップ2Aの主面に半田バンプ20を形成した状態を示す平面図である。図示のように、半田バンプ20は、チップ2Aの主面にアレイ状に配置されている。ボンディングパッド13と半田バンプ20とは、再配線と呼ばれるCu配線21を介して電気的に接続されている。Cu配線21は、ボンディングパッド13のピッチを半田バンプ20のピッチに変換するインターポーザとして機能し、これによって半田バンプ20のピッチをボンディングパッド13のピッチよりも広くすることができるの、パッケージ基板1として高価なビルドアップ基板を使用しなくともよく、配線5のピッチが広い安価な樹脂基板を使用することができる。

30

#### 【0051】

Cu配線21および半田バンプ20は、ウエハプロセスの最終工程で形成される。すなわち、Cu配線21は、ウエハの表面保護膜上にポリイミド樹脂などの有機絶縁膜を形成した後、この有機絶縁膜上に電解メッキ法などを用いて形成される。Cu配線21とボンディングパッド13は、ボンディングパッド13上の有機絶縁膜に形成したスルーホールを通じて電気的に接続される。また、半田バンプ20は、Cu配線21の一端にスクリーン印刷法で半田ペーストを印刷し、次に、ウエハを加熱してこの半田ペーストを溶融させることによって形成する。半田バンプ20は、例えば2重量%のSnを含むPb-Sn合金(液相線温度320～325)などで構成する。なお、図示は省略するが、フラッシュメモリが形成されたチップ2Bの主面にも同様の方法でCu配線21および半田バンプ20を形成する。

40

#### 【0052】

次に、図28に示すように、マルチ配線基板100のそれぞれのパッケージ基板形成領域にチップ2A、2Bを位置決めした後、マルチ配線基板100を電気炉内で340程度

50

に加熱して半田バンプ 20 をリフローすることによって、チップ 2A、2B の半田バンプ 20 とマルチ配線基板 100 の配線 5 とを電気的に接続する。

#### 【0053】

次に、図 29 に示すように、2 個のチップ 2A、2B の上にチップ 2C を搭載する。チップ 2A、2B とチップ 2C との接着は、前記実施の形態 1 と同様、チップ 2C の裏面に貼り付けた接着剤 7 を使用する。

#### 【0054】

次に、図 30 および図 31 に示すように、マルチ配線基板 100 のボンディングパッド 9 とチップ 2C のボンディングパッド 13 とを Au ワイヤ 8 で接続する。Au ワイヤ 8 の接続は、前記実施の形態 1 と同様、例えば超音波振動と熱圧着とを併用したワイヤボンダを使用して行う。

10

#### 【0055】

次に、図 32 に示すように、チップ 2A、2B の周辺部にディスペンサなどを使って液状のアンダーフィル樹脂 6 を供給した後、アンダーフィル樹脂 6 を加熱、硬化させることによって、チップ 2A、2B とマルチ配線基板 100 の隙間、およびチップ 2A とチップ 2B の隙間にアンダーフィル樹脂 6 を充填する。液状のアンダーフィル樹脂 6 は流動性が高く、また添加されているシリカフィラーの粒径は、チップ 2A とチップ 2B の隙間 (20 μm ~ 100 μm 程度) よりも小さい (3 μm 程度) ため、チップ 2A とチップ 2B の隙間をアンダーフィル樹脂 6 で完全に充填することができる。

#### 【0056】

また、本実施形態では、液状のアンダーフィル樹脂 6 をチップ 2A、2B の周辺部に供給する際、パッケージ基板形成領域の周辺部にも供給し、ボンディングパッド 13 の表面がアンダーフィル樹脂 6 で覆われるようとする。アンダーフィル樹脂 6 は、全てのボンディングパッド 13 の表面を完全に覆う必要はない。この状態でアンダーフィル樹脂 6 を硬化すると、ボンディングパッド 13 の表面に接続された Au ワイヤ 8 の一端部がアンダーフィル樹脂 6 によって固定されるため、ボンディングパッド 13 と Au ワイヤ 8 の接続信頼性が向上する。また、アンダーフィル樹脂 6 を充填前にワイヤボンディング工程が完了しているので、アンダーフィル樹脂 6 により基板上の形成された電極パッドの汚染も回避できる。

20

#### 【0057】

次に、図 33 に示すように、マルチ配線基板 100 をモールド金型 (図示せず) に装着し、マルチ配線基板 100 の主面全体を一括して樹脂封止する。モールド樹脂 3 は、例えば粒径 70 μm ~ 100 μm 程度のシリカを分散させた熱硬化型エポキシ系樹脂からなる。前述したように、チップ 2A、2B とマルチ配線基板 100 の隙間、およびチップ 2A とチップ 2B の隙間には、あらかじめアンダーフィル樹脂 6 が充填されているので、マルチ配線基板 100 の主面を樹脂封止したときに、これらの隙間に空気溜まり (ボイド) が生じることはない。また、本実施形態では、Au ワイヤ 8 の一端部がアンダーフィル樹脂 6 によってボンディングパッド 13 の表面に固定されているので、溶融したモールド樹脂 3 をモールド金型内に注入した時の圧力による Au ワイヤ 8 の断線を確実に防止することができる。

30

#### 【0058】

次に、図 34 に示すように、マルチ配線基板 100 の裏面の電極パッド 10 に半田バンプ 11 を接続する。図示は省略するが、その後、前記実施の形態 1 と同様の方法でマルチ配線基板 100 を切断することにより、本実施形態のマルチチップモジュール (MCM) が完成する。

40

#### 【0059】

##### (実施の形態 3)

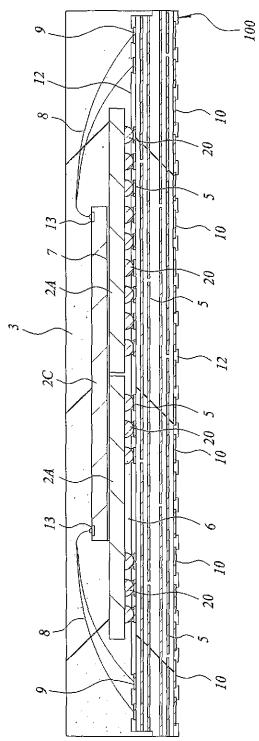

本実施形態の半導体装置の製造方法を図 35 ~ 図 37 を用いて工程順に説明する。

#### 【0060】

まず、図 35 に示すように、チップ 2A、2B の半田バンプ 20 とマルチ配線基板 100

50

の配線 5 とを電気的に接続し、続いて 2 個のチップ 2 A、2 B の上に接着剤 7 を介してチップ 2 C を搭載した後、マルチ配線基板 100 のボンディングパッド 9 とチップ 2 C のボンディングパッド 13 とを Au ワイヤ 8 で接続する。ここまででの工程は、前記実施の形態 2 の図 27～図 31 に示した工程と同じである。

#### 【0061】

次に、図 36 に示すように、マルチ配線基板 100 をモールド金型（図示せず）に装着し、マルチ配線基板 100 の正面全体を一括して樹脂封止する。このとき、本実施形態では、前記実施の形態 1、2 で用いたアンダーフィル樹脂 6 と同様、添加されているシリカフィラーラーの粒径が 3 μm 程度のモールド樹脂 3 を使用する。このモールド樹脂 3 に添加されているシリカフィラーラーの粒径は、チップ 2 A とチップ 2 B の隙間（20 μm～100 μm 程度）よりも小さいため、チップ 2 A、2 B とマルチ配線基板 100 の隙間、およびチップ 2 A とチップ 2 B の隙間をモールド樹脂 3 で完全に充填することができる。このモールド樹脂 3 は、前記実施の形態 1、2 で用いた粒径 70 μm～100 μm 程度のシリカが添加されたモールド樹脂 3 に比べて高価であるが、チップ 2 A、2 B とマルチ配線基板 100 の隙間、およびチップ 2 A とチップ 2 B の隙間にアンダーフィル樹脂 6 を充填する工程を省略することができる。10

#### 【0062】

次に、図 37 に示すように、前記実施の形態 1、2 と同様の方法でマルチ配線基板 100 の裏面の電極パッド 9 に半田バンプ 11 を接続する。図示は省略するが、その後、前記実施の形態 1、2 と同様の方法でマルチ配線基板 100 を切断することにより、本実施形態のマルチチップモジュール（MCM）が完成する。20

#### 【0063】

##### （実施の形態 4）

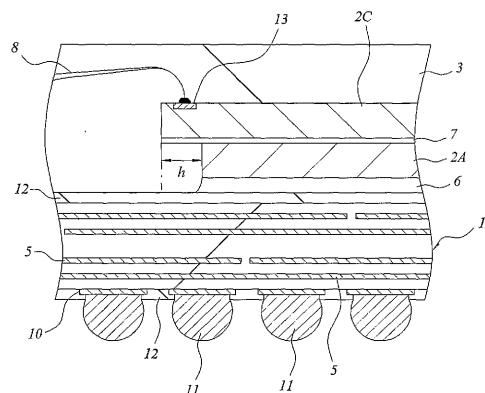

図 38 は、本実施形態の半導体装置を示す断面図、図 39 は、図 38 の一部を拡大して示す断面図である。

#### 【0064】

本実施形態の半導体装置は、DRAM が形成された 1 個のチップ 2 A をパッケージ基板 1 の正面に実装すると共に、高速マイクロプロセッサ（MPU）が形成された 1 個のチップ 2 C をチップ 2 A の上部に積層し、これら 2 個のチップ 2 A、2 C をモールド樹脂 3 で封止したマルチチップモジュール（MCM）である。30

#### 【0065】

下層のチップ 2 A は、パッケージ基板 1 の正面に形成された Au バンプ 4 を介してパッケージ基板 1 の配線 5 と電気的に接続されている。すなわち、チップ 2 A は、フリップチップ方式によって実装されている。チップ 2 A の正面（下面）とパッケージ基板 1 の正面との隙間には、アンダーフィル樹脂 6 が充填されている。

#### 【0066】

上層のチップ 2 C は、接着剤 7 によってチップ 2 A の上面に接着されている。チップ 2 C の正面に形成されたボンディングパッド 13 は、複数本の Au ワイヤ 8 によってパッケージ基板 1 のボンディングパッド 9 と電気的に接続されている。すなわち、チップ 2 C は、ワイヤボンディング方式によって実装されている。40

#### 【0067】

上記 2 個のチップ 2 A、2 C を実装するパッケージ基板 1 の下面には、上記配線 5 に電気的に接続された複数の電極パッド 10 がアレイ状に配置されており、それぞれの電極パッド 10 には、マルチチップモジュール（MCM）の外部接続端子（ピン）を構成する半田バンプ 11 が接続されている。パッケージ基板 1 の正面および下面には、配線 5 とチップ 2 A との接続部、ボンディングパッド 9、電極パッド 10 などの表面を除き、エポキシ系樹脂やアクリル系樹脂などからなるソルダレジスト 12 がコーティングされている。

#### 【0068】

前記図 13 に示すように、DRAM が形成されたチップ 2 A は、長方形の平面形状を有し、その正面の中央には複数の Au バンプ 4 が一列に配置されている。また、前記図 18 に50

示すように、マイクロプロセッサが形成されたチップ2Cは、略正方形の平面形状を有し、その正面の4辺に沿ってボンディングパッド13が形成されている。チップ2Cに形成されたボンディングパッド13の数は、チップ2Aに形成されたボンディングパッド(Auバンプ4)の数よりも多い。

#### 【0069】

前述したように、ボンディングパッド数が少なく、ボンディングパッドの最小ピッチが大きいチップ2Aと、ボンディングパッド数が多く、ボンディングパッドの最小ピッチが小さいチップ2Cを積層する場合は、ボンディングパッドの最小ピッチが大きいチップ2AをAuバンプ4によってフェースダウン実装し、ボンディングパッドの最小ピッチが小さいチップ2Cをワイヤボンディングによりフェースアップ実装する。これにより、パッケージ基板1に対する配線密度の要求を緩くすることができるので、パッケージ基板1としてより安価なものを使用することが可能となり、低成本で高密度実装が可能なパッケージを提供することができる。10

#### 【0070】

図39に示すように、上記のような長方形の平面形状を有する1個のチップ2Aの上に略正方形の平面形状を有するチップ2Cを積層する場合には、上層のチップ2Cの周辺部が下層のチップ2Aの周辺部よりも外側に張り出す(オーバーハング)ことがある。

#### 【0071】

このとき、上層のチップ2Cのオーバーハング量が大きいと、このチップ2Cの周辺部に形成されたボンディングパッド13上にAuワイヤ13をボンディングする際に、チップ2Cの周辺部に加わる荷重によってチップ2Cが割れる虞れがある。その対策として、下層のチップと基板との隙間に充填する樹脂の量を多くすることによって、チップ2Cの周辺部直下にも充填してやる方法が考えられる(特開2000-299431号公報)。この方法によれば、ワイヤボンディング時に上層のチップ2Cの周辺部に荷重が加わっても、チップ2Cの周辺部は樹脂によって支持されているので、チップ2Cの割れを防ぐことができる。20

#### 【0072】

しかし、上記した対策は、アンダーフィル樹脂6の供給量の制御によって、下層チップ2Aからその外周へのアンダーフィル樹脂6のはみ出し量を制御するものであるので、そのはみ出し量の正確な制御は困難である。特に、下層チップ2Aの接着工程において、過剰なアンダーフィル樹脂6のはみ出しによって、パッケージ基板1主面上のボンディングパッド9を汚染してしまうと、その後のワイヤボンディング工程においてボンディングワイヤとボンディングパッド9との非接続不良を招く虞れがある。また、このような問題を解決するために、たとえ過剰なアンダーフィル樹脂9のはみ出しがあってもボンディングパッド9が汚染されないように、上層チップ2Cのボンディングパッド13が配置される領域からボンディングパッド9までの距離を充分に確保しようとすると、パッケージ基板1の大型化、ひいてはMCMの大型化につながり、好ましくない。30

#### 【0073】

そこで、本実施形態では、図39に示すように、アンダーフィル樹脂6のはみ出し量のばらつきがあったとしてもボンディングパッド9の汚染が発生しないように、上層チップ2Cが下層チップ2Aの外側にオーバーハングしている場合において、上層チップ2Cのボンディングパッド13をアンダーフィル樹脂6のはみ出し部で支えない構成にすると共に、ワイヤボンディング工程時の上層チップ2Cの割れを防ぐために、上層チップ2Cが支えられていない部分の長さ(h)を最大でも1.5mm以下、好ましくは1mm以下に設定する。40

#### 【0074】

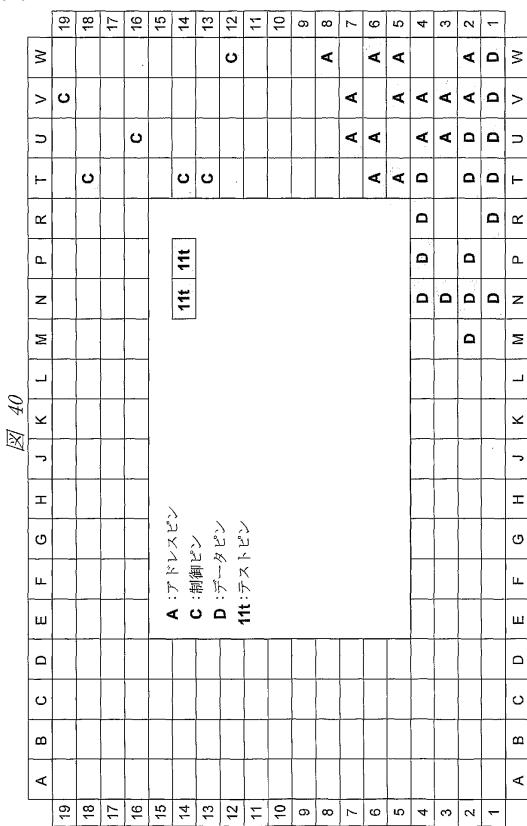

図40は、本実施形態によるマルチチップモジュール(MCM)のピン(端子)配置図である。

#### 【0075】

本実施形態のマルチチップモジュール(MCM)に使用されるパッケージ基板1は、高速50

マイクロプロセッサ（M P U）が形成された1個のチップ2Cを実装するために設計されたパッケージ基板と共に共通のピン配置を有している。従って、図40に示すピンのうち、2個のチップ2A、2Cに共通するピンである制御ピン（C A S L、R A S L、C S 3、R D W R、W E 1、W E 0：以下、全てCと表記）、アドレスピン（A 0～A 1 4：以下、全てAと表記）およびデータピン（D 0～D 1 5：以下、全てDと表記）のそれぞれは、共通の配線5で接続される。

#### 【0076】

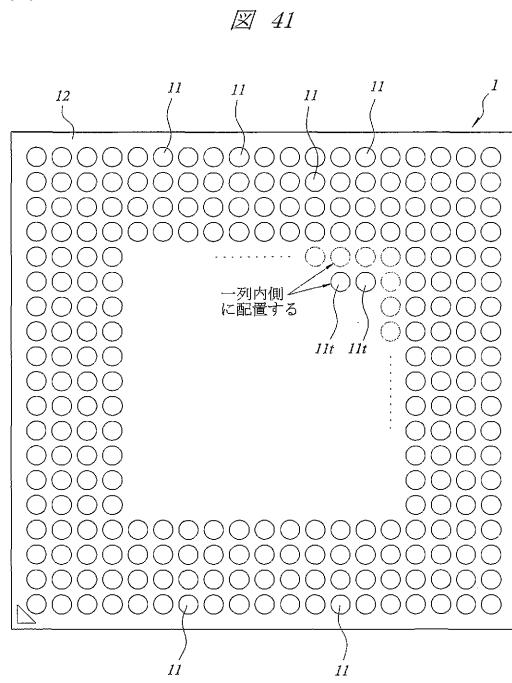

また、チップ2Cの他にチップ2Aを実装してマルチチップモジュール（M C M）を構成する場合、パッケージ基板1にはチップ2Cの電気特性をテストするピンの他にチップ2Aの特性をテストするピン（D R A Mの場合、2個程度）が必要になる。そこで、本実施形態では、図41に示すように、チップ実装領域の直下にチップ2Aのテストピン11tを配置する。10

#### 【0077】

この場合、パッケージ基板1の中央付近にテストピン11tを配置するとテストピン11tに接続される配線5が長くなるので、パッケージ基板1の配線設計が困難となる。他方、テストピン11tに接続される配線5の長さを最短距離にするために、他のピン（半田バンプ11）が配置されている領域に隣接してテストピン11tを配置すると、他のピン（半田バンプ11）とテストピン11tとの距離が狭くなるので、テストピン11tに隣接する他のピンに接続される配線5のレイアウトが困難となり、この場合は、M C Mを実装するための実装基板の配線設計が困難となる。20

#### 【0078】

上記のような問題を解決するためには、図41に示すように、他のピン（半田バンプ11）が配置されている領域に隣接してテストピン11tを配置するのではなく、それよりもさらに1列内側にテストピン11tを配置するのがよい。また、他のピン（半田バンプ11）の中にノンコネクトピンが2個以上ある場合は、このノンコネクトピンが配置される領域にテストピン11tを配置すればよい。

#### 【0079】

このように、高速マイクロプロセッサ（M P U）が形成された1個のチップ2Cを実装するために設計されたパッケージ基板と共に共通のピン配置（テストピン11tを除く）を有するパッケージ基板1を使ってマルチチップモジュール（M C M）を構成することにより、パッケージ基板1の設計コストを低減することができる。また、パッケージ基板1の使い勝手も向上する。30

#### 【0080】

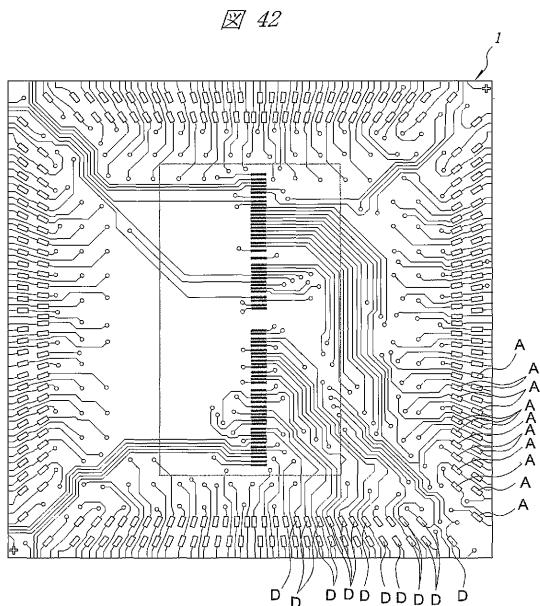

図42は、パッケージ基板1のアドレスピン（A）群とデータピン（D）群の配置を示している。図に示すように、高速マイクロプロセッサ（M P U）のようにピン数の多いチップ2Cを実装するパッケージ基板1は、一般に、アドレスピン（A）同士、データピン（D）同士をそれぞれ特定の領域に集中して配置すると共に、アドレスピン（A）群とデータピン（D）群を隣接して配置することによって、例えばパッケージ基板1を外付けのメモリチップと接続する際の配線長を短縮できるようにしている。

#### 【0081】

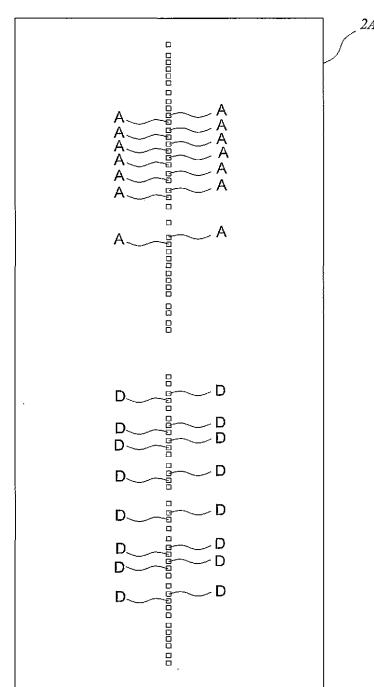

一方、図43に示すように、D R A Mが形成されたチップ2Aは、一般に、チップ2Aの長辺方向の一端側にアドレスピン（A）群を配置し、他端側にデータピン（D）群を配置する。

#### 【0082】

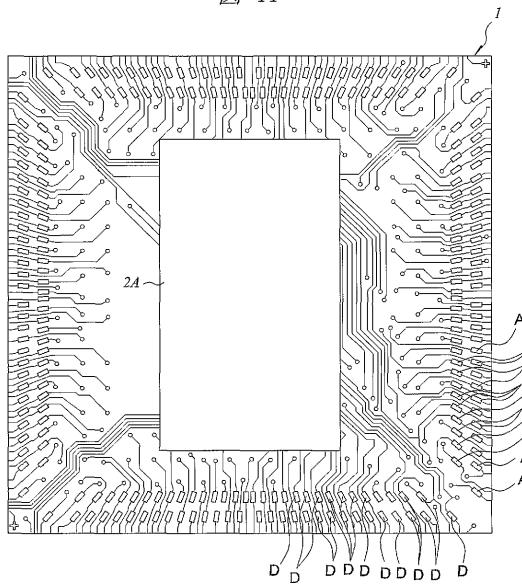

従って、本実施形態のように、チップ2Aの上にチップ2Cを積層してマルチチップモジュール（M C M）を構成する場合は、図44に示すように、パッケージ基板1のアドレスピン（A）群とチップ2Aのアドレスピン（A）群およびパッケージ基板1のデータピン（D）群とチップ2Aのデータピン（D）群がそれぞれ近接して配置されるように、チップ2Aの向きをレイアウトするのがよい。

#### 【0083】

10

20

30

40

50

これにより、パッケージ基板1のアドレスピン( A )群とチップ2Aのアドレスピン( A )群とを接続する配線5群、およびパッケージ基板1のデータピン( D )群とチップ2Aのデータピン( D )群とを接続する配線5群をパッケージ基板1上で互いに交差しないようにレイアウトすることができるので、パッケージ基板1の配線設計が容易になる。

#### 【 0 0 8 4 】

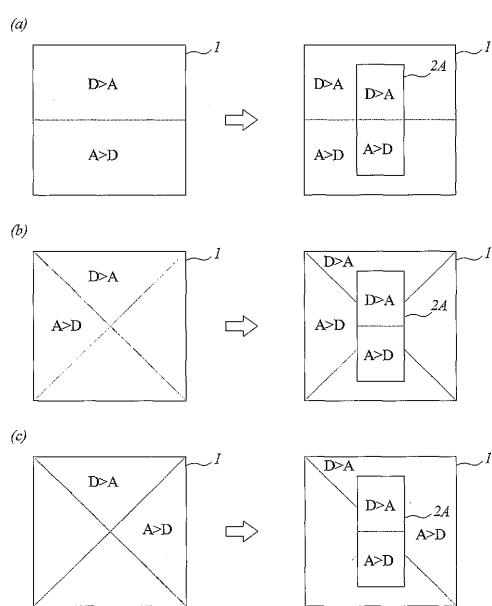

図45(a)～(c)は、パッケージ基板1のアドレスピン( A )群とデータピン( D )群のレイアウトを例示したものである。ここで、符号( D > A )を付した領域は、主としてデータピン( D )群が配置された領域、符号( A > D )を付した領域は、主としてアドレスピン( A )群が配置された領域を示している。これらの例では、DRAMが形成されたチップ2Aを、図に示したような向きにレイアウトすることにより、パッケージ基板1のアドレスピン( A )群とチップ2Aのアドレスピン( A )群とを接続する配線5群、およびパッケージ基板1のデータピン( D )群とチップ2Aのデータピン( D )群とを接続する配線5群をパッケージ基板1上で互いに交差しないようにレイアウトすることができる。

10

#### 【 0 0 8 5 】

本実施形態は、DRAMが形成されたチップ2Aの上にチップ2Cを積層したマルチチップモジュール(MCM)であるが、例えば前記図14に示すようなフラッシュメモリが形成されたチップ2B上にチップ2Cを積層してマルチチップモジュール(MCM)を構成する場合も、チップ2Bの向きを上記と同じようにレイアウトするのがよい。

20

#### 【 0 0 8 6 】

すなわち、前記図14に示すようなフラッシュメモリが形成されたチップ2Bにおいては、一般に対向する2つの短辺の一方にアドレスピン( A )群が配置され、他方にデータピン( D )群が配置される。従って、この場合も、パッケージ基板1のアドレスピン( A )群とチップ2Bのアドレスピン( A )群、およびパッケージ基板1のデータピン( D )群とチップ2Bのデータピン( D )群がそれぞれ近接して配置されるように、チップ2Bの向きをレイアウトすることにより、パッケージ基板1のアドレスピン( A )群とチップ2Bのアドレスピン( A )群とを接続する配線5群、およびパッケージ基板1のデータピン( D )群とチップ2Bのデータピン( D )群とを接続する配線5群をパッケージ基板1上で互いに交差しないようにレイアウトすることができる。

30

#### 【 0 0 8 7 】

また、前記実施の形態1のマルチチップモジュール(MCM)のように、DRAMが形成されたチップ2Aおよびフラッシュメモリが形成されたチップ2Bの上に高速マイクロプロセッサ(MPU)が形成されたチップ2Cを積層する場合に前記MPUチップ2Cの土台となるチップ2Aおよび2Bの中心がパッケージ基板1の中心と一致しない場合がある。通常、配線基板上にチップを積層する場合、土台となるチップの中心に、積層されるチップの中心を合わせて配置するのが一般的であるが、前記DRAMチップ2Aおよびフラッシュチップ2Bに比較してピン数が多く、また最小ボンディングパッドピッチも小さいMPUチップ2Cの配置を、土台となるチップの中心に合わせるために、モジュール基板1の中心からずらしてしまうと、ボンディングワイヤ長さの不均一などの問題を招いてしまうという問題がある。

40

#### 【 0 0 8 8 】

すなわち、MPUチップ2Cとの接続に必要なモジュール基板1上のボンディングパッド9は、その数が非常に多いために、なるべくモジュール基板1の外周に沿って配置する事で、そのボンディングパッド9の間隔を確保することができる。しかし、MPUチップ2Cの配置がモジュール基板1の中心からずれるほど、MPUチップ2Cの外周に沿って配置されたボンディングパッド13と、モジュール基板1上のボンディングパッド9との距離が不均一になるため、ボンディングワイヤ8の長さに偏りが出て、特にボンディングワイヤ8が長くなった部分での樹脂封止時のワイヤ流れ、ショートなどの問題が発生するおそれがある。

#### 【 0 0 8 9 】

50

このような問題を解決するために、M P Uチップ2Cの中心がモジュール基板1の中心からはずれたままで、ボンディングパッド13とボンディングパッド9の距離を均一にするためには、ボンディングパッド9の間隔を狭めて、モジュール基板1の主面上に納まるよう配置するか、もしくはボンディングパッド9が全て配置できるようにモジュール基板1を大型化する必要がある。

#### 【0090】

従って、基板の中心からはずれた位置に配置されたチップ2A、チップ2Bの上にチップ2Cを積層する場合でも、チップ2Cのピン数がチップ2A、チップ2Bに比較して多く、チップ2Cに対応するボンディングパッド9のピッチをより緩和する必要がある場合には、チップ2Cの中心をチップ2Aの中心よりもパッケージ基板1の中心に近づけるように積層することが望ましい。10

#### 【0091】

以上、本発明者によってなされた発明を前記実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【0092】

例えば前記実施の形態4のように、D R A Mが形成された1個のチップ2AとM P Uが形成された1個のチップ2Cと組み合わせてマルチチップモジュール(M C M)を構成するような場合は、図46に示すように、パッケージ基板1の主面上にD R A Mが形成された1個のチップ2Aとダミーのチップ2Dとを並べて配置し、これら2個のチップ2A、2Dの上部にチップ2Cを積層してもよい。この場合、ダミーのチップ2Dは、例えば集積回路が形成されていない鏡面ウエハをダイシングして形成し、その厚さを、チップ2Aの厚さとA uバンプ4の高さを合計した厚さと同じにする。このような実装方法は、例えば上層のチップ2Cの外径寸法が下層のチップ2Aの外径寸法よりも相当大きく、前記図39で説明した下層のチップ2Aに対する上層のチップ2Cのオーバーハング量(h)が1.5mm以下に設定できないような場合に有効である。20

#### 【0093】

パッケージ基板上にフリップチップ方式で実装するチップは、D R A M単独、フラッシュメモリ単独、D R A Mとフラッシュメモリの組み合わせに限定されるものではなく、D R A M同士、フラッシュメモリ同士、D R A MまたはフラッシュメモリとS R A M(Static Random Access Memory)など、各種メモリチップを任意に組み合わせることが可能である。また、メモリチップの上に積層するチップもマイクロプロセッサやA S I Cに限定されるものではなく、メモリチップよりもピッチの狭いL S Iが形成されたチップを使用することが可能である。さらに、パッケージ基板上に実装するチップの数も2個あるいは3個に限定されるものではない。30

#### 【0094】

パッケージ基板上には、コンデンサや抵抗素子など、チップ以外の小型電子部品を実装することもできる。例えば、メモリチップの外周に沿ってチップコンデンサを搭載することにより、メモリチップの駆動時に生じるノイズを低減して高速動作を実現することができる。40

#### 【0095】

また、チップを実装するパッケージ基板としてビルドアップ基板を使用したり、パッケージ基板の一部に放熱用のキャップを取り付けたりするなど、本発明の要旨を変更しない範囲で種々の設計変更を行うことができる。

#### 【発明の効果】

#### 【0096】

本発明の好ましい一実施態様によれば、複数個のチップの上に他のチップを積層して樹脂封止したマルチチップモジュールの信頼性を向上させることができる。

#### 【0097】

本発明の好ましい他の実施態様によれば、複数個のチップの上に他のチップを積層して樹50

脂封止したマルチチップモジュールの製造コストを低減することができる。

【図面の簡単な説明】

【0098】

【図1】本発明の一実施形態である半導体装置の平面図である。

【図2】本発明の一実施形態である半導体装置の断面図である。

【図3】本発明の一実施形態である半導体装置の平面図である。

【図4】本発明の一実施形態である半導体装置の製造に用いるマルチ配線基板の平面図である。

【図5】本発明の一実施形態である半導体装置の製造に用いるマルチ配線基板の平面図である。 10

【図6】図5に示すマルチ配線基板の要部拡大平面図である。

【図7】図5に示すマルチ配線基板の要部拡大断面図である。

【図8】図5に示すマルチ配線基板の要部拡大平面図である。

【図9】本発明の一実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。 20

【図10】本発明の一実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大平面図である。

【図11】本発明の一実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。

【図12】本発明の一実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大平面図である。 20

【図13】本発明の一実施形態である半導体装置の製造に用いる半導体チップの平面図である。

【図14】本発明の一実施形態である半導体装置の製造に用いる半導体チップの平面図である。

【図15】本発明の一実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。

【図16】本発明の一実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。 30

【図17】本発明の一実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大平面図である。

【図18】本発明の一実施形態である半導体装置の製造に用いる半導体チップの平面図である。

【図19】本発明の一実施形態である半導体装置の製造方法を示す半導体ウエハの斜視図である。

【図20】本発明の一実施形態である半導体装置の製造方法を示す半導体ウエハの側面図である。

【図21】本発明の一実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。

【図22】本発明の一実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大平面図である。 40

【図23】本発明の一実施形態である半導体装置の製造方法を示すマルチ配線基板の平面図である。

【図24】本発明の一実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。

【図25】本発明の一実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。

【図26】本発明の一実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。

【図27】本発明の他の実施形態である半導体装置の製造に用いる半導体チップの平面図 50

である。

【図28】本発明の他の実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。

【図29】本発明の他の実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。

【図30】本発明の他の実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。

【図31】本発明の他の実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大平面図である。

【図32】本発明の他の実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。 10

【図33】本発明の他の実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。

【図34】本発明の他の実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。

【図35】本発明の他の実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。

【図36】本発明の他の実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。

【図37】本発明の他の実施形態である半導体装置の製造方法を示すマルチ配線基板の要部拡大断面図である。 20

【図38】本発明の他の実施形態である半導体装置の断面図である。

【図39】図38の一部を拡大して示す断面図である。

【図40】本発明の他の実施形態である半導体装置のピン(端子)配置図である。

【図41】本発明の他の実施形態である半導体装置におけるテストピンの配置を示すマルチ配線基板の平面図である。

【図42】本発明の他の実施形態である半導体装置におけるアドレスピン群とデータピン群の配置を示すマルチ配線基板の平面図である。

【図43】、メモリチップのアドレスピン群とデータピン群の配置を示す平面図である。

【図44】本発明の他の実施形態である半導体装置におけるメモリチップの最適実装方向を示す平面図である。 30

【図45】(a)～(c)は、本発明の他の実施形態である半導体装置におけるメモリチップの最適実装方向を示す概略平面図である。

【図46】本発明の他の実施形態である半導体装置の断面図である。

#### 【符号の説明】

##### 【0099】

1 パッケージ基板

2 A、2 B、2 C チップ

2 D ダミーのチップ

3 モールド樹脂

4 Auバンプ

5 配線

6 アンダーフィル樹脂(封止樹脂)

6 a 樹脂テープ

7 接着剤

8 Auワイヤ

9 ボンディングパッド

10 電極パッド

11 半田バンプ

11 t テストピン

10

20

30

40

50

- |       |           |

|-------|-----------|

| 1 2   | ソルダレジスト   |

| 1 3   | ボンディングパック |

| 1 4   | ウエハ       |

| 1 5   | ダイシングテープ  |

| 2 0   | 半田バンブ     |

| 2 1   | C u 配線    |

| 1 0 0 | マルチ配線基板   |

| 1 0 1 | 溝         |

| 1 0 2 | ヒートツール    |

| L     | ダイシングライン  |

10

【 四 1 】

図 1

【 図 2 】

2

【図3】

図3

【図4】

【図5】

【図6】

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

【図12】

【図13】

【図14】

【図15】

図15

【図16】

図16

【図17】

図17

図17

【図18】

図18

【図19】

図19

図19

【図20】

図20

【図21】

図21

【図22】

図22

【図23】

図23

【図24】

図24

【図25】

図25

【図26】

図26

【図27】

【図 28】

図 28

【図 29】

図 29

【図 30】

図 30

【図 31】

図 31

【図32】

四三二

【図33】

四

33

【図34】

四

34

【図35】

35

【図36】

図36

【図37】

図37

【図38】

図38

【図39】

図39

【図40】

【図41】

【図42】

【図43】

【図 4 4】

図 44

【図 4 5】

図 45

【図 4 6】

図 46

---

フロントページの続き

(72)発明者 池上 光

東京都小平市上水本町五丁目20番1号 株式会社日立製作所 半導体グループ内

(72)発明者 菊池 隆文

東京都小平市上水本町五丁目20番1号 株式会社日立製作所 半導体グループ内

審査官 今井 拓也

(56)参考文献 特開2000-299431(JP, A)

国際公開第99/026285(WO, A1)

特開2001-044358(JP, A)

特開平07-086492(JP, A)

特開2002-026236(JP, A)

国際公開第01/018864(WO, A1)

特開2001-056346(JP, A)

特開2000-332193(JP, A)

特開2000-243900(JP, A)

特開2001-094042(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/065

H01L 25/07

H01L 25/18