(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5665263号

(P5665263)

(45) 発行日 平成27年2月4日(2015.2.4)

(24) 登録日 平成26年12月19日(2014.12.19)

(51) Int.Cl.

F 1

G 11 C 29/12 (2006.01)

G 11 C 29/00

6 7 1 Z

G 11 C 11/401 (2006.01)

G 11 C 11/34

3 7 1 A

G 11 C 11/407 (2006.01)

G 11 C 11/34

3 6 2 T

請求項の数 11 (全 23 頁)

(21) 出願番号

特願2008-143580 (P2008-143580)

(22) 出願日

平成20年5月30日 (2008.5.30)

(65) 公開番号

特開2009-289374 (P2009-289374A)

(43) 公開日

平成21年12月10日 (2009.12.10)

審査請求日

平成23年3月9日 (2011.3.9)

(73) 特許権者 513192281

ピースフォー ルクスコ エスエイアールエル

P S 4 L u x c o S. a. r. l.

ルクセントルク大公国エル-2121、ル

クセントルク、ヴァル デ ポン マラテ

ス208

(74) 代理人 100101454

弁理士 山田 卓二

(72) 発明者 石川 透

東京都中央区八重洲二丁目2番1号 エル

ピーダメモリ株式会社内

(72) 発明者 小林 勝太郎

東京都中央区八重洲二丁目2番1号 エル

ピーダメモリ株式会社内

最終頁に続く

(54) 【発明の名称】半導体記憶装置、及び該半導体記憶装置のテスト方法

(57) 【特許請求の範囲】

【請求項 1】

第1メモリ部と、

第1ビット数からなる第1データと、

前記第1ビット数より小さい第2ビット数からなる第2データと、

制御回路と、を備え、

前記制御回路は、複数の前記第2データに基づいて前記第1データを生成し、前記生成された第1データを前記第1メモリ部に並列して書き込み、

さらに、第2メモリ部と、を備え、

前記制御回路は、

前記第1メモリ部に書き込まれた前記第1データのビットを前記第1メモリ部から並列して読み出し、

前記第1メモリ部から読み出された前記第1データに基づいて前記第1ビット数を有する第3データを生成し、

前記生成された第3データのビットを前記第2メモリ部に並列して書き込む、ことを特徴とする半導体記憶装置。

【請求項 2】

前記第2ビット数と同数のビット数からなる第4データと、を備え、

前記制御回路は、

前記第2メモリ部に書き込まれた前記第3データのビットを前記第2メモリ部から読み

10

20

出し、

前記読み出された第3データに基づいて複数の前記第4データを生成し、

さらに、前記半導体記憶装置の故障検出テストとして前記第4データを所定のデータと一致するか否かをテストするテスターに、前記生成された複数の前記第4データをそれぞれ出力する、ことを特徴とする請求項1に記載の半導体記憶装置。

#### 【請求項3】

前記第2データ又は前記第4データを前記半導体記憶装置へ入出力するように構成した入出力端子を含み、

前記第1メモリ部は、前記第1データを第1メモリ部へ入出力するように構成した第1内部端子を含み、

前記第2メモリ部は、前記第3データを第2メモリ部へ入出力するように構成した第2内部端子を含み、

前記第1内部端子及び前記第2内部端子の数は、前記入出力端子の数より大きいことを特徴とする請求項2に記載の半導体記憶装置。

#### 【請求項4】

前記半導体記憶装置に供給されるリードコマンド及びライトコマンドを備え、

前記リードコマンドが前記半導体記憶装置に供給された後に前記ライトコマンドが前記半導体記憶装置に供給される場合に、

前記制御回路は、

前記ライトコマンドが前記半導体記憶装置に供給された後に、前記半導体記憶装置に供給されたリードコマンドを受け取るのに応じて前記第1メモリ部から前記第1データのビットを読み出し、

前記読み出しの後、前記半導体記憶装置に供給されたライトコマンドを受け取るのに応じて前記第2メモリ部へ前記第3データのビットを書き込むことを特徴とする請求項3に記載の半導体記憶装置。

#### 【請求項5】

前記第1データの前記第1ビット数は、複数の前記第2データの総ビット数と同数であることを特徴とする請求項4に記載の半導体記憶装置。

#### 【請求項6】

データを記憶するメモリ部と、

$n(n-2)$ 個のデータ入出力端子を介してnビット幅のデータを前記メモリ部にクロック信号に同期して入出力する手段と、

前記n個のデータ入出力端子のうちの予め選択されたm(m<n)個のデータ入出力端子を介して前記メモリ部にデータを入出力する手段と、

前記メモリ部の任意の記憶領域から順次前記nビット幅でデータを読み出し、前記読み出した該nビット幅のデータを前記記憶領域とは異なる記憶領域に記憶させるループバック回路と、

を備えることを特徴とする半導体記憶装置。

#### 【請求項7】

前記メモリ部は、前記nビット幅のデータの読み出し及び書き込みを独立に行うメモリブロックを複数有し、

前記ループバック回路は、前記メモリブロックから入力されるnビット幅のデータを異なる前記メモリブロックへ出力する

ことを特徴とする請求項6に記載の半導体記憶装置。

#### 【請求項8】

前記半導体記憶装置は、

書き込みコマンドが読み出しコマンド入力後予め定められたクロックサイクル経過後に入力されると、前記読み出しコマンドで指定される前記メモリ部の記憶領域から前記nビット幅のデータを読み出すと共に、前記ループバック回路を使用して読み出した該データを前記書き込みコマンドで指定される前記メモリ部の記憶領域に記憶させる

ことを特徴とする請求項 7 に記載の半導体記憶装置。

**【請求項 9】**

前記データ入出力端子は、データの入出力を行うデータ端子と共に、前記半導体記憶装置の故障検出テスト用データの入出力のみを行うテストデータ専用端子とを含み、

前記 n ビット幅のデータは、前記テストデータ専用端子を介して入力されたデータである

ことを特徴とする請求項 8 に記載の半導体記憶装置。

**【請求項 10】**

半導体記憶装置におけるテスト方法であって、

テスターからのテストデータの入出力としてはテストデータ専用端子のみ使用し、

10

前記テスターが、前記テストデータ専用端子から前記テストデータを入力し、メモリ部の第 1 の記憶領域に記憶させるテストデータ入力過程と、

前記メモリ部の前記第 1 の記憶領域から前記テストデータを読み出すと共に、ループバック回路を使用して読み出した該テストデータを前記メモリ部の前記第 1 の記憶領域とは異なる第 2 の記憶領域に記憶させる動作テスト過程と、

前記テスターが、前記メモリ部の前記第 2 の記憶領域から前記テストデータを前記テストデータ専用端子から読み出し、読み出した該テストデータが予め定めたデータと一致するか否かにより前記半導体記憶装置の故障を検出するテストデータ出力過程と

を有することを特徴とするテスト方法。

**【請求項 11】**

20

前記テストデータ入力過程又は前記テストデータ出力過程における前記半導体記憶装置に入力されるクロック信号の周波数は、前記動作テスト過程における前記半導体記憶装置に入力されるクロック周波数より遅い

ことを特徴とする請求項 10 に記載のテスト方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、主に半導体記憶装置、特に、動作テストに用いる入出力端子を削減することができる半導体記憶装置に関する。

**【背景技術】**

30

**【0002】**

従来の半導体記憶装置、例えば、DDR - SDRAMなど、のテストは、半導体記憶装置の所定の領域に外部からデータを書き込み、書き込んだデータを外部に読み出す動作を繰返すことで行っている。

**【0003】**

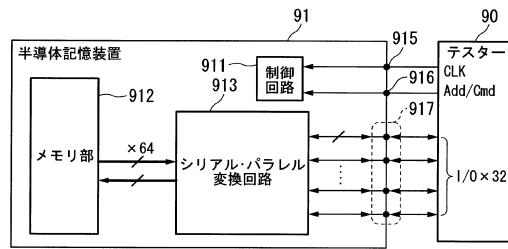

図 14 は、従来の半導体記憶装置 91、テスター 90、及び接続を示す概略図である。半導体記憶装置 91 は、制御回路 911、メモリセルアレイを含むメモリ部 912、シリアル・パラレル変換回路 913、クロック入力端子 915、制御信号入力端子 916、32 個の入出力端子を含むデータ入出力端子 917 を有している。

テスター 90 は、半導体記憶装置 91 にクロック信号、アドレス信号及び読み出しや書き込み等の動作を示すコマンド信号を含む制御信号を出力し、32 個の入出力ピンを用いて半導体記憶装置 91 のデータ入出力端子とデータの入出力を行う。

40

**【0004】**

半導体記憶装置 91において、制御回路 911 は、クロック信号入力端子 915 から入力されるクロック信号及び制御信号入力端子 916 から入力される制御信号に基づいて、メモリ部 912 の読み出し及び書き込みを行わせる。メモリ部 912 は、メモリセルアレイを含む。シリアル・パラレル変換回路 913 は、メモリ部 912 からクロック信号の立上がりにより入出力される 64 ビット幅のデータを、クロック信号の立上がり及び立下りにより入出力される 32 ビット幅の連続するデータに変換する。

**【0005】**

50

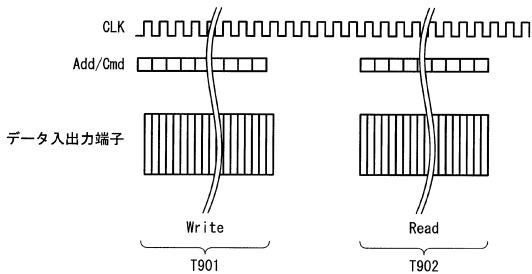

図15は、半導体記憶装置91とテスター90とを用いたテスト動作を示す概略図である。T901で図示される期間において、テスター90は、書き込みコマンドを含む制御信号及びクロック信号を半導体記憶装置91に出力すると共に、32ビット幅のデータを半導体記憶装置91に出力して書き込む。T902で図示される期間において、テスター90は、読み出しを示す制御信号及びクロック信号を半導体記憶装置91に出力すると共に、32ビット幅のデータが半導体記憶装置91から入力される。テスター90は、入力されたデータが予め定めたデータと一致するか否かを判定することで、半導体記憶装置91の不良を検出する。

#### 【0006】

このように半導体記憶装置のテストを行うと、半導体記憶装置のデータ入出力端子数の増加に応じて、半導体記憶装置に接続するために要するテスターの入出力端子が増加し、テスターに同時に接続できる半導体記憶装置の数が減る。これにより、テストに要する時間及びコストが増加するという問題がある。

例えば、256個の入出力端子を備えるテスターは、4ビット幅のデータ入出力端子を備える半導体記憶装置を64個同時にテストを行える。しかし、32ビット幅のデータ入出力端子を備える半導体記憶装置をテストする場合、同時にテストできる個数は8個となり、8分の1になってしまう。

#### 【0007】

また、別の問題として、高速に信号の入出力を行う半導体装置、例えば、533MHzや666MHzで動作するDDR-SDRAMの制御装置、をテストするには、短い時間で変化する信号を測定できる分解能が高い高精度のテスターが必要となる。そこで、高速な半導体装置の出力信号を入力信号として内部に戻すループバックを行う回路を用いることで、高精度のテスターを用いずともテストを行う技術がある（特許文献1）。

#### 【0008】

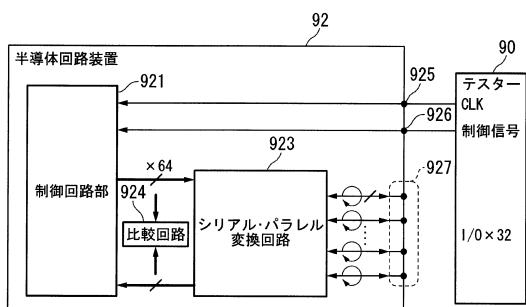

特許文献1では、図16に示すように、シリアル・パラレル変換回路923は、制御回路部921から入力されるデータを、比較回路924に出力する。比較回路924は、制御回路部921から入力されるデータと、シリアル・パラレル変換回路923から入力されるデータと比較する。このように、半導体回路装置92は、制御回路部921の出力するデータを比較することにより、半導体回路装置92とテスター90との間で高速に信号の入出力を行わざとも、半導体回路装置92をテストすることができる。

#### 【0009】

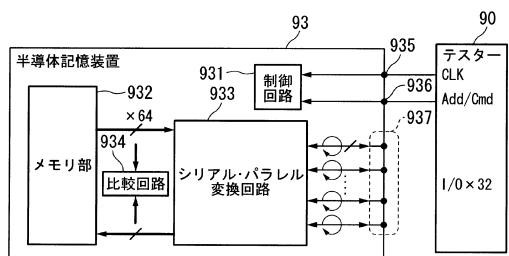

図17は、特許文献1の技術を適用した半導体記憶装置93とテスター90、及び接続を示した概略図である。半導体記憶装置93は、制御回路931、メモリ部932、シリアル・パラレル変換回路933、比較回路934、クロック入力端子935、制御信号入力端子936、データ入出力端子937を備えている。テスター90は、クロック信号と、アドレス信号及び読み出しや書き込み等の動作を示すコマンド信号を含む制御信号とを半導体記憶装置93に出力する。

#### 【0010】

半導体記憶装置93において、制御回路931は、クロック信号入力端子935から入力されるクロック信号及び制御信号入力端子936から入力される制御信号に基づいて、メモリ部932の読み出し及び書き込みを行わせると共に、シリアル・パラレル変換回路933の切替えを行う。更に、制御回路931は、テストにおいて、比較回路934にメモリ部932が出力する信号と、シリアル・パラレル変換回路933の出力する信号とを比較させ、比較結果を出力させる。

#### 【0011】

シリアル・パラレル変換回路933は、読み出し動作において、クロック信号の立上がりによりメモリ部932から入出力される64ビット幅のデータを、クロック信号の立上がり及び立下りにより出力される32ビット幅の連続するデータに変換し、変換したデータをデータ入出力端子937に出力する。また、シリアル・パラレル変換回路933は、書き込み動作において、クロック信号の立上がり及び立下りによりデータ入出力端子93

10

20

30

40

50

7から入力される32ビット幅の連続するデータ信号を、クロック信号の立上がり信号により出力される64ビット幅のデータ信号に変換してメモリ部932及び比較回路934に出力する。更に、シリアル・パラレル変換回路933は、テストにおける結果判定時に、メモリ部932から入力された64ビット幅のデータ信号を比較回路934に出力する。

#### 【0012】

比較回路934は、メモリ部932から入力される64ビット幅のデータ信号と、シリアル・パラレル変換回路933から入力される64ビット幅のデータ信号とを比較し、比較結果を出力する。

テスター90は、半導体記憶装置93にクロック信号及びデータの読み出しを示す制御信号を出力する。半導体記憶装置93において、制御回路931は、入力されるクロック信号及びデータの読み出しを示す制御信号に基づいて、メモリ部932に記憶されているデータをシリアル・パラレル変換回路933に出力させる。

また、制御回路931は、シリアル・パラレル変換回路933に入力されたデータ信号を比較回路934に出力させる。

#### 【0013】

比較回路934は、メモリ部932から入力される64ビット幅のデータ信号と、シリアル・パラレル変換回路933から入力される64ビット幅のデータ信号とを比較し、比較結果を出力する。更に、制御回路931は、比較回路934が出力した比較結果をテスター90に出力する。

このように、半導体記憶装置93とテスター90との間で実動作速度、例えば、533MHzや666MHzのように高速なデータの入出力を行わずとも、メモリ部932の入出力データが経由するシリアル・パラレル変換回路933を、実動作速度など、でテストを行うことができる。

#### 【先行技術文献】

#### 【特許文献】

#### 【0014】

#### 【特許文献1】特開2007-317016号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0015】

しかしながら、上述の方法では、メモリ部からデータを読み出し、読み出したデータを比較するのみで、書き込み動作も含めてメモリ部のテストを行っていないという問題がある。特に高速で32ビットや64ビット幅のデータを扱う半導体記憶装置において、データ用の配線で複数の信号が一度に変化するとクロストーク・ノイズなどの影響により書き込むデータや読み出すデータの入出力が正しく行われない故障を発生することがある。このため、メモリ部の書き込みを含めたテストは重要である。

#### 【0016】

また、前述したように、半導体記憶装置のデータ幅が32ビット、64ビットと増加すると接続に要するテスターの入出力端子が増加し、テスターに同時に接続できる半導体記憶装置の数が減り、テストに要する時間及びコストが増加するという問題もある。

#### 【0017】

本発明は、上記問題を解決すべくなされたもので、その目的は、半導体記憶装置の実動作速度でテストを行い、且つ接続に要するテスターの入出力端子数を削減できる半導体記憶装置を提供することにある。

#### 【課題を解決するための手段】

#### 【0018】

上記問題を解決するために、本発明は、第1メモリ部と、第1ビット数からなる第1データと、前記第1ビット数より小さい第2ビット数からなる第2データと、制御回路と、を備え、前記制御回路は、複数の前記第2データに基づいて前記第1データを生成し、前

10

20

30

40

50

記生成された第1データを前記第1メモリ部に並列して書き込み、さらに、第2メモリ部と、を備え、前記制御回路は、前記第1メモリ部に書き込まれた前記第1データのビットを前記第1メモリ部から並列して読み出し、前記第1メモリ部から読み出された前記第1データに基づいて前記第1ビット数を有する第3データを生成し、前記生成された第3データのビットを前記第2メモリ部に並列して書き込む、ことを特徴とする半導体記憶装置である。

(1) また、本発明は、データを記憶するメモリ部と、 $n(n-2)$ 個のデータ入出力端子を介して $n$ ビット幅のデータを前記メモリ部にクロック信号に同期して入出力する手段(制御回路11、21、31及びループバック回路14、24、34)と、前記 $n$ 個のデータ入出力端子のうちの予め選択された $m(m-n)$ 個のデータ入出力端子を介して前記メモリ部にデータを入出力する手段(制御回路11、21、31及びループバック回路14、24、34)と、前記メモリ部の任意の記憶領域から順次前記 $n$ ビット幅でデータを読み出し、読み出した該 $n$ ビット幅のデータを前記記憶領域とは異なる記憶領域に記憶させるループバック回路と、を備えることを特徴とする半導体記憶装置である。

10

#### 【0019】

(2) また、本発明は、動作テストモードを有し、データの入出力をを行うテストデータ専用端子を備える導体記憶装置であって、データを記憶するメモリ部と、 $n(n-2)$ 個のデータ入出力端子を介して $n$ ビット幅のデータを前記メモリ部にクロック信号に同期して入出力する手段(制御回路11、21、31及びループバック回路14、24、34)と、前記動作テストモードにおいて、前記テストデータ専用端子を介して前記メモリ部にデータを入出力する手段(制御回路11、21、31及びループバック回路14、24、34)と、前記メモリ部の任意の記憶領域から順次前記 $n$ ビット幅でデータを読み出し、読み出した該 $n$ ビット幅のデータを前記記憶領域とは異なる記憶領域に記憶させるループバック回路と、を備えることを特徴とする半導体記憶装置である。

20

#### 【0020】

(3) また、本発明は、上記記載の発明において、前記メモリ部は、前記 $n$ ビット幅のデータの読み出し及び書き込みを独立に行うメモリブロックを複数有し、前記ループバック回路は、前記メモリブロックから入力される $n$ ビット幅のデータを異なる前記メモリブロックへ出力することを特徴とする。

30

#### 【0021】

(4) また、本発明は、上記記載の発明において、前記 $n$ 個のデータ入出力端子のなかから選択される前記 $m$ 個のデータ入出力端子は、当該データ入出力端子に接続される論理素子に供給される前記クロック信号の最終段のクロックバッファが異なるデータ入出力端子から優先的に選択されることを特徴とする。

40

#### 【0022】

(5) また、本発明は、上記記載の発明において、前記半導体記憶装置は、書き込みコマンドが読み出しコマンド入力後予め定められたクロックサイクル経過後に入力されると、前記読み出しコマンドで指定される前記メモリ部の記憶領域から前記 $n$ ビット幅のデータを読み出すと共に、前記ループバック回路を使用して読み出した該データを前記書き込みコマンドで指定される前記メモリ部の記憶領域に記憶することを特徴とする。

40

#### 【0023】

(6) また、本発明は、上記記載の発明における、テスターからのテストデータの入出力としては前記 $m$ 個のデータ入出力端子のみ使用し、前記テスターが、前記 $m$ 個のデータ入出力端子から前記テストデータを入力し、前記メモリ部の任意の記憶領域に記憶させるテストデータ入力過程と、前記メモリ部の前記記憶領域から前記テストデータを読み出すと共に、前記ループバック回路を使用して読み出した該テストデータを前記メモリ部の前記記憶領域とは異なる記憶領域に記憶させる動作テスト過程と、前記テスターが、前記メモリ部の前記記憶領域及び他から前記テストデータを前記 $m$ 個のデータ入出力端子から読み出し、読み出した該テストデータが予め定めたデータと一致するか否かにより前記半導体記憶装置の故障を検出するテストデータ出力過程とを有することを特徴とするテスト方

50

法である。

**【0024】**

(7) また、本発明は、半導体記憶装置におけるテスト方法であって、テスターからのテストデータの入出力としてはテストデータ専用端子のみ使用し、前記テスターが、前記テストデータ専用端子から前記テストデータを入力し、メモリ部の第1の記憶領域に記憶させるテストデータ入力過程と、前記メモリ部の前記第1の記憶領域から前記テストデータを読み出すと共に、ループバック回路を使用して読み出した該テストデータを前記メモリ部の前記第1の記憶領域とは異なる第2の記憶領域に記憶させる動作テスト過程と、前記テスターが、前記メモリ部の前記第2の記憶領域から前記テストデータを前記テストデータ専用端子から読み出し、読み出した該テストデータが予め定めたデータと一致するか否かにより前記半導体記憶装置の故障を検出するテストデータ出力過程とを有することを特徴とするテスト方法である。 10

**【0025】**

(8) また、本発明は、上記記載の発明において、前記テストデータ入力過程又は前記テストデータ出力過程における前記半導体記憶装置に入力されるクロック信号の周波数は、前記動作テスト過程における前記半導体記憶装置に入力されるクロック周波数より遅いことを特徴とする。

**【発明の効果】**

**【0026】**

この発明によれば、半導体記憶装置が有するデータ入出力端子の一部を用いてテストデータの入出力を行い、半導体記憶装置が記憶するテストデータを外部に出力せずに異なる記憶領域に書き込み記憶させる構成とした。これにより、半導体記憶装置の実動作速度でテストを行うこと、且つ接続に要するテスターの入出力端子数を削減することが可能となる。 20

**【図面の簡単な説明】**

**【0027】**

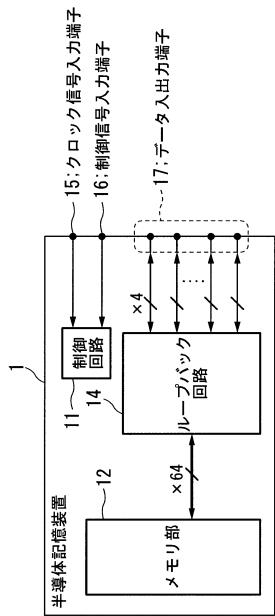

【図1】第1実施形態における半導体記憶装置の構成を示す概略ブロック図である。

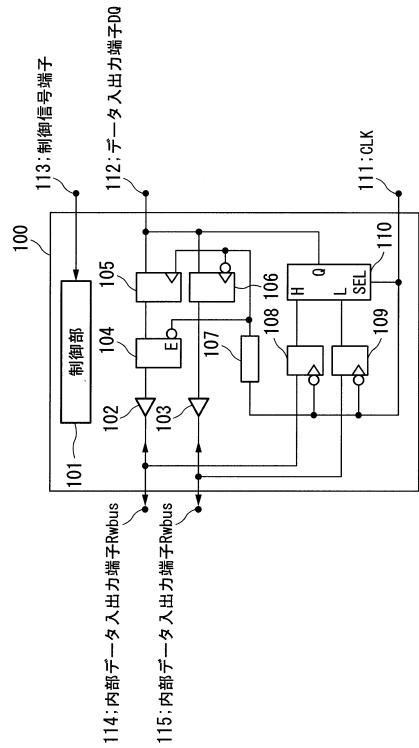

【図2】同実施形態におけるループバック回路の構成を示す概略図である。

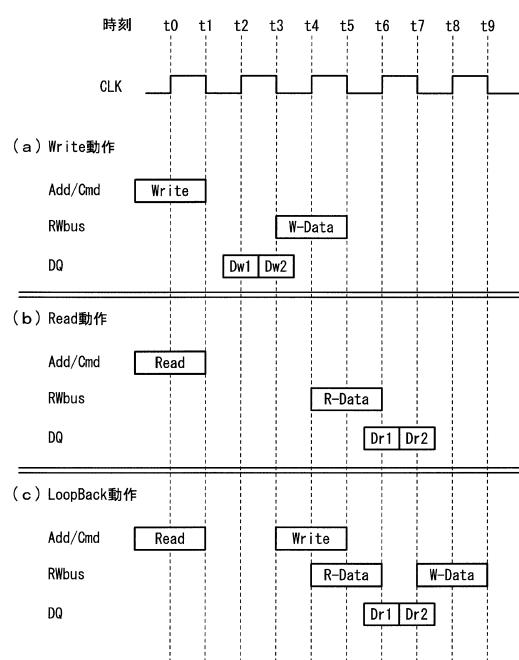

【図3】同実施形態におけるループバック回路の動作を示すタイミングチャートである。

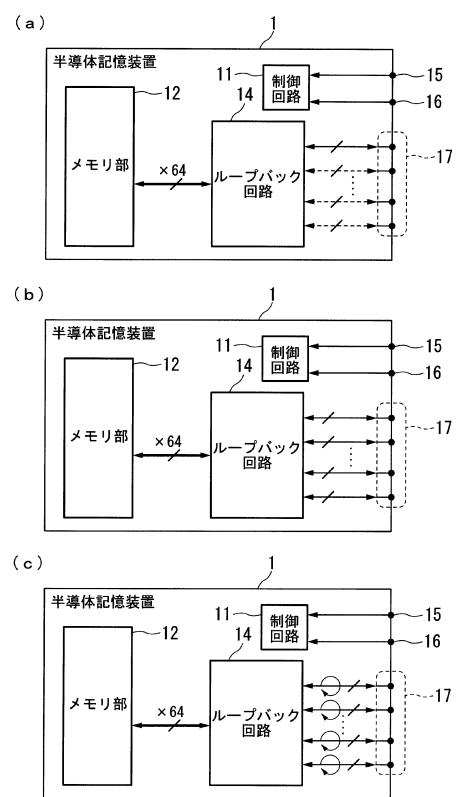

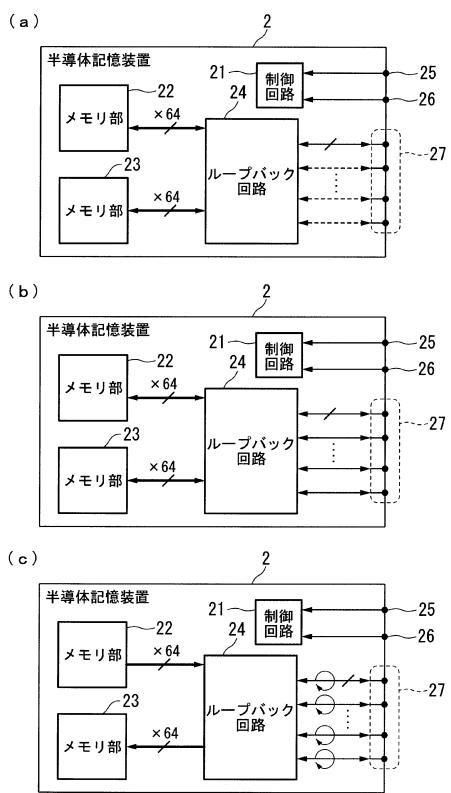

【図4】同実施形態における半導体記憶装置の動作形態を示す概略図である。 30

【図5】同実施形態における半導体記憶装置のテスト方法を示す概略図である。

【図6】同実施形態における半導体記憶装置のテスト動作を示す概略図である。

【図7】同実施形態における半導体記憶装置のデータ入出力端子のクロックツリーを示す概略図である。

【図8】第2実施形態における半導体記憶装置の構成を示す概略ブロック図である。

【図9】同実施形態における半導体記憶装置の動作形態を示す概略図である。

【図10】同実施形態における反動他記憶装置のテスト方法を示す概略図である。

【図11】第3実施形態における半導体記憶装置の構成を示す概略ブロック図である。

【図12】同実施形態における半導体記憶装置の動作形態を示す概略図である。

【図13】同実施形態における半導体記憶装置のテスト動作を示す概略図である。 40

【図14】従来例における半導体記憶装置の構成、及びテスターとの接続を示す概略図である。

【図15】従来例における半導体記憶装置のテスト動作を示す概略図である。

【図16】従来例における半導体回路装置とテスターとの接続を示す概略図である。

【図17】従来例における半導体記憶措置の構成、及びテスターとの接続を示すが略図である。

**【発明を実施するための形態】**

**【0028】**

以下、本発明の実施形態による半導体記憶装置及びテスト方法を図面を参照して説明する。 50

**【0029】**

(第1実施形態)

図1は、第1実施形態における半導体記憶装置1の構成を示す概略ブロック図である。半導体記憶装置1は、制御回路11、メモリ部12、ループバック回路14、クロック信号が入力されるクロック信号入力端子15、制御信号が入力される制御信号入力端子16及び32ビット幅のデータ入出力端子17を有している。

**【0030】**

半導体記憶装置1において、制御回路11は、クロック信号入力端子15から入力されるクロック信号に同期して、制御信号入力端子16から入力されるアドレス信号を含む制御信号に基づいて、メモリ部12データの読み出し及び書き込み動作を行わせる。ここで、制御信号は、例えば、チップセレクト信号、行アドレス・ストローブ信号、列アドレス・ストローブ信号、ライト・イネーブル信号などが含まれる。また、制御回路11は、ループバック回路14の制御を行う。

**【0031】**

メモリ部12には、ループバック回路14から入力されるデータが制御回路11から指定される領域に記憶される。また、ループバック回路14には、メモリ部12から読み出されるデータが入力される。

**【0032】**

ループバック回路14は、クロック信号の立上がりに同期してデータ入出力端子17から入力される32ビット幅のデータと、クロック信号の立下りに同期してデータ入出力端子17から入力される32ビット幅のデータとをまとめて64ビット幅のデータとして、クロック信号の立下りに同期してメモリ部12に出力する。

また、ループバック回路14は、メモリ部12からクロック信号の立下りに同期して入力される64ビット幅のデータを2つの32ビット幅のデータに分け、分けたデータの一方をクロックの立上がりに同期してデータ入出力端子17に出力し、分けたデータの他方をクロック信号の立下りに同期してデータ入出力端子17に出力する。

また、ループバック回路14は、メモリ部12から入力される64ビット幅のデータをメモリ部12へ出力するループバックを行う。このループバック回路14の動作は、制御回路11が選択する。また、ループバック回路14は、半導体記憶装置1の故障検出を行う動作テストモードの読み出し動作において、メモリ部12から入力される64ビット幅のデータから順に4ビットのデータを選択し、選択した4ビットのデータをデータ入出力端子17のうちの予め選択された4つの端子から出力する。

また、ループバック回路14は、動作テストのテストデータの書き込み及び読み出しの際に用いる64ビット幅のバッファ・レジスタを有している。

**【0033】**

図2は、ループバック回路14に含まれるループバック・ブロック100の構成を示す概略ブロック図である。

ループバック・ブロック100は、制御部101、バッファ102、103、ラッチ104、フリップ・フロップ105、106、108、109、プログラマブル遅延素子107、セレクタ110、クロック信号入力端子111、データ入出力端子112、制御信号端子113、内部データ入出力端子114、115を有している。

**【0034】**

ループバック・ブロック100において、内部データ入出力端子114、115は、それぞれ32ビット幅のデータが入出力される端子であり、メモリ部12に接続され、メモリ部12の64ビット幅のデータの入出力は、内部データ入出力端子114、115を介して行われる。

制御信号端子113には、読み出し動作及び書き込み動作を示す信号、及びプログラマブル遅延素子107の遅延時間を選択する信号を含む制御信号が入力される。

データ入出力端子112は、32ビット幅のデータが入出力される端子であり、データ入出力端子17に接続される。

10

20

30

40

50

クロック信号入力端子 111 は、クロック信号入力端子 15 に接続される。

#### 【0035】

クロック信号入力端子 111 は、クロック信号が入力され、入力されたクロック信号をセレクタ 110、フリップ・フロップ 108, 109、及びプログラマブル遅延素子 107 に出力する。

#### 【0036】

セレクタ 110 は、クロック信号入力端子 111 から入力されたクロック信号のレベルに応じて、「H」レベル (High) のときフリップ・フロップ 108 の出力するデータを選択して出力し、「L」レベル (Low) のときフリップ・フロップ 109 の出力するデータを選択して出力する。なお、データ入出力端子 112 からデータが入力されるとき、セレクタ 110 は、制御部 101 により、出力をハイ・インピーダンス状態にされる。

10

#### 【0037】

フリップ・フロップ 109 は、入力されたクロック信号の立下りに同期して、内部データ入出力端子 115 から入力される 32 ビットのデータを記憶する。

フリップ・フロップ 108 は、入力されたクロック信号の立下りに同期して、内部データ入出力端子 114 から入力される 32 ビットのデータを記憶する。

#### 【0038】

プログラマブル遅延素子 107 は、入力されるクロック信号を遅延させた遅延クロックを出力する。ここで、プログラマブル遅延素子 107 は、フリップ・フロップ 108、109 に入力されて記憶されたデータが、セレクタ 110 を介してフリップ・フロップ 105、106 に入力されて記憶される際に、データとクロック信号のレーシングの発生を防ぐためにクロックを遅延させる。ここで、プログラマブル遅延素子 107 の遅延時間は、例えば、回路素子の配置及び配線後に得られる測定結果に基づいて選択される。

20

#### 【0039】

フリップ・フロップ 106 は、データ入出力端子 112 又はセレクタ 110 から入力される 32 ビットのデータを遅延クロックの立下りに同期して記憶する。

フリップ・フロップ 105 は、データ入出力端子 112 又はセレクタ 110 から入力される 32 ビットのデータを遅延クロックの立上がりに同期して記憶する。

#### 【0040】

ラッチ 104 は、「L」レベルのクロック信号が入力されると、フリップ・フロップ 105 から入力される 32 ビットのデータをバッファ 102 に出力する。また、ラッチ 104 は、入力されるクロック信号が「L」レベルから「H」レベルに変化すると、入力されている 32 ビットのデータをラッチして出力する。

30

#### 【0041】

バッファ 102 は、メモリ部 12 にデータを記憶させる書き込み動作において、ラッチ 104 から入力されるデータを内部データ出力端子 114 に出力する。また、制御部 101 は、メモリ部 12 が記憶するデータを出力する読み出し期間において、バッファ 102 の出力をハイ・インピーダンス状態にする。

バッファ 103 は、メモリ部 12 にデータを記憶させる書き込み動作において、フリップ・フロップ 106 から入力されるデータを内部データ出力端子 115 に出力する。また、制御部 101 は、メモリ部 12 が記憶するデータを出力する読み出し期間において、バッファ 103 の出力をハイ・インピーダンス状態にする。バッファ 103 の動作の切替えは、制御部 101 により行われる。

40

制御部 101 は、制御信号端子 113 を介して制御回路 11 から入力される読み出し動作及び書き込み動作を示す信号に基づいて、セレクタ 110 及びバッファ 102、103 の出力を制御する。

#### 【0042】

次に、ループバック・ロック 100 の動作を説明する。図 3 は、ループバック・ロック 100 の書き込み動作 ((a) Write 動作)、読み出し動作 ((b) Read 動作)、及びループバック動作 ((c) Loopback 動作) を示したタイミングチャート

50

トである。なお、半導体記憶装置1は、DDR1の規格のSDRAMであり、BL(Burst Length)は2であり、CL(Column address strobe Latency)は2.5とする。

#### 【0043】

##### [書き込み動作：(a) Write動作]

まず、時刻t0において、制御回路11は、データを書き込む領域を示すアドレス信号を含む書き込みコマンド(Write)が、制御信号入力端子16(Add/Cmdと図示)を介して入力されると、入力された書き込みコマンドをデコードした信号を制御信号端子113に出力する。制御部101は、制御信号端子113から入力される信号をデコードして、セレクタ110の出力をハイ・インピーダンスにする。

#### 【0044】

時刻t2において、フリップ・フロップ105は、データ入出力端子112から入力されているデータDw1を遅延クロック信号の立上がりに同期して記憶する。

#### 【0045】

時刻t3において、ラッチ104は、「L」レベルの遅延クロック信号が入力されると、フリップ・フロップ105の出力信号をバッファ102に出力する。バッファ102は、入力された信号を内部データ入出力端子114(RWbus)に出力する。

フリップ・フロップ106は、データ入出力端子112から入力されているデータDw2を遅延クロック信号の立下りに同期して記憶する。また、フリップ・フロップ106は、記憶したデータをバッファ103に出力する。バッファ103は、入力された信号を内部データ出力信号端子115(RWbus)に出力する。

10

#### 【0046】

時刻t4において、ラッチ104は、入力されていたフリップ・フロップ105の出力データDw1をラッチして出力する。

#### 【0047】

上述のように、ループバック・ロック100は、書き込みコマンドが入力されると、データ入出力端子112から入力される、クロック信号の立上がりに同期したデータDw1及びクロック信号の立下りに同期したデータDw2を、一旦記憶して、クロック信号の立下りに同期したデータDw1とデータDw2とを併せたデータW-Dataとして内部データ出力端子114、115に出力する。

20

#### 【0048】

##### [読み出し動作：(b) Read動作]

まず、時刻t0において、制御回路11は、読み出すデータが記憶されている領域を示すアドレス信号を含む読み出しコマンド(Read)が、制御信号入力端子16(Add/Cmdと図示)から入力されると、入力された読み出しコマンドをデコードした信号を制御信号端子113に出力する。制御部101は、制御信号端子113から入力される信号をデコードして、バッファ102、103の出力をハイ・インピーダンスにする。

30

#### 【0049】

時刻t4において、ループバック回路14には、メモリ部12から読み出したデータR-Dataが内部データ入出力端子114、115から入力される。

#### 【0050】

時刻t5において、フリップ・フロップ108は、クロック信号の立下りに同期して、入力されているデータR-DataのうちデータDr2を記憶して出力する。フリップ・フロップ109は、クロック信号の立下りに同期して、入力されているデータR-DataのうちデータDr1を記憶して出力する。このとき、セレクタ110は、入力されている「L」レベルのクロック信号によりフリップ・フロップ109の出力であるデータDr1を選択して、データ入出力端子112に出力する。

40

#### 【0051】

時刻t6において、セレクタ110は、「H」レベルのクロック信号が入力されると、フリップ・フロップ108が出力するデータDr2を選択して、データ入出力端子112に出力する。

50

**【0052】**

上述のように、ループバック・ブロック100は、読み出しコマンドが入力されると、クロック信号の立下りに同期してメモリ部12から読み出された64ビットのデータR-Dataが入力される。また、ループバック・ブロック100は、入力されたデータR-Dataのうち一方の32ビットのデータDr1をクロック信号の立上がりに同期して出力し、データR-Dataの他方の32ビットのデータDr2をクロック信号の立下りに同期して出力する。

**【0053】****[ループバック動作：(c) Loopback動作]**

まず、時刻t0において、制御回路11は、読み出すデータが記憶されている領域を示すアドレス信号を含む読み出しコマンド(Read)が、制御信号入力端子16(Add/Cmdと図示)から入力されると、入力された読み出しコマンドをデコードした信号を制御信号端子113に出力する。制御部101は、制御信号端子113から入力される信号をデコードして、バッファ102、103の出力をハイ・インピーダンスにする。

10

次に、時刻t3において、制御回路11は、データを書き込む領域を示すアドレス信号を含む書き込みコマンド(Write)が、制御信号入力端子16(Add/Cmdと図示)を介して入力されると、入力された書き込みコマンドをデコードした信号を制御信号端子113に出力する。

**【0054】**

時刻t4において、ループバック回路14には、メモリ部12から読み出したデータR-Dataが内部データ入出力端子114、115から入力される。

20

**【0055】**

時刻t5において、フリップ・フロップ108は、クロック信号の立下りに同期して、入力されているデータR-DataのうちデータDr2を記憶して出力する。フリップ・フロップ109は、クロック信号の立下りに同期して、入力されているデータR-DataのうちデータDr1を記憶して出力する。このとき、セレクタ110は、入力されている「L」レベルのクロック信号によりフリップ・フロップ109の出力であるデータDr1を選択して、データ入出力端子112に出力する。

フリップ・フロップ106は、遅延クロック信号の立下りに同期して、セレクタ110が出力するデータDr1を記憶する。

30

**【0056】**

時刻t6において、フリップ・フロップ105は、セレクタ110が出力するデータDr1を遅延クロック信号の立上がりに同期して記憶する。

**【0057】**

時刻t7において、制御部101は、バッファ102、103に入力されているデータを出力させる。セレクタ110は、「L」レベルのクロック信号が入力されると、フリップ・フロップ108の出力するデータDr2を選択してデータ入出力端子112、フリップ・フロップ105、106に出力する。フリップ・フロップ106は、遅延クロック信号の立下りに同期して、セレクタ110の出力するデータDr2を記憶して、バッファ103に出力する。バッファ103は、入力されたデータDr2を内部データ入出力端子115に出力する。

40

**【0058】**

ラッチ104は、「L」レベルのクロック信号が入力されると、フリップ・フロップ105から入力されるデータDr1をバッファ102に出力する。バッファ102は、入力されるデータDr1を内部データ入出力端子114に出力する。

時刻t8において、ラッチ104は、遅延クロックの立上がりに同期してフリップ・フロップ105から入力されているデータDr1をラッチする。

**【0059】**

上述のように、読み出しコマンド(Read)の読み出しデータと、書き込みコマンドの書き込みデータとが重なるクロックサイクル間隔で、読み出しコマンド及び書き込みコ

50

マンドを入力する。これにより、ループバック・ブロック 100 は、内部データ入出力端子 114、115 から入力された読み出しコマンドに対応するデータ R - Data (データ Dr1 及びデータ Dr2) を、書き込みコマンドに対応するデータとして内部データ入出力端子 114、115 に出力するループバックを行う。この結果、半導体記憶装置 1 は、メモリ部 12 に記憶されたデータを読み出し、読み出したデータを半導体記憶装置 1 の外部に出力することなく読み出したデータをメモリ部 12 の異なる記憶領域に書き込み記憶させることが可能となる。

マンドの CL と書き込みコマンドのデータを入力するタイミング (レイテンシ) に基づいて定められる。

#### 【0060】

10

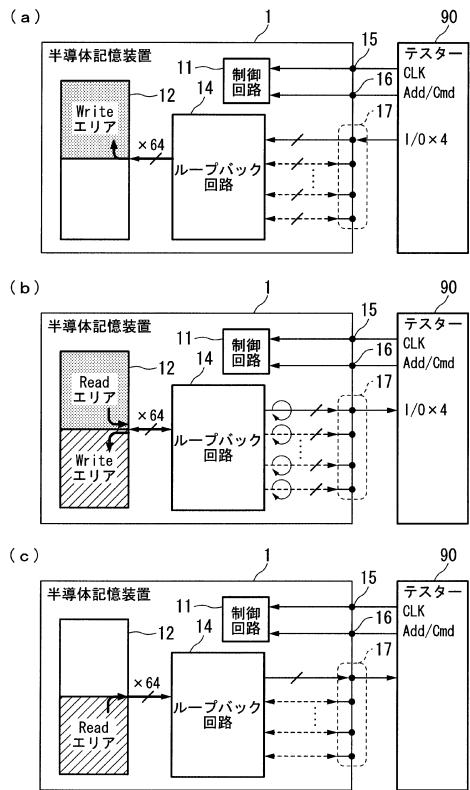

次に、半導体記憶装置 1 の動作について説明する。図 4 は、半導体記憶装置 1 が有する動作形態を示す概略図である。

図 4 (a) は、半導体記憶装置 1 が、データ入出力端子 17 のうち予め選択された 4 個の端子であるテスト兼用端子を介してデータの入出力を実行する動作テストにおける動作を示している。データ入出力端子 17 とループバック回路 14との間の破線は、有効なデータが入出力されていないことを示している。実線で接続されているテスト兼用端子を介した 4 ビット幅のデータによる読み出し及び書き込みは、例えば、次のようにして行う。

#### 【0061】

読み出し動作において、制御回路 11 は、ループバック回路 14 に、メモリ部 12 から読み出し 64 ビット幅のデータを一旦バッファ・レジスタに記憶させ、記憶させた 64 ビットのデータから 4 ビットずつテスト兼用端子から出力させる。書き込み動作において、制御回路 11 は、ループバック回路 14 に、制御回路 11 が入力される 4 ビット幅のデータをバッファ・レジスタに順に記憶させ、64 ビット分の書き込みデータが整うと、メモリ部 12 に書き込み記憶させる。

20

#### 【0062】

図 4 (b) は、半導体記憶装置 1 が、データ入出力端子 17 の全ての端子を用いて、データの入出力を実行する通常動作における動作を示している。データ入出力端子 17 とループバック回路 14 との間の実線は、データ入出力端子 17 の全ての端子を介してデータが入出力されることを示している。

#### 【0063】

30

図 4 (c) は、半導体記憶装置 1 が、データ入出力端子 17 を介さずにメモリ部 12 から 64 ビット幅のデータを読み出し及び 64 ビット幅のデータをメモリ部 12 に書き込む動作テストにおける動作を示している。なお、ループバック回路 14 は、この動作において、ループバックを行っている。

#### 【0064】

次に、半導体記憶装置 1 の動作テストを行う動作テストモードにおけるテスト方法を説明する。図 5 は、半導体記憶装置 1 のテスト方法を示した図である。図示するように、半導体記憶装置 1 は、テスター 90 からクロック信号入力端子 15 を介してクロック信号が入力され、制御信号入力端子 16 を介して制御信号が入力され、テスター 90 の備える 4 個の I/O 端子がテスト兼用端子と接続されてテストデータが入出力される。

40

#### 【0065】

まず、図 5 (a) は、テスター 90 から半導体記憶装置 1 へのテストデータの書き込み動作を示す概略図である。テスター 90 は、制御信号に含まれるアドレス信号で示した領域 (Write エリア) にテストデータを 4 ビットずつ入力する。入力されたテストデータは、ループバック回路 14 が有するバッファ・レジスタを介して、メモリ部 12 に書き込まれて記憶される。

#### 【0066】

図 5 (b) は、ループバック回路 14 のループバック動作を用いた動作を示す概略図である。テスター 90 は、テストデータの書き込みが完了すると、読み出しコマンドと書き込みコマンドと制御信号入力端子 16 から交互に半導体記憶装置 1 に入力する。これによ

50

り、制御回路 11 は、ループバック回路 14 のループバック動作を用いて、書き込んだテストデータをメモリ部 12 から読み出して、メモリ部 12 の異なる領域に 64 ビットずつ順次書き込み記憶させる。

#### 【 0 0 6 7 】

図 5 (c) は、テスター 90 から読み出しこmandoを入力して、テストデータを読み出す動作を示した概略図である。テスター 90 は、テスト用の読み出しこmandoを半導体記憶装置 1 に入力し、ループバック動作を用いて書き込み記憶させたデータを読み出し、読み出したテストデータが予め用意しておいた期待値と一致するか否かを判定し、当該テスト対象の半導体記憶装置 1 に故障があるか否かの検出を行う。なお、読み出すテストデータは、ループバック回路 14 が有するバッファ・レジスタを介して、4 ビットずつテスター 90 に出力される。

10

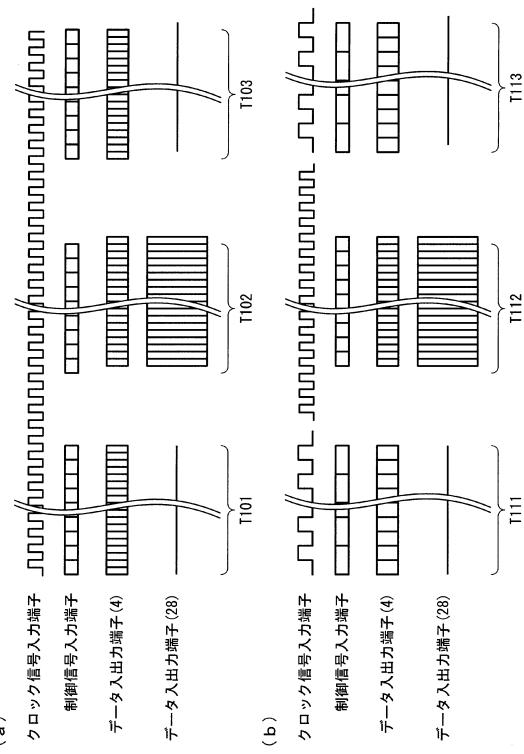

#### 【 0 0 6 8 】

図 6 (a) は、半導体装置 1 とテスター 90 を用いたテスト動作を示す概略図である。T101 で図示される入力期間において、テスター 90 は、書き込みコmandoを含む制御信号及びクロック信号を半導体記憶装置 1 に出力すると共に、4 ビット幅のデータを半導体記憶装置 1 に出力してテストデータを書き込む。

#### 【 0 0 6 9 】

次に、T102 で図示される期間において、テスター 90 は、クロック信号と、ループバック動作を行わせる読み出しこmando及び書き込みコmandoを含む制御信号を半導体記憶装置 1 に出力する。これにより、T102 で示される期間において、半導体記憶装置 1 は、メモリ部 12 に記憶されているテストデータを読み出して、読み出したテストデータを書き込みコmandoに含まれるアドレス信号で示される領域に書き込み記憶させる。

20

#### 【 0 0 7 0 】

続く T103 で図示される期間において、テスター 90 は、読み出しこmandoを含む制御信号及びクロック信号を半導体記憶装置 1 に出力して、ループバック動作を用いて書き込み記憶させたテストデータを 4 ビットずつ読み出し、読み出したテストデータが予め用意しておいたデータである期待値と一致するか否かを判定し、当該テスト対象の半導体記憶装置 1 に故障があるか否かの検出を行う。

#### 【 0 0 7 1 】

上述のように半導体記憶装置 1 へのテストデータを書き込み及び読み出しを行うことと、半導体記憶装置 1 との接続に要する端子数を削減してテストを行うことが可能となる。

30

なお、図 6 (b) に示すように、T111 で図示される半導体記憶装置 1 にテストデータを書き込む際の書き込みコmando、及び T113 で図示される半導体記憶装置 1 からテストデータを読み出す際の読み出しこmandoを、半導体記憶装置 1 の実動作速度よりも遅いクロック周波数を用いて行ってもよい。この場合、高速にデータの入出力が行える I/O 端子を有する高精度のテスターを用いることなく、半導体記憶装置 1 の実動作速度でのテストを行うことが可能となる。

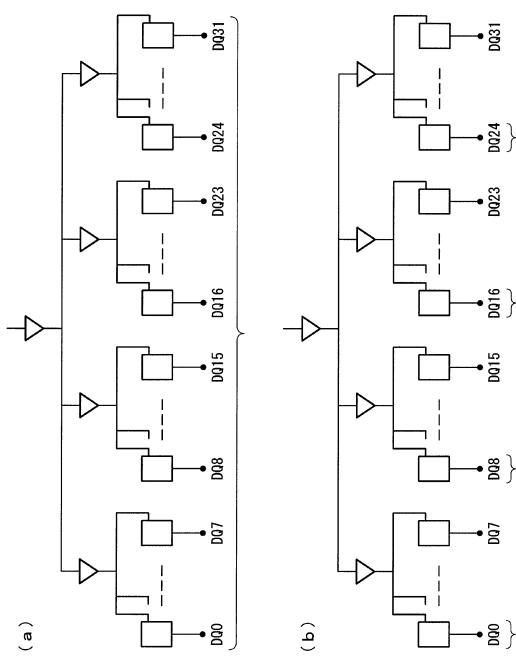

#### 【 0 0 7 2 】

次に、データ入出力端子 17 からテスター 90 に接続する端子の選択方法について説明する。図 7 (a) 及び (b) は、データ入出力端子 17 に接続される論理素子に供給されるクロック信号の接続を示した概略図である。図示するようにクロック信号は、接続されるバッファ段数が等しく、また、接続されるデータ入出力端子数が等しくなるツリー構造となっている。また、ここでは、8 個のデータ入出力端子ごとにまとめられ、まとめられたデータ入出力端子それぞれの A C タイミングは大差ない値となる。これにより、クロック信号の変化がそれぞれのデータ入出力端子に伝搬するまでの遅延時間 (A C タイミング) の調整を行いやすくなり、設計が容易になる。

40

#### 【 0 0 7 3 】

このように設計されている半導体記憶装置 1 において、図 7 (b) に示すように、テスター 90 に接続される端子は、最終段のクロックバッファを共有するデータ入出力端子のグループそれぞれから選択される。すなわち、接続される端子として D Q 0, 8, 16、

50

24を選択する。これにより、それぞれのクロックツリーのACタイミングを計測することができる。また、このようにデータ入出力端子を選択することで、テスター90との接続に用いるデータ入出力端子17を削減した場合においても、クロックツリーごとのACタイミングを測定することができ、クロックツリーごとのACタイミングのばらつきの検出が可能である。

上述したように、データ入出力端子17からテスター90との接続に用いる端子の選択は、クロック信号を分配するクロックツリーの構成に基づいて行う。

#### 【0074】

(第2実施形態)

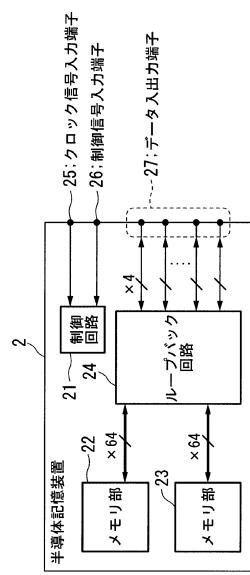

図8は、第2実施形態における半導体記憶装置2の構成を示す概略ブロック図である。

10

半導体記憶装置2は、制御回路21、メモリ部22、23、ループバック回路24、クロック信号が入力されるクロック信号入力端子25、制御信号が入力される制御信号入力端子26及び32ビット幅のデータ入出力端子27を有している。

#### 【0075】

半導体記憶装置2において、制御回路21は、クロック信号入力端子25から入力されるクロック信号に同期して、制御信号入力端子26から入力されるアドレス信号を含む制御信号に基づいて、メモリ部22、23データの読み出し及び書き込み動作を行わせる。

20

ここで、制御信号は、例えば、チップセレクト信号、行アドレス・ストローブ信号、列アドレス・ストローブ信号、ライト・イネーブル信号などが含まれる。また、制御回路21は、ループバック回路24の制御を行う。

#### 【0076】

メモリ部22、23は、ループバック回路24から入力されるデータが制御回路21から指定される領域に記憶される。また、メモリ部22、23は、制御回路21から指定される領域に記憶されているデータが読み出されてループバック回路24に出力される。また、メモリ部22、23は、それぞれ独立に64ビット幅の出力端子、ロウ・アドレスデコーダ、カラム・アドレスデコーダなどを備えている。これにより、メモリ部22、23は、独立に読み出し動作と書き込み動作を行うことができる。

#### 【0077】

ループバック回路24は、クロック信号の立上がり及び立下りに同期してデータ入出力端子27から入力される32ビット幅のデータを、一旦記憶し、64ビット幅のデータとして、クロック信号の立下りに同期してメモリ部22、23に出力する。なお、制御回路21は、入力される書き込みコマンドに含まれるアドレス信号により、ループバック回路24にメモリ部22及びメモリ部23のいずれにデータを出力するかを定める。

30

また、ループバック回路24は、メモリ部22、23からクロック信号の立下りに同期して入力される64ビット幅のデータを2つの32ビット幅のデータに分け、分けたデータの一方をクロックの立上がりに同期してデータ入出力端子27に出力し、分けたデータの他方をクロック信号の立下りに同期してデータ入出力端子27に出力する。

#### 【0078】

また、ループバック回路24は、メモリ部22、23から入力される64ビット幅のデータをメモリ部22、23へ出力するループバックを行う。このループバック回路24の動作は、制御回路21が選択する。また、ループバック回路24は、半導体記憶装置2の故障検出を行う動作テストモードの読み出し動作において、メモリ部22、23から入力される64ビット幅のデータから順に4ビットのデータを選択し、選択した4ビットのデータをデータ入出力端子27のうちの予め選択された4つの端子から出力する。

40

#### 【0079】

また、図示していないが、ループバック回路24は、図2で示したループバック・ブロック100を2つ有している。2つのループバック・ブロック100は、内部データ入出力端子114、115がそれぞれメモリ部23、24に接続され、データ入出力端子112がデータ入出力端子27と共に接続される。

#### 【0080】

10

20

30

40

50

半導体記憶装置 2 は、第 1 実施形態の半導体記憶装置 1 と比べ、2 つのメモリ部 2 2、2 3 を備えることで、それぞれ独立に読み出し及び書き込みを行える構成となっている。

#### 【0081】

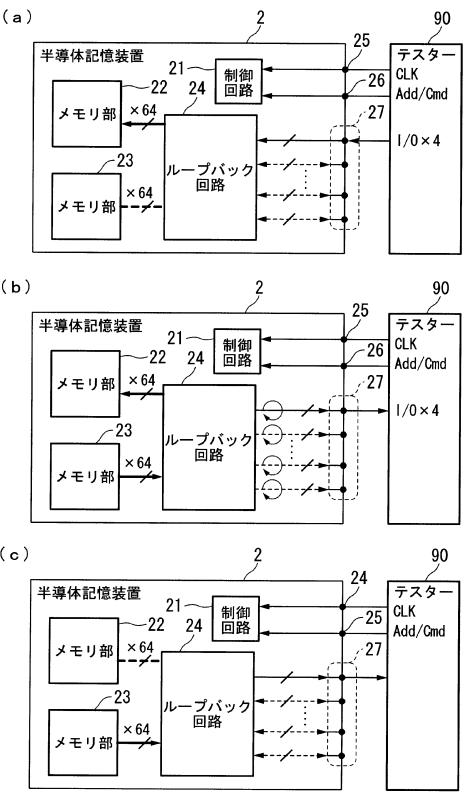

次に、次に半導体記憶装置 2 の動作について説明する。図 9 は、半導体記憶装置 2 が有する動作形態を示す概略図である。

図 9 ( a ) は、半導体記憶装置 2 が、データ入出力端子 2 7 のうち予め選択された 4 個の端子であるテスト兼用端子を介してデータの入出力を行う動作テストにおける動作を示している。データ入出力端子 2 7 とループバック回路 2 4との間の破線は、有効なデータが入出力されていないことを示している。

#### 【0082】

図 9 ( b ) は、半導体記憶装置 2 が、データ入出力端子 2 7 の全ての端子を用いて、データの入出力を行う通常動作における動作を示している。データ入出力端子 2 7 とループバック回路 2 4との間の実線は、データ入出力端子 2 7 の全ての端子を介してデータが入出力されることを示している。

#### 【0083】

図 9 ( c ) は、半導体記憶装置 2 が、データ入出力端子 2 7 を介さずにメモリ部 2 2 から 6 4 ビット幅のデータを読み出し、読み出した 6 4 ビット幅のデータをメモリ部 2 3 に書き込む動作テストにおける動作を示している。なお、ループバック回路 2 4 は、この動作において、ループバックを行っている。

なお、半導体記憶装置 2 は、メモリ部 2 3 から 6 4 ビット幅のデータを読み出し、読み出した 6 4 ビット幅のデータをメモリ部 2 2 に書き込む動作テストも行う。

#### 【0084】

次に、半導体記憶装置 2 の動作テストを行う動作テストモードにおけるテスト方法を説明する。図 10 は、半導体記憶装置 2 のテスト方法を示した図である。図示するように、半導体記憶装置 2 は、テスター 9 0 からクロック信号入力端子 2 5 を介してクロック信号が入力され、制御信号入力端子 2 6 を介して制御信号が入力され、テスター 9 0 が備える 4 個の I / O 端子とテスト兼用端子とが接続されてテストデータが入出力される。

#### 【0085】

まず、図 10 ( a ) は、テスター 9 0 から半導体記憶装置 2 へのテストデータの書き込み動作を示す概略図である。テスター 9 0 は、制御信号に含まれるアドレス信号で示した領域 ( Write エリア ) にテストデータを 4 ビットずつ入力してメモリ部 2 2 に記憶させる。

#### 【0086】

図 10 ( b ) は、ループバック回路 2 4 のループバック動作を用いた動作を示す概略図である。テスター 9 0 は、テストデータの書き込みが完了すると、メモリ部 2 2 に対するバースト読み出しコマンドとメモリ部 2 3 に対するバースト書き込みコマンドとを制御信号入力端子 2 6 から半導体記憶装置 2 に入力する。これにより、制御回路 2 1 は、ループバック回路 2 4 のループバック動作を用いて、メモリ部 2 2 に書き込んだテストデータをバースト読み出して、バースト読み出しされたテストデータを連続してメモリ部 2 3 に書き込み記憶させる。

#### 【0087】

図 10 ( c ) は、テスター 9 0 から読み出しコマンドを入力して、テストデータを読み出す動作を示した概略図である。テスター 9 0 は、読み出しコマンドを半導体記憶装置 2 に入力し、メモリ部 2 3 にループバック動作を用いて書き込み記憶させたデータを読み出し、読み出したテストデータが予め用意しておいた期待値と一致するか否かを判定し、当該テスト対象の半導体記憶装置 2 に故障があるか否かの検出を行う。

#### 【0088】

半導体記憶装置 2 は、第 1 実施形態の半導体記憶装置 1 に比べ、2 つのメモリ部 2 2、2 3 を備え、それぞれのメモリ部 2 2、2 3 に対して独立にアクセスできる。これにより、メモリ部 2 2、2 3 の一方にバースト読み出しコマンドによるテストデータを読み出し

10

20

30

40

50

、他方にバースト書き込みコマンドによるテストデータによるテストデータの書き込みを行いループバック動作によるテストデータの書き込みに要するクロックサイクル数を削減することが可能になる。この結果、テストに要する時間及びコストを削減することが可能となる。

#### 【0089】

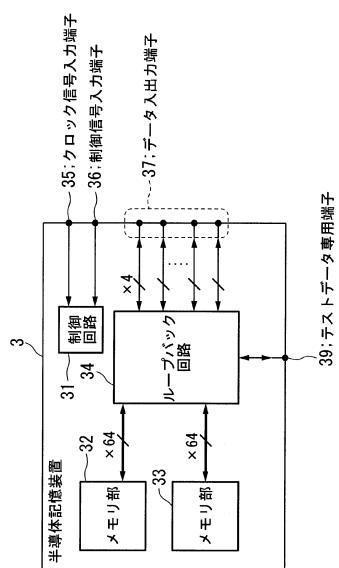

(第3実施形態)

図11は、第3実施形態における半導体記憶装置3の構成を示す概略ブロック図である。半導体記憶装置3は、制御回路31、メモリ部32、33、ループバック回路34、クロック信号が入力されるクロック信号入力端子35、制御信号が入力される制御信号入力端子36、32ビット幅のデータ入出力端子37、及びテストデータ専用端子39を有している。10

#### 【0090】

半導体記憶装置3において、制御回路31は、クロック信号入力端子35から入力されるクロック信号に同期して、制御信号入力端子36から入力されるアドレス信号を含む制御信号に基づいて、メモリ部32、33データの読み出し及び書き込み動作を行わせる。ここで、制御信号は、例えば、チップセレクト信号、行アドレス・ストローブ信号、列アドレス・ストローブ信号、ライト・イネーブル信号などが含まれる。また、制御回路31は、ループバック回路34の制御を行う。

#### 【0091】

メモリ部32、33は、ループバック回路34から入力されるデータが制御回路31から指定される領域に記憶される。また、メモリ部32、33は、制御回路31から指定される領域に記憶されているデータが読み出されてループバック回路34に出力される。また、メモリ部32、33は、それぞれ独立に64ビット幅の出力端子、ロウ・アドレスデコーダ、カラム・アドレスデコーダなどを備えている。これにより、メモリ部32、33は、独立に読み出し動作と書き込み動作を行うことができる。20

#### 【0092】

ループバック回路34は、クロック信号の立上がり及び立下りに同期してデータ入出力端子37から入力される32ビット幅のデータを、一旦記憶し、64ビット幅のデータとして、クロック信号の立下りに同期してメモリ部32、33に出力する。なお、制御回路31は、入力される書き込みコマンドに含まれるアドレス信号により、ループバック回路34にメモリ部32及びメモリ部33のいずれにデータを出力するかを定める。30

また、ループバック回路34は、メモリ部32、33からクロック信号の立下りに同期して入力される64ビット幅のデータを2つの32ビット幅のデータに分け、分けたデータの一方をクロックの立上がりに同期してデータ入出力端子37に出力し、分けたデータの他方をクロック信号の立下りに同期してデータ入出力端子37に出力する。

#### 【0093】

また、ループバック回路34は、動作テストのテストデータの書き込み及び読み出しの際に用いるバッファ・レジスタを有している。

更に、ループバック回路34は、テストデータ専用端子39と接続され、動作テストのテストデータの入出力をテストデータ専用端子39を介して行う。40

また、ループバック回路34は、メモリ部32、33から入力される64ビット幅のデータをメモリ部32、33へ出力するループバックを行う。このループバック回路34の動作は、制御回路31が選択する。

#### 【0094】

また、図示していないが、ループバック回路34は、図2で示したループバック・プロック100を2つ有している。2つのループバック・プロック100は、内部データ入出力端子114、115がそれぞれメモリ部33、34に接続され、ループバック・プロック100それぞれのデータ入出力端子112がデータ入出力端子37と共に接続される。

#### 【0095】

半導体記憶装置3は、第1実施形態の半導体記憶装置1と比べ、2つのメモリ部32、50

3 3 を備えることで、それぞれ独立に読み出し及び書き込みを行える構成となっている。

また、半導体記憶装置 3 は、第 2 実施形態の半導体記憶装置 2 と比べ、テストデータの入出力をデータ入出力端子 3 7 を用いずに、テストデータ専用端子 3 9 を用いて行う構成となっている。

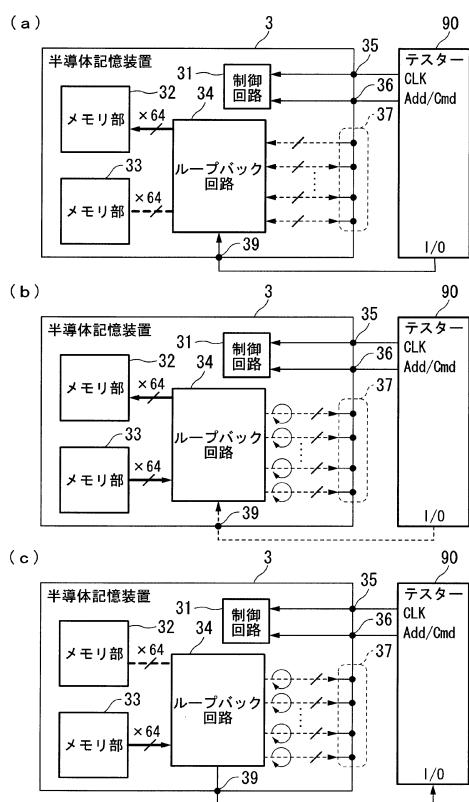

#### 【 0 0 9 6 】

次に、半導体記憶装置 3 の動作テストを行う動作テストモードにおけるテスト方法を説明する。図 1 2 は、半導体記憶装置 3 のテスト方法を示した図である。図示するように、半導体記憶装置 3 は、テスター 9 0 からクロック信号入力端子 3 5 を介してクロック信号が入力され、制御信号入力端子 3 6 を介して制御信号が入力され、テスター 9 0 の I / O 端子とテストデータ専用端子 3 9 とが接続されてテストデータが入出力される。

10

#### 【 0 0 9 7 】

まず、図 1 2 ( a ) は、テスター 9 0 から半導体記憶装置 3 へのテストデータの書き込み動作を示す概略図である。テスター 9 0 は、制御信号に含まれるアドレス信号で示した領域にテストデータをテストデータ専用端子 3 9 を介して 1 ビットずつ書き込む。ここで、テストデータ専用端子 3 9 から入力されるデータは、ループバック回路 1 4 が備えるバッファ・レジスタに記憶され、6 4 ビットごとメモリ部 3 2 に記憶される。

#### 【 0 0 9 8 】

図 1 2 ( b ) は、ループバック回路 3 4 のループバック動作を用いた動作を示す概略図である。テスター 9 0 は、テストデータの書き込みが完了すると、メモリ部 3 2 に対するバースト読み出しコマンドとメモリ部 3 3 に対するバースト書き込みコマンドとを制御信号入力端子 3 6 から半導体記憶装置 3 に入力する。これにより、制御回路 3 1 は、ループバック回路 3 4 のループバック動作を用いて、メモリ部 3 2 が記憶するテストデータをバースト読み出しして、バースト読み出しされたテストデータを連続してメモリ部 3 3 に書き込み記憶させる。

20

#### 【 0 0 9 9 】

図 1 2 ( c ) は、テスター 9 0 から読み出しコマンドを入力して、テストデータを読み出す動作を示した概略図である。テスター 9 0 は、読み出しコマンドを半導体記憶装置 3 に入力し、メモリ部 3 3 にループバック動作を用いて書き込み記憶させたデータをテストデータ専用端子 3 9 を介して読み出し、読み出したテストデータが予め用意しておいた期待値と一致するか否かを判定し、当該テスト対象の半導体記憶装置 3 に故障があるか否かの検出を行う。ここで、読み出すテストデータは、ループバック回路 1 4 が備えるバッファ・レジスタに記憶され、順次テストデータ専用端子 3 9 から出力される。

30

#### 【 0 1 0 0 】

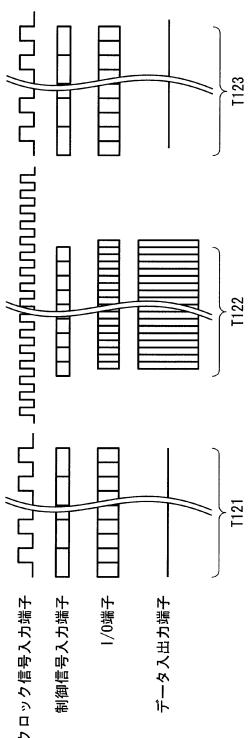

図 1 3 は、半導体記憶装置 3 とテスター 9 0 を用いたテスト動作を示す概略図である。T 1 2 1 で図示される入力きかんにおいて、テスター 9 0 は、書き込みコマンドを含む制御信号及びクロック信号を半導体記憶装置 3 に出力すると共に、テストデータ専用端子 3 9 を介してテストデータを半導体記憶装置 3 に出力してテストデータを書き込む。

#### 【 0 1 0 1 】

次に、T 1 2 2 で図示される期間において、テスター 9 0 は、クロック信号とループバック動作を行わせる読み出しコマンド及び書き込みコマンドを含む制御信号を半導体記憶装置 3 に出力する。これにより、T 1 2 2 で示される期間において、半導体記憶装置 3 は、メモリ部 3 2 に記憶されているテストデータを読み出し、読み出したテストデータをメモリ部 3 3 に書き込んで記憶させる。

40

#### 【 0 1 0 2 】

続く T 1 3 3 で図示される期間において、テスター 9 0 は、読み出しコマンドを含む制御信号及びクロック信号を半導体記憶装置 1 に出力して、ループバック動作を用いて書き込み記憶させたテストデータをテストデータ専用端子 3 9 を介して読み出し、読み出したテストデータが予め用意しておいたデータである期待値と一致するか否かを判定し、当該テスト対象の半導体記憶装置 3 に故障があるか否かの検出を行う。

#### 【 0 1 0 3 】

50

上述のように、半導体記憶装置3のテスター90を用いたテストは行われる。半導体記憶装置3は、テストの際にデータ入出力端子37を用いないため、動作テスト用の回路が不要になる。これにより、データ入出力端子37のそれぞれの端子の負荷を揃えることが容易になり、データ入出力端子37の端子相互のACタイミングのずれの解消が容易になる。なお、テスター90と半導体記憶装置3との間のテストデータの転送は、半導体記憶装置3の実動作速度より遅くてもよい。

#### 【0104】

上述した第1実施形態から第3実施形態のテスト方法を用いることで、データビット幅が広い半導体記憶装置の動作テストにおいても、テストデータの入出力に要するテスターのI/O端子数を削減することができ、一度に動作テストが行える半導体記憶装置の数を増やすことが可能となる。10

また、テスターと半導体記憶装置との間で実動作速度のような高速なデータ転送を行わずとも、半導体記憶装置のメモリ部に対してデータの読み出し及び書き込みを行う実動作速度による高速な動作テストを行うことが可能になる。

この結果、テスターが目的とする動作テストの周波数でデータの入出力は行えなくとも、目的の周波数のクロック信号が出力できれば、高速に動作する半導体記憶装置の故障検出のための動作テストを行うことが可能となる。このようなテスターは、高速にデータの入出力が行えるテスターに比べ安価であるため半導体記憶装置のコストの削減に効果的である。

#### 【0105】

また、通常動作においても、ループバック回路にループバック動作を行わせることで、半導体記憶装置は、読み出されるデータを外部の装置を介さずに異なる記憶領域に書き込み記憶させることができる。これにより、半導体記憶装置において、記憶されているデータを異なる記憶領域にコピーする動作に要するクロックサイクルを削減することが可能となる。なお、第1から第3実施形態は、DDR-SDRAMを用いて説明したが、これ以外の半導体記憶装置、例えば、SDRAMなどであってもよい。20

#### 【符号の説明】

#### 【0106】

1、2、3…半導体記憶装置

11、21、31…制御回路

12、13、22、23、32、33…メモリ部

14、24、34…ループバック回路

15、25、35…クロック信号入力端子

16、26、36…制御信号入力端子

17、27、37…データ入出力端子

39…テストデータ専用端子

90…テスター

100…ループバック・ロック

101…制御部、102、103…バッファ、104…ラッチ

105、106、108、109…フリップ・フロップ

107…プログラマブル遅延素子

110…セレクタ

111…クロック信号入力端子、112…データ入出力端子

113…制御信号端子

114、115…内部データ入出力端子

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

審査官 小林 紀和

(56)参考文献 特開平04-275654 (JP, A)

特開平04-373047 (JP, A)

特開平01-251400 (JP, A)

特開2000-156078 (JP, A)

特開2000-331498 (JP, A)

特開2001-043699 (JP, A)

特開平03-062245 (JP, A)

特開昭58-205992 (JP, A)

特開平10-207787 (JP, A)

特開2000-231800 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 29 / 12

G 11 C 11 / 401

G 11 C 11 / 407