(12)发明专利

(10)授权公告号 CN 105981173 B

(45)授权公告日 2019.05.10

(21)申请号 201480075197.3

(73)专利权人 丰田自动车株式会社

(22)申请日 2014.10.06

地址 日本爱知县

(65)同一申请的已公布的文献号

(72)发明人 高谷秀史 斋藤顺 添野明高

申请公布号 CN 105981173 A

滨田公守 水野祥司 青井佐智子

渡辺行彦

(43)申请公布日 2016.09.28

(74)专利代理机构 北京金信知识产权代理有限公司 11225

(30)优先权数据

代理人 苏萌萌 范文萍

2014-023869 2014.02.10 JP

(51)Int.Cl.

H01L 29/12(2006.01)

(85)PCT国际申请进入国家阶段日

H01L 29/06(2006.01)

2016.08.09

H01L 29/78(2006.01)

(86)PCT国际申请的申请数据

审查员 梁庆然

PCT/JP2014/076722 2014.10.06

(87)PCT国际申请的公布数据

W02015/118721 JA 2015.08.13

权利要求书2页 说明书8页 附图15页

(54)发明名称

半导体装置以及半导体装置的制造方法

(57)摘要

一种半导体装置，具有：终端沟槽，其围绕形成有多个栅极沟槽的区域的周围一周；下端p型区，其为p型，并与终端沟槽的下端相接；外周p型区，其为p型，并从外周侧与终端沟槽相接，且露出于半导体基板的表面；多个保护环区，其为p型，并被形成在与外周p型区相比靠外周侧，且露出于半导体基板的表面；外周n型区，其为n型，并使外周p型区与多个保护环区分离，且使多个保护环区相互分离。

1.一种半导体装置,其具有半导体基板,并具有:

第一区域,其为n型,并位于所述半导体基板内且露出于所述半导体基板的表面;

第二区域,其为p型,并被配置在所述第一区域的下侧;

第三区域,其为n型,并被配置在所述第二区域的下侧,且通过所述第二区域而与第一区域分离;

多个栅极沟槽,其被形成在所述表面上,并贯穿所述第一区域及所述第二区域而到达所述第三区域;

第一绝缘层,其被配置在所述栅极沟槽内;

栅电极,其被配置在所述栅极沟槽内,并隔着所述第一绝缘层而与所述第二区域对置;

第四区域,其为p型,并与所述栅极沟槽的下端相接;

终端沟槽,其被形成在所述表面上,并在俯视观察所述表面时围绕形成有多个所述栅极沟槽的区域的周围一周;

第二绝缘层,其被配置在所述终端沟槽内;

下端p型区,其为p型,并与所述终端沟槽的下端相接;

外周p型区,其为p型,并被形成在与所述终端沟槽相比靠外周侧,且与所述终端沟槽相接,并且露出于所述表面;

多个保护环区,其为p型,并被形成在与所述外周p型区相比靠外周侧,且露出于所述表面;

外周n型区,其为n型,并被形成在与所述终端沟槽相比靠外周侧,且与所述第三区域相连,并且使所述外周p型区与多个所述保护环区分离,且使多个所述保护环区相互分离,

通过在所述表面上形成高低差部,从而使所述表面具有第一表面以及从所述第一表面突出的第二表面,

所述终端沟槽被形成在所述第二表面上,

所述外周p型区露出于从所述第二表面跨至所述第一表面的范围内,

多个所述保护环区露出于所述第一表面

所述第四区域通过所述第三区域而与所述第二区域分离,

所述第二区域通过所述第三区域而与所述下端p型区以及所述外周p型区分离,

所述第四区域通过所述第三区域而与所述下端p型区以及所述外周p型区分离。

2.如权利要求1所述的半导体装置,其中,

各所述第四区域与对应的一个栅极沟槽的下端相接,并且未与其他的栅极沟槽的下端相接。

3.如权利要求1或2所述的半导体装置,其中,

所述终端沟槽与所述高低差部之间的间隔在 $10\mu\text{m}$ 以上。

4.如权利要求1或2所述的半导体装置,其中,

所述外周p型区中的处于外周侧的端部且露出于所述表面的区域为,铝的浓度高于硼的浓度的铝高浓度区,所述外周p型区中的与所述铝高浓度区相邻的区域为,硼的浓度高于铝的浓度的硼高浓度区。

5.如权利要求4所述的半导体装置,其中,

所述铝高浓度区的宽度与各个所述保护环区的宽度相比较宽。

6. 如权利要求1或2所述的半导体装置,其中,

所述下端p型区的一部分扩展至与所述终端沟槽相比靠内周侧,

扩展至与所述终端沟槽相比靠内周侧的所述下端p型区的所述一部分未扩展至与所述终端沟槽的下端相比靠上侧。

7. 如权利要求1或2所述的半导体装置,其中,

所述保护环区含有铝。

8. 一种制造权利要求1的半导体装置的方法,包括:

使p型层在n型层上生长的工序;

通过去除所述p型层的一部分,从而形成露出了所述n型层的表面以及露出了所述p型层且与露出了所述n型层的表面相比而突出的表面的工序;

通过向从露出了所述n型层的所述表面跨至露出了所述p型层的所述表面的范围内注入p型杂质,从而形成所述外周p型区的工序;

通过向露出了所述n型层的所述表面注入p型杂质,从而形成所述保护环区的工序;

在露出了所述p型层的所述表面上形成所述终端沟槽的工序。

## 半导体装置以及半导体装置的制造方法

### 技术领域

[0001] (关联申请的相互参照)

[0002] 本申请为2014年2月10日提交的日本专利申请2014-023869的关联申请，并主张基于该日本专利申请的优先权，且援引该日本专利申请所记载的全部内容作为构成本说明书的内容。

[0003] 本说明书所公开的技术涉及一种半导体装置。

### 背景技术

[0004] 日本特开2008-135522号公报中公开的半导体装置具有MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor: 金属氧化物场效应晶体管) 以及被形成在MOSFET的周围的多个终端沟槽。各终端沟槽以包围形成有MOSFET的区域的方式而以环状延伸。在各终端沟槽内配置有绝缘层。此外，在与各终端沟槽的底面相接的范围内的半导体层中形成有p型浮置区。在MOSFET断开时，耗尽层从MOSFET的体区向外周侧(形成终端沟槽的区域)延伸。当耗尽层延伸到最内侧的终端沟槽的下侧的p型浮置区时，耗尽层将进一步从该p型浮置区向外周侧延伸。由此，当耗尽层延伸到相邻的p型浮置区时，耗尽层将进一步从该p型浮置区向外周侧延伸。如此，耗尽层在经由各p型浮置区的同时，向形成有MOSFET的区域的周围广泛地扩展。由此，半导体装置的耐压得到提高。

### 发明内容

[0005] 发明所要解决的课题

[0006] 近年来，针对上述类型的半导体装置的耐压的要求变得越来越高。一直以来，上述的p型浮置区通过如下方式而形成，即，在形成了终端沟槽之后向终端沟槽的底面注入p型杂质，之后，使所注入的p型杂质向半导体层内扩散。然而，根据半导体的材料或其他的制造工序的各种条件，会存在p型杂质的扩散距离缩短，从而无法充分缩窄各p型浮置区之间的间隔的情况。在这种情况下，难以使耗尽层充分地向该间隔的区域内伸展。虽然考虑到通过缩窄各终端沟槽之间的间隔从而缩窄各p型浮置区之间的间隔，但由于加工精度的问题等，在缩窄各终端沟槽间的间隔方面存在界限。在现有的终端沟槽的结构中，在耐压的提高方面存在界限。因此，在本说明书中，公开一种能够实现更高耐压的半导体装置。

[0007] 用于解决课题的方法

[0008] 本说明书公开一种具有半导体基板的半导体装置。该半导体装置具有半导体基板，并具有：第一区域，其为n型，并位于所述半导体基板内且露出于所述半导体基板的表面；第二区域，其为p型，并被配置在所述第一区域的下侧；第三区域，其为n型，并被配置在所述第二区域的下侧，且通过所述第二区域而与第一区域分离；多个栅极沟槽，其被形成在所述表面上，并贯穿所述第一区域及所述第二区域而到达所述第三区域；第一绝缘层，其被配置在所述栅极沟槽内；栅电极，其被配置在所述栅极沟槽内，并隔着所述第一绝缘层而与所述第二区域对置；第四区域，其为p型，并与所述栅极沟槽的下端相接；终端沟槽，其被形

成在所述表面上，并在俯视观察所述表面时围绕形成有多个所述栅极沟槽的区域的周围一周；第二绝缘层，其被配置在所述终端沟槽内；下端p型区，其为p型，并与所述终端沟槽的下端相接；外周p型区，其为p型，并被形成在与所述终端沟槽相比靠外周侧，且与所述终端沟槽相接，并且露出于所述表面；多个保护环区，其为p型，并被形成在与所述外周p型区相比靠外周侧，且露出于所述表面；外周n型区，其为n型，并被形成在与所述终端沟槽相比靠外周侧，且与所述第三区域相连，并且使所述外周p型区与多个所述保护环区分离，且使多个所述保护环区相互分离。

[0009] 另外，在本说明书中，外周侧是指，从形成有多个栅极沟槽的区域远离的方向的意思。此外，上述的下端p型区既可以与上述的外周p型区连接，也可以与外周p型区分离。

[0010] 在该半导体装置中，通过第一区域、第二区域、第三区域、第四区域以及栅电极而形成了开关元件。在开关元件断开时，耗尽层将从第二区域向第三区域内扩展。在耗尽层抵达栅极沟槽的下端时，耗尽层将到达第四区域。于是，耗尽层再从第四区域向第三区域内扩展。由此，确保了形成有开关元件的区域内的耐压。此外，在从第二区域扩展至第三区域内的耗尽层抵达终端沟槽的下端时，耗尽层将到达下端p型区。于是，耗尽层从下端p型区以及外周p型区向外周n型区内延伸。在从外周p型区起延伸的耗尽层到达外周p型区的相邻的保护环区时，耗尽层将进一步从该保护环区向相邻的保护环区延伸。耗尽层经由各保护环区向外周侧扩展。由此，耗尽层广泛地向外周侧的区域伸展，从而确保了耐压。如此，在该半导体装置中，通过露出于半导体基板的表面的保护环，从而能够促进耗尽层的伸展。此外，由于保护环区被形成在露出于半导体基板的表面的范围内，因此能够高精度地形成。因此，能够较为容易地缩窄保护环区之间的间隔。因此，在该半导体装置中，能够通过保护环区而确保足够的耐压。

[0011] 在上述的半导体装置中，可以采用如下方式，即，通过在所述表面上形成高低差部，从而使所述表面具有第一表面以及从所述第一表面突出的第二表面。所述终端沟槽可以被形成在所述第二表面上。所述外周p型区可以露出于从所述第二表面跨至所述第一表面的范围内。多个所述保护环区露出于所述第一表面。此外，在该情况下，所述终端沟槽与所述高低差部之间的间隔可以在 $10\mu\text{m}$ 以上。

[0012] 在上述任一半导体装置中，可以采用如下方式，即，所述外周p型区中的位于外周侧的端部且露出于所述表面的区域为，A1的浓度高于B的浓度的A1高浓度区，所述外周p型区中的与所述A1高浓度区相邻的区域为，B的浓度高于A1的浓度的B高浓度区。在该情况下，可以采用如下方式，即，所述A1高浓度区的宽度与各个所述保护环区的宽度相比较宽。另外，上述的宽度表示从内周侧朝向外周侧的方向上的尺寸。

[0013] 根据这种结构，能够抑制外周p型区的漏电流。

[0014] 在上述的任一半导体装置中，也可以采用如下方式，即，所述下端p型区的一部分扩展至与所述终端沟槽相比靠内周侧，扩展至与所述终端沟槽相比靠内周侧的所述下端p型区的所述一部分未扩展至与所述终端沟槽的下端相比靠上侧。

[0015] 在上述的任一项的半导体装置中，也可以采用如下方式，即，所述保护环区含有铝。

[0016] 根据这种结构，能够更高精度地形成保护环区。

[0017] 上述的具有高低差的半导体装置可以通过以下的方法而进行制造。该方法包括：

使p型层在n型层上生长的工序；通过去除所述p型层的一部分，从而形成露出了所述n型层的表面以及露出了所述p型层且与露出了所述n型层的表面相比而突出的表面的工序；通过向从露出了所述n型层的所述表面跨至露出了所述p型层的所述表面的范围内注入p型杂质，从而形成所述外周p型区的工序；通过向露出了所述n型层的所述表面注入p型杂质，从而形成所述保护环区的工序；在露出了所述p型层的所述表面上形成终端沟槽的工序。

## 附图说明

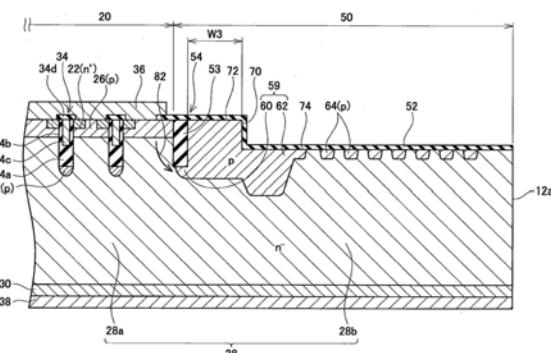

- [0018] 图1为半导体装置10的俯视图。

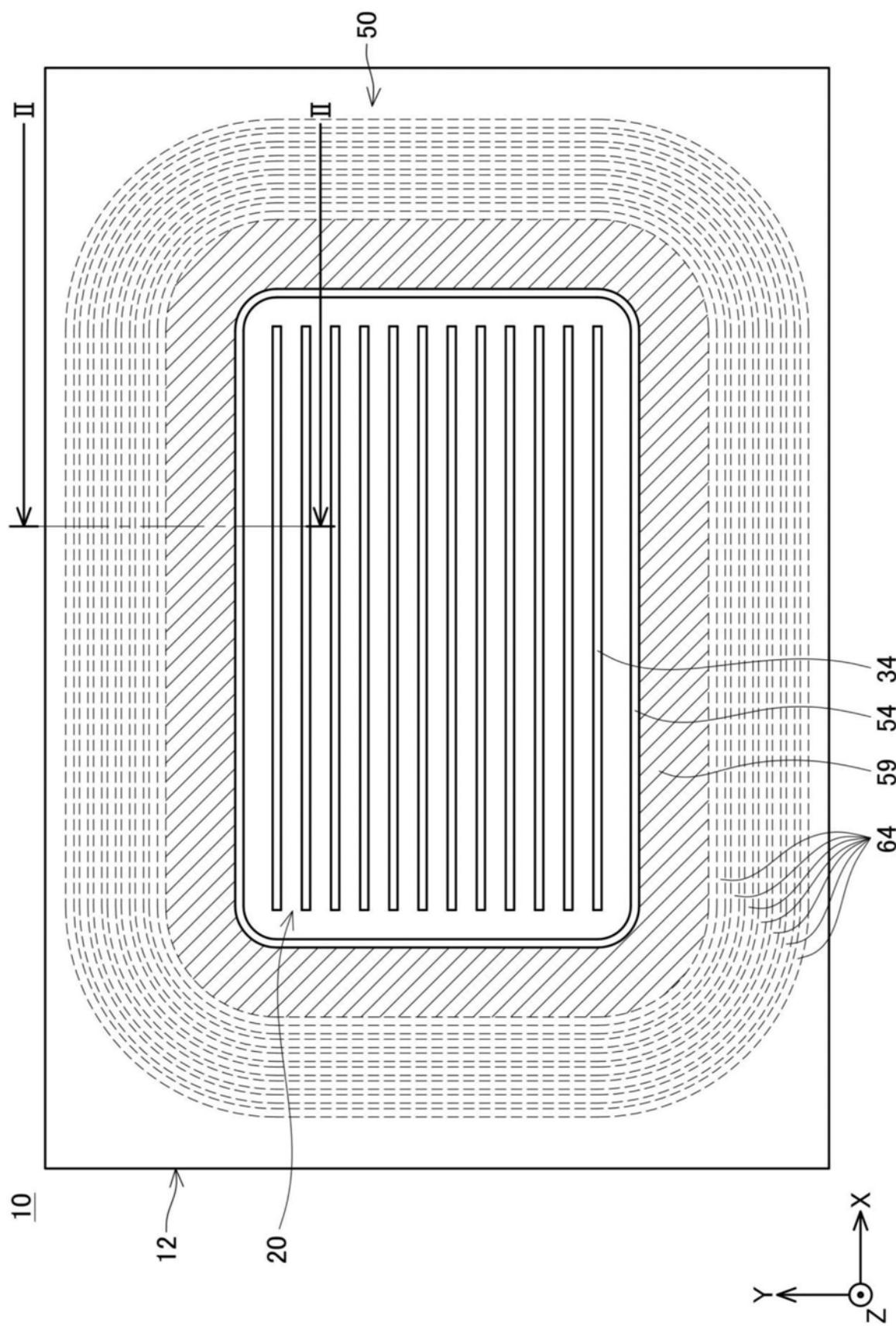

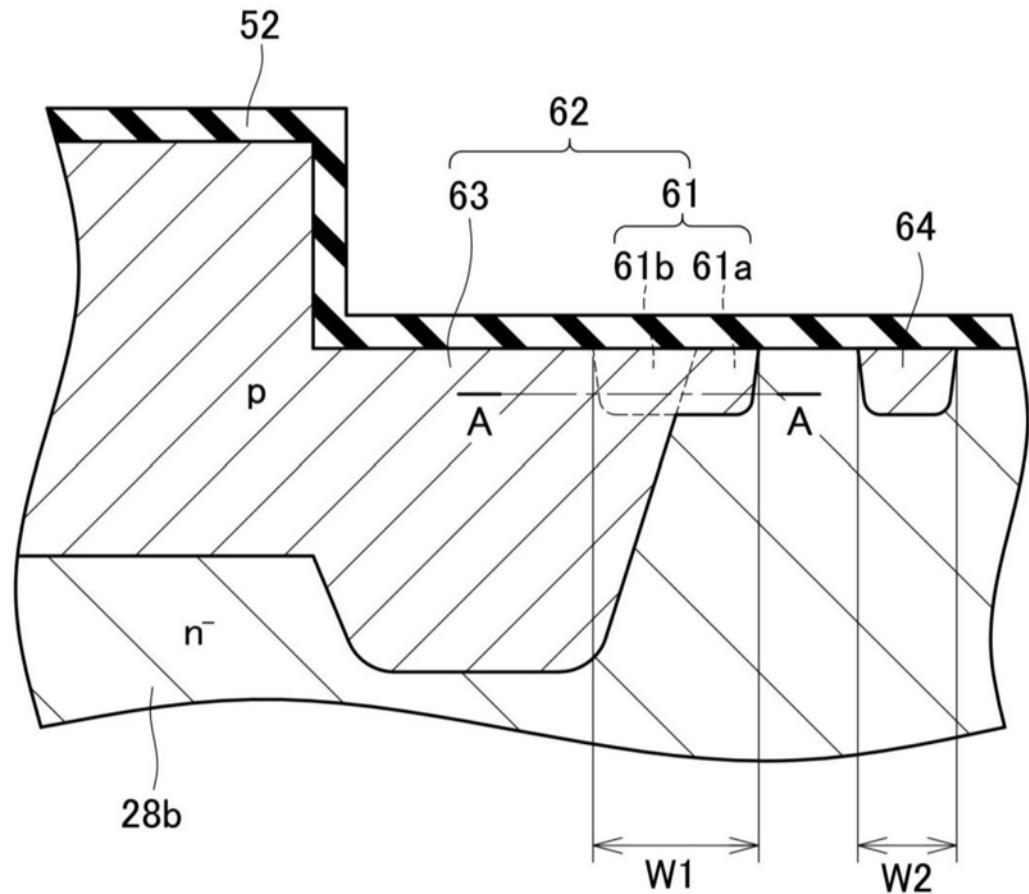

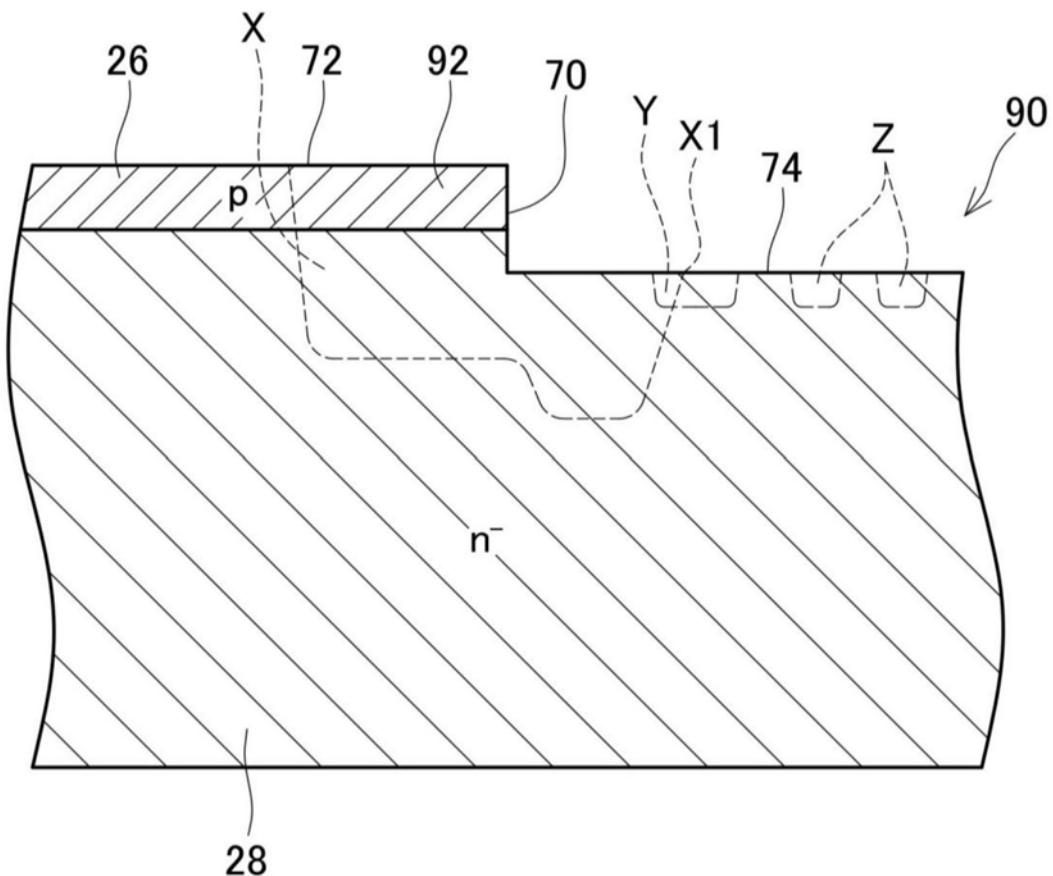

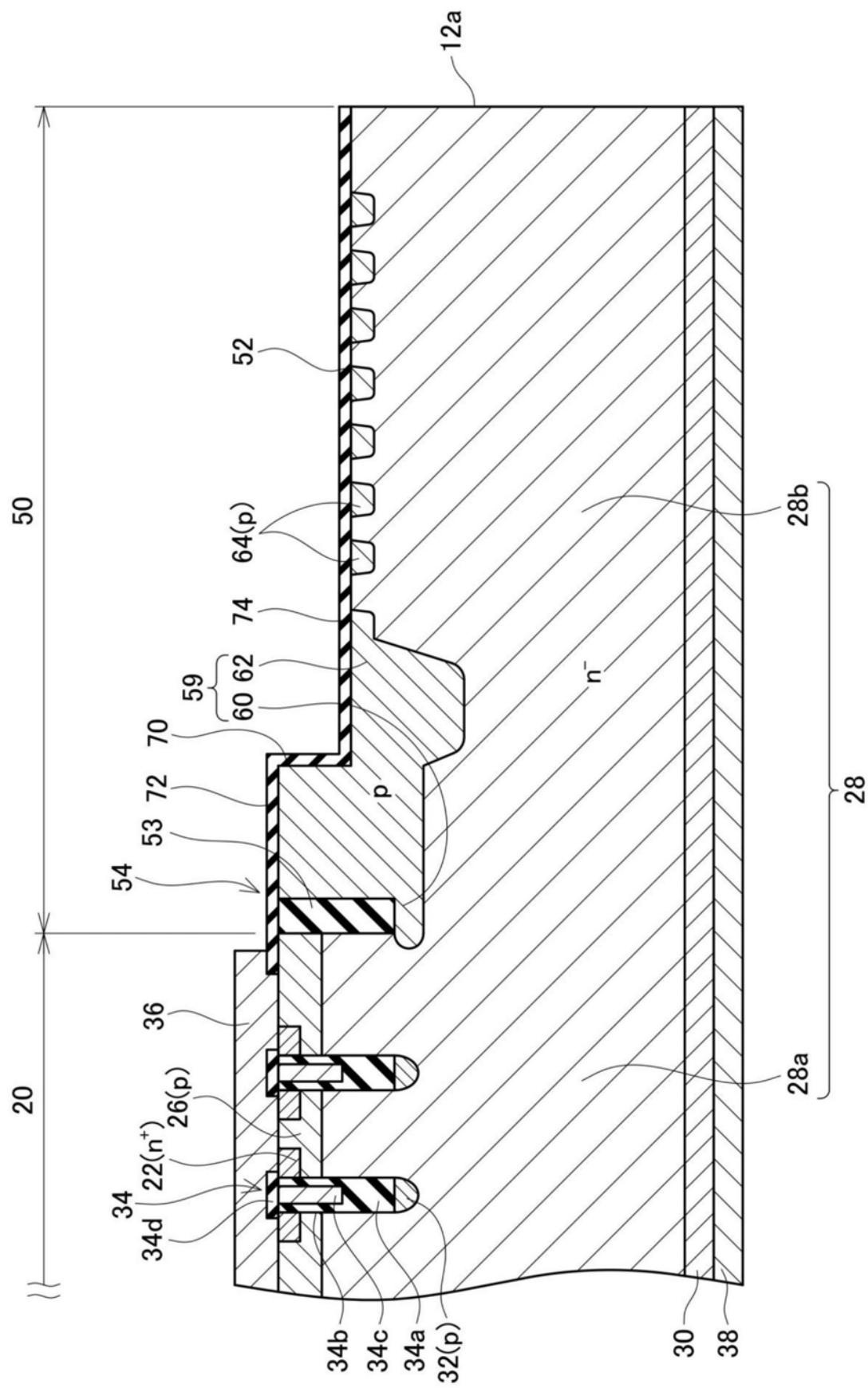

- [0019] 图2为图1中的Ⅱ-Ⅱ线处的纵剖视图。

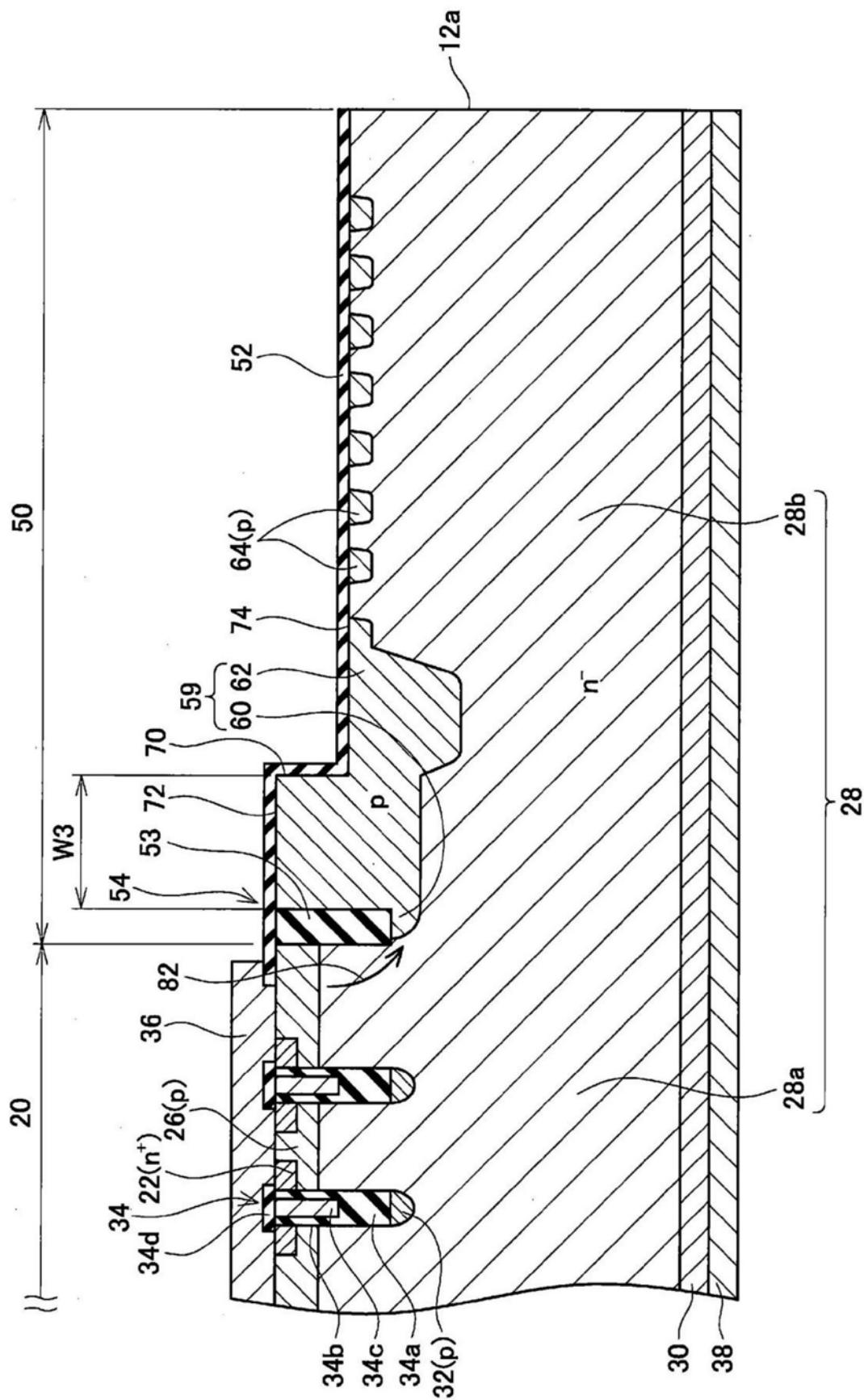

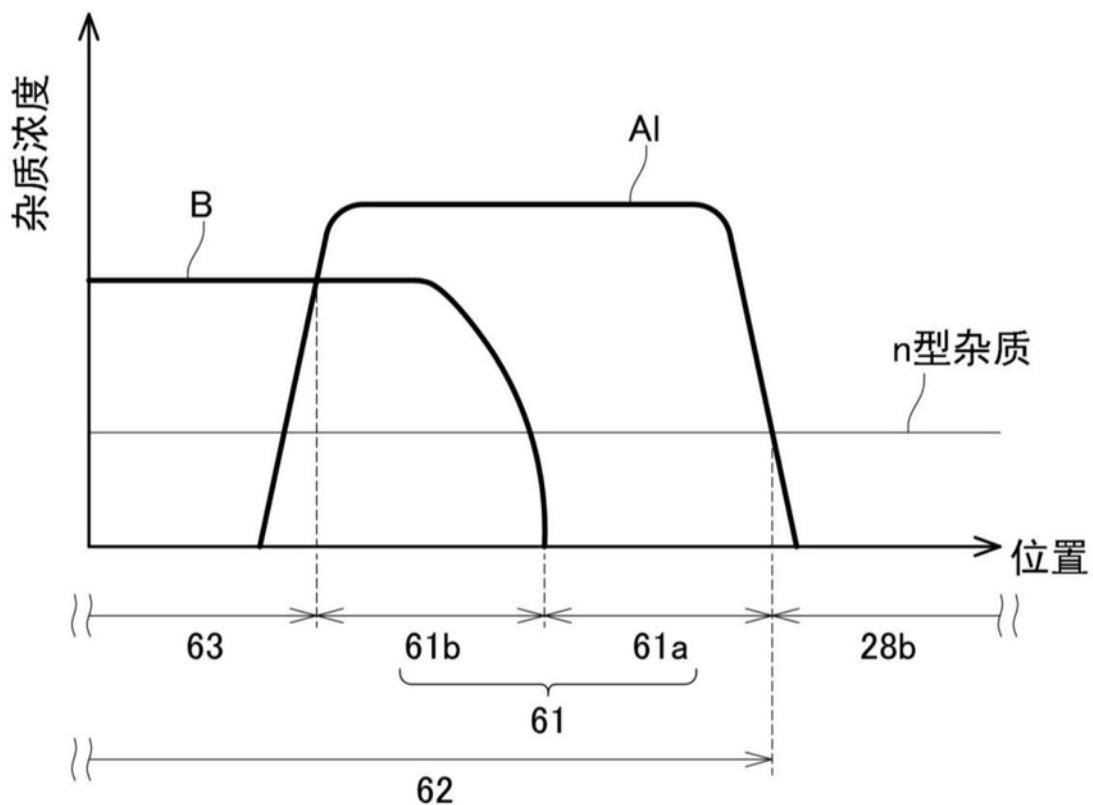

- [0020] 图3为外周p型区62的放大剖视图。

- [0021] 图4为表示图3的A-A线处的杂质浓度分布的曲线图。

- [0022] 图5为半导体装置10的制造工序的说明图。

- [0023] 图6为半导体装置10的制造工序的说明图。

- [0024] 图7为半导体装置10的制造工序的说明图。

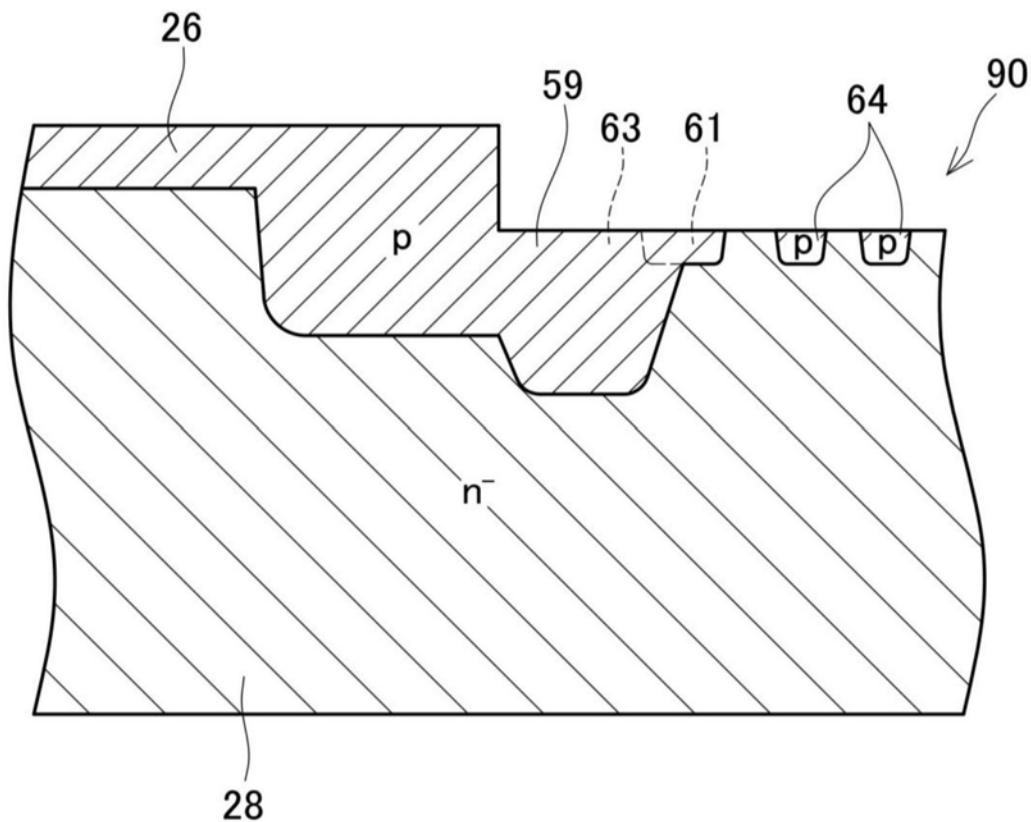

- [0025] 图8为半导体装置10的制造工序的说明图。

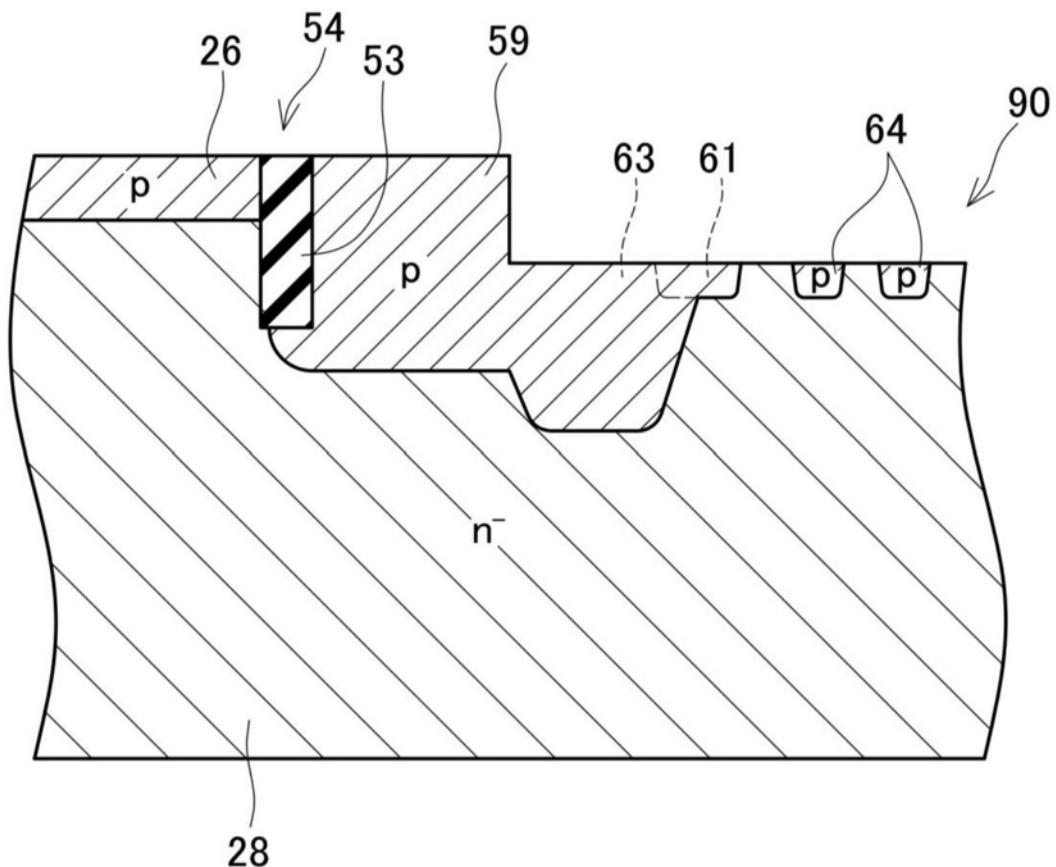

- [0026] 图9为半导体装置10的制造工序的说明图。

- [0027] 图10为半导体装置10的制造工序的说明图。

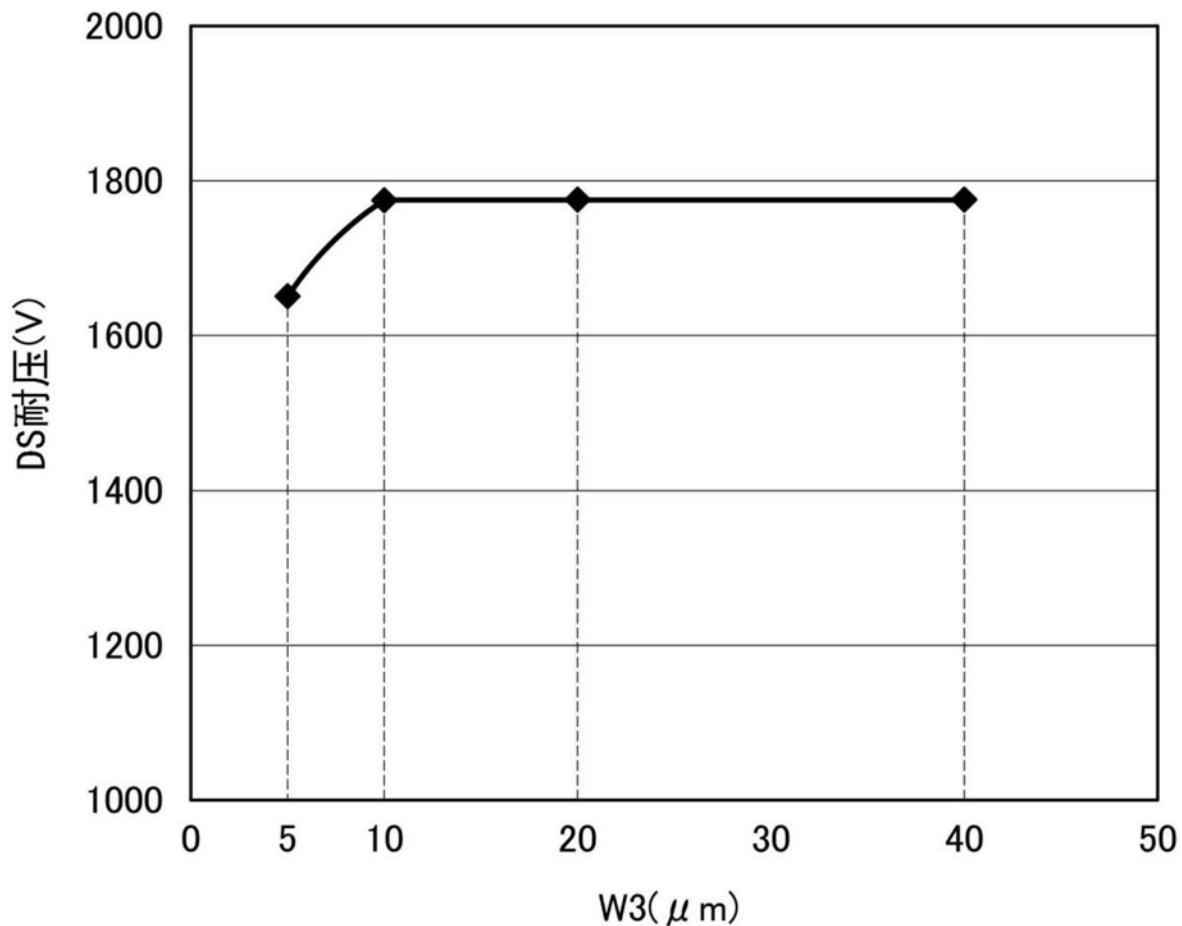

- [0028] 图11为表示宽度W3与DS耐压的关系的曲线图。

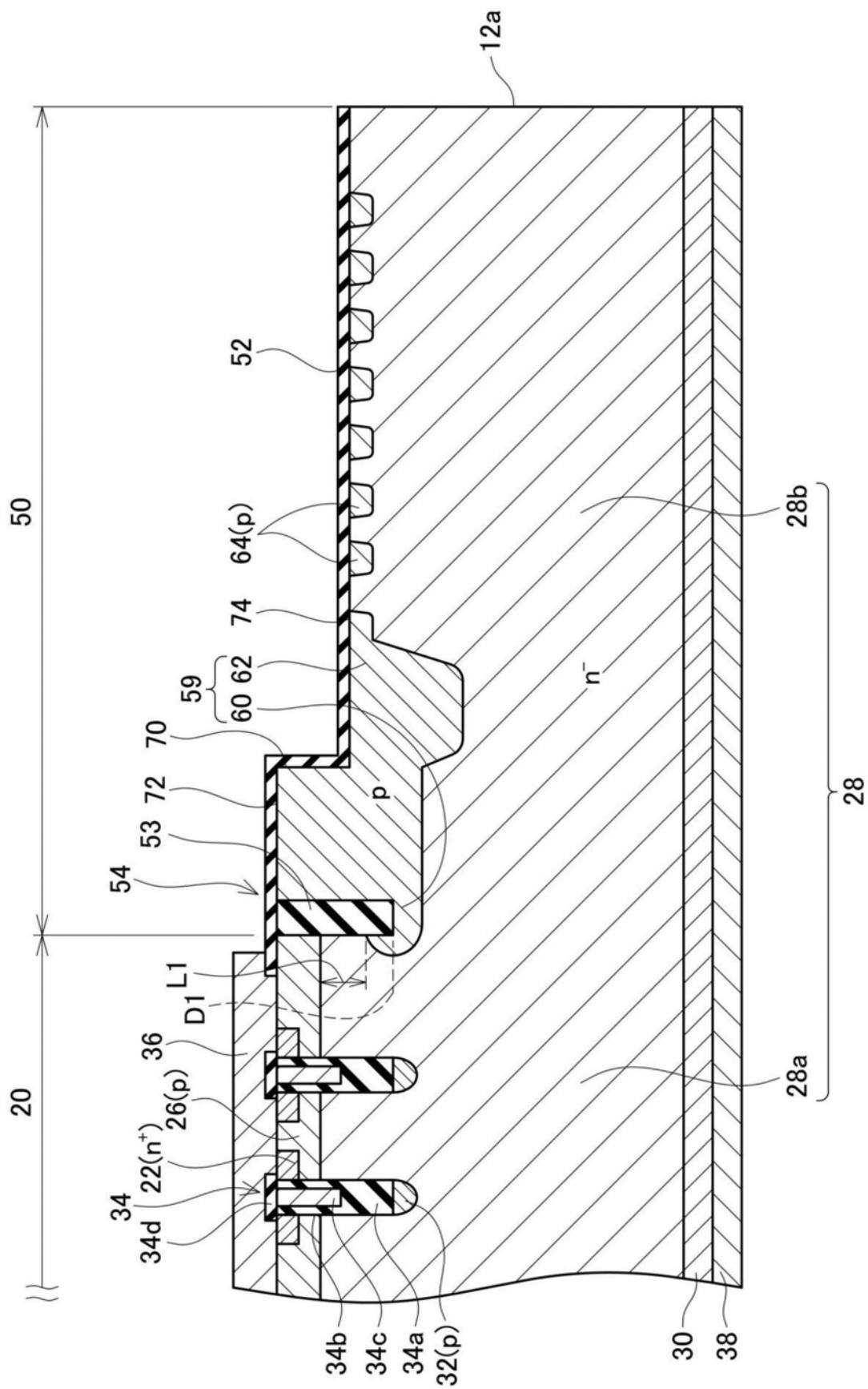

- [0029] 图12为第一改变例的半导体装置的与图2对应的纵剖视图。

- [0030] 图13为第二改变例的半导体装置的与图2对应的纵剖视图。

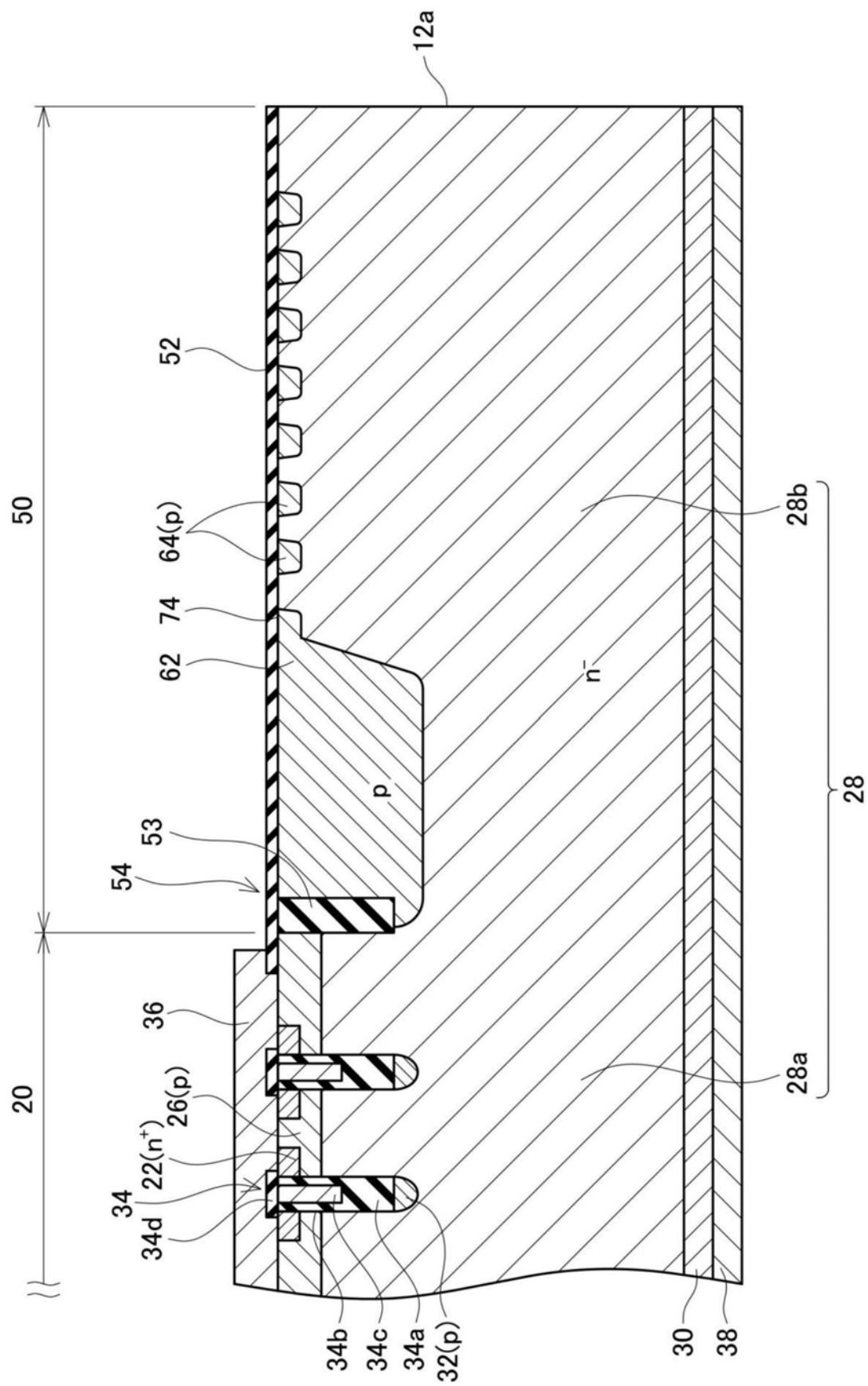

- [0031] 图14为第三改变例的半导体装置的与图2对应的纵剖视图。

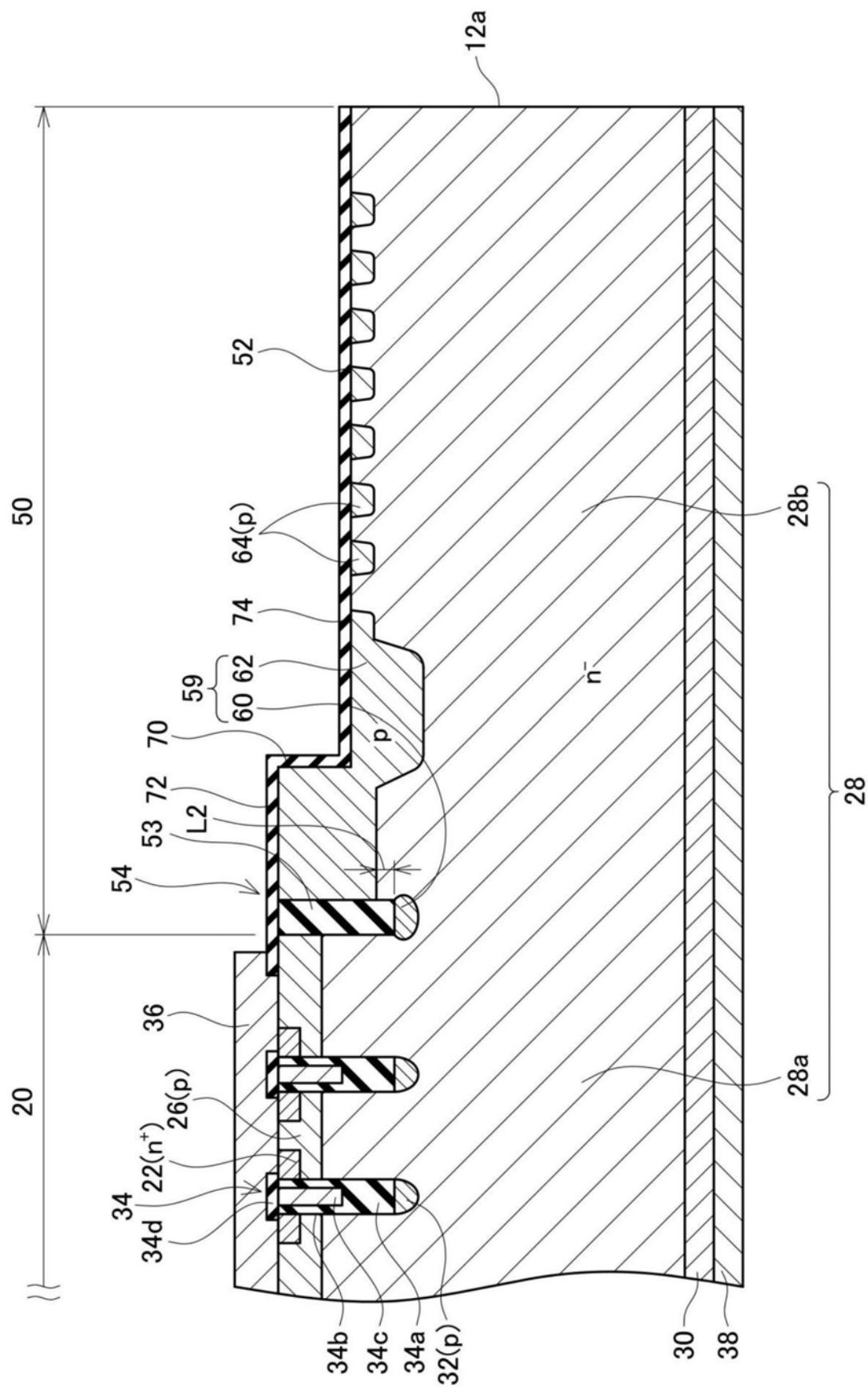

- [0032] 图15为第四改变例的半导体装置的与图2对应的纵剖视图。

## 具体实施方式

[0033] 如图1所示，实施例1所涉及的半导体装置10具有由SiC(碳化硅)构成的半导体基板12。半导体基板12具有MOSFET区20和外周区50。在MOSFET区20内形成有MOSFET。另外，在图1中，考虑到附图的易观察性，而在MOSFET区20内仅图示了栅极沟槽34。外周区50为MOSFET区20的外侧的区域。在本实施例中，外周区50为MOSFET区20与半导体基板12的端面12a之间的区域。在外周区50内形成有耐压结构。另外，在图1中，考虑到附图的易观察性，在外周区50内仅图示了终端沟槽54、边界部p型区59以及保护环区64。

[0034] 如图2所示，在MOSFET区20内，形成有源极区22、体区26、漂移区28、漏极区30、p型浮置区32、栅极沟槽34、源极电极36以及漏极电极38。

[0035] 源极区22在MOSFET区20内形成有多个。源极区22为以高浓度含有n型杂质的n型区。源极区22被形成在露出于半导体基板12的上表面的范围内。

[0036] 体区26被形成在源极区22的侧方以及下侧，并与源极区22相接。体区26为p型区。体区26在未形成有源极区22的位置处露出于半导体基板12的上表面。

[0037] 漂移区28为以低浓度含有n型杂质的n型区。漂移区28的n型杂质浓度低于源极区22的n型杂质浓度。漂移区28被形成在体区26的下侧。漂移区28与体区26相接，并通过体区26而与源极区22分离。

[0038] 漏极区30为以高浓度含有n型杂质的n型区。漏极区30的n型杂质浓度高于漂移区28的n型杂质浓度。漏极区30被形成在漂移区28的下侧。漏极区30与漂移区28相接，并通过漂移区28而与体区26分离。漏极区30被形成在露出于半导体基板12的下表面的范围内。

[0039] 栅极沟槽34在MOSFET区20内形成有多个。栅极沟槽34为被形成在半导体基板12的上表面上的槽。各栅极沟槽34以贯穿源极区22和体区26而到达漂移区28的方式被形成。如图1所示，多个栅极沟槽34以相互平行的方式延伸。如图2所示，在各栅极沟槽34内形成有底部绝缘层34a、栅极绝缘膜34b以及栅电极34c。底部绝缘层34a为被形成在栅极沟槽34的底部的较厚的绝缘层。底部绝缘层34a的上侧的栅极沟槽34的侧面被栅极绝缘膜34b覆盖。在底部绝缘层34a的上侧的栅极沟槽34内形成有栅电极34c。栅电极34c隔着栅极绝缘膜34b而与源极区22、体区26以及漂移区28对置。栅电极34c通过栅极绝缘膜34b以及底部绝缘层34a而与半导体基板12绝缘。栅电极34c的上表面被绝缘层34d覆盖。

[0040] p型浮置区32位于半导体基板12内，且被形成在与各栅极沟槽34的底面(即，下端)相接的范围内。p型浮置区32的周围被漂移区28包围。各p型浮置区32通过漂移区28而被相互分离。此外，各p型浮置区32通过漂移区28而与体区26分离。

[0041] 源极电极36被形成在MOSFET区20内的半导体基板12的上表面上。源极电极36与源极区22以及体区26导通。

[0042] 漏极电极38被形成在半导体基板12的下表面上。漏极电极38与漏极区30导通。

[0043] 上述的漂移区28以及漏极区30扩展至外周区50。漂移区28和漏极区30扩展到半导体基板12的端面12a处。此外，漏极电极38被形成在包括外周区50在内的半导体基板12的整个下表面上。此外，外周区50内的半导体基板12的上表面被绝缘层52覆盖。在下文中，有时将MOSFET区20内的漂移区28称为元件部漂移区28a，并将外周区50内的漂移区28称为外周部漂移区28b。

[0044] 在外周区50内的半导体基板12的表面上形成有高低差部70。通过高低差部70，半导体基板12的表面被划分为中央部侧的表面72和端面12a侧的表面74。表面72相对于表面74而向上侧突出。因此，在与表面72对应的部分处，较之于与表面74对应的部分，半导体基板12的厚度较厚。上述的MOSFET区20被形成在与表面72对应的部分(厚度较厚的部分)处。高低差部70的高度大于体区26的厚度。因此，表面74与体区26的下端相比位于下侧(背面侧)。

[0045] 在外周区50内的半导体基板12的表面72上形成有终端沟槽54。在终端沟槽54内形成有绝缘层53。终端沟槽54被形成在与体区26相邻的位置处。终端沟槽54具有与栅极沟槽34大致相同的深度。因此，绝缘层53在与体区26相比较深的位置处与元件部漂移区28a相接。如图1所示，终端沟槽54以在俯视观察半导体基板12的表面时围绕MOSFET区20的周围一周的方式而延伸。因此，体区26通过绝缘层53而与外周区50内的任意p型区分离。即，在本实施例中，被终端沟槽54包围的区域为MOSFET区20。

[0046] 如图2所示，在与终端沟槽54的下端(即，底面)相接的位置处形成有下端p型区60。在本实施例中，下端p型区60未被形成在MOSFET区20内。此外，在与终端沟槽54相比靠外周侧的区域且与终端沟槽54相接的位置处，形成有外周p型区62。外周p型区62以从露出于表面72的位置跨至露出于表面74的位置的方式而被形成。外周p型区62露出于表面72、高低差部70以及表面74。此外，外周p型区62扩展到与终端沟槽54的下端相比较深的位置处。如图

所示,在本实施例中,下端p型区60与外周p型区62相连。由于下端p型区60与外周p型区62为一个p型区,因此在下文中有时会将两者统称为边界部p型区59。即,边界部p型区59为,以跨及露出于终端沟槽54的下端的位置、露出于表面72的位置以及露出于表面74的位置的方式而延伸的p型区。如图1所示,边界部p型区59以沿着终端沟槽54而围绕MOSFET区20的周围一周的方式被形成。如图2所示,在边界部p型区59的下侧形成有外周部漂移区28b。

[0047] 图3图示了外周p型区62的外周端部附近的放大剖视图。如图所示,外周p型区62具有A1(铝)高浓度区61和B(硼)高浓度区63。A1高浓度区61为与B相比A1的浓度较高的p型区,B高浓度区63为与A1相比B的浓度较高的p型区。除了不能控制的误差水平之外,外周p型区62不含有B和A1以外的p型杂质。A1高浓度区61被形成在外周p型区62露出于表面74的范围内的外周p型区62的外周端部处。B高浓度区63被形成在A1高浓度区61以外的外周p型区62内。外周p型区62的大部分由B高浓度区63构成。图4图示了外周p型区62的外周端部附近的杂质浓度分布(沿着图3的A-A线的杂质浓度分布)。在图3、图4中,区域61a为,含有A1而不含有B的区域。区域61b为,含有A1和B,且A1的浓度高于B的浓度的区域。A1高浓度区61由区域61a和区域61b构成。图3所示的A1高浓度区61的宽度W1(即,从内周侧朝向外周侧的方向上的尺寸)与后述的保护环区64各自的宽度W2相比较宽。另外,上述的宽度W1、W2表示从内周侧朝向外周侧的方向上的尺寸的意思。

[0048] 如图2所示,在外周p型区62的外周侧形成有多个保护环区64。各保护环区64为p型区,并被形成在露出于表面74的范围内。各保护环区64仅被形成在较浅的范围内。因此,各保护环区64的下端与外周p型区62的下端相比位于上侧(表面侧)。在各保护环区64的下侧形成有外周部漂移区28b。在最内周侧(MOSFET区20侧)的保护环区64与外周p型区62之间形成有外周部漂移区28b。通过外周部漂移区28b,最内周侧的保护环区64与外周p型区62分离。此外,在各保护环区64之间形成有外周部漂移区28b。通过外周部漂移区28b,各保护环区64相互分离。各保护环区64含有A1以作为p型杂质。除了不能控制的误差水平之外,各保护环区64不含有A1以外的p型杂质。

[0049] 接下来,对半导体装置10的工作进行说明。在使半导体装置10进行工作时,向漏极电极38与源极电极36之间施加使漏极电极38成为正的电压。并且,通过向栅电极34c施加栅极导通电压,从而使MOSFET区20内的MOSFET导通。即,在与栅电极34c对置的位置处的体区26内形成有沟道,从而电流从源极电极36经由源极区22、沟道、漂移区28、漏极区30而向漏极电极38流通。当停止栅极导通电压向栅电极34c的施加时,沟道将消失,从而MOSFET断开。在MOSFET断开时,耗尽层将从体区26与漂移区28的边界部的pn结向漂移区28内扩展。当耗尽层到达MOSFET区20内的p型浮置区32时,耗尽层还将从p型浮置区32向漂移区28内扩展。由此,两个p型浮置区32之间的漂移区28被有效耗尽化。因此,MOSFET区20内的电场集中被抑制。由此,实现了MOSFET区20内的较高的耐压。

[0050] 此外,如图2的箭头标记82所示,从上述的pn结起延伸的耗尽层也到达终端沟槽54的下侧的边界部p型区59。于是,耗尽层从边界部p型区59向漂移区28内扩展。栅极沟槽34与终端沟槽54之间的漂移区28通过从栅极沟槽34的下侧的p型浮置区32起扩展的耗尽层以及从终端沟槽54的下侧的边界部p型区59(即,下端p型区60)起扩展的耗尽层而被耗尽化。此时,由于栅极沟槽34的深度与终端沟槽54的深度大致相等(即,p型浮置区32的深度方向上的位置与下端p型区60的深度方向上的位置大致相等),因此在栅极沟槽34与终端沟槽54之

间的漂移区28内,等电位线在横向(与表面72平行的方向)上延伸。由此,终端沟槽54的附近的电场集中被抑制。

[0051] 此外,边界部p型区59从与终端沟槽54的下端相接的范围扩展到与半导体基板12的表面74相接的位置。因此,在表面74的附近,耗尽层从边界部p型区59朝向最内周侧的保护环区64扩展。在耗尽层到达最内周侧的保护环区64时,耗尽层将从该保护环区64向与之相邻的保护环区64伸展。如此,耗尽层依次经由各保护环区64而向外周侧扩展。因此,耗尽层广泛地在外周区50内伸展。由此,实现了外周区50内的较高的耐压。

[0052] 如此,在该半导体装置中,通过终端沟槽54的下侧的边界部p型区59被设置在与p型浮置区32相同的深度的位置处,从而抑制了MOSFET区20的外周端部附近的电场集中。此外,通过在与终端沟槽54相比靠外周侧处,边界部p型区59从终端沟槽54的底面延伸到半导体基板12的表面74,从而能够使耗尽层到达仅被形成在表面74附近的较浅的范围内的保护环区64。其结果为,通过多个保护环区64而促进了外周区50内的耗尽层的伸展。此外,由于各保护环区64相互分离,因此能够使电位在外周区50内比较均匀地分布。因此,实现了外周区50内的较高的耐压。

[0053] 此外,在该半导体装置中,在位于外周p型区62的外周端部处且露出于表面74的范围内,形成有Al高浓度区61。通过以这种方式形成Al高浓度区61,从而能够抑制在外周p型区62的表面附近流通的漏电流。

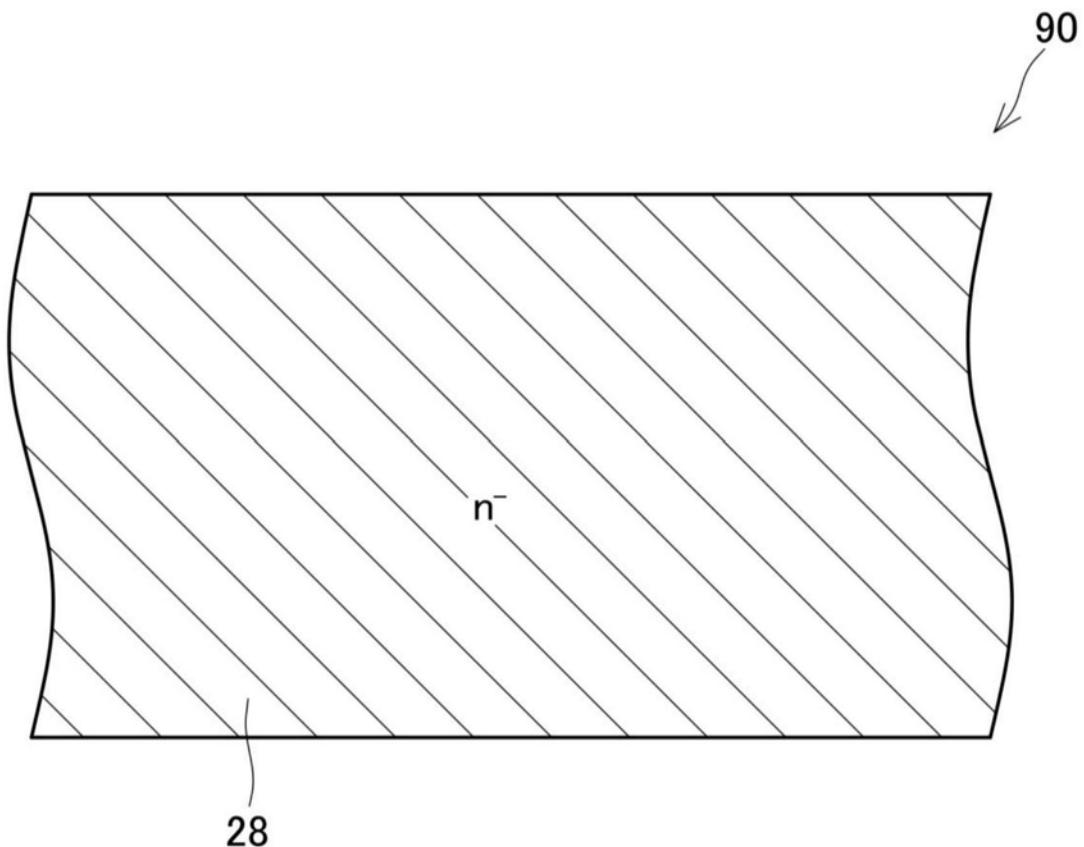

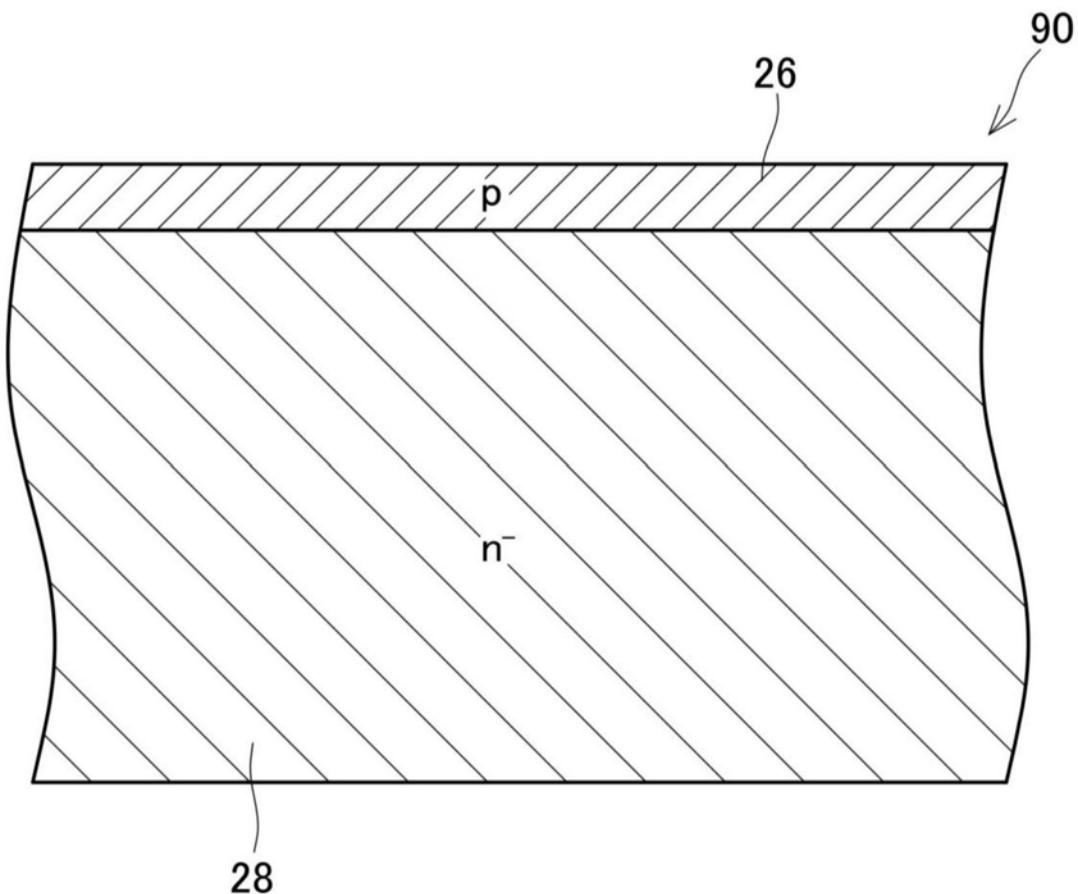

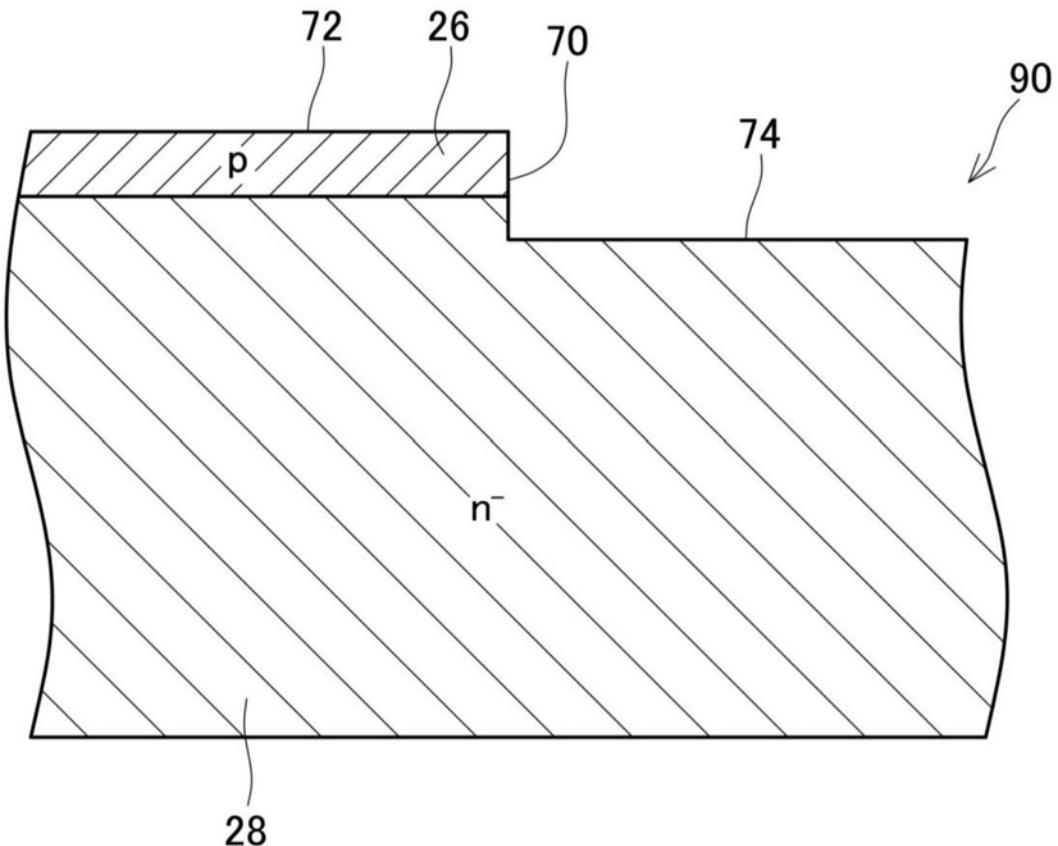

[0054] 接下来,对半导体装置10的制造方法进行说明。首先,如图5所示,准备仅由n型层28构成的半导体晶片90。n型层28成为漂移区28的区域。接下来,如图6所示,通过外延生长而在n型层28的表面上形成p型层26。p型层26成为体区26的区域。接下来,对预定范围内的半导体晶片90的表面局部地进行蚀刻。在此,在进行了蚀刻的范围内,如图7所示,以去除p型层26从而露出n型层28的方式而实施蚀刻。由此,在半导体晶片90的表面形成高低差部70。通过高低差部70而使半导体晶片90的表面被划分为表面72和表面74。

[0055] 接下来,实施针对边界部p型区59的离子注入。即,首先,向半导体晶片90的表面中的包含高低差部70在内的范围(即,从表面72跨至表面74的范围)内注入B。在此,通过对B的注入能量进行调节,从而如图8的注入范围X所示,以使B从较浅的位置分布到比较深的位置的方式而对B进行注入。接下来,在半导体晶片90的表面74中的包括注入范围X的外周端部X1在内的范围(即,图8的注入范围Y)内注入Al。在此,通过将Al的注入能量设为较低,从而以仅在半导体晶片90的表面74附近注入Al的方式而对Al进行注入。

[0056] 接下来,实施针对保护环区64的离子注入。即,向半导体晶片90的表面74中的与注入范围Y相比靠外周侧(与各保护环区64对应的注入范围Z)注入Al。在此,通过将Al的注入能量设为较低,从而以仅在半导体晶片90的表面74附近注入Al的方式而对Al进行注入。另外,注入范围Z的宽度与注入范围Y的宽度相比较窄。

[0057] 接下来,通过对半导体晶片90进行热处理,从而使所注入的Al和B扩散并活化。由此,如图9所示,形成边界部p型区59和保护环区64。此时,由于与Al相比,B在SiC中的扩散系数较大,因此B的分布范围扩大。即,与注入范围X相比,扩散后的B所分布的范围变得相当广。当以上述的方式扩大Al的注入范围Y的宽度时,即使B的分布范围扩大,也能够容易地将Al高浓度区61配置在边界部p型区59的外周端部。此外,由于保护环区64被形成在半导体晶片90的表面74附近的较浅的位置处,因此能够高精度地形成保护环区64。尤其是由于被注

入到保护环区64内的Al在SiC中的扩散系数较低,因此能够更高精度地形成保护环区64。因此,能够使各保护环区64之间的间隔狭小化。并且,还能够使外周p型区62与保护环区64之间的间隔狭小化。

[0058] 接下来,如图10所示,在外周p型区62的端部(与Al高浓度区61为相反的一侧的端部)形成终端沟槽54,并在终端沟槽54内形成绝缘层53。

[0059] 之后,通过形成MOSFET区20内的结构,并形成其他的必要的结构(扩散层、电极、绝缘层等),从而完成图1的半导体装置10。另外,上述的制造方法的各工序的顺序能够进行适当变更。此外,可以先于外周区50内的结构而形成MOSFET区20内的结构,也可以与外周区50内的结构并行地形成MOSFET区20内的结构。

[0060] 如以上所说明的那样,根据该制造方法,能够使各保护环区64之间的间隔狭小化。此外,还能够使外周p型区62与保护环区64之间的间隔狭小化。因此,在该半导体装置10中,耗尽层易于在外周区50内延伸。因此,根据该方法,能够制造出外周区50的耐压较高的半导体装置10。

[0061] 另外,图11图示了终端沟槽54与高低差部70之间的间隔W3(参照图2)与半导体装置10的DS间耐压(漏极-源极间的耐压)的关系。如图所示,在间隔W3小于10μm时,DS间耐压将急剧地下降。因此,优选为,间隔W3在10μm以上。

[0062] 此外,在上述的实施例的半导体装置10中,终端沟槽54的下侧的边界部p型区59(即,下端p型区60)未被形成在MOSFET区20侧。然而,如图12所示,下端p型区60的一部分也可以与终端沟槽54相比向MOSFET区20侧突出。根据这种结构,更容易使栅极沟槽34与终端沟槽54之间的漂移区28耗尽化。另外,在该情况下,优选为,该突出的部分与终端沟槽54的下端相比不向上侧(体区26侧)突出。即,当如图13那样,下端p型区60的一部分在MOSFET区20内与终端沟槽54的下端的深度D1相比位于上侧时,下端p型区60与体区26之间的距离L1将缩短。当距离L1缩短时,DS间耐压将下降。因此,位于MOSFET区20内的下端p型区60优选为,仅存在于与终端沟槽54的下端相比而靠下侧处。但是,也可以根据情况,而将下端p型区60的一部分配置在与深度D1相比靠上侧处,并使距离L1最优化,从而确保DS间耐压。

[0063] 此外,虽然在上述的半导体装置10中,在半导体基板12的表面上形成有高低差部70,但也可以如图14所示那样,半导体基板12的表面是平的。另外,图14的半导体装置的体区26通过离子注入而被形成。与外延生长不同,通过离子注入,能够仅在半导体晶片的表面的必要的区域内形成体区26。因此,在图14的半导体装置的制造工序中,不需要实施在上述的实施例中所说明的对p型层26(体区26)的一部分进行蚀刻的工序(即,形成高低差部70的工序)。因此,在图14的半导体装置中,半导体基板12的表面成为平的。

[0064] 此外,在上述的实施例中,下端p型区60与外周p型区62相连。然而,也可以如图15所示那样,下端p型区60与外周p型区62分离。在图15中,外周p型区62被形成在与终端沟槽54相比较浅的范围内。因此,通过漂移区28而使下端p型区60与外周p型区62分离。即使在这种结构中,只需将下端p型区60与外周p型区62之间的距离L2设定为耗尽层能够从下端p型区60伸展到外周p型区62的距离,便能够与上述的实施例同样地确保外周区50的耐压。另外,为了使耗尽层伸展,优选为,以满足数学式 $L2 \leq \{2\epsilon(Vbi-V)/q \times Nb\}^{1/2}$ 的方式而对距离L2进行设定。在此,ε为漂移区28的介电常数,Vbi为下端p型区60与漂移区28之间的内建电位,V为施加电压,q为元电荷,Nb为漂移区28的n型杂质浓度。

[0065] 此外,虽然在上述的实施例中,对具有MOSFET的半导体装置进行了说明,但也可以代替MOSFET而形成IGBT等其他的元件。此外,虽然在上述的实施例中,由SiC构成了半导体基板12,但也可以使用由Si等其他的材质构成的半导体基板。

[0066] 虽然以上对本发明的具体示例进行了详细说明,但这些只不过是例示,并不是对权利要求书进行限定的内容。在权利要求书所记载的技术中,包括对以上所例示的具体示例进行了各种改变、变更的内容。

[0067] 本说明书或附图中所说明的技术要素以单独或各种组合的形式而发挥技术上的有用性,并不被限定于申请时权利要求所记载的组合。此外,本说明书或附图中所例示的技术为同时达到多个目的的技术,并且达到其中一个目的本身便具有技术上的有用性。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15