(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4455547号

(P4455547)

(45) 発行日 平成22年4月21日(2010.4.21)

(24) 登録日 平成22年2月12日(2010.2.12)

(51) Int.Cl.

F 1

|                     |                  |              |         |

|---------------------|------------------|--------------|---------|

| <b>G 11 C 29/12</b> | <b>(2006.01)</b> | G 11 C 29/00 | 6 7 1 B |

| <b>G 01 R 31/28</b> | <b>(2006.01)</b> | G 01 R 31/28 | B       |

| <b>G 11 C 29/34</b> | <b>(2006.01)</b> | G 01 R 31/28 | V       |

| <b>G 11 C 29/44</b> | <b>(2006.01)</b> | G 11 C 29/00 | 6 7 1 P |

|                     |                  | G 11 C 29/00 | 6 5 5 Z |

請求項の数 5 (全 27 頁)

(21) 出願番号

特願2006-188391 (P2006-188391)

(22) 出願日

平成18年7月7日(2006.7.7)

(65) 公開番号

特開2008-16156 (P2008-16156A)

(43) 公開日

平成20年1月24日(2008.1.24)

審査請求日

平成21年2月10日(2009.2.10)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100075812

弁理士 吉武 賢次

(74) 代理人 100088889

弁理士 橋谷 英俊

(74) 代理人 100082991

弁理士 佐藤 泰和

(74) 代理人 100096921

弁理士 吉元 弘

(74) 代理人 100103263

弁理士 川崎 康

最終頁に続く

(54) 【発明の名称】半導体集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリに与える書き込みデータを生成して出力するデータ生成器と、

前記メモリに与えるアドレス信号を生成して出力するアドレス生成器と、

前記メモリを制御する制御信号を生成して出力する制御信号生成器と、

フラグ信号を与えられて組み込み自己テスト(以下、B I S Tという)の結果を解析し

、B I S T結果信号を出力する結果解析器と、

前記データ生成器、前記アドレス生成器、前記制御信号生成器、前記結果解析器の動作

をそれぞれ制御し、またB I S Tの状態を示すB I S T状態信号を出力するB I S T制御

回路と、

前記フラグ信号が与えられない間は、第1のクロックに従って、前記B I S T制御回路

から出力された最新の前記アドレス信号と前記B I S T状態信号とを取り込んで出力し、

前記フラグ信号が与えられるとその時点における出力を維持する第1の取り込みレジスタ

と、前記第1のクロックより低速な第2のクロックに従い、シフトイネーブル信号が与え

られない間は、前記取り込みレジスタからの出力を与えられて保存することで、前記フラ

グ信号が与えられた時点における前記アドレス信号と前記B I S T状態信号とを保存し、

前記シフトイネーブル信号が与えられると、保存内容を外部にシフト出力する保存レジス

タと、前記第1の取り込みレジスタからの出力と前記保存レジスタの保存内容とを比較す

ることで、前記フラグ信号が一旦与えられた後、前記第1の取り込みレジスタから出力さ

れた前記最新の前記アドレス信号と前記B I S T状態信号とが前記保存レジスタに保存さ

10

20

れた前記アドレス信号と前記B I S T制御信号とに一致するまでの間、フラグ抑制信号を出力するフラグ抑制手段とを含む診断データ保存回路と、

を有するB I S T回路と、

前記第1のクロックに従い、前記書き込みデータ、前記アドレス信号、前記制御信号を与えられて書き込み動作を行い、書き込んだデータを読み出して出力するメモリセルと、

シフトイネーブル信号が与えられずかつ前記フラグ信号が与えられない間は、前記メモリセルから出力された最新のデータを与えられて取り込み、前記フラグ信号が与えられるときの時点における保持内容を維持し、前記シフトイネーブル信号が与えられるとその時点での保持内容を外部にシフト出力する第2の取り込みレジスタと、

前記第2の取り込みレジスタからの出力と期待値とを比較し、不一致の場合にフェイル検出を意味する比較結果信号を出力する比較回路と、10

前記フラグ抑制信号が与えられない間は、前記比較結果信号に基づいて前記フラグ信号を出力し、前記フラグ抑制信号が与えられると前記フラグ信号の出力が抑制されるフラグレジスタと、

を有するメモリカラーと、

を備えることを特徴とする半導体集積回路。

#### 【請求項2】

前記B I S T制御回路は、

前記フラグ信号が前記フラグレジスタから出力されるとB I S Tを中断し、この中断時点より遡る再開時点からB I S Tを再開することを特徴とする請求項1記載の半導体集積回路。20

#### 【請求項3】

前記B I S T制御回路は、

前記中断時点から前記再開時点までの前記メモリに書き込まれたデータが、B I S Tが前記再開時点から前記中断時点まで実行されたことによってB I S Tの実行前と異なるデータに書き換えられている場合は、B I S Tの実行前と同じデータに書き戻した後、前記再開時点からB I S Tを再開することを特徴とする請求項1又は2記載の半導体集積回路。。

#### 【請求項4】

前記メモリセルが複数設けられている場合、前記メモリカラーが各メモリセル毎に対応して複数設けられており、30

前記メモリカラーにおける前記第2の取り込みレジスタが相互にシリアルに接続されており、シフトイネーブル信号が与えられると、前記第2の取り込みレジスタにそれぞれ保持された内容が外部にシリアルにシフト出力されることを特徴とする請求項1乃至3のいずれか一に記載の半導体集積回路。

#### 【請求項5】

動作設定データが与えられ、当該B I S T回路がB I S T対象であるか否か、前記メモリがB I S T対象であるか否かを少なくとも設定するB I S T動作設定レジスタと、

メモリに与える書き込みデータを生成して出力するデータ生成器と、

前記メモリに与えるアドレス信号を生成して出力するアドレス生成器と、40

前記メモリを制御する制御信号を生成して出力する制御信号生成器と、

フラグ信号を与えられてB I S Tの結果を解析し、B I S T結果信号を出力する結果解析器と、

前記データ生成器、前記アドレス生成器、前記制御信号生成器、前記結果解析器の動作をそれぞれ制御し、またB I S Tの状態を示すB I S T状態信号を出力するB I S T制御回路と、

前記フラグ信号が与えられない間は、第1のクロックに従って、前記B I S T制御回路から出力された最新の前記アドレス信号と前記B I S T状態信号とを取り込んで出力し、前記フラグ信号が与えられるとその時点における出力を維持する第1の取り込みレジスタと、前記第1のクロックより低速な第2のクロックに従い、シフトイネーブル信号が与え50

られない間は、前記取り込みレジスタからの出力を与えられて保存することで、前記フラグ信号が与えられた時点における前記アドレス信号と前記B I S T状態信号とを保存し、前記シフトイネーブル信号が与えられると、保存内容を外部にシフト出力する保存レジスタと、前記第1の取り込みレジスタからの出力と前記保存レジスタの保存内容とを比較することで、前記フラグ信号が一旦与えられた後、前記第1の取り込みレジスタから出力された前記最新の前記アドレス信号と前記B I S T状態信号とが前記保存レジスタに保存された前記アドレス信号と前記B I S T制御信号とに一致するまでの間、フラグ抑制信号を出力するフラグ抑制手段とを含む診断データ保存回路と、

前記B I S T動作設定レジスタに設定された内容に従って、前記保存レジスタの保存内容、あるいは入力信号のいずれかを切り替えて出力する第1のマルチプレクサと、10

を有し、それぞれの前記第1のマルチプレクサが相互にシリアルに接続された複数のB I S T回路と、

前記第1のクロックに従い、前記書き込みデータ、前記アドレス信号、前記制御信号を与えられて書き込み動作を行い、書き込んだデータを読み出して出力するメモリセルと、

シフトイネーブル信号が与えられずかつ前記フラグ信号が与えられない間は、前記メモリセルから出力された最新のデータを与えられて取り込み、前記フラグ信号が与えられるときの時点における保持内容を維持し、前記シフトイネーブル信号が与えられるとその時点での保持内容を外部にシフト出力する第2の取り込みレジスタと、

前記第2の取り込みレジスタからの出力と期待値とを比較し、不一致の場合にフェイル検出を意味する比較結果信号を出力する比較回路と、20

前記フラグ抑制信号が与えられない間は、前記比較結果信号に基づいて前記フラグ信号を出力し、前記フラグ抑制信号が与えられると前記フラグ信号の出力が抑制されるフラグレジスタと、

前記B I S T動作設定レジスタに設定された内容に従って、前記第2の取り込みレジスタの保持内容、あるいは前記フラグレジスタからの出力のいずれかを切り替えて出力する第2のマルチプレクサと、

を有し、それぞれの前記第2のマルチプレクサが相互にシリアルに接続された複数のメモリカラーと、

を備えることを特徴とする半導体集積回路。

#### 【発明の詳細な説明】

30

#### 【技術分野】

#### 【0001】

本発明は半導体集積回路に係わり、特にメモリの組み込み自己テスト回路が組み込まれ、この回路を用いて故障診断動作を行う半導体集積回路に好適なものに関する。

#### 【背景技術】

#### 【0002】

メモリを含む半導体集積回路において、組み込み自己テスト(Built-In Self Test、以下、B I S Tという)回路を組み込み、B I S T回路を用いてB I S Tを行って不良のチップを検出し、次にB I S T回路を用いて該不良チップに故障診断を行ってメモリの不良箇所の候補を抽出する手法が用いられている。40

#### 【0003】

B I S T回路には、書き込みデータと同一の期待値と、メモリから読み出したデータとの比較を行い、故障の有無を判別する比較器型B I S T回路や、メモリから読み出されたデータをB I S T回路内で圧縮し、圧縮した結果を用いて故障の有無を判別する圧縮器型B I S T回路等がある。

#### 【0004】

先ず、比較器型B I S T回路を有する従来の半導体集積回路におけるB I S T動作について述べる。

#### 【0005】

B I S T回路内のB I S T制御回路が、データ生成器、アドレス生成器、制御信号生成50

器を制御する。BIST対象となるメモリは、メモリカラーと呼ばれるブロック内にBIST動作に必要な各論理要素とともに含まれている。

#### 【0006】

データ生成器から生成された書き込みデータ、アドレス生成器から生成されたアドレスデータ、制御信号生成器から生成された制御信号がそれぞれ、メモリに与えられる。

#### 【0007】

メモリから出力されたデータは、メモリの出力側に配置された取り込みレジスタに一旦保持される。取り込みレジスタからの出力が、データ生成器から生成されたデータ期待値と比較器によって比較され、比較結果がフラグレジスタに保持される。フラグレジスタからの出力がBIST回路内の結果解析器に入力され、最終的なBIST結果が出力される。

10

#### 【0008】

一つのBIST回路で複数のメモリにBISTを行っている場合は、それぞれのフラグデータが結果解析器に入力され、全体的なBISTによる良否判定が行われた後、最終的なBIST結果が出力される。

#### 【0009】

次に、圧縮器型メモリBIST回路を有する従来の半導体集積回路におけるBIST動作について述べる。

#### 【0010】

比較器型メモリBIST回路を有する半導体集積回路の場合と同様に、BIST回路内のBIST制御回路が、データ生成器、アドレス生成器、制御信号生成器の動作を制御する。BIST対象となるメモリはメモリカラーに含まれる。

20

#### 【0011】

データ生成器から生成された書き込みデータ、アドレス生成器から生成されたアドレスデータ、制御信号生成器から生成された制御信号がメモリに与えられ、メモリからの出力が圧縮器に入力されて順次圧縮されてゆく。

#### 【0012】

ここで圧縮機の構造としては、後述する非特許文献1に記載されたものがある。一般には、リニアフィードバックシフトレジスタの変形であるMISR (Multiple Input Signature Register) が用いられている。

30

#### 【0013】

BIST終了時に、圧縮器に保存されている値がBIST結果として予め計算された期待値と比較され、メモリの良否が判定される。

#### 【0014】

また、メモリにおける故障箇所の候補を抽出するためBIST回路を用いて故障診断を行う際には、複数のメモリからの出力データを順次シリアルに外部に取り出して外部テスト装置により観測する。

#### 【0015】

上述の比較器型BIST回路を用いる場合には、各メモリカラー内にあるメモリの出力を取り込む取り込みレジスタと、各メモリカラー内の比較器からの出力とをそれぞれ受けけるフラグレジスタとを全てシリアルに接続する。そしてこれらと、それぞれのBIST回路内にあるアドレス生成回路からのアドレスを与えられるアドレスレジスタと、全体のフラグレジスタとを全てシリアルに接続し、全体で一本の循環的なシフトパスを形成する。

40

#### 【0016】

故障診断時にこのシフトパスを使用し、読み出しのタイミングに従ってそれぞれのレジスタの値をシフト出力する。シフトパスが循環的に形成されているため、シフト出力終了後にBIST動作中断時の状態に復帰することができる。

#### 【0017】

そして、BISTを再開し、再び次の読み出しタイミングでレジスタの値をシフト出力する。このようなBIST動作の中止、シフト出力、BIST動作の再開を繰り返すことに

50

より、メモリ内部の状態を読み出すことが可能となる。得られた結果に基づいて、メモリのセルアレイ内の故障ビット位置を示すフェイルビットマップを作成し、故障解析を行う。

#### 【0018】

しかし、このような従来の手法では全てのBIST結果をシリアルに読み出していく必要があるため、故障診断対象でないメモリからの出力もシフト出力しなくてはならない。よって、一つのBIST回路でBISTを行うメモリの数が多い場合には、BIST時間が非常に長くなる。

#### 【0019】

さらにBIST結果をシフト出力した際に、シフト出力の観測と期待値との比較を外部テスト装置を用いて行わなければならない。このため、半導体集積回路の実動作での動作速度より遅い外部テスト装置の動作速度により制約を受けることになる。従って、半導体集積回路の実速度で故障診断を行うことが困難であり、実速度で故障診断を行った場合に限り検出可能な故障候補を検出することができなかった。

10

#### 【0020】

以下に、リニアフィードバックシフトレジスタの変形であるMISRを開示した文献名を記載する。

【非特許文献1】Built-In Test for VLSI: Pseudo Random Techniques, Paul H. Bardell, William H. McAnney and Jacob Savir, John Wiley & Sons, 1987

#### 【発明の開示】

20

#### 【発明が解決しようとする課題】

#### 【0021】

本発明は、故障診断対象であるメモリのみから読み出したデータを取り出することで故障診断時間を短縮し、かつ実速度で故障診断が可能な半導体集積回路を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0022】

本発明の一態様による半導体集積回路は、メモリに与える書き込みデータを生成して出力するデータ生成器と、前記メモリに与えるアドレス信号を生成して出力するアドレス生成器と、前記メモリを制御する制御信号を生成して出力する制御信号生成器と、フラグ信号を与えられてBISTの結果を解析し、BIST結果信号を出力する結果解析器と、前記データ生成器、前記アドレス生成器、前記制御信号生成器、前記結果解析器の動作をそれぞれ制御し、またBISTの状態を示すBIST状態信号を出力するBIST制御回路と、前記フラグ信号が与えられない間は、第1のクロックに従って、前記BIST制御回路から出力された最新の前記アドレス信号と前記BIST状態信号とを取り込んで出力し、前記フラグ信号が与えられるとその時点における出力を維持する第1の取り込みレジスタと、前記第1のクロックより低速な第2のクロックに従い、シフトイネーブル信号が与えられない間は、前記取り込みレジスタからの出力を与えられて保存することで、前記フラグ信号が与えられた時点における前記アドレス信号と前記BIST状態信号とを保存し、前記シフトイネーブル信号が与えられると、保存内容を外部にシフト出力する保存レジスタと、前記第1の取り込みレジスタからの出力と前記保存レジスタの保存内容とを比較することで、前記フラグ信号が一旦与えられた後、前記第1の取り込みレジスタから出力された前記最新の前記アドレス信号と前記BIST状態信号とが前記保存レジスタに保存された前記アドレス信号と前記BIST制御信号とに一致するまでの間、フラグ抑制信号を出力するフラグ抑制手段とを含む診断データ保存回路とを有するBIST回路と、前記第1のクロックに従い、前記書き込みデータ、前記アドレス信号、前記制御信号を与えられて書き込み動作を行い、書き込んだデータを読み出して出力するメモリセルと、シフトイネーブル信号が与えられずかつ前記フラグ信号が与えられない間は、前記メモリセルから出力された最新のデータを与えられて取り込み、前記フラグ信号が与えられるとその時点における保持内容を維持し、前記シフトイネーブル信号が与えられるとその時点での保

30

40

50

持内容を外部にシフト出力する第2の取り込みレジスタと、前記第2の取り込みレジスタからの出力と期待値とを比較し、不一致の場合にフェイル検出を意味する比較結果信号を出力する比較回路と、前記フラグ抑制信号が与えられない間は、前記比較結果信号に基づいて前記フラグ信号を出力し、前記フラグ抑制信号が与えられると前記フラグ信号の出力が抑制されるフラグレジスタとを有するメモリカラーとを備えることを特徴とする。

#### 【0023】

また本発明の一態様による半導体集積回路は、動作設定データが与えられ、当該BIST回路がBIST対象であるか否か、前記メモリがBIST対象であるか否かを少なくとも設定するBIST動作設定レジスタと、メモリに与える書き込みデータを生成して出力するデータ生成器と、前記メモリに与えるアドレス信号を生成して出力するアドレス生成器と、前記メモリを制御する制御信号を生成して出力する制御信号生成器と、フラグ信号を与えられてBISTの結果を解析し、BIST結果信号を出力する結果解析器と、前記データ生成器、前記アドレス生成器、前記制御信号生成器、前記結果解析器の動作をそれぞれ制御し、またBISTの状態を示すBIST状態信号を出力するBIST制御回路と、前記フラグ信号が与えられない間は、第1のクロックに従って、前記BIST制御回路から出力された最新の前記アドレス信号と前記BIST状態信号とを取り込んで出力し、前記フラグ信号が与えられるとその時点における出力を維持する第1の取り込みレジスタと、前記第1のクロックより低速な第2のクロックに従い、シフトイネーブル信号が与えられない間は、前記取り込みレジスタからの出力を与えられて保存することで、前記フラグ信号が与えられた時点における前記アドレス信号と前記BIST状態信号とを保存し、前記シフトイネーブル信号が与えられると、保存内容を外部にシフト出力する保存レジスタと、前記第1の取り込みレジスタからの出力と前記保存レジスタの保存内容とを比較することで、前記フラグ信号が一旦与えられた後、前記第1の取り込みレジスタから出力された前記最新の前記アドレス信号と前記BIST状態信号とが前記保存レジスタに保存された前記アドレス信号と前記BIST制御信号とに一致するまでの間、フラグ抑制信号を出力するフラグ抑制手段とを含む診断データ保存回路と、前記BIST動作設定レジスタに設定された内容に従って、前記保存レジスタの保存内容、あるいは入力信号のいずれかを切り替えて出力する第1のマルチプレクサと、を有し、それぞれの前記第1のマルチプレクサが相互にシリアルに接続された複数のBIST回路と、前記第1のクロックに従い、前記書き込みデータ、前記アドレス信号、前記制御信号を与えられて書き込み動作を行い、書き込んだデータを読み出して出力するメモリセルと、シフトイネーブル信号が与えられずかつ前記フラグ信号が与えられない間は、前記メモリセルから出力された最新のデータを与えられて取り込み、前記フラグ信号が与えられるとその時点における保持内容を維持し、前記シフトイネーブル信号が与えられるとその時点での保持内容を外部にシフト出力する第2の取り込みレジスタと、前記第2の取り込みレジスタからの出力と期待値とを比較し、不一致の場合にフェイル検出を意味する比較結果信号を出力する比較回路と、前記フラグ抑制信号が与えられない間は、前記比較結果信号に基づいて前記フラグ信号を出力し、前記フラグ抑制信号が与えられると前記フラグ信号の出力が抑制されるフラグレジスタと、前記BIST動作設定レジスタに設定された内容に従って、前記第2の取り込みレジスタの保持内容、あるいは前記フラグレジスタからの出力のいずれかを切り替えて出力する第2のマルチプレクサとを有し、それぞれの前記第2のマルチプレクサが相互にシリアルに接続された複数のメモリカラーとを備えることを特徴とする。

#### 【発明の効果】

#### 【0024】

本発明の半導体集積回路によれば、故障診断時間の短縮、及び実速度での故障診断が可能である。

#### 【発明を実施するための最良の形態】

#### 【0025】

以下、本発明の実施の形態について図面を参照して説明する。

#### 【0026】

10

20

30

40

50

(1) 実施の形態 1

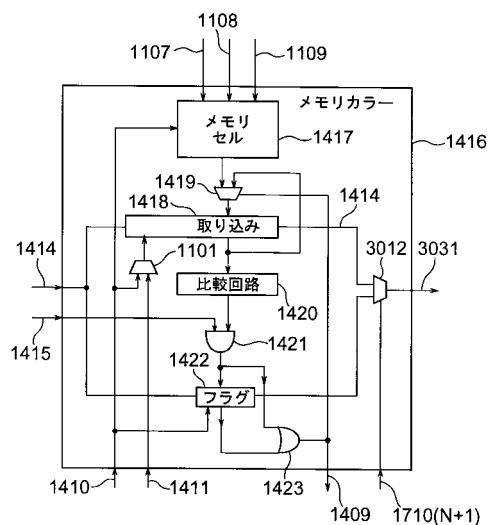

図1に、本発明の実施の形態1による半導体集積回路の構成を示す。

【0027】

この半導体集積回路は、BIST回路400及びメモリカラー416を備え、BIST回路400がBIST制御回路401、データ生成器402、アドレス生成器403、制御信号生成器404、結果解析器405、診断データ保存回路406を有する。ここで本実施の形態1は、BIST回路400が診断データ保存回路406を備える点に特徴がある。

【0028】

一方、BIST対象となるメモリセル417はメモリカラー416と呼ばれるブロックに、BIST動作に必要な要素であるマルチプレクサ419、取り込みレジスタ418、マルチプレクサ101、比較回路420、AND回路421、フラグレジスタ422、OR回路423とともに含まれる。 10

【0029】

BIST回路400において、BIST制御回路401、データ生成器402、アドレス生成器403、制御信号生成器404、結果解析器405、診断データ保存回路406に高速クロック410が入力される。

【0030】

BIST制御回路401が、データ生成器402、アドレス生成器403、制御信号生成器404、結果解析器405、診断データ保存回路406の動作を制御するため必要な制御信号を順次生成させ、それぞれに与える。 20

【0031】

データ生成器402から生成された書き込みデータ109、アドレス生成器403から生成されたアドレスデータ108、制御信号生成器404から生成されたメモリ制御信号107が、それぞれメモリセル417に与えられる。

【0032】

メモリカラー416において、高速クロック410が、メモリセル417、マルチプレクサ101、フラグレジスタ422に与えられる。マルチプレクサ101には、低速クロック411も与えられる。

【0033】

書き込みデータ109、アドレスデータ108、メモリ制御信号107がメモリセル417に与えられて、データが書き込まれる。メモリセル417から読み出されたデータは、マルチプレクサ419を介して一旦取り込みレジスタ418に入力される。 30

【0034】

ここでマルチプレクサ419には、メモリセル417からの出力とともに取り込みレジスタ418からの出力も与えられ、OR回路423から出力された、フェイルの検出を意味するフラグ信号409によって出力の切替が行われる。フェイルが検出されるまでの間はフラグ信号409は論理「0」であり、マルチプレクサ419からはメモリセル417からの出力がそのまま出力される。一旦フェイルが検出されて論理「1」のフラグ信号409がマルチプレクサ419に与えられると、取り込みレジスタ418からの出力が選択されて出力される。これにより、取り込みレジスタ418は同じ出力を維持することになる。 40

【0035】

取り込みレジスタ418は、通常はマルチプレクサ101から高速クロック410を与えられ、さらに外部からシフトイネーブル信号413が与えられ、マルチプレクサ419から出力されたデータを与えられて高速クロック410に従って比較回路420に出力する。しかし、BIST終了後に診断データ保存回路406からシフトイネーブル信号413が与えられると、マルチプレクサ101から低速クロック410に従って格納していたデータをシリアル出力信号414としてシリアルに外部へ出力する。

【0036】

ここで、メモリカラー416が複数設けられ、1つのBIST回路400によりBIST動作が制御される場合は、各取り込みレジスタ418がシリアルに接続され、それぞれの出力がシリアルに外部へ出力される。

#### 【0037】

取り込みレジスタ418から出力されたデータが、データ生成器402から生成された書き込みデータ109と同一のデータ期待値と、比較器420において比較される。一致している間は論理「0」、不一致、即ちフェイルが検出されると論理「1」の比較結果信号がAND回路421を介してフラグレジスタ422に与えられて保持される。

#### 【0038】

ここで、後述するようにBIST開始時にはフェイルが検出されていないので、診断データ保存回路406からは論理「1」のフェイル抑制信号415がAND回路421に与えられており、AND回路421からは比較回路420からの比較結果信号がそのまま出力される。

#### 【0039】

しかし、一旦フェイルが検出されBISTをより以前の時点から再開して、このフェイル箇所に到達するまでの間は、診断データ保存回路406から論理「0」のフラグ抑制信号415が出力されて、フェイル箇所に到達するまでの間、AND回路421に入力される。これにより、AND回路421からは、比較回路420からの比較結果信号は出力されずに論理「0」のデータを出力し続けることになる。

#### 【0040】

フラグレジスタ422への入力信号とフラグレジスタ422からの出力信号とがOR回路423に出力される。これにより、一旦フェイルが検出された後、詳細には、BIST開始時におけるフェイルが検出されていない段階で比較回路420からフェイルの検出を意味する比較結果信号が出力された場合、あるいは一旦フェイルが検出されBISTを再開した際に、AND回路421にフラグ抑制信号415が与えられてフェイルを意味する比較結果信号は出力されないが、それ以前のフェイル検出によりフラグレジスタ422に論理「1」のフラグが保持されている場合、OR回路423からはフラグ信号409が出力される。尚、BISTが再開されると、その時点でフラグレジスタ422は論理「0」に初期化される。

#### 【0041】

このフラグ信号409がマルチプレクサ419に入力されると、上述したように、マルチプレクサ419は取り込みレジスタ418からの出力を保持し続けることになる。

#### 【0042】

また、フラグレジスタ422からのフラグ信号409は、BIST回路400内の結果解析器405に入力される。

#### 【0043】

ひとつのBIST回路400を用いて複数のメモリセルをBISTする場合には、上述したようにメモリセル毎にメモリカラー416の構成を配置し、そしてそれぞれのメモリカラー416のフラグレジスタ422から出力されたフラグ信号409が結果解析器405に共通に入力される。

#### 【0044】

結果解析器405において、全体的なBISTの良否判定が行われた上で、最終的なBIST結果信号424として外部テスト装置に出力される。

#### 【0045】

さらに、OR回路423から出力されたフラグ信号409は、診断データ保存回路406にも入力される。一旦フェイルが検出されてフラグ信号409が発生すると、診断データ保存回路406にフェイル発生という情報が与えられることになる。

#### 【0046】

このようにして、BIST回路を用いたBIST動作が行われ、各メモリセル417に対する良否判定が行われる。

10

20

30

40

50

**【0047】**

次に、BIST回路を用いて故障診断が行われる。図2に、診断データ保存回路406の回路構成を詳細に示す。

**【0048】**

診断データ保存回路406は、アドレス信号407、BIST状態信号408にそれぞれ対応して、マルチプレクサ101A及び101B、取り込みレジスタ505及び506、保存レジスタ508及び509、比較回路514及び515、AND回路516、OR回路517及び519、フラグ抑制信号用レジスタ518を有する。

**【0049】**

アドレス生成器403が生成した現在のアドレス信号407と、BIST制御回路401が出力した現在のBIST状態信号408とが、マルチプレクサ101A、101Bを介して、高速クロック410に同期してそれぞれ取り込みレジスタ505、506に取り込まれる。BIST状態信号408は、BISTを実行している最中において、現在BISTシーケンス中のどの箇所に位置しているかを示す信号である。

**【0050】**

ここで、マルチプレクサ101A、101Bには、アドレス信号407、BIST状態信号408の他に、取り込みレジスタ505、506からの出力がそれぞれ与えられる。そして、フラグ信号409に応じていずれかの信号が選択されて、マルチプレクサ101A、101Bから出力される。

**【0051】**

フェイルが検出されず、フラグ信号409が論理「0」である場合は、マルチプレクサ101A、101Bからはアドレス信号407とBIST状態信号408とが出力され、それぞれ取り込みレジスタ505、506に保持される。

**【0052】**

一旦フェイルが検出されてフラグ信号409が論理「1」になると、マルチプレクサ101A、101Bは取り込みレジスタ505、506からの出力を選択して出力することにより、取り込みレジスタ505、506は現在の保持状態を維持することになる。これにより、新たなアドレス信号407、BIST状態信号408がマルチプレクサ101A、101Bに入力された場合であっても、取り込みレジスタ505、506の内容は更新されなくなる。

**【0053】**

取り込みレジスタ505および506からの出力は、同じビット幅の保存レジスタ508および509に、低速クロック411に同期して保存レジスタ508、509に取り込まれる。

**【0054】**

ここで、保存レジスタ508の出力端子が保存レジスタ509の入力端子にシリアルに接続されている。さらに、保存レジスタ508の入力端子は、BIST回路が複数段接続されている場合に、図示されていない前段の診断データ保存回路406における保存レジスタ509の出力端子か、BIST単位で最前段の場合はシフト入力端子にシリアルに接続されており、シフト入力信号512が入力される。同様に、当該保存レジスタ509の出力端子は、図示されていない後段の診断データ保存回路406における保存レジスタ508の入力端子にシリアルに接続されており、シフト出力信号513が出力される。このシフト出力信号513は、次のグループのBIST回路に接続され、グループ単位で最終段の場合は、装置外部に設けられた外部テスト装置によって観測され、故障診断による故障箇所の候補が抽出される。

**【0055】**

取り込みレジスタ505、506は、メモリセル417と同速度で動作するように高速クロック410に同期してデータを取り込んで保持して出力する。しかし、保存レジスタ508、509は低速クロック411に同期してデータを取り込んで保持し出力する。これは、保存レジスタ508、509からの出力は上述のようにシフトされて外部テスト装

10

20

30

40

50

置により観測されるが、速度が速すぎて観測不能とならないように、メモリセル417より低速な外部テスト装置の動作速度に適合させるためである。

#### 【0056】

また、取り込みレジスタ505、506は、フェイルが発生しフラグ信号409が出力されるまでは、新しいデータを与えられて保持内容を更新させていく。フラグ信号409が出力されてマルチプレクサ101A、101Bに与えられると、上述のように取り込みレジスタ505、506は自己の出力を保持することになる。一旦フェイルが検出され、フェイル箇所より遡った時点からBISTを再開し、このフェイル箇所まで到達するまでのフラグが抑制されている間は、保持内容を維持していくことになる。

#### 【0057】

保存レジスタ508および509は、シフトイネーブル信号413が論理「0」である場合に、取り込みレジスタ505、506からの出力を取り込んで保持し、低速クロック411に同期して比較器514、515に出力する。

#### 【0058】

シフトイネーブル信号413が論理「1」になるとシフトモードに移行し、シフト入力信号512を与えられた保存レジスタ508からの出力が取り込みレジスタ506からシフト出力信号513として出力され、シフトレジスタを構成する。これにより、不良が検出されたメモリセルからのデータ出力を、BIST中断後に外部テスト装置へ出力することができる。

#### 【0059】

BIST中にフェイルが検出されてBIST動作が一旦停止した後、BIST動作が再開されると、シフトイネーブル信号413は論理「0」となる。そこで、取り込みレジスタ505、506から出力されたデータが保存レジスタ508、509へ転送されて保持され、比較器514、515に出力される。

#### 【0060】

フェイルが検出されたこの時点では、フラグ信号409は論理「1」であるが、BIST再開後は論理「0」へ変化する。これにより、アドレス信号407、BIST状態信号503が再度マルチプレクサ101A、101Bを介して取り込みレジスタ505、506に取り込まれて保持される。

#### 【0061】

そして、取り込みレジスタ505、506の保持内容が、それぞれ保存レジスタ508、509の保持内容とともに比較回路514、515に与えられて比較される。

#### 【0062】

双方がともに一致し、比較回路514、515の出力がともに論理「1」になったとき、即ち一旦フェイルが検出された後、フェイル箇所より遡ってBISTを再開してからこのフェイル箇所に到達した時点で、AND回路516からの出力が論理「1」になる。OR回路517から論理「1」が出力されて、比較状態レジスタ（フラグ抑制信号用レジスタ）518からの出力値が初めて論理「1」になる。

#### 【0063】

保存レジスタ508、509は、フェイルが検出されるまでの間は、取り込みレジスタ505、506と同様に、新しいデータを与えられて保持内容を更新していく。しかし、一旦フェイルが検出されると、外部から入力されたシフトイネーブル信号413によりシフトモードに切り替わり、シフトレジスタとして動作しシフト出力信号513として出力されていく。これにより、保存レジスタ508、509の保持内容は破壊される。

#### 【0064】

この後、取り込みレジスタ505、506からの出力が1回保存レジスタ508、509に与えられて保持され、以降はこの内容を保持し続けて取り込みレジスタ505、506からの出力は取り込まない。即ち、フェイル検出時におけるアドレス信号407とBIST状態信号408とが保持される。

#### 【0065】

10

20

30

40

50

比較状態レジスタ 518 から出力された論理「1」は、OR回路 519 を介してフラグ抑制信号 415 として出力され、メモリカラー 416 内の AND 回路 421 へ与えられる。ここで、BIST 再開時には、比較状態レジスタ 518 は初期化されて論理「0」を保持し、抑制状態となる。

#### 【0066】

この OR 回路 517、比較状態レジスタ 518、OR 回路 519 により、一旦 AND 回路 516 から論理「1」のフラグ抑制信号 415 が出力されると、その後 OR 回路 519 からは論理「1」の出力状態が保持される。

#### 【0067】

一方、メモリカラー 416 内において、比較回路 420 の出力が論理「1」になると、10 フラグ抑制信号 415 の論理「1」の値とともに AND 回路 421 に与えられて、論理「1」が出力される。

#### 【0068】

これ以降、OR 素子 423 からのフラグ信号 409 が論理「1」を維持し、この値がマルチプレクサ 419 の出力切替に関する制御端子に入力される。これにより、取り込みレジスタ 418 の入力には、メモリセル 417 からの出力がマルチプレクサ 419 を介して与えられるのでなく、自己の出力がフィードバックして与えられる。これにより、取り込みレジスタ 419 は現在の値を保持する。

#### 【0069】

ただし、BIST 回路 400 における診断データ保存回路 406 からのフラグ抑制信号 415 が論理「0」の間は、AND 回路 421 の出力が論理「0」となり、フラグレジスタ 422 への入力が論理「0」を維持する。このため、メモリセル 417 の出力に不良があった場合にも、フラグレジスタ 422 への入力が論理「1」にはならないので、取り込みは抑制されず BIST 実行が継続される。20

#### 【0070】

これにより、フェイルが複数回検出され、その都度 BIST を中断し各フェイル箇所より今まで遡って BIST を再開した場合、最新のフェイル箇所に到達するまでは、既に検出されたより以前のフェイルに対して再度フラグ信号 409 を出力することなく、BIST を進めることができる。

#### 【0071】

取り込みレジスタ 418 は、BIST 実行中は高速な BIST クロックと同一の高速クロック 410 により動作する。このため、オンチップのクロック生成回路等で生成された高速クロックでの BIST の実行が可能である。30

#### 【0072】

BIST 動作が中断された際は、メモリカラー 416 におけるマルチプレクサ 101 により、BIST 回路 400 において直接制御可能な低速クロック 411 が選択出力されて取り込みレジスタ 418 に与えられて動作する。

#### 【0073】

この低速クロック 411 は、図 2 に示された診断データ保存回路 406 内の保存レジスタ 508、509 に与えられるクロックと同一であり、同じクロック源から供給される。40

#### 【0074】

シフトモードでは、上述したように、保存レジスタ 508、509 がシフトレジスタを構成する。この場合、保存レジスタ 509 から出力されたシフト出力信号 513 をシリアル出力信号 414 として取り込みレジスタ 418 に与える。これにより、フェイル検出時における BIST 制御回路 401 におけるアドレス信号 407、BIST 状態信号 408、メモリセル 417 からの出力を外部に取り出して、外部テスト装置に入力して観測することができる。

#### 【0075】

尚、一つの BIST 回路 400 で複数のメモリセル 417 を BIST する場合には、メモリセル 417 毎に対応して設けられたメモリカラー 416 内の取り込みレジスタ 418 50

を相互にシリアルに接続して、シフトレジスタを構成することとなる。

**【0076】**

図3に、本実施の形態1においてBISTを実行する際の手順を示す。ここでは、BIST回路400が、13Nという名称のマーチングパターンと称されるBISTを行うものとする。

**【0077】**

ここでマーチングパターンとは、例えば論理「0」状態のメモリから論理「0」を読み出し、論理「1」を書き込み、論理「1」を読み出すひとたまりの動作(マーチエレメントr0w1r1)を、全アドレスに対し順次実行するパターンであり、メモリの状態が論理「0」が論理「1」に置き換わる。

10

**【0078】**

これに対し、ウォーキングパターンとは、例えば論理「0」状態のメモリから論理「0」を読み出し、論理「1」を書き込み、論理「1」を読み出し、さらに論理「0」を書き込むマーチエレメント(r0w1r1w0)を用いるパターンであり、メモリの状態が論理「0」で維持される。

**【0079】**

先ず、時刻T0から(WRITE動作)としてBIST動作を開始し、メモリセル417の全アドレスに所定のデータパターン(全ビットに論理「0」のデータ、あるいはチェックカードパターン等のデータ)を書き込む。

20

**【0080】**

(READ-WR、ITE-READ動作)として、各アドレスにおいて、正データパターン(例えば、「1011」)の読み出しと逆パターン(例えば、「0100」)の書き込みとをアドレス昇順で行う。次に、各アドレスにおいて、逆データパターンの読み出しと正データパターンの書き込みとをアドレス昇順で行う。

**【0081】**

さらに、各アドレスにおいて、正データパターンの読み出しと逆パターンの書き込みとをアドレス降順で行い、続いて各アドレスにおいて逆データパターンの読み出しと正データパターンの書き込みとをアドレス降順で行う。

**【0082】**

時刻T2において最初のフェイルが検出されると、BIST動作を中断する。時刻T2におけるBIST制御回路401におけるBIST状態信号408、アドレス信号407、シリアル出力データ414(シフト出力データ513)を外部テスト装置へ出力する。そして、1回目のフェイルが検出されたアドレスデータと、BISTにおけるどの箇所に現在位置しているかを示すBIST状態信号とが保存レジスタ508、509に保存される。

30

**【0083】**

この後、BIST動作を再開する。しかし、中断地点の時刻T2からではなく、ある一定のステップを越った時刻T1から再開する。これは、中断地点(時刻T2)から再開すると、隣接動作間にシフト動作が入り、実速度でのBISTを行うことができなくなるためである。

40

**【0084】**

ここで、遡る時点(時刻T1)は、マーチング動作の切れ目であってもよいし、あるいは中断時点から一定アドレスだけ遡った時点でもよい。このいずれかを切り替えて選択するようにしたり、あるいは遡るアドレス数をBIST開始前に外部から設定してもよい。図3に示された例では、マーチング動作の切れ目である時刻T1まで遡っている。

**【0085】**

ここで留意すべき点は、実行しているBISTがマーチングである場合、遡った時点(時刻T1)のアドレスにおけるデータは正パターンと逆パターンとが入れ替わった異なるデータに既に書き換えられており、書き換えられる前の状態を前提とした読み出し動作が行われるマーチングテストでは、正しい動作にならないということである。

50

**【0086】**

そこで本実施の形態1では、アドレスを遡った時点（時刻T1）から、一回中断した時点（時刻T2）までのデータを書き戻すという動作を入れる。

**【0087】**

一方、データを前の状態にしたままでBISTを進行させるウォーキングテストの場合は、データが書き換えられることがないので書き戻しの動作は必要なく、遡った時点からすぐにBISTを再開することができる。

**【0088】**

本実施の形態1では、書き戻しは時刻T1からT2の間で行われ、再び時刻T1に戻った後、BIST動作が再開される。

10

**【0089】**

2回目のBIST実行では、時刻T1から時刻T2までの間、フラグ抑制信号415が出力されている。このため、時刻T2に到達し再度フェイルが検出されてもフラグが抑制されフラグ信号409が出力されず、フェイル検出と見なされない。

**【0090】**

2回目のBIST実行において、アドレスデータ407とBIST状態信号408とが取り込みレジスタ505、506に格納されていく。この情報と、保存レジスタ508、509に格納されている1回目のBISTにおいてフェイルが検出されたときのアドレスデータ407とBIST状態信号408とが比較されることで、1回目のフェイルが検出された時刻T2に到達したことが判明する。この時刻T2までは、フラグが抑制される。

20

**【0091】**

この後、BIST動作は次のフェイル箇所である時刻T4まで進む。時刻T4においてBIST動作が一旦中断し、アドレス信号407、BIST状態信号408とともに、データがシリアル出力信号414（シフト出力信号513）として出力される。この後、時刻T1の場合と同様に、データ書き戻しの時刻T3まで戻ってBIST動作が再開される。

**【0092】**

その後、新たな不良が検出されない場合は、BIST動作が時刻T5で終了する。外部テスト装置には、時刻T2およびT4におけるフェイル情報が保存される。

30

**【0093】**

図4に、BIST制御回路401の内部構成を示す。BIST制御回路401は、状態制御回路1201、データ生成器制御ブロック1202、アドレス生成器制御ブロック1203、制御信号生成器制御ブロック1204、結果解析器制御ブロック1205を備える。

**【0094】**

状態制御回路1201は、BIST状態の遷移、即ちBISTシーケンスを制御する。状態制御回路1201から、状態制御回路1201の現在の状態を示すBIST状態信号408が診断データ保存回路406に出力される。

**【0095】**

データ生成器制御ブロック1202は、データ生成器402の状態をモニタしながらその次の動作を制御する。

40

**【0096】**

アドレス生成器制御ブロック1203は、アドレス生成器403の状態をモニタしながらその次の動作を制御する。

**【0097】**

制御信号生成器制御ブロック1204は、制御信号生成器404の状態をモニタしながらその次の動作を制御する。

**【0098】**

結果解析器制御ブロック1205は、結果解析器405の状態をモニタしながらその次の動作を制御する。

50

**【0099】**

図5に、BIST制御回路401の動作手順を示す。以下に示す制御動作は、状態制御回路1201が行う。

**【0100】**

先ずステップS10として、状態制御回路1201がBISTの実行を開始する。

**【0101】**

ステップS12として、BIST終了か否かを判断する。終了する場合は直ちに終了する。終了しない場合はステップS14へ移行する。

**【0102】**

ステップS14において、アドレスを進めてBIST動作を行う。

10

**【0103】**

ステップS16として、不良検出の有無を判断する。不良を検出していない場合はステップS12へ戻り、検出した場合はステップS18へ移行する。

**【0104】**

ステップS18として、不良が発生した時点における状態を保存し、BIST動作を停止する。

**【0105】**

ステップS20として、不良状態を外部テスト装置に出力する。

**【0106】**

ステップS22において、行ったBISTがマーチングテストであるか否かを判断する。マーチングテストでない場合、即ちウォーキングテストである場合はステップS26へ、マーチングテストである場合はステップS24へ移行する。

20

**【0107】**

ステップS24において、BISTを再開する位置から現在の不良が検出された位置までデータを書き戻す。

**【0108】**

ステップS28として、終了か否かを判断する。終了する場合は直ちに終了する。終了しない場合は、ステップS30へ移行し、アドレスを進めてさらに動作を進める。

**【0109】**

ステップS32において、ステップS18で保存した不良発生時点における状態（アドレス）と現在の状態とを比較する。一致する場合はステップS12へ戻って同様な動作を繰り返し、不一致の場合はステップS28へ戻る。

30

**【0110】**

本実施の形態1によれば、先ずBIST回路を用いてBIST動作を行い、次にBIST回路を用いて故障診断動作を行う。フェイル検出時におけるメモリからの読み出しデータ、期待値との比較結果をレジスタに格納する。フェイルが検出されるとBIST動作を一旦中断し、故障診断の対象となっているメモリのみから出力されたデータを外部へシリアルに出力し、非対象のメモリからは出力しない。そして、中断時点より前に遡った再開時点からBIST動作を再開し、それまでに検出されたフェイル箇所では再度フェイル検出フラグを出力することなく通過し、中断時点以降へ故障診断を進めていく。

40

**【0111】**

このように、フェイル検出の度にテストを開始した時点まで遡ってBISTを再開するのではなく、必要なだけ遡ってBISTを再開することで、メモリセル内の全ての不良情報を効率良く取得することができる。

**【0112】**

また、本実施の形態1によれば、新たにフェイルが検出された時点においてのみメモリからのデータを出力するため、故障診断に要する時間が削減される。

**【0113】**

さらに、故障診断の対象となっていないメモリからの出力も含めて全て外部にシリアルに出力していた従来と異なり、本実施の形態1によれば故障診断の対象となっているメモ

50

りからの出力のみを取り出すことにより、故障診断に要する時間を短縮することができる。特にメモリの数が多い場合には、大幅に短縮することが可能となる。

#### 【0114】

また、メモリの通常動作で用いる高速クロックを用いてBISTを行い、BIST結果を外部へシフト出力する際には外部テスト装置が動作可能な低速クロックを用いることにより、実動作にてBISTを行うことが可能である。この結果、実速度テストでしか現れないフェイルの情報を取得することができる。

#### 【0115】

(参考例1)

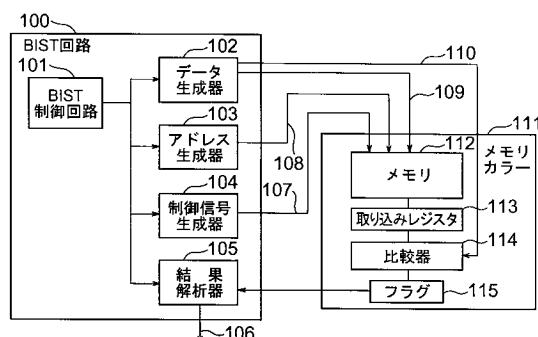

図6に、参考例1による比較器型メモリBIST回路を用いてBIST動作を行う半導体集積回路の構成を示す。 10

#### 【0116】

BIST回路100内のBIST制御回路101が、データ生成器102、アドレス生成器103、制御信号生成器104を制御するために必要な制御信号を順次生成させて出力する。

#### 【0117】

メモリカラー111と称されるブロック内に、BIST対象のメモリ112が、BIST動作に必要な各論理要素である取り込みレジスタ113、比較器114、フラグ115とともに含まれる。

#### 【0118】

データ生成器102から生成された書き込みデータ109及び期待値110、アドレス生成器103から生成されたアドレスデータ108、制御信号生成器104から生成された制御信号107がメモリ112に与えられる。 20

#### 【0119】

メモリ112からの出力は一度取り込みレジスタ113に入力され、その出力がデータ生成器102から生成されたデータ期待値110と比較器114により比較され、その結果がフラグレジスタ115に保持される。

#### 【0120】

フラグレジスタ115からの出力はBIST回路100の結果解析器105に入力され、最終的なBIST結果がBIST結果出力106として出力される。 30

#### 【0121】

単一のBIST回路100を用いて複数のメモリをBISTする場合には、メモリ毎に設けられたメモリカラー内のフラグレジスタからの出力がBIST回路100の結果解析器105に入力され、全体的な故障診断の良否判定が行われた後、BIST結果信号106として出力される。

#### 【0122】

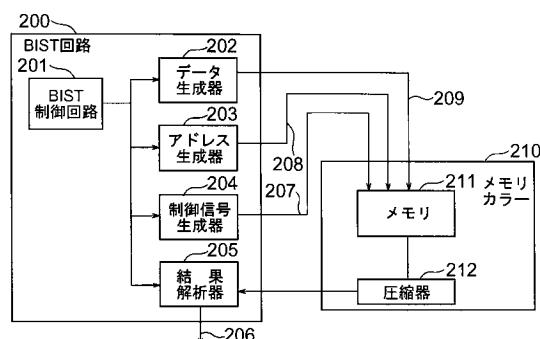

(参考例2)

図7に、参考例2による圧縮器型メモリBIST回路を用いてBISTを行う半導体集積回路の構成を示す。

#### 【0123】

BIST回路200内のBIST制御回路201が、データ生成器202、アドレス生成器203、制御信号生成器204、結果解析器205を制御するために必要な制御信号を順次生成して出力する。BIST対象となるメモリ211が、圧縮器212とともにメモリカラー210に含まれる。 40

#### 【0124】

データ生成器202から生成された書き込みデータ209、アドレス生成器203から生成されたアドレスデータ208、制御信号生成器204から生成された制御信号207が、それぞれメモリ211に与えられる。メモリ211からの出力が圧縮器212に入力され、順次圧縮されて出力される。

#### 【0125】

50

20

30

40

50

BIST終了時に圧縮器212に保存された値が、結果解析器205において期待値と比較され、BISTの良否が判定されて判定結果206として出力される。

#### 【0126】

単一のBIST回路100で複数のメモリをBISTする場合には、メモリ毎に対応して設けられたメモリカラーに含まれる複数の圧縮器をシリアルに接続し、単一のBIST回路200内の結果解析器106にデータを転送することでBISTを実行することができる。

#### 【0127】

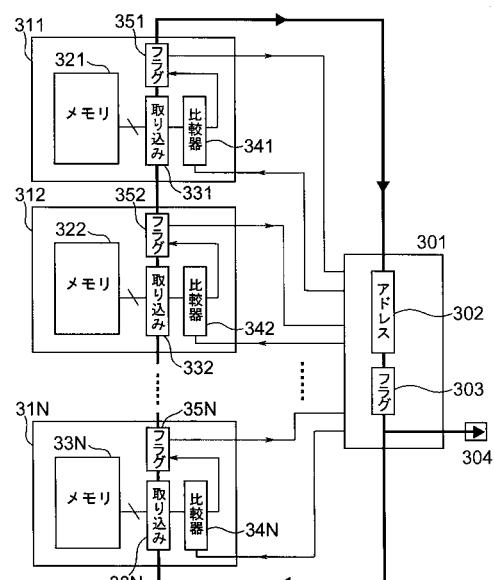

次に、参考例1によるBIST回路100を使用して、メモリ故障箇所のビット位置の特定を行う際には、BIST回路200による読み出しのタイミングでメモリ211の出力をシリアルに観測する場合について述べる。

#### 【0128】

図8に示されたように、複数のメモリカラー311、312、...、31N(Nは、2以上の整数)内にあるメモリ321、322、...、32Nの出力を取り込む取り込みレジスタ331、332、...、33Nと、比較器341、342、...、34Nからの出力を受けるフラグレジスタ351、352、...、35Nとをそれぞれシリアルに接続する。そして全体として、BIST回路内のBIST制御回路301に含まれるアドレス生成回路302内のアドレスレジスタ302とフラグレジスタ303とともに、一本の循環的なシフトパスを形成する。

#### 【0129】

このシフトパスを使用し、読み出しのタイミングで取り込みレジスタ331～33Nの値を、外部出力端子304を介して外部にシフト出力する。シフトパスが循環的に形成されているので、シフト出力終了後にBIST動作中断時の状態に復帰することができる。

#### 【0130】

そしてBISTを再開し、再び読み出しタイミングで取り込みレジスタ331～33Nの値をシフト出力する。BIST動作の中止、シフト出力、BIST動作の再開を繰り返すことにより、メモリ321～32Nの内部状態を読み出すことができる。

#### 【0131】

しかしこの場合には、故障診断対象でないメモリから出力された取り込みレジスタのデータもシフト出力しなくてはならない。このため、故障診断時間が非常に長くなる。さらに、シフト出力されたデータの観測と期待値との比較を、外部テスト装置を用いて行わなければならぬため、テスト装置の動作速度による制約を受ける。従って、メモリの実測度で故障診断を行うことができず、実測度でのみ観測されるフェイルを検出することができない場合がある。

#### 【0132】

これに対し、上述したように上記実施の形態1によれば、故障診断の対象となっているメモリからの出力のみを外部にシフト出力することで時間短縮が可能であり、また実動作速度での故障診断が可能である。

#### 【0133】

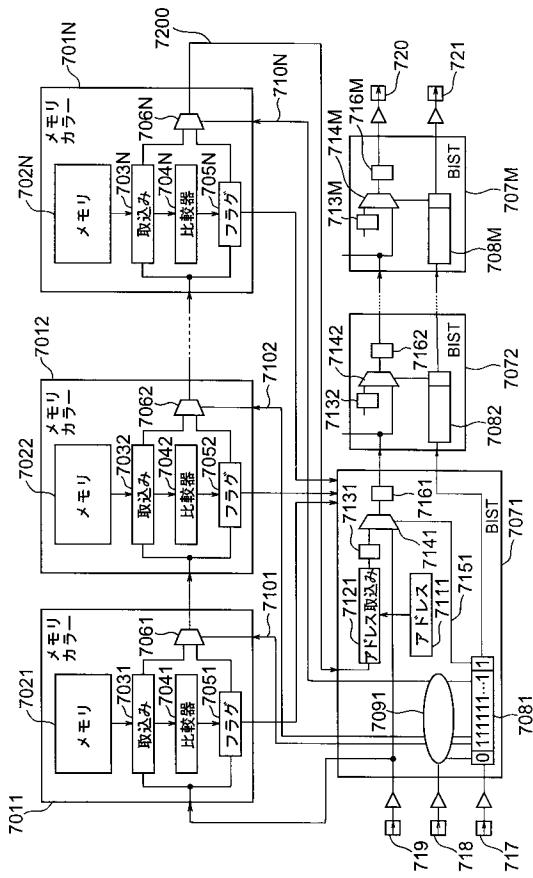

(参考例3)

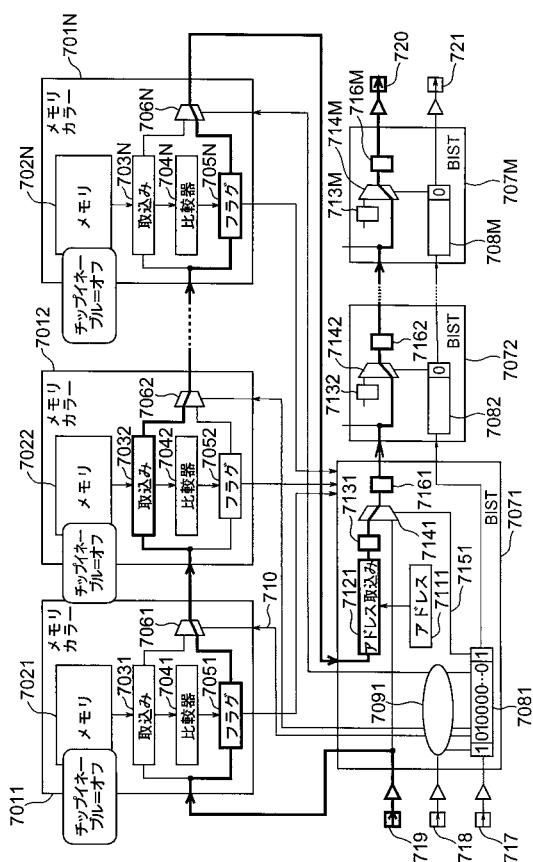

参考例3によるBIST回路を用いて故障診断を行う半導体集積回路について、その構成を示した図9を用いて説明する。

#### 【0134】

この半導体集積回路は、N個から成る1組のメモリカラー7011～701Nと、このメモリカラー7011～701NにBISTを実行する一つのBIST回路7071と、図示されていないA(Aは1以上の整数)個のメモリカラーと、このA個のメモリカラーにBISTを実行するBIST回路7072と、図示されていないB(Bは1以上の整数)個のメモリカラーと、このB個のメモリカラーにBISTを実行する図示されていないBIST回路7073と、...、図示されていないC(Cは1以上の整数)個のメモリカラーと、このC個のメモリカラーにBISTを実行するBIST回路707Mと、動作設定

10

20

30

40

50

ビット列シリアル信号が入力される入力端子 717、メモリ選択信号が入力される入力端子 718、シフトバスシリアルデータが入力される入力端子 719、シリアルデータが出力される出力端子 720、動作設定ビット列シリアルデータが出力される出力端子 721 を備えている。

#### 【0135】

各メモリカラー 7011～701N は同一の構成を備え、それぞれメモリ 7021～702N、取り込みレジスタ 7031～703N、比較器 7041～704N、フラグレジスタ 7051～705N を有している。

#### 【0136】

BIST 回路 7072～707M により BIST が実行される図示されていない M-1 10 組のメモリカラーも同様の構成を備えており、説明を省略する。

#### 【0137】

メモリカラー 7011において、メモリ 7021からの出力が取り込みレジスタ 7031 に取り込まれ、比較器 7041で期待値と比較され、その結果がフラグレジスタ 7051 に保持される。保持された内容が、マルチプレクサ 7061 及び BIST 回路 7071 に入力される。

#### 【0138】

上記実施の形態 1 と異なり、メモリカラー 7011 内の取り込みレジスタ 7031 とフラグレジスタ 7051 とはシリアルでなくパラレルに接続され、それぞれの出力が出力切り替え用のマルチプレクサ 7061 により切り替えられる。

20

#### 【0139】

BIST 回路 7071 は、アドレス取り込みレジスタ 7121、アドレスレジスタ 7111、終了フラグレジスタ 7131、BIST 設定デコーダ 7091、BIST 動作設定レジスタ 7081、マルチプレクサ 7141、判定フラグレジスタ 7161 を有する。他の BIST 回路 7072～707M も同様の構成を備えており、説明を省略する。

#### 【0140】

BIST 動作設定レジスタ 7081 には、外部から入力端子 717 を介して、動作設定ビット列シリアルデータが入力され、動作設定が行われる。複数の各 BIST 回路 7071～707M 内の各 BIST 動作設定レジスタ 7081～708M は、相互にシリアルに接続されている。これにより、動作設定に必要な外部端子数を最小限に抑えることができる。

30

#### 【0141】

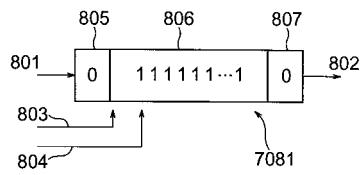

図 10 に、BIST 動作設定レジスタ 7081～708M の一例として、BIST 動作設定レジスタ 7081 の構成を示す。この BIST 動作設定レジスタ 7081 は、入力端子 801 から出力端子 802 へ順次データがシフト転送されていくシフトレジスタ構成を有している。入力端子 717 から入力された動作設定ビット列シリアルデータが入力端子 801 に入力される。BIST 動作設定レジスタ 7081 は、シフトイネーブル信号 803 を与えられてシフトイネーブル状態になり、シフトクロック 804 に同期して順次シフト動作を行う。

#### 【0142】

40

BIST 動作設定レジスタ 7081 は、動作モード設定ビット 805、メモリ選択ビット列 806 及び BIST 動作イネーブルビット 807 を有する。

#### 【0143】

動作モード設定ビット 805 は、BIST 動作と故障診断動作とを切り替えるものであり、このビットが論理「0」のとき当該メモリは BIST の対象となり、論理「1」のとき故障診断の対象となる。図 10 の動作モード設定ビット 805 は論理「0」であり、BIST の対象であることを示している。

#### 【0144】

メモリ選択ビット列 806 は、BIST 対象あるいは故障診断対象となるメモリの選択を設定するデータである。ここでは、各ビットがいずれか一つのメモリにそれぞれ対応し

50

ており、当該ビットが論理「1」であるメモリがBIST対象あるいは故障診断の対象となる。図10に示された例では、全ビット(ここではNビット)が論理「1」となっており、N個全てのメモリ $7021 \sim 702N$ がBIST対象であることを示す。

#### 【0145】

BIST動作イネーブルビット807は、各BIST回路 $7071 \sim 707M$ 毎に、当該BIST回路が現時点でBIST対象あるいは故障診断の対象であるか否かを設定するデータである。このビットが論理「0」のときは対象とならず、論理「1」のときに対象であることを示す。

#### 【0146】

例えば、BIST回路 $7071$ がBIST対象あるいは故障診断対象である場合は、このBIST回路 $7071$ によって動作が制御されるメモリカラー $7011 \sim 701N$ にBISTあるいは故障診断が行われる。10

#### 【0147】

論理「0」が設定されたBIST回路では、当該BIST回路内のマルチプレクサ $7141$ の切替設定により、当該BIST回路内をシフト転送するバスにアドレス取り込みレジスタ $7121$ 、終了フラグレジスタ $7131$ が含まれず、判定フラグレジスタ $7161$ のみが含まれる。これにより、判定フラグレジスタ $7161$ の1段のみによってシフトされるだけとなり、シフト回数を最小限にすることができる。

#### 【0148】

従って、BISTあるいは故障診断の対象外であるにもかかわらず、アドレス取り込みレジスタ $7121$ 、終了フラグレジスタ $7131$ 、判定フラグレジスタ $7161$ の全て、ならびにこれらのバスに接続されたメモリカラーのバスを含めて通過する場合と比較し、大幅にシフト段数が減少する。20

#### 【0149】

反対に、このBIST動作イネーブルビット807が論理「1」の場合は、BISTあるいは故障診断の対象となっている例えばBIST回路 $7071$ により制御されるメモリカラー $7011 \sim 701N$ 内のバスと、アドレス取り込みレジスタ $7121$ 、終了フラグレジスタ $7131$ 、判定フラグレジスタ $7161$ とがシフトバスに含まれる。メモリカラー $7011 \sim 701N$ 内のバスでは、メモリ選択ビット列806により、例えばBIST対象あるいは故障診断対象とされていないメモリカラー $7011$ ではフラグレジスタ $7051$ のみ、BIST対象あるいは故障診断対象とされているメモリカラー $7012$ ではメモリ $7022$ からの出力が取り込まれた取り込みレジスタ $7032$ 、...、BIST対象あるいは故障診断対象とされていないメモリカラー $701N$ ではフラグレジスタ $705N$ が、アドレス取り込みレジスタ $7121$ 、終了フラグレジスタ $7131$ 、判定フラグレジスタ $7161$ とともにシフトバスに含まれることになる。30

#### 【0150】

ここで、シフトバスにアドレス取り込みレジスタ $7121$ が含まれる場合は、アドレスレジスタ $7111$ から出力されたアドレスがアドレス取り込みレジスタ $7121$ に与えられるため、このアドレスがシフトバスによって外部へ転送される。

#### 【0151】

BIST回路 $7071$ において、BIST動作設定レジスタ $7081$ からパラレルに出力された動作モード設定ビット805、メモリ選択ビット列806、BIST動作イネーブルビット807が、BIST設定デコーダ $7091$ に与えられる。BIST設定デコーダ $7091$ は、メモリカラー $7011 \sim 701N$ 内のマルチプレクサ $7061 \sim 706N$ の出力の切替を制御するための切り替え制御信号 $7101 \sim 710N$ 、さらにはメモリ $7021 \sim 702N$ のチップイネーブルの制御を行うための図示されていないイネーブル信号等の出力を行う。40

#### 【0152】

図11を参照し、本参考例3において故障診断動作を行う際の信号の流れ及び動作設定について説明する。50

**【0153】**

故障診断は、通常は故障解析を容易にするため、一つの例えはBIST回路7071に接続された複数のメモリカラー7011～701Nにおけるいずれか一つのメモリカラーに含まれるメモリを対象に行うことを前提としている。そこで、BIST動作設定レジスタ7081～708Mにおけるメモリ選択ビット列806のなかで、故障診断対象となるメモリに対応する1ビットのみを論理「1」に設定する。

**【0154】**

ここでは、図11における左から2番目のメモリカラー7012に含まれるメモリ7022を対象とし、他のメモリカラーに含まれるメモリは対象外とする。そこで、BIST回路7071内のBIST動作設定レジスタ7081において、図10に示されたメモリ選択ビット列806におけるシリアルバスの入力端子801側から2ビット目のみが論理「1」となるようにビット列を設定する。10

**【0155】**

他のBIST回路7071、7073～707Mは、対応するメモリが全て故障診断対象から外れるように、BIST動作設定レジスタ7081、7083～708MにおけるBIST動作イネーブルビット807を論理「0」に設定する。

**【0156】**

これにより、故障診断実行時には、BIST回路7071内のBIST動作設定レジスタ7081のメモリ選択ビット列806において該当するビットが論理「1」であるメモリ7022のみに対して、チップイネーブル入力信号803が論理「1」（オン状態）になるとともに、マルチプレクサ7062が取り込みレジスタ7032からのシリアル出力を選択して出力する。20

**【0157】**

BIST回路7071に接続された他のメモリ7021、7023～702Nに対しては、チップイネーブル入力信号803が論理「0」（オフ状態）になるとともに、マルチプレクサ7061、7063～706Nはフラグレジスタ7051、7053～705Nの出力を選択する。

**【0158】**

これにより、図11において太線で示されたように、入力端子719、非選択のメモリカラー7011におけるフラグレジスタ7051及びマルチプレクサ7061、選択されたメモリカラー7012の取り込みレジスタ7032及びマルチプレクサ7062、非選択のメモリカラー7013～701Nのフラグレジスタ7053～705N及びマルチプレクサ7063～706N、さらに対象となっているBIST回路7071におけるアドレス取り込みレジスタ7121、終了フラグレジスタ7131、マルチプレクサ7141、判定フラグレジスタ7161、対象となっていないBIST回路7072～707Mにおけるそれぞれのマルチプレクサ7142及び判定フラグレジスタ7162、…、マルチプレクサ714M及び判定フラグレジスタ716M、出力端子720がシリアルに接続された状態になる。30

**【0159】**

ここで、シリアル入力信号が入力端子719からメモリカラーへの入力される接続経路についてであるが、図11に示された構成では、BIST回路に一旦入力された後、メモリカラーへ入力されている。しかしこの構成に限らず、BIST回路を経由することなく、入力端子719から直接メモリカラーに入力される接続構成を備えてよい。40

**【0160】**

これにより、BIST回路7071に接続されたメモリ7011～701Nのうち、故障診断対象となっているメモリ7022から出力され取り込みレジスタ7032に取り込まれたデータと、選択されていない各メモリカラー7012～701Nの判定フラグレジスタ7162、…、716Mと、故障診断対象となっているBIST回路7071におけるアドレスレジスタ7111に格納されアドレス取り込みレジスタ7121に取り込まれていたアドレスとが順次シフト出力されていく。50

**【0161】**

この結果、故障診断対象となっていないメモリからの不要な出力をシフト出力する必要がないので、故障診断実行中における不要な電力の消費が削減され故障診断に要する時間も短縮される。

**【0162】**

ここで、本参考例3では故障解析を容易に行うために单一のメモリ7022のみを故障診断の対象としている。しかし、故障解析は複雑化するが同時に複数のメモリを故障診断の対象とすることも可能である。例えば、メモリ7021と7022とが故障診断の対象である場合は、図11に太線で示されたシリアルバスに、メモリカラー7011においてフラグ7051の替わりに取り込みレジスタ7032が接続されることになる。

10

**【0163】**

故障診断動作中は、例えばメモリ7022の読み出し動作が行われるたびに取り込みレジスタ7032をシフト動作させ、メモリ7022からの出力を外部出力端子720から取り出して観測する。

**【0164】**

この際、同じBIST回路7071に接続されたメモリ7021～702Nのうち、故障診断対象となるメモリ7022以外は、上述したように1ビットのみシフトされることになる。従って、故障診断の対象以外のメモリ7021、7023～702Nからのデータをシフト出力する必要がないので、全てのメモリからのデータをシフト出力する場合と比較して故障診断に要する時間が短縮される。

20

**【0165】**

また、他のBIST回路7072～707Mでは、それぞれ判定フラグレジスタ7162～7-6Mのみがシリアルバスに接続される。このため、シフトに要するステップが短縮され、故障診断に要する外部テスト装置の実行時間が短縮される。

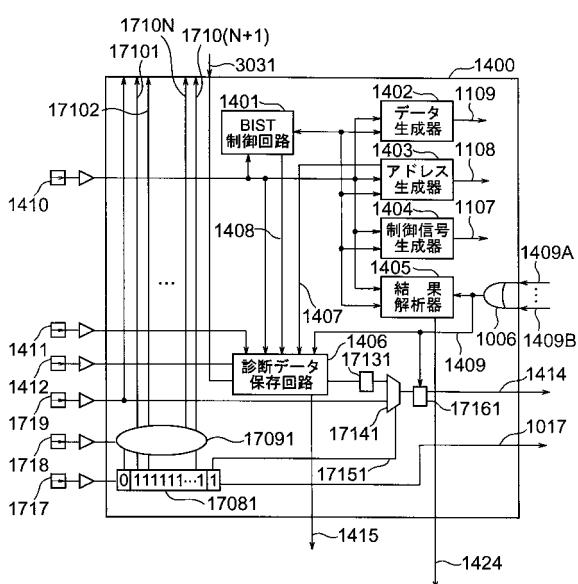

**【0166】****(2) 実施の形態2**

本発明の実施の形態2による半導体集積回路について、その構成を示した図面を用いて説明する。本実施の形態2は、図1に示された上記実施の形態1におけるBIST回路400及びメモリカラー416の構成に、図9に示された参考例3におけるBIST回路7071の構成を組み合わせたものに相当する。

30

**【0167】**

本実施の形態3におけるBIST回路1400は図12に示された構成を備え、メモリカラー1416は図13に示された構成を備えている。

**【0168】**

BIST回路1400は、上記実施の形態1におけるBIST回路400と同様に、BIST制御回路1401、データ生成器1402、アドレス生成器1403、制御信号生成器1404、結果解析器1405、診断データ保存回路1407を備え、さらに上記参考例3におけるBIST回路7071と同様に、BIST設定デコーダ17091、BIST動作設定レジスタ17081、終了フラグレジスタ17131、マルチブレクサ17141、判定フラグレジスタ17161を備えている。

40

**【0169】**

さらに、図1に示された上記実施の形態1におけるフラグ信号409に相当するフラグ信号1409A～1409Bを複数個のメモリカラー1416から与えられて入力し、結果解析器1405、診断データ保存回路1406に出力するOR回路1006を有している。

**【0170】**

診断データ保存回路1406の詳細な構成は、図2に示された上記実施の形態1における診断データ保存回路406と同様であり説明を省略する。

**【0171】**

メモリカラー1416は、上記実施の形態1におけるメモリカラー416と同様に、メ

50

モリセル 1417、マルチブレクサ 1419、取り込みレジスタ 1418、マルチブレクサ 1101、比較回路 1420、AND 回路 1421、フラグレジスタ 1422、OR 回路 1423 を備えている。さらに、デコーダ 17091 から出力された切替制御信号 1710 (N+1) を与えられて、取り込みレジスタ 1418 の出力とフラグレジスタ 1422 の出力のいずれか一方を切り替えて信号 3031 を出力するマルチブレクサ 3012 を有している。

#### 【0172】

ここで、メモリカラー 1416 が複数設けられている場合は相互にシリアルに接続され、前段に配置されたメモリカラー 1416 から出力された信号 3031 が後段に配置されたメモリカラー 1416 に信号 1414 として入力された状態で、取り込みレジスタ 1418 に格納されたデータがシリアルに外部に出力される。10

#### 【0173】

このような構成を備える本実施の形態 2 における動作について、以下に説明する。

#### 【0174】

BIST 制御回路 1401、データ生成器 1402、アドレス生成器 1403、制御信号生成器 1404、結果解析器 1405 に高速クロック 1410 が入力され、BIST 制御回路 1401 からデータ生成器 1402、アドレス生成器 1403、制御信号生成器 1404、結果解析器 1405 の動作を制御するために必要な各種信号が生成されてそれ出力される。20

#### 【0175】

データ生成器 1402、アドレス生成器 1403、制御信号生成器 1401 からそれぞれ出力されたデータ 1109、アドレス 1108、制御信号 1107 は、メモリカラー 1416 におけるメモリセル 1417 に与えられる。

#### 【0176】

本実施の形態 3 におけるメモリカラー 1416 では、診断データ保存回路 1406 からのシリアル出力 1414 が、取り込みレジスタ 1418 のみならずフラグレジスタ 1422 にも与えられて保持される。そして、取り込みレジスタ 1418 からの出力 1414 のみならず、フラグレジスタ 1422 からの出力がマルチブレクサ 3012 に与えられ、マルチブレクサ 3012 は診断データ保存回路 406 から出力された制御信号 1710 (N+1) に基づいていずれか一方を選択して出力する。ここで、マルチブレクサ 3012 において、取り込みレジスタ 1418 からの出力 1414 とフラグレジスタ 1422 からの出力のうち、いずれか一方が選択されている間は、他方がシフトされないようにしてもよい。他の動作は上記実施の形態 1 によるメモリカラー 416 におけるものと同様であり、説明を省略する。30

#### 【0177】

フラグレジスタ 1422 から OR 回路 1423 を介して出力されたフラグ信号 1409 は、図 12 における BIST 回路 1400 内の結果解析器 1405 に入力される。ひとつの BIST 回路 1400 を用いて複数のメモリセルを BIST する場合には、メモリセル毎にメモリカラー 1416 の構成を配置し、それぞれのメモリカラー 1416 のフラグレジスタ 1422 から出力されたフラグ信号 1409A ~ 1409B が OR 回路 1006 を介して結果解析器 1405 に入力される。40

#### 【0178】

結果解析器 1405 において、全体的な BIST の良否判定が行われた上で、最終的な BIST 結果信号 1424 として外部テスト装置に出力される。

#### 【0179】

さらに、フラグレジスタ 1422 から OR 回路 1423 を介して出力されたフラグ信号 1409 は、診断データ保存回路 1406 にも入力される。また、診断データ保存回路 1406 には、図 13 に示されたメモリカラー 1416 からの出力 3031 が入力される。一旦フェイルが検出されてフラグ信号 1409 が発生すると、診断データ保存回路 1406 にフェイル発生という情報が与えられる。50

**【0180】**

このようにして、BIST回路を用いたBIST動作が行われ、各メモリセル1417に対する良否判定が行われる。

**【0181】**

次に、診断データ保存回路1406を用いた故障診断が行われるが、その回路構成並びに動作は図2に示された上記実施の形態1による診断データ保存回路406と同様であり、説明を省略する。

**【0182】**

BIST回路1400が複数配置されている場合は、前段に配置されたBIST回路1400から出力された信号1414が後段に配置されたBIST回路1400に信号1719として入力される。そして、BIST動作設定レジスタ17081に設定され、BIST設定デコーダ17091によりデコードされた信号1710(N+1)により、マルチプレクサ3012の切替が設定され、当該メモリセル1417から出力され取り込みレジスタ1418に取り込まれたデータと、フラグレジスタ1422に保持された内容のいずれかが選択されてシリアルに外部に出力される。10

**【0183】**

このように本実施の形態2によれば、上記実施の形態1と同様に、高速クロック1410を用いてメモリのBIST並びに故障診断を実速度で行うことができる、低速クロックによるシフト動作では検出できないフェイル情報を取得することができる。また、一旦フェイルが発生した後にBIST再開時の溯りを最小限にすることができるため、201回目のBIST開始時点まで遡って再度実行を繰り返す場合に比べて、テスト時間を削減することができる。

**【0184】**

さらに、上記参考例3と同様に故障診断の際に不良箇所のデータのみを外部にシフト出力することにより、故障診断時間を短縮しコスト低減を実現することができるとともに、BIST動作設定用レジスタ17081の設定に従い故障診断対象となっていないメモリからの出力をシフト出力する必要がないので故障診断に要する時間の一層の短縮に寄与することができる。30

**【0185】**

上述した実施の形態はいずれも一例であって、本発明を限定するものではなく、本発明の技術的範囲内において様々に変形することが可能である。

**【図面の簡単な説明】****【0186】**

【図1】本発明の実施の形態1による比較器型BIST回路を用いて故障診断動作を行う半導体集積回路の構成を示すブロック図。

【図2】同半導体集積回路が有する診断データ保存回路の構成を示すブロック図。

【図3】同半導体集積回路におけるメモリの故障診断の手順を示した説明図。

【図4】同半導体集積回路が有するBIST制御回路に含まれる状態制御回路の構成を示すブロック図。

【図5】同状態制御回路における動作の手順を示すフローチャート。40

【図6】参考例1による比較器型BIST回路を用いてBIST動作を行う半導体集積回路の構成を示したブロック図。

【図7】参考例2による圧縮器型BIST回路を用いてBIST動作を行う半導体集積回路の構成を示したブロック図。

【図8】参考例1による半導体集積回路を用いて故障診断動作を行う際の構成を示したブロック図。

【図9】参考例3によるBIST回路を用いて故障診断動作を行う半導体集積回路の構成を示したブロック図。

【図10】同半導体集積回路におけるBIST動作設定レジスタの構成を示した説明図。

【図11】同半導体集積回路において故障診断を行う場合の信号の流れを示したブロック50

図。

【図12】本発明の実施の形態2によるBIST回路を用いて故障診断動作を行う半導体集積回路が有するBIST回路の構成を示したブロック図。

【図13】同半導体集積回路が有するメモリカラーの構成を示したブロック図。

【符号の説明】

【0187】

|                  |              |

|------------------|--------------|

| 400、1400         | BIST回路       |

| 401、1401         | BIST制御回路     |

| 402、1402         | データ生成器       |

| 403、1403         | アドレス生成器      |

| 404、1404         | 制御信号生成器      |

| 405、1405         | 結果解析器        |

| 406、1406         | 診断データ保存回路    |

| 416、1416         | メモリカラー       |

| 417、1417         | メモリセル        |

| 418、505、506、1418 | 取り込みレジスタ     |

| 420、514、515      | 比較回路         |

| 422              | フラグレジスタ      |

| 508、509          | 保存レジスタ       |

| 518              | フラグ抑制信号用レジスタ |

10

20

【図1】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【 四 9 】

【図10】

【 図 1 1 】

【 図 1 2 】

【図13】

---

フロントページの続き

(72)発明者 安 藏 顯一

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 德 永 千佳子

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 小林 紀和

(56)参考文献 特許第4157066(JP, B2)

特開2009-26372(JP, A)

特開2009-59434(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 29 / 12

G 01 R 31 / 28

G 11 C 29 / 44

G 11 C 29 / 56