(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4305960号

(P4305960)

(45) 発行日 平成21年7月29日(2009.7.29)

(24) 登録日 平成21年5月15日(2009.5.15)

(51) Int.Cl.

G 11 C 11/22 (2006.01)

F 1

G 11 C 11/22 501 H

G 11 C 11/22 501 G

請求項の数 10 (全 16 頁)

(21) 出願番号 特願2005-377708 (P2005-377708)

(22) 出願日 平成17年12月28日 (2005.12.28)

(65) 公開番号 特開2007-179664 (P2007-179664A)

(43) 公開日 平成19年7月12日 (2007.7.12)

(54) 審査請求日 平成18年12月4日 (2006.12.4)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100079108

弁理士 稲葉 良幸

(74) 代理人 100080953

弁理士 田中 克郎

(74) 代理人 100093861

弁理士 大賀 真司

(72) 発明者 山村 光宏

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 高野 芳徳

最終頁に続く

(54) 【発明の名称】強誘電体メモリ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の第1のビット線と、

各第1のビット線に接続され、第1のデータ又は第2のデータを記憶する複数の第1のメモリセルと、

前記複数の第1のビット線のそれぞれに接続されており、前記複数の第1のメモリセルからデータが読み出されたときに、当該データに基づく読み出電圧を生成する複数の第1の読み出電圧生成部と、

第2のビット線と、

前記第2のビット線に接続され、前記第1のデータを記憶する第2のメモリセルと、 10

前記第2のビット線に接続されており、前記第2のメモリセルからデータが読み出されたときに、当該データに基づく読み出電圧を生成する第2の読み出電圧生成部と、

前記第2の読み出電圧生成部に接続された第1の基準電圧生成部と、

各第1の読み出電圧生成部と前記第1の基準電圧生成部とに接続された複数の第1のセンスアンプと、

を備え、

前記各読み出電圧生成部は、

ソースに第1の電圧が供給された第1のn型MOSトランジスタと、

前記第1のn型MOSトランジスタのドレインを、前記第1の電圧よりも高い正電圧である第2の電圧にプリチャージする第1のプリチャージ部と、

前記メモリセルに記憶されたデータが各ビット線に読み出されたときに、当該ビット線の電圧に基づいて前記第1のn型MOSトランジスタの前記ソースと前記ドレインとの間のチャネル抵抗を制御して、前記第2の電圧にプリチャージされた前記ドレインの電圧を低下させて、前記読み出電圧を生成するトランジスタ制御部と、

前記ドレインの電圧の低下に基づいて、前記ビット線の電圧を低下させる電圧制御部と、

、

を有し、

前記第1の基準電圧生成部は、前記第2の読み出電圧生成部よりも電圧供給能力が高く、前記第2の読み出電圧生成部が生成した読み出電圧を受け取り、当該読み出電圧と略同電圧である第1の基準電圧を生成し、

前記複数の第1のセンスアンプは、対応する前記第1の読み出電圧生成部が生成した読み出電圧と前記第1の基準電圧とを比較して、第1のメモリセルに記憶されたデータを判定することを特徴とする強誘電体メモリ装置。

#### 【請求項2】

前記第1の基準電圧生成部は、負帰還がかけられたオペアンプであって、前記第2の読み出電圧生成部が生成した読み出電圧を入力として受け取り、前記第1の基準電圧を出力することを特徴とする請求項1記載の強誘電体メモリ装置。

#### 【請求項3】

第3のビット線と、

前記第3のビット線に接続され、前記第2のデータを記憶する第3のメモリセルと、

前記第3のビット線に接続されており、前記第3のメモリセルから読み出されたデータに基づく読み出し電圧を生成する第3の読み出電圧生成部と、

前記第3の読み出電圧生成部よりも電圧供給能力が高く、前記第3の読み出電圧生成部が生成した読み出電圧と略同電圧である第2の基準電圧を生成する第2の基準電圧生成部と、

各第1の読み出電圧生成部に接続されており、各第1の読み出電圧生成部が生成した読み出電圧と前記第2の基準電圧とを比較する複数の第2のセンスアンプと、

をさらに備え、

各第1のビット線に接続された前記第1のセンスアンプ及び前記第2のセンスアンプは、当該第1のセンスアンプの比較結果と当該第2のセンスアンプの比較結果とにに基づいて、各第1のメモリセルから読み出されたデータを判定する

ことを特徴とする請求項1記載の強誘電体メモリ装置。

#### 【請求項4】

前記第2の読み出電圧生成部と前記第1の基準電圧生成部とに接続されており、前記第2の読み出電圧生成部が生成した読み出電圧を前記第1の基準電圧生成部に供給する第1の配線と、

前記第3の読み出電圧生成部と前記第2の基準電圧生成部とに接続されており、前記第3の読み出電圧生成部が生成した読み出電圧を前記第2の基準電圧生成部に供給する第2の配線と、

前記第1の配線と前記第2の配線との間に設けられた容量素子と、

をさらに備えたことを特徴とする請求項3記載の強誘電体メモリ装置。

#### 【請求項5】

前記第1の基準電圧生成部は、負帰還がかけられた第1のオペアンプであって、前記第2の読み出電圧生成部が生成した読み出電圧を入力として受け取り、前記第1の基準電圧を出力し、

前記第2の基準電圧生成部は、負帰還がかけられた第2のオペアンプであって、前記第2の読み出電圧生成部が生成した読み出電圧を入力として受け取り、前記第2の基準電圧を出力することを特徴とする請求項3又は4記載の強誘電体メモリ装置。

#### 【請求項6】

前記第1のオペアンプの出力と前記複数の第1のセンスアンプとに接続された第1の基準電圧線と、

10

20

30

40

50

前記第2のオペアンプの出力と前記複数の第2のセンスアンプとに接続された第2の基準電圧線と、

前記第1の基準電圧線及び前記第2の基準電圧線を前記第1の電圧にプリチャージする第2のプリチャージ部と、

をさらに備え、

前記第1の基準電圧生成部及び前記第2の基準電圧生成部は、前記第1の電圧にプリチャージされた前記第1の基準電圧線及び前記第2の基準電圧線に、それぞれ前記第1の基準電圧及び前記第2の基準電圧を供給する

ことを特徴とする請求項5記載の強誘電体メモリ装置。

【請求項7】

10

前記トランジスタ制御部は、

前記第1のn型MOSトランジスタのゲートを所定の正電圧にプリチャージする第3のプリチャージ部と、

前記ビット線と前記ゲートとの間に設けられた第1のキャパシタと、

を有することを特徴とする請求項1から6のいずれか1項記載の強誘電体メモリ装置。

【請求項8】

前記第2のプリチャージ部は、前記ゲートを、前記第1のn型MOSトランジスタの閾値電圧にプリチャージすることを特徴とする請求項7記載の強誘電体メモリ装置。

【請求項9】

20

前記電圧制御部は、前記第1のn型MOSトランジスタのドレインと前記ビット線との間に設けられた第2のキャパシタを有することを特徴とする請求項1から8のいずれか1項記載の強誘電体メモリ装置。

【請求項10】

前記第1の電圧は、接地電圧であることを特徴とする請求項1から9のいずれか1項記載の強誘電体メモリ装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、強誘電体メモリ装置に関する。

30

【背景技術】

【0002】

従来の強誘電体メモリとして、特開2002-157876号公報（特許文献1）に開示されたものがある。上記従来の強誘電体メモリでは、基準電圧を生成するための1ビット分の2T2Cセルに接続されたビット線が、PMOSトランジスタからなるPチャネル・ソースフォロワーのレベルシフト回路を介してセンスアンプに接続されており、センスアンプは、レベルシフト回路を通した後の電圧を基準電圧としている（第3の実施の形態参照）。

【特許文献1】特開2002-157876号公報

【発明の開示】

40

【発明が解決しようとする課題】

【0003】

しかしながら、上記従来の強誘電体メモリは、レベルシフト回路を通した後の電圧を基準電圧としているので、読み出しマージンが小さくなってしまうという問題が生じていた。また、上記従来の強誘電体メモリでは、レベルシフト回路を、基準電圧を生成するためのセルが接続されたビット線だけではなく、本来、レベルシフト回路を必要としない他のビット線にも接続しなければならぬので、レイアウト面積が増大するという問題が生じていた。

【0004】

よって、本発明は、上記の課題を解決することのできる強誘電体メモリ装置を提供する

50

ことを目的とする。この目的は特許請求の範囲における独立項に記載の特徴の組み合わせにより達成される。また従属項は本発明の更なる有利な具体例を規定する。

【課題を解決するための手段】

【0005】

上記課題を解決するため、本発明の一形態によれば、複数の第1のビット線と、各第1のビット線に接続され、第1のデータ又は第2のデータを記憶する複数の第1のメモリセルと、複数の第1のビット線のそれぞれに接続されており、複数の第1のメモリセルからデータが読み出されたときに、当該データに基づく読み出電圧を生成する複数の第1の読み出電圧生成部と、第2のビット線と、第2のビット線に接続され、第1のデータを記憶する第2のメモリセルと、第2のビット線に接続されており、第2のメモリセルからデータが読み出されたときに、当該データに基づく読み出電圧を生成する第2の読み出電圧生成部と、第2の読み出電圧生成部に接続された第1の基準電圧生成部と、各第1の読み出電圧生成部と第1の基準電圧生成部とに接続された複数の第1のセンスアンプと、を備え、各読み出電圧生成部は、ソースに第1の電圧が供給された第1のn型MOSトランジスタと、第1のn型MOSトランジスタのドレインを、第1の電圧よりも高い正電圧である第2の電圧にプリチャージする第1のプリチャージ部と、メモリセルに記憶されたデータが各ビット線に読み出されたときに、当該ビット線の電圧に基づいて第1のn型MOSトランジスタのソースとドレインとの間のチャネル抵抗を制御して、第2の電圧にプリチャージされたドレインの電圧を低下させて、読み出電圧を生成するトランジスタ制御部と、ドレインの電圧の低下に基づいて、ビット線の電圧を低下させる電圧制御部と、を有し、第1の基準電圧生成部は、第2の読み出電圧生成部よりも電圧供給能力が高く、第2の読み出電圧生成部が生成した読み出電圧を受け取り、当該読み出電圧と略同電圧である第1の基準電圧を生成し、複数の第1のセンスアンプは、対応する第1の読み出電圧生成部が生成した読み出電圧と第1の基準電圧とを比較して、第1のメモリセルに記憶されたデータを判定することを特徴とする強誘電体メモリ装置を提供する。10

【0006】

上記形態によれば、複数の第1のメモリセルからデータが読み出されると、複数の第1のビット線の電圧は当該データに基づいて変化し、各トランジスタ制御部は、当該第1のビット線の電圧に基づいて、各第1の読み出電圧生成部に設けられた第1のn型MOSトランジスタをオンし、さらにそのオン抵抗（チャネル抵抗）を制御することとなる。そして、各第1のn型MOSトランジスタがオンすると、第2の電圧にプリチャージされたドレイン電圧が低下し、各第1の読み出電圧生成部は、低下したドレイン電圧を、当該第1のメモリセルに記憶されたデータの読み出電圧として出力することとなる。30

【0007】

他方、第2のメモリセルからデータが読み出されると、同様に、第2の読み出電圧生成部は、当該データに基づいて低下した第2のn型MOSトランジスタのドレイン電圧を、当該第2のメモリセルに記憶されたデータの読み出電圧として出力することとなる。第2の読み出電圧生成部から読み出電圧が出力されると、第1の基準電圧生成部は、かかる読み出電圧と略同電圧である第1の基準電圧を生成する。ここで、第1の基準電圧生成部は、第2の読み出電圧生成部よりも電圧供給能力が高いので、第2の読み出電圧生成部の電圧供給能力が低くとも、第1の基準電圧は、その電圧値をほとんど変化させずに、複数の第1のセンスアンプに供給されることとなる。40

【0008】

以上のとおり、上記形態によれば、電圧供給能力が高い第1の基準電圧生成部を備えるので、電圧供給能力が低い第2の読み出電圧生成部が出力した読み出電圧の電圧値をほとんど変化させずに、複数の第1のセンスアンプに供給することができるので、読み出し動作の安定した強誘電体メモリ装置を提供することができる。また、上記形態によれば、電圧供給能力が高い第1の基準電圧生成部を、第2の読み出電圧生成部に対してのみ設ければよいので、強誘電体メモリ装置のチップ面積の増大を抑えることができる。

【0009】

50

20

30

40

50

また、上記形態によれば、第1のn型MOSトランジスタのオン抵抗は、ビット線の電圧の微小な変化によっても大きく変化する。従って、上記形態によれば、極めて簡易な構成で、第1のn型MOSトランジスタのドレイン電圧の低下量を、メモリセルに記憶されたデータに基づいて、大きく異ならせることができるので、回路規模やチップ面積が小さく、読み出しマージンが大きい強誘電体メモリ装置を提供することができる。

【0010】

また、上記形態によれば、電圧制御部がビット線の電圧の上昇を抑えるので、メモリセルにかかる電圧を高くすることができる。従って、上記形態によれば、読み出しマージンをさらに大きくすることができる。

【0011】

上記強誘電体メモリ装置は、第3のビット線と、第3のビット線に接続され、第2のデータを記憶する第3のメモリセルと、第3のビット線に接続されており、第3のメモリセルから読み出されたデータに基づく読み出し電圧を生成する第3の読み出電圧生成部と、第3の読み出電圧生成部よりも電圧供給能力が高く、第3の読み出電圧生成部が生成した読み出電圧と略同電圧である第2の基準電圧を生成する第2の基準電圧生成部と、各第1の読み出電圧生成部に接続されており、各第1の読み出電圧生成部が生成した読み出電圧と第2の基準電圧とを比較する複数の第2のセンスアンプと、をさらに備え、各第1のビット線に接続された第1のセンスアンプ及び第2のセンスアンプは、当該第1のセンスアンプの比較結果と当該第2のセンスアンプの比較結果とに基づいて、各第1のメモリセルから読み出されたデータを判定してもよい。

10

【0012】

上記強誘電体メモリ装置は、第2の読み出電圧生成部と第1の基準電圧生成部とに接続されており、第2の読み出電圧生成部が生成した読み出電圧を第1の基準電圧生成部に供給する第1の配線と、第3の読み出電圧生成部と第2の基準電圧生成部とに接続されており、第3の読み出電圧生成部が生成した読み出電圧を第2の基準電圧生成部に供給する第2の配線と、第1の配線と第2の配線との間に設けられた容量素子と、をさらに備えてもよい。

20

【0013】

上記強誘電体メモリ装置は、第1の基準電圧生成部は、負帰還がかけられた第1のオペアンプであって、第2の読み出電圧生成部が生成した読み出電圧を入力として受け取り、第1の基準電圧を出力し、第2の基準電圧生成部は、負帰還がかけられた第2のオペアンプであって、第2の読み出電圧生成部が生成した読み出電圧を入力として受け取り、第2の基準電圧を出力してもよい。

30

【0014】

上記強誘電体メモリ装置は、第1のオペアンプの出力と複数の第1のセンスアンプとに接続された第1の基準電圧線と、第2のオペアンプの出力と複数の第2のセンスアンプとに接続された第2の基準電圧線と、第1の基準電圧線及び第2の基準電圧線を第1の電圧にプリチャージする第2のプリチャージ部と、をさらに備え、第1の基準電圧生成部及び第2の基準電圧生成部は、第1の電圧にプリチャージされた第1の基準電圧線及び第2の基準電圧線に、それぞれ第1の基準電圧及び第2の基準電圧を供給してもよい。

40

【0015】

上記強誘電体メモリ装置において、トランジスタ制御部は、第1のn型MOSトランジスタのゲートを所定の正電圧にプリチャージする第3のプリチャージ部と、ビット線とゲートとの間に設けられた第1のキャパシタと、を有してもよい。

【0016】

上記強誘電体メモリ装置において、第2のプリチャージ部は、ゲートを、第1のn型MOSトランジスタの閾値電圧にプリチャージしてもよい。

【0017】

上記強誘電体メモリ装置において、電圧制御部は、第1のn型MOSトランジスタのドレインとビット線との間に設けられた第2のキャパシタを有してもよい。

【0018】

50

上記強誘電体メモリ装置において、第1の電圧は、接地電圧であってもよい。

【発明を実施するための最良の形態】

【0019】

以下、図面を参照しつつ、発明の実施形態を通じて本発明を説明するが、以下の実施形態は特許請求の範囲に係る発明を限定するものではなく、また、実施形態の中で説明されている特徴の組み合わせのすべてが発明の解決手段に必須であるとは限らない。

【0020】

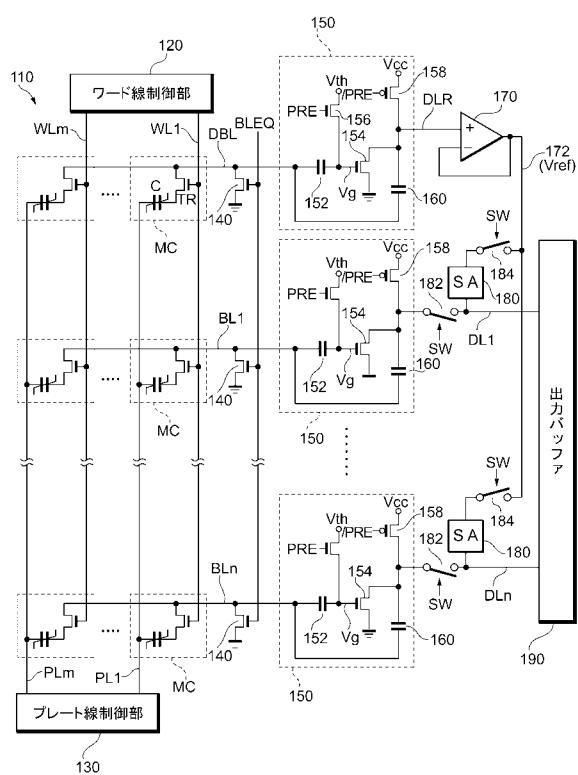

図1は、本発明の第1実施形態に係る強誘電体メモリ装置を示す図である。強誘電体メモリ装置は、メモリセルアレイ110と、ワード線制御部120と、プレート線制御部130と、n型MOSトランジスタ140と、読出電圧生成部150と、オペアンプ170と、センスアンプ180と、出力バッファ190とを備えて構成される。

【0021】

また、強誘電体メモリ装置は、m本(mは正の整数)のワード線WL1~m及びプレート線PL1~mと、複数の第1のビット線の一例であるn本(nは正の整数)のビット線BL1~nと、第2のビット線の一例であるダミービット線DBLと、n本のデータ線DL1~nと、ダミーデータ線DLRと、n個のスイッチ182とn個のスイッチ184とを備えて構成される。

【0022】

メモリセルアレイ110は、アレイ状に配置されたm×n個のメモリセルMCを有する。メモリセルMCは、n型MOSトランジスタTRと、強誘電体キャパシタCとを有して構成される。

【0023】

n型MOSトランジスタTRは、ゲートがワード線WL1~mのいずれかに接続され、ソースがダミービット線DBL及びビット線BL1~nのいずれかに接続され、ドレインが強誘電体キャパシタCの一方端に接続されている。すなわち、n型MOSトランジスタTRは、ワード線WL1~mの電圧に基づいて、強誘電体キャパシタCの一方端を、ダミービット線DBL及びビット線BL1~nに接続するか否かを切り換える。

【0024】

強誘電体キャパシタCは、他方端がプレート線PL1~mのいずれかに接続されており、その一方端と他方端との電位差に基づいて、所定のデータを記憶し、また、記憶されたデータに基づいて所定量の電荷をダミービット線DBL及びビット線BL1~nに放出する。本実施形態において、強誘電体キャパシタCは、一方端の電位に対して、他方端の電位が、その抗電圧より高くなった場合に“1”を記憶し、他方端の電位に対して、一方端の電位が、その抗電圧より高くなった場合に“0”を記憶する。

【0025】

ワード線制御部120は、ワード線WL1~mに接続されており、ワード線WL1~mの電圧を制御する。具体的には、ワード線制御部120は、強誘電体メモリ装置の外部から供給されたアドレス信号に基づいて、ワード線WL1~mのうちの所定のワード線WLの電位を、他のワード線WLの電位より高くして、当該所定のワード線WLに接続されたn個のメモリセルMCを選択する。

【0026】

プレート線制御部130は、プレート線PL1~mに接続されており、プレート線PL1~mの電圧を制御する。具体的には、プレート線制御部130は、アドレス信号に基づいて、プレート線PL1~mのうちの所定のプレート線PLの電位を、他のプレート線PLの電位より高くして、当該所定のプレート線PLを選択する。そして、プレート線制御部130は、当該所定のプレート線PLを選択する。

【0027】

n型MOSトランジスタ140は、ソースが接地されており、ドレインがダミービット線DBL及びビット線BL1~nに接続されている。また、n型MOSトランジスタ140は、ゲートに信号BLEQが供給されており、信号BLEQの電圧に基づいて、ダミー

10

20

30

40

50

ビット線 D B L 及びビット線 B L 1 ~ n を接地するか否かを切り換える。

【 0 0 2 8 】

読み出電圧生成部 150 は、第1のキャパシタの一例であるキャパシタ 152 と、n型MOSトランジスタ 154 及び 156 と、p型MOSトランジスタ 158 と、第2のキャパシタの一例であるキャパシタ 160 とを有して構成される。読み出電圧生成部 150 は、ダミービット線 D B L 及びビット線 B L 1 ~ n に対応してそれぞれ設けられており、メモリセル M C からデータが読み出されたときのダミービット線 D B L 及びビット線 B L 1 ~ n の電圧を増幅して出力する。

【 0 0 2 9 】

キャパシタ 152 は、その一方端がダミービット線 D B L 及びビット線 B L 1 ~ n に接続されており、他方端が n 型 MOS トランジスタ 154 のゲートに接続されている。そして、キャパシタ 152 は、ダミービット線 D B L 及びビット線 B L 1 ~ n の電圧の変化に基づいて、n 型 MOS トランジスタ 154 のゲート電圧を変化させる。

【 0 0 3 0 】

n 型 MOS トランジスタ 154 は、ソースが接地されており、ドレインが読み出電圧生成部 150 の出力に接続されている。そして、n 型 MOS トランジスタ 154 は、そのゲート電圧に基づいてオン又はオフする。さらに、n 型 MOS トランジスタ 154 は、オン時には、ゲート電圧に基づいて、ソース・ドレイン間のチャネル抵抗を制御して、そのドレイン電圧を、ビット線 B L 1 ~ n 及びダミービット線 D B L に読み出されたデータに基づく読み出電圧として、スイッチ 182 を介してデータ線 D L 1 ~ n に、そして直接ダミーデータ線 D L R に出力する。

【 0 0 3 1 】

n 型 MOS トランジスタ 156 は、ソースが n 型 MOS トランジスタ 154 のゲートに接続されており、ドレインに、n 型 MOS トランジスタ 154 の閾値電圧付近の電圧 V t h が供給されている。そして、n 型 MOS トランジスタ 156 は、ゲートに供給される信号 P R E の電圧に基づいて、n 型 MOS トランジスタのゲートをその閾値電圧付近に充電する。

【 0 0 3 2 】

p 型 MOS トランジスタ 158 は、ソースに第2の電圧の一例である、強誘電体メモリ装置の動作電圧 V C C が供給されており、ドレインが n 型 MOS トランジスタ 154 のドレインに接続されている。そして、p 型 MOS トランジスタ 158 は、ゲートに供給される信号 / P R E ( 信号 P R E の反転信号 ) に基づいて、n 型 MOS トランジスタ 154 のドレインを V C C に充電する。本実施形態では、p 型 MOS トランジスタ 158 によって n 型 MOS トランジスタ 154 のドレイン電圧を V C C にプリチャージし、n 型 MOS トランジスタ 154 によって当該ドレイン電圧を V C C から 0 V の間の電圧に低下させるので、読み出電圧生成部 150 において使用する電圧の範囲を、強誘電体メモリ装置において使用する接地電圧から V C C の範囲とすることができるので、高速かつ電圧制御が容易で、レベルシフト回路が不要な構成とすることができる。

【 0 0 3 3 】

キャパシタ 160 は、一方端が n 型 MOS トランジスタ 154 のドレインに接続されており、他方端がダミービット線 D B L 及びビット線 B L 1 ~ n に接続されている。そして、キャパシタ 160 は、n 型 MOS トランジスタ 154 のドレイン電圧の変化に基づいて、ダミービット線 D B L 及びビット線 B L 1 ~ n の電圧を変化させる。

【 0 0 3 4 】

オペアンプ 170 は、正入力端、負入力端及び出力端を有しており、正入力端がダミーデータ線 D L R に接続されており、負入力端が出力端に接続されている。すなわち、オペアンプ 170 は、負帰還がかけられており、正入力端に供給された読み出電圧と略同じ電圧を、基準電圧 V r e f として、その出力端に接続された配線 172 に供給する。また、オペアンプ 170 は、読み出電圧生成部 150 よりも、電圧供給能力が高くなるように構成される。なお、本実施形態において、基準電圧 V r e f は、ビット線 B L 1 ~ n に接続され

10

20

30

40

50

たメモリセルMCに記憶されたデータが“0”である場合における読み出電圧と、当該データが“1”である場合における読み出電圧との間の電圧となるように設定されている。

【0035】

センスアンプ180は、一方端及び他方端を有しており、一方端が、データ線DL1～nに接続されるとともに、スイッチ182を介して読み出電圧生成部150の出力に接続されている。また、センスアンプ180は、他方端がスイッチ184を介して配線172に接続されている。スイッチ182及び184は、例えば、MOSトランジスタや伝送ゲート等であり、信号SWの論理値に応じてオン・オフし、センスアンプ180をデータ線DL1～n及び配線172に接続するか否かを切り換える。信号SWは、センスアンプ180を動作させるか否かを制御する信号と同期した信号であってもよい。

10

【0036】

すなわち、センスアンプ180は、スイッチ182及び184がオンしている期間に、一方端に各ビット線BL1～nに読み出されたデータに基づく読み出電圧が供給され、他方端には基準電圧Vrefが供給されている。そして、センスアンプ180は、スイッチ182及び184がオフしている期間に読み出電圧と基準電圧Vrefとを比較して、その比較結果を出力バッファ190に供給する。具体的には、センスアンプ180は、読み出電圧が基準電圧Vrefよりも高い場合、データ線DL1～nの電圧をVCCとし、読み出電圧が基準電圧Vrefよりも低い場合、データ線DL1～nの電圧を0Vとする。すなわち、センスアンプ180は、データ線DL1～nの読み出電圧が、基準電圧Vrefよりも高い場合、データ線DL1～nの電圧をVCCとして、メモリセルMCに記憶されたデータが“0”であると判定する一方、低い場合、データ線DL1～nの電圧を0Vとして、当該データが“1”であると判定する。

20

【0037】

出力バッファ190は、データ線DL1～nが接続されており、センスアンプ180がデータ線DL1～nにおいて増幅したデータを強誘電体メモリ装置の外部に出力する。

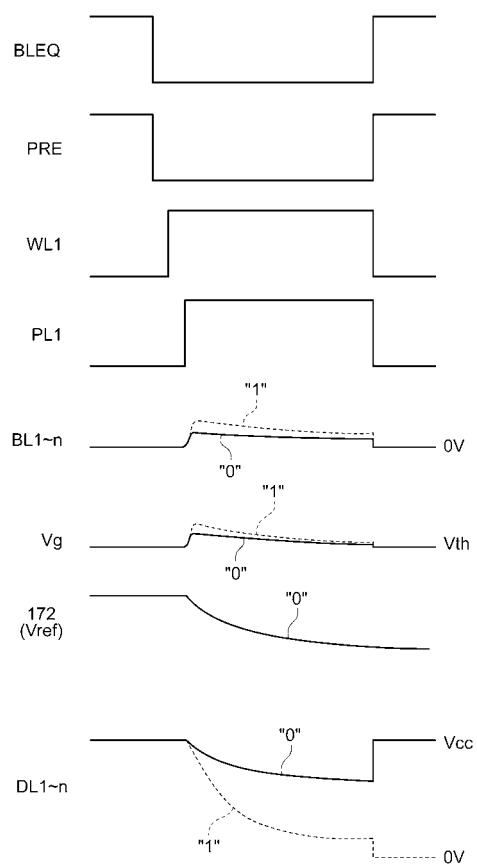

【0038】

図2は、本実施形態の強誘電体メモリ装置の動作を示すタイミングチャートである。図1及び図2を参照して、ワード線WL1及びプレート線PL1を選択して、ビット線BL1～nに接続されたメモリセルMCに記憶されたデータを読み出す場合を例に、本実施形態の強誘電体メモリ装置の動作について説明する。

30

【0039】

以下の例において各信号がL論理を示すときの当該信号の電圧は接地電圧であり、各信号がH論理を示すときの当該信号電圧は、強誘電体メモリ装置の動作電圧であるVCC、VDD、又はVPPである。なお、各信号の電圧は、これに限られるものではなく、H論理を示すときの信号の電圧が、L論理を示すときの信号の電圧より高いものであればよい。

【0040】

まず、初期状態において、信号BLEQはH論理を示しており、各n型MOSトランジスタ140はオンし、ダミービット線DBL及びビット線BL1～nの電圧は、接地電圧となる。そして、信号BLEQがL論理となり、ダミービット線DBL及びビット線BL1～nは接地電圧にプリチャージされる。また、配線172は、VCCにプリチャージされている。また、初期状態において、スイッチ182及び184は、オンしており、センスアンプ180は、読み出電圧生成部150のn型MOSトランジスタ154のドレイン、及び、配線172に接続されている。

40

【0041】

また、初期状態において、信号PREはH論理を示し、信号/PREはL論理を示しており、n型MOSトランジスタ156及びp型MOSトランジスタ158はオンし、n型MOSトランジスタ154のゲート電圧は、閾値電圧Vthとなり、ドレイン電圧はVCCとなる。そして、信号PREがL論理となり、信号/PREがH論理となって、n型MOSトランジスタ154のゲート及びドレインは、それぞれVth及びVCCにプリチャ

50

ージされる。

【0042】

次に、ワード線制御部120は、ワード線WL1の電圧を上昇させて、ワード線WL1に接続されたメモリセルMCを構成するn型MOSトランジスタTRをオンさせる。これにより、ワード線WL1に接続されたメモリセルMCを構成する強誘電体キャパシタCは、ダミービット線DBL及びビット線BL1～nに接続される。

【0043】

次に、プレート線制御部130は、プレート線PL1の電圧をVCCに上昇させる。これにより、ワード線WL1に接続されたメモリセルMCを構成する強誘電体キャパシタCには、ダミービット線DBL及びビット線BL1～nの電圧を基準として、VCCがかかる。

10

【0044】

これにより、強誘電体キャパシタCに記憶されたデータに応じて、当該強誘電体キャパシタCから取り出された電荷が、ダミービット線DBL及びビット線BL1～nに放出されるので、各メモリセルMCに記憶されたデータに基づいて、ダミービット線DBL及びビット線BL1～nの電圧が上昇する。具体的には、メモリセルMCに記憶されたデータが“1”である場合のビット線BL1～nの電圧（図中点線）は、当該データが“0”である場合のビット線BL1～nの電圧（図中実線）よりも高くなる。また、本実施形態において、ダミービット線DBLに接続されたメモリセルMCに設けられた強誘電体キャパシタCの面積は、ビット線BL1～nに接続されたメモリセルMCに設けられた強誘電体キャパシタCの面積よりも大きく、メモリセルMCに記憶されたデータが“1”である場合のダミービット線DBLの電圧は、ビット線BL1～nの電圧よりも高くなり、当該データが“0”である場合のダミービット線DBLの電圧は、ビット線BL1～nの電圧よりも低くなる。

20

【0045】

メモリセルMCからデータが読み出されて、ダミービット線DBL及びビット線BL1～nの電圧、すなわち、キャパシタ152の一方端の電圧が上昇すると、キャパシタ152は、一方端の電圧に基づいて、他方端の電圧、すなわち、n型MOSトランジスタ154のゲート電圧Vgを上昇させる。

【0046】

30

n型MOSトランジスタ154のゲート電圧Vgは閾値電圧であるVthにプリチャージされているので、キャパシタ152の一方端の電圧が上昇すると、ゲート電圧VgはVthより高い電圧となり、n型MOSトランジスタ154がオンする。

【0047】

n型MOSトランジスタ154がオンすると、そのドレインは、n型MOSトランジスタ154のチャネル抵抗（オン抵抗）を介して、接地されたソースと接続される。また、n型MOSトランジスタのチャネル抵抗の大きさは、ゲート電圧Vgの大きさによって変化する。すなわち、n型MOSトランジスタ154のチャネル抵抗の大きさは、メモリセルMCに記憶されたデータに応じて変化する。

【0048】

40

従って、n型MOSトランジスタ154のドレインに接続されたデータ線DL1～n及びダミーデータ線DLRの電圧は、メモリセルMCに記憶されたデータが“0”である場合に比して、当該データが“1”である場合の方が、大きく低下することとなる。すなわち、n型MOSトランジスタ154は、ゲート電圧Vgの微小な変化を、ドレイン電圧、すなわち、データ線DL1～n及びダミーデータ線DLRの電圧を変化させることによって大きく増幅することができる。

【0049】

また、n型MOSトランジスタ154のドレイン電圧、すなわち、キャパシタ160の一方端の電圧が低下すると、キャパシタ160は、当該低下に基づいて、その他方端、すなわち、ビット線BL1～nの電圧上昇を抑える。これにより、ビット線BL1～nとブ

50

レート線 P L 1 との電位差、すなわち、強誘電体キャパシタ C にかかる電圧を大きく保つことができる。ビット線 B L 1 ~ n に放出される電荷量が増加させることができる。

【 0 0 5 0 】

また、ダミーデータ線 D L R の電圧が変化すると、それに応じて、オペアンプ 1 7 0 の正入力端の電圧が変化する。

【 0 0 5 1 】

そして、本実施形態において、ダミービット線 D B L に接続された強誘電体キャパシタ C には “ 0 ” が記憶されている。そして、上述のとおり、当該強誘電体キャパシタ C の面積を他の強誘電体キャパシタ C よりも大きく設定している。このため、当該強誘電体キャパシタ C からダミービット線 D B L に放出される電荷量は、“ 0 ” が記憶された強誘電体キャパシタ C からビット線 B L 1 ~ n に放出される電荷量よりも多い。従って、オペアンプ 1 7 0 の正入力端に接続されたダミーデータ線 D L R の電圧は、ビット線 B L 1 ~ n に接続されたメモリセル M C に記憶されたデータが “ 0 ” である場合のデータ線 D L 1 ~ n の電圧（以下、「データ “ 0 ” のデータ線 D L 1 ~ n の読み出電圧」という。）と、当該データが “ 1 ” である場合のデータ線 D L 1 ~ n の電圧（以下、「データ “ 1 ” のデータ線 D L 1 ~ n の読み出電圧」という。）との間の電圧となり、負帰還がかけられたオペアンプ 1 7 0 は、ダミーデータ線 D L R の電圧を、基準電圧 V r e f として出力端に接続された配線 1 7 2 に供給する。

【 0 0 5 2 】

そして、読み出電圧及び基準電圧 V r e f がそれぞれデータ線 D L 1 ~ n 及び配線 1 7 2 に供給されて一定時間が経過した後、信号 S W の論理値を変化させて、スイッチ 1 8 2 及び 1 8 4 をオフし、読み出電圧生成部 1 5 0 及び配線 1 7 2 とセンスアンプ 1 8 0 とを切り離す。そして、センスアンプ 1 8 0 の動作を開始させると、センスアンプ 1 8 0 は、データ線 D L 1 ~ n に出力された読み出電圧と、センスアンプ 1 8 0 の他方端に供給された基準電圧とを比較して、メモリセル M C に記憶されたデータを判定する。具体的には、センスアンプ 1 8 0 は、オンしたときに、読み出電圧が基準電圧よりも高い場合、すなわち、ビット線 B L 1 ~ n に接続されたメモリセル M C に記憶されたデータが “ 0 ” である場合、データ線 D L 1 ~ n の電圧を V C C 付近まで上昇させ（図中実線）、当該データが “ 1 ” である場合、データ線 D L 1 ~ n の電圧を接地電圧付近まで低下させる（図中点線）。以上の動作により、本実施形態の強誘電体メモリ装置において、強誘電体キャパシタ C に記憶されたデータが読み出される。

【 0 0 5 3 】

本実施形態によれば、電圧供給能力が高いオペアンプ 1 7 0 を備えるので、電圧供給能力が低い読み出電圧生成部 1 5 0 が出力した読み出電圧の電圧値をほとんど変化させずに、複数のセンスアンプ 1 8 0 に供給することができる。読み出し動作の安定した強誘電体メモリ装置を提供することができる。また、本実施形態によれば、電圧供給能力が高いオペアンプ 1 7 0 を、ダミーデータ線 D L R に接続された読み出電圧生成部 1 5 0 に対して設ければよいので、強誘電体メモリ装置のチップ面積の増大を抑えることができる。

【 0 0 5 4 】

上記発明の実施形態を通じて説明された実施例や応用例は、用途に応じて適宜に組み合わせて、又は変更若しくは改良を加えて用いることができ、上記発明は上述した実施形態の記載に限定されるものではない。そのような組み合わせ又は変更若しくは改良を加えた形態も上記発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

【 0 0 5 5 】

例えば、上記実施形態においては、ダミービット線 D B L に接続された強誘電体キャパシタ C の面積を大きくして “ 0 ” を記憶しているが、ダミービット線 D B L に接続された強誘電体キャパシタ C の面積を小さくして “ 1 ” を記憶してもよい。

【 0 0 5 6 】

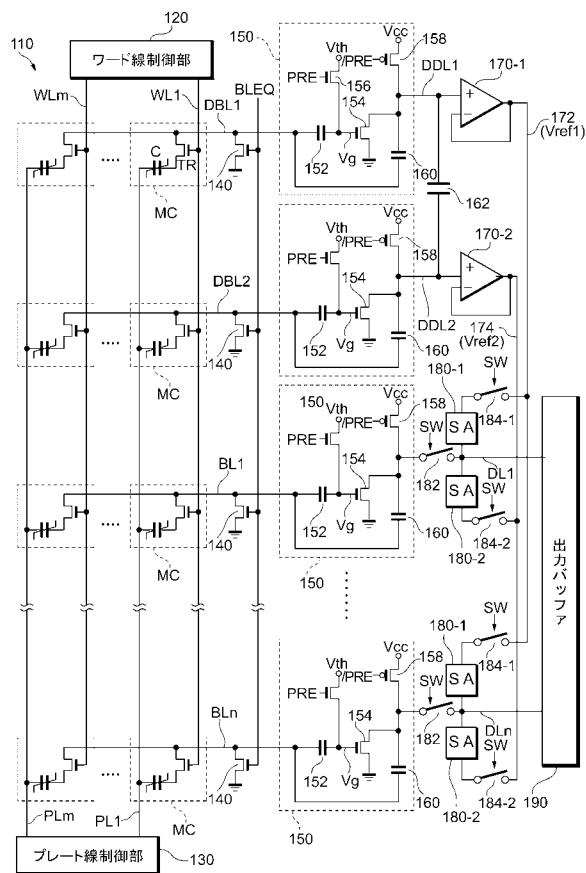

図 3 は、強誘電体メモリ装置の第 2 実施形態を示す図である。以下において、第 1 実施

10

20

30

40

50

形態と異なる点を中心に第2実施形態の強誘電体メモリ装置について説明する。なお、第1実施形態と同一の符号を付した構成については、第1実施形態と同様の機能を有する。

【0057】

本実施形態の強誘電体メモリ装置は、2本のダミービット線DBL1及び2と、2本のダミーデータ線DDL1及び2と、容量素子162と、2つのオペアンプ170-1及び2と、各データ線DL1～nに対して2つのセンスアンプ180-1及び2を備える点において、第1実施形態の強誘電体メモリ装置と異なる。

【0058】

また、本実施形態において、ダミービット線DBL1に接続されたメモリセルMCにはデータ“0”が記憶されており、ダミービット線DBL2に接続されたメモリセルMCにはデータ“1”が記憶されている。さらに、本実施形態において、ダミービット線DBL1及び2に接続された強誘電体キャパシタCの面積は、ビット線BL1～nに接続された強誘電体キャパシタCの面積と略等しい。10

【0059】

容量素子162は、一方端がダミーデータ線DDL1に接続されており、他方端がダミーデータ線DDL2に接続されている。また、容量素子162が有する容量は、ダミーデータ線DDL1とダミーデータ線DDL2との間に存在する寄生容量よりも大きい。

【0060】

オペアンプ170-1及び2は、メモリセルMCからデータが読み出されたときのダミーデータ線DDL1及び2の電圧と略同じ電圧を、基準電圧Vref1及びVref2として、それぞれ配線172及び174に供給する。また、配線172は、センスアンプ180-1の他方端に接続されており、配線174は、センスアンプ180-2の他方端に接続されている。すなわち、センスアンプ180-1は、基準電圧Vref1とデータ線DL1～nの読み出電圧とを比較し、センスアンプ180-2は、基準電圧Vref2とデータ線DL1～nの読み出電圧とを比較する。20

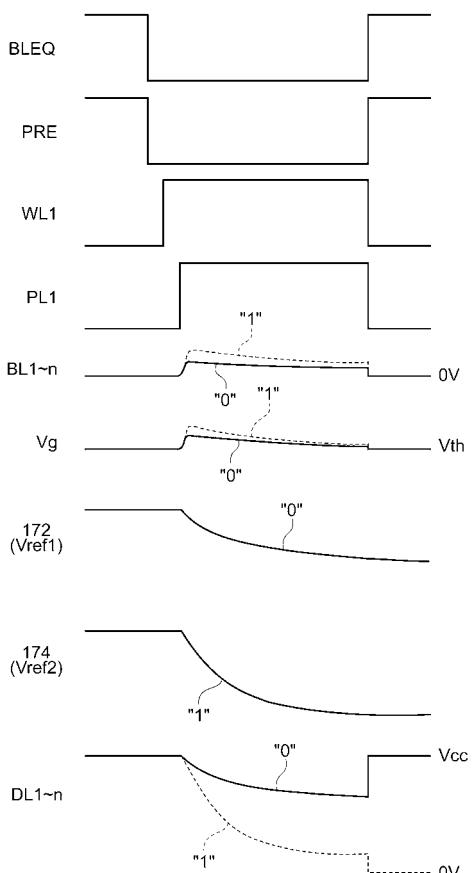

【0061】

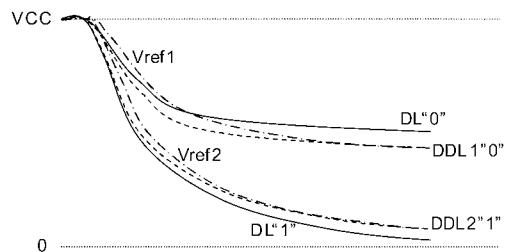

図4は、本実施形態の強誘電体メモリ装置の動作を示すタイミングチャートである。また、図5は、図4におけるダミーデータ線DDL1、ダミーデータ線DDL2、データ線DL1～n及び基準電圧Vref1、2の電圧の変化を対比して示した図である。図5において、データ“0”的データ線DL1～nの読み出電圧(DL“0”)、データ“1”的データ線DL1～nの読み出電圧(DL“1”)を実線で示し、ダミーデータ線DDL1の電圧(DDL1“1”)、ダミーデータ線DDL2の電圧(DDL2“0”)を点線で示し、基準電圧Vref1及び2の電圧を一点鎖線で示している。図3乃至図5を参照して、ワード線WL1及びプレート線PL1を選択して、ビット線BL1～nに接続されたメモリセルMCに記憶されたデータを読み出す場合を例に、第1実施形態と異なる点を中心に、本実施形態の強誘電体メモリ装置の動作について説明する。30

【0062】

ワード線WL1及びプレート線PL1の電圧が上昇し、メモリセルMCからデータが読み出されると、ダミービット線DBL1及び2並びにビット線BL1～nの電圧が上昇し、各メモリセルMCに記憶されたデータに応じて、ダミーデータ線DDL1及び2並びにデータ線DL1～nの電圧が低下する。40

【0063】

本例において、ダミービット線DBL1に接続されたメモリセルMCにはデータ“0”が記憶されており、ダミービット線DBL2に接続されたメモリセルMCにはデータ“1”が記憶されているので、各メモリセルMCからデータが読み出されると、図5に示すように、ダミーデータ線DDL1に接続されたn型MOSトランジスタ154のドレイン電圧(DDL1“0”)は、データ“0”的データ線DL1～nの読み出電圧(DL“0”)と同様に低下し、ダミーデータ線DDL2に接続されたn型MOSトランジスタ154のドレイン電圧(DDL2“1”)は、データ“1”的データ線DL1～nの読み出電圧(DL“1”)と同様に低下する。しかし、ダミーデータ線DDL1とダミーデータ線DDL

2との間には容量素子162が設けられているので、ダミーデータ線DDL1の電圧は、データ“0”的データ線DL1～nの読み出電圧よりも低い電圧となり、ダミーデータ線DDL2の電圧は、データ“1”的データ線DL1～nの読み出電圧よりも高い電圧となる。そして、オペアンプ170-1及び2は、ダミーデータ線DDL1及び2の電圧(DDL1“0”及びDDL2“1”)を、それぞれ基準電圧Vref1及び2として、それぞれ配線172及び174に供給する。

【0064】

センスアンプ180-1は、データ線DL1～nに出力された読み出電圧とデータ“0”に対応する基準電圧Vref1とを比較し、センスアンプ180-2は、当該読み出電圧とデータ“1”に対応する基準電圧Vref2とを比較する。そして、データ“0”的データ線DL1～nの読み出電圧は、基準電圧Vref1及び2より高くなるので、センスアンプ180-1及び2は、データ線DL1～nの電圧をVCC付近まで上昇させる(図4中実線)。

【0065】

一方、データ“1”的データ線DL1～nの読み出電圧は、基準電圧Vref1及び2より低くなるので、センスアンプ180-1及び2は、データ線DL1～nの電圧を0V付近まで低下させる(図4中点線)。以上の動作により、本実施形態の強誘電体メモリ装置において、強誘電体キャパシタCに記憶されたデータが読み出される。

【0066】

なお、本実施形態では、ダミーデータ線DDL1とDDL2との間に容量素子162が接続されているが、容量素子162がなくても正常に動作する。

【0067】

このとき、ビット線BL1～nにデータ“0”が読み出された場合、基準電圧Vref1はデータ“0”的データ線DL1～nの読み出電圧と等しくなるため、センスアンプ180-1の動作は一時的に不安定となる。しかし、基準電圧Vref2はデータ“0”的データ線DL1～nの読み出電圧より低いので、センスアンプ180-2が動作すると、センスアンプ180-2はデータ線DL1～nの電圧を上昇させる。データ線DL1～nの電圧が上昇すると、データ線DL1～nの読み出電圧は基準電圧Vref1より高くなるため、センスアンプ180-1の動作が安定し、2つのセンスアンプはそろってデータ線DL1～nの電圧をVCC付近まで上昇させる。

【0068】

また、ビット線BL1～nにデータ“0”が読み出された場合には、上記とは逆に、センスアンプ180-2が一時的に不安定となっている間に、センスアンプ180-1がデータ線DL1～nの電圧を低下させるため、センスアンプ180-1及び2は、そろってデータ線DL1～nの電圧を0V付近まで低下させることとなる。

【0069】

一方、本実施形態では、ダミーデータ線DDL1とDDL2との間に容量素子162が接続されているので、片方のセンスアンプの動作状態が一時的に不安定になることがなく、常に両方のセンスアンプが協力してデータ線DL1～nの電圧を増幅することとなる。したがって、センスアンプ180-1及び180-2の読み出しマージンを向上させることができ、また、センス動作を高速化させることができる。

【0070】

上記発明の実施形態を通じて説明された実施例や応用例は、用途に応じて適宜に組み合わせて、又は変更若しくは改良を加えて用いることができ、本発明は上述した実施形態の記載に限定されるものではない。そのような組み合わせ又は変更若しくは改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

【0071】

例えば、上記実施形態においては、ダミービット線DBL1に接続された強誘電体キャパシタには“0”を記憶し、ダミービット線DBL2に接続された強誘電体キャパシタには“1”を記憶しているが、逆であってもよい。またダミービット線DBL1に接続され

10

20

30

40

50

た強誘電体キャパシタに記憶するデータと、ダミービット線D B L 2に接続された強誘電体キャパシタに記憶するデータとをアクセスごと、あるいは不定期に入れ替えても良い。

【0072】

なお、容量素子162は強誘電体キャパシタであってもよい。容量素子162を強誘電体キャパシタで形成すると、極めて小さな面積に容量素子162を配置できるため、チップ面積がさらに小さい強誘電体メモリ装置を実現することができる。

【0073】

一般的に同一の半導体回路を配置する場合、自分自身のパターン構造のみでなく、その周りの回路パターン構造も同一にすることにより、それぞれの同一回路の微小なパターン形状差をなくして電気的特性誤差を抑えることができる。よって、ダミーデータ線D D L 1とD D L 2との間にセンスアンプ180-1及び2と等しいダミーセンスアンプを配置することで、そのダミーセンスアンプ内の寄生容量を容量素子162としてもよい。この場合、新しく配置したダミーセンスアンプに隣接する回路、すなわち、ダミービット線D B L 1及び2に接続された読出電圧生成部150と、D L 1に接続されたセンスアンプ180-1及び2の電気的特性誤差を減らすことができる。

10

【0074】

また、ダミーデータ線D D L 1とD D L 2との間に容量素子162を設けずに、他の手段によって基準電圧Vref1及びVref2を生成してもよい。例えば、容量素子162を設けずに、ダミービット線D B L 1に接続されるメモリセルMCの容量を、ダミービット線D B L 2に接続されるメモリセルMCの容量と異ならせることによって、基準電圧Vref1及びVref2を生成するようにしてもよい。

20

【0075】

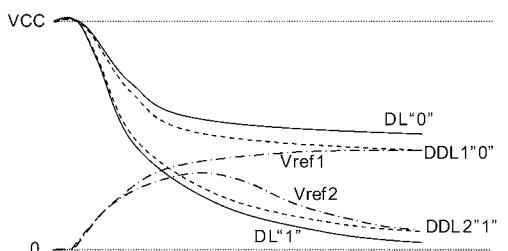

図6は、第2実施形態の他の例におけるデータ線D L 1～nの読出電圧並びに基準電圧Vref1及び2の変化を示す図である。配線172及び174は、図4で説明した例においてVCCにプリチャージされていたが、本例においては、0Vにプリチャージされている。図6において、データ“0”的データ線D L 1～nの読出電圧(D L “0”)、データ“1”的データ線D L 1～nの読出電圧(D L “1”)を実線で示し、ダミーデータ線D D L 1の電圧(D D L 1 “0”)、ダミーデータ線D D L 2の電圧(D D L 2 “1”)を点線で、基準電圧Vref1及びVref2を一点鎖線で示している。

30

【0076】

同図に示すように、配線172及び174を0Vにプリチャージした場合には、基準電圧Vref1及びVref2の電圧がダミーデータ線D D L 1の電圧(D D L 1 “0”)及びダミーデータ線D D L 2の電圧(D D L 2 “1”)の電圧に追従するのに時間がかかる。そのため、その間、基準電圧Vref1とデータ“0”的データ線D L 1～nの読出電圧との電位差、及び、基準電圧Vref2とデータ“1”的データ線D L 1～nの読出電圧との電位差が広がるので、読み出しマージンをさらに向上させることができる。

上記発明の実施形態を通じて説明された実施例や応用例は、用途に応じて適宜に組み合わせて、又は変更若しくは改良を加えて用いることができ、本発明は上述した実施形態の記載に限定されるものではない。そのような組み合わせ又は変更若しくは改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

40

【図面の簡単な説明】

【0077】

【図1】本発明の第1実施形態に係る強誘電体メモリ装置を示す図である。

【図2】本実施形態の強誘電体メモリ装置の動作を示すタイミングチャートである。

【図3】強誘電体メモリ装置の第2実施形態を示す図である。

【図4】本実施形態の強誘電体メモリ装置の動作を示すタイミングチャートである。

【図5】図4におけるダミーデータ線D D L 1及びD D L 2、参照電圧Vref1及びVref2、並びに、データ線D L 1～nの電圧の変化を対比して示した図である。

【図6】第2実施形態の他の例におけるダミーデータ線D D L 1及びD D L 2、データ線D L 1～nの読出電圧並びに基準電圧Vref1及び2の変化を示す図である。

50

## 【符号の説明】

【 0 0 7 8 】

110 . . . メモリセルアレイ、120 . . . ワード線制御部、130 . . . プレート線制御部、140 . . . n型MOSトランジスタ、150 . . . 読出電圧生成部、152 . . . キャパシタ、154 . . . n型MOSトランジスタ、156 . . . n型MOSトランジスタ、158 . . . p型MOSトランジスタ、160 . . . キャパシタ、162 . . . 容量素子、170 . . . オペアンプ、172、174 . . . 配線、180 . . . センスアンプ、190 . . . 出力バッファ、B L 1 ~ n . . . ビット線、D B L , D B L 1 , D B L 2 . . . ダミービット線、D L 1 ~ n . . . データ線、M C . . . メモリセル、P L 1 ~ m . . . プレート線、W L 1 ~ m . . . ワード線

10

【 义 1 】

【 四 2 】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(56)参考文献 特許第4186119(JP,B2)

特開2004-253108(JP,A)

特開2002-157876(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11 / 22