(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5117950号

(P5117950)

(45) 発行日 平成25年1月16日(2013.1.16)

(24) 登録日 平成24年10月26日(2012.10.26)

(51) Int.Cl.

F 1

G 11 C 16/06 (2006.01)

G 11 C 17/18 (2006.01)G 11 C 17/00 634C

G 11 C 17/00 306A

請求項の数 9 (全 24 頁)

(21) 出願番号 特願2008-187721 (P2008-187721)

(22) 出願日 平成20年7月18日 (2008.7.18)

(65) 公開番号 特開2010-27146 (P2010-27146A)

(43) 公開日 平成22年2月4日 (2010.2.4)

審査請求日 平成23年6月24日 (2011.6.24)

(73) 特許権者 308033711

ラピスセミコンダクタ株式会社

東京都八王子市東浅川町550番地1

(74) 代理人 100079049

弁理士 中島 淳

(74) 代理人 100084995

弁理士 加藤 和詳

(74) 代理人 100085279

弁理士 西元 勝一

(74) 代理人 100099025

弁理士 福田 浩志

(72) 発明者 村田 伸一

東京都港区虎ノ門1丁目7番12号 沖電

気工業株式会社内

最終頁に続く

(54) 【発明の名称】データ読出回路及び半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ソースが電源に接続され、データ読出対象のメモリセルが接続される入力端にドレインが接続され、ゲートに第1バイアス電圧が供給され、飽和領域で動作するよう構成された第1PMOSトランジスタと、

ソースが前記第1PMOSトランジスタのドレインに接続され、ドレインが出力端に接続され、ゲートに第2バイアス電圧が供給される第2PMOSトランジスタと、

ドレインが前記第2PMOSトランジスタのドレインに接続され、ソースが接地され、ゲートに第3バイアス電圧が供給される第1NMOSトランジスタと、

前記第2PMOSトランジスタを飽和領域で動作させ、かつ前記第1PMOSトランジスタのドレインと前記第2PMOSトランジスタのソースとの接続点が前記入力端の基準電圧に保たれるように調整された第2バイアス電圧を第2PMOSトランジスタのゲートに供給するバイアス電圧供給部と、

10

を含むデータ読出回路。

## 【請求項 2】

前記バイアス電圧供給部は、前記入力端の基準電圧  $V_{BLREF}$  がソースに供給され、ゲートが前記第2PMOSトランジスタのゲートに接続されると共にドレインと短絡された第3PMOSトランジスタと、前記第3PMOSトランジスタのドレインに接続された定電流源と、を備え、前記第2PMOSトランジスタと前記第3PMOSトランジスタに電流ミラーが成り立ち、前記第1PMOSトランジスタの閾値電圧を  $V_{TP}$ 、前記第1バ

20

バイアス電圧を  $V_{BIA SP}$  としたときに、

$$V_{BLREF} < V_{BIA SP} + |V_{TP}|$$

が成り立つ第2バイアス電圧を前記第2PMOSトランジスタのゲートに供給するように構成されている請求項1記載のデータ読出回路。

**【請求項3】**

ソースが電源に接続され、ゲートに第1バイアス電圧が供給され、線形領域で動作するように構成された第1PMOSトランジスタと、

ソースが前記第1PMOSトランジスタのドレインに接続され、ゲートに第2バイアス電圧が供給され、ドレインが出力端に接続され、飽和領域で動作するように構成された第2PMOSトランジスタと、

10

ドレインが前記第2PMOSトランジスタのドレインに接続され、ソースが接地され、ゲートに第3バイアス電圧が供給され、飽和領域で動作するように構成された第1NMOSトランジスタと、

ソースが前記第1PMOSトランジスタのドレインに接続され、データ読出対象のメモリセルが接続される入力端にドレインが接続された第4PMOSトランジスタと、

前記入力端の基準電圧が入力され、前記第4PMOSトランジスタのドレインが前記入力端の基準電圧に保たれるように前記第4PMOSトランジスタに接続された差動増幅部と、

を含むデータ読出回路。

**【請求項4】**

20

ソースが電源に接続され、ゲートに第1バイアス電圧が供給され、線形領域で動作するように構成された第1PMOSトランジスタと、

ソースが前記第1PMOSトランジスタのドレインに接続され、ゲートに第2バイアス電圧が供給され、ドレインが出力端に接続され、飽和領域で動作するように構成された第2PMOSトランジスタと、

ドレインが前記第2PMOSトランジスタのドレインに接続され、ソースが接地され、ゲートに第3バイアス電圧が供給され、飽和領域で動作するように構成された第1NMOSトランジスタと、

ドレインが前記第1PMOSトランジスタのドレインに接続され、データ読出対象のメモリセルが接続される入力端にソースが接続された第2NMOSトランジスタと、

30

前記入力端の基準電圧が入力され、前記第2NMOSトランジスタのソースが前記入力端の基準電圧に保たれるように前記第2NMOSトランジスタに接続された差動増幅部と、

を含むデータ読出回路。

**【請求項5】**

第1PMOSトランジスタの閾値電圧を  $V_{TP}$ 、前記第1バイアス電圧を  $V_{BIA SP}$ 、前記第1PMOSトランジスタのドレインと前記第2PMOSトランジスタのソースが接続されたノードBLAの電圧を  $V_{BLA}$  としたときに、

$$V_{BLA} > V_{BIA SP} + |V_{TP}|$$

が成り立つ前記第1バイアス電圧が前記第1PMOSトランジスタに供給される請求項3又は請求項4記載のデータ読出回路。

40

**【請求項6】**

前記第1PMOSトランジスタのゲートが前記出力端に接続されている請求項3～請求項5の何れか1項記載のデータ読出回路。

**【請求項7】**

前記第1PMOSトランジスタ及び前記第2PMOSトランジスタのゲートが前記出力端に接続されている請求項3～請求項5の何れか1項記載のデータ読出回路。

**【請求項8】**

データを保持可能なメモリセルが複数設けられたメモリセルアレイと、

第1入力端に入力された第1電圧と第2入力端に入力された第2電圧を比較し、比較結

50

果を出力する比較回路と、

請求項 1 ~ 請求項 6 の何れか 1 項記載のデータ読出回路から成り、前記入力端がデータ読出対象のメモリセルに接続され、前記出力端が前記比較回路の前記第 1 入力端に接続されたデータ読出部と、

請求項 1 ~ 請求項 6 の何れか 1 項記載のデータ読出回路から成り、前記出力端が前記比較回路の前記第 2 入力端に接続された参照電圧供給部と、

を備えた半導体記憶装置。

#### 【請求項 9】

データを保持可能なメモリセルが複数設けられたメモリセルアレイと、

第 1 入力端に入力された第 1 電圧と第 2 入力端に入力された第 2 電圧を比較し、比較結果を出力する比較回路と、10

請求項 3 ~ 請求項 6 の何れか 1 項記載のデータ読出回路から成り、前記入力端がデータ読出対象のメモリセルに接続され、前記出力端が前記比較回路の前記第 1 入力端に接続されたデータ読出部と、

請求項 7 記載のデータ読出回路から成り、前記出力端が前記比較回路の前記第 2 入力端及び前記データ読出回路の前記第 2 PMOS トランジスタのゲートに各々接続された参照電圧供給部と、

を備えた半導体記憶装置。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

本発明はデータ読出回路及び半導体記憶装置に係り、特に、データ読出対象のメモリセルからデータを読み出すデータ読出回路、及び、該データ読出回路を備えた半導体記憶装置に関する。

##### 【背景技術】

##### 【0002】

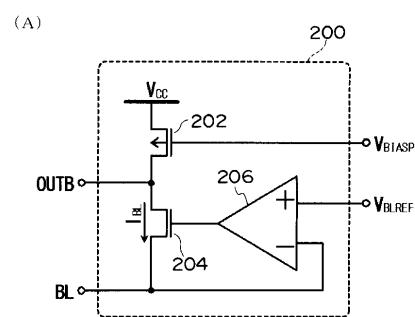

E PROM 等の半導体メモリセルからのデータの読み出しに関し、特許文献 1 には、半導体メモリセルに接続されたデータ線に定電圧を印加すると共に、前記データ線を定電圧に維持するのに要する電流を検出する機能を備えたセンスアンプ回路（電流ソース型のセンスアンプ回路）が開示されている。例として図 15 (A) に示すように、特許文献 1 に開示されているセンスアンプ回路 200 は、ソースが電源 Vcc に接続されゲートにはバイアス電圧入力端を介してバイアス電圧  $V_{BIA SP}$  が供給されドレインが出力端 OUTB に接続された PMOS トランジスタ 202 と、ドレインが PMOS トランジスタ 202 のドレインに接続されソースが入力端 BL に接続された NMOS トランジスタ 204 と、反転入力端が NMOS トランジスタ 204 のドレインに接続され非反転入力端には基準電圧入力端を介して基準電圧  $V_{BLREF}$  が供給され出力端が NMOS トランジスタ 204 のゲートに接続されたオペアンプ 206 と、から構成されている。30

##### 【0003】

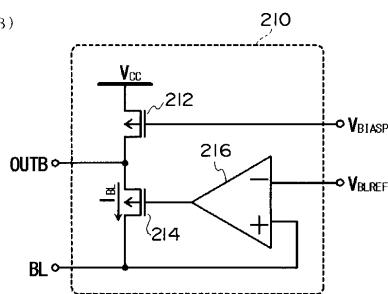

なお、センスアンプ回路 200 と同様の機能は、図 15 (B) に示すように、ソースが電源 Vcc に接続されゲートにはバイアス電圧入力端を介してバイアス電圧  $V_{BIA SP}$  が供給されドレインが出力端 OUTB に接続された PMOS トランジスタ 212 と、ソースが PMOS トランジスタ 212 のドレインに接続されドレインが入力端 BL に接続された PMOS トランジスタ 214 と、非反転入力端が PMOS トランジスタ 214 のドレインに接続され反転入力端には基準電圧入力端を介して基準電圧  $V_{BLREF}$  が供給され出力端が PMOS トランジスタ 214 のゲートに接続されたオペアンプ 216 と、から成るセンスアンプ回路 210 によっても実現できる。40

##### 【0004】

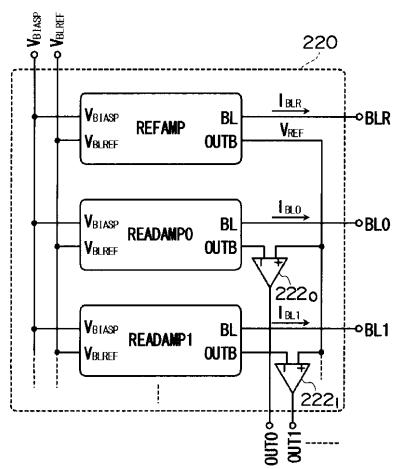

センスアンプ回路 200 は図 16 に示すアンプブロック回路 220 における読出用センスアンプ回路 READAMPn ( $n = 0, 1, \dots$ ) や参照用センスアンプ回路 REFAMP として各々用いられることで、半導体メモリセルからデータを読み出可能に半導体メモリセルと接続される。す50

なわち、個々のセンスアンプ回路200にはバイアス電圧入力端に接続されたバイアス電圧供給線を介してバイアス電圧 $V_{BIAS}$ が各々供給されると共に、基準電圧入力端に接続された基準電圧供給線を介して基準電圧 $V_{REF}$ が各々供給される。また、読出用センスアンプ回路READAMPnを構成するセンスアンプ回路200は、入力端BLがビット線(データ線)BLnを介して半導体メモリセルのドレイン端子に接続されており、出力端OUTBがオペアンプ222nの反転入力端に接続されている。また、参照用センスアンプ回路REFAMPを構成するセンスアンプ回路200は、入力端BLに基準流出電流 $I_{BLR}$ が流れ、出力端OUTBが各オペアンプ222nの非反転入力端に各々接続されている。なお、センスアンプ回路200に代えて、読出用センスアンプ回路READAMPnや参照用センスアンプ回路REFAMPをセンスアンプ回路210で構成することも可能である。

10

#### 【0005】

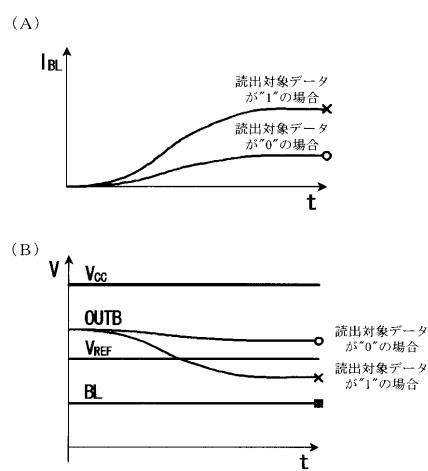

半導体メモリセルからデータを読み出す場合、半導体メモリセルのドレイン端子を一定電圧に保つことが一般的である。センスアンプ回路200, 210では、オペアンプ206, 216が差動增幅回路として動作することで、入力端BLに接続されたビット線BLnの電圧がオペアンプ206, 216に供給されている基準電圧 $V_{REF}$ に保たれ、ビット線BLnに接続された半導体メモリセルのドレイン端子も基準電圧 $V_{REF}$ に準ずる電圧に保たれる。また、半導体メモリセルからのデータ読出時には入力端BLからビット線BLnへ電流が流出し、この電流流出に伴って出力端OUTBからの出力電圧が低下するが、出力電圧の低下量はビット線BLnへの流出電流 $I_{BL}$ の大きさに応じて変化し、流出電流 $I_{BL}$ の大きさは、例として図17(A)にも示すように、読出対象の半導体メモリセルに保持されているデータ(読出対象データ)が"0"か"1"かに応じて相違する。

20

#### 【0006】

アンプロック回路220の参照用センスアンプ回路REFAMPは、読出対象データが"0"の場合と"1"の場合の流出電流 $I_{BL}$ の大きさ(出力電圧の低下量)を識別するために設けられており、例として図17(B)にも示すように、出力端OUTBからの出力電圧(各オペアンプ222nに入力される基準電圧 $V_{REF}$ )が、読出対象データが"0"の場合の低下後の出力電圧と"1"の場合の低下後の出力電圧の中間に相当する大きさとなるように構成されている。なお、図17(B)では出力端OUTBの電圧を"OUTB"と表記して示すと共に、ビット線の電圧を"BL"と表記して示しているが、ビット線の電圧は読出対象データが"0"の場合と"1"の場合とで殆ど差が生じないため、読出対象データが"0"の場合と"1"の場合を重ねて示している。

30

#### 【0007】

上記のように、基準電圧 $V_{REF}$ を前記中間に相当する大きさとすることは、例えば参照用センスアンプ回路REFAMPの入力端BLを流れる基準流出電流 $I_{BLR}$ を、読出対象データが"1"の場合の流出電流 $I_{BL}$ と読出対象データが"0"の場合の流出電流 $I_{BL}$ の中間に相当する大きさとすることで実現できる。これにより、差動増幅器として動作する各オペアンプ222nからの出力に基づいて、読出対象データが"0"か"1"かを判別することができる。

#### 【特許文献1】特許第2513795号公報

##### 【発明の開示】

40

##### 【発明が解決しようとする課題】

#### 【0008】

ところで、センスアンプ回路200, 210では、前述のようにビット線BLへの流出電流 $I_{BL}$ が大きくなるに従って出力端OUTBからの出力電圧が大きく低下するので、出力電圧の電圧利得を大きくするためにセンスアンプ回路200のPMOSトランジスタ202やNMOSトランジスタ204、センスアンプ回路210のPMOSトランジスタ212, 214は飽和領域を動作領域に含むことが望ましい。

#### 【0009】

ここで、センスアンプ回路200において、PMOSトランジスタ202のソース-ドレイン間電圧を $V_{SDP}$ 、PMOSトランジスタ202の閾値電圧を $V_{TP}$ 、NMOSト

50

ランジスタ204のドレイン - ソース間電圧を $V_{DSN}$ 、NMOSトランジスタ204のゲート - ソース間電圧 $V_{GSN}$ 、NMOSトランジスタ204の閾値電圧を $V_{TN}$ とすると、センスアンプ回路200のPMOSトランジスタ202及びNMOSトランジスタ204を飽和領域で動作させることは、PMOSトランジスタ202については次の(1)式を満足し、NMOSトランジスタ204については次の(2)式を満足するように動作させることで実現できる。

$$V_{SDP} > V_{CC} - V_{BIASP} - |V_{TP}| \quad \dots(1)$$

$$V_{DSN} > V_{GSN} - V_{TN} \quad \dots(2)$$

上記の(1),(2)式より、

$$V_{SDP} + V_{DSN} > V_{CC} - V_{BIASP} - |V_{TP}| + V_{GSN} - V_{TN} \quad \dots(3)$$

上記の(3)式が得られる。また、PMOSトランジスタ202とNMOSトランジスタ204は電源 $V_{CC}$ と入力端BL(ビット線BLn)の間に直列に接続されており、ビット線BLnの電圧は基準電圧 $V_{BLREF}$ に保たれていることから、

$$V_{CC} - V_{BLREF} = V_{SDP} + V_{DSN} \quad \dots(4)$$

上記の(4)式が成り立つ。(3),(4)式より、

$$V_{BLREF} < V_{BIASP} + |V_{TP}| - V_{GSN} + V_{TN} \quad \dots(5)$$

である。従って、センスアンプ回路200では(5)式を満足すればPMOSトランジスタ202及びNMOSトランジスタ204を飽和領域で動作させることができ、これは通常、バイアス電圧 $V_{BIASP}$ などを調整することで実現できるが、電源 $V_{CC}$ が比較的低い電圧であったり基準電圧 $V_{BLREF}$ が比較的高い電圧である場合は(5)式を満たすことが困難となる。その結果、PMOSトランジスタ202やNMOSトランジスタ204が飽和領域で動作できず利得が低下したり、ビット線の電圧を基準電圧 $V_{BLREF}$ に保てない等、致命的な不具合が生じる。

#### 【0010】

また、センスアンプ回路210において、PMOSトランジスタ212のソース - ドレイン間電圧を $V_{SDP1}$ 、PMOSトランジスタ212のソース - ゲート間電圧を $V_{SGP1}$ 、PMOSトランジスタ214のソース - ドレイン間電圧を $V_{SDP2}$ 、PMOSトランジスタ214のソース - ゲート間電圧を $V_{SGP2}$ とすると、センスアンプ回路210のPMOSトランジスタ212, 214を飽和領域で動作させることは、PMOSトランジスタ212については次の(6)式を満足し、PMOSトランジスタ214については次の(7)式を満足するように動作させることで実現できる。

$$V_{SDP1} > V_{CC} - V_{BIASP} - |V_{TP}| \quad \dots(6)$$

$$V_{SDP2} > V_{SGP2} - |V_{TP}| \quad \dots(7)$$

上記の(6),(7)式より、

$$V_{SDP1} + V_{SDP2} > V_{CC} - V_{BIASP} - |V_{TP}| + V_{SGP2} - |V_{TP}| \quad \dots(8)$$

上記の(8)式が得られる。また、PMOSトランジスタ212, 214は電源 $V_{CC}$ と入力端BL(ビット線BLn)の間に直列に接続されており、ビット線BLnの電圧は基準電圧 $V_{BLREF}$ に保たれていることから、

$$V_{CC} - V_{BLREF} = V_{SDP1} + V_{SDP2} \quad \dots(9)$$

上記の(9)式が成り立つ。(8),(9)式より、

$$V_{BLREF} < V_{BIASP} + 2|V_{TP}| - V_{SGP2} \quad \dots(10)$$

である。従って、センスアンプ回路210では(10)式を満足すればPMOSトランジスタ212, 214を飽和領域で動作させることができ、これは通常、バイアス電圧 $V_{BIASP}$ などを調整することで実現できるが、センスアンプ回路200と同様、電源 $V_{CC}$ が比較的低い電圧であったり基準電圧 $V_{BLREF}$ が比較的高い電圧である場合は(10)式を満たすことが困難となる。その結果、PMOSトランジスタ212, 214が飽和領域で動作できず利得が低下したり、ビット線BLの電圧を基準電圧 $V_{BLREF}$ に保てない等、致命的な不具合が生じる。

#### 【0011】

本発明は上記事実を考慮して成されたもので、利得が低下することなく入力端の電圧を

10

20

30

40

50

基準電圧に保ってメモリセルからデータを読み出すことを、電源電圧がより低い、或いは入力端の基準電圧がより高い条件でも実現できるデータ読出回路及び半導体記憶装置を得ることが目的である。

【課題を解決するための手段】

【0012】

上記目的を達成するために請求項1記載の発明に係るデータ読出回路は、ソースが電源に接続され、データ読出対象のメモリセルが接続される入力端にドレインが接続され、ゲートに第1バイアス電圧が供給され、飽和領域で動作するよう構成された第1PMOSトランジスタと、ソースが前記第1PMOSトランジスタのドレインに接続され、ドレインが出力端に接続され、ゲートに第2バイアス電圧が供給される第2PMOSトランジスタと、ドレインが前記第2PMOSトランジスタのドレインに接続され、ソースが接地され、ゲートに第3バイアス電圧が供給される第1NMOSトランジスタと、前記第2PMOSトランジスタを飽和領域で動作させ、かつ前記第1PMOSトランジスタのドレインと前記第2PMOSトランジスタのソースとの接続点が前記入力端の基準電圧に保たれるように調整された第2バイアス電圧を第2PMOSトランジスタのゲートに供給するバイアス電圧供給部と、を含んで構成されている。10

【0013】

請求項2記載の発明は、請求項1記載の発明において、前記バイアス電圧供給部は、前記入力端の基準電圧  $V_{BLREF}$  がソースに供給され、ゲートが前記第2PMOSトランジスタのゲートに接続されると共にドレインと短絡された第3PMOSトランジスタと、前記第3PMOSトランジスタのドレインに接続された定電流源と、を備え、前記第2PMOSトランジスタと前記第3PMOSトランジスタに電流ミラーが成り立ち、前記第1PMOSトランジスタの閾値電圧を  $V_{TP}$  、前記第1バイアス電圧を  $V_{BIASP}$  としたときに、20

$$V_{BLREF} < V_{BIASP} + |V_{TP}|$$

が成り立つ第2バイアス電圧を前記第2PMOSトランジスタのゲートに供給するように構成されている。

【0014】

請求項3記載の発明に係るデータ読出回路は、ソースが電源に接続され、ゲートに第1バイアス電圧が供給され、線形領域で動作するよう構成された第1PMOSトランジスタと、ソースが前記第1PMOSトランジスタのドレインに接続され、ゲートに第2バイアス電圧が供給され、ドレインが出力端に接続され、飽和領域で動作するよう構成された第2PMOSトランジスタと、ドレインが前記第2PMOSトランジスタのドレインに接続され、ソースが接地され、ゲートに第3バイアス電圧が供給され、飽和領域で動作するよう構成された第1NMOSトランジスタと、ソースが前記第1PMOSトランジスタのドレインに接続され、データ読出対象のメモリセルが接続される入力端にドレインが接続された第4PMOSトランジスタと、前記入力端の基準電圧が入力され、前記第4PMOSトランジスタのドレインが前記入力端の基準電圧に保たれるよう前記第4PMOSトランジスタに接続された差動増幅部と、を含んで構成されている。30

【0015】

請求項4記載の発明に係るデータ読出回路は、ソースが電源に接続され、ゲートに第1バイアス電圧が供給され、線形領域で動作するよう構成された第1PMOSトランジスタと、ソースが前記第1PMOSトランジスタのドレインに接続され、ゲートに第2バイアス電圧が供給され、ドレインが出力端に接続され、飽和領域で動作するよう構成された第2PMOSトランジスタと、ドレインが前記第2PMOSトランジスタのドレインに接続され、ソースが接地され、ゲートに第3バイアス電圧が供給され、飽和領域で動作するよう構成された第1NMOSトランジスタと、ドレインが前記第1PMOSトランジスタのドレインに接続され、データ読出対象のメモリセルが接続される入力端にソースが接続された第2NMOSトランジスタと、前記入力端の基準電圧が入力され、前記第2NMOSトランジスタのソースが前記入力端の基準電圧に保たれるよう前記第2NMOS4050

トランジスタに接続された差動増幅部と、を含んで構成されている。

**【0016】**

請求項5記載の発明は、請求項3又は請求項4記載の発明において、第1PMOSトランジスタの閾値電圧を $V_{TP}$ 、前記第1バイアス電圧を $V_{BIASP}$ 、前記第1PMOSトランジスタのドレインと前記第2PMOSトランジスタのソースが接続されたノードBLAの電圧を $V_{BLA}$ としたときに、

$$V_{BLA} > V_{BIASP} + |V_{TP}|$$

が成り立つ前記第1バイアス電圧が前記第1PMOSトランジスタに供給される。

**【0017】**

請求項6記載の発明は、請求項3～請求項5の何れかに記載の発明において、前記第1PMOSトランジスタのゲートが前記出力端に接続されている。 10

**【0018】**

請求項7記載の発明は、請求項3～請求項5の何れかに記載の発明において、前記第1PMOSトランジスタ及び前記第2PMOSトランジスタのゲートが前記出力端に接続されている。

**【0019】**

請求項8記載の発明に係る半導体記憶装置は、データを保持可能なメモリセルが複数設けられたメモリセルアレイと、第1入力端に入力された第1電圧と第2入力端に入力された第2電圧を比較し、比較結果を出力する比較回路と、請求項1～請求項6の何れか1項記載のデータ読出回路から成り、前記入力端がデータ読出対象のメモリセルに接続され、前記出力端が前記比較回路の前記第1入力端に接続されたデータ読出部と、請求項1～請求項6の何れか1項記載のデータ読出回路から成り、前記出力端が前記比較回路の前記第2入力端に接続された参照電圧供給部と、を備えている。 20

**【0020】**

請求項9記載の発明に係る半導体記憶装置は、データを保持可能なメモリセルが複数設けられたメモリセルアレイと、第1入力端に入力された第1電圧と第2入力端に入力された第2電圧を比較し、比較結果を出力する比較回路と、請求項3～請求項6の何れか1項記載のデータ読出回路から成り、前記入力端がデータ読出対象のメモリセルに接続され、前記出力端が前記比較回路の前記第1入力端に接続されたデータ読出部と、請求項7記載のデータ読出回路から成り、前記出力端が前記比較回路の前記第2入力端及び前記データ読出回路の前記第2PMOSトランジスタのゲートに各々接続された参照電圧供給部と、を備えている。 30

**【発明の効果】**

**【0021】**

本発明は、利得が低下することなく入力端の電圧を基準電圧に保ってメモリセルからデータを読み出すことを、電源電圧がより低い、或いは入力端の基準電圧がより高い条件でも実現できる、という優れた効果を有する。

**【発明を実施するための最良の形態】**

**【0022】**

以下、図面を参照して本発明の実施形態の一例を詳細に説明する。 40

**【0023】**

**〔第1実施形態〕**

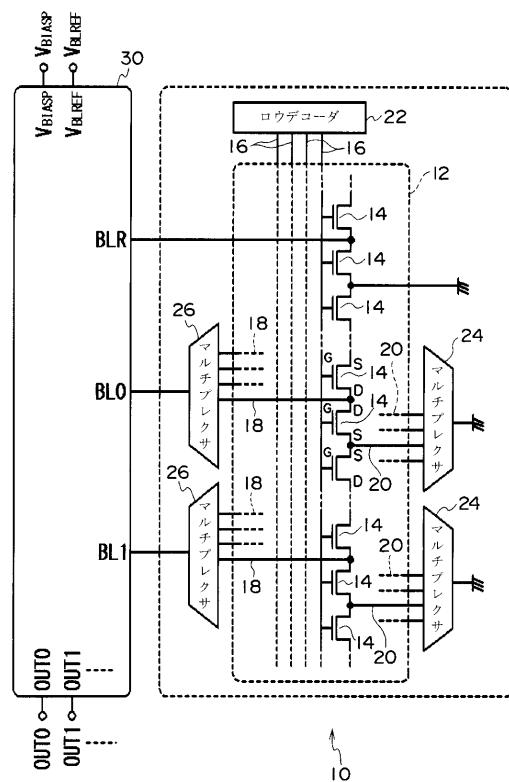

図3には本実施形態に係るMOS型半導体記憶装置10が示されている。MOS型半導体記憶装置10は、多数個のメモリセル14がマトリクス状に配列されると共に、メモリセル14の行方向に沿って延びるワード線16が複数本配設され、更にメモリセル14の列方向に沿って延びるビット線18及びソース線20も各々複数本配設された構成のメモリセルアレイ12を備えている。

**【0024】**

図3では、一部のメモリセル14についてのみドレインを"D"、ソースを"S"、ゲートを"G"と表記して示すが、この表記からも明らかのように、個々のメモリセル14は、行 50

方向に沿って隣合う一対のメモリセル14のうちの一方のメモリセル14とドレイン同士が接続されていると共に、前記一対のメモリセル14のうちの他方のメモリセル14とソース同士が接続されている。隣合うメモリセル14のドレイン同士を接続するノードには複数本のビット線18のうちの何れかが各々接続されており、隣合うメモリセル14のソース同士を接続するノードには複数本のソース線20のうちの何れかが各々接続されている。また図3に示すように、行方向に沿って並ぶ複数のメモリセル14のゲートが複数本のワード線16のうちの同一のワード線16に接続されるように、個々のメモリセル14のゲートがワード線16に各々接続されている。

#### 【0025】

メモリセルアレイ12に配設された複数本のワード線16はロウデコーダ22に各々接続されている。ロウデコーダ22にはメモリセルアレイ12からのデータ読出時にデータ読出対象のメモリセル14の行アドレスが外部から入力され、ロウデコーダ22は、複数本のワード線16のうち入力された行アドレスに対応する单一のワード線16を選択電圧を供給する。また、メモリセルアレイ12に配設された複数本のソース線20は、複数設けられたマルチプレクサ24のうちの何れかのマルチプレクサ24の入力端に各々接続されている。各マルチプレクサ24は出力端が接地端子に各々接続されており、メモリセルアレイ12からのデータ読出時に外部から入力される選択信号に従い、データ読出対象のメモリセル14のソースに接続されたソース線20を接地端子に接続させる。また、メモリセルアレイ12に配設された複数本のビット線18は複数設けられたマルチプレクサ26のうちの何れかのマルチプレクサ26の入力端に各々接続されている。各マルチプレクサ26は出力端がアンプブロック回路30のビット線接続端BLnに接続されており、メモリセルアレイ12からのデータ読出時に外部から入力される選択信号に従い、データ読出対象のメモリセル14のドレインに接続されたビット線18をアンプブロック回路30のビット線接続端BLnに接続させる。

#### 【0026】

詳細は後述するが、アンプブロック回路30は、メモリセルアレイ12からのデータ読出時に、ビット線接続端BLnに接続されたビット線18に一定電圧を供給する。従って、メモリセルアレイ12からのデータ読出時には、データ読出対象のメモリセル14は、ゲートに選択電圧(例えば5V程度)が与えられ、ソースが接地電位(例えば0V)とされ、ドレインに一定電圧(例えば1.2V程度)が与えられ、これに伴ってデータ読出対象のメモリセル14のドレイン-ソース間に電流(後述する流出電流 $I_{BL}$ )が流れる。

#### 【0027】

この電流の大きさはデータ読出対象のメモリセル14のフローティングゲート内に過剰電子が存在しているか否かに応じて相違し、フローティングゲートに過剰電子が存在していない場合(すなわちデータ読出対象のメモリセル14に保持されている読出対象データが"1"の場合)には、フローティングゲートに過剰電子が存在している場合(すなわちデータ読出対象のメモリセル14に保持されている読出対象データが"0"の場合)よりも上記電流の大きさが大きくなる。このため、アンプブロック回路30は、メモリセルアレイ12からのデータ読出時に、ビット線接続端BLnに接続されたビット線18を流れる電流(流出電流 $I_{BL}$ )の大きさに基づいて、データ読出対象のメモリセル14に保持されている読出対象データが"0"か"1"かを判定している。

#### 【0028】

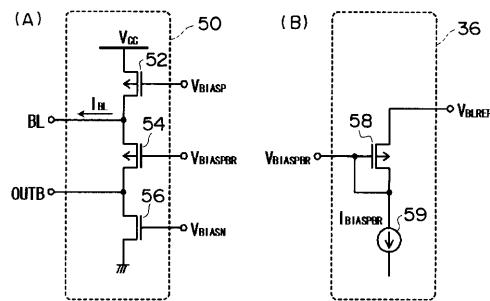

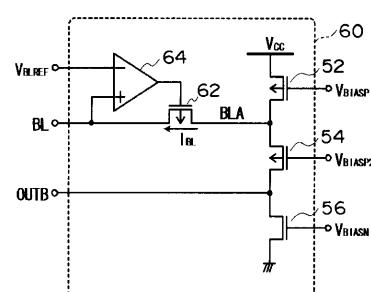

次にアンプブロック回路30の説明に先立ち、アンプブロック回路30を構成するセンスアンプ回路50及び電圧生成回路36を説明する。本第1実施形態に係るセンスアンプ回路50は電流ソース型のセンスアンプ回路であり、図1(A)に示すように、ソースが電源Vccに接続されゲートが第1バイアス電圧入力端に接続されドレインが入力端BLに接続されたPMOSトランジスタ52を備えている。PMOSトランジスタ52のゲートには第1バイアス電圧入力端を介してバイアス電圧 $V_{BIAS_P}$ が供給される。なお、本第1実施形態ではPMOSトランジスタ52が飽和領域で動作するように、バイアス電圧 $V_{BIAS_P}$ の大きさやPMOSトランジスタ52の特性が調整されている。

10

20

30

40

50

## 【0029】

また、PMOSトランジスタ52のドレインにはPMOSトランジスタ54のソースが接続されており、PMOSトランジスタ54は、ゲートが第2バイアス電圧入力端に接続され、ドレインが出力端OUTBに接続されている。PMOSトランジスタ54のゲートには第2バイアス電圧入力端を介してバイアス電圧 $V_{BIASPB_R}$ が供給される。本第1実施形態ではPMOSトランジスタ54が飽和領域で動作すると共に、PMOSトランジスタ54のソース-ドレイン間の電流 $I_{SD}$ を規定する次の(11)式において(但し、 $V_{SG_P}$ はPMOSトランジスタ54のソース-ドレイン間電圧、 $V_{TP}$ はPMOSトランジスタ54の閾値電圧、Kはトランスクンダクタンス係数)、

$$I_{SD} = K (V_{SG_P} - |V_{TP}|)^2 \quad \dots(11)$$

10

トランスクンダクタンス係数Kの値が所定値以上になるように、バイアス電圧 $V_{BIASPB_R}$ の大きさやPMOSトランジスタ54の特性が調整されている。

## 【0030】

また、PMOSトランジスタ54のドレインにはNMOSトランジスタ56のドレインが接続されており、NMOSトランジスタ56は、ゲートが第3バイアス電圧入力端に接続され、ソースが接地端子に接続されている。NMOSトランジスタ56のゲートには第3バイアス電圧入力端を介してバイアス電圧 $V_{BIASN}$ が供給される。本第1実施形態では、NMOSトランジスタ56が線形領域で動作するようにバイアス電圧 $V_{BIASN}$ の大きさやNMOSトランジスタ56の特性が調整されている。

## 【0031】

20

また、図1(B)に示すように、本第1実施形態に係る電圧生成回路36は、ドレインが基準電圧入力端に接続されたPMOSトランジスタ58を備えており、このPMOSトランジスタ58は、ゲートがバイアス電圧出力端に接続され、ドレインがゲートに接続されると共に、一定電流 $I_{BIASPB_R}$ を発生する定電流源59に接続されている。

## 【0032】

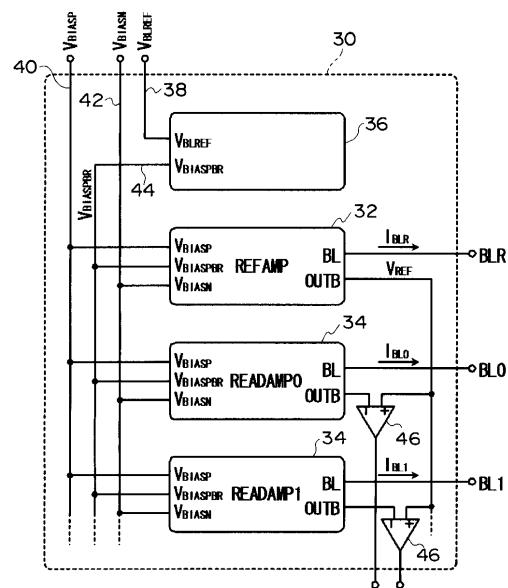

図2に示すように、本第1実施形態に係るアンプブロック回路30は、各々センスアンプ回路50によって構成される単一の参照用センスアンプ回路32及び複数の読み出用センスアンプ回路34を各々備えると共に、電圧生成回路36も備えている。電圧生成回路36の基準電圧入力端は基準電圧供給線38に接続されており、図示しない外部回路から基準電圧供給線38を介して基準電圧 $V_{BLREF}$ が供給される。

30

## 【0033】

また、参照用センスアンプ回路32及び個々の読み出用センスアンプ回路34の第1バイアス電圧入力端は第1バイアス電圧供給線40に各々接続されており、図示しない外部回路から第1バイアス電圧供給線40を介してバイアス電圧 $V_{BIAS_P}$ が各々供給される(このバイアス電圧 $V_{BIAS_P}$ は、参照用センスアンプ回路32及び個々の読み出用センスアンプ回路34を構成するセンスアンプ回路50のPMOSトランジスタ52のゲートに各々供給される)。また、参照用センスアンプ回路32及び個々の読み出用センスアンプ回路34の第3バイアス電圧入力端は第3バイアス電圧供給線42に各々接続されており、図示しない外部回路から第3バイアス電圧供給線42を介してバイアス電圧 $V_{BIAS_N}$ が各々供給される(このバイアス電圧 $V_{BIAS_N}$ は、参照用センスアンプ回路32及び個々の読み出用センスアンプ回路34を構成するセンスアンプ回路50のNMOSトランジスタ56のゲートに各々供給される)。

40

## 【0034】

また、参照用センスアンプ回路32及び個々の読み出用センスアンプ回路34の第2バイアス電圧入力端は第2バイアス電圧供給線44に各々接続されており、この第2バイアス電圧供給線44は電圧生成回路36のバイアス電圧出力端に接続されている。参照用センスアンプ回路32及び個々の読み出用センスアンプ回路34の第2バイアス電圧入力端には、電圧生成回路36から第2バイアス電圧供給線44を介してバイアス電圧 $V_{BIASPB_R}$ が各々供給される(このバイアス電圧 $V_{BIASPB_R}$ は、参照用センスアンプ回路32及び個々の読み出用センスアンプ回路34を構成するセンスアンプ回路50のPMOS

50

トランジスタ 5 4 のゲートに各々供給される)。

**【 0 0 3 5 】**

また、個々の読出用センスアンプ回路 3 4 の入力端BLは、複数のマルチブレクサ 2 6 のうち互いに異なるマルチブレクサ 2 6 の出力端に接続されている。従って、メモリセルアレイ 1 2 からのデータ読出時には、個々の読出用センスアンプ回路 3 4 の入力端BLには、マルチブレクサ 2 6 を介して個々の読出用センスアンプ回路 3 4 と接続されたデータ読出対象のメモリセル 1 4 に保持されている読出対象データの値("0"又は"1")に応じた大きさの流出電流  $I_{B\ L\ n}$  が流れる。一方、参照用センスアンプ回路 3 2 の入力端BLは、図 3 に示すように、メモリセルアレイ 1 2 の特定メモリセル 1 4 のドレインに固定的に接続されている。この特定メモリセル 1 4 はソースが接地されており、メモリセルアレイ 1 2 からのデータ読出時には、参照用センスアンプ回路 3 2 の入力端BLに一定の流出電流(基準流出電流  $I_{B\ L\ R}$ )が流れる。

10

**【 0 0 3 6 】**

更に、アンプブロック回路 3 0 は読出用センスアンプ回路 3 4 と同数のオペアンプ 4 6 を備えており、個々の読出用センスアンプ回路 3 4 の出力端OUTBは、互いに異なるオペアンプ 4 6 の反転入力端に接続されている。また、参照用センスアンプ回路 3 2 の出力端OUTBは個々のオペアンプ 4 6 の非反転入力端に各々接続されており、個々のオペアンプ 4 6 の非反転入力端には参照用センスアンプ回路 3 2 の出力端OUTBから出力された基準電圧  $V_{R\ E\ F}$  が各々供給される。

20

**【 0 0 3 7 】**

なお、センスアンプ回路 5 0 及び電圧生成回路 3 6 は請求項 1 記載のデータ読出回路に対応しており、詳しくは、センスアンプ回路 5 0 のPMOSトランジスタ 5 2 は請求項 1 に記載の第 1 PMOSトランジスタに、PMOSトランジスタ 5 4 は請求項 1 に記載の第 2 PMOSトランジスタに、NMOSトランジスタ 5 6 は請求項 1 に記載の第 1 NMOSトランジスタに、電圧生成回路 3 6 は請求項 1 (より詳しくは請求項 2 ) に記載のバイアス電圧供給部に各々対応している。また、PMOSトランジスタ 5 2 のゲートに供給されるバイアス電圧  $V_{B\ I\ A\ S\ P}$  は請求項 1 に記載の第 1 バイアス電圧に、PMOSトランジスタ 5 4 のゲートに供給されるバイアス電圧  $V_{B\ I\ A\ S\ P\ B\ R}$  は請求項 1 に記載の第 2 バイアス電圧に、NMOSトランジスタ 5 6 のゲートに供給されるバイアス電圧  $V_{B\ I\ A\ S\ N}$  は請求項 1 に記載の第 3 バイアス電圧に各々対応している。更に、電圧生成回路 3 6 のPMOSトランジスタ 5 8 は請求項 2 に記載の第 3 PMOSトランジスタに、定電流源 5 9 は請求項 2 に記載の定電流源に各々対応している。

30

**【 0 0 3 8 】**

また、本第 1 実施形態に係るアンプブロック回路 3 0 を含むMOS型半導体記憶装置 1 0 は請求項 8 に記載の半導体記憶装置に対応しており、メモリセルアレイ 1 2 が請求項 8 に記載のメモリセルアレイに、オペアンプ 4 6 が請求項 8 に記載の比較回路に、センスアンプ回路 5 0 から成る読出用センスアンプ回路 3 4 が請求項 8 に記載のデータ読出部に、同じくセンスアンプ回路 5 0 から成る参照用センスアンプ回路 3 2 が請求項 8 に記載の参照電圧供給部に各々対応している。

40

**【 0 0 3 9 】**

次に本第 1 実施形態の作用として、メモリセルアレイ 1 2 からのデータ読出時の、センスアンプ回路 5 0 及び電圧生成回路 3 6 の動作を説明する。参照用センスアンプ回路 3 2 及び個々の読出用センスアンプ回路 3 4 を構成する個々のセンスアンプ回路 5 0 は、入力端BLがメモリセル 1 4 のドレインに接続されるので、メモリセル 1 4 からデータを読み出すためには、個々のセンスアンプ回路 5 0 の入力端BLを基準電圧  $V_{B\ L\ R\ E\ F}$  に保ち、個々のセンスアンプ回路 5 0 に接続されたメモリセル 1 4 のドレインに基準電圧  $V_{B\ L\ R\ E\ F}$  を与える必要がある。これに対して本第 1 実施形態では、個々のセンスアンプ回路 5 0 における流出電流  $I_{B\ L\ n} = 0$  のとき、電圧生成回路 3 6 のPMOSトランジスタ 5 8 と個々のセンスアンプ回路 5 0 のPMOSトランジスタ 5 4 に電流ミラーが成り立つよう、電圧生成回路 3 6 の定電流源 5 9 が発生する一定電流  $I_{B\ I\ A\ S\ P\ B\ R}$  の大きさや、

50

電圧生成回路36のPMOSトランジスタ58の特性が調整されている。これにより、電圧生成回路36のPMOSトランジスタ58と個々のセンスアンプ回路50のPMOSトランジスタ54に電流ミラーが成り立ち、個々のセンスアンプ回路50における流出電流 $I_{BLn} = 0$ のときの入力端BLの電圧は基準電圧 $V_{BLREF}$ に等しくなる。

#### 【0040】

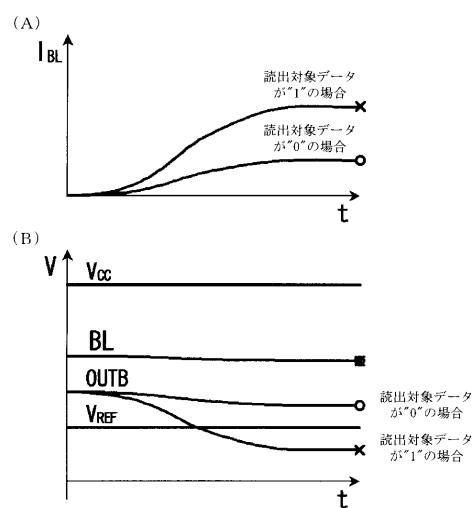

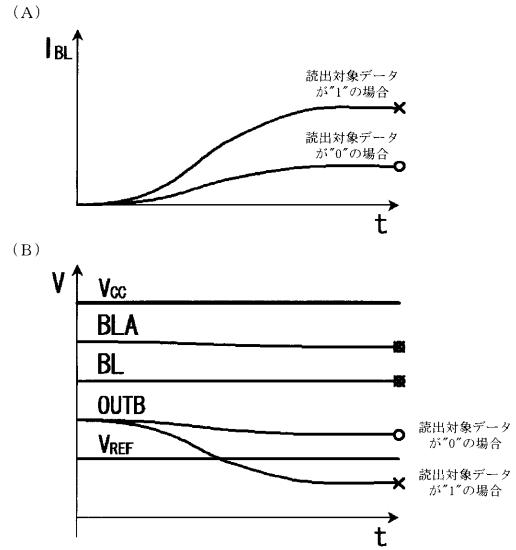

ここで、データ読出対象のメモリセル14からの読出対象データの読出しが開始され、読出用センスアンプ回路34(を構成する個々のセンスアンプ回路50)の入力端BLに流出電流 $I_{BL}$ が流れると、読出用センスアンプ回路34の入力端BLの電圧は、例として図4(B)に"BL"と表記して示すように基準電圧 $V_{BLREF}$ から僅かに低下する。ここで、流出電流 $I_{BL}$ が流れても読出用センスアンプ回路34の入力端BLの電圧の低下量が僅かであるのは、PMOSトランジスタ54のトランスクンダクタンス係数Kが所定値以上であるためである。PMOSトランジスタ52は飽和領域で動作しているため、入力端BLの電圧が僅かに低下してもPMOSトランジスタ52のソース-ドレイン間電流 $I_{SDP}$ は変化しない。

#### 【0041】

一方、PMOSトランジスタ54のトランスクンダクタンス係数Kが所定値以上であるため、流出電流 $I_{BL}$ が流れても入力端BLの電圧が基準電圧 $V_{BLREF}$ から僅かに低下すると、PMOSトランジスタ54のソース-ドレイン間電流 $I_{SDP}$ は流出電流 $I_{BL}$ 分減少する。また、NMOSトランジスタ56のドレイン-ソース間電流 $I_{DSN}$ も流出電流 $I_{BL}$ 分減少し、出力端OUTBからの出力電圧が低下する。従って、出力端OUTBからの出力電圧の低下量は流出電流 $I_{BL}$ の大きさに応じて変化し、図4(A)に示すように、読出対象データが"1"の場合には読出対象データが"0"の場合よりも流出電流 $I_{BL}$ が大きくなるので、読出対象データが"1"か"0"かに応じてPMOSトランジスタ54のソース-ドレイン間電流 $I_{SDP}$ 及びNMOSトランジスタ56のドレイン-ソース間電流 $I_{DSN}$ の減少量が相違することで、出力端OUTBからの出力電圧の低下量も読出対象データが"1"か"0"かに応じて明確に相違する。

#### 【0042】

アンプブロック回路30の参照用センスアンプ回路32は、例として図4(B)に示すように、出力端OUTBからの出力電圧(各オペアンプ46に供給する基準電圧 $V_{REF}$ )が、読出対象データが"0"の場合に流出電流 $I_{BL}$ の大きさに応じて低下した後の出力電圧と、読出対象データが"1"の場合の流出電流 $I_{BL}$ の大きさに応じて低下した後の出力電圧の中間に相当する大きさとなるように構成されている。

#### 【0043】

上記のように、基準電圧 $V_{REF}$ を前記中間に相当する大きさとすることは、例えば参照用センスアンプ回路32の入力端BLを流れる基準流出電流 $I_{BLR}$ が、読出対象データが"1"の場合の流出電流 $I_{BL}$ と読出対象データが"0"の場合の流出電流 $I_{BL}$ の中間に相当する大きさとなるように、参照用センスアンプ回路32に接続された特定メモリセル14のフローティングゲート内の電子を調節することで実現できる。これにより、差動増幅器として動作する各オペアンプ46からの出力に基づいて、読出対象データが"0"か"1"かを判別することができる。

#### 【0044】

次に、本第1実施形態に係るセンスアンプ回路50の動作条件について説明する。PMOSトランジスタ54に着目し、PMOSトランジスタ52を飽和領域で動作させるためのバイアス電圧 $V_{BIASP}$ の条件を求めるとき、PMOSトランジスタ52の閾値電圧を $V_{TP}$ とした場合、

$$V_{BLREF} < V_{BIASP} + |V_{TP}| \quad \dots (12)$$

となる。このため、本第1実施形態では(12)式を満たすようにセンスアンプ回路50に供給するバイアス電圧 $V_{BIASP}$ などが調整されている。図15に示したセンスアンプ回路でMOSトランジスタを飽和領域で動作させるためには先の(5)式又は(10)式を満たす必要があるが、本第1実施形態に係るセンスアンプ回路50では、上記の(12)式を満たせ

10

20

30

40

50

ばPMOSトランジスタ54(及びPMOSトランジスタ52)を飽和領域で動作させることができ、入力端BLの電圧を基準電圧 $V_{BLREF}$ に保ち、流出電流 $I_{BL}$ に応じて変化する出力電圧から読み出対象データが"0"か"1"かを判別することができる。

#### 【0045】

(12)式を(5)式と比較しても明らかなように、本第1実施形態に係るセンスアンプ回路50は、図15(A)に示したセンスアンプ回路200と比較して" $V_{GSN} - V_{TN}$ "だけバイアス電圧 $V_{BIASP}$ の条件が緩和されている。また、(12)式を(10)式と比較しても明らかなように、本第1実施形態に係るセンスアンプ回路50は、図15(B)に示したセンスアンプ回路210と比較して" $|V_{SGP} - |V_{TP}|$ "だけバイアス電圧 $V_{BIASP}$ の条件が緩和されている。従って、本第1実施形態に係るセンスアンプ回路50は、従来のセンスアンプ回路200, 210と比較してそれぞれ" $V_{GSN} - V_{TN}$ "、" $|V_{SGP} - |V_{TP}|$ "だけ電源 $V_{CC}$ の電圧が低下したり、基準電圧 $V_{BLREF}$ が高くなったりしても、PMOSトランジスタ52, 54が線形領域で動作してしまうことで利得が低下することなく、入力端BLの電圧を $V_{BLREF}$ に保つことができる。10

#### 【0046】

##### 〔第2実施形態〕

次に本発明の第2実施形態について説明する。なお、第1実施形態と同一の部分には同一の符号を付し、説明を省略する。

#### 【0047】

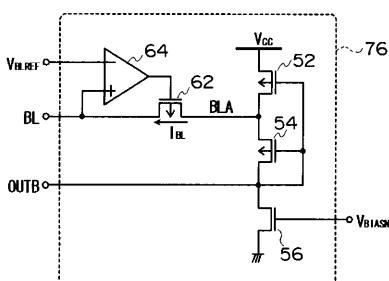

図5に示すように、本第2実施形態に係るセンスアンプ回路60は、第1実施形態で説明したセンスアンプ回路50に対してPMOSトランジスタ62及びオペアンプ64が追加されている。PMOSトランジスタ62は、PMOSトランジスタ52のドレイン(PMOSトランジスタ54のソース)と入力端BLの間に設けられており、ソースがPMOSトランジスタ52のドレイン(PMOSトランジスタ54のソース)に接続され(この接続点をノードBLAと称する)、ドレインが入力端BLに接続されている。またオペアンプ64は、基準電圧 $V_{BLREF}$ が供給される基準電圧入力端に反転入力端が接続され、非反転入力端が入力端BLに接続され、出力端がPMOSトランジスタ62のゲートに接続されている。20

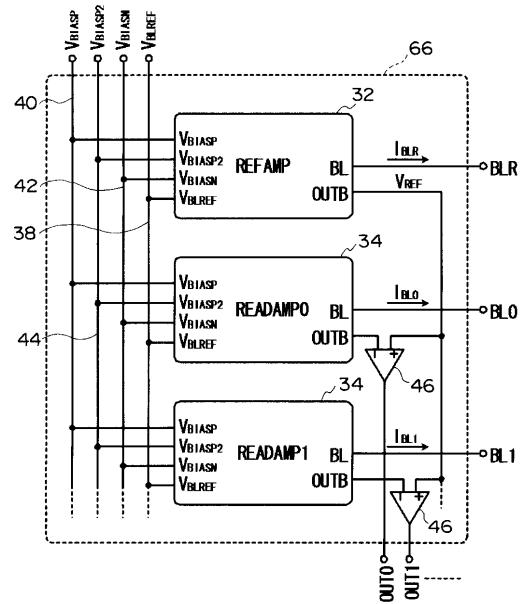

#### 【0048】

また図6に示すように、本第2実施形態に係るアンプブロック回路66は、第1実施形態で説明したアンプブロック回路30に対し、電圧生成回路36が省略され、単一の参照用センスアンプ回路32及び複数の読み出用センスアンプ回路34が上述したセンスアンプ回路60で各々構成されている点で相違している。30

#### 【0049】

単一の参照用センスアンプ回路32及び複数の読み出用センスアンプ回路34を構成する個々のセンスアンプ回路60は、PMOSトランジスタ54のゲートに接続される第2バイアス電圧入力端が第2バイアス電圧供給線44に接続されているが、この第2バイアス電圧供給線44は第1実施形態のように電圧生成回路36には接続されておらず、図示しない外部回路に接続されている。第2バイアス電圧供給線44が接続された外部回路は第2バイアス電圧供給線44を介してバイアス電圧 $V_{BIASP2}$ を供給し、このバイアス電圧 $V_{BIASP2}$ は個々のセンスアンプ回路60のPMOSトランジスタ54のゲートに各々供給される。また、個々のセンスアンプ回路60のオペアンプ64の反転入力端に接続された個々のセンスアンプ回路60の基準電圧入力端は、基準電圧供給線38を介して図示しない外部回路に接続されており、当該外部回路は基準電圧供給線38を介して基準電圧 $V_{BLREF}$ を供給し、この基準電圧 $V_{BLREF}$ は個々のセンスアンプ回路60のオペアンプ64の反転入力端に各々供給される。40

#### 【0050】

本第2実施形態に係るセンスアンプ回路60では、PMOSトランジスタ52が線形領域で動作するように、PMOSトランジスタ52のゲートに供給されるバイアス電圧 $V_{BIASP}$ の大きさやPMOSトランジスタ52の特性が調整されている。また、PMOS

10

20

30

40

50

トランジスタ54が飽和領域で動作するように、PMOSトランジスタ54のゲートに供給されるバイアス電圧 $V_{BIA5P2}$ の大きさやPMOSトランジスタ54の特性が調整されている。また、NMOSトランジスタ56が飽和領域で動作するように、NMOSトランジスタ56のゲートに供給されるバイアス電圧 $V_{BIASN}$ の大きさやNMOSトランジスタ56の特性が調整されている。

#### 【0051】

なお、センスアンプ回路60は請求項3記載のデータ読出回路に対応しており、詳しくは、センスアンプ回路60のPMOSトランジスタ52は請求項3に記載の第1PMOSトランジスタに、PMOSトランジスタ54は請求項3に記載の第2PMOSトランジスタに、NMOSトランジスタ56は請求項3に記載の第1NMOSトランジスタに、PMOSトランジスタ62は請求項3に記載の第4PMOSトランジスタに、オペアンプ64は請求項3に記載の差動増幅部に各々対応している。また、PMOSトランジスタ52のゲートに供給されるバイアス電圧 $V_{BIASP}$ は請求項3(より詳しくは請求項5)に記載の第1バイアス電圧に、PMOSトランジスタ54のゲートに供給されるバイアス電圧 $V_{BIA5P2}$ は請求項3に記載の第2バイアス電圧に、NMOSトランジスタ56のゲートに供給されるバイアス電圧 $V_{BIASN}$ は請求項3に記載の第3バイアス電圧に各々対応している。

10

#### 【0052】

また、本第2実施形態に係るアンプブロック回路66を含むMOS型半導体記憶装置10も請求項8に記載の半導体記憶装置に対応しており、メモリセルアレイ12が請求項8に記載のメモリセルアレイに、オペアンプ46が請求項8に記載の比較回路に、センスアンプ回路60から成る読出用センスアンプ回路34が請求項8に記載のデータ読出部に、同じくセンスアンプ回路60から成る参照用センスアンプ回路32が請求項8に記載の参照電圧供給部に各々対応している。

20

#### 【0053】

次に本第2実施形態の作用として、本第2実施形態に係るセンスアンプ回路60の動作を説明する。メモリセル14からデータを読み出すためには、個々のセンスアンプ回路60の入力端BLを基準電圧 $V_{BLREF}$ に保ち、データ読出対象のメモリセル14のドレインに基準電圧 $V_{BLREF}$ を与える必要がある。これに対して本第2実施形態では、個々のセンスアンプ回路60のオペアンプ64が、図15に示すセンスアンプ回路200, 210のオペアンプ206, 216と同様に差動増幅器として動作することで、入力端BLの電圧が基準電圧 $V_{BLREF}$ に保たれデータ読出対象のメモリセル14のドレインに基準電圧 $V_{BLREF}$ が与えられる。

30

#### 【0054】

ここで、データ読出対象のメモリセル14からの読出対象データの読出しが開始され、読出用センスアンプ回路34(を構成する個々のセンスアンプ回路60)の入力端BLに流出電流 $I_{BL}$ が流れると、個々のセンスアンプ回路60のノードBLAの電圧は、例として図7(B)に"BLA"と表記して示すように基準電圧 $V_{BLREF}$ から僅かに低下する。一方、PMOSトランジスタ54、NMOSトランジスタ56が飽和領域で動作しているため、PMOSトランジスタ54のソース - ドレイン間電流 $I_{SDP}$ 、NMOSトランジスタ56のドレイン - ソース間電流 $I_{DSN}$ は、ノードBLAの電圧が僅かに低下しても殆ど変化しない。また、PMOSトランジスタ54はゲート接地増幅回路として作用するため、ノードBLAの電圧が僅かに低下すると出力端OUTBの電圧は比較的大きく低下する。

40

#### 【0055】

結果として、出力端OUTBからの出力電圧の低下量は流出電流 $I_{BL}$ の大きさに応じて変化し、図7(A)に示すように、読出対象データが"1"の場合には読出対象データが"0"の場合よりも流出電流 $I_{BL}$ が大きくなるので、読出対象データが"1"か"0"かに応じて出力端OUTBからの出力電圧の低下量は読出対象データが"1"か"0"かに応じて明確に相違する。本第2実施形態に係る参照用センスアンプ回路32(を構成するセンスアンプ回路60)は、第1実施形態と同様に、出力端OUTBからの出力電圧(各オペアンプ46に供給する基準

50

電圧  $V_{REF}$ ) が、読み出対象データが "0" の場合に流出電流  $I_{BL}$  の大きさに応じて低下した後の出力電圧と、読み出対象データが "1" の場合の流出電流  $I_{BL}$  の大きさに応じて低下した後の出力電圧の中間に相当する大きさとなるように構成されている(図 7(B)参照)ので、差動増幅器として動作する各オペアンプ 46 からの出力に基づいて、読み出対象データが "0" か "1" かを判別することができる。

#### 【0056】

次に、本第 2 実施形態に係るセンスアンプ回路 60 の動作条件について説明する。PMOSトランジスタ 52 に着目し、PMOSトランジスタ 52 を線形領域で動作させるためのノードBLAの電圧  $V_{BLA}$  の条件を求めるとき、PMOSトランジスタ 52 の閾値電圧を  $V_{TP}$  とした場合、

$$V_{BLA} > V_{BIASP} + |V_{TP}| \dots (13)$$

となる。このため、本第 2 実施形態では(13)式を満たすようにセンスアンプ回路 60 に供給するバイアス電圧  $V_{BIASP}$  などが調整されている。上記の(13)式を、図 15(A)に示すセンスアンプ回路 200 の動作条件である先の(5)式や、図 15(B)に示すセンスアンプ回路 210 の動作条件である先の(10)式、第 1 実施形態で説明したセンスアンプ回路 50 の動作条件である先の(12)式と比較しても明らかのように、本第 2 実施形態に係るセンスアンプ回路 60 の動作条件である(13)式では基準電圧  $V_{BLREF}$  の上限が規定(制限)されない。従って、本第 2 実施形態に係るセンスアンプ回路 60 は、図 15(A)に示すセンスアンプ回路 200 や図 15(B)に示すセンスアンプ回路 210 のみならず、第 1 実施形態で説明したセンスアンプ回路 50 と比較した場合にも、利得が低下することなく入力端BLの電圧を  $V_{BLREF}$  に保持できる状態を、電源  $Vcc$  の電圧がより低下したり、基準電圧  $V_{BLREF}$  がより高くなった場合にも維持することができる、という効果を有する。

#### 【0057】

また、本第 2 実施形態に係るセンスアンプ回路 60 は、第 1 実施形態で説明したセンスアンプ回路 50 のように PMOSトランジスタ 54 のトランスクンダクタンス係数 K の値が所定値以上になるように PMOSトランジスタ 54 の特性を調整する必要もないので、回路設計の自由度を向上させることができ、PMOSトランジスタ 54 を高速に動作するように設計することも容易になる、という利点も有する。

#### 【0058】

##### 〔第 3 実施形態〕

次に本発明の第 3 実施形態について説明する。なお、第 1 実施形態及び第 2 実施形態と同一の部分には同一の符号を付し、説明を省略する。

#### 【0059】

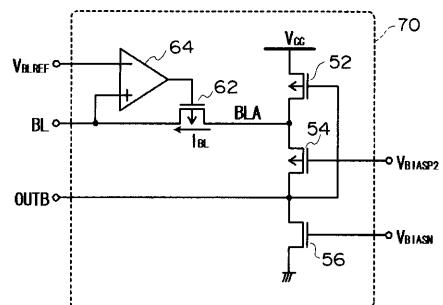

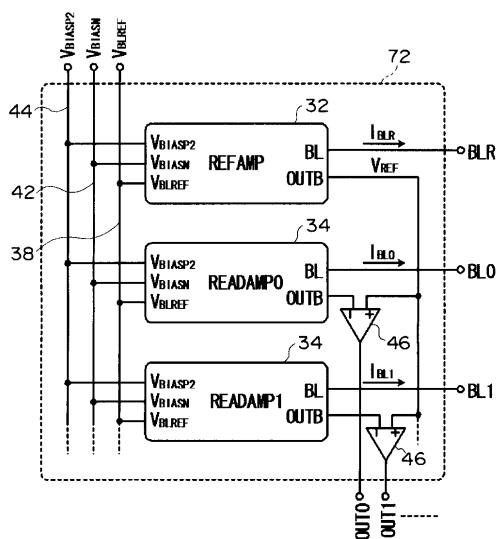

図 8 に示すように、本第 3 実施形態に係るセンスアンプ回路 70 は、第 2 実施形態で説明したセンスアンプ回路 60 に対し、第 1 バイアス電圧入力端子が省略され、PMOSトランジスタ 52 のゲートが出力端 OUTB に接続されている点で相違している。また、図 9 に示すように、本第 3 実施形態に係るアンプブロック回路 72 は、第 2 実施形態で説明したアンプブロック回路 66 に対し、单一の参照用センスアンプ回路 32 及び複数の読み出用センスアンプ回路 34 が上記のセンスアンプ回路 70 で各自構成され、第 1 バイアス電圧供給線 40 が省略されている点で相違している。

#### 【0060】

なお、センスアンプ回路 70 は請求項 3 (より詳しくは請求項 6) に記載のデータ読み出回路に対応しており、詳しくは、センスアンプ回路 70 の PMOSトランジスタ 52 は請求項 3 (より詳しくは請求項 6) に記載の第 1 PMOSトランジスタに、PMOSトランジスタ 54 は請求項 3 に記載の第 2 PMOSトランジスタに、NMOSトランジスタ 56 は請求項 3 に記載の第 1 NMOSトランジスタに、PMOSトランジスタ 62 は請求項 3 に記載の第 4 PMOSトランジスタに、オペアンプ 64 は請求項 3 に記載の差動増幅部に各自対応している。また、本第 3 実施形態に係るアンプブロック回路 72 を含む MOS型半導体記憶装置 10 も請求項 8 に記載の半導体記憶装置に対応しており、メモリセルアレ

10

20

30

40

50

イ 1 2 が請求項 8 に記載のメモリセルアレイに、オペアンプ 4 6 が請求項 8 に記載の比較回路に、センスアンプ回路 7 0 から成る読出用センスアンプ回路 3 4 が請求項 8 に記載のデータ読出部に、同じくセンスアンプ回路 7 0 から成る参照用センスアンプ回路 3 2 が請求項 8 に記載の参照電圧供給部に各々対応している。

#### 【 0 0 6 1 】

次に本第 3 実施形態の作用として、本第 3 実施形態に係るセンスアンプ回路 7 0 の動作について、第 2 実施形態で説明したセンスアンプ回路 6 0 と異なる部分のみ説明する。本第 3 実施形態に係るセンスアンプ回路 7 0 は PMOS トランジスタ 5 2 のゲートが出力端 OUTB に接続されているため、PMOS トランジスタ 5 2 がゲート接地増幅回路として作用すると共に、出力端 OUTB からの出力電圧の変化に伴って PMOS トランジスタ 5 2 のオン抵抗も変化する。10 すなわち、出力端 OUTB からの出力電圧が低下すると PMOS トランジスタ 5 2 のオン抵抗が小さくなり、ノード BLA の電圧が高くなる。また、出力端 OUTB からの出力電圧が高くなると PMOS トランジスタ 5 2 のオン抵抗が大きくなり、ノード BLA の電圧が低下する。これらの動作は、PMOS トランジスタ 5 2 から成るゲート接地増幅回路に対するフィードバック動作であり、回路動作の安定性が向上する。

#### 【 0 0 6 2 】

また、出力端 OUTB からの出力電圧は差動増幅器として動作するオペアンプ 4 6 の反転入力端に入力されるが、出力端 OUTB が PMOS トランジスタ 5 2 のゲートに接続されていることで、出力端 OUTB からの出力電圧は、PMOS トランジスタ 5 2 がオンする電圧、すなわち、電源電圧を V<sub>CC</sub>、出力端 OUTB からの出力電圧を V<sub>OUTB</sub>、PMOS トランジスタ 5 2 の閾値電圧を V<sub>TP</sub> とすると、20

$$V_{CC} - V_{OUTB} > |V_{TP}|$$

を満たす電圧へ自動的に調整され、オペアンプ 4 6 から成る差動増幅器の動作を保障することができる。これにより、差動増幅器の動作を保障できるように設定したバイアス電圧 V<sub>BIAS\_P</sub> を生成して PMOS トランジスタ 5 2 のゲートに供給する外部回路が不要となるため、第 2 実施形態で説明したセンスアンプ回路 6 0 と比較して周辺回路の構成の簡略化を実現できる。

#### 【 0 0 6 3 】

##### 〔 第 4 実施形態 〕

次に本発明の第 4 実施形態について説明する。なお、第 1 実施形態～第 3 実施形態と同一の部分には同一の符号を付し、説明を省略する。30

#### 【 0 0 6 4 】

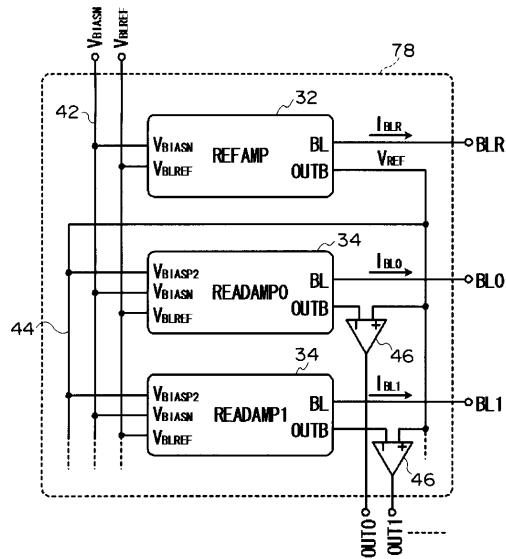

図 1 0 に示すように、本第 4 実施形態に係るセンスアンプ回路 7 6 は、第 3 実施形態で説明したセンスアンプ回路 7 0 に対し、第 2 バイアス電圧入力端子が省略され、PMOS トランジスタ 5 2 のゲートに加えて、PMOS トランジスタ 5 4 のゲートも出力端 OUTB に接続されている点で相違している。また、図 1 1 に示すように、本第 4 実施形態に係るアンプブロック回路 7 8 は、第 3 実施形態で説明したアンプブロック回路 7 2 に対し、単一の参照用センスアンプ回路 3 2 が上記のセンスアンプ回路 7 6 で構成されている（複数の読出用センスアンプ回路 3 4 については、アンプブロック回路 7 2 と同様に第 3 実施形態で説明したセンスアンプ回路 7 0 で構成されている）と共に、個々の読出用センスアンプ回路 3 4 の第 2 バイアス電圧入力端に各々接続された第 2 バイアス電圧供給線 4 4 が、参照用センスアンプ回路 3 2 の出力端 OUTB に接続され、参照用センスアンプ回路 3 2 から出力された基準電圧 V<sub>REF</sub> が個々の読出用センスアンプ回路 3 4 の PMOS トランジスタ 5 4 のゲートにバイアス電圧 V<sub>BIAS\_P2</sub> として供給される点で相違している。40

#### 【 0 0 6 5 】

なお、センスアンプ回路 7 6 は請求項 3 （より詳しくは請求項 7 ）に記載のデータ読出回路に対応しており、詳しくは、センスアンプ回路 7 6 の PMOS トランジスタ 5 2 は請求項 3 （より詳しくは請求項 7 ）に記載の第 1 PMOS トランジスタに、PMOS トランジスタ 5 4 は請求項 3 （より詳しくは請求項 7 ）に記載の第 2 PMOS トランジスタに、NMOS トランジスタ 5 6 は請求項 3 に記載の第 1 NMOS トランジスタに、PMOS T50

ランジスタ 6 2 は請求項 3 に記載の第 4 PMOS トランジスタに、オペアンプ 6 4 は請求項 3 に記載の差動増幅部に各々対応している。また、本第 3 実施形態に係るアンププロック回路 7 8 を含む MOS 型半導体記憶装置 1 0 は請求項 9 に記載の半導体記憶装置に対応しており、メモリセルアレイ 1 2 が請求項 9 に記載のメモリセルアレイに、オペアンプ 4 6 が請求項 9 に記載の比較回路に、センスアンプ回路 7 0 から成る読出用センスアンプ回路 3 4 が請求項 9 に記載のデータ読出部に、センスアンプ回路 7 6 から成る参照用センスアンプ回路 3 2 が請求項 9 に記載の参照電圧供給部に各々対応している。

#### 【 0 0 6 6 】

次に本第 4 実施形態の作用を説明する。本第 4 実施形態に係るセンスアンプ回路 7 6 では、PMOS トランジスタ 5 4 のゲートが出力端 OUTB に接続されており、出力端 OUTB からの出力電圧が PMOS トランジスタ 5 4 のゲートに供給されることで、PMOS トランジスタ 5 4 が飽和領域で動作することを保障することができる。また、本第 4 実施形態では参照用センスアンプ回路 3 2 を上記のセンスアンプ回路 7 6 で構成しており、参照用センスアンプ回路 3 2 (センスアンプ回路 7 6 ) から出力された基準電圧  $V_{REF}$  を、個々の読出用センスアンプ回路 3 4 にバイアス電圧  $V_{BIAS_2}$  として供給しているため、バイアス電圧  $V_{BIAS_2}$  を供給する外部回路が不要となり、周辺回路の構成の簡略化を実現できる。

#### 【 0 0 6 7 】

なお、第 4 実施形態では、請求項 9 に記載のデータ読出部に相当する読出用センスアンプ回路 3 4 として、第 3 実施形態で説明したセンスアンプ回路 7 0 を適用した様子を説明したが、これに限定されるものではなく、第 2 実施形態で説明したセンスアンプ回路 6 6 を読出用センスアンプ回路 3 4 として適用してもよい。

#### 【 0 0 6 8 】

##### 〔 第 5 実施形態 〕

次に本発明の第 5 実施形態について説明する。なお、第 2 実施形態と同一の部分には同一の符号を付し、説明を省略する。

#### 【 0 0 6 9 】

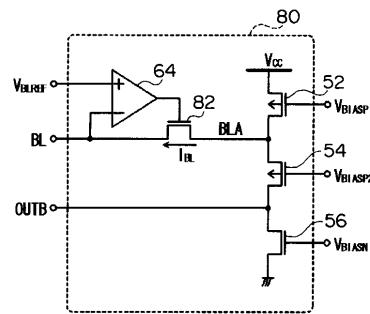

図 1 2 に示すように、本第 5 実施形態に係るセンスアンプ回路 8 0 は、第 2 実施形態で説明したセンスアンプ回路 6 0 における PMOS トランジスタ 6 2 に代えて、NMOS トランジスタ 8 2 が設けられている点でセンスアンプ回路 6 0 と相違している。またオペアンプ 6 4 は、非反転入力端が、基準電圧  $V_{BLREF}$  が供給される基準電圧入力端に接続され、反転入力端が入力端 BL に接続され、出力端が NMOS トランジスタ 8 2 のゲートに接続されている。

#### 【 0 0 7 0 】

なお、センスアンプ回路 8 0 は請求項 4 記載のデータ読出回路に対応しており、詳しくは、センスアンプ回路 8 0 の PMOS トランジスタ 5 2 は請求項 4 に記載の第 1 PMOS トランジスタに、PMOS トランジスタ 5 4 は請求項 4 に記載の第 2 PMOS トランジスタに、NMOS トランジスタ 5 6 は請求項 4 に記載の第 1 NMOS トランジスタに、NMOS トランジスタ 8 2 は請求項 4 に記載の第 2 NMOS トランジスタに、オペアンプ 6 4 は請求項 4 に記載の差動増幅部に各々対応している。また、PMOS トランジスタ 5 2 のゲートに供給されるバイアス電圧  $V_{BIAS_P}$  は請求項 4 (より詳しくは請求項 5 ) に記載の第 1 バイアス電圧に、PMOS トランジスタ 5 4 のゲートに供給されるバイアス電圧  $V_{BIAS_2}$  は請求項 4 に記載の第 2 バイアス電圧に、NMOS トランジスタ 5 6 のゲートに供給されるバイアス電圧  $V_{BIAS_N}$  は請求項 4 に記載の第 3 バイアス電圧に各々対応している。

#### 【 0 0 7 1 】

次に本第 5 実施形態の作用として、本第 5 実施形態に係るセンスアンプ回路 8 0 の動作について、第 2 実施形態で説明したセンスアンプ回路 6 0 と異なる部分のみ説明する。本第 5 実施形態に係るセンスアンプ回路 8 0 は、第 2 実施形態のセンスアンプ回路 6 0 における PMOS トランジスタ 6 2 に代えて NMOS トランジスタ 8 2 が設けられているが、

10

20

30

40

50

一般に、このような回路構成の場合、PMOSトランジスタよりもNMOSトランジスタを使用する方が、動作の高速化と安定化が期待できる。但し、NMOSトランジスタ82をオンさせるには、NMOSトランジスタ82の閾値電圧 $V_{TN}$ を考慮する必要がある。すなわち、オペアンプ64の出力端の電圧は基準電圧 $V_{BLREF}$ よりNMOSトランジスタ82の閾値電圧 $V_{TN}$ 分以上、高電圧でなければならない。従って、電源 $V_{cc}$ の電圧が比較的低い電圧であったり基準電圧 $V_{BLREF}$ が比較的高い電圧である場合には、使用が困難となる。

#### 【0072】

なお、その他の回路構成、回路動作等は第2実施形態と同様のため説明を省略する。

#### 【0073】

##### 〔第6実施形態〕

次に本発明の第6実施形態について説明する。なお、第3実施形態と同一の部分には同一の符号を付し、説明を省略する。

#### 【0074】

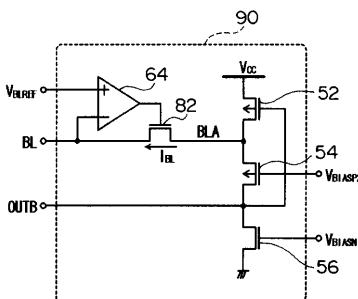

図13に示すように、本第6実施形態に係るセンスアンプ回路90は、第3実施形態で説明したセンスアンプ回路70におけるPMOSトランジスタ62に代えて、NMOSトランジスタ82が設けられている点でセンスアンプ回路70と相違している。またオペアンプ64は、非反転入力端が、基準電圧 $V_{BLREF}$ が供給される基準電圧入力端に接続され、反転入力端が入力端BLに接続され、出力端がNMOSトランジスタ82のゲートに接続されている。

20

#### 【0075】

なお、センスアンプ回路90は請求項4(より詳しくは請求項6)に記載のデータ読出回路に対応しており、詳しくは、センスアンプ回路90のPMOSトランジスタ52は請求項4(より詳しくは請求項6)に記載の第1PMOSトランジスタに、PMOSトランジスタ54は請求項4に記載の第2PMOSトランジスタに、NMOSトランジスタ56は請求項4に記載の第1NMOSトランジスタに、NMOSトランジスタ82は請求項4に記載の第2NMOSトランジスタに、オペアンプ64は請求項4に記載の差動増幅部に各々対応している。

#### 【0076】

次に本第6実施形態の作用として、本第6実施形態に係るセンスアンプ回路90の動作について、第3実施形態で説明したセンスアンプ回路70と異なる部分のみ説明する。本第6実施形態に係るセンスアンプ回路90は、第3実施形態のセンスアンプ回路70におけるPMOSトランジスタ62に代えてNMOSトランジスタ82が設けられているが、一般に、このような回路構成の場合、PMOSトランジスタよりもNMOSトランジスタを使用する方が、動作の高速化と安定化が期待できる。但し、NMOSトランジスタ82をオンさせるには、NMOSトランジスタ82の閾値電圧 $V_{TN}$ を考慮する必要がある。すなわち、オペアンプ64の出力端の電圧は基準電圧 $V_{BLREF}$ よりNMOSトランジスタ82の閾値電圧 $V_{TN}$ 分以上、高電圧でなければならない。従って、電源 $V_{cc}$ の電圧が比較的低い電圧であったり基準電圧 $V_{BLREF}$ が比較的高い電圧である場合には、使用が困難となる。

30

#### 【0077】

なお、その他の回路構成、回路動作等は第3実施形態と同様のため説明を省略する。

#### 【0078】

##### 〔第7実施形態〕

次に本発明の第7実施形態について説明する。なお、第4実施形態と同一の部分には同一の符号を付し、説明を省略する。

#### 【0079】

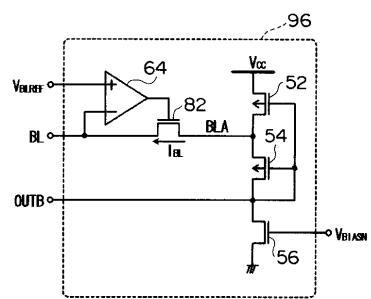

図14に示すように、本第7実施形態に係るセンスアンプ回路96は、第4実施形態で説明したセンスアンプ回路76におけるPMOSトランジスタ62に代えて、NMOSトランジスタ82が設けられている点でセンスアンプ回路76と相違している。またオペア

40

50

ンプ 6 4 は、非反転入力端が、基準電圧  $V_{BLREF}$  が供給される基準電圧入力端に接続され、反転入力端が入力端 BL に接続され、出力端が NMOS トランジスタ 8 2 のゲートに接続されている。

#### 【0080】

なお、センスアンプ回路 9 6 は請求項 4 (より詳しくは請求項 7) に記載のデータ読出回路に対応しており、詳しくは、センスアンプ回路 9 6 の PMOS トランジスタ 5 2 は請求項 4 (より詳しくは請求項 7) に記載の第 1 PMOS トランジスタに、PMOS トランジスタ 5 4 は請求項 4 (より詳しくは請求項 7) に記載の第 2 PMOS トランジスタに、NMOS トランジスタ 5 6 は請求項 4 に記載の第 1 NMOS トランジスタに、NMOS トランジスタ 8 2 は請求項 4 に記載の第 2 NMOS トランジスタに、オペアンプ 6 4 は請求項 4 に記載の差動増幅部に各々対応している。また、本第 7 実施形態に係るセンスアンプ回路 9 6 は、第 4 実施形態で説明したセンスアンプ回路 7 6 と同様に、アンプブロック回路の单一の参照用センスアンプ回路 3 2 として用いられる。10

#### 【0081】

次に本第 7 実施形態の作用として、本第 7 実施形態に係るセンスアンプ回路 9 6 の動作について、第 4 実施形態で説明したセンスアンプ回路 7 6 と異なる部分のみ説明する。本第 7 実施形態に係るセンスアンプ回路 9 6 は、第 4 実施形態のセンスアンプ回路 7 6 における PMOS トランジスタ 6 2 に代えて NMOS トランジスタ 8 2 が設けられているが、一般に、このような回路構成の場合、PMOS トランジスタよりも NMOS トランジスタを使用する方が、動作の高速化と安定化が期待できる。但し、NMOS トランジスタ 8 2 をオンさせるには、NMOS トランジスタ 8 2 の閾値電圧  $V_{TN}$  を考慮する必要がある。すなわち、オペアンプ 6 4 の出力端の電圧は基準電圧  $V_{BLREF}$  より NMOS トランジスタ 8 2 の閾値電圧  $V_{TN}$  分以上、高電圧でなければならない。従って、電源  $V_{CC}$  の電圧が比較的低い電圧であったり基準電圧  $V_{BLREF}$  が比較的高い電圧である場合には、使用が困難となる。20

#### 【0082】

なお、その他の回路構成、回路動作等は第 4 実施形態と同様のため説明を省略する。

#### 【0083】

また、上記では本発明に係るデータ読出回路によってデータを読み出し可能なメモリセルは、一定電圧が与えられた状態で、保持しているデータの値によって大きさの異なる電流が流れる構成のメモリ(セル)であればよく、E PROM 以外に、例えば EEPROM やフラッシュメモリ等を適用可能である。30

#### 【図面の簡単な説明】

#### 【0084】

【図 1】第 1 実施形態に係るセンスアンプ回路を示す回路図である。

【図 2】第 1 実施形態に係るアンプブロック回路を示す概略ブロック図である。

【図 3】本実施形態に係る MOS 型半導体記憶装置の回路図である。

【図 4】第 1 実施形態におけるデータ読出時の各種電圧の変化を示す線図である。

【図 5】第 2 実施形態に係るセンスアンプ回路を示す回路図である。

【図 6】第 2 実施形態に係るアンプブロック回路を示す概略ブロック図である。40

【図 7】第 2 実施形態におけるデータ読出時の各種電圧の変化を示す線図である。

【図 8】第 3 実施形態に係るセンスアンプ回路を示す回路図である。

【図 9】第 3 実施形態に係るアンプブロック回路を示す概略ブロック図である。

【図 10】第 4 実施形態に係るセンスアンプ回路を示す回路図である。

【図 11】第 4 実施形態に係るアンプブロック回路を示す概略ブロック図である。

【図 12】第 5 実施形態に係るセンスアンプ回路を示す回路図である。

【図 13】第 6 実施形態に係るセンスアンプ回路を示す回路図である。

【図 14】第 7 実施形態に係るセンスアンプ回路を示す回路図である。

【図 15】従来のセンスアンプ回路を示す回路図である。

【図 16】従来のセンスアンプ回路を用いたアンプブロック回路を示す概略ブロック図で50

ある。

【図17】従来のセンスアンプ回路におけるデータ読出時の各種電圧の変化を示す線図である。

【符号の説明】

【0085】

|     |             |    |

|-----|-------------|----|

| 1 0 | MOS型半導体記憶装置 |    |

| 1 2 | メモリセルアレイ    |    |

| 1 4 | メモリセル       |    |

| 3 0 | アンプブロック回路   |    |

| 3 2 | 参照用センスアンプ回路 | 10 |

| 3 4 | 読出用センスアンプ回路 |    |

| 3 6 | 電圧生成回路      |    |

| 4 6 | オペアンプ       |    |

| 5 0 | センスアンプ回路    |    |

| 5 2 | PMOSトランジスタ  |    |

| 5 4 | PMOSトランジスタ  |    |

| 5 6 | NMOSトランジスタ  |    |

| 5 8 | PMOSトランジスタ  |    |

| 5 9 | 定電流源        |    |

| 6 0 | センスアンプ回路    | 20 |

| 6 2 | PMOSトランジスタ  |    |

| 6 4 | オペアンプ       |    |

| 6 6 | アンプブロック回路   |    |

| 6 6 | センスアンプ回路    |    |

| 7 0 | センスアンプ回路    |    |

| 7 2 | アンプブロック回路   |    |

| 7 6 | センスアンプ回路    |    |

| 7 8 | アンプブロック回路   |    |

| 8 0 | センスアンプ回路    |    |

| 8 2 | NMOSトランジスタ  | 30 |

| 9 0 | センスアンプ回路    |    |

| 9 6 | センスアンプ回路    |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

(B)

【図16】

【図17】

---

フロントページの続き

(72)発明者 松井 克晃

東京都港区虎ノ門1丁目7番12号 沖電気工業株式会社内

審査官 滝谷 亮一

(56)参考文献 特開平06-203587(JP,A)

特開平08-315592(JP,A)

特開平03-147596(JP,A)

特表平08-510079(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/06

G11C 17/18