**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) . Int. Cl.

*H01L 21/20* (2006.01)

(11) 공개번호 10-2006-0126712

(43) 공개일자 2006년12월08일

(21) 출원번호 10-2006-7014242

(22) 출원일자 2006년07월14일

심사청구일자 없음

번역문 제출일자 2006년07월14일

(86) 국제출원번호 PCT/US2004/042260

국제출원일자 2004년12월16일

(87) 국제공개번호 WO 2005/059983

국제공개일자 2005년06월30일

(30) 우선권주장 10/740,376 2003년12월17일 미국(US)

(71) 출원인 니트로넥스 코오포레이션

미국 노쓰 캐롤라이나 (우편번호 : 27606) 랠레이 휴톤 스트리트 628 스위트 103

(72) 발명자 존슨, 제리, 더블유.

미국 27615 노쓰캐롤라이나주 롤리 텐워쓰 드라이브 925

테리엔, 로버트, 제이.

미국 27502 노쓰캐롤라이나주 에이펙스 빅 리프 루프 1466

베스칸, 안드레이

독일 52134 헤르조겐라츠 뮐렌슈트라쎄 6에

브라운, 제프리, 디.

미국 27529 노쓰캐롤라이나주 가너 베킹검 로드 1102

(74) 대리인 주성민

백만기

이중희

전체 청구항 수 : 총 73 항

(54) 전극 형성층을 포함하는 질화갈륨 재료 영역을 사용하는반도체 구조물, 트랜지스터 및 쇼트키 다이오드, 및 그들을형성하는 방법

**(57) 요약**

질화갈륨 재료 장치 및 그것을 형성하기 위한 방법이 제공된다. 이 장치는 전극 형성층을 포함한다. 전극 형성층은 전형적으로 그 내부에 전극이 (적어도 부분적으로) 형성된 비아(via)를 갖는다. 따라서, 비아는 전극의 치수를 (적어도 부분적으로) 정의한다. 몇몇 경우에, 전극 형성층은 질화갈륨 재료 영역 상에 형성된 부동태층이다.

**대표도**

도 1a

## 특허청구의 범위

### 청구항 1.

질화갈륨 재료 영역;

상기 질화갈륨 재료 영역 위에 형성되고 내부에 형성된 비아(via)를 포함하는 전극 형성층- 상기 비아의 상단에서의 단면 적은 상기 비아의 하단에서의 단면적보다 큼 -; 및

상기 질화갈륨 재료 영역 상에 및 상기 비아 내에 형성된 전극을 포함하며,

상기 전극 길이는 상기 비아의 하단에서 정의되는 반도체 구조물.

### 청구항 2.

제1항에 있어서, 상기 전극은 게이트 전극인 반도체 구조물.

### 청구항 3.

제2항에 있어서, 상기 질화갈륨 재료 영역 상에 형성된 소스 전극 및 상기 질화갈륨 재료 영역 상에 형성된 드레인 전극을 더 포함하는 반도체 구조물.

### 청구항 4.

제3항에 있어서, 상기 반도체 구조물은 트랜지스터인 반도체 구조물.

### 청구항 5.

제1항에 있어서, 상기 전극 형성층의 측벽은 상기 전극 형성층의 저면에서부터 약 10도 내지 약 60도 사이의 각으로 상향 연장된 반도체 구조물.

### 청구항 6.

제1항에 있어서, 상기 전극 형성층의 측벽은 상기 전극 형성층의 저면에서부터 약 15도 내지 약 40도 사이의 각으로 상향 연장된 반도체 구조물.

### 청구항 7.

제1항에 있어서, 상기 전극 형성층의 측벽은 상기 전극 형성층의 상단면에서부터 약 90도 내지 약 160도 사이의 각으로 하향 연장된 반도체 구조물.

### 청구항 8.

제1항에 있어서, 상기 전극 형성층의 측벽은 상기 전극 형성층의 상단면에서부터 약 90도 내지 약 135도 사이의 각으로 하향 연장된 반도체 구조물.

### 청구항 9.

제1항에 있어서, 기판을 더 포함하며,

상기 질화갈륨 재료 영역이 상기 기판 상에 형성된 반도체 구조물.

### 청구항 10.

제9항에 있어서, 상기 기판은 실리콘인 반도체 구조물.

### 청구항 11.

제9항에 있어서, 상기 질화갈륨 재료 영역과 상기 기판 사이에 형성된 전이층을 더 포함하는 반도체 구조물.

### 청구항 12.

제11항에 있어서, 상기 전이층은 조성 경사를 갖는(compositionally-graded) 반도체 구조물.

### 청구항 13.

제1항에 있어서, 상기 전극 형성층은 부동태층(passivating layer)인 반도체 구조물.

### 청구항 14.

제1항에 있어서, 상기 전극 형성층은 질화실리콘 화합물을 포함하는 반도체 구조물.

### 청구항 15.

제1항에 있어서, 상기 전극 형성층은 산화실리콘 화합물을 포함하는 반도체 구조물.

### 청구항 16.

제1항에 있어서, 상기 전극 형성층은 상기 질화갈륨 재료 영역 바로 위에 형성된 반도체 구조물.

### 청구항 17.

제1항에 있어서, 상기 전극은 상기 전극 형성층의 상단면의 일부분 위로 연장된 반도체 구조물.

### 청구항 18.

제3항에 있어서, 상기 게이트 전극은 상기 전극 형성층의 상단면의 일부분 위로, 상기 게이트 전극과 상기 드레인 전극 사이 거리의 약 2% 내지 약 60%의 거리만큼 상기 드레인 전극의 방향으로 연장된 반도체 구조물.

### 청구항 19.

제18항에 있어서, 상기 게이트 전극은 상기 전극 형성층의 상단면의 일부분 위로, 상기 드레인 전극 방향으로의 거리가 상기 소스 전극 방향으로의 거리보다 크게 연장된 반도체 구조물.

### 청구항 20.

제19항에 있어서, 상기 게이트 전극은 상기 전극 형성층의 상단면의 일부분 위로, 상기 게이트 전극이 상기 전극 형성층 위로 상기 드레인 전극의 방향으로 확장된 거리의 50% 미만의 거리만큼, 상기 소스 전극의 방향으로 연장된 반도체 구조물.

### 청구항 21.

제1항에 있어서, 상기 비아의 상단에서의 단면 치수에 대한 상기 전극 길이의 비는 약 0.50 내지 0.95 사이인 반도체 구조물.

### 청구항 22.

제1항에 있어서, 상기 비아의 상단에서의 단면 치수에 대한 상기 전극 길이의 비는 약 0.75 내지 0.90 사이인 반도체 구조물.

### 청구항 23.

제1항에 있어서, 상기 비아를 형성하는 상기 전극 형성층의 측벽들은 상기 질화갈륨 재료 영역에 대해 위로 오목한 반도체 구조물.

### 청구항 24.

제1항에 있어서, 상기 비아의 단면적은 상기 비아의 상단으로부터 상기 비아의 하단으로 갈수록 계속 작아지는 반도체 구조물.

### 청구항 25.

제1항에 있어서, 상기 전극은 상기 질화갈륨 재료 영역에 바로 접촉해 있는 반도체 구조물.

### 청구항 26.

제1항에 있어서, 상기 전극은 제1 금속 성분 및 제2 금속 성분을 포함하는 반도체 구조물.

**청구항 27.**

제26항에 있어서, 상기 전극의 제1 금속 성분은 상기 전극 길이 전체에 걸쳐 상기 질화갈륨 재료 영역에 바로 접촉해 있으며, 상기 전극의 제2 금속 성분은 상기 전극 길이의 임의의 일부분에 걸쳐 상기 질화갈륨 재료 영역에 바로 접촉해 있지 않은 반도체 구조물.

**청구항 28.**

제27항에 있어서, 상기 제1 금속은 니켈이고, 상기 제2 금속은 금인 반도체 구조물.

**청구항 29.**

제25항에 있어서, 상기 전극 길이에 걸쳐, 상기 전극은 상기 질화갈륨 재료 영역에 바로 접촉하여 일정한 조성을 갖는 반도체 구조물.

**청구항 30.**

제1항에 있어서, 게이트 전극이 상기 비아를 완벽하게 채운 반도체 구조물.

**청구항 31.**

제1항에 있어서, 상기 질화갈륨 재료 영역은 0.005 미크론/미크론<sup>2</sup> 미만의 균열 레벨을 갖는 반도체 구조물.

**청구항 32.**

제1항에 있어서, 상기 질화갈륨 재료 영역은 둘 이상의 질화갈륨 재료 층들을 포함하는 반도체 구조물.

**청구항 33.**

제1항에 있어서, 상기 질화갈륨 재료 영역은 질화갈륨층을 포함하는 반도체 구조물.

**청구항 34.**

제1항에 있어서, 상기 비아는 상기 전극 형성층의 상단면으로부터 상기 전극 형성층의 저면으로 연장된 반도체 구조물.

**청구항 35.**

제1항에 있어서, 상기 비아는 오직 상기 전극 형성층의 상단면과 부동태층의 저면 사이 거리의 일부분에만 연장된 반도체 구조물.

**청구항 36.**

제1항에 있어서, 상기 전극 형성층과 상기 질화갈륨 재료 영역 사이에 형성된 적어도 하나의 층을 더 포함하는 반도체 구조물.

### 청구항 37.

제36항에 있어서, 상기 전극 형성층과 상기 질화갈륨 재료 영역 사이에 형성된 부동태층을 더 포함하는 반도체 구조물.

### 청구항 38.

제1항에 있어서, 상기 전극은 쇼트키 컨택트인 반도체 구조물.

### 청구항 39.

제38항에 있어서, 상기 질화갈륨 재료 영역 상에 형성된 옴 전극을 더 포함하는 반도체 구조물.

### 청구항 40.

질화갈륨 재료 영역;

상기 질화갈륨 재료 영역 위에 형성되고 내부에 형성된 비아를 포함하는 전극 형성층- 상기 비아의 단면적은 상기 비아의 하단에서보다 상기 비아의 상단에서 크며, 상기 비아의 측벽은 상기 비아의 하단으로부터 약 5도 내지 약 85도 사이의 각으로 상향 연장되고, 상기 비아의 상단으로부터 약 90도 내지 약 160도 사이의 각으로 하향 연장됨 -;

상기 질화갈륨 재료 영역 상에 형성된 소스 전극;

상기 질화갈륨 재료 영역 상에 형성된 드레인 전극; 및

상기 질화갈륨 재료 영역 상에 및 상기 비아 내에 형성된 게이트 전극을 포함하며,

상기 게이트 전극의 길이는 상기 비아의 하단에서 정의되고, 상기 비아의 상단에서의 단면 치수에 대한 상기 게이트 전극 길이의 비는 약 0.50 내지 0.95 사이인 트랜지스터.

### 청구항 41.

제40항에 있어서, 상기 전극 형성층의 측벽은 상기 전극 형성층의 저면에서부터 약 10도 내지 약 60도 사이의 각으로 상향 연장된 트랜지스터.

### 청구항 42.

제40항에 있어서, 상기 전극 형성층의 측벽은 상기 전극 형성층의 상단면에서부터 약 90도 내지 약 135도 사이의 각으로 하향 연장된 트랜지스터.

### 청구항 43.

제40항에 있어서, 기판을 더 포함하며,

상기 질화갈륨 재료 영역이 상기 기판 상에 형성된 트랜지스터.

#### 청구항 44.

제43항에 있어서, 상기 기판은 실리콘인 트랜지스터.

#### 청구항 45.

제44항에 있어서, 상기 질화갈륨 재료 영역과 상기 기판 사이에 형성된 조성 기울기를 갖는 전이층을 더 포함하는 트랜지스터.

#### 청구항 46.

제40항에 있어서, 상기 전극 형성층은 부동태층인 트랜지스터.

#### 청구항 47.

제40항에 있어서, 상기 전극 형성층은 상기 질화갈륨 재료 영역 바로 위에 형성된 트랜지스터.

#### 청구항 48.

제40항에 있어서, 상기 게이트 전극은 상기 전극 형성층의 상단면의 일부분 위로, 상기 게이트 전극과 상기 드레인 전극 사이 거리의 약 2% 내지 약 60%의 거리만큼 상기 드레인 전극의 방향으로 연장된 트랜지스터.

#### 청구항 49.

제40항에 있어서, 상기 게이트 전극은 상기 전극 형성층의 상단면의 일부분 위로, 상기 게이트 전극이 상기 전극 형성층 위로 상기 드레인 전극의 방향으로 확장된 거리의 50% 미만의 거리만큼, 상기 소스 전극의 방향으로 연장된 트랜지스터.

#### 청구항 50.

제40항에 있어서, 상기 비아의 상단면에서의 단면 치수에 대한 상기 전극 길이의 비는 약 0.75 내지 0.90 사이인 트랜지스터.

#### 청구항 51.

제40항에 있어서, 상기 비아를 형성하는 상기 전극 형성층의 측벽들은 상기 질화갈륨 재료 영역에 대해 위로 오목한 트랜지스터.

#### 청구항 52.

제40항에 있어서, 상기 전극은 제1 금속 성분 및 제2 금속 성분을 포함하는 트랜지스터.

### 청구항 53.

제52항에 있어서, 상기 전극의 제1 금속 성분은 상기 게이트 길이 전체에 걸쳐 상기 질화갈륨 재료 영역에 바로 접촉해 있으며, 상기 전극의 제2 금속 성분은 상기 게이트 길이의 임의의 일부분에 걸쳐 상기 질화갈륨 재료 영역에 바로 접촉해 있지 않은 트랜지스터.

### 청구항 54.

제40항에 있어서, 상기 제1 금속은 니켈이고, 상기 제2 금속은 금인 트랜지스터.

### 청구항 55.

제40항에 있어서, 상기 게이트 전극이 상기 비아를 완벽하게 채운 트랜지스터.

### 청구항 56.

제40항에 있어서, 상기 질화갈륨 재료 영역은 0.005 미크론/미크론<sup>2</sup> 미만의 균열 레벨을 갖는 트랜지스터.

### 청구항 57.

제40항에 있어서, 상기 비아는 상기 전극 형성층의 상단면으로부터 상기 전극 형성층의 저면으로 연장된 트랜지스터.

### 청구항 58.

제40항에 있어서, 상기 비아는 오직 상기 전극 형성층의 상단면과 상기 부동태층의 저면 사이 거리의 일부분에만 연장된 반도체 트랜지스터.

### 청구항 59.

질화갈륨 재료 영역;

상기 질화갈륨 재료 영역 위에 형성되고 내부에 형성된 비아를 포함하는 전극 형성층- 상기 비아의 상단에서의 단면적은 상기 비아의 하단에서의 단면적 보다 크며, 상기 비아의 측벽은 상기 비아의 하단으로부터 약 5도 내지 약 85도 사이의 각으로 상향 연장되고, 상기 비아의 상단으로부터 약 90도 내지 약 160도 사이의 각으로 하향 연장됨 -;

상기 질화갈륨 재료 영역 상에 및 상기 비아 내에 형성된 쇼트키 전극(Schottky electrode)- 상기 전극 길이는 상기 비아의 하단에서 정의됨 -; 및

상기 질화갈륨 재료 영역 상에 형성된 옴 전극을 포함하는 쇼트키 다이오드.

### 청구항 60.

제59항에 있어서, 상기 전극 형성층의 측벽은 상기 전극 형성층의 저면에서부터 약 10도 내지 약 60도 사이의 각으로 상향 연장된 쇼트키 다이오드.

### 청구항 61.

제59항에 있어서, 상기 전극 형성층의 측벽은 상기 전극 형성층의 상단면에서부터 약 90도 내지 약 135도 사이의 각으로 하향 연장된 쇼트키 다이오드.

### 청구항 62.

제59항에 있어서, 기판을 더 포함하며,

상기 질화갈륨 재료 영역이 상기 기판 상에 형성된 쇼트키 다이오드.

### 청구항 63.

제59항에 있어서, 상기 기판은 실리콘인 쇼트키 다이오드.

### 청구항 64.

제59항에 있어서, 상기 질화갈륨 재료 영역과 상기 기판 사이에 형성된 조성 기울기를 갖는 전이층을 더 포함하는 쇼트키 다이오드.

### 청구항 65.

제59항에 있어서, 상기 전극 형성층은 부동태층인 쇼트키 다이오드.

### 청구항 66.

제59항에 있어서, 상기 게이트 전극은 상기 전극 형성층의 상단면의 일부분 위로, 상기 게이트 전극과 상기 드레인 전극 간의 거리의 약 2% 내지 약 60%의 거리만큼 상기 드레인 전극의 방향으로 연장된 쇼트키 다이오드.

### 청구항 67.

질화갈륨 재료 영역 상에 전극 형성층을 형성하는 단계;

비아의 상단에서의 단면 치수가 상기 비아의 하단에서의 단면 치수보다 크도록 상기 전극 형성층 내에 비아를 형성하는 단계; 및

상기 질화갈륨 재료 영역 상에 및 상기 비아 내에 전극을 형성하는 단계를 포함하고.

상기 전극의 길이는 상기 비아의 하단에 의해 정의되는 반도체 구조물 형성 방법.

**청구항 68.**

제67항에 있어서, 상기 비아를 플라즈마 에칭 단계에서 형성하는 단계를 포함하는 방법.

**청구항 69.**

제68항에 있어서, 플라즈마 내에서의 압력 조건은 약 1 mTorr 내지 약 100 mTorr 사이인 방법.

**청구항 70.**

제67항에 있어서, 상기 플라즈마 에칭 단계는 약 50 Watt 미만의 RF 전력 조건을 유지하는 단계를 포함하는 방법.

**청구항 71.**

제67항에 있어서, 부동태층의 저면으로부터 위쪽으로 연장되는 상기 부동태층의 측벽의 각을 약 5도 내지 약 85도 사이가 되도록 제어하는 단계를 더 포함하는 방법.

**청구항 72.**

질화갈륨 재료 영역 상에 전극 형성층을 형성하는 단계;

비아의 상단에서의 단면 치수가 상기 비아의 하단에서의 단면 치수보다 크고, 상기 비아의 측벽이 상기 비아의 하단에서부터 약 5도 내지 약 85도 사이의 각으로 상향 연장되고, 상기 비아의 상단에서부터 약 90도 내지 약 160도 사이의 각으로 하향 연장되도록, 상기 전극 형성층 내에 비아를 형성하는 단계;

상기 질화갈륨 재료 영역 상에 소스 전극을 형성하는 단계;

상기 질화갈륨 재료 영역 상에 드레인 전극을 형성하는 단계; 및

상기 질화갈륨 재료 영역 상에 및 상기 비아 내에 게이트 전극을 형성하는 단계를 포함하며,

상기 게이트 전극의 길이는 상기 비아의 하단에서 정의되고, 상기 비아의 상단에서의 단면 치수에 대한 상기 게이트 전극 길이의 비는 약 0.50 내지 0.95 사이인 트랜지스터 형성 방법.

**청구항 73.**

질화갈륨 재료 영역 상에 전극 형성층을 형성하는 단계;

비아의 상단에서의 단면 치수가 상기 비아의 하단에서의 단면 치수보다 크고, 상기 비아의 측벽이 상기 비아의 하단에서부터 약 5도 내지 약 85도 사이의 각으로 상향 연장되고, 상기 비아의 상단에서부터 약 90도 내지 약 160도 사이의 각으로 하향 연장되도록, 상기 전극 형성층 내에 비아를 형성하는 단계;

상기 질화갈륨 재료 영역 상에 음 전극을 형성하는 단계; 및

상기 질화갈륨 재료 영역 상에 및 상기 비아 내에 쇼트키 전극을 형성하는 단계를 포함하며,

상기 전극 길이는 상기 비아의 하단에서 정의되는 쇼트키 다이오드 형성 방법.

## 명세서

### 기술분야

본 발명은 일반적으로 질화갈륨 재료에 관한 것이며, 보다 구체적으로 전극 형성층을 포함하는 질화갈륨 재료 장치 및 그 형성 방법에 관한 것이다.

### 배경기술

질화갈륨(GaN) 재료는 GaN과, AlGaN, InGaN 및 AlInGaN 등의 그 합금을 포함한다. 이 재료들은 매우 강한 에너지의 전자 전이가 일어나는 것을 허용하는 상대적으로 넓고 직접적인 벤드갭을 갖는 반도체 화합물들이다. 질화갈륨 재료는 높은 전자이동도, 청색 광을 효율적으로 방출하기 위한 능력, 신호를 고주파수에서 전송하기 위한 능력 등을 포함하는 다수의 이로운 속성들을 갖는다. 따라서, 질화갈륨 재료는 트랜지스터, 필드 이미터(field emitter) 및 광전자 장치 등의 다수의 마이크로전자 응용에서 광범위하게 개발되고 있다.

### <발명의 요약>

본 발명은 전극 형성층을 포함하는 질화갈륨 재료 장치 및 그 형성 방법을 제공한다.

일 실시예에서, 반도체 구조물이 제공된다. 이 구조는 질화갈륨 재료 영역 및 질화갈륨 재료 영역 위에 형성된 전극 형성층을 포함한다. 전극 형성층은 그 내부에 형성된 비아(via)를 포함한다. 비아의 상단에서의 단면적은 비아의 하단에서의 단면적보다 크다. 이 구조는 또한 질화갈륨 재료 영역 상에 및 비아 내에 형성된 전극도 포함하는데, 여기서 전극 길이는 비아의 하단에서 정의된다.

또 다른 실시예에서, 트랜지스터가 제공된다. 트랜지스터는 질화갈륨 재료 영역 및 질화갈륨 재료 영역 위에 형성된 전극 형성층을 포함한다. 전극 형성층은 그 내부에 형성된 비아를 포함한다. 비아의 단면적은 비아의 하단에서보다 비아의 상단에서 더욱 크다. 비아의 측벽은 비아의 하단에서부터 약 5도 내지 약 85도 사이의 각으로 상향 연장되고, 비아의 상단으로부터 약 90도 내지 약 160도 사이의 각으로 하향 연장된다. 트랜지스터는 또한 질화갈륨 재료 영역 상에 형성된 소스 전극, 질화갈륨 재료 영역 상에 형성된 드레인 전극 및 질화갈륨 재료 영역 상에 및 비아 내에 형성된 게이트 전극을 포함한다. 게이트 전극의 길이는 비아의 하단에서 정의되고, 비아의 상단에서의 단면 치수에 대한 게이트 전극 길이의 비는 약 0.50 내지 0.95 사이이다.

또 다른 실시예에서, 쇼트키 다이오드(Schottky diode)가 제공된다. 쇼트키 다이오드는 질화갈륨 재료 영역 및 질화갈륨 재료 영역 위에 형성된 전극 형성층을 포함한다. 전극 형성층은 그 내부에 형성된 비아를 포함한다. 비아의 상단에서의 단면적은 비아의 하단에서의 단면적보다 크다. 비아의 측벽은 비아의 하단으로부터 약 5도 내지 약 85도 사이의 각으로 상향 연장되고, 비아의 상단으로부터 약 90도 내지 약 160도 사이의 각으로 하향 연장된다. 쇼트키 다이오드는 또한 질화갈륨 재료 영역 상에 및 비아 내에 형성된 쇼트키 전극을 포함하며, 전극 길이는 비아의 하단에서 정의된다. 쇼트키 다이오드는 또한 질화갈륨 재료 영역 상에 형성된 옴 전극(ohmic electrode)을 포함한다.

또 다른 실시예에서, 반도체 구조물을 형성하는 방법이 제공된다. 이 방법은 질화갈륨 재료 영역 위에 전극 형성층을 형성하는 단계 및 비아의 상단에서의 단면 치수가 비아의 하단에서의 단면 치수보다 크도록 전극 형성층 내에 비아를 형성하는 단계를 포함한다. 이 방법은 또한 질화갈륨 재료 영역 상에 및 비아 내에 전극을 형성하는 단계를 포함하는데, 전극의 길이는 비아의 하단에서 정의된다.

또 다른 실시예에서, 트랜지스터를 형성하는 방법이 제공된다. 이 방법은 질화갈륨 재료 영역 상에 전극 형성층을 형성하는 단계 및 전극 형성층 내에 비아를 형성하는 단계를 포함한다. 비아의 상단에서의 단면 치수는 비아의 하단에서의 단면 치수보다 크며, 비아의 측벽은 비아의 하단에서부터 약 5도 내지 약 85도 사이의 각으로 상향 연장되고, 비아의 상단으로부터 약 90도 내지 약 160도 사이의 각으로 하향 연장된다. 이 방법은 또한 질화갈륨 재료 영역 상에 소스 전극을 형성하는 단계, 질화갈륨 재료 영역 상에 드레인 전극을 형성하는 단계 및 질화갈륨 재료 영역 상에 게이트 전극을 형성하는 단계를 포함한다. 게이트 전극의 길이는 비아 하단에서 정의되며, 비아의 상단에서의 단면 치수에 대한 게이트 전극 길이의 비율은 약 0.50 내지 0.95 사이이다.

또 다른 실시예에서, 쇼트키 다이오드를 형성하는 방법이 제공된다. 이 방법은 질화갈륨 재료 영역 상에 전극 형성층을 형성하는 단계 및 전극 형성층 내에 비아를 형성하는 단계를 포함한다. 비아의 상단에서의 단면 치수는 비아의 하단에서의 단면 치수보다 크다. 비아의 측벽은 비아의 하단에서부터 약 5도 내지 약 85도 사이의 각으로 상향 연장되고, 비아의 상단에서부터 약 90도 내지 약 160도 사이의 각으로 하향 연장된다. 이 방법은 또한 질화갈륨 재료 영역 위에 옴 전극을 형성하는 단계, 질화갈륨 재료 영역 상에 및 비아 내에 쇼트키 전극을 형성하는 단계를 포함하는데, 전극 길이는 비아의 하단에서 정의된다.

본 발명의 다른 양태, 실시예 및 특징은 첨부된 도면에 관련하여 고려될 때 다음의 본 발명의 상세한 설명으로부터 명백해 질 것이다. 첨부된 도면은 개요적인 것일뿐 크기를 한정하기 위해 의도된 것은 아니다. 도면에서, 여러 도면에 나타내진 각각의 동일한 또는 상당히 유사한 컴포넌트는 하나의 번호 또는 표식으로 나타내진다. 명료하게 하기 위해, 모든 도면 내의 모든 컴포넌트들이 라벨링(labeling)되지는 않는다. 참조에 의해 여기에 통합된 모든 특허출원 및 특허들은 참조에 의해 그들의 전체가 통합된다. 분쟁의 경우에는 정의를 포함하는 본 명세가 조정할 것이다.

## 실시예

본 발명은 질화갈륨 재료 장치 및 그 형성 방법을 제공한다. 이 장치는 전극 형성층을 포함한다. 전극 형성층은 전형적으로 그 내부에 (적어도 부분적으로) 전극이 형성된 비아를 갖는다. 따라서, 비아는 (적어도 부분적으로) 전극의 치수를 정의한다. 몇몇 경우에, 전극 형성층은 질화갈륨 재료 영역 상에 형성된 부동태층이다.

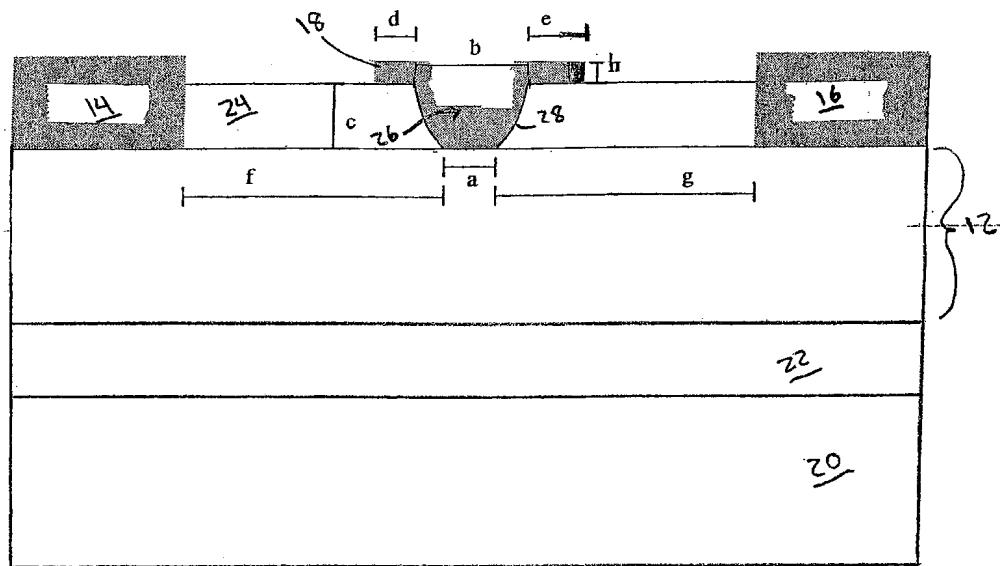

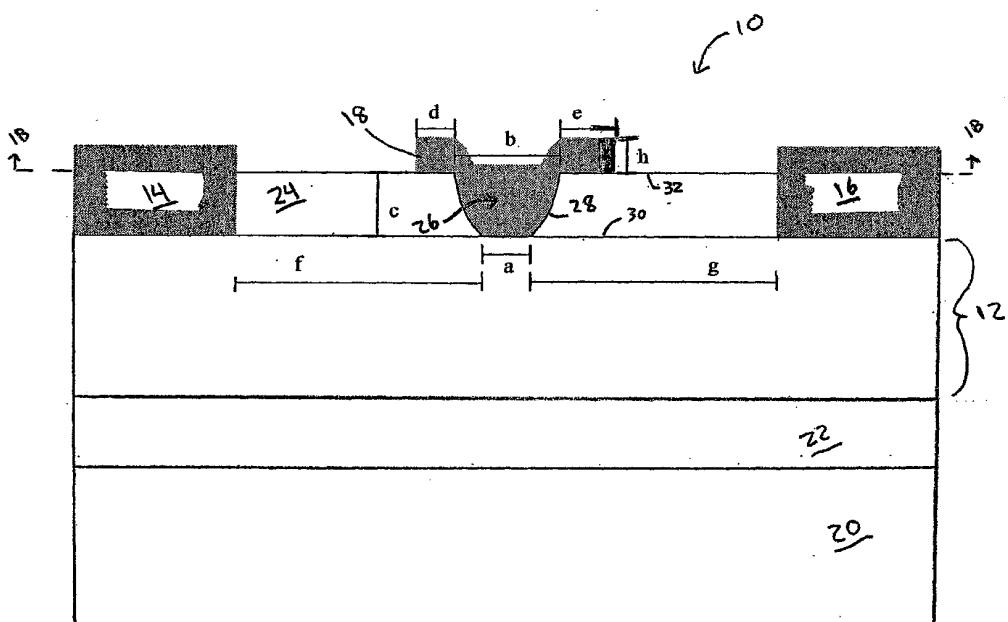

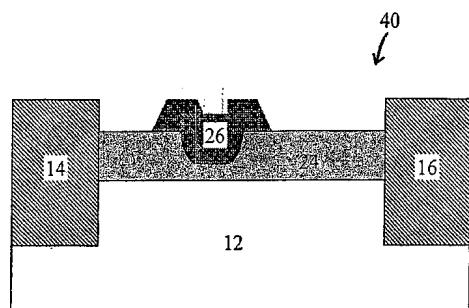

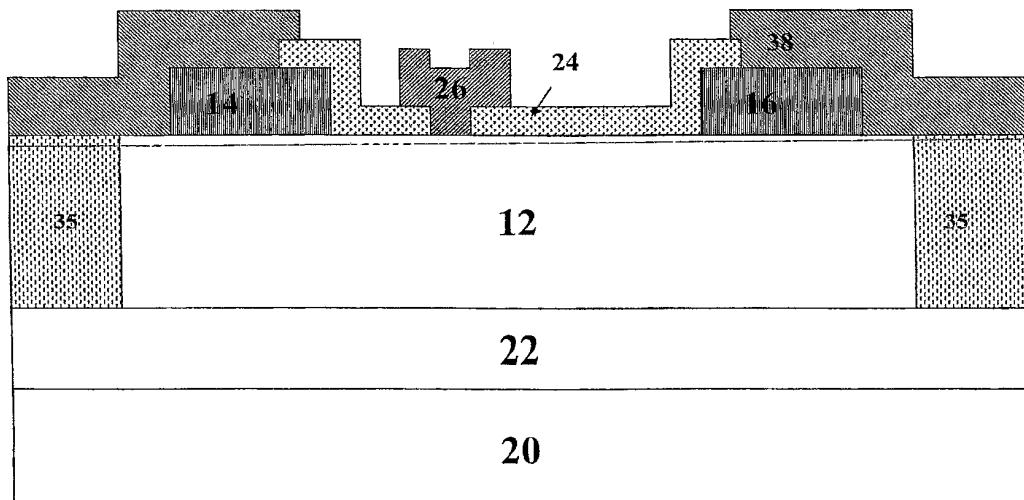

도 1a 및 1b는 본 발명의 일 실시예에 따른 질화갈륨 재료 영역(12)을 포함하는 반도체 장치(10)를 나타낸다. 나타낸 실시예에서, 장치(10)는 질화갈륨 재료 영역 상에 형성된 소스 전극(14), 드레인 전극(16) 및 게이트 전극(18)을 포함하는 FET (field effect transistor)이다. 질화갈륨 재료 영역은 기판(20) 상에 형성되며, 나타낸 바와 같이, 전이층(22)은 기판과 질화갈륨 재료 영역 사이에 형성될 수 있다. 나타낸 바와 같이, 장치는 질화갈륨 재료 영역의 표면을 보호하고 부동태화하는 부동태층(passivating layer)인 전극 형성층(24)을 포함한다. 비아(26)는 부분적으로 층(24) 내에 형성되고, 그 내부에 게이트 전극이 형성된다. 후술된 바와 같이, 비아의 모양 및 크기는, 그리고 그에 따른 게이트 전극의 모양 및 크기는, 장치의 속성을 향상시키도록 제어될 수 있다.

도 1a 및 1b에 나타낸 실시예에서는 장치(10)가 FET이지만, 후술된 것과 같이 본 발명은 다른 유형의 장치들도 포함한다. 본 발명의 FET가 사용되지 않는 실시예에서, 전극 형성층은 게이트 전극 이외의 쇼트키 컨택트 등의 다른 유형의 전극을 형성할 수 있다는 것이 이해되어야 한다. 또한, 도 1a 및 1b 내의 전극 형성층은 부동태층으로서 동작하지만, 다른 실시예에서, 전극 형성층은 부동태층으로서 동작하지 않을 수도 있다(예를 들어, 도 4 참조).

층이 다른 층 또는 기판 "상에(on)" 또는 "위에(over)" 있다고 언급될 때, 그것은 층 또는 기판 상에 바로 위치하는 것일 수 있으며, 또는 매개층이 또한 존재할 수도 있다. 다른 층 또는 기판 "바로 위에" 있는 층은 매개층에 없다는 것을 의미한다. 또한 층이 다른 층 또는 기판 "상에" 또는 "위에" 있다고 언급될 때, 그것은 층이나 기판 전체, 또는 층이나 기판의 일부분을 덮을 수 있다는 것도 이해되어야 한다.

여기에 사용된 바와 같이, "부동태층"이란 용어는 하지층(예를 들어, 질화갈륨 재료 장치(12)) 상에 성장되면, 하지층의 밴드갭 내의 표면/계면 준위의 개수를 줄이고, 및/또는 그것의 성분을 보호하거나, 하지층의 표면/계면에서의 자유 캐리어(예를 들어, 전극 또는 홀) 트랩핑 준위(free carrier trapping state)의 개수를 줄이고, 및/또는 그것의 성분을 보호하는 임의의 층을 의미한다. 예를 들어, 트랩핑 준위는 종결되지 않은 화학적 결합에 의해 생성되는 표면 준위에 관련되어, 주위 환경으로부터 표면에 흡수된 이온 또는 표면에서의 전위(dislocation)를 스레딩(threading)할 수 있게 된다. FET 장치에서, 트랩핑 준위는 자유 캐리어를 캡처하고 DC 또는 RF 동작 동안 바람직하지 않은 공핍 영역을 생성할 수 있다. 이러한 영향은 그것이 없었다면 동작하는 동안 FET의 채널 내에서 흘렀을 전류의 양을 줄일 수 있으며, 따라서 장치의 성능을 약화시킬 수 있다. 부동태층은 이러한 영향을 상당히 줄임으로써, 향상된 출력 전력 또는 효율 등의 장치의 전기적 성능을 향상시킬 수 있다. 부동태층은 또한 장치의 항복 전압을 증가시킬 수 있다.

부동태층은 또한 포토리소그래픽, 에칭, 금속(예를 들어, 게이트, 상호접속) 퇴적, 주입, 습식 화학, 및 레지스트 스트립(예를 들어, 플라즈마 내의) 단계들을 포함하는 후속 프로세스 단계들 동안 하지층(예를 들어, 질화갈륨 재료 장치(12))을 보호할 수 있다는 것이 이해되어야 한다. 따라서, 부동태층은 다른 프로세스 종류(예를 들어, 액체, 이온, 플라즈마, 가스 종류)가 질화갈륨 재료의 표면과 반응 및/또는 상호작용하는 것을 제한 또는 제거할 수 있다. 이러한 반응 및/또는 상호작용은 표면 형태학, 표면 준위 개수, 표면 전하의 양, 표면 전하의 극성 또는 이들의 임의의 조합을 변경시킴으로써 장치의 전기적 속성에 불리해질 수 있다.

전극 형성층(24)의 적절한 성분은 질화물 기반 화합물(예를 들어, 질화실리콘 화합물), 산화물 기반 화합물(예를 들어, 산화실리콘 화합물), 폴리이미드(polyimide), 다른 비전기적 재료, 또는 이러한 성분들의 조합(예를 들어, 산화실리콘과 질화실리콘)을 포함하지만, 이에만 한정되는 것은 아니다. 몇몇의 경우에는, 전극 형성층이 질화실리콘 화합물(예를 들어,  $\text{Si}_3\text{N}_4$ ) 또는 비화학량론(non-stoichiometric) 질화실리콘 화합물인 것이 바람직할 수 있다. 이러한 성분은, 전극 형성층이 부동태층으로 기능하거나(도 1a 및 1b에 도시된 바와 같음), 전극 형성층이 부동태층으로 기능하지 않을 때 적절하다는 것이 이해되어야 한다.

전극 형성층(24)의 두께는 장치의 설계에 따른다. 몇몇 경우, 전극 형성층은 약 50 옹스트롬 내지 1.0 미크론 사이의 두께를 가질 수 있다. 몇몇 경우에는 두께가 약 700 옹스트롬 내지 약 1200 옹스트롬 사이일 수도 있다.

나타낸 바와 같이, 전극 형성층(24)은 전극 영역(소스(14), 드레인(16) 및 게이트(18))을 제외한 질화갈륨 재료 영역(12)의 표면 전체를 덮는다.

도 1-2에서, 중요한 치수를 나타내기 위해 다음의 지정들이 사용된다: 게이트 길이(즉, 비아의 하단에서의 게이트의 단면 치수)(a), 비아의 상단에서의 단면 치수(b), 전극 형성층 두께(c), 소스 전극측 돌출 거리(d), 드레인 전극측 돌출 거리(e), 게이트-소스 간격(f), 게이트-드레인 간격(g) 및 게이트 전극 높이(h).

상기 언급된 단면적은 소스 및 드레인 전극에 수직인 평면 P(도 1b) 내에서 측정된 것이며, 그들 간의 최소 거리를 정의한다.

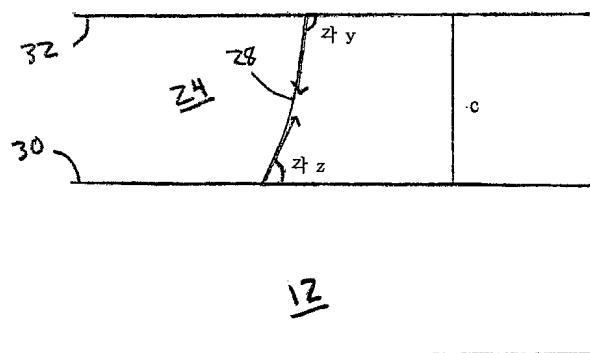

도 2는 비아 및 대응하는 게이트 전극의 프로파일을 나타낸다. 각 Z는 전극 형성층의 측벽(28)이 전극 형성층의 저면(30)으로부터 위쪽으로 연장된 각이고, 각 Y는 측벽이 전극 형성층의 상단면(32)으로부터 아래쪽으로 연장된 각이다. 각 Y 및 Z는 각각 저면(30) 및 상단면(32)에서 측정되며, 측벽(28)은 저면 및 상단면으로부터 떨어져 있는 곳에서 이러한 각들에서 벗나갈 수 있다.

전술된 치수 및 각은 도 1 및 2의 FET 실시예들의 게이트 전극에 관련하여 나타내져있지만, 이러한 치수 및 각 중에서 몇몇은 또한 후술된 바와 같은 FET를 사용하지 않는 실시예들의 다른 유형의 전극에도 적용될 수 있다.

유리하게도, 후술된 본 발명의 장치 형성 방법은 게이트 전극 치수(예를 들어, a)가 전체적으로 전극 형성층 내에 형성되는 것을 허용한다. 이것은 전극 형성층 퇴적 이전에 게이트 전극을 형성하는 프로세스, 또는 게이트 길이(a)가 아니라 게이트 전극 일부분을 전극 형성층 내에 형성하는 프로세스와는 구별된다. 예를 들어, 전극 형성층 내에 게이트 전극의 일부분을 정의하는 이러한 프로세스는 게이트 전극 재료로 완벽하게 채워지지 않는 영역(예를 들어, 전극 형성층을 언더컷(undercut)한 저면(30)에 인접한 영역)을 비아 내에 포함할 수 있다. 이러한 프로세스에서, 게이트 길이는 이에 따라 완전히 전극 형성층에 의해서만 정의되지 못할 수 있다. 반대로, 소정의 바람직한 본 발명의 방법에서, 비아 전체가 게이트 전극 재료로 채워져, 비아의 치수가 게이트 치수, 특히 게이트 길이에 정확하게 대응하게 된다. 따라서, 본 발명의 방법을 이용하면, 중요한 전극 치수(예를 들어, 게이트 길이)는 장치 성능을 최적화하도록 정확하게 제어될 수 있다. 본 발명의 일 양태는 어떠한 게이트 전극 치수(게이트 전극 프로파일 포함)가 FET 장치(10) 내의 성능 향상을 이끌어낼 수 있다는 것을 개시한다.

본 발명의 몇몇 방법에서, 게이트 전극 높이(h)가 전극 형성층 두께(c)보다 작으면(도 15 참조), 상단면(32)에서의 또는 그에 인접한 비아의 영역은 게이트 전극 재료로 채워지지 않을 수 있다는 것이 이해되어야 한다.

도 1a 및 1b에 나타낸 실시예에서, 게이트 길이(a)는 비아의 상단에서의 단면 치수(b)보다 작다. 비아(26)(따라서, 게이트 전극(18))는 또한 비아의 하단에서의 단면적보다 넓은 비아의 상단에서의 단면적을 갖는다. 나타낸 바와 같이, 비아(따라서, 게이트 전극(18))의 단면적은 비아의 상단에서 비아의 하단으로 갈수록 작아진다. 측벽(28)은 곧은(굽지 않은) 경사를 갖는 것이 바람직할 수 있다. 몇몇 경우에는, 측벽(28)이 굽은 경사를 갖는 것이 바람직할 수도 있다. 측벽이 굽은 경사를 갖는 경우, 나타낸 바와 같이 측벽은 질화갈륨 재료 영역(12)에 대하여 위로 오목한(concave-up) 모양을 가질 수 있다. 후술된 바와 같이, 전극 형성층에 청 단계는 원하는 게이트 프로파일을 제공하도록 제어될 수 있다.

비아(및 전극)의 단면적은 나타낸 전극 형성층에 의해 형성된 평면에 평행한 평면에서 측정된다는 것이 이해되어야 한다.

(a)/(b)의 비율이 항복 전압에 영향을 주는, 장치(10)에 대한 중요한 설계 매개변수일 수 있다는 것은 알려져 있다. 본 발명의 몇몇 실시예에서, (a)/(b)의 비율은 약 0.50 내지 약 0.95 사이가 되도록 제어된다. 몇몇 경우에는, 비율을 약 0.75 내지 0.90이 되도록 제어하는 것이 바람직할 수도 있다. 이러한 범위 내의 (a)/(b) 비율 값은 항복 전압을 향상시킬 수 있다. (a)/(b) 비율의 최적 값은 특정한 장치에 따라 달라지며, 또한 다른 설계 매개변수에 따라 달라질 수도 있다. 후술된 바와 같이, 전극 형성층 에칭 단계의 매개변수는 원하는 (a)/(b) 비율을 제공하도록 제어될 수 있다.

케이트 길이 (a)의 절대값은 특정한 장치 설계에 따른다. 예를 들어, (a)는 약 0.1 미크론 내지 약 5.0 미크론 사이일 수 있다. 그러나, (a)에 대한 다른 값들도 또한 적절할 수 있음이 이해되어야 한다.

또한 각 Y 및 Z가 장치 동작에 대하여 바람직한 범위를 갖는다는 것도 알려져 있다. 각 Z는 90도 미만인 것이 바람직할 수 있다. 예를 들어, 각 Z는 약 5도 내지 약 85 사이가 바람직할 수 있지만, 몇몇 경우에는 약 10도 내지 약 60도 사이, 그리고 몇몇 경우에는 약 15도 내지 약 40도 사이가 바람직할 수 있다. 각 Y는 90도 초과인 것이 바람직할 수 있다. 각 Y는 전형적으로 약 90도 내지 약 160도 사이이다. 각 Y는 약 90도 내지 약 135도 사이인 것이 바람직하지만, 몇몇 경우에는 약 90도 내지 약 110도 사이인 것이 바람직할 수 있다.

각 Y 및 Z가 장치에 의해 형성된 전기장의 위치 및 세기에 영향을 준다고 판정되어 왔다. Y 및 Z의 값은 상기 범위 내로 제어함으로써, 장치 동작 동안 케이트 전극의 드레인 에지(drain edge)에 인접하게 생성되는 최고 전기장이 감소될 수 있다. 이러한 개선은 동작 전압을 증가시키고 및/또는 케이트 누설 전류를 감소시킬 수 있다. Y 및 Z의 값이 상기 범위 이외의 값이면, 케이트 전극의 드레인 에지에 인접하게 생성된 최고 전기장이 너무 높아, 초과 케이트 누설 전류 및/또는 조기 장치 실패를 발생시킬 수 있다.

전술된 각 Y 및 Z의 범위는 또한 케이트 전극 재료로 비아를 완벽하게 채우게 하는데 중요하다. 각 Y 및 Z의 최적 값(들)은 특정한 장치에 따르며, 또한 다른 설계 매개변수에 따른다. 후술된 바와 같이, 전극 형성층 에칭 단계는 각 Y 및 Z의 원하는 값을 제공하도록 제어될 수 있다.

후술된 바와 같이, 각 Y 및 Z은 또한 FET 장치를 사용하지 않는 쇼트키 다이오드(예를 들어, 도 5의 (a) 및 (b) 참조)에 중요할 수 있다.

여기서 언급된 각들은 예를 들어, (도 13a에 나타낸 바와 같이) SEM을 사용하여 현미경 스케일(예를 들어, 약 50 또는 100 웅스트롬보다 큰 치수)로 측정될 수 있다는 것이 이해되어야 한다. 각은 예를 들어 TEM을 사용하여 각의 값을 왜곡시킬 수 있는 존재 표면 효과(예를 들어, 원자의 단층)를 나타내는 원자 스케일로 측정되도록 의도되지 않는다.

또한 케이트 전극은 하지 전극 형성층(24) 위로 돌출된 일부분을 포함하는 T자형 설계를 갖는 것도 바람직하다. 장치의 항복 전압을 생성하는데 드레인 전극측 돌출 거리(e)가 특히 중요하다고 판정됐다. 드레인 전극의 방향에서 전극 형성층 위로 돌출된 케이트 전극의 일부분은 (다른 유용한 효과들 중에서) 장치의 항복 전압을 증가시키는 필드 플레이트(field plate)로 기능할 수 있다. 예를 들어, (e)가 케이트 드레인 간격(g)의 약 2 퍼센트 내지 약 60 퍼센트 사이일 때, 항복 전압은 증가할 수 있음이 알려져 있다. 몇몇의 경우, 장치의 항복 전압을 더욱 최적화하기 위해 (e)는 약 10 퍼센트 내지 약 50 퍼센트 사이인 것이 바람직할 수 있다. (e)의 최적 값(들)은 특정한 장치에 따라 달라지며, 또한 다른 설계 매개변수에 따라 달라질 수도 있다.

소스 전극측 돌출 거리(d)를 드레인 전극측 돌출 거리(e)보다 짧도록 제어하는 것이 이롭다는 것도 또한 알려져 있다. 몇몇 경우에, (d)는 (e)의 50 퍼센트보다 짧거나, 심지어는 (e)의 20%보다 짧은 것이 바람직하다. 몇몇 경우에는, 비아 전체가 채워질 것을 보장하는 한편, (d)를 최소화하는 것이 이롭다. (d)의 값을 줄이는 것은 원하지 않는 케이트-소스 용량을 제한 또는 방지한다.

(d) 및 (e)의 값은 부분적으로 후술되는 패터닝 단계 및 금속 퇴적에 의해 제어된다.

소스 전극측 돌출 거리(d), 드레인 전극측 돌출 거리(e), 케이트 소스 간격(f) 및 케이트 드레인 거리(g)의 절대값은 장치 설계에 따른다. 비록 다른 값들도 가능하지만, 전형적인 (f) 및 (g) 값은 약 0.1 미크론 내지 약 10 미크론 사이이다.

몇몇 실시예에서, 케이트 전극 높이(h)의 값은 전극 형성층 두께(c)의 값보다 크다(도 1a 참조). 다른 실시예에서, 케이트 전극 높이(h)의 값은 전극 형성층 두께(c)의 값보다 작다(도 15 참조). 다른 케이트 치수들만큼 중요하진 않지만, (h)의 바

람직한 값은 특정한 장치에 따르며, 또한 다른 설계 매개변수에 따를 수도 있다. 예를 들어, (h)는 약 100 옹스트롬 내지 2.0 미크론 사이일 수 있다. (h) 값은 후술된 바와 같은 게이트 전극 재료를 퇴적시키는데 사용되는 프로세싱 조건에 의해 제어될 수 있다.

게이트 전극(18)은 금속(예를 들어, Au, Ni), 금속 화합물(예를 들어, WSi, WSiN), 합금, 반도체, 폴리실리콘, 질화물 또는 이들 재료의 조합물 등의 임의의 적절한 도전성 금속으로 형성될 수 있다. 예를 들어, 게이트 전극은 금, 니켈 또는 둘 모두로 형성될 수 있다. 유익하게도, 비아(26) 내에 게이트 전극을 형성함으로써 게이트 길이 전체에 걸쳐 질화갈륨 금속 영역에 바로 접촉하여 단일 도전성 금속 성분(예를 들어, 니켈)을 포함하는 게이트 전극을 형성할 수 있으며, 게이트 전극이 제2 도전성 금속 성분도 포함하는 경우에도 그러하다. 예를 들어, 게이트 전극이 니켈 및 금으로 형성될 때, 니켈층은 게이트 길이 전체에 걸쳐 질화갈륨 재료 영역에 바로 접촉해 있을 수 있으며, 금층이 니켈층 위에 형성될 수 있다(도 13a 참조). 반대로, 복수의 금속 성분을 포함하는 게이트 전극을 형성하기 위한 종래 기술은 게이트 길이의 내부에 바로 접촉해 있는 제1 성분(예를 들어, 니켈) 및 게이트 길이의 애지부에 바로 접촉해 있는 제2 성분(예를 들어, 금)을 포함할 수 있다(도 13b 참조). 게이트 길이 전체에 걸쳐 질화갈륨 재료 영역에 바로 접촉하여 단일 성분을 제공하는 것은 제2 성분이 게이트 길이의 일부분들에 바로 접촉해 있을 때 발생할 수 있는 손실을 제거함으로써 게이트 누설 전류를 줄이는 등의 전기적 속성을 향상시킬 수 있다. 또한, 복수의 성분들이 질화갈륨 재료 영역에 바로 접촉해 있을 때는, 게이트 전극의 쇼트카 장벽 높이가 금속 성분에 의해 제어될 수 없을 수 있다.

또한 소스 전극(14) 및 드레인 전극(16)은 Ti, Al, Pt 또는 Si뿐만 아니라 게이트 전극에 관련하여 전술된 것과 동일한 금속을 포함하는 임의의 적절한 도전성 재료로 형성될 수도 있다.

어떤 바람직한 실시예에서, 기판(20)은 실리콘 기판이다. 여기에 사용된 바와 같이, 실리콘 기판은 실리콘면을 포함하는 임의의 기판을 의미한다. 적절한 실리콘 기판의 예는 다른 것들 중에서 전체적으로 실리콘으로만 구성된 기판(예를 들어, 벌크 실리콘 웨이퍼(bulk silicon wafer)), SOI(silicon-on-insulator) 기판, SOS(silicon-on-sapphire) 기판 및 SIMOX 기판을 포함한다. 적절한 실리콘 기판은 또한 다이아몬드, AlN 또는 다른 다결정 재료 등의 또 다른 재료에 본딩(bonding) 되된 실리콘 웨이퍼를 갖는 기판을 포함한다. 다른 결정학적 방향을 갖는 실리콘 기판이 사용될 수도 있다. 몇몇 경우에는 실리콘(111) 기판이 바람직하다. 다른 경우에는 실리콘(100) 기판이 바람직하다.

사파이어, 탄화실리콘, 질화갈륨 및 질화알루미늄 기판을 포함하는 다른 유형의 기판들도 사용될 수 있음이 이해되어야 한다.

기판(20)은 임의의 적절한 치수를 가질 수 있으며, 그것의 특정한 치수는 응용에 따라 지시된다. 2인치(50mm), 4인치(100mm), 6인치(150mm) 및 8인치(200mm)가 적절한 지름이지만, 이에만 한정되는 것은 아니다. 몇몇 실시예에서, 기판(20)은 예를 들어 250 미크론보다 상대적으로 두껍다. 보다 두꺼운 기판은 일반적으로 얇은 기판에서 몇몇 경우에 발생할 수 있는 휨(bending)을 방지할 수 있다. 다른 실시예에서는 보다 얇은 기판(예를 들어, 250 미크론보다 얇음)이 사용된다.

전이층(22)은 질화갈륨 재료 영역(12)이 퇴적되기 전에 기판(20) 상에 형성될 수 있다. 전이층은 다음 중 하나 이상을 수행할 수 있다: 질화갈륨 재료와 기판 간의 열팽창율 차로부터 발생되는 열 스트레스를 낮춤으로써 질화갈륨 재료 영역(12) 내의 균열(crack) 형성을 줄이는 것; 질화갈륨 재료와 기판 간의 격자상수 차로부터 발생되는 격자 스트레스를 낮춤으로써 질화갈륨 재료 영역 내의 결합 형성을 줄이는 것; 및 기판과 질화갈륨 재료 간의 밴드 갭 차를 줄임으로써 기판과 질화갈륨 재료 영역 간의 도전성을 증가시키는 것. 질화갈륨 재료와 실리콘 간의 열팽창율과 격자상수에의 큰 차이 때문에, 실리콘 기판을 사용할 때 전이층이 존재하는 것이 특히나 바람직할 수 있다. 다양한 이유로 전이층은 또한 기판(20)과 질화갈륨 재료 영역 사이에 형성될 수 있음이 이해되어야 한다. 몇몇 경우에, 예를 들어, 실리콘 기판이 사용되지 않는 경우, 장치는 전이층을 포함하지 않을 수 있다.

전이층(22)의 성분은 적어도 부분적으로 기판의 유형 및 질화갈륨 재료 영역(12)의 성분에 따른다. 실리콘 기판을 사용하는 몇몇 실시예에서, 전이층은 층의 적어도 일부분에 걸쳐 다양한 성분을 갖는 조성-기울기를 갖는 전이층(compositionally-graded transition layer)을 포함하는 것이 바람직할 수 있다. 적절한 조성-기울기를 갖는 전이층은, 예를 들어 여기에 참조에 의해 통합된 미국특허번호 제6,649,287의 "Gallium Nitride Materials and Methods"(2000년 12월 14일)에 설명되어 있다. 조성-기울기를 갖는 전이층은 특히 질화갈륨 재료와 기판(예를 들어, 실리콘) 간의 열팽창율 차로부터 발생하는 열 스트레스를 줄임으로써 질화갈륨 재료 영역 내의 균열 형성을 줄이는데 효과적이다. 몇몇 실시예에서, 조성-기울기를 갖는 전이층은  $Al_xIn_yGa_{(1-x-y)}N$ ,  $Al_xGa_{(1-x)}N$  또는  $In_yGa_{(1-y)}N$  등의 질화갈륨의 합금으로 형성되며, 여기서  $0 \leq x \leq 1$ ,  $0 \leq y \leq 1$ 이다. 이러한 실시예에서, 합금의 요소(예를 들어, Ga, Al, In) 중 적어도 하나의 농도는 전형적으로 층의 단면 두께의 적어도 일부분에 걸쳐 다양하다. 몇몇 경우, 전이층은 단일결정 구조를 갖는다.

다른 실시예에서, 전이층(22)은 그것의 두께에 걸쳐 일정한(즉, 다양하지 않은) 성분을 갖는다. 이러한 전이층은 또한 베퍼층으로 언급될 수도 있다.

몇몇 실시예에서, 장치(10)는 또한 도면에 나타내지 않은 다른 층들도 선택적으로 포함할 수 있다. 예를 들어, 장치(10)는 하나 이상의 중간층을 포함할 수 있다. 예를 들어, 중간층은 기판과 전이층(예를 들어, 조성-기울기를 갖는 전이층) 사이에 및/또는 전이층과 질화갈륨 재료 영역 사이에 형성될 수 있다. 예를 들어, 적절한 중간층은 상기 참조에 의해 통합된 미국 특허번호 제6,649,287호에 설명 및 나타나 있다. 몇몇 실시예에서, 중간층은 질화갈륨 합금( $Al_xIn_yGa_{(1-x-y)}N, Al_xGa_{(1-x)}$  N 또는  $In_yGa_{(1-y)}N$  등)의 일정한 성분, 질화알루미늄 또는 질화알루미늄 합금을 가질 수 있다. 몇몇 경우에, 중간층(들)은 단일결정 구조를 갖는다.

질화갈륨 재료 영역(12)은 적어도 하나의 질화갈륨 재료 층을 포함한다. 여기에 사용된 바와 같이, "질화갈륨 재료"란 구문은 질화갈륨(GaN) 및 다른 것들 중에서  $Al_xGa_{(1-x)}N$ ,  $In_yGa_{(1-y)}N$ ,  $Al_xIn_yGa_{(1-x-y)}N$ ,  $GaAs_aP_bN_{(1-a-b)}$ ,  $Al_xIn_yGa_{(1-x-y)}As_aP_bN_{(1-a-b)}$  등의 임의의 합금을 의미한다. 전형적으로, 비소 및/또는 인이 존재할 경우, 그들은 농도가 낮다(즉, 5 무게 페센트 미만). 어떤 바람직한 실시예에서, 질화갈륨 재료는 고농도의 갈륨을 가지며, 알루미늄 및/또는 인듐을 거의 포함하지 않거나 아예 포함하지 않는다. 고농도 갈륨의 실시예에서,  $(x+y)$ 의 합은 0.4 미만이거나, 0.2 미만이거나, 0.1 미만이거나, 심지어는 그 미만일 수 있다. 몇몇 경우에서, 질화갈륨 재료 층은 GaN 성분을 갖는 것이 바람직하다(즉,  $x+y=0$ ). 질화갈륨 재료는 n형 또는 p형 도핑(dopping)될 수 있거나, 진성(intrinsic)일 수 있다. 적절한 질화갈륨 재료는 상기 참조에 의해 통합된 미국특허번호 제6,649,287호에 설명되어 있다.

몇몇 경우에, 질화갈륨 재료 영역(12)은 오직 하나의 질화갈륨 재료 층만을 포함한다. 다른 경우에, 질화갈륨 재료 영역(12)은 2개 이상의 질화갈륨 재료 층을 포함한다. 상이한 층들은 반도체 장치의 상이한 영역을 형성할 수 있다. 질화갈륨 재료 영역(12)은 또한 다른 III-V 족 화합물 또는 합금, 산화층 및 금속층 등의 질화갈륨 재료 성분을 갖지 않는 하나 이상의 층을 포함할 수도 있다.

질화갈륨 재료 영역(12)은 그것 내에 장치의 형성을 허용하기에 충분히 품질이 높다. 가급적 질화갈륨 재료 영역(12)은 낮은 균열 레벨 및 낮은 결함 레벨을 갖는다. 전술된 바와 같이, 전이층(22)(특히 조성-기울기를 갖는 것일 경우)은 균열 및/또는 결함 형성을 줄일 수 있다. 몇몇 실시예에서, 질화갈륨 재료 영역은 약  $10^9$  결함/cm<sup>2</sup>를 갖는다. 낮은 균열 레벨을 갖는 질화갈륨 재료는 상기 참조에 의해 통합된 미국특허번호 제6,649,287호에 설명되어 있다. 몇몇 경우, 질화갈륨 재료 영역은  $0.005\mu m/\mu m^2$  미만의 균열 레벨을 갖는다. 몇몇 경우, 질화갈륨 재료 영역은  $0.001\mu m/\mu m^2$  미만의 매우 낮은 균열 레벨을 갖는다. 특정한 경우에, 질화갈륨 재료 영역은  $0.0001\mu m/\mu m^2$  미만의 균열 레벨로 정의된 바와 같이 실제로 균열이 없는 것이 바람직할 수 있다.

어떤 경우, 질화갈륨 재료 영역(12)은 단일결정 구조를 갖는 층 또는 층들을 포함한다. 몇몇 경우, 질화갈륨 재료 영역은 우르짜이트(Wurtzite)(우방정계) 구조를 갖는 하나 이상의 층들을 포함한다.

질화갈륨 재료 영역(12)의 두께 및 다른 층들의 개수는 적어도 부분적으로 특정한 장치의 요구사항에 의해 지시된다. 최소한, 질화갈륨 재료 영역(12)의 두께는 원하는 장치의 형성을 허용할만큼 충분하다. 항상 그런 것은 아니지만, 질화갈륨 재료 영역(12)은 일반적으로 0.1 미크론 이상의 두께를 갖는다. 다른 경우, 질화갈륨 재료 영역(12)은 0.5 미크론 이상의, 0.75 미크론 이상의, 0.1 미크론 이상의, 2.0 미크론 이상의, 또는 심지어 5.0 미크론 이상의 두께를 갖는다.

도 3은 본 발명의 다른 실시예에 따른 반도체 장치(40)를 나타낸다. 도 3의 실시예에서, 비아(26)는 전극 형성층(24)의 두께를 통한 길의 일부분만으로 연장된다. 따라서, 전극 형성층 일부분은 게이트 전극(18)과 질화갈륨 재료 영역(12) 사이에 남아있다. 몇몇 실시예에서, 전극 형성층은 산화실리콘, 질화실리콘, 폴리이미드, 다른 유전체 재료 또는 이를 성분의 조합(예를 들어, 산화실리콘 및 질화실리콘) 등의 절연 재료로 형성되는 것이 바람직하다. 전극 형성층이 절연 재료로 형성되는 실시예에서, 장치(40)는 MISFET(metal-insulator-semiconductor)를 형성한다.

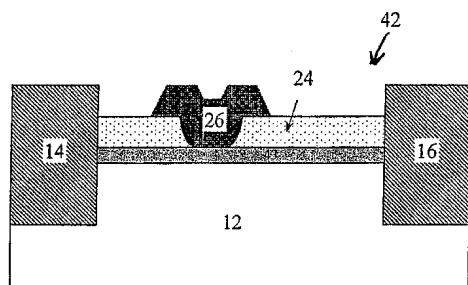

도 4는 본 발명의 다른 실시예에 따른 반도체 장치(42)를 나타낸다. 장치(42)는 전극 형성층(24)과 질화갈륨 재료 영역(12) 사이에 형성된 층(43)을 포함한다. 층(43)은 전극 형성층(24)과 다른 구조물을 갖는다. 몇몇 경우에, 층(43)은 부동태층인 것이 바람직하다. 적절한 부동태층 구성이 전술되었다. 몇몇 경우에는, 2개 이상의 층이 전극 형성층과 질화갈륨 재료 영역 사이에 형성될 수 있다는 것이 이해되어야 한다.

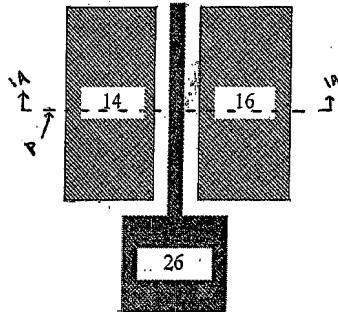

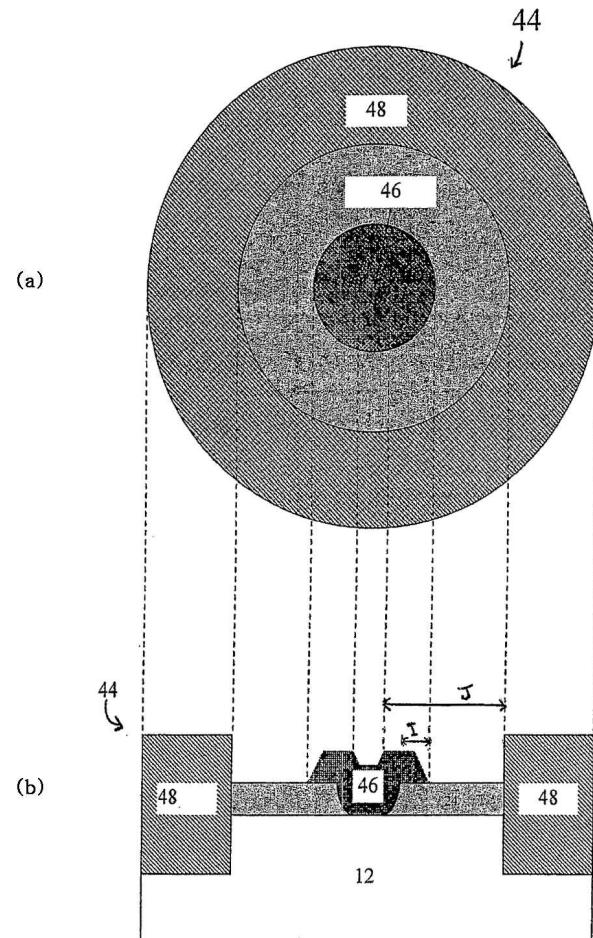

도 5a 및 5b는 본 발명의 다른 실시예에 따른 반도체 장치(44)를 나타낸다. 이 실시예에서, 장치(44)는 비아(26) 내에 (부분적으로) 형성된 쇼트키 전극(46)(즉, 쇼트키 컨택트)을 포함하는 쇼트키 다이오드이다. 장치(44)는 또한 그 구조의 지름 둘레에 형성된 옴 전극(48)을 포함한다.

쇼트키 다이오드 실시예(또는 다른 장치)에서 FET 실시예에 관련하여 전술된 각 Y 및 Z의 범위도 또한 중요하다. 특히, 전술된 범위 내의 Y 및 Z의 값은, 다른 장점들 중에서 비아를 전극 재료로 완벽하게 채우는 것을 촉진시킨다. 각 Y 및 Z의 최적 값(들)은 특정한 장치에 따르며, 또한 다른 설계 매개변수에 따를 수 있다. 후술된 바와 같이, 전극 형성층에 청 단계는 각 Y 및 Z의 원하는 값을 제공하도록 제어될 수 있다.

쇼트키 전극(46)은 또한, 도 1a 및 1b의 FET 실시예에 관련하여 설명된 바와 같이 하지 전극 형성층(24)에서 돌출된 일부분을 포함하는 T자형 설계를 갖는 것이 바람직할 수 있다. 돌출 거리(i)가 장치의 항복 전압에 영향을 주는데 특히 중요하다고 결정됐다. 전극 형성층에서 옴 전극 방향으로 돌출된 쇼트키 전극의 일부분은 다른 유익한 효과들 중에서 장치의 항복 전압을 증가시키는 필드 플레이트로 기능할 수 있다. 예를 들어 (i)가 쇼트키 전극과 옴 전극 사이의 거리 (j)의 약 2퍼센트 내지 약 60퍼센트 사이일 때 항복 전압이 증가될 수 있다는 것이 알려져 있다. 몇몇 경우, 장치의 항복 전압을 더욱 최적화하기 위해 (i)는 (j)의 약 10 퍼센트 내지 약 50 퍼센트 사이인 것이 바람직할 수 있다. (j)의 최적 값(들)은 특정한 장치에 따르며, 또는 다른 설계 매개변수에 따를 수 있다.

본 발명의 쇼트키 다이오드는 또한 원이 아닌 레이아웃을 가질 수 있다는 것이 이해되어야 한다.

또한, 본 발명이 트랜지스터 및 쇼트키 다이오드에 관련하여 전술되었지만, 본 발명은 다른 장치들도 포함할 수 있다는 것이 이해되어야 한다. 예를 들어, 다른 전기 또는 전기광학 장치가 전극 형성층(몇몇 경우에 부동태층으로도 기능할 수 있음)을 사용할 수 있다. 적절한 장치는 쇼트키 정류기, 건 효과 다이오드(Gunn-effect diode), 버랙터 다이오드(varactor diode), 전압 제어 발진기, 광 방출 다이오드, 레이저 또는 광검출기를 포함한다.

도 6-11은 본 발명의 일 예시된 방법에 따른 상이한 프로세싱 단계 이후의 결과적인 반도체 구조물의 단면도를 나타낸다. 도 6-11이 본 발명의 일 방법에 따른 FET의 생성을 나타내지만, 유사한 방법 단계들을 사용하여 본 발명의 다른 장치들도 생성될 수 있다는 것도 또한 이해되어야 한다.

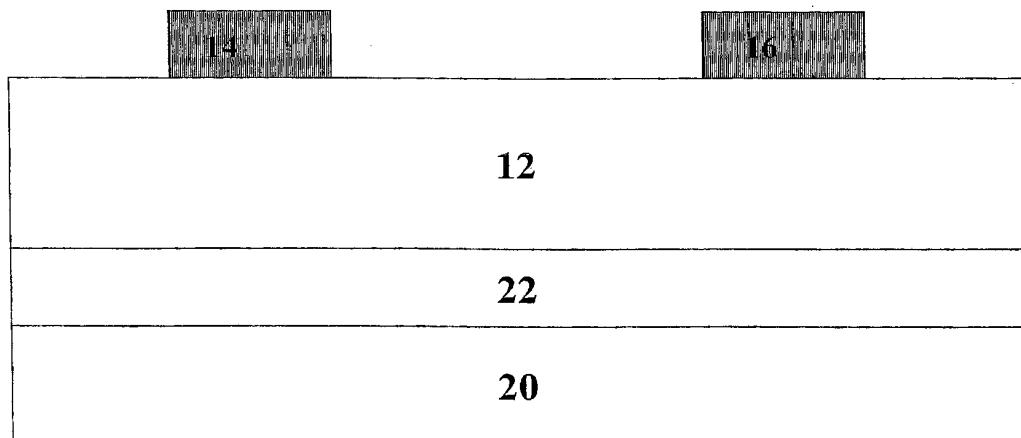

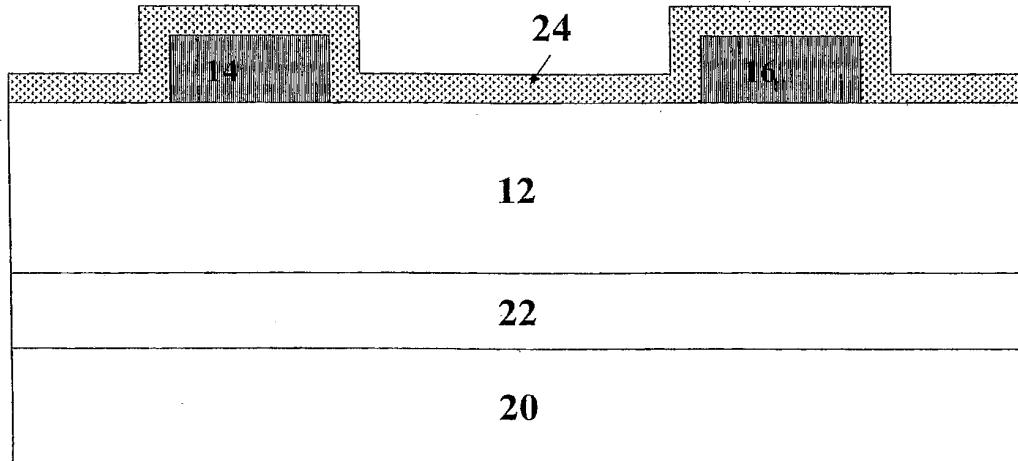

도 6은 기판(20) 상의 질화갈륨 재료 영역(12)과 전이층(22)의 퇴적, 및 소스 전극(14)과 드레인 전극(16)의 퇴적 이후의 구조의 단면도를 나타낸다.

전이층(22) 및 질화갈륨 재료 영역(12)은 다른 기술들 중에서 예를 들어 MOCVD(metalorganic chemical vapor deposition), MBE(molecular beam epitaxy) 및 HVPE(hydride vapor phase epitaxy)를 사용하여 기판(20) 상에 퇴적될 수 있다. 소정의 경우에는, MOCVD 프로세스가 바람직할 수 있다. 실리콘 기판 위에 조성-기울기를 갖는 전이층 및 질화갈륨 재료 영역을 형성하기 위한 적절한 MOCVD 프로세스가 상기 참조에 의해 통합된 미국특허번호 제6,649,287호에 설명되어 있다. 질화갈륨 재료 영역(12)이 상이한 계층들을 가질 때, 몇몇 경우에는 단일 퇴적 단계(예를 들어, MOCVD 단계)를 사용하여 전체 영역(12)을 형성하는 것이 바람직할 수 있다. 단일 퇴적 단계를 사용할 때는, 상이한 층들을 형성하기 위해 프로세싱 매개변수가 알맞은 시간에 적절하게 바뀐다. 어떠한 바람직한 경우에는, 단일 성장 단계를 사용하여 전이층 및 질화갈륨 재료 영역이 형성될 수 있다.

예를 들어, 참조에 의해 여기에 통합된 미국특허 번호 제6,051,849호에 설명된 바와 같이, 본 발명의 다른 실시예에서(나타내지 않음), 질화갈륨 재료 영역을 형성하기 위해 마스크 개구를 통한 후 측면으로 마스크 위에 하지 질화갈륨층을 성장시키는 것에 관련된 LEO(lateral epitaxial overgrowth) 기술을 사용하여 질화갈륨 재료 영역(12)을 성장시킬 수 있다. 마스크 영역은 도면에 나타나지 않는다.

예를 들어, 참조에 의해 여기에 통합된 미국특허번호 제6,177,688호에 설명되어 있는 바와 같이, 본 발명의 다른 실시예에서(나타내지 않음), 인접한 측벽으로부터의 성장이 유착되어 질화갈륨 재료 영역을 형성할 때까지, 질화갈륨 재료 포스트의 측벽을 트랜치(trench) 내에 성장시키는 것에 관련된 펜더에피택셜 기술(pendeloepitaxial technique)을 사용하여 영역(12)을 성장시킬 수 있다. 이러한 측면 성장 기술로, 매우 낮은 결함 밀도를 갖는 질화갈륨 재료 영역이 생성될 수 있다.

예를 들어, 질화갈륨 재료 영역의 적어도 일부분은 약  $10^5$  결함/cm<sup>2</sup> 미만의 결함 밀도를 가질 수 있다.

소스 전극(14) 및 드레인 전극(16)은 증착 기술 등의 알려진 기술을 사용하여 질화갈륨 재료 영역 상에 퇴적될 수 있다. 전극이 2개의 금속을 포함하는 경우에, 금속은 전형적으로 연속적인 단계들에서 퇴적된다. 퇴적된 금속층은 전극을 형성하기 위한 종래 방법을 사용하여 패터닝될 수 있다.

도 6에 나타낸 구조는, 예를 들어 구조가 약 500°C 내지 1000°C 사이의 온도로 가열되는 RTA(rapid thermal annealing) 단계에 영향을 받을 수 있다. 몇몇 경우에, 온도는 약 800°C 내지 900°C 사이일 수 있다. RTA 단계는 소스 및 드레인 전극 내의 상이한 재료들의 합금화를 촉진시키고, 이러한 전극과 하지 질화갈륨 재료 영역 간의 초기 접촉의 형성을 촉진시키기 위해 수행된다.

도 7은 전극 형성층(24)이 퇴적된 후의 반도체 구조물의 단면도를 나타낸다. 나타낸 바와 같이, 전극 형성층(24)은 확실하게 질화갈륨 재료 영역(12)을 덮는다. 전극 형성층은 임의의 적절한 기술을 사용하여 퇴적될 수 있다. 사용된 기술은 부분적으로 전극 형성층의 구성에 따른다. 적절한 기술은 CVD, PECVD, LP-CVD, ECR-CVD, ICP-CVD, 증착 및 스퍼터링(sputtering)을 포함하지만, 이에만 한정되는 것은 아니다. 전극 형성층이 질화실리콘 재료로 형성된 때는, PECVD를 사용하여 층을 퇴적시키는 것이 바람직할 수 있다.

전술된 바와 같이, 게이트 전극을 형성하기 전에 전극 형성층을 퇴적시키는 것은 유리하게도 게이트 전극을 형성하는 단계를 포함하는 다음의 프로세싱 단계 동안 전극 형성층이 질화갈륨 재료 영역을 부동태화 및 보호할 수 있게 한다. 본 발명의 다른 방법에서는, 소스 및 드레인 전극이 퇴적되기 전에 전극 형성층이 퇴적될 수 있다는 것이 이해되어야 한다. 이러한 실시예에서, 예를 들어 에칭 기술을 사용하여 각각의 비아가 전극 형성층 내에서 열려, 소스 및 드레인 전극과 하지 질화갈륨 재료 영역 사이가 접촉될 수 있다.

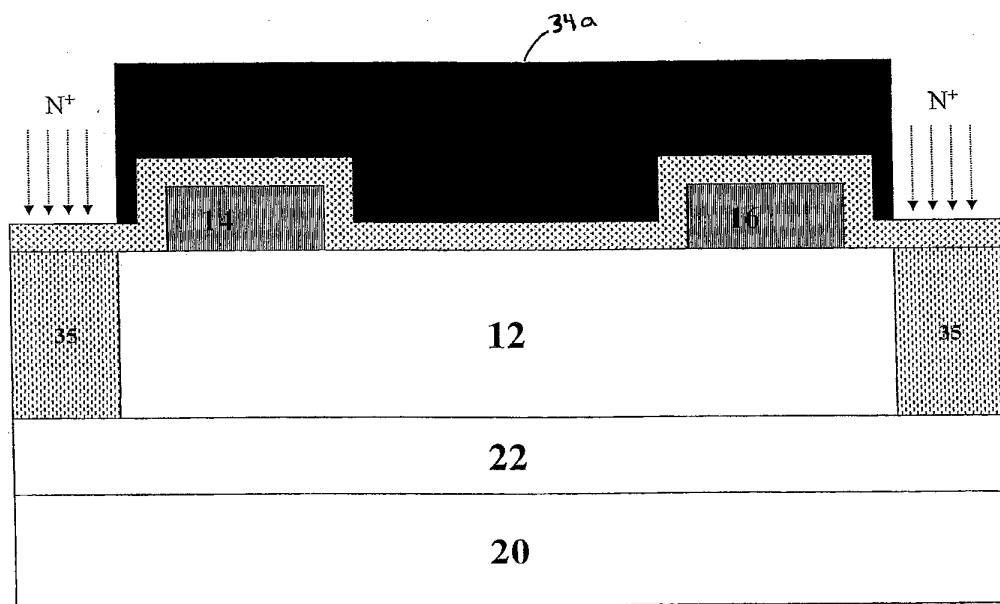

도 8은 이온 주입 단계 동안의 구조의 단면도를 나타낸다. 드레인 및 소스 전극의 각 층 상의 영역을 노출시키기 위해 감광성 수지막층(34)이 패터닝된다. 나타낸 실시예에서, 질소 이온이 노출된 영역에 주입되어 그 영역 아래에 비결정질화된(amorphized) 질화갈륨 재료 영역(35)이 형성된다. 비결정질화된 영역은 동일한 웨이퍼 상에 형성된 인접한 장치로부터 장치를 전자적으로 격리시킨다.

주입 단계에 다른 유형의 이온들이 또한 사용되거나, 인접한 장치를 격리하기 위한 다른 기술들이 사용될 수 있다. 몇몇 경우에, 인접한 장치들은 질화갈륨 재료 영역의 일부분뿐만 아니라 전극 형성층을 제거하는 에칭 단계를 사용해 격리될 수 있다. 최적의 에칭 깊이 값은 특정한 장치에 따르며, 또한 다른 설계 매개변수에 따를 수도 있다. 다른 경우에, 인접한 장치를 격리시킬 필요가 없을 수 있으며, 따라서 주입 단계가 요구되지 않는다.

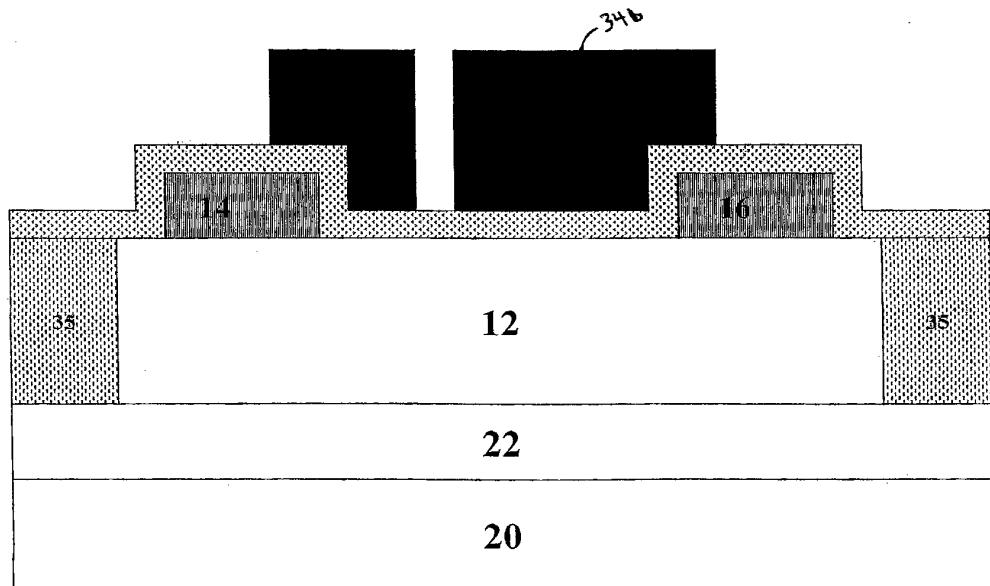

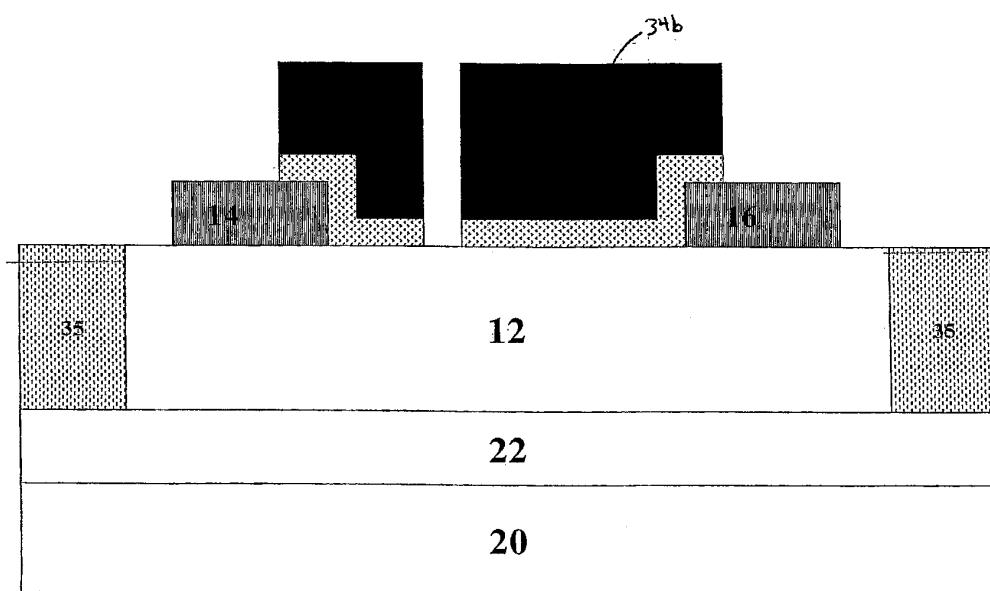

도 9는 감광성 수지막층(34a)이 제거된 후 제2 감광성 수지막층(34b)이 패터닝된 구조의 단면도를 나타낸다.

도 10은 감광성 수지막층(34b)이 제거되고 전극 형성층(24)이 에칭된 후의 반도체 구조물의 단면도를 나타낸다. 이 에칭 단계는 비아(26)를 형성한다. 플라즈마 에칭 기술을 사용하여 제어된 치수로 비아를 형성하는 것이 바람직하다. 어떠한 종래의 건습 화학 에칭 기술은 중요한 비아 치수를 충분히 제어하지 않음이 발견되었다. 몇몇 방법에서는, 고밀도 플라즈마 기술(예를 들어, ICP 또는 ECR)을 사용하여 플라즈마가 생성된다. 다른 방법에서는, RIE 또는 CAIBE 기술이 사용될 수 있다. 이온화되어 플라즈마를 형성할 수 있는 적절한 가스는 불소가 첨가된 탄화수소, 불소가 첨가된 유황-기반 가스, 산소 및 아르곤을 포함한다. 에칭을 시작하기 전, 산소-기반 또는 아르곤-기반 플라즈마 처리를 통해 전극 형성층의 표면 상의 임의의 남아있는 탄화수소 종류를 제거할 수 있다.

전술된 것과 같은 원하는 치수 및 프로파일을 갖춘 비아(26)를 형성하도록 에칭 조건을 제어할 수 있다. 하나의 중요한 프로세싱 매개변수는 플라즈마 종류의 평균 자유 경로를 대략적으로 결정하고 이에 따라 에칭의 방향성을 제어하는 플라즈마 내의 압력 조건이다. 에칭의 방향성 또는 이방성은 다른 비아 치수들(예를 들어, a, b) 중에서 비아의 프로파일, 각 Y 및 각 Z를 제어한다. 각 Y 및 Z를 갖는 비아를 생성하기에 적절한 압력 조건은 약 1 내지 100mTorr 사이일 수 있음이 밝혀졌다.

RF 전력은 건습 에칭 프로세스에 대한 또 다른 중요한 프로세스 매개변수이다. RF 전력은 처리중인 구조의 표면 상에 충돌하는 종류의 이온 에너지에 영향을 미친다. 이온 주입은 에칭의 이방성에 영향을 미치며, 이에 따라 다른 비아 치수들(예를 들어, a, b) 중에서 비아의 프로파일, 각 Y 및 각 Z를 제어한다. 몇몇 경우에, 약 50Watt 미만의 RF 전력을 유지하는 것이 바람직할 수 있다. 몇몇 경우에는 약 10Watt 미만의 RF 전력을 유지하는 것이 바람직할 수 있다. 상기 범위 내의 RF 전력을 사용하여, 비아를 형성할 때 다른 한편으로 발생될 수 있는 질화갈륨 재료 영역에 대한 플라즈마 유도 손상을 제한 또는 방지할 수 있다.

ICP 전력은 ICP 플라즈마를 사용하는 에칭 프로세스에 대한 다른 중요한 프로세싱 매개변수이다. ICP 전력은 플라즈마 챔버(plasma chamber) 벽 외부의 유도성 코일에 적용되는 전력으로서 측정된다. 이 전력은 조밀한 플라즈마를 한정 및 생성하는 자계를 생성한다. 따라서, ICP 전력은 다른 매개변수들 중에서 다음에 전극 형성층의 에칭 속도를 제어하는데 사용될 수 있는 플라즈마 밀도(이온 에너지에 상대적으로 독립적임)를 제어한다. 이 방식에서, 에칭 속도는 실제로 비아 치수를 조정하는 비아의 프로파일로부터 분리될 수 있다. 몇몇 경우에, ICP 전력을 약 5W 내지 약 300W 사이로 유지하는 것이 바람직함이 밝혀졌다. 몇몇 경우에는, ICP 전력을 약 10W 내지 약 100W 사이로 유지하는 것이 바람직할 수 있다. 이 범위 이상의 ICP 전력 값은 감광성 수지막층(34b)에 불리한 효과를 발생시킬 수 있으며, 이 범위 이하의 ICP 전력 값은 전극 형성 층(24)의 에칭 속도를 수용불가능한 레벨로 낮출 수 있다.

ICP 플라즈마를 사용하는 어떤 프로세스에서, RF 전력은 전술된 바람직한 영역 내에 있을 수 있으며, 몇몇 경우에는 0일 수 있다는 것이 이해되어야 한다.

이 에칭 단계는 또한 주입된 영역들 위뿐만 아니라 소스 및 드레인 전극 상의 영역들을 포함하는 다른 노출된 영역으로부터 전극 형성 층(24)을 제거할 수 있다.

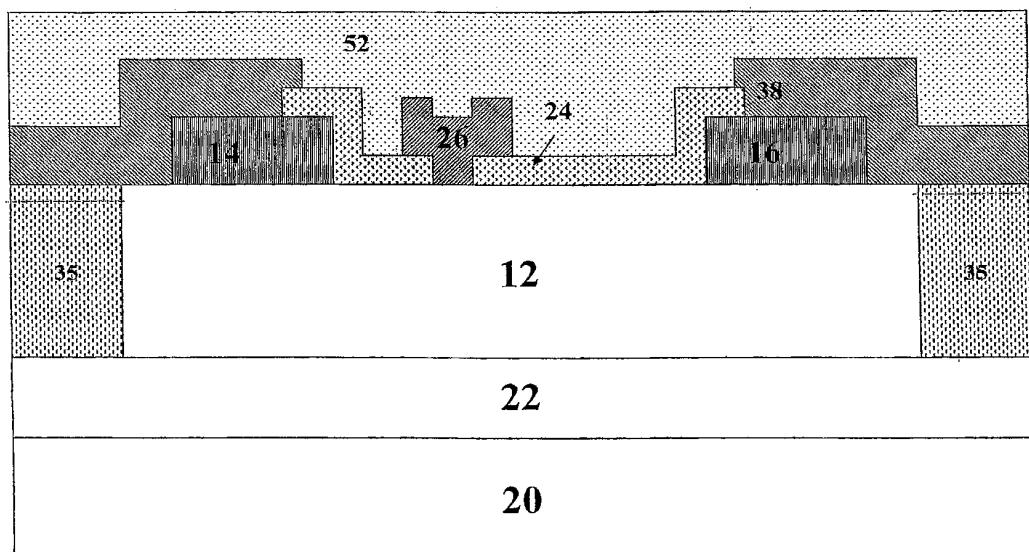

도 11은 게이트 전극 및 상호접속 패터닝, 및 퇴적 단계 이후의 반도체 구조물의 단면도를 나타낸다. 패터닝 단계는 원하는 소스 전극 층 돌출 거리(d) 및 드레인 전극 층 돌출 거리(e)를 제공하도록 제어된다. 종래 패터닝 및 퇴적 단계들이 사용될 수도 있다. 게이트 및 상호접속(38)은 별개의 단계 또는 같은 단계에서 패터닝 및 퇴적될 수 있다.

도 12는 캡슐화층(52)이 퇴적된 이후의 반도체 구조물의 단면도를 나타낸다.

본 발명이 여기에 구체적으로 설명된 것들 이외의 다른 방법들도 포함한다는 것이 이해되어야 한다. 또한, 전술된 방법에 대한 변형물들은 당업자들에게 알려진 것이며, 본 발명의 영역 내에 속하는 것이다.

다음의 예들은 예시적인 것일 뿐 제한적인 것은 아니다.

### 예 1

이 예는 본 발명의 FET 장치의 속성을 종래 FET 장치에 비교함으로써, 전기적 속성에 대한 게이트 전극 구성 및 모양의 효과를 나타낸다.

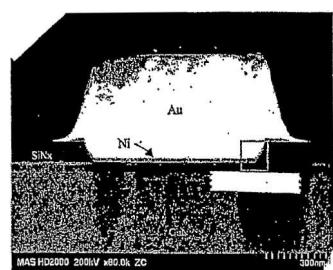

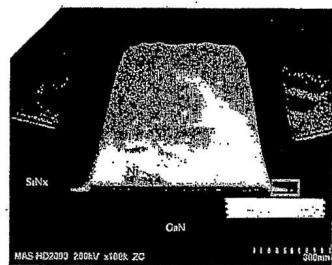

도 13a는 본 발명의 FET 장치의 T자형 게이트 전극의 단면도를 나타낸다. 단면 내에서 비아의 상단에서 비아의 하단으로 갈수록 작아지는 비아 내에 게이트 전극이 형성된다. 전극은 니켈 성분 및 금 성분으로 형성된다. 니켈 성분은 게이트 일부분들을 포함하는 전체 게이트 길이에 걸쳐 질화갈륨 재료 영역에 바로 접촉해 있다.

도 13b는 종래 FET 장치의 사다리꼴형 게이트 전극의 단면도를 나타낸다. 전극은 니켈 성분 및 금 성분으로 형성된다. 니켈 성분은 게이트 길이의 내부에 바로 접촉해 있으며, 금 성분은 게이트 길이의 에지부에 바로 접촉해 있다.

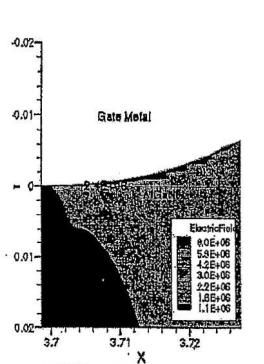

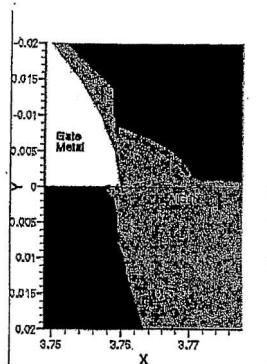

도 13c 및 13d 각각은 도 13a 및 13b의 게이트 전극들의 드레인 에지에서의 2차원 전기장 시뮬레이션이다. 시뮬레이션은  $V_{DS}=28$  및  $V_{GS}=0V$ 에서 수행됐다. 최고 전기장은 도 13c의 게이트 전극에 대해서  $2.4 \times 10^6 V/cm$ 이고, 도 13d의 게이트 전극에 대해서  $6.4 \times 10^6 V/m$ 였다.

종래 FET 장치에 비교되는 본 발명의 FET 장치에 대한 감소된 최고 전기장은 게이트 전극의 드레인 에지에 모이는 감소된 전기장으로부터 구해진다. 이러한 감소는 게이트 전극의 모양, 특히 비아 측벽의 모양에 기인하며, 이것은 비아의 단면적이 비아의 상단으로부터 비아의 하단으로 갈수록 낮아지게 한다. 이러한 감소는 증가된 동작 전압 및/또는 감소된 게이트 누설 전류를 포함하는 개선된 전극 형성 특성을 이끌어낸다.

이 예는 본 발명의 FET 장치가 종래 FET 장치에 비해 향상된 전자적 속성을 가질 수 있다는 것을 입증한다.

### 예 2

이 예는 본 발명의 FET 장치의 드레인 전극 층 돌출 거리(e)를 다양하게 하는 것에 대한 영향을 나타낸다.

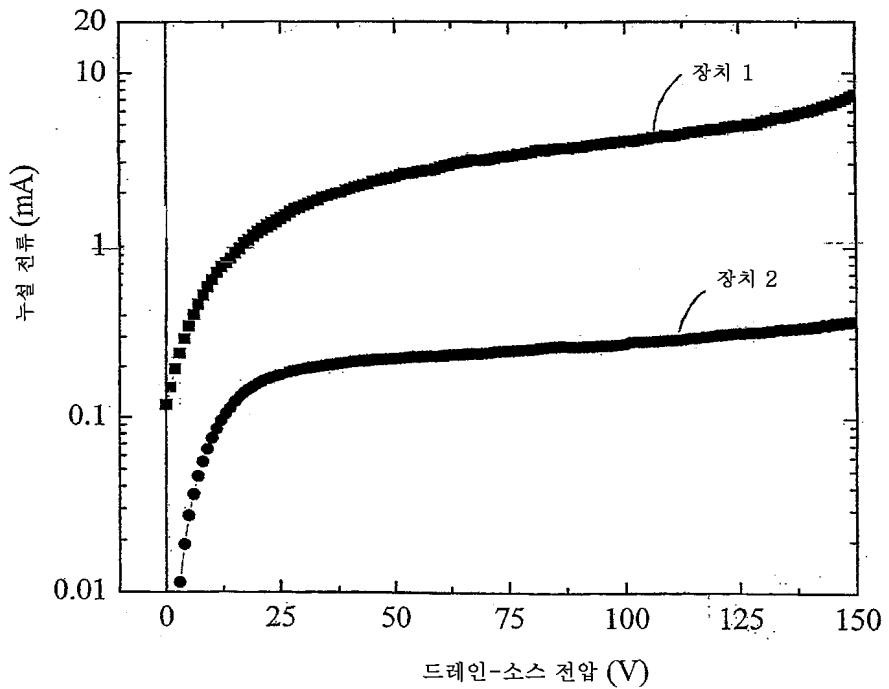

드레인 누설 전류는 도 1a 및 1b에 나타낸 장치와 같은 동일한 일반적인 설계를 갖는 2개의 FET 장치(장치 1 및 장치 2)에 대한 드레인-소스 전압의 기능으로서 측정되었다. 측정 동안, 게이트 전압은 -8 볼트의 값에서 일정하게 유지되었다.

장치 1 및 2는 다음의 치수를 포함한다:

$a = 0.7$  미크론

$b = 0.9$  미크론

$a/b = .78$

$d = 0.1$  미크론

$f = 1.0$  미크론

$g = 3.0$  미크론

$h = 5.2$  미크론

$y = 100^\circ$

$z = 20^\circ$

장치 1은 게이트 드레인 간격( $g$ )의 5%인 0.15 미크론의 드레인 전극 측 돌출 거리( $e$ )를 포함했다.

장치 2는 게이트 드레인 간격( $g$ )의 20%인 0.60 미크론의 드레인 전극 측 돌출 거리( $e$ )를 포함했다.

도 14는 장치 1 및 2의 드레인 누설 전류를 드레인-소스 전압의 함수로서 나타낸다. 양 장치에서, 드레인 누설 전류는 일반적으로 이러한 게이트들을 갖는 FET 장치에 대한 모든 드레인-소스 전압에서 10mA 이하였다. 장치 2 내의 드레인 누설 전류는 장치 1 내의 드레인 누설 전류보다 상당히 낮다. 이 장치 설계에 대해서, 돌출 거리( $e$ )를 게이트 드레인 간격( $g$ )의 5%로부터 게이트 드레인 간격의 20%로 증가시키면, 드레인 누설 전류가 줄어든다.

이러한 발명의 적어도 하나의 실시예에 대한 설명된 몇몇 양태들을 통해, 당업자들은 다양한 변형물, 수정물 및 개선들을 쉽게 생각해낼 것이란 것이 자명하다. 이러한 대안물, 수정물 및 개선물들은 이러한 개시의 일부로 의도되며, 본 발명의 취지 및 영역 내에 속하도록 의도된다. 따라서, 상기 설명 및 도면들은 단지 예일 뿐이다.

### 도면의 간단한 설명

도 1a는 본 발명의 일 실시예에 따라 전극 형성층을 포함한 질화갈륨 재료 장치의 단면도.

도 1b는 도 1a의 질화갈륨 재료 장치의 평면도.

도 2는 본 발명의 일 실시예에 따른 전극 형성층의 프로파일(profile)을 나타내는 도면.

도 3은 본 발명의 일 실시예에 따라 전극 형성층의 두께에 걸쳐 일부분만을 연장시킨 비아를 포함하는 전극 형성층을 포함하는 질화갈륨 재료 장치의 단면도.

도 4는 본 발명의 일 실시예에 따라 전극 형성층과 질화칼륨 재료 영역 사이에 형성된 부동태층을 포함하는 질화갈륨 재료 장치의 단면도.

도 5의 (a) 및 (b) 각각은 본 발명의 일 실시예에 따른 쇼트키 다이오드의 평면도 및 단면도.

도 6은 본 발명의 방법에 따른 금속화 단계 이후의 반도체 구조물의 단면도.

도 7은 본 발명의 방법에 따른 전극 형성층의 퇴적 이후의 반도체 구조물의 단면도.

도 8은 본 발명의 방법에 따른 이온주입 단계 동안의 반도체 구조물의 단면도.

도 9는 본 발명의 방법에 따른 감광성 수지막 패터닝 단계(photoresist patterning step) 이후의 반도체 구조물의 단면도.

도 10은 본 발명의 방법에 따른 전극 형성층 에칭 단계 이후의 반도체 구조물의 단면도.

도 11은 본 발명의 방법에 따른 금속화 단계 이후의 반도체 구조물의 단면도.

도 12는 본 발명의 방법에 따른 캡슐화 단계 이후의 반도체 구조물의 단면도.

도 13a은 예1에 설명된 것과 같은 본 발명의 FET 장치의 T자형 게이트 전극의 단면도.

도 13b는 예1에 설명된 것과 같은 종래 FET 장치의 사다리꼴형 게이트 전극의 단면도.

도 13c 및 13d는 각각 예1에 설명된 것과 같은, 도 10a 및 10b의 게이트 전극들의 드레인 에지에서의 2차원 전기장 시뮬레이션.

도 14는 예2에 설명된 장치에 대하여 드레인 누설 전류를 드레인-소스 전압의 함수로서 나타내는 도면.

도 15는 본 발명의 일 실시예에 따른, 부동태층의 두께보다 얇은 게이트 전극 높이를 포함하는 질화갈륨 재료 장치의 단면도.

도면

도면1a

도면1b

도면2

도면3

도면4

도면5

도면6

### 도면7

## 도면8

도면9

도면10

도면11

도면12

도면13a

도면13b

도면13c

도면13d

### 도면14

### 도면15