(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년03월27일

(11) 등록번호 10-1378007

(24) 등록일자 2014년03월19일

- (51) 국제특허분류(Int. Cl.)

*H03M 1/12* (2006.01) *H03M 1/64* (2006.01)

(21) 출원번호 10-2010-0060412

(22) 출원일자 2010년06월25일

심사청구일자 2013년06월13일

(65) 공개번호 10-2011-0047961

(43) 공개일자 2011년05월09일

(30) 우선권주장

12/609,031 2009년10월30일 미국(US)

(56) 선행기술조사문현

DE4308000 A1\*

EP02031791 A1\*

\*는 심사관에 의하여 인용된 문현

- (73) 특허권자

엘에스아이 코포레이션

미국 캘리포니아 95131, 새너제이, 라이더 파크

드라이브 1320

(72) 발명자

리우 진펭

미국 콜로라도 80503 롱몬트 캐논 마운틴 드라이

브 1434

송 홍웨이

미국 콜로라도 80503 롱몬트 캐논 마운틴 드라이

브 1613

(74) 대리인

장훈

전체 청구항 수 : 총 10 항

심사관 : 성경아

## (54) 발명의 명칭 타이밍 복구 루프를 위한 위상 검출기

**(57) 요약**

일 실시예에서, (하드-드라이브) 판독 채널은 타이밍 복구 루프에서 사용된 위상 검출기를 갖는다. 위상 검출기는 수신된 LLR(log-likelihood ratio) 신호로부터 부호 비트 및 신뢰도 값을 사용하여 평균값을 생성시킨다. 이 평균값은 부분 응답 타겟으로 컨볼빙되어 추정된 타이밍 에러 신호를 생성시킨다. 하드-드라이브 판독 채널에서 실행될 때, 위상 검출기는 더 작은 LOLRs(loss-of-lock rates)에 의하여 타이밍 복구를 허용한다.

**대 표 도**

## 특허청구의 범위

### 청구항 1

신호 프로세서에 있어서,

아날로그 입력 신호를 디지털 출력 신호로 변환하는 신호 처리 경로로서, 상기 신호 처리 경로는 등화된 값들 및 멀티비트 소프트 값들을 생성하고, 각각의 멀티비트 소프트 값은 부호 비트 및 멀티비트 신뢰도 값을 가지는, 상기 신호 처리 경로; 및

상기 아날로그 입력 신호를 샘플링하기 위하여 상기 신호 처리 경로에 의해 사용된 샘플링 클록 신호를 생성하기 위해 상기 부호 비트들과, 상기 소프트 값들의 상기 멀티비트 신뢰도 값들 중 하나 이상의 비트들을 사용하는 타이밍 복구 루프를 포함하며,

상기 타이밍 복구 루프는 상기 부호 비트들과 상기 소프트 값들의 상기 멀티비트 신뢰도 값들 중 하나 이상의 비트들에 기초하여 추정된 타이밍 에러 신호들을 생성하는 위상 검출기를 포함하고, 상기 추정된 타이밍 에러 신호는 상기 샘플링 클록 신호를 생성하기 위해 로컬발진기(local oscillator; LO) 클록 신호를 조정하는데 사용되며,

상기 위상 검출기는:

상기 부호 비트들과 상기 소프트 값들의 상기 멀티비트 신뢰도 값들 중 하나 이상의 비트들에 기초하여 평균값들을 생성하는 모듈;

필터링된 값들을 생성하기 위해 상기 평균값들을 필터링하는 필터;

지연된 등화된 값들(equalized values)을 생성하기 위해 상기 신호 처리 경로로부터 상기 등화된 값들을 지연시키는 제 1 지연 모듈;

지연된 필터링된 값들을 생성하기 위해 상기 필터링된 값들을 지연시키는 제 2 지연 모듈;

제 1 곱셈값들을 생성하기 위해 상기 지연된 등화된 값들 및 상기 필터링된 값들을 곱하는 제 1 곱셈기;

제 2 곱셈값들을 생성하기 위해 상기 등화된 값들 및 상기 지연된 필터링된 값들을 곱하는 제 2 곱셈기; 및

상기 제 1 및 제 2 곱셈값들 사이의 차이들에 기초하여 상기 추정된 타이밍 에러 신호를 생성하는 차이 노드를 포함하는, 신호 프로세서.

### 청구항 2

제 1 항에 있어서,

상기 신호 처리 경로는:

디지털 입력 신호를 생성하기 위해 상기 샘플링 클록 신호에 기초하여 상기 아날로그 입력 신호를 샘플링하는 아날로그-디지털 컨버터(ADC);

등화된 신호를 생성하기 위해 상기 디지털 입력 신호를 등화하는 등화기;

상기 등화된 신호로부터 상기 소프트 값들을 생성하는 소프트 검출기; 및

상기 디지털 출력 신호를 생성하기 위해 상기 소프트 값들을 디코딩하는 디코더를 포함하는, 신호 프로세서.

### 청구항 3

제 1 항에 있어서,

상기 타이밍 복구 루프는:

평균 에러 신호를 생성하기 위해 상기 추정된 타이밍 에러 신호를 필터링하는 루프 필터; 및

상기 샘플링 클록 신호를 생성하기 위해 상기 평균된 예러 신호에 기초하여 상기 LO 클록 신호의 위상을 조정하는 인터폴레이터를 더 포함하는, 신호 프로세서.

#### 청구항 4

제 1 항에 있어서,

상기 평균값들을 생성하는 모듈은 상기 소프트 값들을 대응하는 평균값들로 변환하는 루업-테이블을 실행하는, 신호 프로세서.

#### 청구항 5

제 4 항에 있어서,

각각의 소프트 값에 대해서:

상기 대응하는 평균값의 부호는 상기 소프트 값의 부호 비트에 기초하고;

상기 대응하는 평균값의 크기는 상기 멀티비트 신뢰도 값들 중 하나 이상의 비트들의 크기에 기초하는, 신호 프로세서.

#### 청구항 6

제 5 항에 있어서,

상기 멀티비트 신뢰도 값은 4 비트들을 포함하는, 신호 프로세서.

#### 청구항 7

신호 처리를 위한 신호 프로세서의 실행 방법(signal processor-implemented method)에 있어서,

(a) 상기 신호 프로세서가 아날로그 입력 신호를 멀티비트 소프트 값들로 변환하는 단계로서, 각각의 멀티비트 소프트 값들은 부호 비트 및 멀티비트 신뢰도 값을 가지는, 상기 변환 단계; 및

(b) 상기 신호 프로세서가 상기 아날로그 입력 신호를 샘플링하는데 사용되는 샘플링 클록 신호를 생성하기 위해 상기 부호 비트들과 상기 소프트 값들의 상기 멀티비트 신뢰도 값들 중 하나 이상의 비트들을 사용하는 단계를 포함하고,

상기 부호 비트들과 상기 소프트 값들의 상기 멀티비트 신뢰도 값들 중 하나 이상의 비트들을 사용하는 단계는, 상기 샘플링 클록 신호를 생성하기 위해 로컬발진기(LO) 클록 신호를 조정하기 위하여 상기 부호 비트들과 상기 소프트 값들의 상기 멀티비트 신뢰도 값들 중 하나 이상의 비트들로부터 추정된 타이밍 예러 신호를 생성하는 단계를 포함하고;

상기 추정된 타이밍 예러 신호 생성단계는:

상기 부호 비트들과 상기 소프트 값들의 상기 멀티비트 신뢰도 값들 중 하나 이상의 비트들에 기초하여 평균값들을 생성하는 단계;

필터링된 값들을 생성하기 위해 상기 평균값들을 필터링하는 단계;

상기 아날로그 입력 신호로부터 등화된 값들을 생성하는 단계;

지연된 등화된 값들을 생성하기 위해 신호 처리 경로로부터 상기 등화된 값들을 지연시키는 단계;

지연된 필터링된 값들을 생성하기 위해 상기 필터링된 값들을 지연시키는 단계;

제 1 곱셈값들을 생성하기 위해 상기 지연된 등화된 값들 및 상기 필터링된 값들을 곱하는 단계;

제 2 곱셈값들을 생성하기 위해 상기 등화된 값들 및 상기 지연된 필터링된 값들을 곱하는 단계; 및

상기 제 1 및 제 2 곱셈값들 사이의 차이들에 기초하여 상기 추정된 타이밍 예러 신호를 생성하는 단계를 포함하는, 신호 처리를 위한 신호 프로세서의 실행 방법.

#### 청구항 8

제 7 항에 있어서,

단계 (a)는:

- (a1) 디지털 입력 신호를 생성하기 위해 상기 샘플링 클록 신호에 기초하여 상기 아날로그 입력 신호를 샘플링 하는 단계;

- (a2) 등화된 신호를 생성하기 위해 상기 디지털 입력 신호를 등화하는 단계;

- (a3) 상기 등화된 신호로부터 상기 멀티비트 소프트 값들을 생성하는 단계; 및

- (a4) 상기 디지털 출력 신호를 생성하기 위해 상기 소프트 값들을 디코딩하는 단계를 포함하는, 신호 처리를 위한 신호 프로세서의 실행 방법.

## 청구항 9

제 7 항에 있어서,

상기 추정된 타이밍 에러 신호를 생성하는 것 이후, 단계 (b)는:

평균 에러 신호를 생성하기 위해 상기 추정된 타이밍 에러 신호를 필터링하는 단계; 및

상기 샘플링 클록 신호를 생성하기 위해 상기 평균 에러 신호에 기초하여 상기 LO 클록 신호의 위상을 조정하는 단계를 더 포함하는, 신호 처리를 위한 신호 프로세서의 실행 방법.

## 청구항 10

신호 처리 장치에 있어서,

(a) 아날로그 입력 신호를 등화된 값들 및 멀티비트 소프트 값들로 변환하는 수단으로서, 각각의 멀티비트 소프트 값들은 부호 비트 및 멀티비트 신뢰도 값을 가지는, 상기 변환 수단; 및

(b) 상기 아날로그 입력 신호를 샘플링하는데 사용되는 샘플링 클록 신호를 생성하기 위해 상기 부호 비트들과 상기 소프트 값들의 멀티비트 신뢰도 값을 중 하나 이상의 비트들을 사용하는 수단을 포함하며,

상기 사용 수단은:

상기 부호 비트들과 상기 소프트 값들의 멀티비트 신뢰도 값을 중 하나 이상의 비트들에 기초하여 추정된 타이밍 에러 신호를 생성하는 수단을 포함하며, 상기 추정된 타이밍 에러 신호는 상기 샘플링 클록 신호를 생성하기 위해 로컬발진기(LO) 클록 신호를 조정하는데 사용되며,

상기 생성 수단은:

상기 부호 비트들과 상기 소프트 값들의 상기 멀티비트 신뢰도 값을 중 하나 이상의 비트들에 기초하여 평균값들을 생성하는 수단;

필터링된 값들을 생성하기 위해 상기 평균값들을 필터링하는 수단;

지연된 등화된 값들을 생성하기 위해 상기 등화된 값들을 지연시키는 수단;

지연된 필터링된 값들을 생성하기 위해 상기 필터링된 값들을 지연시키는 수단;

제 1 곱셈값들을 생성하기 위해 상기 지연된 등화된 값들 및 상기 필터링된 값들을 곱하는 수단;

제 2 곱셈값들을 생성하기 위해 상기 등화된 값들 및 상기 지연된 필터링된 값들을 곱하는 수단; 및

상기 제 1 및 제 2 곱셈값들 사이의 차이들에 기초하여 상기 추정된 타이밍 에러 신호를 생성하는 수단을 포함하는, 신호 처리 장치.

## 명세서

### 기술 분야

본 발명은 신호 처리에 관한 것으로서, 특히 타이밍 복구 루프들에서 위상 검출에 관한 것이다.

## 배경 기술

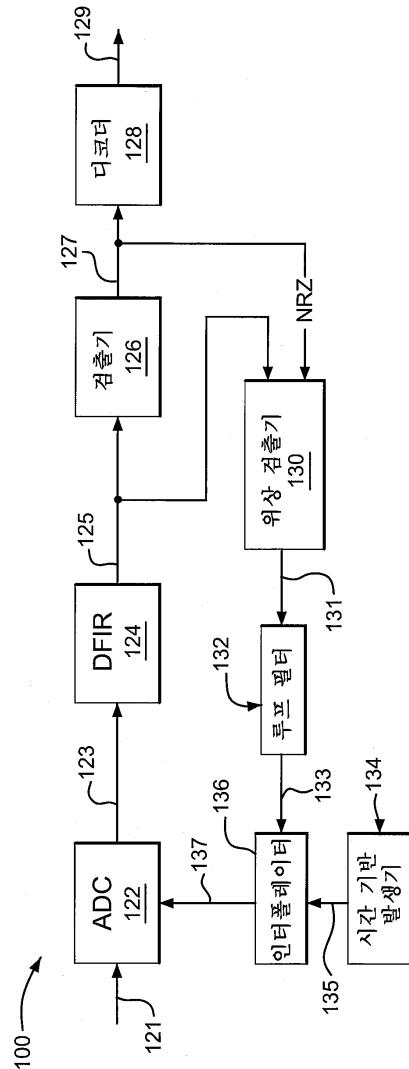

[0002] 도 1은 하드 드라이브를 위한 종래 기술의 판독 채널(100)의 블록도이다. 판독 채널(100)은 하드 드라이브에 저장된 데이터에 대응하는 아날로그 입력 신호(121)를 수신하고 하드 드라이브에 저장된 데이터를 나타내는 디지털 디코딩된 출력 신호(129)를 발생한다.

[0003] 특히, 아날로그-디지털 컨버터(ADC)(122)는 디지털 입력 신호(123)를 생성하기 위해 아날로그 입력 신호(121)를 디지털화한다. DFIR(digital finite impulse response) 필터 등화기(124)는 등화된 디지털 신호(125)를 발생하기 위해 디지털 입력 신호(123)를 등화한다(equalize). 소프트 검출기(126)는 등화된 디지털 신호(125)를 멀티비트 로그 최우비(multi-bit log likelihood ratio : LLR) 값들(127)과 같은 소프트값들로 변환하며, 여기서 각각의 LLR 값은 경판정 부호 비트(hard-decision sign bit) 및 멀티비트(예로서, 4-비트) 신뢰도 값(confidence value)을 갖는다. 소프트 검출기(126)는 LLR 값들(127)을 발생하기 위하여, 비터비(Viterbi) 소프트-출력 검출 또는 MAP(maximum a posteriori) 검출과 같은 적절한 검출 기술을 실행한다. 디코더(128)는 디코딩된 출력 신호(129)를 발생하기 위해 LLR 값들을 디코딩한다. 예를 들어, 하드 드라이브에 저장된 데이터가 LDPC(low-density parity check) 코드를 사용하여 인코딩되면, 그때 디코더(128)는 LDPC 디코딩을 실행하여 LLR 값들(127)로부터 디코딩된 출력 신호(129)를 생성시킨다.

[0004] 위상 검출기(130)는 등화기(124)로부터 등화된 디지털 신호(125)를 처리하고 소프트 검출기(126)로부터 LLR 값들(127)의 부호 비트들을 처리하여 추정된 타이밍 에러 신호(131)를 생성시킨다. 하나의 종래 실시예에서, 위상 검출기(130)는, (i) 상기 부호 비트들을 FIR 필터로 컨볼빙(convolving)하는 것과, (ii) 상기 FIR 필터 출력과 등화된 디지털 신호(125)의 1 사이클 지연된 버전(one-cycle-delayed version) 사이의 차이를 발생하는 것과, (iii) 상기 차이를 등화된 디지털 신호(125)의 슬롭의 추정치(estimate)만큼 증대시키는 것에 의하여 추정된 타이밍 에러 신호(131)를 생성시킨다. 루프 필터(132)는 평균화된 에러 신호(133)를 출력하기 위하여 추정된 타이밍 에러 신호(131)를 적분한다(integrate). 시간 기반 발생기(예로서, 로컬발진기(L0))(134)는 L0 클록 신호(135)를 생성시킨다. 인터폴레이터(interpolator)(136)는 평균화된 에러 신호(133)에 기초한 L0 클록 신호(135)의 위상을 변위하여 샘플링 클록 신호(137)를 생성시키고, 이 샘플링 클록 신호가 ADC(122)에 의해 아날로그 입력 신호(121)의 샘플링하는 시간을 결정한다.

[0005] 하드 드라이브 리드-채널 기술에서, 신호 대 노이즈 비(SNR)는 디스크들의 저장 밀도의 증가로 인하여 계속 감소되고 있다. 등화된 샘플들(등화된 디지털 신호(125)와 같은 것)과 경판정들(LLR 값들(127)의 부호 비트들과 같은 것)로부터 타이밍 정보를 추정하는 종래 타이밍-복구 위상 검출기들은 낮은-SNR 환경들에서는 적절하게 작동하지 않으며, 그 결과 허용될 수 없는 높은 LOLR(loss-of-lock rate)을 초래하며, 이것이 시스템 처리율을 감소시킨다.

## 발명의 내용

### 해결하려는 과제

[0006] 도 1의 판독 채널(100)에서, 다만 LLR 값들(127)의 부호 비트들만이 위상 검출기(130)에 의해 사용된다. 그 결과, 위상 검출기(130)는 타이밍 에러 신호들을 출력할 수 있으며, 이 타이밍 에러 신호들이 비교적 높은 LOLR과 비교적 낮은 시스템 처리율을 초래한다.

[0007] 개시된 본 발명은 NRZs(Non Return Zeros)에서 점진적(graduated) 또는 "소프트" 변화들을 위해 그리고 종래 기술에서 NRZs의 비교적 큰 또는 "하드" 변화들과는 대조적으로, 개시된 본 발명의 ADC를 위한 샘플링 클록 신호를 조정하는데 사용된 메카니즘을 제공함으로써 종래 기술의 문제점들을 해결한다. 이것은, 위상 검출기가 부호 비트와 나머지 신뢰도-값 비트들 중 하나 이상 및 가능하면 모두를 사용하여 추정된 타이밍 에러 신호를 생성하기 때문이다. 신뢰도 값들은 위상 검출기로 하여금 다른 부호 비트들을 개별적으로 처리하게 하여 추정된 타이밍 에러 신호를 생성시키며, 여기서 신뢰도 값은 수신된 부호 비트를 위한 신뢰성(reliability) 정보를 제공한다. 예를 들어, 부호 비트를 위한 저신뢰도 값들은 위상 검출기가 부호 비트의 임팩트(impact)를 감소시키게 하며, 한편 고신뢰도 값들은 추정된 타이밍 에러 신호들에서 더 큰 변화들을 초래할 수 있다.

[0008] 개시된 본 발명의 결과로서, 위상 변화들은 종래 기술의 위상 검출기들에 비하여 더 큰 정확도 및 신뢰성을 가지고 검출된다. 종래 기술의 샘플링 클록 신호에서 잠재적으로 크고 급격한 위상 변화들은 개시된 시스템에 의하여 더 원활하고 점진적인 "소프트" 위상 변화들로 대체된다. 이것은 ADC에서 점진적 또는 "소프트" 조정들을 가능하게 하는 샘플링 클록 신호들을 초래한다. 추가로, 개시된 위상 검출기는 인터폴레이터를 정지하여 재조정

하지 않고 그 작동들을 역동적으로 그리고 "활동중에(on the fly)" 수행한다.

### 과제의 해결 수단

[0009] 일 실시예에서, 본 발명은 신호 프로세서이다. 신호 프로세서는 아날로그 입력 신호를 디지털 출력 신호로 변환하는 신호 처리 경로로서, 상기 신호 처리 경로는 멀티비트 소프트값들을 생성시키고, 각각의 멀티비트 소프트값들은 부호 비트 및 멀티비트 신뢰도 값을 가지는, 상기 신호 처리 경로; 및 상기 신호 처리 경로에 의해 사용된 샘플링 클록 신호를 생성시켜 아날로그 입력 신호를 샘플링하기 위해 상기 부호 비트들과 상기 소프트값들의 멀티비트 신뢰도 값을 중 하나 이상의 비트들을 사용하는 타이밍 복구 루프를 포함한다.

[0010] 다른 실시예에서, 본 발명은 신호 처리 방법이다. 이 방법은, 아날로그 입력 신호를 멀티비트 소프트값들로 변환하는 단계로서, 각각의 멀티비트 소프트값들은 부호 비트 및 멀티비트 신뢰도 값을 가지는, 상기 변환 단계; 및 상기 부호 비트들과 상기 소프트값들의 멀티비트 신뢰도 값을 중 하나 이상의 비트들을 사용하여 샘플링 클록 신호를 생성시키기 위해 아날로그 입력 신호를 샘플링하는 단계를 포함한다.

[0011] 다른 실시예에서, 본 발명은 신호 처리 장치이다. 이 장치는, 아날로그 입력 신호를 멀티비트 소프트값들로 변환하는 수단으로서, 상기 각각의 멀티비트 소프트값들은 부호 비트 및 멀티비트 신뢰도 값을 가지는, 상기 변환 수단; 및 상기 부호 비트들과 상기 소프트값들의 멀티비트 신뢰도 값을 중 하나 이상의 비트들을 사용하여 샘플링 클록 신호를 생성시키기 위하여 아날로그 입력 신호를 샘플링하는 수단을 포함한다.

### 발명의 효과

[0012] 본 발명은 타이밍 복구 루프를 위한 위상 검출기를 제공한다.

### 도면의 간단한 설명

[0013] 도 1은 하드 드라이브를 위한 종래 기술의 판독 채널의 블록도.

도 2는 개시된 본 발명의 하드 드라이브를 위한 판독 채널의 블록도.

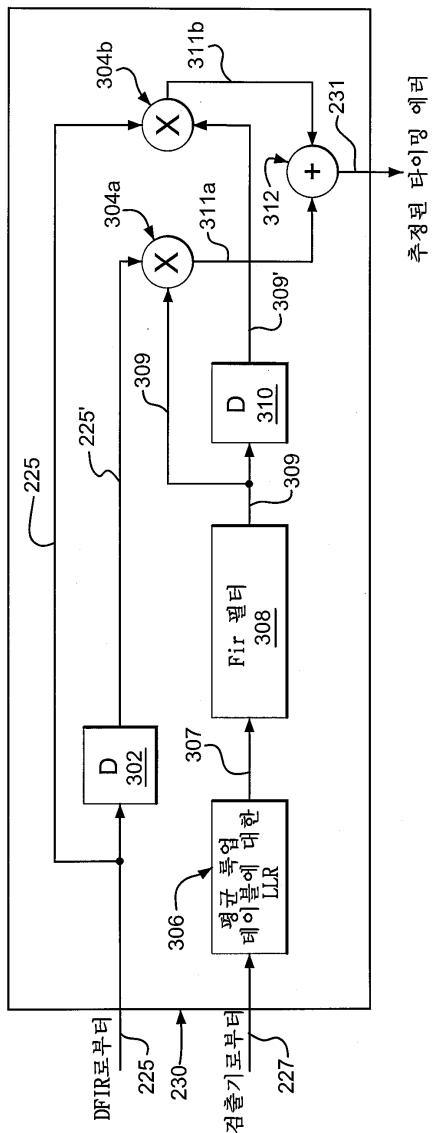

도 3은 도 2의 판독 채널의 위상 검출기의 블록도.

도 4는 도 3의 위상 검출기의 예시적인 작동을 위한 루업-테이블(LUT).

도 5는 도 2의 개시된 판독 채널 대 도 1의 종래 기술의 판독 채널에 대한 성능의 그래프도.

### 발명을 실시하기 위한 구체적인 내용

[0014] 이제 유사한 또는 대응하는 부호들이 유사한 또는 대응하는 컴포넌트들을 가리키는 도면들에 주목하기로 한다.

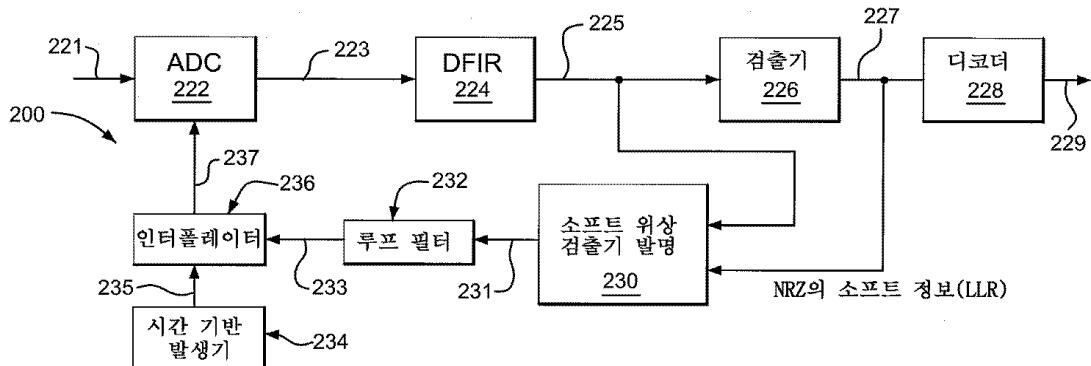

[0015] 도 2는 개시된 본 발명의 "소프트" 위상 검출기(230)를 채용하는 하드 드라이브를 위한 판독 채널(200)의 블록도이다. 도 1의 판독 채널(100)과 같이, 판독 채널(200)은 하드 드라이브에 저장된 데이터에 대응하는 아날로그 입력 신호(221)를 수신하고 하드 드라이브에 저장된 데이터를 나타내는 디지털 디코딩된 출력 신호(229)를 생성시킨다. 도 2의 엘리먼트들(222-236) 및 신호들(221-237)은 각각 도 1의 엘리먼트들(122-136) 및 신호들(121-137)과 유사하다. 위상 검출기(230)를 제외하면, 도 2의 엘리먼트들 각각은 도 1의 대응하는 엘리먼트와 유사한 방법으로 동작한다.

[0016] 도 1의 위상 검출기(130), 즉 등화기(124)로부터 등화된 디지털 신호(125)에 기초하여 그리고 소프트 검출기(126)로부터 LLR 값들(127)의 부호 비트들만을 기초하여 추정된 타이밍 에러 신호(131)를 생성시키는, 상기 위상 검출기(130)와는 다르게, 도 2의 위상 검출기(230)는 등화기(224)로부터 등화된 디지털 신호(225) 및 소프트 검출기(226)로부터 완전한 LLR 값들(227)에 기초하여 추정된 타이밍 에러 신호(231)를 생성시킨다. LLR 값들(227)의 모든 비트들(즉, 부호 비트들 및 NRZ의 소프트 정보로서 공지된 멀티비트 신뢰도 값을)을 사용함으로써, 위상 검출기(230)는 멀티비트 신뢰도 값을 크기에 기초하여 결과적으로 생성된 추정된 타이밍 에러 신호(231)에 LLR 값들(227)의 임팩트를 가중할 수 있다. 멀티비트 신뢰도 값이 클수록 부호 비트의 값에서 더 높은 신뢰도가 존재하고 추정된 타이밍 에러 신호에 더 큰 임팩트가 가해진다.

[0017] 위상 검출기(230)는 신뢰도 값을 사용하여 부호 비트의 신뢰성을 결정하고 입력 LLR 값의 부호 비트만을 사용하여 비교될 때 더욱 정확한 추정된 타이밍 에러 신호를 생성시킨다. 도 1의 위상 검출기(130)의 작동이 "모든 또는 전혀 없는(all or nothing)" 것과는 대조적으로, 위상 검출기(230)는 "소프트" 위상 검출기로서 알려져

있다. 5개 이외의 비트들의 개수를 갖는 LLR 값들은 판독 채널(200)의 다른 실행들에도 가능하다.

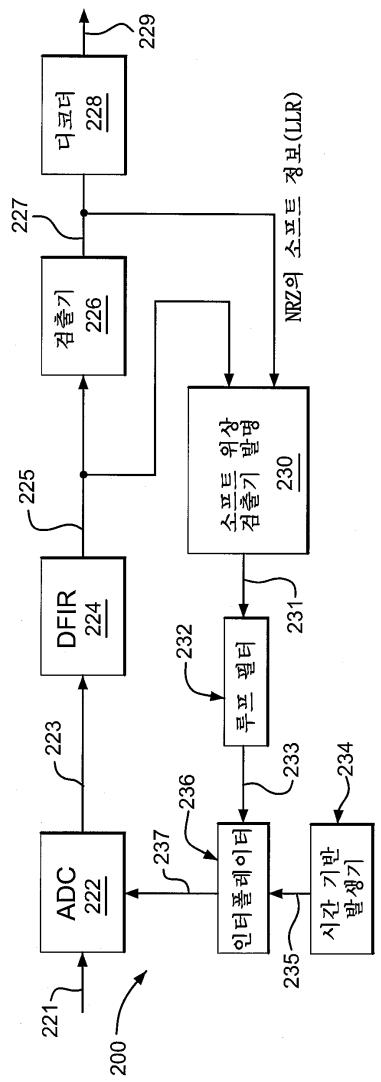

[0018] 도 3은 도 2의 위상 검출기(230)의 블록도를 도시한다. 위상 검출기(230)는 등화기(224)로부터 등화된 디지털 신호(225)를 수신하고, 소프트 검출기(226)로부터 LLR 값들(227), 예를 들어 부호 비트의 신뢰성을 나타내는, 하나의 부호 비트 및 4-비트 신뢰도 값을 갖는 5-비트 LLR 값들을 수신한다.

[0019] 각각의 등화된 디지털 값(225)은 지연 메카니즘(302)에서 1-클록-사이클(one-clock-cycle) 지연을 경험하고, 그 결과로 지연된 신호(225')는 곱셈기(multiplier; 304a)에 의해 수신된다. 또한, 등화된 신호(225)는 직접(즉, 지연됨이 없이) 곱셈기(304b)로 전송된다.

[0020] LLR 값들(227)의 각각은 모듈(306)로 입력되고, 상기 모듈이 루업-테이블(LUT)을 실행하고, 이 루업-테이블이 각각의 입력 LLR 값(227)을 대응하는 현재(current) 평균값(307)으로 맵핑(mapping)한다. 도 4는 각각의 입력 LLR 값을 하나의 현재 평균값(307)으로 맵핑하는 예시적인 LUT를 도시하고 있다. 상술한 맵핑은 대안으로서 다른 LLR 값을 대응하는 현재 평균값들로 변환하는, 조각적 선형 함수(piece-wise linear function)와 같은 연속 함수를 이용하여 수행될 수도 있다.

[0021] 모듈(306)은 평균값들(307)을 FIR 필터(308)로 전송하고, 이 필터는 상기 평균값들을 부분 반응(PR) 타겟으로 컨볼빙하여 필터링된 신호(309)를 생성시킨다. PR 타겟은 등화용 FIR 필터(308)에 사용하기 위한 텁(tap) 계수들을 제공한다. 예를 들어, FIR 필터(308)는 2-텝 8/14 FIR 필터가 될 수 있고, 다음과 같이 표현된다:

$$X = 14 \cdot Y_{mc} + 8 \cdot Y_{mp}$$

[0023] 여기서, X는 FIR 필터(308)에 의해 출력된 필터링된 신호(309)의 현재값,

[0024]  $Y_{mc}$ 는 모듈(306)에 의해 출력된 평균 신호(307)의 현재값, 및

[0025]  $Y_{mp}$ 는 평균 신호(307)의 이전값(즉, 이전 클록 사이클)이다.

[0026] 대안 실행예들로서, 다른 텁 계수들, 값들, 및/또는 다른 개수들의 텁들을 갖는 PR 타겟들이 사용될 수 있다.

[0027] 각각의 필터링된 값(309)은 지연 메카니즘(310)에서 1-클록-사이클 지연을 경험하고, 그 결과로 지연된 신호(309')는 곱셈기(304b)에 의해 수신된다. 또한, 필터링된 신호(309)는 직접(즉, 지연됨이 없이) 곱셈기(304a)로 전송된다.

[0028] 곱셈기(304a)는 지연된 등화된 신호(225') 및 미지연(undelayed) 필터링된 신호(309)를 승산하여 곱셈(product) 신호(311a)를 생성시키고, 한편 곱셈기(304b)는 미지연된 등화된 신호(225) 및 지연된 필터링된 신호(309')를 승산하여 곱셈 신호(311b)를 생성시킨다. 차이 노드(difference node)(312)는 곱셈 신호들(311a 및 311b) 사이의 차이에 기초하여 추정된 타이밍 에러 신호(231)를 생성시킨다.

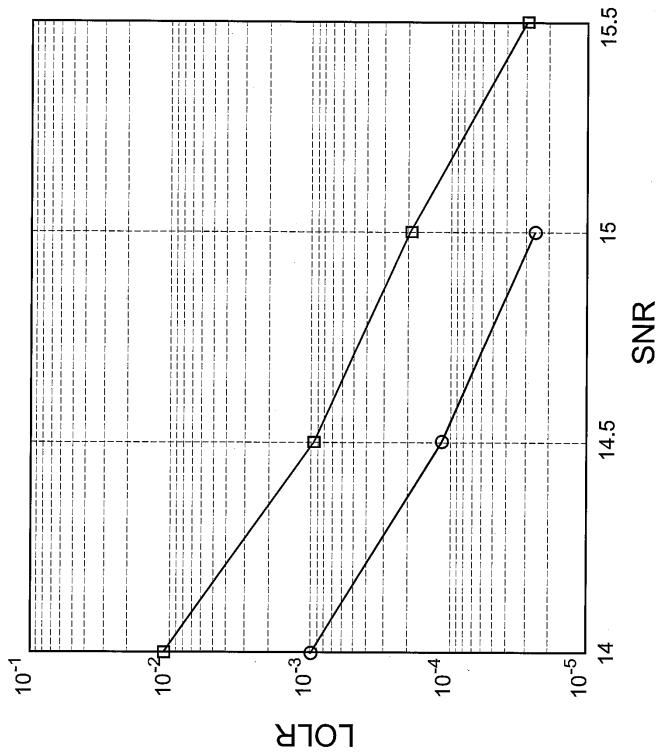

[0029] 도 5는 도 2의 판독 채널(200) 대 도 1의 종래 기술의 판독 채널(100)에 대한 성능의 그래프도이다. 특히, 도 5는 신호 대 노이즈 비(SNR)의 함수로서 각 판독 채널에 대한 LOLR을 도시하며, 여기서 종래 기술의 판독 채널(100)에 대한 결과들이 정사각형으로 표시되고, 판독 채널(200)에 대한 결과들이 원들로 표시된다. 주어진 SNR 값에 대해서, 판독 채널(200)은 종래 기술의 판독 채널(100)에 비하여 대략 10배(an order of magnitude)가 향상된다.

[0030] 개시된 본 발명이 LLR 값들에 기초하여 추정된 타이밍 에러들을 생성시키는 위상 검출기의 내용을 설명하였지만, 개시된 본 발명은 LLR 값들 이외의 값들을 사용하여 실행될 수 있다.

[0031] 개시된 본 발명이 하드-드라이브 판독 채널내에서 타이밍 복구를 위한 위상 검출기의 콘텍스트를 설명하였지만, 개시된 본 발명은 다른 애플리케이션들에 대해서 실행될 수 있다.

[0032] 본 발명은, 단일 집적 회로(ASIC 또는 FPGA와 같은 것), 멀티칩 모듈, 단일카드, 또는 멀티카드 회로 팩으로서 가능한 실행을 포함하여, (아날로그, 디지털, 또는 아날로그와 디지털의 하이브리드) 회로 기반 프로세스들로서 실행될 수 있다. 당업자에게는 명백히 알 수 있듯이, 회로 엘리먼트들의 여러 가지 기능들은 또한 소프트웨어 프로그램에서 처리 블록들로서 실행될 수 있다. 그러한 소프트웨어는 예를 들어, 디지털 신호 프로세서, 마이크로 컨트롤러, 또는 범용 컴퓨터에서 채용될 수 있다.

[0033] 프로세스의 일부를 포함하는 상술된 프로세스들은 소프트웨어, 하드웨어 또는 이들의 조합들에 의하여 수행될 수 있다. 상기 프로세스들 및 그 일부분들은 컴퓨터들, 컴퓨터형 디바이스들, 워크스테이션들, 프로세서들, 마이크로-프로세서들, 기타 전자 검색 툴들 및 메모리, 및 이와 관련된 다른 기억 디바이스들에 의하여 수행될 수

있다. 또한, 상기 프로세스들 및 그 일부분들은 프로그램가능 기억 디바이스들에서 구현될 수 있는데, 예를 들어, 기계 등에 의하여 판독될 수 있는 컴팩트 디스크(CD)들, 또는 자기 디스크, 광학 디스크 등을 포함하는 다른 디스크들, 또는 자기, 광학 또는 반도체 저장, 또는 전자 신호들의 다른 소스를 포함하는 다른 컴퓨터 이용 가능 저장 매체에서 구현될 수 있다.

[0034] 청구범위에서 도면 부호들 및/또는 도면 기호들을 사용하는 것은 청구범위의 해석을 용이하게 하기 위하여 청구한 대상의 하나 이상의 가능한 실시예들을 식별하기 위해 의도된다. 그러한 사용은 대응하는 도면들에 도시된 실시예들로 청구범위를 반드시 제한하는 것으로 해석되어서는 안 된다.

[0035] 본원에서 언급한 "일 실시예"는 이 실시예와 관련하여 설명된 특정한 피처, 구조, 또는 특성이 본 발명의 적어도 일 실시예에 포함될 수 있다는 것을 의미한다. 본 명세서의 여러 곳에서 "일 실시예에서"라는 표현은 반드시 동일한 실시예를 언급하는 것은 아니며, 다른 실시예를 반드시 서로 배제하는 별개의 또는 대안 실시예들을 언급하는 것도 아니다. 용어 "실행(implementation)"에도 동일하게 적용한다.

[0036] 프로세스들(방법들) 및 시스템들은 그들의 구성요소들을 포함하여, 본원에서 특정한 하드웨어 및 소프트웨어를 예시적인 참조로 설명된 것이다. 이 프로세스들(방법들)은 예시로서 설명되어 있으며, 이에 의해 특정한 단계들 및 그들의 순서는 당업자들에 의하여 이러한 실시예들을 감소함으로써 과도한 실험을 하지 않고 실시하도록 생략될 수 있으며, 및/또는 변화될 수 있다. 프로세스들(방법들) 및 시스템들은 당업자들에 의하여 어떤 실시예들을 감소함으로써 과도한 실험을 하지 않고 그리고 종래 기술들을 사용하여 실시하며 필요한 대로 다른 하드웨어 및 소프트웨어에 용이하게 적용할 수 있기에 충분한 방식으로 설명되어 있다.

[0037] 개시된 본 발명의 양호한 실시예들은 당업자가 개시된 본 발명을 실시할 수 있도록 설명되어 있지만, 상기 설명은 실례로서만 의도된다. 첨부한 청구범위를 참고하여 결정되어야 하는 개시된 본 발명의 범위를 제한하는데 사용되어서는 안 된다.

### 부호의 설명

[0038] 200 : 판독 채널

224 : DFIR

226, 228 : 검출기

230 : 위상 검출기

232 : 루프 필터

234 : 시간 기반 발생기

236 : 인터폴레이터

## 도면

## 도면1

종래기술

도면2

도면3

## 도면4

Look-up table (LUT) of the LLR to mean:

- $LLR \geq -4$ , Mean= 1

- $LLR \geq -2$ , Mean= 0.75

- $LLR \geq -1$ , Mean= 0.5

- $LLR \geq -1$ , Mean= 0,

- $LLR \geq -4$ , Mean= -1

- $LLR \geq -2$ , Mean= -0.75

- $LLR \geq -1$ , Mean= -0.5

## 도면5