# AIPO OMPI

#

# (10) International Publication Number WO 2010/020070 A1

(43) International Publication Date 25 February 2010 (25.02.2010)

(51) International Patent Classification: H01L 33/00 (2010.01) H01L 21/20 (2006.01)

(21) International Application Number:

PCT/CN2008/001494

(22) International Filing Date:

19 August 2008 (19.08.2008)

(25) Filing Language:

English

(26) Publication Language:

English

- (71) Applicant (for all designated States except US): LATTICE POWER (JIANGXI) CORPORATION [CN/CN]; No.235, East Nanjing Road, Nanchang, Jiangxi 330047 (CN).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): JIANG, Fengyi [CN/CN]; No. 235 East Nanjing Road, Nanchang, Jiangxi 330047 (CN). TANG, Yingwen [CN/CN]; No. 235 East Nanjing Road, Nanchang, Jiangxi 330047 (CN). MO, Chunlan [CN/CN]; No. 235 East Nanjing Road, Nanchang, Jiangxi 330047 (CN). WANG, Li [CN/CN]; No. 235 East Nanjing Road, Nanchang, Jiangxi 330047 (CN).

- (74) Agent: KING & WOOD PRC LAWYERS; 31/F, Office Tower A, 39 Dongsanhuan zhonglu, Chaoyang District, Beijing 100022 (CN).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

with international search report (Art. 21(3))

(54) Title: SEMICONDUCTOR LIGHT-EMITTING DEVICE WITH PASSIVATION IN P-TYPE LAYER

3K

FIG. 3

(57) Abstract: A semiconductor light-emitting device includes a substrate, a first doped semiconductor layer, a second doped semiconductor layer situated above the first doped semiconductor layer, and a multi-quantum-well (MQW) active layer situated between the first and the second doped layers. The device also includes a first electrode coupled to the first doped semiconductor layer, wherein part of the first doped semiconductor layer is passivated, and wherein the passivated portion of the first doped semiconductor layer substantially insulates the first electrode from the edges of the first doped semiconductor layer, thereby reducing surface recombination. The device further includes a second electrode coupled to the second doped semiconductor layer and a passivation layer which substantially covers the sidewalls of the first and second doped semiconductor layers, the MQW active layer, and part of the horizontal surface of the second doped semiconductor layer which is not covered by the second electrode.

# SEMICONDUCTOR LIGHT-EMITTING DEVICE WITH PASSIVATION IN P-TYPE LAYER

#### **BACKGROUND**

#### **Field**

[0001] The present disclosure relates to a semiconductor light-emitting device. More specifically, the present invention relates to a novel semiconductor light-emitting device with passivation in the p-type layer that can effectively reduce the leakage current and enhance the device reliability.

#### Related Art

[0002] Solid-state lighting is expected to be the next wave of illumination technology. High-brightness light-emitting diodes (HB-LEDs) are emerging in an increasing number of applications, from serving as the light source for display devices to replacing light bulbs for conventional lighting. Typically, cost, efficiency, and brightness are the three foremost metrics for determining the commercial viability of LEDs.

[0003] An LED produces light from an active region which is "sandwiched" between a positively doped layer (p-type doped layer) and a negatively doped layer (n-type doped layer). When the LED is forward-biased, the carriers, which include holes from the p-type doped layer and electrons from the n-type doped layer, recombine in the active region. In direct band-gap materials, this recombination process releases energy in the form of photons, or light, whose wavelength corresponds to the band-gap energy of the material in the active region.

[0004] To ensure high efficiency of an LED, it is desirable to have the carriers recombine only in the active region instead of other places such as the lateral surface of the LED. However, due to the abrupt termination of the crystal structure at the lateral surface of the LED, there are large

numbers of recombination centers on such surface. In addition, the surface of an LED is very sensitive to its surrounding environment, which may lead to added impurities and defects. Environmentally induced damage can severely degrade the reliability and stability of an LED. In order to insulate an LED from various environmental factors, such as humidity, ion impurity, external electrical field, heat, etc., and to maintain the functionality and stability of the LED, it is important to maintain the surface cleanness and to ensure reliable LED packaging. Moreover, it is also critical to protect the surface of an LED using surface passivation, which typically involves depositing a thin layer of non-reactive material on the surface of the LED.

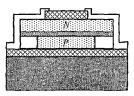

[0005] FIG. 1 illustrates a traditional passivation method for an LED with a vertical-electrode configuration with, from the top down, a passivation layer 100, an n-side (or p-side) electrode 102, an n-type (or p-type) doped semiconductor layer 104, an active layer 106 based on a multi-quantum-well (MQW) structure, a p-type (or n-type) doped semiconductor layer108, a p-side (or n-side) electrode 110, and a substrate 112.

surface. For the vertical-electrode LED structure shown in FIG. 1, surface recombination at the LED occur on the sidewalls of the MQW active region 106. However, the sidewall coverage by a conventional passivation layer, for example, layer 100 shown in FIG. 1, is often less than ideal. The poor sidewall coverage is typically a result of standard thin-film deposition techniques, such as plasma-enhanced chemical vapor deposition (PECVD) and magnetron sputtering deposition. The quality of sidewall coverage by the passivation layer is worse in devices with steeper steps, e.g., steps higher than 2 μm, which is the case for most vertical-electrode LEDs. Under such conditions, the passivation layer often contains a large number of pores, which can severely degrade its ability to block the surface recombination of carriers. An increased surface recombination rate, in turn, increases the amount of the reverse leakage current, which results in reduced efficiency and stability of the LED. In addition, the metal that forms the p-side electrode can diffuse into the p-n junction, leading to increased leakage current.

#### **SUMMARY**

[0007] One embodiment of the present invention provides a semiconductor light-emitting device. The device includes a substrate, a first doped semiconductor layer situated above the substrate; a second doped semiconductor layer situated above the first doped semiconductor layer, and a multi-quantum-well (MQW) active layer situated between the first and the second doped semiconductor layers. The device also includes a first electrode coupled to the first doped semiconductor layer, wherein part of the first doped semiconductor layer is passivated, and wherein the passivated portion of the first doped semiconductor layer substantially insulates the first electrode from the edges of the first doped semiconductor layer, thereby reducing surface recombination. The device further includes a second electrode coupled to the second doped semiconductor layer and a passivation layer which substantially covers the sidewalls of the first and second doped semiconductor layers, the MQW active layer, and part of the horizontal surface of the second doped semiconductor layer which is not covered by the second electrode.

- [0008] In a variation on this embodiment, the substrate comprises at least one of the following materials: Cu, Cr, Si, and SiC.

- [0009] In a variation on this embodiment, the passivation layer comprises at least one of the following materials:  $SiO_x$ ,  $SiN_x$ , and  $SiO_xN_y$ .

- [0010] In a variation on this embodiment, the first doped semiconductor layer is a p-type doped semiconductor layer.

- [0011] In a further variation on this embodiment, the passivated portion of the p-type doped semiconductor layer is not covered by Pt and is formed by a selective low-temperature annealing process which precludes the dopants in the passivated portion from being activated.

- [0012] In a further variation on this embodiment, the passivated portion of the p-type doped semiconductor layer is formed by a selective passivation process which introduces hydrogen ions to the passivated portion.

- [0013] In a variation on this embodiment, the second doped semiconductor layer is an n-type doped semiconductor layer.

[0014] In a variation on this embodiment, the MQW active layer comprises GaN and InGaN.

[0015] In a variation on this embodiment, the passivation layer is formed by one of the following processes: plasma-enhanced chemical vapor deposition (PECVD), magnetron sputtering deposition, and electron beam (e-beam) evaporation.

[0016] In a variation on this embodiment, the thickness of the passivation layer is between 300 Å and 10,000 Å.

#### BRIEF DESCRIPTION OF THE FIGURES

- [0017] FIG. 1 illustrates a traditional passivation method for an LED with a vertical-electrode configuration.

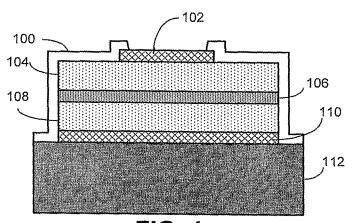

- [0018] FIG. 2A illustrates part of a substrate with pre-patterned grooves and mesas in accordance with one embodiment of the present invention.

- [0019] FIG. 2B illustrates the cross section of a pre-patterned substrate in accordance with one embodiment of the present invention.

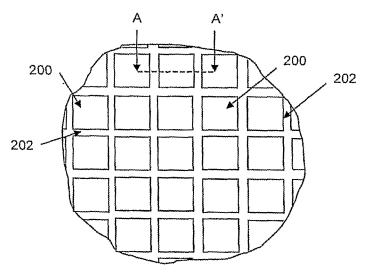

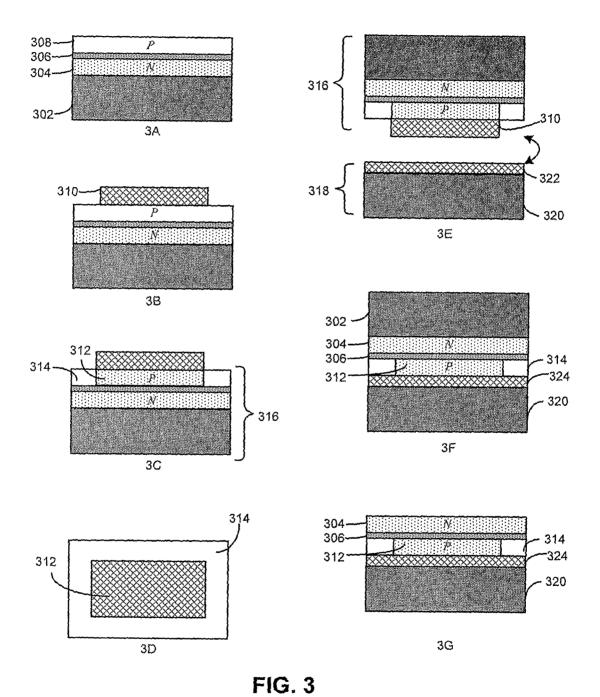

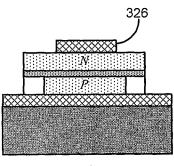

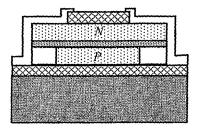

- [0020] FIG. 3 presents a diagram illustrating the process of fabricating a light-emitting device with passivation in the p-type layer in accordance with one embodiment of the present invention.

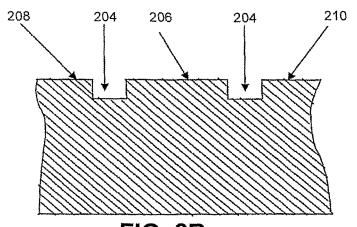

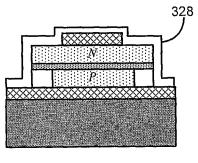

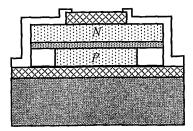

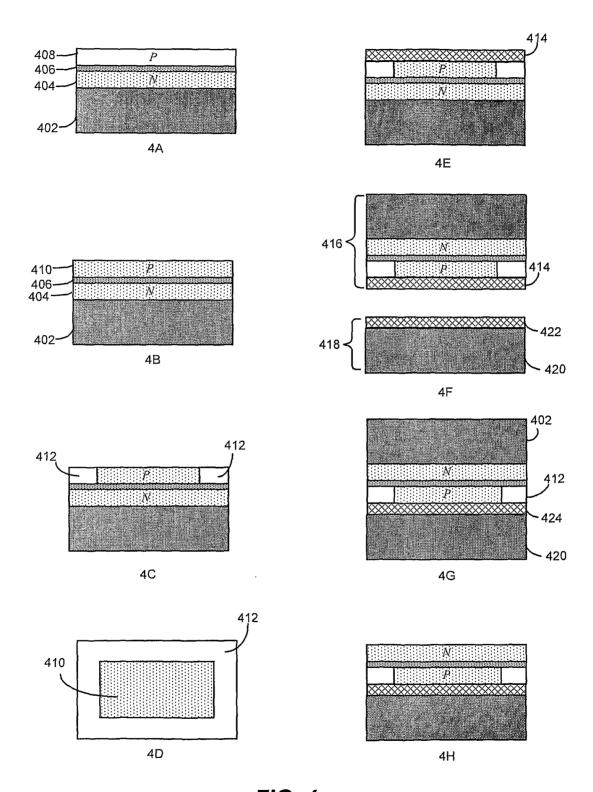

- [0021] FIG. 4 presents a diagram illustrating the process of fabricating a light-emitting device with passivation in the p-type layer in accordance with one embodiment of the present invention.

#### **DETAILED DESCRIPTION**

[0022] The following description is presented to enable any person skilled in the art to make and use the invention, and is provided in the context of a particular application and its requirements. Various modifications to the disclosed embodiments will be readily apparent to those skilled in the art, and the general principles defined herein may be applied to other embodiments and applications without departing from the spirit and scope of the present invention. Thus, the present invention is

not limited to the embodiments shown, but is to be accorded the widest scope consistent with the claims.

#### Overview

[0023] Embodiments of the present invention provide a method for fabricating an LED device with passivation inside the p-type layer. The combination of a passivated portion inside the p-type layer and a separate passivation layer can effectively reduce surface recombination of the carriers, resulting in improved reliability of the LED device. In one embodiment of the present invention, instead of depositing only a single passivation layer at the outer surface of a multilayer semiconductor structure (which includes an n-typed doped layer, a p-type doped layer, and an active layer), a passivated portion is also formed inside the p-type layer. The presence of the passivated portion inside the p-type layer provides substantial insulation between the sidewalls of the p-n junction and the p-side electrode, thereby reducing the leakage current.

#### Preparing the Substrate

[0024] InGaAlN (In<sub>x</sub>Ga<sub>y</sub>Al<sub>1-x-y</sub>N,  $0 \le x \le 1$ ,  $0 \le y \le 1$ ) is one of the optimal materials for manufacturing short-wavelength light-emitting devices. In order to grow a crack-free multilayer InGaAlN structure on a conventional large-area substrate (such as a Si wafer), a growth method that pre-patterns the substrate with grooves and mesas is introduced. Pre-patterning the substrate with grooves and mesas can effectively release the stress in the multilayer structure that is caused by lattice-constant and thermal-expansion-coefficient mismatches between the substrate surface and the multilayer structure.

[0025] FIG. 2A illustrates a top view of a part of a substrate with a pre-etched pattern using photolithographic and plasma-etching techniques in accordance with one embodiment of the present invention. Square mesas 200 and grooves 202 are the result of the etching. FIG. 2B more clearly illustrates the structure of mesas and grooves by showing a cross section of the pre-patterned substrate along a horizontal line AA' in FIG. 2A in accordance with one embodiment of the present

invention. As seen in FIG. 2B, the sidewalls of grooves 204 effectively form the sidewalls of the isolated mesa structures, such as mesa 206, and partial mesas 208 and 210. Each mesa defines an independent surface area for growing a respective semiconductor device.

[0026] Note that it is possible to apply different lithographic and etching techniques to form the grooves and mesas on the semiconductor substrate. Also note that other than forming square mesas 200 as shown in FIG. 2A, alternative geometries can be formed by changing the patterns of grooves 202. Some of these alternative geometries can include, but are not limited to: triangular, rectangular, parallelogram, hexagon, circular, or other non-regular shapes.

#### Passivation in P-type Layer By Selective Annealing

[0027] FIG. 3 presents a diagram illustrating the process of fabricating a light-emitting device with passivation in the p-type layer in accordance with one embodiment of the present invention. In operation 3A, after a pre-patterned substrate with grooves and mesas is prepared, an InGaAIN multilayer structure can be formed using various growth techniques, which can include but are not limited to metalorganic-chemical-vapor-deposition (MOCVD). The multilayer structure can include a substrate 302, which can be a Si wafer; an n-type doped semiconductor layer 304, which can be a Si doped GaN layer; an active layer 306, which can be a multi-period GaN/InGaN MQW structure; and a p-type doped semiconductor layer 308, which can be a Mg doped GaN layer. It is possible to reverse the sequence of the growth between the p-type layer and n-type layer. Note that the MOCVD grown p-type layer 308, which can be a Mg doped GaN layer, usually shows semi-insulating properties. Therefore, a thermal annealing process is used to activate the p-type dopant (the Mg ions).

[0028] In operation 3B, a thin metal layer 310 is formed on top of the p-type doped semiconductor layer covering the center portion of the p-type layer. Metal layer 310 may include several types of metal, such as nickel (Ni), gold (Au), platinum (Pt), and an alloy thereof. In one embodiment of the present invention, thin metal layer 310 includes a layer of Pt, which is in contact with the p-type layer. The presence of Pt makes it possible to activate the p-type dopant using a low

temperature thermal annealing process. Metal layer 310 can be deposited using an evaporation technique such as electro-beam (e-beam) evaporation.

[0029] In operation 3C, low-temperature thermal annealing is performed to the multi-layer structure 316. As a result, the acceptors in a portion of p-type layer 308 that is covered by thin metal layer 310 are activated, forming a substantially conductive p-type region 312. On the other hand, the acceptors in the portion of p-type doped layer 308 that is not covered by thin metal layer 310 remain un-activated, forming a substantially insulating (or passivation) region 314. Illustration 3D shows the top view of the multilayer structure after the low-temperature annealing process.

[0030] In operation 3E, multilayer structure 316 is flipped upside down to bond with a supporting conductive structure 318. Note that, in one embodiment, supporting conductive structure 318 includes a supporting substrate 320 and a bonding layer 322. In addition, a layer of bonding metal can be deposited on metal layer 310 to facilitate the bonding process. Supporting substrate layer 320 is conductive and may include silicon (Si), copper (Cu), silicon carbide (SiC), chromium (Cr), and other materials. Bonding layer 322 may include gold (Au). Illustration 3F shows the multilayer structure after bonding. Note that, after bonding, metal layer 310 and bonding layer 322 bond together to form a p-side electrode 324.

[0031] In operation 3G, substrate 302 is removed. Techniques that can be used for the removal of the substrate layer 302 can include, but are not limited to: mechanical grinding, dry etching, chemical etching, and any combination of the above methods. In one embodiment, the removal of substrate 302 is completed by employing a chemical-etching process, which involves submerging the multilayer structure in a solution based on hydrofluoric acid, nitric acid, and acetic acid. Note that supporting substrate layer 320 can be optionally protected from this chemical etching.

[0032] In operation 3H, the edge of the multilayer structure is removed to reduce surface recombination centers and to ensure high material quality throughout the entire device. However, if the growth procedure can guarantee a good edge quality of the multilayer structure, then this edge removal operation can be optional.

[0033] In operation 3I, after the edge removal, n-side electrode 326 is formed on top of the multilayer structure. The metal composition and the formation process of the n-side electrode can be similar to that of metal layer 310.

[0034] In operation 3J, a top passivation layer 328 is deposited. Materials that can be used to form the top passivation layer include, but are not limited to, the following: SiO<sub>x</sub>, SiN<sub>x</sub>, and SiO<sub>x</sub>N<sub>y</sub>. Various thin-film deposition techniques, such as PECVD and magnetron sputtering deposition, can be used to deposit the top passivation layer. The thickness of the top passivation layer can be between 300 and 10,000 angstroms. In one embodiment of the present invention, the top passivation layer has a thickness of approximately 2,000 angstroms.

[0035] In operation 3K, photolithographic patterning and etching are applied to top passivation layer 328 to expose the n-side electrode.

#### Passivation in P-type Layer By Selective Passivation

[0036] FIG. 4 presents a diagram illustrating the process of fabricating a light-emitting device with passivation in the p-type layer in accordance with one embodiment of the present invention. Operation 4A is similar to operation 3A, which results in an InGaAIN multilayer semiconductor structure that includes a substrate 402, an n-type doped semiconductor layer 404, an active layer 406, and a p-type doped semiconductor layer 408.

[0037] In operation 4B, the multilayer structure undergoes a high temperature thermal annealing process. As a result, the p-type dopant, or the acceptors, inside p-type layer 408 are activated. As a result, a substantially conductive p-type layer 410 is formed.

[0038] In operation 4C, conductive p-type layer 410 is selectively passivated in certain regions, such as passivated regions 412. The selective passivation process can be performed by first protecting the center portion of the p-type layer with a mask, and then exposing the multilayer structure to H<sub>2</sub> or NH<sub>3</sub> plasma. The H ions can effectively passivate the unprotected regions of p-type layer 410, resulting in substantially insulating regions 412. After the passivation process, the mask is removed. Illustration 4D shows the top view of the multilayer structure after the selective

passivation process.

[0039] In operation 4E, a metal layer 414 is deposited on top of p-type layer 410. Metal layer 414 may include several types of metal such as Ni, Au, Pt, and an alloy thereof. Metal layer 414 can be deposited using an evaporation technique such as electro-beam (e-beam) evaporation.

[0040] In operation 4F, multilayer structure 416 is flipped upside down to bond with a supporting conductive structure 418. Note that, in one embodiment, supporting conductive structure 418 includes a supporting substrate 420 and a bonding layer 422. In addition, a layer of bonding metal can be deposited on metal layer 414 to facilitate the bonding process. Supporting substrate layer 420 is conductive and may include silicon (Si), copper (Cu), silicon carbide (SiC), chromium (Cr), and other materials. Bonding layer 422 may include Au. Illustration 4G shows the multilayer structure after bonding. Note that, after bonding, metal layer 414 and bonding layer 422 bond together to form a p-side electrode 424.

[0041] In operation 4H, substrate 402 is removed. Techniques that can be used for the removal of the substrate layer 402 can include, but are not limited to: mechanical grinding, dry etching, chemical etching, and any combination of the above methods. In one embodiment, the removal of substrate 402 is completed by employing a chemical-etching process, which involves submerging the multilayer structure in a solution based on hydrofluoric acid, nitric acid, and acetic acid. Note that supporting substrate layer 420 can be optionally protected from this chemical etching.

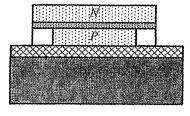

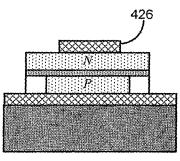

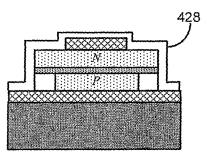

[0042] In operation 4I, the edge of the multilayer structure is removed to reduce surface recombination centers and to ensure high material quality throughout the entire device. However, if the growth procedure can guarantee a good edge quality of the multilayer structure, then this edge removal operation can be optional.

[0043] In operation 4J, after the edge removal, n-side electrode 426 is formed on top of the multilayer structure. The metal composition and the forming process of the n-side electrode can be similar to that of metal layer 414.

[0044] In operation 4K, a top passivation layer 428 is deposited. Materials that can be used

to form the top passivation layer include, but are not limited to:  $SiO_x$ ,  $SiN_x$ , and  $SiO_xN_y$ . Various thin-film deposition techniques, such as PECVD and magnetron sputtering deposition, can be used to deposit the top passivation layer. The thickness of the top passivation layer can be between 300 and 10,000 angstroms. In one embodiment of the present invention, the top passivation layer has a thickness of approximately 2,000 angstroms.

[0045] In operation 4L, photolithographic patterning and etching are applied to top passivation layer 428 to expose n-side electrode 426.

[0046] The foregoing descriptions of embodiments of the present invention have been presented only for purposes of illustration and description. They are not intended to be exhaustive or to limit the present invention to the forms disclosed. Accordingly, many modifications and variations will be apparent to practitioners skilled in the art. Additionally, the above disclosure is not intended to limit the present invention. The scope of the various embodiments is defined by the appended claims.

# What Is Claimed Is:

| 1  | 1. A se                                                                                            | miconductor light-emitting device, comprising:                                             |  |  |  |

|----|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| 2  | a substrate;                                                                                       |                                                                                            |  |  |  |

| 3  | a firs                                                                                             | a first doped semiconductor layer situated above the substrate;                            |  |  |  |

| 4  | a sec                                                                                              | a second doped semiconductor layer situated above the first doped semiconductor layer;     |  |  |  |

| 5  | a mu                                                                                               | alti-quantum-well (MQW) active layer situated between the first and the second doped       |  |  |  |

| 6  | semiconduc                                                                                         | tor layers;                                                                                |  |  |  |

| 7  | a firs                                                                                             | st electrode coupled to the first doped semiconductor layer;                               |  |  |  |

| 8  | whe                                                                                                | rein part of the first doped semiconductor layer is passivated, and wherein the passivated |  |  |  |

| 9  | portion of th                                                                                      | ne first doped semiconductor layer substantially insulates the first electrode from the    |  |  |  |

| 10 | edges of the                                                                                       | first doped semiconductor layer, thereby reducing surface recombination;                   |  |  |  |

| 11 | a sec                                                                                              | cond electrode coupled to the second doped semiconductor layer; and                        |  |  |  |

| 12 | a passivation layer which substantially covers the sidewalls of the first and second doped         |                                                                                            |  |  |  |

| 13 | semiconductor layers, the MQW active layer, and part of the horizontal surface of the second doped |                                                                                            |  |  |  |

| 14 | semiconduc                                                                                         | tor layer which is not covered by the second electrode.                                    |  |  |  |

| 1  | 2.                                                                                                 | The semiconductor light-emitting device of claim 1,                                        |  |  |  |

| 2  | whe                                                                                                | rein the substrate comprises at least one of the following materials:                      |  |  |  |

| 3  |                                                                                                    | Cu,                                                                                        |  |  |  |

| 4  |                                                                                                    | Cr,                                                                                        |  |  |  |

| 5  |                                                                                                    | Si, and                                                                                    |  |  |  |

| 6  |                                                                                                    | SiC.                                                                                       |  |  |  |

| 1  | 3.                                                                                                 | The semiconductor light-emitting device of claim 1,                                        |  |  |  |

| 2  | whe                                                                                                | rein the passivation layer comprises at least one of the following materials:              |  |  |  |

| 3  |                                                                                                    | silicon oxide (SiO <sub>x</sub> ),                                                         |  |  |  |

| 4 |                | silicon nitride (SiN <sub>x</sub> ,), and                                              |

|---|----------------|----------------------------------------------------------------------------------------|

| 5 |                | silicon oxynitride (SiO <sub>x</sub> N <sub>y</sub> ).                                 |

|   |                |                                                                                        |

| 1 | 4.             | The semiconductor light-emitting device of claim 1,                                    |

| 2 | where          | in the first doped semiconductor layer is a p-type doped semiconductor layer.          |

| 1 | 5.             | The semiconductor light-emitting device of claim 4,                                    |

|   |                | •                                                                                      |

| 2 |                | in the passivated portion of the p-type doped semiconductor layer is not covered by Pt |

| 3 | and is formed  | by a selective low-temperature annealing process which precludes the dopants in the    |

| 4 | passivated po  | rtion from being activated.                                                            |

|   |                |                                                                                        |

| 1 | 6.             | The semiconductor light-emitting device of claim 4,                                    |

| 2 | where          | in the passivated portion of the p-type doped semiconductor layer is formed by a       |

| 3 | selective pass | ivation process which introduces hydrogen ions to the passivated portion.              |

|   |                |                                                                                        |

| 1 | 7.             | The semiconductor light-emitting device of claim 1,                                    |

| 2 | where          | in the second doped semiconductor layer is an n-type doped semiconductor layer.        |

| _ |                | •                                                                                      |

| 1 | 8.             | The semiconductor light-emitting device of claim 1,                                    |

| 2 |                | in the MQW active layer comprises GaN and InGaN.                                       |

| ۷ | WHOLE          | in the ivic it detre layer comprises can take an analysis of                           |

| 1 | 9.             | The semiconductor light-emitting device of claim 1,                                    |

| 2 |                | in the passivation layer is formed by at least one of the following processes:         |

|   | Where          |                                                                                        |

| 3 |                | plasma-enhanced chemical vapor deposition (PECVD),                                     |

| 4 |                | magnetron sputtering deposition, or                                                    |

| 5 |                | electro-beam (e-beam) evaporation.                                                     |

| 1  | 10.                                                                                 | The semiconductor light-emitting device of claim 1,                                        |  |  |

|----|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| 2  | wherein the thickness of the passivation layer is between 300 and 10,000 angstroms. |                                                                                            |  |  |

|    |                                                                                     |                                                                                            |  |  |

| 1  | 11.                                                                                 | A method for fabricating a semiconductor light-emitting device, the method                 |  |  |

| 2  | comprising:                                                                         |                                                                                            |  |  |

| 3  | fabri                                                                               | cating a multilayer semiconductor structure on a first substrate, wherein the multilayer   |  |  |

| 4  | semiconduc                                                                          | tor structure comprises a first doped semiconductor layer, an MQW active layer, and a      |  |  |

| 5  | second dope                                                                         | ed semiconductor layer;                                                                    |  |  |

| 6  | form                                                                                | ing a passivated portion in the first doped semiconductor layer, thereby substantially     |  |  |

| 7  | insulating th                                                                       | ne edges of the first doped semiconductor layer from a subsequently formed first           |  |  |

| 8  | electrode;                                                                          |                                                                                            |  |  |

| 9  | formi                                                                               | ng the first electrode, which is coupled to the first doped semiconductor layer;           |  |  |

| 10 | bondi                                                                               | ng the multilayer structure to a second substrate;                                         |  |  |

| 11 | rem                                                                                 | oving the first substrate;                                                                 |  |  |

| 12 | forn                                                                                | ning a second electrode, which is coupled to the second doped semiconductor layer; and     |  |  |

| 13 | forn                                                                                | ning a passivation layer, which substantially covers the sidewalls of the first and second |  |  |

| 14 | doped semi                                                                          | conductor layers, the MQW active layer, and part of the surface of the second doped        |  |  |

| 15 | semiconduc                                                                          | ctor layer which is not covered by the second electrode.                                   |  |  |

|    |                                                                                     |                                                                                            |  |  |

| 1  | 12.                                                                                 | The method of claim 11,                                                                    |  |  |

| 2  | whe                                                                                 | rein the substrate comprises at least one of the following materials:                      |  |  |

| 3  |                                                                                     | Cu,                                                                                        |  |  |

| 4  |                                                                                     | Cr,                                                                                        |  |  |

| 5  |                                                                                     | Si, and                                                                                    |  |  |

| 6  |                                                                                     | SiC.                                                                                       |  |  |

| 1 | 13. The method of claim 11,                                                      |                                                                                          |  |  |  |

|---|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|

| 2 | wherein the passivation layer comprises at least one of the following materials: |                                                                                          |  |  |  |

| 3 |                                                                                  | silicon oxide (SiO <sub>x</sub> ),                                                       |  |  |  |

| 4 |                                                                                  | silicon nitride (SiN <sub>x</sub> ), and                                                 |  |  |  |

| 5 |                                                                                  | silicon oxynitride (SiO <sub>x</sub> N <sub>y</sub> ).                                   |  |  |  |

| 6 |                                                                                  |                                                                                          |  |  |  |

| 1 | 14.                                                                              | The method of claim 11,                                                                  |  |  |  |

| 2 | wherei                                                                           | n the first doped semiconductor layer is a p-type doped semiconductor layer.             |  |  |  |

| 1 | 15.                                                                              | The method of claim 14,                                                                  |  |  |  |

| 2 | where                                                                            | in forming a passivated portion in the p-type doped semiconductor layer comprises        |  |  |  |

| 3 | selectively act                                                                  | ivating the p-type dopant in the un-passivated portions by introducing Pt to the un-     |  |  |  |

| 4 | passivated por                                                                   | tions during a low-temperature annealing process.                                        |  |  |  |

| 1 | 16.                                                                              | The method of claim 14,                                                                  |  |  |  |

| 2 | where                                                                            | in forming a passivated portion in the p-type doped semiconductor layer comprises        |  |  |  |

| 3 | first activating                                                                 | the dopants in the entire p-type layer and then selectively passivating a portion of the |  |  |  |

| 4 | p-type layer by                                                                  | y introducing hydrogen ions to the passivated portion.                                   |  |  |  |

| 5 |                                                                                  |                                                                                          |  |  |  |

| 1 | 17.                                                                              | The method of claim 11,                                                                  |  |  |  |

| 2 | wherei                                                                           | n the second doped semiconductor layer is an n-type doped semiconductor layer.           |  |  |  |

| 1 | 18.                                                                              | The method of claim 11,                                                                  |  |  |  |

| 2 | where                                                                            | n the MQW active layer comprises GaN and InGaN.                                          |  |  |  |

| 1 | 19.  | The method of claim 11,                                                       |

|---|------|-------------------------------------------------------------------------------|

| 2 | wher | ein the first substrate comprises a pre-defined pattern of grooves and mesas. |

|   |      |                                                                               |

| 1 | 20.  | The method of claim 11,                                                       |

| 2 | whe  | rein the passivation layer is formed by one of the following processes:       |

| 3 |      | plasma-enhanced chemical vapor deposition (PECVD),                            |

| 4 |      | magnetron sputtering deposition, and                                          |

| 5 |      | e-beam deposition.                                                            |

|   |      |                                                                               |

| 1 | 21.  | The method of claim 11,                                                       |

| 2 | whe  | rein the thickness of the passivation layer is between 300 Å and 10,000 Å.    |

| 3 |      |                                                                               |

FIG. 1 (PRIOR ART)

FIG. 2A

FIG. 2B

ЗН

31

3J

3K

FIG. 3 (continued)

FIG. 4

41

4J

4K

4L

FIG. 4 (continued)

International application No.

PCT/CN2008/001494

#### A. CLASSIFICATION OF SUBJECT MATTER

#### See extra sheet

According to International Patent Classification (IPC) or to both national classification and IPC

#### FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC (2010.01) H01L33/00, H01L21/20

5F041/AA03, 5F041/AA04, FI/F-term 5F041/AA08

EC H01L33/00G3D, H01L33/00G6, H01L33/00C3D

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

#### EPODOC, WPI, PAJ, CNPAT, CNKI:

LED, light emitting diode, light emitting device; MQW, multiple quantum well; active layer, active region; recombinat+; current, charge, carrier, hole, electron; efficiency, intensity, brightness, output; passivat+, insulat+, isolat+; GaN, gallium nitride; Pt, platinum, metal; anneal, heat treatment; electrode;

#### C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages     | Relevant to claim No. |

|-----------|----------------------------------------------------------------------------------------|-----------------------|

| A         | US2006/0157714A1 (Yoo et al.), 20 July 2006 (20.07.2006), the whole document           | 1-21                  |

| A         | JP6-204558A (KYOCERA CORP.), 22 July 1994 (22.07.1994), the whole document             | 1-21                  |

| Α         | CN1825643A (UNIV BEIJING POLYTECHNIC), 30 August 2006 (30.08.2006), the whole document | 1-21                  |

| X | urther | documents | s are liste | d in the | continuation | ot Rox | C. K |

|---|--------|-----------|-------------|----------|--------------|--------|------|

|---|--------|-----------|-------------|----------|--------------|--------|------|

- See patent family annex.

- Special categories of cited documents:

- document defining the general state of the art which is not considered to be of particular relevance

- earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim (S) or which is cited to establish the publication date of another citation or other special reason (as specified)

- document referring to an oral disclosure, use, exhibition or

- document published prior to the international filing date but later than the priority date claimed

- later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the

- document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

- "&"document member of the same patent family

Date of mailing of the international search report Date of the actual completion of the international search 05 Sep. 2008 (05.09.2008)

Name and mailing address of the ISA/CN The State Intellectual Property Office, the P.R.China 6 Xitucheng Rd., Jimen Bridge, Haidian District, Beijing, China

Authorized officer

LIU, Zhen

23 Oct. 2008(23.10.2008)

Telephone No. (86-10)62414074

Form PCT/ISA/210 (second sheet) (April 2007)

Facsimile No. 86-10-62019451

International application No. PCT/CN2008/001494

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                         | Relevant to claim No  |

|-----------|------------------------------------------------------------------------------------------------------------|-----------------------|

|           | Chadon of document, with indication, where appropriate, of the relevant passages                           | Relevant to ciann 190 |

| Α         | US2003/0121468A1 (Boone et al.), 03 July 2003 (03.07.2003), the whole document                             | 1-21                  |

| Α         | US2007/0243414A1 (MiKi), 18 October 2007 (18.10.2007), the whole document                                  | 1-21                  |

| Α         | US2006/0175682A1 (Muraki et al.), 10 August 2006 (10.08.2006), the whole document                          | 1-21                  |

| Α ,       | JP10-251957A (MITSUBISHI RAYON CO LTD.), 22 September 1998 (22.09.1998), the whole document                | 1-21                  |

| Α         | US2004/0256631A1 (Shin), 23 December 2004 (23.12.2004), the whole document                                 | 1-21                  |

| Α         | JP2006-196589A (SHARP KK), 27 July 2006 (27.07.2006), the whole document                                   | 1-21                  |

| <b>A</b>  | CN1738066A (DONGGUAN FUDI ELECTRONIC MATERIALS CO LTD.), 22 February 2006 (22.02.2006), the whole document | 1-21                  |

| Α         | CN1354528A (INST SEMICONDUCTORS CHINESE ACAD SCI), 19 June 2002 (19.06.2002), the whole document           | 1-21                  |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            | ~                     |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

|           |                                                                                                            |                       |

Form PCT/ISA/210 (continuation of second sheet ) (April 2007)

Information on patent family members

International application No. PCT/CN2008/001494

| Patent Documents referred in the Report | Publication Date | Patent Family             | Publication Date |

|-----------------------------------------|------------------|---------------------------|------------------|

| US2006/0157714A1                        | 20.07.2006       | WO2005/008795A1           | 27.01.2005       |

|                                         |                  | KR20050009658A            | 25.01.2005       |

|                                         |                  | KR100432246B              | 10.05.2004       |

| JP6-204558A                             | 22.07.1994       | JP2912781B2               | 28.06.1999       |

| CN1825643A                              | 30.08.2006       | None                      |                  |

| US2003/0121468A1                        | 03.07.2003       | WO03/036697A              | 01.05.2003       |

|                                         |                  | US7179329B2               | 20.02.2007       |

|                                         |                  | US2004/0029368A1          | 12.02.2004       |

| - ,                                     |                  | US7179731B2               | 20.02.2007       |

|                                         |                  | JP2005508077T             | 24.03.2005       |

|                                         |                  | CN1608310A                | 20.04.2005       |

|                                         |                  | CN100359638C              | 02.01.2008       |

| US2007/0243414A1                        | 18.10.2007       | WO2005/117151A            | 08.12.2005       |

|                                         |                  | JP2006-013475A 2006-01-12 |                  |

|                                         |                  | TW260099B                 | 11.08.2006       |

| US2006/0175682A1                        | 10.08.2006       | JP2006-245555A            | 14.09.2006       |

| JP10-251957A                            | 22.09.1998       | None                      |                  |

| US2004/0256631A1                        | 23.12.2004       | US6949773B2               | 27.09.2005       |

|                                         |                  | KR20050000197A            | 03.01.2005       |

|                                         |                  | JP2005-019939A            | 20.01.2005       |

|                                         |                  | JP3745763B2               | 15.02.2006       |

| JP2006-196589A                          | 27.07.2006       | None                      |                  |

| CN1738066A                              | 22.02.2006       | None                      |                  |

| CN1354528A                              | 19.06.2002       | CN1147010C                | 21.04.2004       |

|                                         |                  |                           |                  |

Form PCT/ISA/210 (patent family annex) (April 2007)

International application No.

PCT/CN2008/001494

| A. CLASSIFICATION OF SUBJECT MATTER            |  |

|------------------------------------------------|--|

| H01L33/00 (2010.01) i<br>H01L21/20 (2006.01) i |  |

|                                                |  |

| •                                              |  |

|                                                |  |

| •                                              |  |

|                                                |  |

|                                                |  |

|                                                |  |

| •                                              |  |

|                                                |  |

|                                                |  |

| Form PCT/ISA/210 (outre sheet) (April 2007)    |  |

Form PCT/ISA/210 (extra sheet) (April 2007)

**CORRECTED SHEET**