### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2010-147239 (P2010-147239A)

(43) 公開日 平成22年7月1日(2010.7.1)

| (51) Int.Cl. |          |               | FΙ             |          |             |           | テーマコー    | ド (参考) |

|--------------|----------|---------------|----------------|----------|-------------|-----------|----------|--------|

| HO1L         | 21/336   | (2006.01)     | HO1L           | 29/78    | 658G        |           | 5F110    |        |

| HO1L         | 29/78    | (2006.01)     | HO1L           | 29/78    | 658H        |           |          |        |

| HO1L         | 29/739   | (2006.01)     | HO1L           | 29/78    | 652H        |           |          |        |

| HO1L         | 27/04    | (2006.01)     | HO1L           | 29/78    | 655A        |           |          |        |

| HO1L         | 29/786   | (2006.01)     | HO1L           | 29/78    | 657C        |           |          |        |

|              |          |               | 審査請求 オ         | ·請求      | 請求項の数 5     | OL        | (全 16 頁) | 最終頁に続く |

| (21) 出願番号    | <u>L</u> | 特願2008-322703 | (P2008-322703) | (71) 出   | 願人 000003   | 078       |          |        |

| (22) 出願日     |          | 平成20年12月18日   |                | 株式会      | 社東芝         |           |          |        |

|              |          |               |                |          | 東京都         | 港区芝浦      | 第一丁目1番1  | l 号    |

|              |          |               |                | 17A) AV: | F# A 100100 | 200 · - · |          |        |

(/4) 代埋人 100109900 弁理士 堀口 浩

70年 本本 <del>本</del>

(72) 発明者 遠藤 幸一

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 泉沢 優

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 原 琢磨

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

# (54) 【発明の名称】半導体装置及びその製造方法

# (57)【要約】

【課題】結晶欠陥形成領域の平面位置精度を上げること が可能な半導体装置及びその製造方法を提供する。

【解決手段】n型ドリフト層12、p型ベース層15、n+型ソース層16及びゲート電極25を有するMOSFETと、n型ドリフト層12の表面から徐々に増加する再結合中心となる結晶欠陥密度分布のテール領域T1を有し、n型ドリフト層12中のp型ベース層15とn型ドリフト層12のpn接合を順方向に流れる電流経路またはその近傍に、テール領域T1から続く欠陥ピーク領域31を有し、裏面に向かって欠陥ピーク領域31から続く徐々に減少するテール領域T2を有し、平面的に選択的に形成されたライフタイム制御領域6と、ライクタイム制御領域6に隣接し、表面の結晶欠陥密度が、ライフタイム制御領域6の表面の結晶欠陥密度が、ライフタイム制御領域6の表面の結晶欠陥密度が、ライフタイム制御領域6の表面の結晶欠陥密度を超えることはなく、表面から裏面に徐々に増加するテール領域T3を有するライフタイム非制御領域7とを備える。

### 【選択図】図1

7 6

: 半導体装置 6:ライフタイム制御領域

7:ライフタイム制御領域

7:ライフタイム非制御領域 11:n・型ドレイン層

12:n型ドリフト層 15:p型ベース層 16:n+型ソース層

21:ゲート総線膜 25:ゲート電極 26:ソース電極

29:ドレイン電極 31:欠略ピーク領域 33:寄生ダイオード

D:ドレイン G:ゲート S:ソース T1、T2、T3:テール領域

#### 【特許請求の範囲】

### 【請求項1】

第1の面及び前記第1の面に平行且つ対向する第2の面を有する第1導電型の第1半導体層と、

前記第2の面の側の表面に設けられ前記第1半導体層と電気的に接続された第1電極と、前記第1の面の表面領域に選択的に設けられた複数の第2導電型の第2半導体層と、

前記第2半導体層の表面領域に選択的に設けられた第1導電型の第3半導体層と、

前記第2半導体層及び前記第3半導体層の表面に接するように設けられた第2電極と、

隣接する前記第2半導体層間の前記第1半導体層上にゲート絶縁膜を介して設けられたゲート電極と、

前記第1の面に垂直に、前記第1半導体層、前記第2半導体層、または前記第3半導体層の少なくとも1つの表面から連続する再結合中心となる結晶欠陥密度分布の徐々に増加する第1のテール領域、前記第1のテール領域から連続し増加から減少に転じるピーク領域、及び前記ピーク領域から連続し徐々に減少する第2のテール領域を有し、前記第2半導体層及び前記第1半導体層の間のpn接合を順方向に流れる電流経路を横切り、且つ前記第1半導体層の中に前記ピーク領域を有する前記第1の面に沿った方向に広がった第1の領域と、

前記第1の領域に隣接し、前記第1の面に沿った方向に広がり、前記第1の面に垂直に、前記第1乃至第3半導体層のいずれかの表面から、徐々に増加する再結合中心となる結晶 欠陥密度分布の第3のテール領域を有し、表面では隣接した前記第1のテール領域の結晶 欠陥密度を超えることはなく、且つ前記第1半導体層の中に前記第3のテール領域に連続 するピーク領域が存在しない第2の領域と、

を備えていることを特徴とする半導体装置。

#### 【請求項2】

第1の面、前記第1の面に平行且つ対向する第2の面、及び前記第1の面から前記第2の面の方向に掘り下げられた前記第1の面に平行な第3の面を有する第1導電型の第1半導体層と、

前記第2の面の側の表面に設けられ前記第1半導体層と電気的に接続された第1電極と、前記第1の面の表面領域に選択的に設けられた複数の第2導電型の第2半導体層と、

前記第2半導体層の表面領域に選択的に設けられた第1導電型の第3半導体層と、

前記第2半導体層及び前記第3半導体層の表面に接するように設けられた第2電極と、

隣接する前記第2半導体層間の前記第1半導体層上にゲート絶縁膜を介して設けられたゲート電極と、

前記第1の面に垂直に、前記第1半導体層、前記第2半導体層、または前記第3半導体層の少なくとも1つの表面から連続する再結合中心となる結晶欠陥密度分布の徐々に増加する第1のテール領域、前記第1のテール領域から連続し増加から減少に転じるピーク領域、及び前記ピーク領域から連続し徐々に減少する第2のテール領域を有し、前記第2半導体層及び前記第1半導体層の間のpn接合を順方向に流れる電流経路を横切り、且つ前記第1半導体層の中に前記ピーク領域を有する前記第1の面に沿った方向に広がった第1の領域と、

前記第1の領域に隣接し、前記第1の面に沿った方向に広がり、前記第3の面に垂直に、前記第3の面から、徐々に増加する再結合中心となる結晶欠陥密度分布の第3のテール領域を有し、前記第3の面では前記第3の面の延長面上で隣接した前記第1のテール領域の結晶欠陥密度を超えることはなく、且つ前記第1半導体層の中に前記第3のテール領域に連続するピーク領域が存在しない第2の領域と、

を備えていることを特徴とする半導体装置。

#### 【請求項3】

基体の上に、絶縁膜を介して形成された第1導電型の第1半導体層と、 前記第1半導体層の表面領域に選択的に設けられた前記第1半導体層とpn接合を形成する第2導電型の第2半導体層と電気的に接続された第1電極と、 10

20

30

40

前記第1半導体層の表面領域に選択的に設けられ、前記第2半導体層と離間した第2導電型の第3半導体層と、

前記第3半導体層の表面に選択的に設けられた第1導電型の第4半導体層と、

前記第3半導体層及び前記第4半導体層の表面に接するように設けられた第2電極と、

隣接する前記第4半導体層と前記第1半導体層の間の前記第3半導体層の上のゲート絶縁膜を介して設けられたゲート電極と、

を有する電力用スイッチング素子と、

前記第1半導体層の表面から徐々に増加する再結合中心となる結晶欠陥密度分布の第1のテール領域を有し、前記第2半導体層及び前記第1半導体層の間の前記pn接合を順方向に流れる電流経路または前記電流経路の近傍であって、且つ前記第1半導体層の中に、前記第1のテール領域から続く増加から減少に転じるピーク領域を有し、且つ、前記第1半導体層の表面に対向する裏面に向かって前記ピーク領域から前記絶縁膜まで続く徐々に減少する結晶欠陥密度分布の第2のテール領域を有し、前記第1半導体層の表面に沿った方向に、選択的に広がりを有する第1の領域と、

前記第1の領域に隣接し、前記第1半導体層の表面に沿った方向に広がり、前記第1半導体層の表面の結晶欠陥密度が、前記第1の領域の表面の結晶欠陥密度を超えることはなく、前記第1半導体層の表面から前記絶縁膜まで、徐々に増加する再結合中心となる結晶欠陥密度分布の第3のテール領域を有する第2の領域と、

を備えていることを特徴とする半導体装置。

### 【請求項4】

少なくとも、基体の上に形成された第1導電型の第1半導体層と、前記第1半導体層の表面領域に選択的に設けられた前記第1半導体層とpn接合を形成する第2導電型の第2半導体層とが形成されている電力用スイッチング素子を選択的に有する半導体装置において、

前記 p n 接合を順方向に流れる電流経路または電流経路近傍に対して、垂直上方に位置する前記第 1 半導体層の表面に、減速材を配置し、前記第 1 半導体層の表面上方から、前記電流経路または前記電流経路近傍に結晶欠陥密度分布のピーク領域が来るように、且つ前記電流経路または前記電流経路近傍を外れた前記第 1 半導体層に結晶欠陥密度分布のピーク領域が存在しないように軽イオンを照射する工程と、

前記減速材を除去する工程と、

を備えていることを特徴とする半導体装置の製造方法。

# 【請求項5】

第1導電型の半導体基板の上に形成された第1導電型の第1半導体層の電力用スイッチング素子となる領域の平面周辺部に、前記第1半導体層の表面から距離D1の深さに底面を有する凹部を形成する工程と、

前記第1半導体層の表面領域に第2導電型の第2半導体層を選択的に形成し、pn接合を 形成する工程と、

前記電力用スイッチング素子の前記 p n 接合を順方向に流れる電流経路または電流経路近傍であって且つ前記 p n 接合を構成する前記第 1 半導体層の中の、前記半導体基板の前記第 1 半導体層に対向する裏面から前記距離 D 1 より小さい距離 D 2 の深さに、再結合中心となる結晶欠陥密度分布のピーク領域が来るように、前記第 1 半導体層の表面から軽イオンを照射する工程と、

を備えていることを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

### 【技術分野】

# [0001]

本発明は、キャリアライフタイム制御により特性改善を図る半導体装置及びその製造方法に関する。

### 【背景技術】

[ 0 0 0 2 ]

10

20

30

40

電力用の半導体装置に、例えば、MOSFET (Metal Oxide Semiconductor Field Effect Transistor) やIGBT (Insulated Gate Bipolar Transistor) 等がある。これらの電力用の半導体装置は、高電圧・大電流化と共に、スイッチングの高速化が要求されることが多い。

## [0003]

MOSFETは、寄生ダイオードが内蔵されている。例えば、インダクタンス負荷を有するDC-DCコンバータ用やインバータ用等に、nチャネル型MOSFETが使用される場合、寄生ダイオードは、順方向に電流を流して、転流用として使用される。寄生ダイオードの逆回復特性を改善するために、電子、H+またはHe2+等の荷電粒子を照射することにより、n型ドリフト層のキャリアライフタイムを短く制御する技術が知られている。つまり、nチャネル型MOSFETは、寄生ダイオードの順方向に電流が流れてバイポーラ動作をするため、n型ドリフト層に電子及びホールが流れ込むが、電子等の荷電粒子照射により再結合中心となる結晶欠陥が形成されている場合、再結合寿命、すなわちキャリアライフタイムが短縮され、逆回復特性が改善される。

### [0004]

また、IGBTは、ターンオフ時、ゲート電極にエミッタ電極に対して負の電圧が印加され、 n + エミッタ層からの電子の流入は止まるが、電子は n 型ドリフト層(または、 n 型ベース層等という)内に残る。一方、ホールの大部分はエミッタ電極に流出するものの、一部のホールは n 型ドリフト層内に残る。残った電子及びホールは、再結合により消滅するので、上述の電子の他、 H + または H e 2 + 等(以降、陽子(プロトン)、重陽子(デューテロン)、ヘリウムイオン等の原子番号(すなわち陽子数)1及び2のイオンを「軽イオン」と記述)を照射することによって、キャリアライフタイムを短く制御することが可能である。

### [00005]

再結合中心と結晶欠陥は次のような関係にある。シリコンのようなバンドギャップが大きい半導体材料は、再結合中心を介して再結合が行われるので、電子と正孔に対しての再結合を効率的に促進するためには、再結合中心をバンドギャップの中央近傍に導入することが理想とされている。そして、軽イオン等を照射し、意図的に結晶欠陥を誘起させることにより、再結合中心がバンドギャップの中央近傍に導入されることが知られている。

## [0006]

結晶欠陥を形成するために、例えば、IGBTにおいて、裏面側のコレクタ電極の表面にアルミニウム等の金属のアブゾーバ、更にその表面に開口を形成したステンレス等のマスクを設け、これらを介してヘリウム等の軽イオンを照射し、マスクの微細開口を通過した部分の軽イオン線はn‐ベース層内に飛程位置が設定されるよう加速エネルギーとアブゾーバの厚さとが調整される製造方法が開示されている(例えば、特許文献 1 参照。)。

#### [0007]

開示されたIGBTは、マスクを用いて軽イオンを照射することにより、全面照射したものに比較して、特性の改善が見られるものの、加速エネルギー20MeVに対して、アブゾーバは30μm厚、マスクは50μm厚が必要であり、マスク開口は半径が140μm等の構成となり、開口の更なる微細化を図ることや平面的な位置精度をあげることは難しいという問題を有している。つまり、基板面に沿った方向で、耐圧維持が必要な領域には軽イオンの照射を行う等の選択的な照射要求に対して答えることが難しいという問題を有している。

【特許文献1】特許第2963204号

## 【発明の開示】

【発明が解決しようとする課題】

#### [00008]

本発明は、結晶欠陥形成領域の平面位置精度を上げることが可能な半導体装置及びその製造方法を提供する。

# 【課題を解決するための手段】

10

20

30

#### [0009]

本発明の一態様の半導体装置は、第1の面及び前記第1の面に平行且つ対向する第2の 面を有する第1導電型の第1半導体層と、前記第2の面の側の表面に設けられ前記第1半 導体層と電気的に接続された第1電極と、前記第1の面の表面領域に選択的に設けられた 複数の第 2 導電型の第 2 半導体層と、前記第 2 半導体層の表面領域に選択的に設けられた 第 1 導電型の第 3 半導体層と、前記第 2 半導体層及び前記第 3 半導体層の表面に接するよ うに設けられた第2電極と、隣接する前記第2半導体層間の前記第1半導体層上にゲート 絶縁膜を介して設けられたゲート電極と、前記第1の面に垂直に、前記第1半導体層、前 記 第 2 半 導 体 層 、 ま た は 前 記 第 3 半 導 体 層 の 少 な く と も 1 つ の 表 面 か ら 連 続 す る 再 結 合 中 心となる結晶欠陥密度分布の徐々に増加する第1のテール領域、前記第1のテール領域か ら連続し増加から減少に転じるピーク領域、及び前記ピーク領域から連続し徐々に減少す る第 2 のテール領域を有し、前記第 2 半導体層及び前記第 1 半導体層の間の p n 接合を順 方向に流れる電流経路を横切り、且つ前記第1半導体層の中に前記ピーク領域を有する前 記第1の面に沿った方向に広がった第1の領域と、前記第1の領域に隣接し、前記第1の 面に沿った方向に広がり、前記第1の面に垂直に、前記第1乃至第3半導体層のいずれか の表面から、徐々に増加する再結合中心となる結晶欠陥密度分布の第3のテール領域を有 し、表面では隣接した前記第1のテール領域の結晶欠陥密度を超えることはなく、且つ前 記 第 1 半 導 体 層 の 中 に 前 記 第 3 の テ ー ル 領 域 に 連 続 す る ピ ー ク 領 域 が 存 在 し な い 第 2 の 領 域とを備えていることを特徴とする。

# [0010]

本発明の別態様の半導体装置は、第1の面、前記第1の面に平行且つ対向する第2の面 、 及 び 前 記 第 1 の 面 か ら 前 記 第 2 の 面 の 方 向 に 掘 り 下 げ ら れ た 前 記 第 1 の 面 に 平 行 な 第 3 の面を有する第1導電型の第1半導体層と、前記第2の面の側の表面に設けられ前記第1 半導体層と電気的に接続された第1電極と、前記第1の面の表面領域に選択的に設けられ た複数の第2導電型の第2半導体層と、前記第2半導体層の表面領域に選択的に設けられ た第1導電型の第3半導体層と、前記第2半導体層及び前記第3半導体層の表面に接する ように設けられた第2電極と、隣接する前記第2半導体層間の前記第1半導体層上にゲー ト絶縁膜を介して設けられたゲート電極と、前記第1の面に垂直に、前記第1半導体層、 前記第2半導体層、または前記第3半導体層の少なくとも1つの表面から連続する再結合 中心となる結晶欠陥密度分布の徐々に増加する第1のテール領域、前記第1のテール領域 から連続 し増加から減少に転じるピーク領域、及び前記ピーク領域から連続し徐々に減少 する 第 2 の テ ー ル 領 域 を 有 し 、 前 記 第 2 半 導 体 層 及 び 前 記 第 1 半 導 体 層 の 間 の p n 接 合 を 順方向に流れる電流経路を横切り、且つ前記第1半導体層の中に前記ピーク領域を有する 前記第1の面に沿った方向に広がった第1の領域と、前記第1の領域に隣接し、前記第1 の面に沿った方向に広がり、前記第3の面に垂直に、前記第3の面から、徐々に増加する 再結合中心となる結晶欠陥密度分布の第3のテール領域を有し、前記第3の面では前記第 3 の面の延長面上で隣接した前記第 1 のテール領域の結晶欠陥密度を超えることはなく、 且 つ 前 記 第 1 半 導 体 層 の 中 に 前 記 第 3 の テ ー ル 領 域 に 連 続 す る ピ ー ク 領 域 が 存 在 し な い 第 2の領域とを備えていることを特徴とする。

#### [0011]

本発明の別態様の半導体装置は、基体の上に、絶縁膜を介して形成された第1導電型の第1半導体層と、前記第1半導体層の表面領域に選択的に設けられた前記第1半導体層と pn接合を形成する第2導電型の第2半導体層と電気的に接続された第1電極と、前記第 1半導体層の表面領域に選択的に設けられ、前記第2半導体層と離間した第2導電型の第 3半導体層と、前記第3半導体層の表面に選択的に設けられた第1導電型の第4半導体層と、前記第3半導体層及び前記第4半導体層の表面に接するように設けられた第2電極と、隣接する前記第4半導体層と前記第1半導体層の間の前記第3半導体層の上のゲート絶縁膜を介して設けられたゲート電極とを有する電力用スイッチング素子と、前記第1半導体層の表面から徐々に増加する再結合中心となる結晶欠陥密度分布の第1のテール領域を有し、前記第2半導体層及び前記第1半導体層の間の前記pn接合を順方向に流れる電流 10

20

30

40

経路または前記電流経路の近傍であって、且つ前記第1半導体層の中に、前記第1のテール領域から続く増加から減少に転じるピーク領域を有し、且つ、前記第1半導体層の表面に対向する裏面に向かって前記ピーク領域から前記絶縁膜まで続く徐々に減少する結晶欠陥密度分布の第2のテール領域を有し、前記第1半導体層の表面に沿った方向に、選択的に広がりを有する第1の領域と、前記第1の領域に隣接し、前記第1半導体層の表面に沿った方向に広がり、前記第1半導体層の表面の結晶欠陥密度が、前記第1の領域の表面の結晶欠陥密度を超えることはなく、前記第1半導体層の表面から前記絶縁膜まで、徐々に増加する再結合中心となる結晶欠陥密度分布の第3のテール領域を有する第2の領域と、を備えていることを特徴とする。

## [0012]

本発明の別態様の半導体装置の製造方法は、少なくとも、基体の上に形成された第1導電型の第1半導体層と、前記第1半導体層の表面領域に選択的に設けられた前記第1半導体層とpn接合を形成する第2導電型の第2半導体層とが形成されている電力用スイッチング素子を選択的に有する半導体装置において、前記pn接合を順方向に流れる電流経路または電流経路近傍に対して、垂直上方に位置する前記第1半導体層の表面に、減速材を配置し、前記第1半導体層の表面上方から、前記電流経路または前記電流経路近傍に結晶欠陥密度分布のピーク領域が存在しないように軽イオンを照射する工程と、前記減速材を除去する工程とを備えていることを特徴とする。

# [ 0 0 1 3 ]

本発明の別態様の半導体装置の製造方法は、第1導電型の半導体基板の上に形成された第1導電型の第1半導体層の電力用スイッチング素子となる領域の平面周辺部に、前記第1半導体層の表面から距離D1の深さに底面を有する凹部を形成する工程と、前記第1半導体層の表面領域に第2導電型の第2半導体層を選択的に形成し、pn接合を形成する工程と、前記電力用スイッチング素子の前記pn接合を順方向に流れる電流経路または電流経路近傍であって且つ前記pn接合を構成する前記第1半導体層の中の、前記半導体基板の前記第1半導体層に対向する裏面から前記距離D1より小さい距離D2の深さに、再結合中心となる結晶欠陥密度分布のピーク領域が来るように、前記第1半導体層の表面から軽イオンを照射する工程とを備えていることを特徴とする。

## 【発明の効果】

### [0014]

本発明によれば、結晶欠陥形成領域の平面位置精度を上げることが可能な半導体装置及びその製造方法を提供することができる。

# 【発明を実施するための最良の形態】

# [0015]

以下、本発明の実施例について、図面を参照しながら説明する。以下に示す図では、比較例も含めて、同一の構成要素には同一の符号を付している。

### 【実施例1】

# [0016]

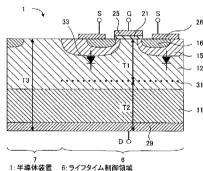

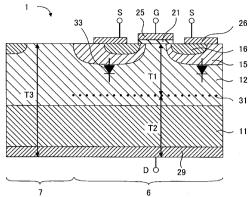

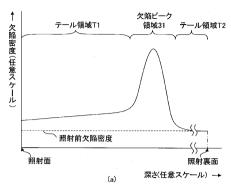

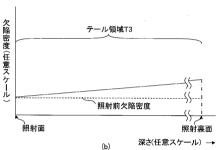

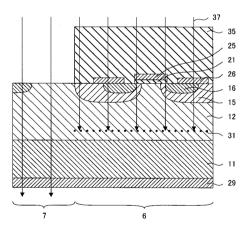

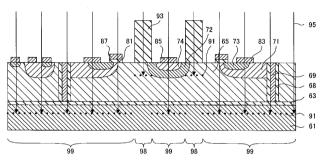

本発明の実施例1に係る半導体装置について、図1乃至図3を参照しながら説明する。図1は半導体装置の構造を模式的に示す断面図である。図2は半導体装置の結晶欠陥密度の分布を模式的に示す図で、図2(a)はキャリアライフタイム(以下、ライフタイムという)制御領域、図2(b)はライフタイム非制御領域を示す。図3は半導体装置の製造工程を模式的に示す構造断面図である。

#### [0017]

図1に示すように、半導体装置1は、第1導電型の第1半導体層であるn型ドリフト層12と、n型ドリフト層12の第2の面である裏面にn+型ドレイン層11を介してn型ドリフト層12と電気的に接続された第1電極であるドレイン電極29と、n型ドリフト層12の第1の面である表面の領域に選択的に設けられた複数の第2導電型の第2半導体層であるp型ベース層15と、p型ベース層15の表面に選択的に設けられた第3半導体

10

20

30

40

10

20

30

40

50

層である n + 型ソース層 1 6 と、 p 型ベース層 1 5 及び n + 型ソース層 1 6 の表面に接するように設けられた第 2 電極であるソース電極 2 6 と、隣接する p 型ベース層 1 5 間の n 型ドリフト層 1 2 上にゲート絶縁膜 2 1 を介して設けられたゲート電極 2 5 とを備えた n チャネル型 M O S F E T を有している。

[0018]

更に、半導体装置1は、p型ベース層15及びゲート絶縁膜21の下(裏面に近い側)の位置のn型ドリフト層12の中に、選択的に、結晶欠陥密度分布のピーク領域(以下、欠陥ピーク領域31という)を有している。欠陥ピーク領域31は、深さ方向に一定の幅を有している。なお、欠陥ピーク領域31は、nチャネル型の場合はn型ドリフト層12の中に形成されることが好ましい。ここで、nチャネル型MOSFETの表面の絶縁膜または保護膜等は図示を省略してある。

[0019]

半導体装置1の表面及び裏面にほぼ平行で、平面的な広がりを持った欠陥ピーク領域31が、半導体装置1の表面及び裏面に垂直に延長された領域をライフタイム制御領域6とし、欠陥ピーク領域31が存在しない同様な領域をライフタイム非制御領域7とする。つまり、半導体装置1を表面に垂直方向から見ると(平面図)、ライフタイム制御領域6とライフタイム非制御領域7に色分けされる。

[0020]

半導体装置1は、p型ベース層15及びn型ドリフト層12との境界に寄生ダイオード33を有している。逆モード動作(ドレインとソースを逆にした逆トランジスタ動作)時、寄生ダイオード33を順方向に流れる電流経路が、ソース電極26から、p型ベース層15、n型ドリフト層12、n+型ドレイン層11、及びドレイン電極29へ形成される。欠陥ピーク領域31は、寄生ダイオード33のpn接合に近接し、n型ドリフト層12内の逆モード動作時の電流経路上に配設されている。

[0021]

図2(a)に示すように、横軸を深さ、縦軸を結晶欠陥密度として、半導体装置1は、ライフタイム制御領域6の表面、すなわち、軽イオンを照射する側の面(照射面)、からn型ドリフト層12の中の欠陥ピーク領域31の手前まで、結晶欠陥密度は徐々に増加する第1のテール領域であるテール領域T1を有する。結晶欠陥密度分布は、テール領域T1から、欠陥ピーク領域31は、両側に結晶欠陥密度が急激に変化する裾を有し、中央部付近にピーク値を有する。結晶欠陥密度は、急激な減少の後、裏面側に徐々に減少する第2のテール領域であるテール領域T2を有し、軽イオン照射前の結晶欠陥密度(破線)に接近する。なお、軽イオンは、他の実施例を含めて陽子(プロトン)を用いているが、その他に、重陽子(デューテロン)、ヘリウムイオン等の原子番号1及び2を有する元素イオン等を使用可能である。

[0022]

照射面側のテール領域 T 1 では、軽イオンを照射する前の結晶欠陥密度に対して、照射面で既に増加位置にあり、その後少しずつ増加して欠陥ピーク領域 3 1 に達する。一方、照射裏面側のテール領域 T 2 では、欠陥ピーク領域 3 1 を過ぎるとテール領域 T 1 より急な傾斜で軽イオンを照射する前の結晶欠陥密度に近付く。

[0023]

欠陥ピーク領域 3 1 は、軽イオン 3 7 が到達する位置、すなわちイオン照射の飛程付近に集中的に誘起され、テール領域 T 1 及びテール領域 T 2 の結晶欠陥密度分布は、図 2 (a)に示す傾きを有することが知られている。

[0024]

欠陥ピーク領域 3 1 の結晶欠陥密度及び深さ方向の広がり(幅)は、軽イオンの種類及び照射時の加速エネルギー(照射エネルギーという)に依存する。照射面側のテール領域 T 1 の軽イオンを照射する前の結晶欠陥密度に対する増加量及び増加率は、軽イオンの照射エネルギーに依存する。結晶欠陥密度は、同一型及び同一不純物濃度の半導体層にあっては、抵抗率にほぼ対応する。

#### [ 0 0 2 5 ]

図2(b)に示すように、半導体装置1は、ライフタイム非制御領域7の照射面(表面)から照射裏面(裏面)まで、軽イオンを照射する前の結晶欠陥密度に対して、結晶欠陥密度は徐々に増加する第3のテール領域であるテール領域T3を有する。照射面において、テール領域T3の結晶欠陥密度は、テール領域T1の結晶欠陥密度より小さい。テール領域T3は、欠陥ピーク領域に達しない。つまり、シリコン結晶に対する軽イオンの平均飛程は、半導体装置1の裏面の外側に出てしまっている。テール領域T3の軽イオンを照射する前の結晶欠陥密度に対する増加量及び増加率は、テール領域T1と同様に、軽イオンの照射エネルギーに依存する。

## [0026]

図 2 ( a )、( b )に示す結晶欠陥密度分布は、照射面を半導体装置 1 の表面としているが、照射面を半導体装置 1 の裏面とすることは可能で、半導体装置 1 の裏面から照射する場合も、図 2 ( a )、( b )に示す結晶欠陥密度分布とほぼ同様な分布となる。

# [ 0 0 2 7 ]

次に、半導体装置1の製造方法について説明する。半導体装置1のnチャネル型MOSFET及びその周辺に配置される素子等は、周知の製造工程により作製される。

### [0028]

図3に示すように、欠陥ピーク領域31をp型ベース層15及びゲート絶縁膜21の下且つn型ドリフト層12の中に形成するために、p型ベース層15及びゲート絶縁膜21の照射面上に、フォトリソグラフィエ程によるパターニングによって、例えば、フォトレジストが、減速膜35として残されて形成される。なお、減速膜35の周辺のライフタイム非制御領域7となる表面に、フォトレジストを減速膜35より薄く残すことは可能である。

#### [0029]

その後、減速膜35及びn型ドリフト層等の上方から、ほぼ垂直に、軽イオン37が照射される。減速膜35に対応したp型ベース層15及びゲート絶縁膜21の下に欠陥ピーク領域31が形成され、ライフタイム制御領域6となる。減速膜35の周辺部は、結晶欠陥密度分布のテール領域が形成され、ライフタイム非制御領域7となる。

# [0030]

つまり、ライフタイム制御領域6では、減速膜35を介して軽イオン37が照射されることで、軽イオン37の速度が減衰され、n型ドリフト層12中に軽イオン37が停止して、欠陥ピーク領域31が形成される。それに対して、ライフタイム非制御領域7では、減速膜を介さずに直接ドリフト層12に軽イオン37が照射されるため、ライフタイム制御領域6のドリフト層12中よりも深く侵入し、n+ドレイン層11の裏面外側に突き抜けて出てしまい、nドリフト層12中には欠陥ピーク領域31が存在しない。

### [0031]

ここで、軽イオンの種類及び照射エネルギー、減速膜35の種類及び膜厚、並びにライフタイム非制御領域7の照射方向の厚さ、すなわち、半導体装置1の厚さは、ライフタイム制御領域6の欠陥ピーク領域31がn型ドリフト層12の中の適する位置に形成され、ライフタイム非制御領域7に欠陥ピーク領域31が形成されないように設定される。例えば、軽イオン37にH+(プロトン)を使用した場合、照射エネルギーは概略数MeV、ドーズ量は1E11~1E12cm-2、減速膜35はAlの薄板である。

## [0032]

ライフタイム制御領域6は、減速膜35を通過した軽イオン37が照射されて、図2(a)に示す結晶欠陥密度分布を有し、ライフタイム非制御領域7は、軽イオン37が直接照射されて、図2(b)に示す結晶欠陥密度分布を有する。軽イオンは、図2に示すように、ピーク値に向かって増加する結晶欠陥密度分布を有する。

### [0033]

減速膜35は、フォトレジストの他、シリコン系の無機または有機絶縁膜、他の樹脂膜、アルミニウム等の金属膜等が選択可能である。感光性のない膜の場合、フォトリソグラ

10

20

30

40

フィエ程によって、例えば、パターニングされたフォトレジストをマスクとして、エッチングして形成される。また、軽イオン37の減速効果を上げるために、複数種の積層膜、 金属等を添加した有機または無機絶縁膜等が選択可能である。

#### [0034]

次に、半導体装置1の表面の減速膜35が湿式またはドライエッチング法により除去され、半導体装置1が完成する。

#### [0035]

上述したように、半導体装置1は、表面にほぼ垂直に電流経路を有する縦型の電力用のnチャネル型MOSFETのp型ベース層15及びゲート絶縁膜21の裏面側に入ったn型ドリフト層12の中に選択的に欠陥ピーク領域31を有し、nチャネル型MOSFETに隣接する領域には、欠陥ピーク領域31に相当する欠陥ピーク領域を有することはない。nチャネル型MOSFETに隣接する領域の表面側の結晶欠陥密度は、nチャネル型MOSFETに隣接する領域の表面側の結晶欠陥密度より高めに推移するが、欠陥ピーク領域31の結晶欠陥密度より極めて小さい。

#### [0036]

その結果、電力用のnチャネル型MOSFETは、寄生ダイオード33を順方向に流れる電流経路に再結合中心が形成されて、ライフタイムを短縮して、半導体装置1は、高速動作が可能となる。

# [0037]

その上、半導体装置1は、再結合中心の平面的な位置が、フォトリソグラフィ法によるパターニングによって形成された減速膜35に基づいて決められるので、p型ベース層15の位置に対する欠陥ピーク領域31の平面位置、すなわち再結合中心の位置を、精度良く且つ再現性良く形成できる。その結果、ライフタイムを制御する領域にのみ再結合中心が形成され、その周辺の、耐圧を維持したい領域には再結合中心の欠陥ピーク領域が形成されず、耐圧の低下を抑制可能となる。特に、耐圧の低下をもたらす可能性の高いnチャネル型MOSFETに隣接する領域のn型ドリフト層12のn+型ドレイン層11寄りの領域において、再結合中心の急激な増加がなく、耐圧の低下が抑制される。

#### [0038]

また、上記実施例は、ライフタイム非制御領域7に欠陥ピーク領域31が形成されないように設定される例であるが、ライフタイム非制御領域7において、例えば、欠陥ピーク領域31がn+型ドレイン層11の中にすっぽり納まるような分布を取ることは可能である。この場合は、n型ドリフト層12のn+型ドレイン層11寄りの領域に再結合中心の増加領域がないので、耐圧の低下が抑制される。

# 【実施例2】

# [0039]

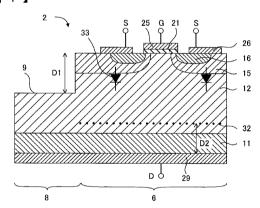

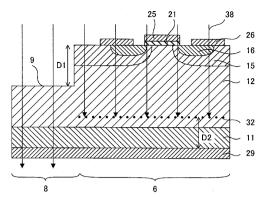

本発明の実施例2に係る半導体装置について、図4及び図5を参照しながら説明する。図4は半導体装置の構造を模式的に示す断面図である。図5は半導体装置の製造工程を模式的に示す構造断面図である。実施例1の半導体装置1とは、ライフタイム非制御領域が掘り込まれて凹部となっていることが異なる。なお、実施例1と同一構成部分には同一の符号を付して、その説明は省略する。

# [0040]

図4に示すように、半導体装置2は、実施例1のライフタイム非制御領域7に相当するライフタイム非制御領域8が、ライフタイム制御領域6に隣接して配置され、ライフタイム非制御領域8は、ライフタイム制御領域6の表面に対して、距離D1だけ下がった、つまり、裏面側に近付いた位置に表面を有する凹部9となっている。ライフタイム制御領域6に配設されている電力用のnチャネル型MOSFETは、実施例1の縦型のnチャネル型MOSFETと同様な構成である。

### [0041]

半導体装置2の製造方法について説明する。図5に示すように、欠陥ピーク領域32をn型ドリフト層12の中に形成する必要があるライフタイム制御領域6の半導体基板11

10

20

30

40

10

20

30

40

50

の裏面と、欠陥ピーク領域32(ピーク値位置)との間の距離D2は、ライフタイム制御領域6のn型ドリフト層12の表面に対するライフタイム非制御領域8の表面の距離D1、つまり凹部9の深さ、より小さく(D2<D1)設定されている。凹部9は、フォトリソグラフィ法によるパターニングによって形成されたマスク膜(図示略)に基づいて平面的な位置が決められて、距離D1は、RIE(Reactive Ion Etching)法または研磨/研削法等により形成される。ライフタイム制御領域6は、フォトリソグラフィ法の精度を有している。なお、凹部9の形成は、nチャネル型MOSFETを形成する前でもよいし、また、nチャネル型MOSFETを形成した後とすることも可能である。

### [0042]

次に、ライフタイム制御領域6及びライフタイム非制御領域8の表面上方から、ほぼ垂直に、軽イオン38が照射される。ライフタイム制御領域6の欠陥ピーク領域32が、p型ベース層15及びゲート絶縁膜21の下且つn型ドリフト層12の中に形成される。ライフタイム非制御領域8には、結晶欠陥密度分布のテール領域が形成される。

### [0043]

ここで、軽イオン38の照射エネルギーは、減速膜等を通過させる必要がないので、実施例1の軽イオン37の照射エネルギーより小さい。ライフタイム制御領域6では、実施例1と同様な位置に欠陥ピーク領域32が形成され、ライフタイム非制御領域8では、欠陥ピーク領域32に相当する欠陥ピーク領域を有することはない。

#### [0044]

その結果、半導体装置2は、実施例1の半導体装置1が有する効果を同様に有している。その上、半導体装置2は、ライフタイム非制御領域8の耐圧の低下をもたらす可能性の高いnチャネル型MOSFETに隣接する領域のn型ドリフト層12のn+型ドレイン層11寄りの領域において、軽イオン37の照射エネルギーがより小さい分、結晶欠陥密度をより低く維持できるので、耐圧の低下をより少なくすることが可能である。

#### 【実施例3】

### [0045]

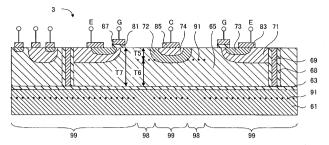

本発明の実施例3に係る半導体装置について、図6及び図7を参照しながら説明する。図6は半導体装置の構造を模式的に示す断面図である。図7は半導体装置の製造工程を模式的に示す構造断面図である。実施例1の半導体装置1とは、SOI(Silicon on Insulator)基板上の集積回路に適用された電力用スイッチング素子であることが異なる。なお、実施例1と同一構成部分には同一の符号を付して、その説明は省略する。

# [0046]

図6に示すように、半導体装置3は、基体である半導体基板61の上に、絶縁膜である埋込絶縁膜63を介して形成された第1導電型の第1半導体層であるn型ドリフト層65の表面領域に選択的に設けられた第2導電型の第2半導体層であるp+型コレクタ層74と電気的に接続された第1電極であるコレクタ電極85と、n型ドリフト層65の表面領域に選択的に設けられ、p+型コレクタ層74と離間した第3半導体層であるp型ベース層71と、p型ベース層71の表面に選択的に設けられた第4半導体層であるn+型エミッタ層73と、p型ベース層71の上のゲート絶縁膜81を介別をであるエミッタ電極83と、隣接するn+型エミッタ層73とn型ドリフト層65の間のp型ベース層71の上のゲート絶縁膜81を介別であるエミッタ電極83と、降接するn+型エミッタ層73とn世が一ト電極87とを有するIGBTを有している。また、p+型コレクタ層4に接して、n型ドリフト層65の中にn+型バッファ層72はなくてもよい。

#### [0047]

更に、半導体装置3は、n型ドリフト層65の表面に沿った方向に選択的に広がりを有する第1の領域であるライフタイム制御領域98を備えている。ライフタイム制御領域98は、n型ドリフト層65の表面から徐々に増加する再結合中心となる結晶欠陥密度分布の第1のテール領域であるテール領域T5を有し、p+型コレクタ層74及びn型ドリフト層65の中のn+型バッファ層72間のpn接合を順方向に流れる電流経路またはこの

電流経路の近傍であって且つ p n 接合の近傍の n 型ドリフト層 6 5 内に、テール領域 T 5 から続く増加から減少に転じる欠陥ピーク領域 9 1 を選択的に有し、且つ、 n 型ドリフト層 6 5 の表面に対向する裏面に向かって欠陥ピーク領域 9 1 から埋込絶縁膜 6 3 まで続く徐々に減少する結晶欠陥密度分布の第 2 のテール領域であるテール領域 T 6 を有する。欠陥ピーク領域 9 1 は、 p + 型コレクタ層 7 4 と n + 型バッファ層 7 2 間の p n 接合にかかることはなく、 n + 型バッファ層 7 2 にかかることは差し支えない。

[0048]

また、半導体装置3は、n型ドリフト層65の表面に沿った方向に選択的に広がりを有する第2の領域であるライフタイム非制御領域99を備えている。ライフタイム非制御領域99は、ライフタイム制御領域98に隣接し、n型ドリフト層65の表面から埋込絶縁膜63まで、徐々に増加する再結合中心となる結晶欠陥密度分布の第3のテール領域であるテール領域T7を有する。

[0049]

また、半導体装置3は、表面から埋込絶縁膜63に達する素子分離絶縁膜68及び隣接する2枚の素子分離絶縁膜68の間に埋め込まれた埋込ポリシリコン69からなる素子分離領域を有している。素子分離絶縁膜68を介して分離されたIGBTに隣接する領域には、別のトランジスタ等の素子が形成されている。

[0050]

半導体装置3は、テール領域T5、T6、T7、及び欠陥ピーク領域91の結晶欠陥密度分布は、実施例1のテール領域T1、T2、T3、及び欠陥ピーク領域31の結晶欠陥密度分布と同様な傾向を有している。

[0051]

次に、半導体装置3の製造方法について説明する。半導体装置3のIGBT及びその周辺に配置される素子等は、周知の製造工程により作製される。

[0052]

図 7 に示すように、欠陥ピーク領域 9 1 を n 型ドリフト層 6 5 の中に形成する必要があるライフタイム制御領域 9 8 の表面にのみ、フォトリソグラフィ法によるパターニングによって、例えば、フォトレジストが、減速膜 9 3 として残されて形成される。ライフタイム非制御領域 9 9 の表面には、フォトレジストが形成されない。

[ 0 0 5 3 ]

ライフタイム制御領域98上の減速膜93及びライフタイム非制御領域99の表面上方から、ほぼ垂直に、軽イオン95が照射される。軽イオンの種類及び照射エネルギー、減速膜93の種類及び膜厚、及びライフタイム非制御領域99のn型ドリフト層65の厚、すなわち、n型ドリフト層65の埋込絶縁膜63に達するまでの深さは、ライフタイム制御領域98の欠陥ピーク領域91がn型ドリフト層65の中の適する位置、すなわち、p+型コレクタ層74の側部下方のn+型バッファ層72及びn型ドリフト層65の中に形成され、且つライフタイム非制御領域99の欠陥ピーク領域91がn型ドリフト層65の外の半導体基板61の中に形成されるように設定される。なお、ライフタイム非制御領域99は、軽イオン95が半導体基板61の裏面外側に突き抜けて出てしまい、半導体基板61の中には欠陥ピーク領域91が存在しなくても差し支えない。

[ 0 0 5 4 ]

上述したように、半導体装置3は、p+型コレクタ層74とn+型バッファ層72との間のpn接合の近傍、このpn接合を順方向に流れるコレクタ電極85とエミッタ電極83を結ぶ電流経路またはこの電流経路の近傍に、欠陥ピーク領域91を有している。半導体装置3は、ライフタイム非制御領域99に、テール領域T7及び埋込絶縁膜63より裏面側に欠陥ピーク領域91を有している。

[0055]

その結果、IGBTは、pn接合を順方向に流れる電流経路に再結合中心が形成されて、ライフタイムを短縮して、半導体装置3は、高速動作が可能となる。横型のIGBTは、欠陥ピーク領域91の平面位置が、フォトリソグラフィ法によるパターニングされた減

10

20

30

40

速膜93により決められるので、平面精度及び再現性のよい再結合中心が形成される。半 導体装置 3 は、ライフタイム非制御領域 9 9 において、再結合中心が低い密度で維持され るので、ライフタイム非制御領域99の耐圧の低下等を抑制可能となる。

[0056]

以上、本発明は上記実施例に限定されるものではなく、本発明の要旨を逸脱しない範囲 内で種々変形して実施することができる。

[0057]

例えば、実施例 1 、 2 を電力用の縦型の n チャネル M O S F E T 、及び実施例 3 を横型 のIGBTを例として示したが、ライフタイム短縮制御が必要な他の構成の素子、すなわ ち、 横型 ま た は 縦 型 の 素 子 、 ま た 、 別 の 種 類 の 素 子 、 例 え ば 、 ダ イ オ ー ド 等 を 実 施 例 1 乃 至3に適用することは可能である。

[0058]

また、実施例はnチャネル型の電力用スイッチング素子に適用する例を示したが、pチ ャネル型の電力用スイッチング素子にも同様に適用することは可能である。

[0059]

本発明は、以下の付記に記載されるような構成が考えられる。

(付記1) 第1の面及び前記第1の面に平行且つ対向する第2の面を有する第1導電型 の第1半導体層と、前記第2の面の側の表面に設けられ前記第1半導体層と電気的に接続 された第1電極と、前記第1の面の表面領域に選択的に設けられた複数の第2導電型の第 2 半導体層と、前記第 2 半導体層の表面領域に選択的に設けられた第 1 導電型の第 3 半導 体 層 と 、 前 記 第 2 半 導 体 層 及 び 前 記 第 3 半 導 体 層 の 表 面 に 接 す る よ う に 設 け ら れ た 第 2 電 極 と 、 隣 接 す る 前 記 第 2 半 導 体 層 間 の 前 記 第 1 半 導 体 層 上 に ゲ ー ト 絶 縁 膜 を 介 し て 設 け ら れたゲート電極と、前記第1の面に垂直に、前記第1半導体層、前記第2半導体層、また は前記第3半導体層の少なくとも1つの表面から連続する再結合中心となる結晶欠陥密度 分 布 の 徐 々 に 増 加 す る 第 1 の テ ー ル 領 域 、 前 記 第 1 の テ ー ル 領 域 か ら 連 続 し 増 加 か ら 減 少 に転じるピーク領域、及び前記ピーク領域から連続し徐々に減少する第2のテール領域を 有し、前記第2半導体層及び前記第1半導体層の間のpn接合を順方向に流れる電流経路 を 横 切 り 、 且 つ 前 記 第 1 半 導 体 層 の 中 に 前 記 ピ ー ク 領 域 を 有 す る 前 記 第 1 の 面 に 沿 っ た 方 向に広がった第1の領域と、前記第1の領域に隣接し、前記第1の面に沿った方向に広が り、前記第1の面に垂直に、前記第1乃至第3半導体層のいずれかの表面から、徐々に増 加する再結合中心となる結晶欠陥密度分布の第3のテール領域を有し、表面では隣接した 前記第1のテール領域の結晶欠陥密度を超えることはなく、且つ前記第1半導体層の中に 前 記 第 3 の テ ー ル 領 域 に 連 続 す る ピ ー ク 領 域 が 存 在 し な い 第 2 の 領 域 と を 備 え て い る 半 導 体装置。

[0060]

(付記2) 再結合中心となる前記結晶欠陥は、原子番号1及び2を有する軽イオン照射 により形成される付記1に記載の半導体装置。

【図面の簡単な説明】

[0061]

【 図 1 】 本 発 明 の 実 施 例 1 に 係 る 半 導 体 装 置 の 構 造 を 模 式 的 に 示 す 断 面 図 。

【図2】本発明の実施例1に係る半導体装置の結晶欠陥密度の分布を模式的に示す図で、

【 図 3 】 本 発 明 の 実 施 例 1 に 係 る 半 導 体 装 置 の 製 造 工 程 を 模 式 的 に 示 す 構 造 断 面 図 。

【図4】本発明の実施例2に係る半導体装置の構造を模式的に示す断面図。

図 2 ( a ) はライフタイム制御領域、図 2 ( b ) はライフタイム非制御領域。

【図5】本発明の実施例2に係る半導体装置の製造工程を模式的に示す構造断面図。

【図6】本発明の実施例3に係る半導体装置の構造を模式的に示す断面図。

【 図 7 】 本 発 明 の 実 施 例 3 に 係 る 半 導 体 装 置 の 製 造 工 程 を 模 式 的 に 示 す 構 造 断 面 図 。

【符号の説明】

[0062]

1、2、3 半導体装置

20

10

30

40

```

6、98 ライフタイム制御領域

```

7、8、99 ライフタイム非制御領域

- 9 凹部

- 1 1 n + 型ドレイン層

- 12、65 n型ドリフト層

- 15、71 p型ベース層

- 16 n + 型ソース層

- 2 1 、 8 1 ゲート絶縁膜

- 25、87 ゲート電極

- 2 6 ソース電極

- 29 ドレイン電極

- 3 1 、 3 2 、 9 1 欠陥ピーク領域

- 33 寄生ダイオード

- 3 5 、 9 3 減速膜

- 37、38、95 軽イオン

- 6 1 半導体基板

- 63 埋込絶縁膜

- 68 素子分離絶縁膜

- 69 埋込ポリシリコン

- 72 n + 型バッファ層

- 7 3 n + 型エミッタ層

- 7 4 p + 型コレクタ層

- 83 エミッタ電極

- 85 コレクタ電極

- C コレクタ

- D ドレイン

- E エミッタ

- G ゲート

- S ソース

- D 1、D 2 距離

T 1、 T 2 、 T 3 、 T 5 、 T 6 、 T 7 テール領域

10

20

# 【図1】

7 6

1: 半導体装置 6: ライフタイム制御領域

7: ライフタイム非制御領域 11: n+型ドレイン層

12: n型ドリフト層 15: p型ベース層 16: n+型ソース層

21: ゲート絶緑膜 25: ゲート電極 26: ソース電極

29: ドレイン電極 31: 欠陥ピーク領域 33: 寄生ダイオード

D: ドレイン G: ゲート S: ソース T1, T2, T3: テール領域

# 【図2】

# 【図3】

6:ライフタイム制御領域 7:ライフタイム非制御領域 11:n+型ドレイン層 12:n型ドリフト層 15:p型ベース層 16:n+型ソース層 21:ゲート絶縁膜 25:ゲート電極 26:ソース電極 29:ドレイン電極 31:欠陥ピーク領域 35:滅速膜 37:軽イオン

# 【図4】

2: 半導体装置 6: ライフタイム制御領域 8: ライフタイム非制御領域 9: 凹部 11: n+型ドレイン層 12: n型ドリフト層 15: p型ベース層 16: n+型ソース層 21: ゲート絶縁膜 25: ゲート電極 26: ソース電極 29: ドレイン電極 32: 欠陥ピーク領域 33: 寄生ダイオード D: ドレイン G: ゲート S: ソース D1, D2: 距離

# 【図5】

6: ライフタイム制御領域 8: ライフタイム非制御領域 9: 凹部 11: n+型ドレイン層 12: n型ドリフト層 15: p型ベース層 16: n+型ソース層 21: ゲート絶縁膜 25: ゲート電極 26: ソース電極 29: ドレイン電極 32: 欠陥ピーク領域 38: 軽イオン D1、D2: 距離

# 【図6】

3: 半導体装置 61: 半導体基板 63: 埋込絶縁膜 65:n型ドリフト層 68: 素子分離絶縁膜 69: 埋込ポリシリコン 71:p型ベース層 72:n+型バッファ層 73:n+型エミッタ層 74:p・型コレクタ層 81: ゲート絶縁膜 83: エミッタ電極 85: コレクタ電極 87: ゲート電板 91: 久略ピーク領域 98: ライフタイム制御領域 99: ライフタイム非制御領域 0: コレクタ E: エミッタ G: ゲート T5, T6, T7: テール領域

# 【図7】

61: 半導体基板 63: 埋込絶縁膜 65:n型ドリフト層 68: 素子分離絶縁膜 69: 埋込ポリシリコン 71:p型ペース層 72:n+型パッファ層 73:n+型エミッタ層 74:p・型コレクタ層 81:ゲート絶縁膜 83:エミッタ電極 85:コレクタ電極 87:ゲート電極 91: 欠略ピーク領域 93:滅速膜 95:軽イオン 98:ライフタイム制御領域 99: ライフタイム非制御領域

# フロントページの続き

| (51) Int.CI.   |           | FΙ        |        |         | テーマコード(参考) |

|----------------|-----------|-----------|--------|---------|------------|

| H 0 1 L 21/322 | (2006.01) | H01L :    | 29/78  | 6 1 8 F |            |

| H 0 1 L 29/861 | (2006.01) | H 0 1 L 2 | 29/78  | 6 2 6 B |            |

|                |           | H 0 1 L 2 | 21/322 | L       |            |

|                |           | H 0 1 L 2 | 29/78  | 6 2 2   |            |

|                |           | H 0 1 L   | 29/91  | J       |            |

(72)発明者 小野 昇太郎

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 馬場 嘉朗

東京都港区芝浦一丁目1番1号 株式会社東芝内

F ターム(参考) 5F110 AA14 AA15 BB12 DD05 DD13 GG02 GG12 GG33 GG52 HM12 NN62 NN65