(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-253680

(P2006-253680A)

(43) 公開日 平成18年9月21日(2006.9.21)

(51) Int.CI.

H01L 27/146 (2006.01)

F 1

H01L 27/14

テーマコード(参考)

A 4M118

審査請求 未請求 請求項の数 23 O L (全 25 頁)

(21) 出願番号 特願2006-60320 (P2006-60320)

(22) 出願日 平成18年3月6日 (2006.3.6)

(31) 優先権主張番号 10-2005-0018763

(32) 優先日 平成17年3月7日 (2005.3.7)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国 443-742 京畿道水原市靈通

区梅灘洞 416

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100110364

弁理士 実広 信哉

最終頁に続く

(54) 【発明の名称】イメージセンサー及びその形成方法

## (57) 【要約】

【課題】イメージセンサー及びその形成方法を提供する。

【解決手段】フォトダイオードが形成された半導体基板上に下部モールド絶縁層と、ダミーパターンが内部に形成された上部モールド絶縁層を順次に形成する。ダミーパターンを除去して下部モールド絶縁層を露出させ、露出された下部モールド絶縁層を異方性エッチングして空洞領域を形成する。これにより、異方性エッチング量を減少させて空洞領域の側壁を殆ど垂直に形成させてフォトダイオードのオープン領域である空洞領域を極大化させうる。

【選択図】図9

**【特許請求の範囲】****【請求項 1】**

複数のフォトダイオードが互いに離隔されて形成された半導体基板上に保護絶縁膜、下部モールド絶縁層及び上部モールド絶縁層を順次に形成する段階；

前記上部モールド絶縁層内に前記下部モールド絶縁層と接触するダミーパターンを形成する段階；

前記ダミーパターンを選択的に除去して前記ダミーパターンと接触した前記下部モールド絶縁層を露出させる予備空洞領域を形成する段階；および

前記露出された下部モールド絶縁層を異方性エッチングして前記フォトダイオード上の前記保護絶縁膜を露出させる空洞領域を形成する段階；

を含むことを特徴とするイメージセンサーの形成方法。

10

**【請求項 2】**

前記上部モールド絶縁層及び前記ダミーパターンを形成する段階は、

前記下部モールド絶縁層上に配線モールド層を形成する段階；

前記配線モールド層内にダミー開口部を形成する段階；および

前記ダミー開口部を充填する充填パターンを形成する段階；

を含み、

前記上部モールド絶縁層は前記配線モールド層を含み、前記ダミーパターンは前記充填パターンを含むこと

を特徴とする請求項 1 に記載のイメージセンサーの形成方法。

20

**【請求項 3】**

前記配線モールド層を形成する段階、前記ダミー開口部を形成する段階及び前記充填パターンを形成する段階を複数回反復的に遂行し、

前記上部モールド絶縁層は、積層された複数の前記配線モールド層を含み、前記ダミーパターンは、積層された複数の前記充填パターンを含み、

前記積層された充填パターンのうちの最下部に設けられた充填パターンは、前記下部モールド絶縁層と接触し、最上部に設けられた充填パターンは露出されること

を特徴とする請求項 2 に記載のイメージセンサーの形成方法。

**【請求項 4】**

前記配線モールド層は、順次に積層されたバリヤ絶縁膜及び層間絶縁膜を含み、前記バリヤ絶縁膜は前記層間絶縁膜についてエッチング選択比を有すること

を特徴とする請求項 2 に記載のイメージセンサーの形成方法。

30

**【請求項 5】**

前記半導体基板は、前記フォトダイオードが形成される画素領域及び周辺回路が形成される周辺領域を有し、

前記周辺領域の上部モールド絶縁層内に少なくとも 1 層の周辺金属配線を形成する段階をさらに含み、前記ダミーパターンと前記少なくとも 1 層の周辺金属配線は、同一な物質で形成すること

を特徴とする請求項 1 に記載のイメージセンサーの形成方法。

40

**【請求項 6】**

前記フォトダイオードの間に設けられた前記上部モールド絶縁層の一部は、前記異方性エッチングによってエッチングされること

を特徴とする請求項 1 乃至請求項 5 のうちのいずれか一つの項に記載のイメージセンサーの形成方法。

**【請求項 7】**

前記上部モールド絶縁層上にマスク層を形成する段階；および

前記マスク層をパターニングして前記ダミーパターンを露出させる開口部を形成する段階；

をさらに含み、

前記フォトダイオードの間に設けられた前記上部モールド絶縁層上に配置された前記バ

50

ターニングされたマスク層の幅は、前記フォトダイオードの間に設けられた前記上部モールド絶縁層の幅に比べて狭く、

前記パターニングされたマスク層をエッチングマスクとして使用して前記異方性エッチングを遂行して前記下部モールド絶縁層及び前記フォトダイオードの間に設けられた前記上部モールド絶縁層の周縁をエッチングすること

を特徴とする請求項6に記載のイメージセンサーの形成方法。

【請求項8】

前記上部モールド絶縁層内に混信防止バリヤを形成する段階をさらに含み、前記混信防止バリヤは、前記フォトダイオードの間に形成された前記パターニングされたマスク層下に設けられること

を特徴とする請求項7に記載のイメージセンサーの形成方法。

【請求項9】

前記混信防止バリヤは、下部モールド層の上部面から上に離隔されるように形成すること

を特徴とする請求項8に記載のイメージセンサーの形成方法。

【請求項10】

前記混信防止バリヤは、前記ダミーパターンと同一な物質で形成されること

を特徴とする請求項8に記載のイメージセンサーの形成方法。

【請求項11】

前記下部モールド絶縁層内に少なくとも1層の画素金属配線を形成する段階をさらに含み、前記画素金属配線は、前記フォトダイオードの間に設けられた前記下部モールド層内に形成され、

前記異方性エッチング時、前記画素金属配線上に設けられる前記上部モールド絶縁層の下部が残存されること

を特徴とする請求項7に記載のイメージセンサーの形成方法。

【請求項12】

前記画素金属配線の上部面は、前記残存する上部モールド絶縁層と接触し、前記上部モールド絶縁層の下部面は、前記画素金属配線内金属元素の拡散を防止する絶縁物質で形成されること

を特徴とする請求項11に記載のイメージセンサーの形成方法。

【請求項13】

前記フォトダイオードの間に設けられた前記上部モールド絶縁層の全面が前記異方性エッチングによってエッチングされること

を特徴とする請求項6に記載のイメージセンサーの形成方法。

【請求項14】

前記下部モールド絶縁層内に少なくとも1層の画素金属配線を形成する段階をさらに含み、前記画素金属配線は、前記フォトダイオードの間に設けられた前記下部モールド絶縁層内に形成され、

前記異方性エッチング時、前記画素金属配線上に設けられる前記上部モールド絶縁層の下部が残存されること

を特徴とする請求項13に記載のイメージセンサーの形成方法。

【請求項15】

前記画素金属配線の上部面は、前記残存する上部モールド絶縁層と接触し、前記上部モールド絶縁層の下部面は、前記画素金属配線内金属元素の拡散を防止する絶縁物質で形成されること

を特徴とする請求項14に記載のイメージセンサーの形成方法。

【請求項16】

前記ダミーパターンは、湿式エッチングで除去すること

を特徴とする請求項1乃至請求項5のうちのいずれか一つの項に記載のイメージセンサーの形成方法。

10

20

30

40

50

**【請求項 17】**

前記空洞領域を形成した後に、

前記半導体基板上に前記空洞領域を充填する透明絶縁層を形成する段階をさらに含むこと

を特徴とする請求項1乃至請求項5のうちのいずれか一つの項に記載のイメージセンサーの形成方法。

**【請求項 18】**

複数のフォトダイオードが互いに離隔されて形成された半導体基板；

前記半導体基板上に順次に積層された保護絶縁膜、下部モールド絶縁層及び上部モールド絶縁層；

前記上部及び下部モールド絶縁層を連続的に貫通して前記フォトダイオード上に設けられた前記保護絶縁膜を露出させる空洞領域を充填する透明絶縁膜；および

前記フォトダイオードの間に設けられた前記上部モールド絶縁層内に形成された混信防止バリヤ；

を含むことを特徴とするイメージセンサー。

**【請求項 19】**

前記上部モールド絶縁層に形成された前記空洞領域の少なくとも一部は、前記下部モールド絶縁層に形成された前記空洞領域の幅に比べて広幅を有すること

を特徴とする請求項18に記載のイメージセンサー。

**【請求項 20】**

前記半導体基板は、前記フォトダイオードを含む画素領域、及び周辺回路が形成された周辺領域を有し、

前記周辺領域の前記上部モールド絶縁層内に少なくとも1層の周辺金属配線をさらに含み、前記混信防止バリヤは、前記周辺金属配線と同一な物質を含むことを特徴とする請求項18に記載のイメージセンサー。

**【請求項 21】**

前記フォトダイオードの間に設けられた前記下部モールド絶縁層内に形成された少なくとも1層の画素金属配線をさらに含むこと

を特徴とする請求項18乃至請求項20のうちのいずれか一つの項に記載のイメージセンサー。

**【請求項 22】**

前記混信防止バリヤは、前記下部モールド絶縁層上に離隔されて配置され、前記混信防止バリヤ下に設けられた前記上部モールド絶縁層の下部は前記フォトダイオードの間に設けられた前記下部モールド絶縁層の全面を覆うこと

を特徴とする請求項21に記載のイメージセンサー。

**【請求項 23】**

前記画素金属配線は、前記上部モールド絶縁層と接触し、前記上部モールド絶縁層の下部面は、前記画素金属配線内金属元素の拡散を防止する絶縁物質で形成されたことを特徴とする請求項21に記載のイメージセンサー。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体素子及びその形成方法に係り、特に、イメージセンサー及びその形成方法に関するものである。

**【背景技術】****【0002】**

イメージセンサーは、外部から伝達される光を電気的信号に変換してイメージを再現す

10

20

30

40

50

る装置である。通常、イメージセンサーは光を電気的信号に変換する光検出器としてフォトダイオードを探査している。外部の光は、フォトダイオードの空乏層に入射されて電子-正孔対（Electron-Hole Pairs；EHPs）を発生させ、信号電荷がフォトダイオード内に蓄積される。蓄積された信号電荷が動作信号によって出力される。これで、イメージセンサーは外部の光を電気的に変換させることができる。

#### 【0003】

最近、CMOS素子の製造技術が高度に発達しているのに伴って、高集積化が容易であり、電力消耗が少ない長所を有するCMOS（Complementary Metal-Oxide-Silicon）イメージセンサーが脚光を浴びている。CMOSイメージセンサーの画素は、外部の光を電気的信号に変換させるフォトダイオードと、フォトダイオードから発生した信号電荷を処理する少なくとも一つのMOSトランジスタと、を含む。10

#### 【0004】

CMOSイメージセンサーは、画素又は/及び周辺回路を構成するための多層の配線を積層できる。配線は、一般にアルミニウム膜をパターニングしたアルミニウム配線を主に使用する。だが、CMOSイメージセンサーが次第に微細になることによってより微細な配線形成方法が要求されている。また、より低い比抵抗を有する金属配線が要求されてもよい。このような要求を充足させるために、イメージセンサーの配線をダマシン技法で形成する方案が提案されたところがある。ダマシン技法に配線を形成する場合、微細な配線のパターニングがより容易になることができる。また、低い比抵抗を有する銅で配線を形成してもよい。20

#### 【0005】

イメージセンサーの画素のフォトダイオード上には、多くの種類の絶縁層を積層できる。特に、多層の銅配線が形成されるCMOSイメージセンサーは、フォトダイオード上に銅配線間の絶縁のための絶縁層と、ダマシン工程のためのエッチング停止層又は/及び銅元素の拡散を防止するためのバリヤ絶縁層が多数積層されうる。この際、フォトダイオード上に積層された絶縁層のうち一部は、外部光に関する透過率を低くすることができる。例えば、拡散防止層又は/及びエッチング停止層として主に使用される窒化シリコンなどは光に関する透過率が低いものとして知られている。このような外部光に関する吸収効率が低い絶縁層がフォトダイオード上に配置されれば、フォトダイオードに入射される外部光の強度などが減殺されてイメージセンサーの光感度を低下できる。従って、フォトダイオード上に積層された低透過率の絶縁層は後続で除去されることが好ましい。フォトダイオード上に積層された絶縁層を除去する従来方法は図1及び図2を参照して説明する。30

#### 【0006】

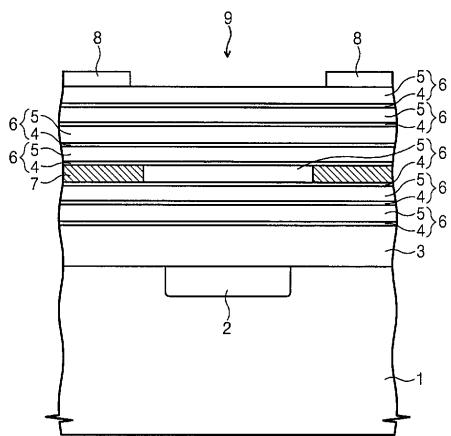

図1及び図2は、イメージセンサーの従来形成方法を説明するための断面図である。

#### 【0007】

図1を参照すれば、p型不純物でドーピングされた半導体基板1にn型不純物イオンを選択的に注入してn型不純物拡散層2を形成する。n型不純物拡散層2は、半導体基板1とpn接合されてフォトダイオードを構成する。

#### 【0008】

半導体基板1上に酸化膜3を形成し、酸化膜3上にシリコン窒化膜4及びシリコン酸化膜5を含むモールド層6を複数回積層させる。積層されたモールド層6内に銅配線7を形成する。図1の銅配線7は、イメージセンサーの画素内MOSトランジスタを動作させるための銅配線7である。勿論、示さないが、周辺回路が形成される領域内にも配線が形成される。銅配線7は、n型不純物拡散層2の上部には形成されない。40

#### 【0009】

シリコン窒化膜4は、銅配線7の形成をグループ又は/及びコンタクトホールの形成のためのエッチング停止層の機能又は/及び銅元素の拡散を防止する機能などを遂行する。

#### 【0010】

最上位に設けられたモールド層6上にマスク層8を形成し、マスク層をパターニングし50

て最上位に設けられたモールド層6を露出させる開口部9を形成する。

【0011】

図2を参照すれば、開口部9を有するマスク層7をエッティングマスクとして使用して積層されたモールド層6を連続的に異方性エッティングしてn型不純物拡散層2上に設けられた酸化膜3を露出させる空洞領域10を形成する。酸化膜3は、n型不純物拡散層2を保護する。

【0012】

前述したイメージセンサーの従来形成方法によれば、空洞領域10は、積層された複数のモールド層6を連続的に異方性エッティングして形成される。複数のモールド層6の厚さが非常に厚くなることによって、空洞領域10の側壁が傾斜するように形成できる。これにより、n型不純物拡散層2の周縁がモールド層6により覆われてフォトダイオードのオープン領域を縮小できる。フォトダイオードのオープン領域が縮小されれば、入射される光量が減少されてイメージセンサーの光感度が低下するおそれがある。また、空洞領域10の傾斜した側壁の傾斜角は不規則的でありうる。これにより、n型不純物拡散層2と開口部9の間の整列マージンが減少されて生産性が低下するおそれがある。

【発明の開示】

【発明が解決しようとする課題】

【0013】

本発明の技術的課題は、高集積化に最適化されたイメージセンサー及びその形成方法を提供するところにある。

【0014】

本発明の他の技術的課題は、光感度を向上させうるイメージセンサー及びその形成方法を提供するところにある。

【0015】

本発明のさらに他の技術的課題は、隣接する画素間の混信を最小化できるイメージセンサー及びその形成方法を提供するところにある。

【課題を解決するための手段】

【0016】

前述した技術的課題を解決するために本発明はイメージセンサーの形成方法を提供する。この方法は、次の段階を含む。複数のフォトダイオードが互いに離隔されて形成された半導体基板上に保護絶縁膜、下部モールド絶縁層及び上部モールド絶縁層を順次に形成する。上部モールド絶縁層内に下部モールド絶縁層と接触するダミーパターンを形成し、ダミーパターンを選択的に除去してダミーパターンと接触した下部モールド絶縁層を露出させる予備空洞領域を形成する。露出された下部モールド絶縁層を異方性エッティングしてフォトダイオード上の保護絶縁膜を露出させる空洞領域を形成する。

【0017】

具体的には、上部モールド絶縁層及びダミーパターンを形成する段階は、次の段階を含むことができる。下部モールド絶縁層上に配線モールド層を形成し、配線モールド層内にダミー開口部を形成する。ダミー開口部を充填する充填パターンを形成する。この際、上部モールド絶縁層は配線モールド層を含み、ダミーパターンは充填パターンを含む。配線モールド層を形成する段階、ダミー開口部を形成する段階及び充填パターンを形成する段階を複数回反復的に遂行できる。この際、上部モールド絶縁層は、積層された複数の配線モールド層を含み、ダミーパターンは、積層された複数の充填パターンを含む。積層された充填パターンのうちに最下部に設けられた充填パターンは、下部モールド絶縁層と接触し、最上部に設けられた充填パターンは露出されることが好ましい。配線モールド層は、順次に積層されたバリヤ絶縁膜及び層間絶縁膜を含むことができる。バリヤ絶縁膜は、層間絶縁膜についてエッティング選択比を有する。半導体基板は、フォトダイオードが形成される画素領域及び周辺回路が形成される周辺領域を有することができる。この際、この方法は、周辺領域の上部モールド絶縁層内に少なくとも1層の周辺金属配線を形成する段階をさらに含むことができる。ダミーパターンと少なくとも1層の周辺金属配線は、同一な

10

20

30

40

50

物質で形成できる。フォトダイオードの間に設けられた上部モールド絶縁層の一部は、異方性エッチングによってエッチングされることが好ましい。

#### 【0018】

一実施形態において、この方法は、上部モールド絶縁層上にマスク層を形成する段階と、マスク層をパターニングしてダミーパターンを露出させる開口部を形成する段階と、をさらに含むことができる。この際、フォトダイオードの間に設けられた上部モールド絶縁層上に配置されたパターニングされたマスク層の幅は、フォトダイオードの間に設けられた上部モールド絶縁層の幅に比べて狭くすることができる。パターニングされたマスク層をエッチングマスクとして使用して異方性エッチングを遂行して下部モールド絶縁層及びフォトダイオードの間に設けられた上部モールド絶縁層の周縁をエッチングすることができる。この方法は、上部モールド絶縁層内に混信防止バリヤ(crosstalk prevention barrier)を形成する段階をさらに含むことができる。混信防止バリヤは、フォトダイオードの間に形成されたパターニングされたマスク層下に設けられる。混信防止バリヤは、下部モールド層の上部面から上に離隔されるように形成できる。混信防止バリヤは、ダミーパターンと同一な物質で形成できる。この方法は、下部モールド絶縁層内に少なくとも1層の画素金属配線を形成する段階をさらに含むことができる。画素金属配線は、フォトダイオードの間に設けられた下部モールド層内に形成され、異方性エッチング時、画素金属配線上に設けられる上部モールド絶縁層の下部が残存されることが好ましい。画素金属配線の上部面は、残存する上部モールド絶縁層と接触し、上部モールド絶縁層の下部面は、画素金属配線内金属元素の拡散を防止する絶縁物質で形成されることが好ましい。

10

20

30

40

50

#### 【0019】

一実施形態において、フォトダイオードの間に設けられた上部モールド絶縁層の全面が異方性エッチングによってエッチングされることができる。この場合にも、この方法は、下部モールド絶縁層内に少なくとも1層の画素金属配線を形成する段階をさらに含むことができる。画素金属配線は、フォトダイオードの間に設けられた下部モールド絶縁層内に形成され、異方性エッチング時、画素金属配線上に設けられる上部モールド絶縁層の下部が残存される。画素金属配線の上部面は、残存する上部モールド絶縁層と接触し、上部モールド絶縁層の下部面は、画素金属配線内金属元素の拡散を防止する絶縁物質で形成されることが好ましい。

#### 【0020】

一実施形態において、ダミーパターンは、湿式エッチングで除去することができる。この方法は、空洞領域を形成した後に、半導体基板上に空洞領域を充填する透明絶縁層を形成する段階をさらに含むことができる。

#### 【0021】

前述した技術的課題を解決するために本発明はイメージセンサーを提供する。このイメージセンサーは、複数のフォトダイオードが互いに離隔されて形成された半導体基板と、半導体基板上に順次に積層された保護絶縁膜、下部モールド絶縁層及び上部モールド絶縁層と、を含むことができる。透明絶縁膜が上部及び下部モールド絶縁層を連続的に貫通してフォトダイオード上に設けられた保護絶縁膜を露出させる空洞領域を充填する。混信防止バリヤがフォトダイオードの間に設けられた上部モールド絶縁層内に形成される。

#### 【0022】

具体的には、上部モールド絶縁層に形成された空洞領域の少なくとも一部は、下部モールド絶縁層に形成された空洞領域の幅に比べて広幅を有することができる。半導体基板は、フォトダイオードを含む画素領域、及び周辺回路が形成された周辺領域を有することができる。この際、イメージセンサーは、周辺領域の上部モールド絶縁層内に少なくとも1層の周辺金属配線をさらに含むことができる。混信防止バリヤは、周辺金属配線と同一な物質を含むことができる。イメージセンサーは、フォトダイオードの間に設けられた下部モールド絶縁層内に形成された少なくとも1層の画素金属配線をさらに含むことができる。混信防止バリヤは、下部モールド絶縁層上に離隔されて配置され、混信防止バリヤ下に設けられた上部モールド絶縁層の下部はフォトダイオードの間に設けられた下部モール

ド絶縁層の全面を覆うことが好ましい。画素金属配線は、上部モールド絶縁層と接触し、上部モールド絶縁層の下部面は、画素金属配線内金属元素の拡散を防止する絶縁物質で形成されることが好ましい。

【発明の効果】

【0023】

本発明によれば、フォトダイオード上部に形成された上部モールド絶縁層内にダミーパターンを形成し、ダミーパターンを選択的に除去して下部モールド絶縁層を露出させた後に、露出された下部モールド絶縁層を異方性エッチングして空洞領域を形成する。これにより、空洞領域の形成のための異方性エッチング時、エッチングされる絶縁層が従来に比べて大きく縮小されることによって、空洞領域の側壁は、殆ど垂直に形成できる。その結果、フォトダイオードのオープン領域である空洞領域を最大に広げてイメージセンサーの光感度を向上させることができる。また、異方性エッチング時、フォトダイオードの間に設けられる上部モールド絶縁層の上部面全面又は周縁を共にエッチングする。これにより、空洞領域の上部の幅が拡大されて外部の光をさらに多く受け入れることができる。その結果、フォトダイオードに入射される光の強度などが増加されてイメージセンサーの光感度を向上させることができる。

【0024】

これに加えて、フォトダイオードの間に形成された上部モールド絶縁層内に混信防止バリヤが形成される。混信防止バリヤによって隣接するフォトダイオード間の入射される光の混合を最小化して画素の信号歪曲を最小化できる。

【発明を実施するための最良の形態】

【0025】

以下、添付した図面を参照して本発明の好適な実施形態を詳細に説明する。しかしながら、本発明はここで説明される実施形態に限定されず異なる形態で具体化されることもできる。むしろ、ここで紹介される実施形態は開示された内容が徹底で完全になることができるようそして当業者に本発明の思想が十分に伝達できるようにするために提供されることである。図面において、層（又は膜）及び領域の厚さは明確性を期するために誇張されたものである。また、層（又は膜）が他の層（又は膜）又は基板“上”にあると言及される場合にそれは他の層（又は膜）又は基板上に直接形成できるか、又はそれらの間に第3の層（又は膜）が介在されてもよい。明細書全体にかけて同一な参照符号で表示された部分は同一な構成要素を示すものとする。

【0026】

（第1の実施形態）

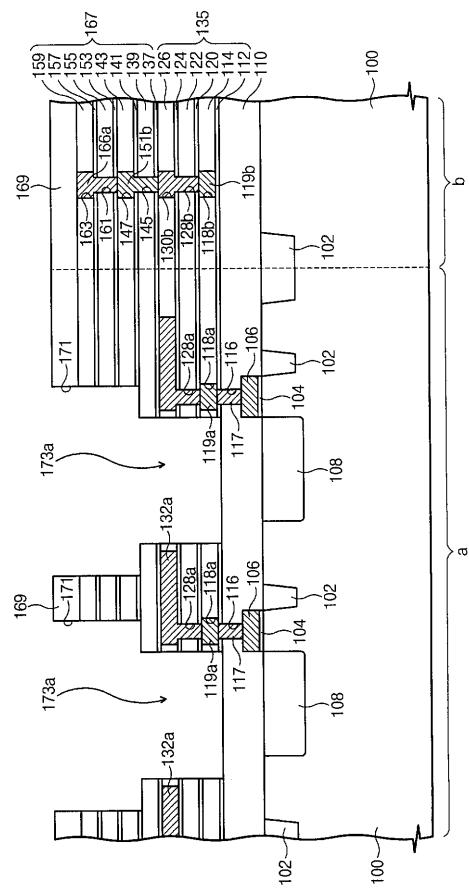

図3～図9は、本発明の一実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【0027】

図3を参照すれば、半導体基板100は、画素領域（a）及び周辺領域（b）を有する。画素領域（a）は、イメージセンサーの画素が形成される領域であり、周辺領域（b）はイメージセンサーの周辺回路が形成される領域である。少なくとも画素領域（a）の半導体基板100は、第1の導電型の不純物でドーピングされている。画素領域（a）の半導体基板100に第1の導電型の不純物でドーピングされたウェルを形成して第1の半導体基板100をドーピングできる。

【0028】

半導体基板100の所定領域に素子分離膜102を形成する。素子分離膜102は、画素領域（a）内に複数の画素活性領域を画定する。勿論、素子分離膜102は、周辺領域（b）内周辺活性領域も画定する。画素活性領域上に順次に積層されたゲート絶縁膜104及びゲート電極106を形成する。ゲート電極106は、CMOSイメージセンサーの画素内トランジスタを構成する。示さないが、ゲート電極106の形成時、周辺領域（b）内にも周辺ゲート電極（図示せず）を形成できる。

【0029】

10

20

20

30

40

50

ゲート電極 106 の一側の画素活性領域に第 2 の導電型の不純物イオンを選択的に注入して不純物拡散層 108 を形成する。不純物拡散層 108 は、第 1 の導電型の半導体基板 100 と p-n 接合されてフォトダイオードを形成する。各画素活性領域内に不純物拡散層 108 が形成される。従って、画素領域 (a) 内に複数の不純物拡散層 108 が互いに離隔されて形成される。すなわち、画素領域 (b) 内には、複数のフォトダイオードが互いに離隔されて形成される。

## 【0030】

ゲート電極 106 の他側に異なる第 2 の導電型の不純物イオンを注入してフローティング拡散層 (図示せず) を形成できる。不純物拡散層 108 とフローティング拡散層は、MOS ドラインのソース / ドレーン領域に該当し得る。不純物拡散層 108 とフローティング拡散層とは相異なる深さで形成できる。10

## 【0031】

第 1 の導電型の不純物と第 2 の導電型の不純物は、相異なるタイプである。例えば、第 1 の導電型の不純物は、n 型不純物であり、第 2 の導電型の不純物は p 型不純物でありうる。これとは違って、第 1 の導電型の不純物は p 型不純物であり、第 2 の導電型の不純物は n 型不純物であることもできる。

## 【0032】

示さないが、不純物拡散層 108 の表面に第 1 の導電型の不純物でドーピングされた表面拡散層 (図示せず) を形成できる。表面拡散層は、不純物拡散層 108 が形成された半導体基板 100 の表面状態 (例、ダングリングボンドなど) によって発生し得る暗電流を最小化できる。表面拡散層は、半導体基板 100 と電気的に接続する。ゲート電極 106 の両側壁にゲートスペーサ (図示せず) が形成されてもよい。20

## 【0033】

不純物拡散層 108 及びゲート電極 106 を有する半導体基板 100 の全面に保護絶縁膜 110 を形成する。保護絶縁膜 110 は、フォトダイオードの上部面が不純物拡散層 108 を保護することと共に層間絶縁機能を遂行する。保護絶縁膜 110 は、光の透過率が高い絶縁物質で形成することが好ましい。例えば、保護絶縁膜 110 は、シリコン酸化膜で形成することが好ましい。

## 【0034】

保護絶縁膜 110 上に第 1 のバリヤ絶縁膜 112 を形成し、第 1 のバリヤ絶縁膜 112 及び保護絶縁膜 110 を連続的にパターニングして画素領域 (a) 内に第 1 の画素ホール 116 を形成する。第 1 の画素ホール 116 は、示されたようにゲート電極 106 の上部面を露出させうる。示さないが、第 1 の画素ホール 116 は、半導体基板 108 を露出させてもよい。第 1 の画素ホール 116 の形成時、周辺領域 (b) 内に形成されたゲート電極 (図示せず) 又は周辺領域 (b) 内の半導体基板 100 を露出させる第 1 の周辺ホール (図示せず) が形成されてもよい。30

## 【0035】

第 1 の画素ホール 116 を充填する導電プラグ 117 を形成する。導電プラグ 117 は、導電物質であるドーピングされたポリシリコン、窒化チタン又は窒化タンタルのような導電性窒化物、又はタンゲステンなどを含むことができる。導電プラグ 117 の形成時、第 1 の周辺ホール (図示せず) を充填する導電プラグ (図示せず) も同時に形成できる。40

## 【0036】

導電プラグ 117 を有する半導体基板 100 の全面上に第 1 の層間絶縁膜 114 を形成する。第 1 の層間絶縁膜 114 をパターニングして画素領域 (a) 内に第 1 の画素グループ 118a 及び周辺領域 (b) 内に第 1 の周辺グループ 118b を形成する。第 1 の画素グループ 118a は、導電プラグ 117 を露出させ、第 1 の周辺グループ 118b は、第 1 の周辺ホール内に形成された導電プラグ (図示せず) を露出させる。

## 【0037】

第 1 の画素グループ 118a 及び第 1 の周辺グループ 118b を充填する第 1 の金属膜を形成し、第 1 の金属膜を第 1 の層間絶縁膜 114 が露出されるときまで平坦化させて第50

1の画素グループ118a内に第1の画素金属配線119a及び第1の周辺グループ118b内に第1の周辺金属配線119bを形成する。第1の画素金属配線119a及び第1の周辺金属配線119bは、銅又はアルミニウムを含むことができる。これに加えて、金属配線119a、119bは銅膜又はアルミニウム膜を取り囲む導電性バリヤをさらに含むことができる。導電バリヤは、窒化チタン又は窒化タンタルのような導電性金属窒化物を含むことができる。

#### 【0038】

第1の画素金属配線119aは、不純物拡散層108上には形成されない。すなわち、第1の画素金属配線119aは、n型不純物拡散層108の間に設けられた第1の層間絶縁膜114内に形成される。第1のバリヤ絶縁膜112及び第1の層間絶縁膜114は、第1の金属配線119a、119bを形成するための第1の配線モールド層を画定する。

#### 【0039】

配線119a、119bを有する半導体基板100上に第2のバリヤ絶縁膜120と、第2の層間絶縁膜122と、第3のバリヤ絶縁膜124及び第3の層間絶縁膜126と、を形成する。第3のバリヤ絶縁膜124、第2の層間絶縁膜122及び第2のバリヤ絶縁膜120を貫通する第2の画素ホール128a及び第2の周辺ホール128bと、第3の層間絶縁膜126内に第2の画素グループ130a及び第2の周辺グループ130bを形成する。第2の画素ホール128a及び第2の画素グループ130aは、画素領域(a)内に形成される。特に、第2の画素ホール128a及び第2の画素グループ130aは、n型不純物拡散層108(すなわち、フォトダイオード)の間に形成できる。第2の周辺ホール128b及び第2の周辺グループ130bは、周辺領域(b)に形成される。第2の画素グループ130a及び第2の画素ホール128aは互いに連通し、第2の周辺グループ130b及び第2の周辺ホール128bは互いに連通する。

#### 【0040】

第2の画素ホール128aは、第1の画素金属配線119aを露出させることができる。これとは違って、第2の画素ホール128aは第1の画素金属配線119aの一側に離隔されたバッファパターン(図示せず)を露出させてよい。バッファパターンは、第1の画素金属配線119aと同時に形成され、画素内他のゲート電極(図示せず)又は半導体基板100と接続できる。第2の周辺ホール128bは第1の周辺金属配線119bを露出させうる。

#### 【0041】

第2の画素及び周辺ホール128a、128bを先ず形成した後に、第2の画素及び周辺グループ130a、130bを形成できる。言い換えれば、第3の層間絶縁膜126、第3のバリヤ絶縁膜124、第2の層間絶縁膜122及び第2のバリヤ絶縁膜120を連続的にパターニングして画素及び周辺ホール128a、128bを形成する。次いで、第3の層間絶縁膜126をパターニングして第2の画素及び周辺ホール128a、128bとそれぞれ連通して第2の画素及び周辺グループ130a、130bを形成できる。

#### 【0042】

これとは違って、第2の画素及び周辺グループ130a、130bを先ず形成した後に、第2の画素及び周辺ホール128a、128bを形成できる。言い換えれば、第3の層間絶縁膜126をパターニングして第3のバリヤ絶縁膜124を露出させる第2の画素及び周辺グループ130a、130bを形成する。次いで、露出された第3のバリヤ絶縁膜124、第2の層間絶縁膜122及び第2のバリヤ絶縁膜120を連続的にパターニングして第2の画素及び周辺ホール128a、128bを形成できる。

#### 【0043】

第2の画素及び周辺グループ130a、130b及び第2の画素及び周辺ホール128a、128bを充填する第2の金属膜を半導体基板100の全面上に形成する。第2の金属膜を第3の層間絶縁膜126が露出されるときまで平坦化させて第2の画素ホール128a及び第2の画素グループ130aを充填する第2の画素金属配線132a、及び第2の周辺ホール128b及び第2の周辺グループ130bを充填する第2の周辺金属配線1

10

20

30

40

50

32bを形成する。第2の金属膜は、アルミニウム又は銅を含むことができる。これに加えて、第2の金属膜はアルミニウム膜又は銅膜を取り囲む導電性バリヤ（例、窒化チタン又は窒化タンタルのような導電性金属窒化物）をさらに含むことができる。

#### 【0044】

第2の画素及び周辺金属配線132bが形成される第3の層間絶縁膜126、第3のバリヤ絶縁膜124、第2の層間絶縁膜122及び第2のバリヤ絶縁膜120は、第2の配線モールド層を画定する。第1及び第2の配線モールド層は、下部モールド絶縁層135を構成する。

#### 【0045】

下部モールド絶縁層135は、画素領域(a)内画素金属配線119a、132aが形成される絶縁構造体に画定される。これにより、前述したように、画素領域(a)内に第1及び第2の画素金属配線119a、132aが形成される場合、下部モールド絶縁層135は、第1及び第2の配線モールド層を含むことができる。これとは違って、画素内に1層の画素金属配線が要求される場合、下部モールド絶縁層135は1層の配線モールド層のみを含むことができる。これとはまた違って、画素内に3層以上の画素金属配線が要求される場合、下部モールド絶縁層135は、3層以上の配線モールド層を含むことができる。

#### 【0046】

言い換えれば、下部モールド絶縁層135は、少なくとも1層以上の配線モールド層を含む。配線モールド層は、第1の配線モールド層のようにバリヤ絶縁膜112及び層間絶縁膜114を1回交代に積層できる。これとは違って、配線モールド層は、第2の配線モールド層のように、バリヤ絶縁膜120、124及び層間絶縁膜122、126を2回交代に積層できる。

#### 【0047】

バリヤ絶縁膜112、120、124は、金属配線119a、119b、132a、132b内金属元素の拡散を防止できる絶縁物質で形成されることが好ましい。また、バリヤ絶縁膜112、120、124は、層間絶縁膜114、122、126についてエッチング選択比を有することが好ましい。例えば、層間絶縁膜114、122、126がシリコン酸化膜で形成され、バリヤ絶縁膜112、120、124はシリコン窒化膜で形成できる。

#### 【0048】

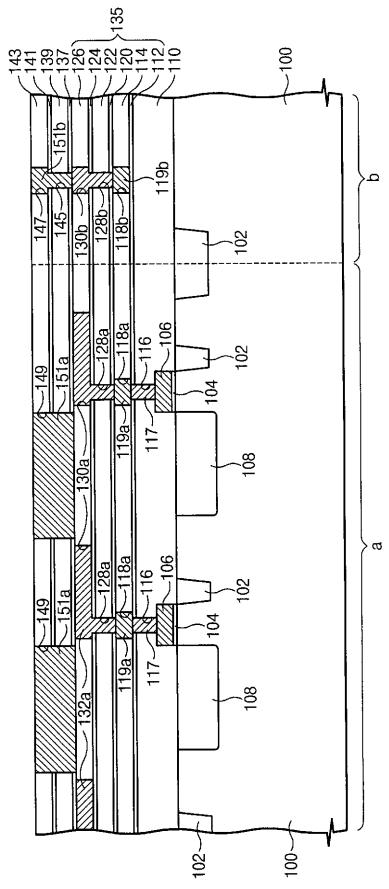

図4を参照すれば、第2の画素及び周辺金属配線132a、132bを有する半導体基板100上に順次に積層された第4のバリヤ絶縁膜137と、第4の層間絶縁膜139と、第5のバリヤ絶縁膜141及び第5の層間絶縁膜143と、を含む第3の配線モールド層を形成する。

#### 【0049】

第5の層間絶縁膜143内の第3の周辺グループ147と、第5のバリヤ絶縁膜141と、第4の層間絶縁膜139と、第4のバリヤ絶縁膜137を貫通して第2の周辺金属配線132bを露出させる第3の周辺ホール145と、を形成する。第3の周辺ホール145及び第3の周辺グループ147は、互いに連通し、周辺領域(b)内に形成される。この際、画素領域(a)の第3の配線モールド層を連続的に貫通して下部モールド絶縁層135を露出させる第1のダミー開口部149を形成する。第1のダミー開口部149は、n型不純物拡散層108（すなわち、フォトダイオード）の上部に形成される。

#### 【0050】

第3の周辺ホール145と、第3の周辺グループ147及び第1のダミー開口部149と、を形成する方法を説明する。第3の配線モールド層を連続的にパターニングして画素領域(a)の第1のダミー開口部149及び周辺領域(b)の第3の周辺ホール145を形成した後に、第5の層間絶縁膜143をパターニングして第3の周辺ホール145と連通する第3の周辺グループ147を形成することが好ましい。第3の周辺グループ147を形成する間にダミー開口部149は、感光膜パターン（図示せず）に覆われていること

10

20

30

40

50

が好ましい。

【0051】

他の方法で、第3の周辺グループ147を形成した後に、第3の周辺ホール145を形成できる。この場合に、第3の周辺グループ147と第1のダミー開口部149の一部（すなわち、第1のダミー開口部149の第5の層間絶縁膜143に形成される部分）は、第3の周辺グループ147と同時に形成され、第1のダミー開口部149の残り部分は、第3の周辺ホール145と同時に形成できる。

【0052】

第1のダミー開口部149、第3の周辺ホール145及び第3の周辺グループ147を充填する第3の金属膜を形成し、第3の金属膜を第3の配線モールド層が露出されるときまで平坦化させて第1のダミー開口部149を充填する第1の充填パターン151a及び第3の周辺ホール145及び第3の周辺グループ147を充填する第3の周辺金属配線151bを形成する。第3の金属膜は、アルミニウム又は銅を含むことができる。これに加えて、第3の金属膜は、アルミニウム膜又は銅膜を取り囲む導電性バリヤ（例、窒化チタン又は窒化タンタルのような導電性金属窒化物）をさらに含むことができる。

【0053】

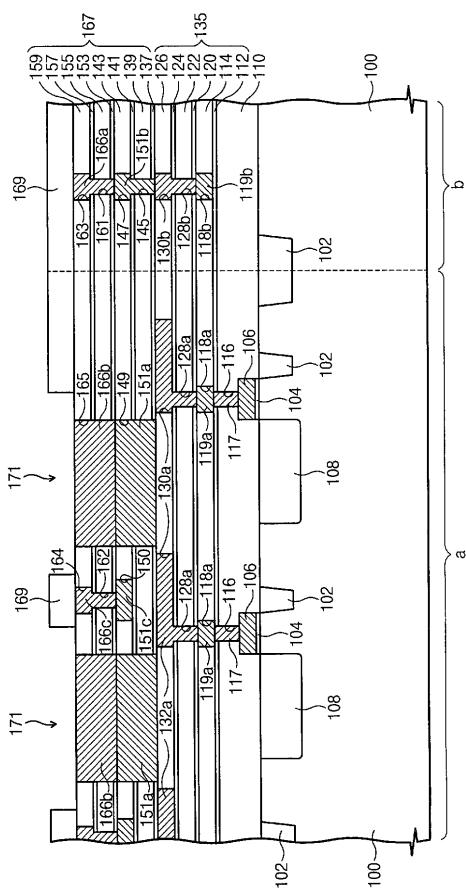

図5を参照すれば、第1の充填パターン151a及び第3の周辺金属配線151bを有する半導体基板100上に順次に積層された第6のバリヤ絶縁膜153、第6の層間絶縁膜155と、第7のバリヤ絶縁膜157及び第7の層間絶縁膜159を含む第4の配線モールド層を形成する。

【0054】

第7の層間絶縁膜159内の第4の周辺グループ163、及び第7のバリヤ絶縁膜157、第6の層間絶縁膜155及び第6のバリヤ絶縁膜153を連続的に貫通して第3の周辺金属配線151bを露出させる第4の周辺ホール161を形成する。この際、画素領域（a）の第4の配線モールド層内には、第1の充填パターン151aを露出させる第2のダミー開口部165が形成される。第4の周辺グループ163は、第4の周辺ホール161と連通する。

【0055】

第4の周辺ホール161、第4の周辺グループ163及び第2のダミー開口部165を形成する方法を具体的に説明する。第4の配線モールド層を連続的にパターニングして画素領域（a）の第2のダミー開口部165及び周辺領域（b）の第4の周辺ホール161を形成し、第7の層間絶縁膜159をパターニングして第4の周辺ホール161と連通する第4の周辺グループ163を形成することが好ましい。勿論、第4の周辺グループ163の形成時、第2のダミー開口部165は、感光膜パターン（図示せず）によって覆われていることが好ましい。

【0056】

他の方法で、第7の層間絶縁膜159をパターニングして第4の周辺グループ163及び画素領域（a）内に第2のダミー開口部165の一部を先ず形成した後に、第4の周辺グループ163に露出された第7のバリヤ絶縁膜157、第6の層間絶縁膜155及び第6のバリヤ絶縁膜153を連続的にエッチングして第4の周辺ホール161を形成できる。この際、第2のダミー開口部165の残り部分は第4の周辺ホール161と同時に形成される。

【0057】

第2のダミー開口部165、第4の周辺ホール161及び第4の周辺グループ163を充填する第4の金属膜を半導体基板100の全面に形成し、第4の金属膜を第4の配線モールド層が露出されるときまで平坦化させて第2のダミー開口部165を充填する第2の充填パターン166b、及び第4の周辺ホール161及び第4の周辺グループ163を充填する第4の周辺金属配線166aを形成する。第2の充填パターン166bは、第1の充填パターン151aと接触する。第4の金属膜もアルミニウム又は銅を含むことができる。これに加えて、第3の金属膜もアルミニウム膜又は銅膜を取り囲む導電性バリヤ（例

10

20

30

40

50

、窒化チタン又は窒化タンタルのような導電性金属窒化物)をさらに含むことができる。

【0058】

第3及び第4の配線モールド層は、上部モールド絶縁層167を構成し、第1及び第2の充填パターン151a、166bはダミーパターンを構成する。すなわち、上部モールド絶縁層167は、画素金属配線119a、132a上に形成された配線モールド層を含み、ダミーパターンは上部モールド絶縁層167内に形成されて下部モールド絶縁層135と接触する。

【0059】

上部モールド絶縁層167内に2層の周辺金属配線151b、166aが示されているが、上部モールド絶縁層167内には、1層以上の周辺金属配線を形成できる。すなわち、上部モールド絶縁層167は、周辺金属配線が形成される1層以上の配線鋳型層を含む。この際、充填パターンの積層数は、周辺金属配線の積層数と同一である。すなわち、ダミーパターンは、周辺金属配線の積層数と同一な数に積層された充填パターンを含む。

【0060】

バリヤ絶縁膜112、120、124、137、141、153、157は、互いに同一な物質で形成されることが好ましい。層間絶縁膜114、122、126、139、143、155、159もやはり互いに同一な物質で形成されることが好ましい。

【0061】

前述したように、下部及び上部モールド絶縁層135、167は、バリヤ絶縁膜及び層間絶縁膜が交互に積層された多層膜である。この際、上部モールド絶縁層167に含まれた絶縁膜の数は、下部モールド絶縁層135に含まれた絶縁膜の数より多いことが好ましい。具体的には、上部モールド絶縁層167に含まれた配線モールド層の数は、下部モールド絶縁層135に含まれた配線モールド層の数と同じか、或いは多いことが好ましい。下部及び上部モールド絶縁層135、167がそれぞれ1層の配線モールド層を有する場合、下部モールド絶縁層135の配線モールド層は、バリヤ絶縁膜112及び層間絶縁膜114が1回交代に積層され、上部モールド絶縁層167の配線モールド層は、バリヤ絶縁膜137、141及び層間絶縁膜139、143が2回交互に積層される。

【0062】

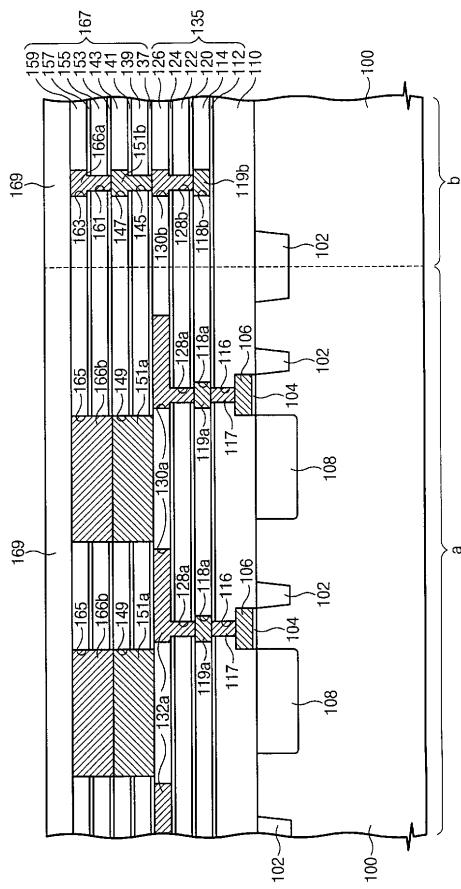

第2の充填パターン166b及び第4の周辺金属配線166aを有する半導体基板10上にマスク層169を形成する。マスク層169は、パッシベーション層でありうる。マスク層169は、下部及び上部モールド絶縁層135、167についてエッティング選択比を有することができる。また、マスク層169は、下部及び上部モールド絶縁層135、167についてエッティングマスクとして使用できる十分な厚さに形成できる。例えば、マスク層169は、シリコン酸化窒化膜などに形成できる。

【0063】

図6を参照すれば、マスク層169をパターニングしてダミーパターンを露出させる開口部171を形成する。この際、開口部171の幅は、ダミーパターンの幅(すなわち、充填パターン166b、151aの幅)に比べて広いことが好ましい。n型不純物拡散層108の間に設けられたパターニングされたマスク層169の幅は、n型不純物拡散層108の間に設けられた上部モールド絶縁層167の幅より狭いことが好ましい。すなわち、開口部171は、n型不純物拡散層108の間に設けられた上部モールド絶縁層167の上部面周縁を露出させる。

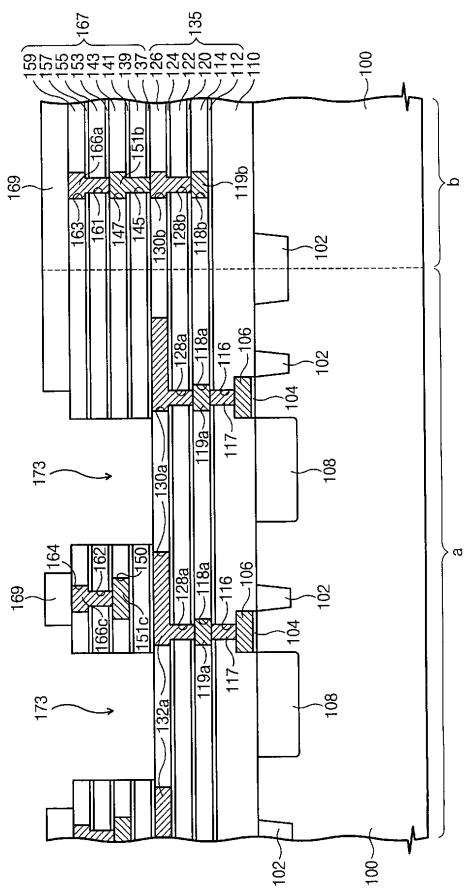

【0064】

図7を参照すれば、露出されたダミーパターンを選択的に除去して下部モールド絶縁層135を露出させる予備空洞領域173を形成する。ダミーパターンは、湿式エッティングに除去することができる。ダミーパターンは、第3及び第4の周辺金属配線151b、166aと同一な金属で形成されることによって選択的に除去できる。

【0065】

図8を参照すれば、開口部171を有するマスク層169をエッティングマスクとして使用して露出された下部モールド絶縁層135を異方性エッティングしてn型不純物拡散層上

に設けられる保護絶縁膜 110 を露出させる空洞領域 173a を形成する。この際、開口部 171 に露出された n 型不純物拡散層 108 の間に設けられた上部モールド絶縁層 167 の周縁も共にエッチングされる。上部モールド絶縁層 167 及び下部モールド絶縁層 135 は、互いに同一な物質で形成されるバリヤ絶縁膜及び層間絶縁膜が交互に積層されている。これにより、下部モールド絶縁層 135 を異方性エッチングするとき、上部モールド絶縁層 167 の周縁も共に異方性エッチングされる。その結果上部モールド絶縁層 167 に形成された空洞領域 173a は、下部モールド絶縁層 135 に形成された空洞領域 173a に比べて広幅を有するように形成される。

#### 【0066】

異方性エッチング時、上部モールド絶縁層 167 の下部がその下に設けられる下部モールド絶縁層 135 を覆うように残存されることが好ましい。上部モールド絶縁層 167 に含まれた絶縁層の数は、下部モールド絶縁層 135 に比べて多い。これにより、異方性エッティング時、上部モールド絶縁層 167 の下部を残存できる。残存する上部モールド絶縁層 167 の下部は、その下に形成された第 2 の画素金属配線 132a を覆う。特に、第 2 の画素金属配線 132a の上部面が下部モールド絶縁層 135 の上部面と同一であることによって、残存する上部モールド絶縁層 167 の下部は、第 2 の画素金属配線 132a と接触する。上部モールド絶縁層 167 の下部面は、バリヤ絶縁膜 137 で形成されている。これにより、第 2 の画素金属配線 132a 内における金属元素の拡散を防止できる。

#### 【0067】

バリヤ絶縁膜 112、120、124、137、141、153、157 が互いに同一な物質で形成され、層間絶縁膜 114、122、126、139、143、155、159 が互いに同一な物質で形成されることによって、上部モールド絶縁層 167 の異方性エッティングされる部分と、下部モールド絶縁層 135 は、互いに同一な物質の絶縁層が同一な順序に積層されている。

#### 【0068】

バリヤ絶縁膜 112、120、124、137、141、153、157 が互いに同一な厚さに形成されることは要求されない。勿論、層間絶縁膜 114、122、126、139、143、155、159 も互いに同一な厚さに形成されることも要求されない。これは、バリヤ絶縁膜 112、120、124、137、141、153、157 と層間絶縁膜 114、122、126、139、143、155、159 のエッティング選択比によって異方性エッティング時、バリヤ絶縁膜 112、120、124、137、141、153、157 及び層間絶縁膜 114、122、126、139、143、155、159 は、互いにエッティング停止層役割を遂行するためである。

#### 【0069】

図 9 を参照すれば、半導体基板 100 上に空洞領域 173a を充填する透明絶縁膜 175 を形成する。透明絶縁膜 175 は、光の透過率が高い絶縁物質で形成する。透明絶縁膜 175 は、スピノによるコーティング方式で形成できる。

#### 【0070】

前述したイメージセンサの形成方法によれば、空洞領域 173a は、上部モールド絶縁層 167 内に形成されたダミーパターンを除去して予備空洞領域 173 を形成した後に、予備空洞領域 173 に露出された下部モールド絶縁層 135 を異方性エッティングして形成される。すなわち、空洞領域 173a の形成のための異方性エッティング深さは、従来に比べて非常に縮められる。これにより、空洞領域 173a の側壁が殆ど垂直に形成されてフォトダイオードのオープン領域を最大化させうる。また、整列マージンを大幅に向上させる。

#### 【0071】

これに加えて、異方性エッティング時、n 型不純物拡散層 108 上に設けられた上部モールド絶縁層 167 がエッティングされる。これにより、空洞領域 173a の下部の幅は、n 型不純物拡散層 108 の上部面に画定されることと共に、空洞領域 173a の上部の幅は、空洞領域 173a の下部に比べて広幅を有する。これにより、フォトダイオードは、外

10

20

30

40

50

部の光をさらに多く受け入れることができる。その結果、フォトダイオードに入射される光の強度などが増加されてイメージセンサーの光感度を向上させうる。

### 【0072】

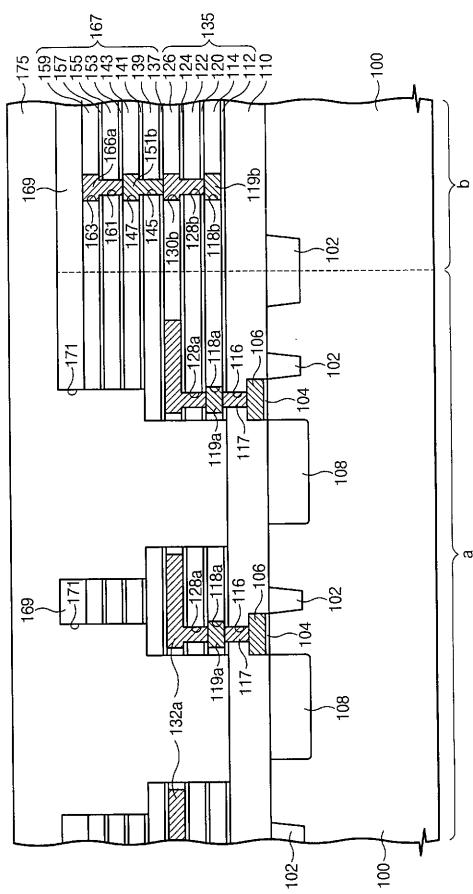

#### (第2の実施形態)

本実施形態は、前述した第1の実施形態と類似する。従って、第1の実施形態と同一な構成要素は、同一な参照符号を使用する。本実施形態によるイメージセンサーの形成方法は、前述した第1の実施形態の図3～図5を参照して説明した方法を同一に含むことができる。

### 【0073】

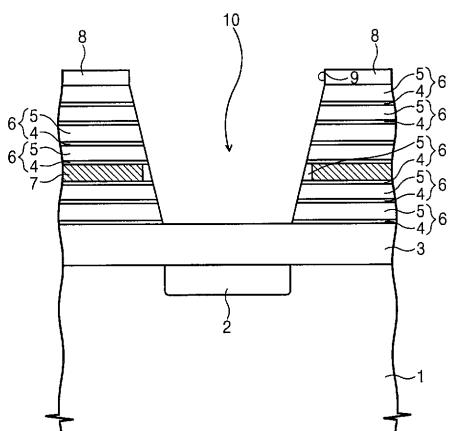

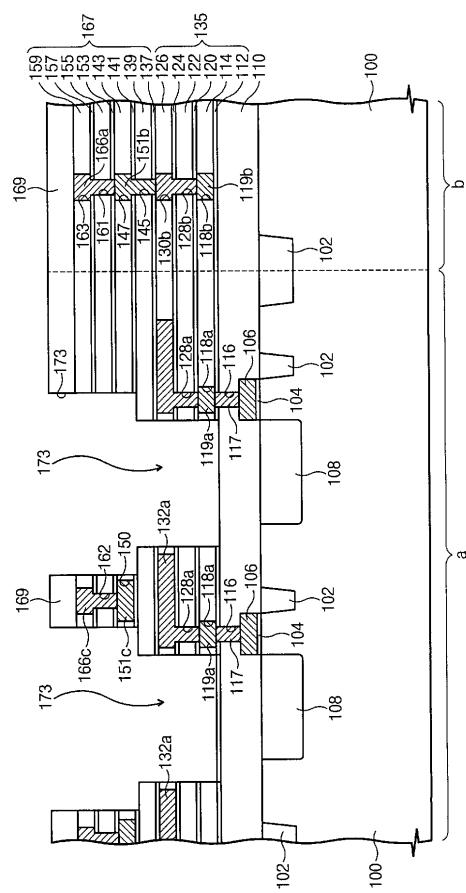

図10～図13は、本発明の他の実施形態によるイメージセンサーの形成方法を説明するための断面図である。

### 【0074】

図5及び図10を参照すれば、第2の充填パターン166b及び第4の周辺金属配線166aを有する半導体基板100上にマスク層169を形成し、マスク層169をパターニングしてダミーパターンを露出させる。この際、n型不純物拡散層108の間に設けられる上部モールド絶縁層167の全面が露出される。すなわち、画素領域(a)と周辺領域(b)の間の境界線に隣接したマスク層169の一部を除外した画素領域(a)の全域のマスク層169が除去される。パターニングされたマスク層169は、周辺領域(b)の第4の周辺金属配線166aを覆う。

### 【0075】

図11を参照すれば、ダミーパターンを選択的に除去して下部モールド絶縁層135を露出させる予備空洞領域173を形成する。ダミーパターンは、前述した第1の実施形態のように、湿式エッチングで除去することが好ましい。

### 【0076】

図12を参照すれば、パターニングされたマスク層169をエッチングマスクとして使用して露出された下部モールド絶縁層135を異方性エッチングしてn型不純物拡散層108上の保護絶縁膜110を露出させる空洞領域173a'を形成する。この際、異方性エッチング時、n型不純物拡散層108の間に設けられた上部モールド絶縁層167の上部面全面がエッチングされる。これにより、隣接する空洞領域173a'の上部は互いに連通する。

### 【0077】

異方性エッチング時、n型不純物拡散層108の間に設けられた上部モールド絶縁層167の下部は残存されることが好ましい。これにより、残存する上部モールド絶縁層167の下部は、n型不純物拡散層108の間に設けられた下部モールド絶縁層135の全面を覆う。勿論、上部モールド絶縁層167の底面は、第2の画素金属配線132a内金属元素の拡散を防止できるバリヤ絶縁膜137で形成されている。その結果、第2の画素金属配線132aが上部モールド絶縁層167と接触されて第2の画素金属配線132a内金属元素の拡散を防止できる。

### 【0078】

図13を参照すれば、空洞領域173a'を充填する透明絶縁膜175を半導体基板100の全面に形成する。

### 【0079】

前述したイメージセンサーの形成方法によれば、異方性エッチング時、n型不純物拡散層108(すなわち、フォトダイオード)の間に設けられた上部モールド絶縁層167の全面がエッチングされる。その結果、空洞領域173a'の上部が互いに連通されてフォトダイオード(すなわち、n型不純物拡散層108)に入射される外部光の強度などをさらに向上させうる。その結果、イメージセンサーの光感度をさらに向上させうる。

### 【0080】

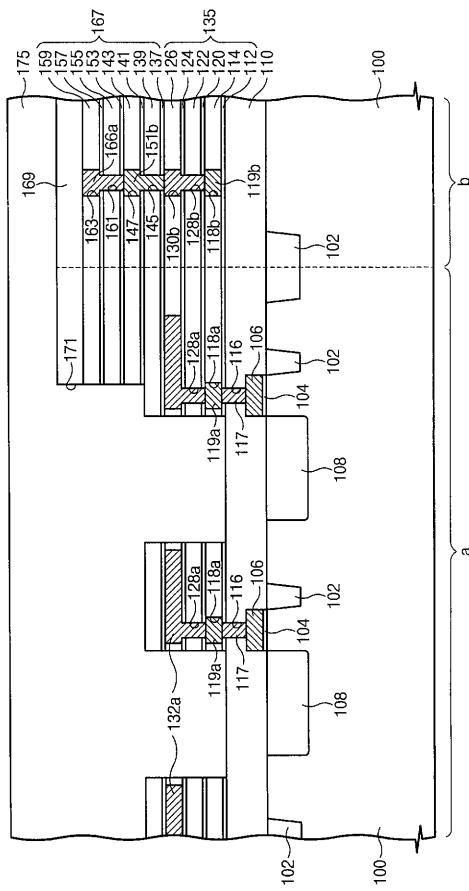

#### (第3の実施形態)

本実施形態では、イメージセンサーの光感度を向上させることと共に、隣接するフォト

10

20

30

40

50

ダイオード間の混信を防止できるイメージセンサーの形成方法を開示する。本実施形態でも、前述した第1の実施形態と同一な構成要素は、同一な参照符号を示すものとする。本実施形態は、前述した第1の実施形態の図3を参照して説明した形成方法を含むことができる。

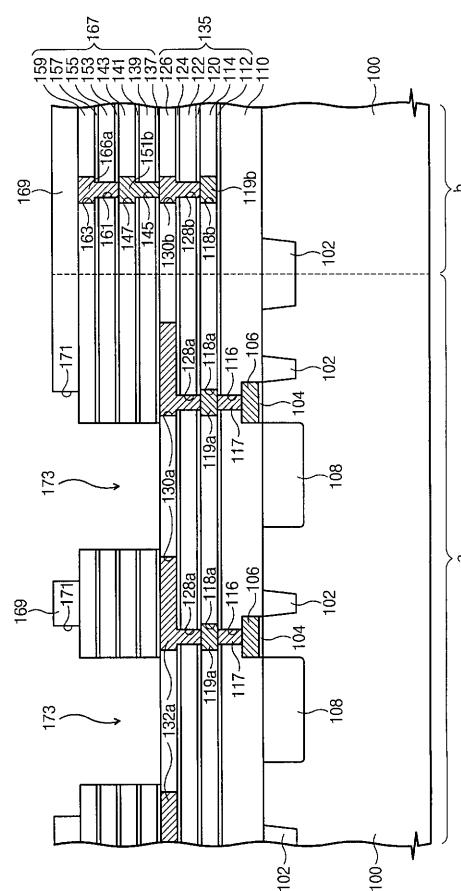

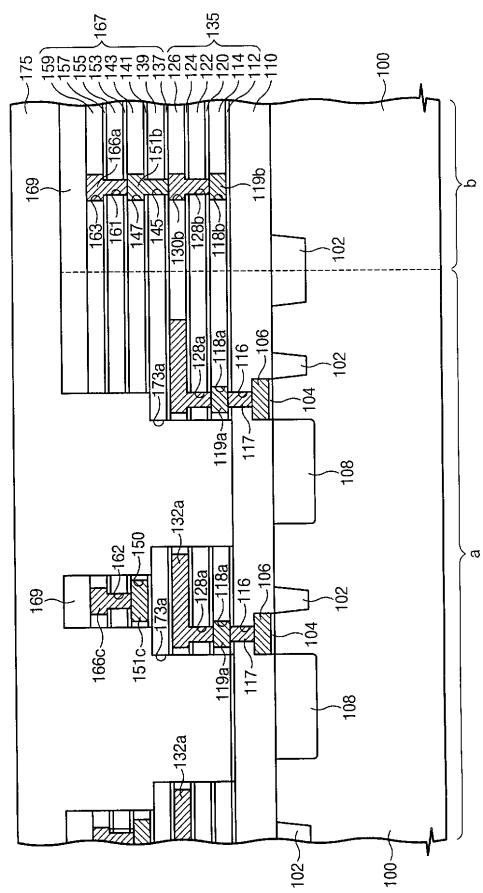

【0081】

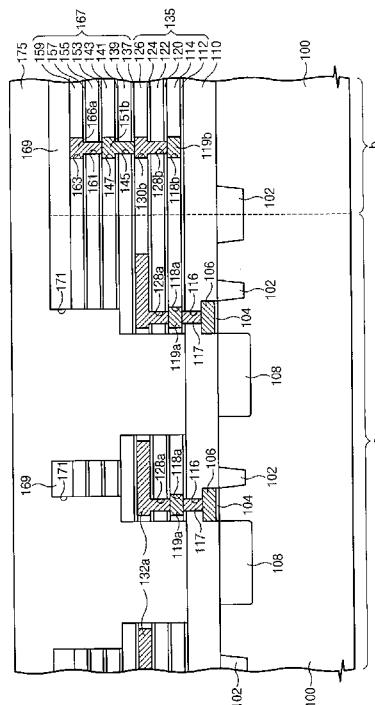

図14～図17は、本発明のさらに他の実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【0082】

図3及び図14を参考すれば、下部モールド絶縁層135及び第2の画素及び周辺金属配線119a、119bを有する半導体基板100上に第3の配線モールド層を形成する。第3の配線モールド層は、順次に積層された第4のバリヤ絶縁膜137と、第4の層間絶縁膜139と、第5のバリヤ絶縁膜141及び第5の層間絶縁膜143と、を含む。

10

【0083】

第3の配線モールド層内に第3の周辺ホール145と、第3の周辺ホール145と連通する第3の周辺グループ147と、第1のダミー開口部149及び第1の混信防止グループ150と、を形成する。第1の混信防止グループ150は、第3の周辺グループ147と同時に形成されることが好ましい。すなわち、第1の混信防止グループ150は、第5の層間絶縁膜143内に形成されることが好ましい。第1の混信防止グループ150は、第5のバリヤ絶縁膜141を露出させて、その底面は下部モールド絶縁層135と離隔されている。

20

【0084】

第1のダミー開口部149、第1の混信防止グループ150、第3の周辺ホール145及び第3のグループ147を充填する第3の金属膜を半導体基板100の全面上に形成する。第3の金属膜は、前述した第1の実施形態と同一な物質を含むことができる。第3の金属膜を第3の配線モールド層（すなわち、第5の層間絶縁膜143）が露出されるときまで平坦化させて第1のダミー開口部149を充填する第1の充填パターン151a、第3の周辺ホール145及び第3の周辺グループ147を充填する第3の周辺金属配線151b及び第1の混信防止グループ150を充填する第1の混信防止パターン151cを形成する。第1の混信防止パターン151cは、下部モールド絶縁層135上に離隔される。

30

【0085】

図15を参照すれば、半導体基板100の全面上に順次に積層された第6のバリヤ絶縁膜153と、第6の層間絶縁膜155と、第7のバリヤ絶縁膜157及び第7の層間絶縁膜159と、を含む第4の配線モールド層を形成する。

【0086】

第4の配線モールド層内に第2のダミー開口部165と、第4の周辺ホール161と、第4の周辺グループ163と、コンタクトグループ162及び第2の混信防止グループ164と、を形成する。コンタクトグループ162は、第4の周辺ホール161と同時に形成され、第2の混信防止グループ164は、第4の周辺グループ163と同時に形成されることが好ましい。すなわち、コンタクトグループ162は、第7のバリヤ絶縁膜157と、第6の層間絶縁膜155及び第6のバリヤ絶縁膜153と、を連続的に貫通して第1の混信防止パターン151cを露出させ、第3の混信防止グループ164は、第7の層間絶縁膜159内に形成され、コンタクトグループ162と連通する。コンタクト及び第2の混信防止グループ162、164は、全てn型不純物拡散層108の間を経る。

40

【0087】

第2のダミー開口部165と、コンタクトグループ162と、第2の混信防止グループ164と、第4の周辺ホール161及び第4の周辺グループ163と、を充填する第4の金属膜を形成する。第4の金属膜は、前述した第1の実施形態と同一な物質を含むことができる。第4の金属膜を第4の配線モールド層が露出されるときまで平坦化させて第4の周辺ホール161及び第4の周辺グループ163を充填する第4の周辺金属配線166a

50

、第2のダミー開口部165を充填する第2の充填パターン166b及びコンタクトグループ162と第2の混信防止グループ164を充填する第2の混信防止パターン166cを形成する。

#### 【0088】

第1及び第2の混信防止パターン151c、166cは、混信防止バリヤを構成する。混信防止バリヤは、上部モールド絶縁層167に形成される充填パターン151a、166bの数と同一な数に積層された混信防止パターン151c、166cを含む。この際、最下位層の混信防止パターン151cは下部モールド絶縁層135と離隔されが好ましい。

#### 【0089】

混信防止バリヤ及びダミーパターンを有する半導体基板100の全面上にマスク層169を形成し、マスク層169をパターニングしてダミーパターンを露出させる開口部171を形成する。この際、n型不純物拡散層108の間に設けられるパターニングされたマスク層169は、混信防止バリヤを覆う。勿論、開口部171は、ダミーパターンの幅に比べて広幅を有する。すなわち、n型不純物拡散層108の間に設けられたパターニングされたマスク層169の幅はn型不純物拡散層108の間に設けられた上部モールド絶縁層167の幅に比べて狭いことが好ましい。

#### 【0090】

図16及び図17を参照すれば、露出されたダミーパターンを選択的に除去して下部モールド絶縁層135を露出させる予備空洞領域173を形成する。ダミーパターンは、湿式エッチングで除去することが好ましい。パターニングされたマスク層169をエッチングマスクとして使用して露出された下部モールド絶縁層135を異方性エッチングしてn型不純物拡散層108上の保護絶縁膜110を露出させる空洞領域173aを形成する。この際、開口部171に露出されたn型不純物拡散層108の間に設けられた上部モールド絶縁層167の周縁もエッチングされる。勿論、異方性エッチング時、上部モールド絶縁層167の下部を残存させが好ましい。上部モールド絶縁層167の残存する部分は、前述した第1の実施形態と同一な機能及び物質を含むことができる。

#### 【0091】

次いで、空洞領域173aを充填する図18の透明絶縁膜175を形成する。

#### 【0092】

前述したイメージセンサーの形成方法によれば、空洞領域173aは、ダミーパターンを選択的に除去した後に、異方性エッチングを遂行して形成される。これにより、空洞領域173aの側壁を殆ど垂直に形成できる。これで、フォトダイオードのオープン領域を最大な確保でき、整列マージンを向上させうる。また、異方性エッチング時、n型不純物拡散層108の間に設けられた上部モールド絶縁層167の周縁も共にエッチングすることによって、空洞領域173aの下部の幅を維持したまま空洞領域173aの上部の幅を拡大させうる。その結果、外部光の入射量を増加させてイメージセンサーの光感度を向上させうる。これに加えて、n型不純物拡散層108の間に設けられた上部モールド絶縁層167内に混信防止バリヤが形成される。これにより、画素間に入射される光の干渉を防止して画素の信号歪曲を最小化できる。

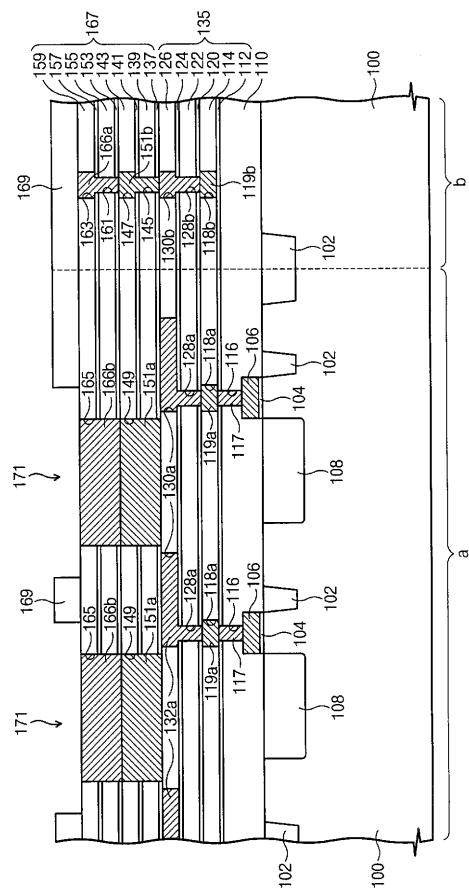

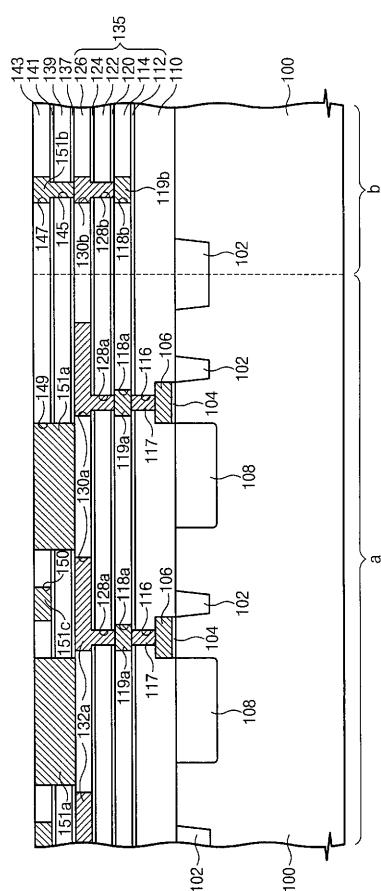

#### 【0093】

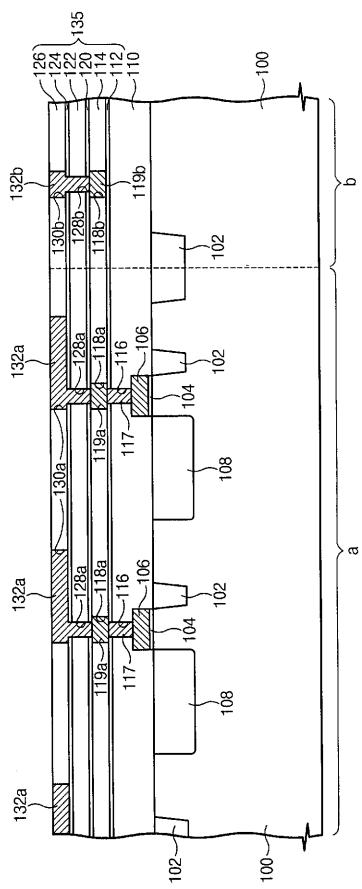

次に、本発明の実施形態によるイメージセンサーを図18を参照して説明する。

#### 【0094】

図18は、本発明の実施形態によるイメージセンサーを示す断面図である。

#### 【0095】

図18を参照すれば、画素領域(a)及び周辺領域(b)を有する半導体基板100に素子分離膜102が配置されて画素領域(a)に複数の画素活性領域を画定し、周辺領域(b)に周辺活性領域を画定する。少なくとも画素領域(a)の半導体基板100は、第1の導電型の不純物でドーピングされる。

#### 【0096】

10

20

30

40

50

画素活性領域上にゲート絶縁膜 104 及びゲート電極 106 が順次に積層される。ゲート電極 106 の一側の画素活性領域に第 2 の導電型の不純物でドーピングされた不純物拡散層 108 が配置される。不純物拡散層 108 は、半導体基板 100 と p-n 接合されてフォトダイオードを形成する。

## 【0097】

保護絶縁膜 110 が半導体基板 100 の全面を覆う。保護絶縁膜 110 上に下部モールド絶縁層 135 及び上部モールド絶縁層 167 が順次に積層される。空洞領域 173a が上部及び下部モールド絶縁層 167、135 を連続的に貫通する。上部モールド絶縁層 167 に形成された空洞領域 173a の幅は、下部モールド絶縁層 135 に形成された空洞領域 173a の幅に比べて狭いことが好ましい。

10

## 【0098】

n 型不純物拡散層 108 の間に設けられた下部モールド絶縁層 135 内に少なくとも 1 層の画素金属配線 119a、132a が配置される。画素金属配線 119a、132a は、それぞれ配線鉄型層内に形成される。図面では、第 1 の画素金属配線 119a 及び第 2 の画素金属配線 132a が示されている。第 1 及び第 2 の画素金属配線 119a、132a は、それぞれ第 1 及び第 2 の配線モールド層内に配置される。第 1 配線モールド層は、順次に積層された第 1 のバリヤ絶縁膜 112 及び第 1 の層間絶縁膜 114 を含み、第 2 の配線モールド層は、第 2 のバリヤ絶縁膜 120 と、第 2 の層間絶縁膜 122 と、第 3 のバリヤ絶縁膜 124 及び第 3 の層間絶縁膜 126 と、を含む。周辺領域 (b) の第 1 の配線モールド層内には、第 1 の周辺金属配線 119b が配置され、周辺領域 (b) の第 2 の配線モールド層内には、第 2 の周辺金属配線 132b が配置される。

20

## 【0099】

下部モールド絶縁層 135、画素金属配線 119a、132a 及び周辺金属配線 119b、132b は、図 3 を参照して説明した形態で形成できる。

## 【0100】

n 型不純物拡散層 108 の間に介在された上部モールド絶縁層 167 内に混信防止バリヤが形成される。混信防止バリヤは、少なくとも 1 層の混信防止パターン 151c、166c を含む。混信防止バリヤは、下部モールド絶縁層 135 から上に離隔されることが好ましい。

30

## 【0101】

混信防止バリヤ上には、パターニングされたマスク層 169 が配置される。マスク層 169 は、上部及び下部モールド絶縁層 167、135 についてエッチング選択比を有する物質であるか、或いは上部及び下部モールド絶縁層 167、135 についてエッチングマスクとして使用できる十分な厚さに形成されることが好ましい。パターニングされたマスク層 169 は、混信防止バリヤの最上部面と接触できる。

40

## 【0102】

画素金属配線 119a、132a のうち、最上層、例えば第 2 の画素金属配線 132a は、上部モールド絶縁層 167 と接触することが好ましい。この際、上部モールド絶縁層 167 の底面は、第 2 の画素金属配線 132a 内金属元素の拡散を防止できるバリヤ絶縁膜 137 からなる。

## 【0103】

周辺領域 (b) の上部モールド絶縁層 167 内には、少なくとも 1 層の周辺画素金属配線 151b、166a が配置される。上部モールド絶縁層 167 内の画素金属配線 151b、166a は、混信防止バリヤと同一な物質を含む。

## 【0104】

透明絶縁膜 175 は、空洞領域 173a を充填する。示さないが、透明絶縁膜 175 にカラーフィルター (図示せず) を配置でき、カラーフィルター上に半球形態の光集束部 (図示せず) を配置できる。

## 【0105】

前述した構造のイメージセンサーによれば、空洞領域 173a の下部の幅が n 型不純物

50

拡散層 108 に画定されることと共に、空洞領域 173a の上部の幅は空洞領域 173a の下部に比べて広い。これにより、空洞領域 173a に入射される外部光の入射量が増加されてイメージセンサーの光感度が向上する。また、混信防止バリヤによって隣接した画素間に外部光の混合を最小化して画素の信号歪曲を最小化できる。

【図面の簡単な説明】

【0106】

【図 1】イメージセンサーの従来形成方法を説明するための断面図である。

【図 2】イメージセンサーの従来形成方法を説明するための断面図である。

【図 3】本発明の一実施形態によるイメージセンサーの形成方法を説明するための断面図である。10

【図 4】本発明の一実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 5】本発明の一実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 6】本発明の一実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 7】本発明の一実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 8】本発明の一実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 9】本発明の一実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 10】本発明の他の実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 11】本発明の他の実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 12】本発明の他の実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 13】本発明の他の実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 14】本発明のさらに他の実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 15】本発明のさらに他の実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 16】本発明のさらに他の実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 17】本発明のさらに他の実施形態によるイメージセンサーの形成方法を説明するための断面図である。

【図 18】本発明の一実施形態によるイメージセンサーを示す断面図である。

【符号の説明】

【0107】

100：半導体基板

108：n型不純物拡散層

135：下部モールド絶縁層

167：上部モールド絶縁層

173：予備空洞領域

173a：空洞領域

175：透明絶縁膜

10

20

30

40

【 図 1 】

【 図 2 】

【図3】

【図4】

【 図 5 】

【 四 7 】

【 四 6 】

〔 四 8 〕

【図9】

【 図 1 3 】

【図14】

【 図 1 5 】

【図16】

【 図 17 】

【 図 1 8 】

---

フロントページの続き

(72)発明者 洪 鍾郁

大韓民国ソウル瑞草区良才洞15 - 10番地 301号

(72)発明者 李 準澤

大韓民国京畿道水原市靈通区靈通洞(番地なし) ファンゴルマウルポーングリムアパート105

3 - 2 ポーングリムアパート235 - 1505

F ターム(参考) 4M118 AA01 AA05 CA02 CA03 CA32 CA34 FA33 GB03 GB11 GB15