(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-144151

(P2016-144151A)

(43) 公開日 平成28年8月8日(2016.8.8)

(51) Int.Cl.

F 1

テーマコード(参考)

**HO4N 5/3745 (2011.01)**

HO 4 N 5/335

7 4 5

**HO4N 5/374 (2011.01)**

HO 4 N 5/335

7 4 0

**HO4N 5/345 (2011.01)**

HO 4 N 5/335

4 5 0

審査請求 未請求 請求項の数 12 O L (全 13 頁)

(21) 出願番号

特願2015-20612(P2015-20612)

(22) 出願日

平成27年2月4日(2015.2.4)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 固体撮像装置の駆動方法、固体撮像装置およびカメラ

## (57) 【要約】

【課題】 固体撮像装置の全画素のうちの一部の画素の信号を利用する場合における電力消費の低減に有利な技術を提供する。

【解決手段】 固体撮像装置は、入射光に基づくアナログ信号を各々が生成する複数の画素が2次元状に配列された画素アレイと、前記画素アレイから出力されるアナログ信号をA/D変換してデジタル信号を生成するA/D変換部と、複数のメモリと、出力線とを有する。前記複数のメモリが前記出力線に順次にデジタル信号を出力する1つの水平転送期間は、前記複数のメモリの一部のメモリから、前記A/D変換部によってA/D変換されたデジタル信号ではない所定値を有するデジタル信号が前記出力線に出力される第1期間と、前記複数のメモリの他の一部のメモリから、前記A/D変換部によってA/D変換されたデジタル信号が前記出力線に出力される第2期間と、を含む。前記第1期間では、前記一部のメモリのうち少なくとも2つのメモリから、前記所定値を有するデジタル信号が連続して前記出力線に出力される。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

入射光に基づくアナログ信号を各々が生成する複数の画素が2次元状に配列された画素アレイと、前記画素アレイから出力されるアナログ信号をA/D変換してデジタル信号を生成するA/D変換部と、複数のメモリと、出力線とを有する固体撮像装置の駆動方法であって、

前記複数のメモリが前記出力線に順次にデジタル信号を出力する1つの水平転送期間が、

前記複数のメモリの一部のメモリから、前記A/D変換部によってA/D変換されたデジタル信号ではない所定値を有するデジタル信号が前記出力線に出力される第1期間と、

前記複数のメモリの他の一部のメモリから、前記A/D変換部によってA/D変換されたデジタル信号が前記出力線に出力される第2期間と、を含み、

前記第1期間では、前記一部のメモリのうち少なくとも2つのメモリから、前記所定値を有するデジタル信号が連続して前記出力線に出力される、

ことを特徴とする固体撮像装置の駆動方法。

**【請求項 2】**

前記A/D変換部は、時間経過とともに変化する参照信号の値と前記画素アレイから出力される複数のアナログ信号の値とをそれぞれ比較する複数の比較器と、前記時間経過に応じたカウント値を生成するカウンタと、を含む、

ことを特徴とする請求項1に記載の固体撮像装置の駆動方法。

**【請求項 3】**

前記一部のメモリは、前記複数の比較器のうちパワーセーブモードに設定された比較器に対応するメモリである、

ことを特徴とする請求項2に記載の固体撮像装置の駆動方法。

**【請求項 4】**

前記固体撮像装置は、前記複数の比較器の一部からの出力または前記複数の比較器の一部への信号の入力を遮断する遮断部を更に有し、

前記一部のメモリは、前記遮断部による遮断がなされた比較器に対応するメモリである、

ことを特徴とする請求項2に記載の固体撮像装置の駆動方法。

**【請求項 5】**

前記A/D変換部は、複数のA/D変換器を含み、

前記一部のメモリは、前記複数のA/D変換器のうちパワーセーブモードに設定されたA/D変換器に対応するメモリである、

ことを特徴とする請求項1に記載の固体撮像装置の駆動方法。

**【請求項 6】**

前記A/D変換部は、複数のA/D変換器を含み、前記固体撮像装置は、前記複数のA/D変換器の一部への信号の入力または前記複数のA/D変換器の一部からの出力を遮断する遮断部を更に有し、

前記一部のメモリは、前記遮断部による遮断がなされたA/D変換器に対応するメモリである、

ことを特徴とする請求項1に記載の固体撮像装置の駆動方法。

**【請求項 7】**

前記A/D変換部がA/D変換を行う前に前記複数のメモリの全てのメモリに対して前記所定値を有するデジタル信号が書き込まれ、

前記A/D変換部は、前記画素アレイから出力される複数のアナログ信号の一部をA/D変換し、これによって生成されたデジタル信号が前記複数のメモリの前記他的一部のメモリに対して書き込まれる、

ことを特徴とする請求項1に記載の固体撮像装置の駆動方法。

**【請求項 8】**

10

20

30

40

50

前記 A D 変換部によって生成された複数のデジタル信号が前記複数のメモリの前記他の一部のメモリに対して書き込まれた後に、前記複数のメモリの前記一部のメモリに対して前記所定値を有するデジタル信号が書き込まれる、

ことを特徴とする請求項 1 に記載の固体撮像装置の駆動方法。

**【請求項 9】**

前記 A D 変換部が A D 変換を行う前に前記複数のメモリの全てのメモリに対して前記所定値を有するデジタル信号が書き込まれる、

ことを特徴とする請求項 8 に記載の固体撮像装置の駆動方法。

**【請求項 10】**

前記複数のメモリに保持された複数のデジタル信号が前記出力線を含む複数の出力線に分配して出力される、

10

ことを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の固体撮像装置の駆動方法。

**【請求項 11】**

入射光に基づくアナログ信号を各々が生成する複数の画素が 2 次元状に配列された画素アレイと、

前記画素アレイから出力されるアナログ信号を A D 変換してデジタル信号を生成する A D 変換部と、

複数のメモリと、

出力線と、

前記複数のメモリにデジタル信号を書き込む書き込み部と、

20

前記書き込み部は、前記複数のメモリが前記出力線に順次にデジタル信号を出力する 1 つの水平転送期間が、前記複数のメモリの一部のメモリから、前記 A D 変換部によって A D 変換されたデジタル信号ではない所定値を有するデジタル信号が前記出力線に出力される第 1 期間と、前記複数のメモリの他の一部のメモリから、前記 A D 変換部によって A D 変換されたデジタル信号が前記出力線に出力される第 2 期間と、を含むように前記複数のメモリに対する書き込みを行い、

前記第 1 期間では、前記一部のメモリのうち少なくとも 2 つのメモリから、前記所定値を有するデジタル信号が連続して前記出力線に出力される、

ことを特徴とする固体撮像装置。

**【請求項 12】**

30

請求項 1 1 に記載の固体撮像装置と、

前記固体撮像装置から出力される信号を処理する処理部と、

を備えることを特徴とするカメラ。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は、固体撮像装置の駆動方法、固体撮像装置およびカメラに関する。

**【背景技術】**

**【0 0 0 2】**

特許文献 1 には、画素アレイの複数の列にそれぞれ対応する複数の A D 変換器を備える固体撮像装置が記載されている。該固体撮像装置は、該複数の A D 変換器によって変換された複数のデジタル信号を複数のデジタルメモリによって保持し、該複数のデジタルメモリによって保持されたデジタル信号は、ブロックデジタル出力線および共通デジタル出力線を介して出力される。

40

**【先行技術文献】**

**【特許文献】**

**【0 0 0 3】**

**【特許文献 1】特開 2012 - 90313 号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

50

## 【0004】

固体撮像装置と該固体撮像装置から出力された信号を処理する処理部とを有するシステムにおいて、該処理部が該固体撮像装置の全画素のうち必要な一部の画素の信号のみを利用する動作モードがありうる。このような動作モードにおいて、該固体撮像装置から全画素の信号を出力すると、該固体撮像装置の内部および外部における信号の伝達経路の充放電による電力消費が大きい。例えば、特許文献1に記載された固体撮像装置が組み込まれたシステムにおいて、全画素のうち必要な一部の画素のみを利用する場合を考えてみる。この場合、全画素の信号を該固体撮像装置から出力すると、該固体撮像装置内のロックデジタル出力線および共通デジタル出力線、更には該固体撮像装置の出力ピンの駆動によって消費される電力が大きい。

10

## 【0005】

本発明は、上記の課題認識を契機としてなされたものであり、固体撮像装置の全画素のうちの一部の画素の信号を利用する場合における電力消費の低減に有利な技術を提供することを目的とする。

## 【課題を解決するための手段】

## 【0006】

本発明の1つの側面は、入射光に基づくアナログ信号を各々が生成する複数の画素が2次元状に配列された画素アレイと、前記画素アレイから出力されるアナログ信号をA/D変換してデジタル信号を生成するA/D変換部と、複数のメモリと、出力線とを有する固体撮像装置の駆動方法であって、前記複数のメモリが前記出力線に順次にデジタル信号を出力する1つの水平転送期間が、前記複数のメモリの一部のメモリから、前記A/D変換部によってA/D変換されたデジタル信号ではない所定値を有するデジタル信号が前記出力線に出力される第1期間と、前記複数のメモリの他の一部のメモリから、前記A/D変換部によってA/D変換されたデジタル信号が前記出力線に出力される第2期間と、を含み、前記第1期間では、前記一部のメモリのうち少なくとも2つのメモリから、前記所定値を有するデジタル信号が連続して前記出力線に出力される。

20

## 【発明の効果】

## 【0007】

本発明によれば、固体撮像装置の全画素のうちの一部の画素の信号を利用する場合における電力消費の低減に有利な技術が提供される。

30

## 【図面の簡単な説明】

## 【0008】

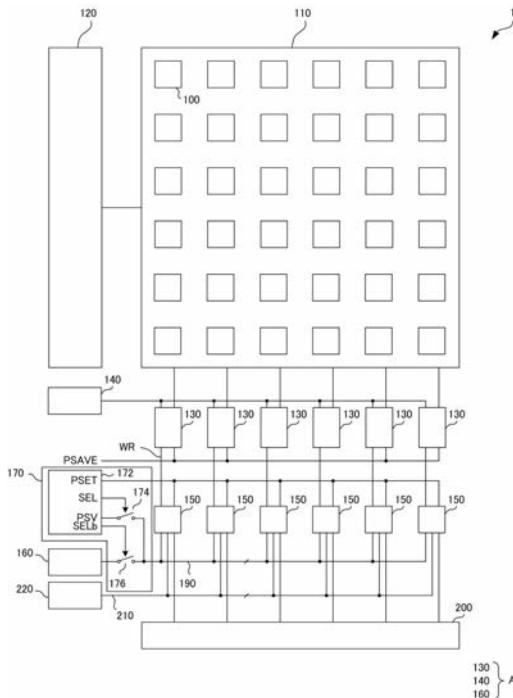

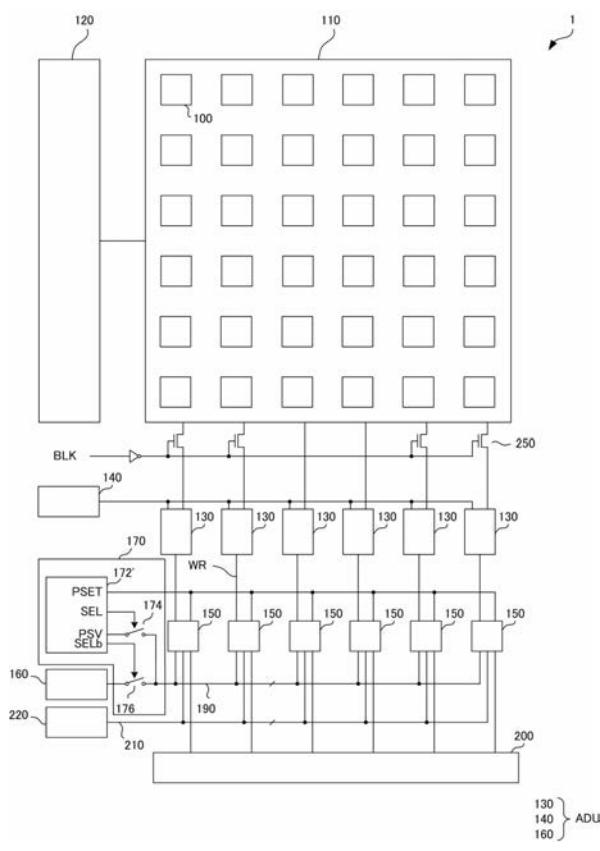

【図1】第1実施形態の固体撮像装置の構成を示す図。

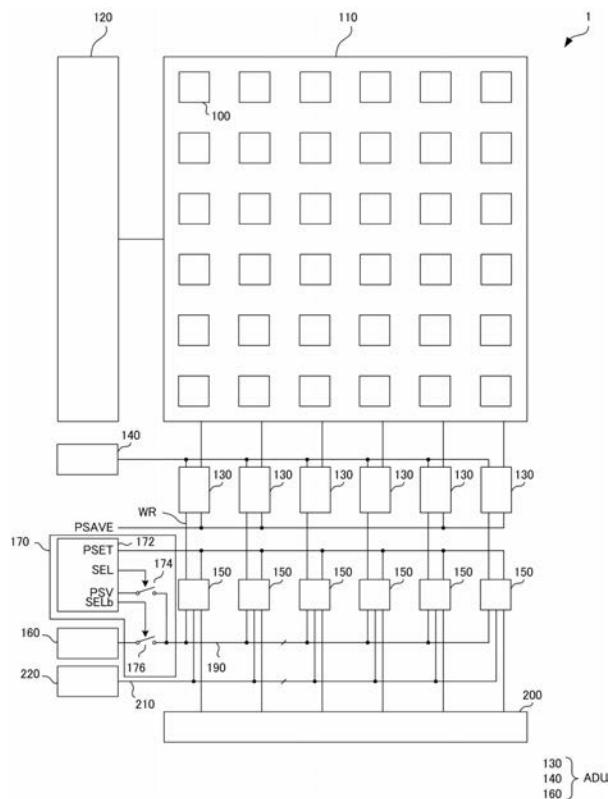

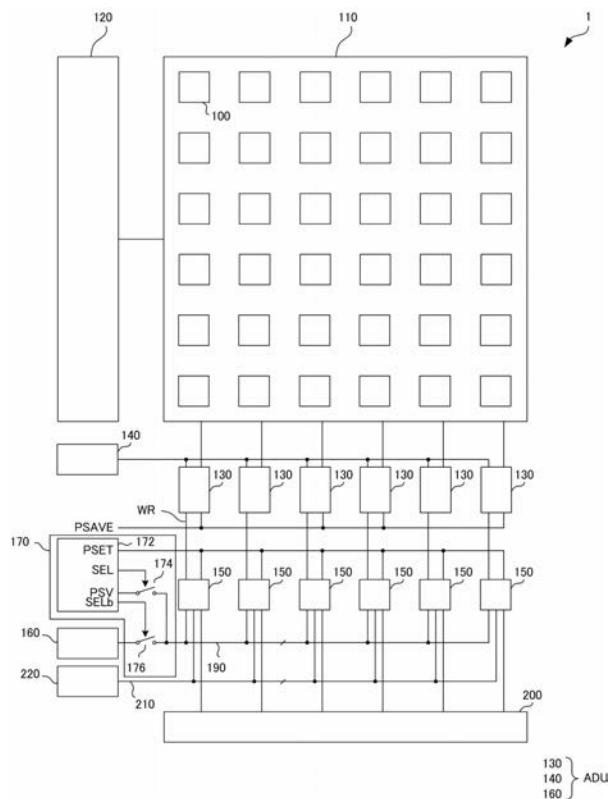

【図2】第1実施形態の動作を示す図。

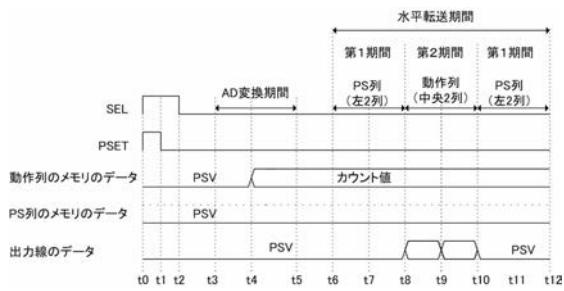

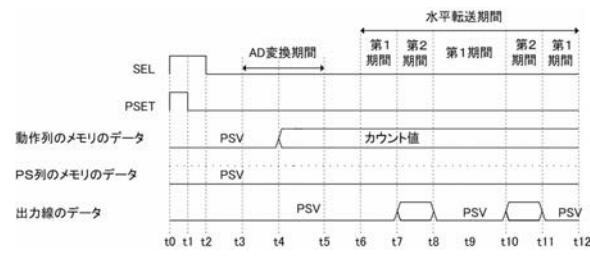

【図3】第1実施形態の第1変形例を示す図。

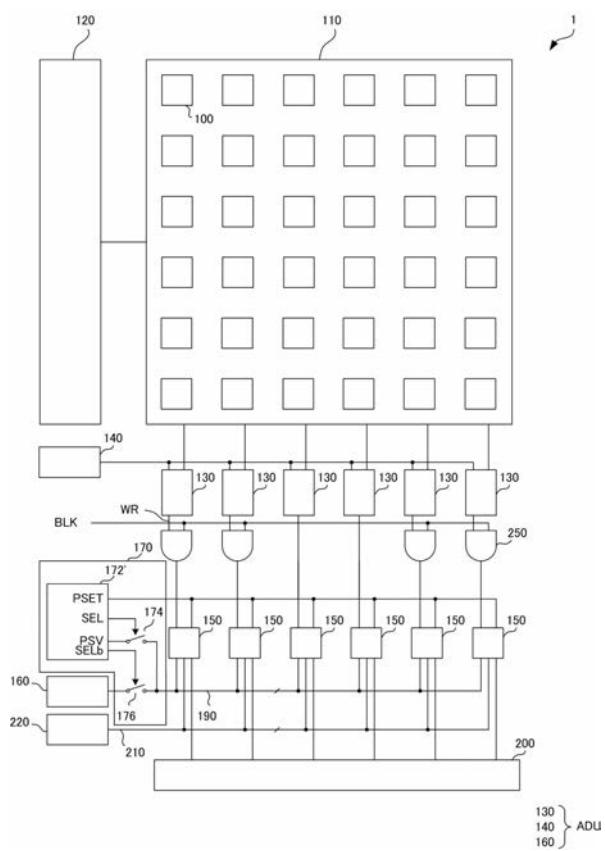

【図4】第1実施形態の第2変形例を示す図。

【図5】第2実施形態の固体撮像装置の構成を示す図。

【図6】第2実施形態の動作を示す図。

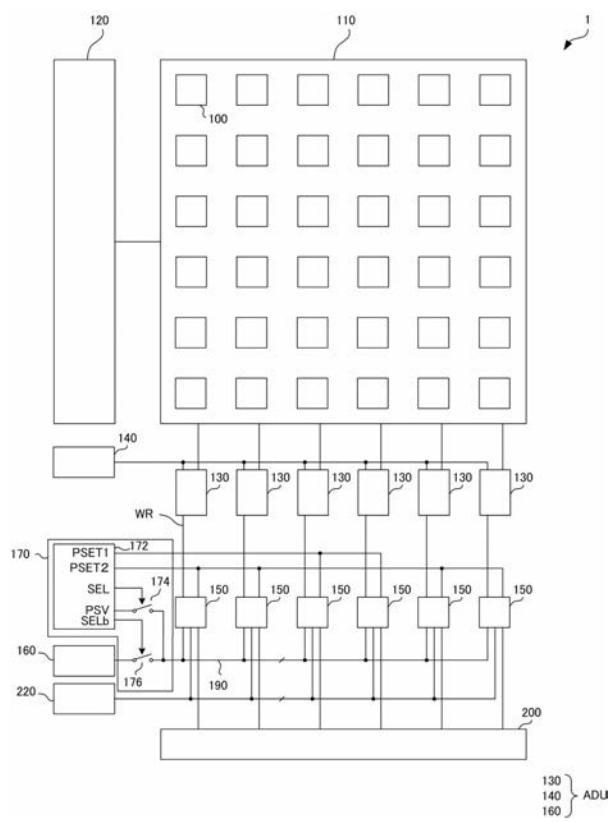

【図7】第3実施形態の固体撮像装置の構成を示す図。

【図8】第3実施形態の動作を示す図。

【図9】第4実施形態の固体撮像装置の構成を示す図。

【図10】1つの実施形態のカメラの構成を示す図。

40

## 【発明を実施するための形態】

## 【0009】

以下、添付図面を参照しながら本発明をその例示的な実施形態を通して説明する。

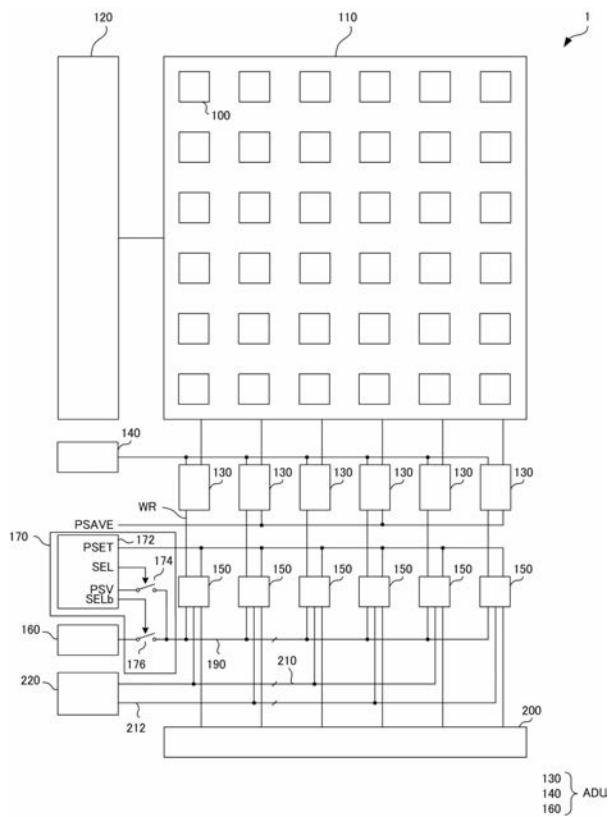

## 【0010】

まず、図1を参照しながら本発明の第1実施形態の固体撮像装置1について説明する。固体撮像装置1は、例えば、画素アレイ110、垂直選択部120、複数の比較器130、参照信号発生部140、複数のメモリ150、カウンタ160、水平選択部(選択部)200、水平出力線(出力線)210、出力部220、書き込み部170を備えうる。他

50

の観点において、固体撮像装置 1 は、A D 変換部 A D U を備え、A D 変換部 A D U は、例えば、複数の比較器 1 3 0 と、参照信号発生部 1 4 0 と、カウンタ 1 6 0 とを含みうる。画素アレイ 1 1 0 は、複数の行および複数の列を構成するように 2 次元状に配列された複数の画素 1 0 0 を有する。各画素 1 0 0 は、入射光に基づくアナログ信号を生成する。各画素 1 0 0 のアナログ信号は、列信号線を介して出力される。1 つの列信号線には、1 つの列を構成する画素 1 0 0 が接続されうる。

#### 【 0 0 1 1 】

第 1 実施形態では、画素アレイ 1 1 0 の全ての画素 1 0 0 のデジタル信号を固体撮像装置 1 から出力する動作モードにおいては、A D 変換部 A D U は、画素アレイ 1 1 0 から出力される複数のアナログ信号の全てを A D 変換してデジタル信号を生成する。一方、画素アレイ 1 1 0 の全ての画素 1 0 0 のうちの一部の画素 1 0 0 のデジタル信号を固体撮像装置 1 から出力する動作モードにおいては、A D 変換部 A D U は、画素アレイ 1 1 0 から出力される複数のアナログ信号の一部を A D 変換してデジタル信号を生成する。

10

#### 【 0 0 1 2 】

A D 変換部 A D U において、参照信号発生部 1 4 0 は、時間経過にともなって変化する参照信号（例えば、ランプ信号）を生成する。各比較器 1 3 0 は、参照信号発生部 1 4 0 が生成する参照信号の値と画素アレイ 1 1 0 （画素 1 0 0 ）から出力されるアナログ信号の値とを比較し、例えば、両者の大小関係が反転したときに、書き込み制御信号 W R （例えば、パルス信号）を出力する。カウンタ 1 6 0 は、時間経過に応じたカウント値を発生してデータ線 1 9 0 に出力する。比較器 1 3 0 が出力する書き込み制御信号 W R は、カウンタ 1 6 0 が生成したカウント値をメモリ 1 5 0 に対して書き込むべきタイミングを示す信号である。

20

#### 【 0 0 1 3 】

他の実施形式において、1 つの比較器 1 3 0 に対して 1 つのカウンタ 1 6 0 が設けられてもよい。比較器 1 3 0 は、画素アレイ 1 1 0 の列（画素 1 0 0 によって構成される列）ごとに設けられる。A D 変換部 A D U は、画素アレイ 1 1 0 の複数の列にそれぞれ対応する複数の A D 変換器の集合として理解することもできる。図 1 に示された例では、1 つの A D 変換器が 1 つの比較器 1 3 0 を含み、参照信号発生部 1 4 0 およびカウンタ 1 6 0 が複数の A D 変換器によって共有される。複数のメモリ 1 5 0 は、A D 変換部 A D U によって生成されたデジタル信号を保持する。

30

#### 【 0 0 1 4 】

水平選択部（選択部）2 0 0 は、複数のメモリ 1 5 0 を順次に選択することによって複数のメモリ 1 5 0 に保持された複数のデジタル信号を順次に水平出力線 2 1 0 に出力する。

#### 【 0 0 1 5 】

書き込み部 1 7 0 は、複数のメモリ 1 5 0 の一部のメモリ 1 5 0 から水平出力線 2 1 0 に対して所定値を有するデジタル信号が出力されるように、複数のメモリ 1 5 0 の当該一部のメモリ 1 5 0 に対して所定値を有するデジタル信号 P S V を書き込む。ここで、書き込み部 1 7 0 は、前記一部のメモリ 1 5 0 の少なくとも 2 つのメモリ 1 5 0 から所定値を有するデジタル信号 P S V が連続して出力線 2 1 0 に出力されるように当該一部のメモリ 1 5 0 に対して所定値を有するデジタル信号 P S V を書き込む。所定値は、例えば、全ビットが “ 0 ” または “ 1 ” の一定の値、または、 “ 0 ” と “ 1 ” との組み合わせからなる一定の値である。書き込み部 1 7 0 は、メモリ 1 5 0 から信号が水平出力線 2 1 0 に出力される前に当該メモリ 1 5 0 に対してデジタル信号 P S V を書き込む。換言すると、書き込み部 1 7 0 によってデジタル信号 P S V が書き込まれたメモリ 1 5 0 からデジタル信号 P S V が水平出力線 2 1 0 に出力されるように、書き込み部 1 7 0 によるデジタル信号 P S V の書き込みが制御される。

40

#### 【 0 0 1 6 】

書き込み部 1 7 0 は、例えば、書き込み制御部 1 7 2 、スイッチ 1 7 4 、 1 7 6 を含む。書き込み制御部 1 7 2 は、書き込み制御信号 P S E T 、選択信号 S E L 、 S E L b およ

びデジタル信号 P S V を出力する。ここで、選択信号 S E L 、 S E L b は、互いに論理が反対の信号である。つまり、選択信号 S E L がハイレベルであるときは、選択信号 S E L b はローレベルであり、選択信号 S E L がローレベルであるときは、選択信号 S E L b はハイレベルである。この例では、選択信号 S E L がハイレベルであるときは、所定値を有するデジタル信号 P S V がデータ線 1 9 0 を介してメモリ 1 5 0 に供給され、選択信号がローレベルであるときは、カウンタ 1 6 0 のカウント値がデータ線 1 9 0 を介してメモリ 1 5 0 に供給される。選択信号 S E L がハイレベルである状態で書き込み制御信号 P S E T がアクティブルレベル（ハイレベル）になると、所定値を有するデジタル信号 P S V がデータ線 1 9 0 を介してメモリ 1 5 0 に書き込まれる。選択信号 S E L がローレベルである状態で、比較器 1 3 0 から書き込み制御信号 W R が出力されると、それに応じて、カウンタ 1 6 0 のカウント値が、A D 変換されたデジタル信号として、データ線 1 9 0 を介してメモリ 1 5 0 に書き込まれる。

10

## 【0017】

画素アレイ 1 1 0 と A D 変換部 A D U との間には、読出部（不図示）が設けられてもよい。該読出部は、例えば、画素アレイ 1 1 0 から出力される信号を増幅する複数のアンプを含みうる。該アンプは、例えば、画素アレイ 1 1 0 の列ごとに設けられうる。

## 【0018】

図 1 に例示された固体撮像装置 1 では、複数の比較器 1 3 0 （ A D 変換器）の一部、具体的には、第 1 列、第 2 列、第 5 列、第 6 列がパワーセーブモードを有し、パワーセーブ信号 P S A V E がアクティブルレベルになると、パワーセーブモードに設定になる。なお、これは説明の簡単化のための例であり、この例は、画素アレイ 1 1 0 の中央部の画素 1 0 0 の信号を読み出す際に、該中央部を含む列以外の列のための比較器 1 3 0 をパワーセーブモードに設定することによって電力消費を低減する動作モードに適用されうる。複数の比較器 1 3 0 は、それらの全てがパワーセーブモードを有し、パワーセーブモードに設定するかどうかが個々に制御されてもよい。

20

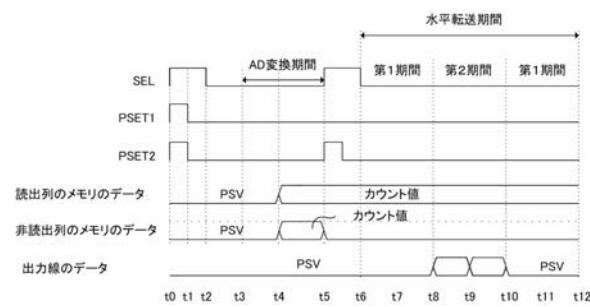

## 【0019】

以下では、図 2 を参照しながら第 1 列、第 2 列、第 5 列、第 6 列の比較器 1 3 0 がパワーセーブモードに設定された場合、即ち、パワーセーブ信号 P S A V E がアクティブルレベルに設定されている場合の固体撮像装置 1 の駆動方法を説明する。図 2 において、「 P S 列」は、パワーセーブモードに設定された列（パワーセーブ列）を意味し、「動作列」は、パワーセーブモードに設定されていない列を意味する。

30

## 【0020】

時刻 t 0 において、選択信号 S E L がハイレベル（選択信号 S E L b がローレベル）に駆動されることにより、データ線 1 9 0 に対して所定値を有するデジタル信号 P S V が出力される。この例では、所定値は、全ビットが “ 0 ” の値であるが、全ビットが “ 1 ” の値でもよいし、“ 0 ” と “ 1 ” との組み合わせからなる任意の値であってもよい。ただし、所定値は、一定の値に固定される。“ 0 ” と “ 1 ” との組み合わせからなる任意の値の場合には、水平出力線 2 1 0 が備える複数のバスの各々の信号レベルが一定となるような信号レベルとする。具体的には、あるビットを伝送するバスの信号値を “ 0 ” で一定とし、別のビットを伝送するバスの信号値を “ 1 ” で一定とする。時刻 t 0 において、選択信号 S E L がハイレベルになる他、書き込み制御信号 P S E T がアクティブルレベル（ここでは、ハイレベル）に駆動されることにより、書き込み部 1 7 0 は、デジタル信号 P S V を全てのメモリ 1 5 0 にデータ線 1 9 0 を介して書き込む。つまり、パワーセーブ列のメモリ 1 5 0 および動作列のメモリ 1 5 0 にデジタル信号 P S V が書き込まれる。

40

## 【0021】

時刻 t 3 から A D 変換期間が始まる。 A D 変換期間では、各比較器 1 3 0 （ A D 変換器）は、画素 1 0 0 からのアナログ信号の値と参照電圧発生部 1 4 0 から供給される参照信号の値とを比較し、比較結果に従って書き込み制御信号 W R をメモリ 1 5 0 に出力する。書き込み制御信号 W R を受けたメモリ 1 5 0 には、カウンタ 1 6 0 からデータ線 1 9 0 を介して供給されるカウント値が書き込まれる。図 2 の例では、時刻 t 4 で動作列のメモリ

50

150にカウント値が書き込まれているが、このタイミングは、画素100からのアナログ信号の値に応じて定まる。一方、パワーセーブモードに設定されている比較器130(AD変換器)からは書き込み制御信号WRが出力されないので、AD変換期間が終了する時刻t5になっても、メモリ150は、所定値を有するデジタル信号PSVを保持したままである。

#### 【0022】

時刻t6から1つの水平転送期間が始まる。水平転送期間では、水平選択部200が複数のメモリ150を順次に選択し、選択されたメモリ150から信号が出力線(水平出力線)210に出力され、その信号が出力部220から固体撮像装置1の外部に出力される。

10

#### 【0023】

水平転送期間は、第1期間と第2期間とを含む。第1期間は、複数のメモリ150の一部のメモリ150から、AD変換部ADUによってAD変換されたデジタル信号ではない所定値を有するデジタル信号PSVが出力線(水平出力線)210に出力される。第1期間では、前記一部のメモリ150のうち少なくとも2つのメモリから、所定値を有するデジタル信号PSVが連続して出力線210に出力される。第2期間では、複数のメモリ150の他の一部のメモリから、AD変換部ADUによってAD変換され当該他のメモリ150に書き込まれたデジタル信号が出力線210に出力される。

#### 【0024】

この例では、時刻t6～t8(第1期間の一部)において、第1列および第2列のメモリ150が順次に選択され、所定値を有する2つのデジタル信号PSVが連続して出力線210に出力される。その後、時刻t8～t10(第2期間)において、第3列および第4列のメモリ150が順次に選択され、画素100からのアナログ信号から変換されたデジタル信号が順次に出力線210に出力される。その後、時刻t10～t12(第1期間の他の一部)において、第5列および第6列のメモリ150が順次に選択され、所定値を有する2つのデジタル信号PSVが連続して出力線210に出力される。ここで、第1期間の一部(時刻t6～t8、t10～t12)において、所定値を有するデジタル信号PSVが出力線210、更には固体撮像装置1の外部に連続的に出力される。よって、信号の伝達経路の負荷の充放電に伴う電力消費を低減することができる。一方、全てのメモリ150に画素100の信号に応じたデジタル信号が書き込まれてそれが出力線210に出力される場合には、その分だけ電力が消費される。図1および図2に示された例では、所定値を有する2つのデジタル信号PSVが連続して出力線210に出力されるが、所定値を有する3以上のデジタル信号PSVが連続して出力線210に出力されてもよい。第1期間は、所定値を有する1つのみのデジタル信号PSVが出力される期間を含んでもよい。

20

#### 【0025】

以上の例は、複数の比較器130(AD変換器)の一部をパワーセーブモードに設定するものであるが、第1実施形態は、不要な信号がメモリ150に書き込まれない他の構成にも適用されうる。図3には、第1実施形態の第1変形例が示されている。第1変形例の固体撮像装置1では、画素アレイ110の全ての画素100のうちの一部の画素100の信号のみが外部の処理部で利用されるモードにおいて、信号が不要な列の比較器130(AD変換器)の出力は、遮断部250によって遮断される。遮断部250は、例えば、AND回路で構成されうる。遮断部250は、遮断信号BLKがアクティブに設定されたときに、比較器130(AD変換器)の出力、即ち書き込み制御信号WRがメモリ150に供給されないように、書き込み制御信号WRを遮断する。

30

#### 【0026】

図4には、第1実施形態の第2変形例が示されている。第2変形例の固体撮像装置1では、画素アレイ110(画素アレイ110の列信号線)と比較器130との経路中に遮断部250(例えば、MOSトランジスタ等のパスゲート)が設けられている。画素アレイ110の全ての画素100のうちの一部の画素100の信号のみが外部の処理部で利用さ

40

50

れるモードにおいて、信号が不要な列の比較器 130 (A/D 変換器) に対する入力は、遮断部 250 によって遮断される。遮断部 250 は、遮断信号 BLK がアクティブに設定されたときに、比較器 130 (A/D 変換器) に画素 100 の信号が供給されないように、比較器 130 への入力を遮断する。

#### 【0027】

第 1 变形例および第 2 变形例は、複数の比較器 130 の一部からの出力または複数の比較器 130 の一部への信号の入力を遮断する遮断部 250 を備える固体撮像装置 1 の構成例である。書き込み部 170 は、遮断部 250 による遮断がなされた比較器 130 に対応するメモリ 150 から水平出力線 210 にデジタル信号 PSV が出力されるように遮断部 250 による遮断がなされた比較器 130 に対応するメモリ 150 にデジタル信号 PSV を書き込む。10

#### 【0028】

図 5 を参照しながら本発明の第 2 実施形態の固体撮像装置 1 について説明する。第 2 実施形態として言及しない事項は、第 1 実施形態に従う。第 2 実施形態は、画素アレイ 110 における複数の列（画素 100 によって構成される列）を 3 列単位でグループ化し、各グループをパワーセーブ列 / 動作列 / パワーセーブ列とする動作モードを提供する。これは、水平方向に関して、画素信号の加算や間引きを行う際に動作不要な比較器 130 (A/D 変換器) をパワーセーブモードに設定し、電力消費を低減することを想定した動作モードである。パワーセーブ列には、パワーセーブ信号 PSAVE が供給され、動作列には、パワーセーブ信号 PSAVE が供給されない。この動作モードは、画素アレイ 110 を構成する複数の列から周期的に選択される列をパワーセーブモードに設定する動作モードの一例である。20

#### 【0029】

図 6 には、パワーセーブ信号 PSAVE がアクティブルレベルに設定されている場合の第 2 実施形態の固体撮像装置 1 の駆動方法が示されている。時刻 t6 からの水平転送期間において、所定値 (PSV)、カウント値 (A/D 変換されたデジタル信号)、所定値 (PSV)、所定値 (PSV)、カウント値 (A/D 変換されたデジタル信号)、所定値 (PSV) の順に信号が出力される。ここで、時刻 t6 ~ t7、t8 ~ t10、t11 ~ t12 が第 1 期間、時刻 t7 ~ t8、t10 ~ t11 が第 2 期間である。第 1 期間において、所定値 (PSV) が連続した期間 (t8 ~ t10) が存在するので、電力消費が低減される。30

#### 【0030】

図 7 を参照しながら本発明の第 3 実施形態の固体撮像装置 1 について説明する。第 3 実施形態として言及しない事項は、第 1 または第 2 実施形態に従う。第 3 実施形態では、書き込み制御部 172 は、第 1 書き込み制御信号 PSET1 および第 2 書き込み制御信号 PSET2 を生成する。第 1 書き込み制御信号 PSET1 は、画素 100 の信号を固体撮像装置 1 から出力する列（読み出し列）のメモリ 150 に対して所定値を有するデジタル信号 PSV を書き込むための制御信号である。第 2 書き込み制御信号 PSET2、画素 100 の信号を固体撮像装置 1 から出力しない列（非読み出し列）のメモリ 150 に対して所定値を有するデジタル信号 PSV を書き込むための制御信号である。この例では、第 2 書き込み制御信号 PSET2 は、パワーセーブ列にメモリ 150 に対して所定値を有するデジタル信号 PSV を書き込むための制御信号である。これにより、画素 100 の信号を固体撮像装置 1 から出力する列（読み出し列）と出力しない列（非読み出し列）に対するデジタル信号 PSV の書き込みを個別に制御することができる。40

#### 【0031】

この例では、第 1 書き込み制御信号 PSET1 は、第 3 列および第 4 列（読み出し列）のメモリ 150 に対するデジタル信号 PSV の書き込みを制御する。一方、第 2 書き込み制御信号 PSET2 は、第 1 列、第 2 列、第 5 列および第 6 列（非読み出し列）のメモリ 150 に対するデジタル信号 PSV の書き込みを制御する。

#### 【0032】

図 8 には、パワーセーブ信号 PSAVE がアクティブルレベルに設定されている場合の第

10

20

30

40

50

3 実施形態の固体撮像装置 1 の駆動方法が示されている。時刻  $t_0$  において、選択信号 S E L、第 1 書き込み制御信号 P S E T 1 および第 2 書き込み制御信号 P S E T 2 がハイレベルに駆動されることにより、全ての列のメモリ 150 に対して所定値を有するデジタル信号 P S V が書き込まれる。

#### 【 0 0 3 3 】

時刻  $t_3$  から始まる A D 変換期間では、各比較器 130 (A D 変換器) による比較に基づいて、画素 100 からのアナログ信号に対応するカウント値、即ち A D 変換されたデジタル信号が全ての列のメモリ 150 に書き込まれる。その後、時刻  $t_5$  において、選択信号 S E L および第 2 書き込み制御信号 P S E T 2 がハイレベルに駆動されることにより、非読み出列のメモリ 150 に再度、所定値を有するデジタル信号 P S V が書き込まれる。以上の動作により、水平転送期間において水平出力線 210 に出力される信号は、図 2 に示された第 1 実施形態と同様になる。したがって、第 3 実施形態においても、電力消費が低減される。

10

#### 【 0 0 3 4 】

図 9 を参照しながら本発明の第 4 実施形態の固体撮像装置 1 について説明する。第 4 実施形態として言及しない事項は、矛盾しない限り、第 1 ~ 第 3 実施形態にしたがうる。第 4 実施形態では、偶数列に配置された比較器 130 (A D 変換器) がパワーセーブモードに設定可能に構成されている。また、第 4 実施形態では、複数の水平出力線として第 1 水平出力線 210 および第 2 水平出力線 212 を有し、複数列のデジタル信号を第 1 水平出力線 210 および第 2 水平出力線 212 に分配して並列に出力することができる。

20

#### 【 0 0 3 5 】

パワーセーブ信号 P S A V E がアクティブルーレベルに設定され、偶数列の比較器 130 がパワーセーブモードに設定された場合について説明する。この場合、複数のメモリ 150 のうち偶数列のメモリ 150 から水平出力線 212 に対して所定値を有するデジタル信号 P S V が出力されるように、複数のメモリ 150 のうち少なくとも偶数列のメモリ 150 に対してデジタル信号 P S V が書き込まれる。この例では、全てのメモリ 150 に対して信号 P S V が書き込まれた後に、奇数列のメモリ 150 に対してのみ A D 変換されたデジタル信号が上書きされる。水平出力線 212 には、デジタル信号 P S V が連続的に出力されるので、水平出力線 212 は一定レベルに維持される。したがって、水平出力線 212 の充放電に伴う電力消費が低減される。

30

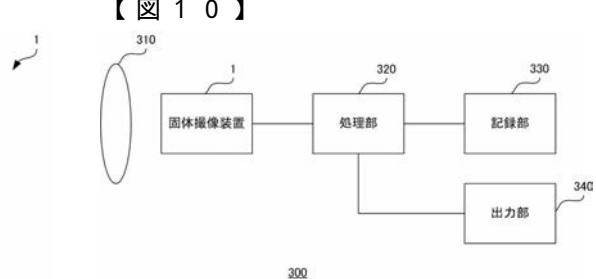

#### 【 0 0 3 6 】

以下、図 10 を参照しながら本発明の 1 つの実施形態のカメラ 300 について説明する。カメラの概念には、撮影を主目的とする装置のみならず、撮影機能を補助的に備える装置（例えば、パーソナルコンピュータ、携帯端末）も含まれる。カメラ 300 は、上記の実施形態として例示された本発明に係る固体撮像装置 1 と、固体撮像装置 1 から出力されるデジタルを処理する処理部 320 とを含む。処理部 320 は、例えば、固体撮像装置 1 から出力されたデジタル信号を処理（例えば、色処理、圧縮など）する。処理部 320 は、例えば、固体撮像装置 1 から出力されたデジタル信号から固体撮像装置 1 によって検出された信号を抽出して処理する機能を含む。カメラ 300 は、更に、記録部 330 および出力部 340 を含みうる。記録部 330 は、処理部 320 によって処理されたデジタル信号を記録媒体に記録する。出力部 340 は、例えば、表示部および通信部の少なくとも 1 つを含み、処理部 320 によって処理されたデジタル信号などの信号を出力する。

40

#### 【 符号の説明 】

#### 【 0 0 3 7 】

1 : 固体撮像装置、100 : 画素、110 : 画素アレイ、A D U : A D 変換部、200 : 水平選択部（選択部）、170 : 書き込み部、130 : 比較器、140 : 参照信号発生部、160 : カウンタ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 小林 秀央

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 板野 哲也

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 中村 恒一

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

F ターム(参考) 5C024 CY42 GY31 HX02 HX23 JX08 JX41