RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 463 555**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21) **N° 79 20651**

-

- (54) Dispositif d'affichage permanent d'information graphique sur un écran de télévision et de transmission simultanée sur ligne téléphonique.

- (51) Classification internationale (Int. Cl. 3). H 04 N 1/40; H 04 M 11/00.

- (22) Date de dépôt ..... 14 août 1979.

- (33) (32) (31) Priorité revendiquée :

- (41) Date de la mise à la disposition du public de la demande ..... B.O.P.I. — « Listes » n° 8 du 20-2-1981.

-

- (71) Déposant : OPTION SA, résidant en France.

- (72) Invention de : Andréi Landau et Dominique Thillet.

- (73) Titulaire : *Idem* (71)

- (74) Mandataire : Cabinet Moutard,

9, square Copernic, résidence Iéna, 78150 Le Chesnay.

-

L'invention se rapporte à un appareil destiné à l'inscription ou l'effacement, l'affichage et la transmission d'une information graphique.

On a décrit, dans la demande de brevet français déposée 5 le 9 Octobre 1978 sous le n° 78 29463 par la Demanderesse pour : "Dispositif d'inscription et de traduction informatique d'un tracé par effet capacatif entre la pointe d'un stylo à bille et un réseau de barres conductrices excitées séquentiellement" une "tablette graphique" sur laquelle un utilisateur exécute à la 10 main, au moyen d'un stylo à pointe conductrice, un dessin ou une inscription quelconque. Cette tablette est équipée du circuit de conversion du tracé en signaux électriques représentatifs des coordonnées de chacun de ses points. Il est prévu plusieurs 15 modes de fonctionnement : tracé continu ; tracé en mode "curseur" dans lequel un pavé indique la position ; tracé en mode "gomme" dans lequel la portion de tracé recouverte par un pavé est gommée ; enfin un mode "effacement" permet d'effacer la totalité du tracé déjà affiché.

La présente invention a pour objet un dispositif, destiné à coopérer avec une tablette graphique du genre susvisé ou 20 avec un organe similaire, en vue de l'affichage permanent immédiat du tracé sur l'écran d'un récepteur de télévision du commerce sous la forme où il se présente à l'écriture, de sa transmission instantanée sur une ligne téléphonique publique et de 25 la réception, sur cette même ligne, d'un tracé exécuté à distance sur une autre tablette graphique, les tracés exécutés localement et à distance se superposant sur l'écran.

Les solutions apportées jusqu'ici à ce genre de problème ne sont que partielles et ne conduisent pas à la réalisation d'un dispositif compact, relativement peu onéreux et permettant 30 un affichage permanent de l'image complète sur un écran de télévision du type "grand public", tout en autorisant l'affichage simultané du tracé effectué localement et d'un autre tracé exécuté à distance.

Le dispositif suivant l'invention est principalement caractérisé en ce que ladite mémoire est organisée pour avoir 35 une capacité suffisante pour contenir l'information graphique correspondant à une image complète de télévision recouvrant tout l'écran d'un récepteur du type grand public, l'adressage 40 de la mémoire étant effectué de manière qu'il existe une cor-

respondance biunivoque entre les emplacements de la mémoire et les points du tracé et que lesdits moyens comprennent un micro-processeur, des interfaces entre le micro-processeur, l'appareil d'inscription et un modem associé à la ligne téléphonique, un organe de balayage apte à engendrer en permanence un signal de télévision dont l'information utile est fournie par lecture de ladite mémoire et des moyens d'interdire l'accès à la mémoire par le micro-processeur pendant des fractions prédéterminées de la durée de chaque ligne de télévision, suffisantes pour que l'accès de la mémoire par l'organe de balayage pendant lesdites fractions permette d'afficher en permanence l'information graphique sur ledit écran.

Suivant un mode d'exécution préféré, la mémoire est organisée en au moins un plan comportant trois pages de 16 K octets chacune, les octets 0 à 95 de chaque ligne de télévision étant distribués entre les trois pages, dans l'ordre 0, 3, 6..93 pour la première, 1, 4, 7..94 pour la seconde et 2, 5, 8..95 pour la troisième, l'organe de balayage effectuant la lecture en parallèle de trois octets à la fois dans les trois pages respectives tandis que le micro-processeur effectue la lecture sélective, de la mémoire page par page et, dans chacune des pages de la mémoire, les lignes de télévision 0 à 511 étant distribuées dans l'ordre 0, 2, 4, 6 - 1, 3, 5, 7 - 8, 10, 12, 14... c'est-à-dire de façon qu'un groupe de quatre lignes de numéros impairs successifs succède toujours à un groupe de quatre lignes de numéros pairs intercalés.

D'autres caractéristiques, ainsi que les avantages de l'invention, apparaîtront clairement à l'aide de la description ci-après.

Au dessin annexé :

La figure 1 est un schéma général de principe d'un dispositif conforme à l'invention ;

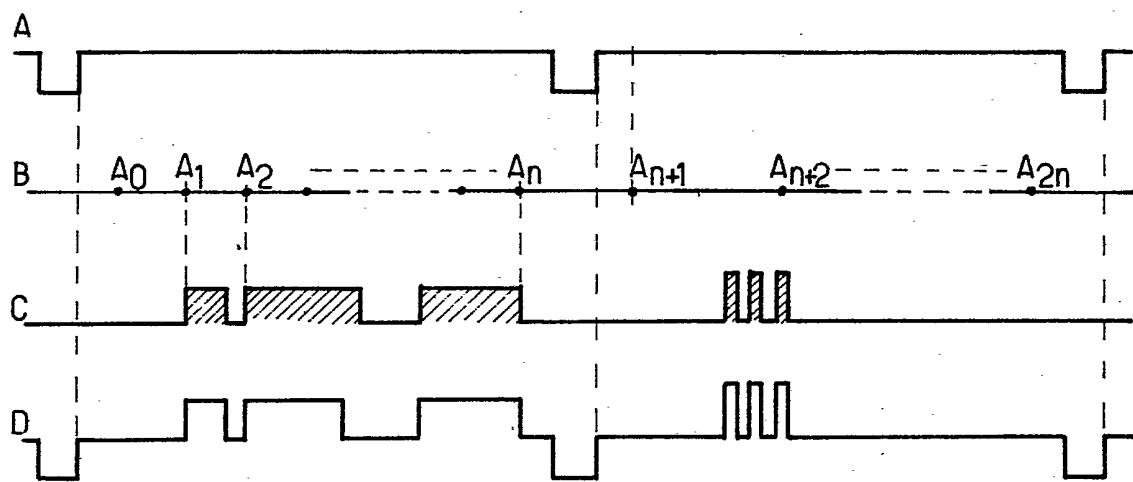

La figure 2 représente schématiquement les signaux engendrés par l'organe de synchronisation que comporte un tel dispositif ;

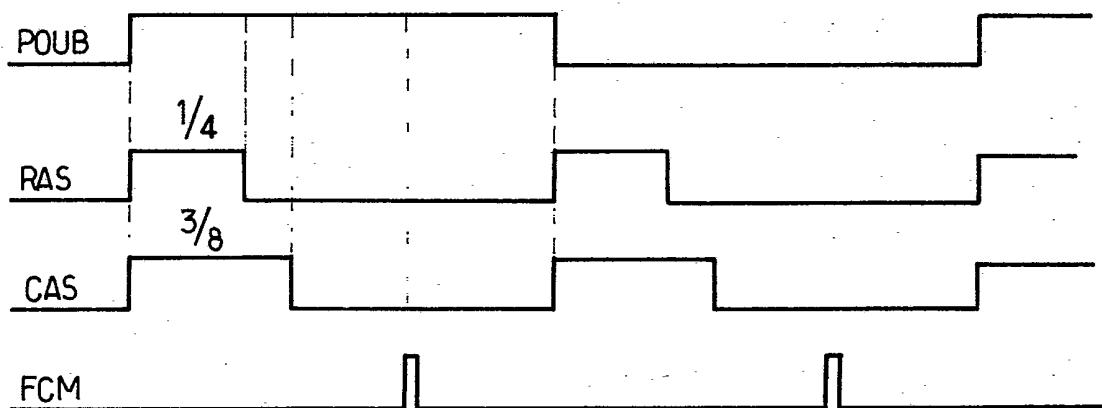

La figure 3 est un schéma plus détaillé d'une partie du dispositif de la figure 1, comportant en particulier, la mémoire, le registre vidéo et les organes de multiplexage et d'arbitrage ;

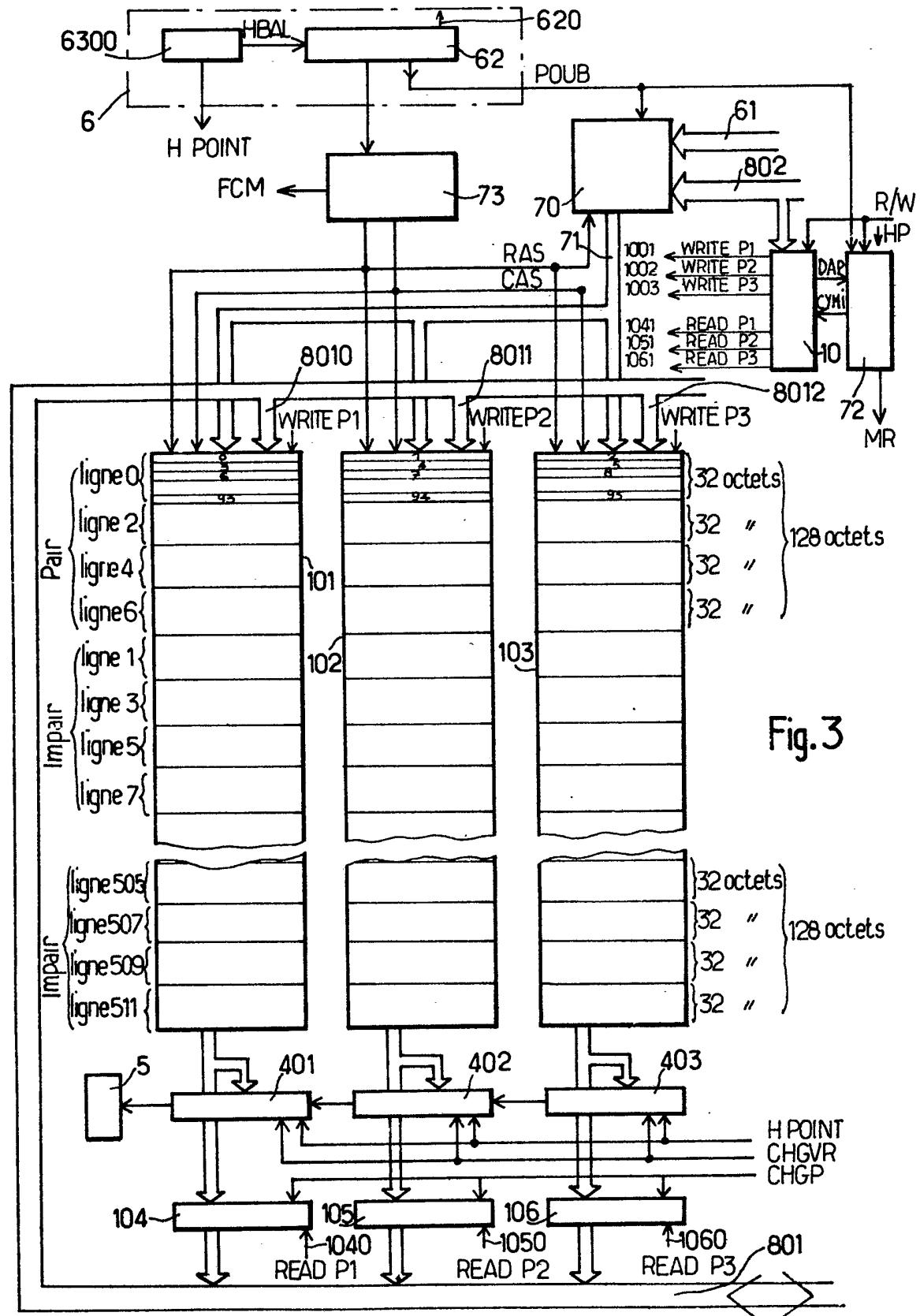

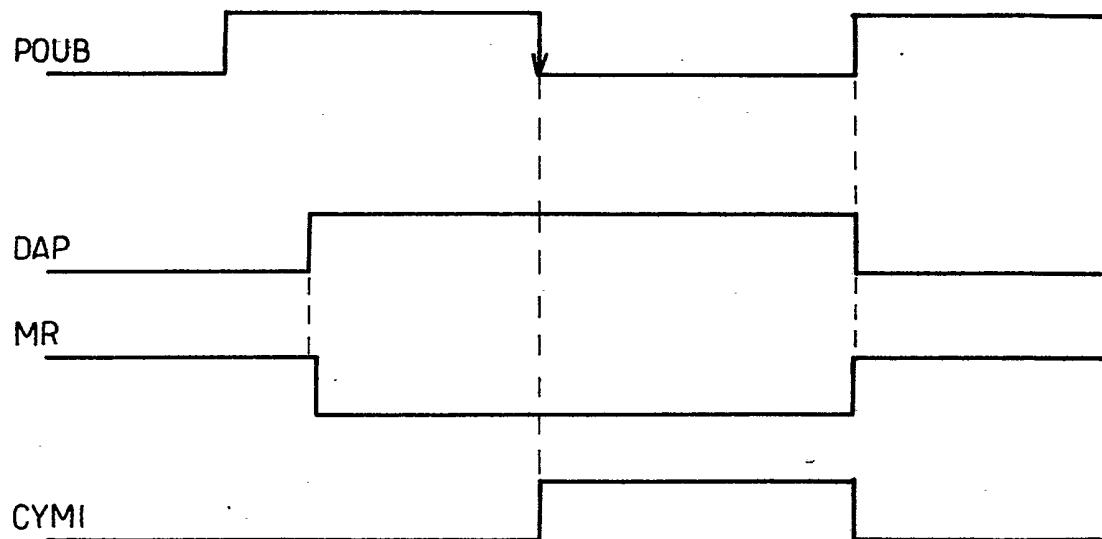

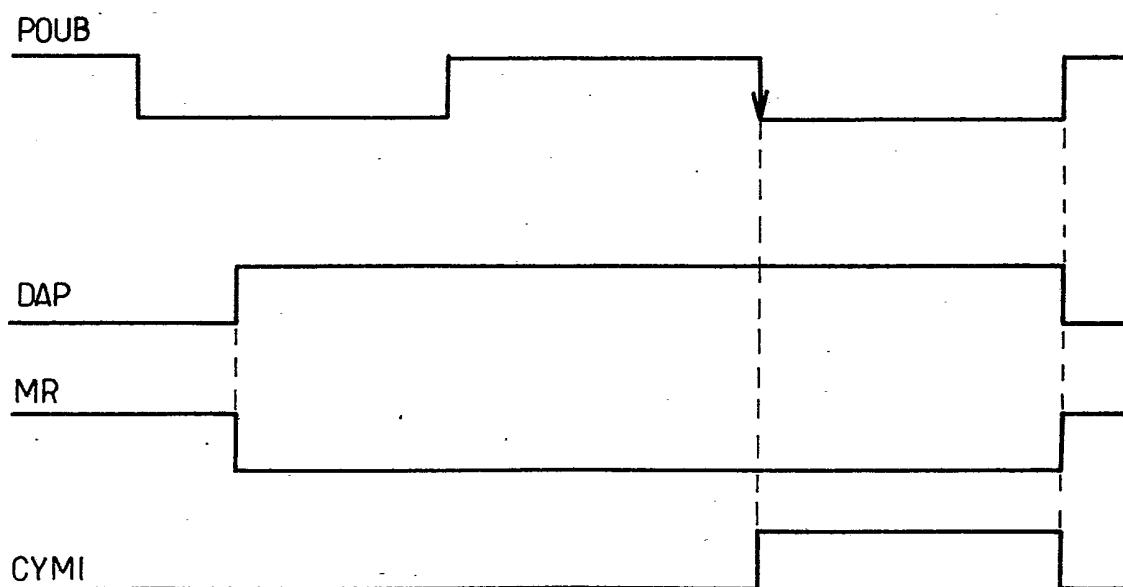

Les figures 4 et 5 représentent les signaux (POUB, DAP, MR, CYMI) d'arbitrage entre le micro-processeur et l'organe de

balayage, respectivement lorsque la demande d'accès du micro-processeur à la mémoire (DAP) intervient pendant un créneau positif du segment POUB et pendant un créneau négatif ;

5 La figure 6 représente les signaux (RAS et CAS) de rafraîchissement des rangées et des colonnes de la mémoire d'image ;

La figure 7 représente le décodeur des adresses fournies par le micro-processeur ;

10 La figure 8 représente l'organisation de l'espace d'adressage du micro-processeur ;

La figure 9 représente le détail du circuit d'arbitrage ;

La figure 10 représente le générateur d'horloge qui comporte l'organe de balayage ;

15 La figure 11 représente le générateur de balayage ;

La figure 12 représente les signaux correspondant à une ligne de télévision ;

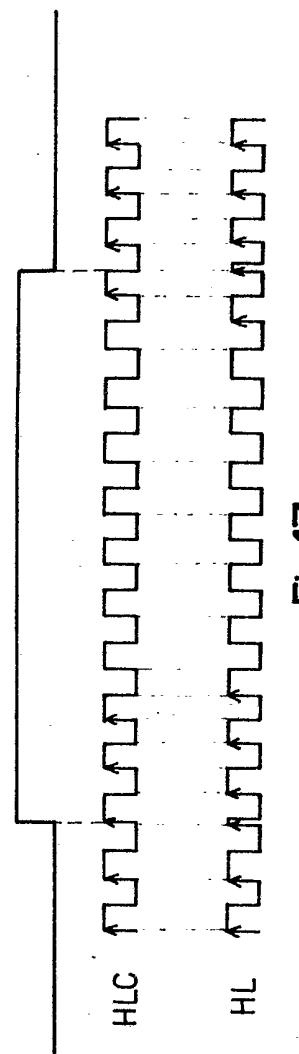

20 La figure 13 représente le signal INVERSION et les signaux d'horloge HLC et HL utilisés dans le générateur de balayage ; et

La figure 14 représente un circuit de doublage du trait.

A la figure 1, on a représenté :

25 - une mémoire 1 destinée à contenir une image graphique fournie, soit par une tablette d'écriture graphique, par l'intermédiaire d'un interface 2 ayant une entrée 201 reliée à la tablette, soit par un modem, par l'intermédiaire d'un interface 3 qui sert à la fois à l'émission (ligne 301) et à la réception (ligne 302)

30 - un registre 4, dont l'entrée est reliée à une sortie de la mémoire 1 et dont la sortie est connectée à un interface de sortie vidéo 5, lui-même relié à un moniteur de télévision 502 par une ligne 501.

35 - un générateur de signaux de balayage de télévision et d'horloge 6 relié, d'une part à l'interface de sortie 5 (liaison 620), d'autre part à un bloc 7 jouant le rôle d'organe de commande et de multiplexage d'adresses de la mémoire d'image 1 (liaison 61).

40 - un micro-processeur central 8, relié par un bus de données 801

à la mémoire 1, à une mémoire de programme et de données 9 et aux interfaces 2 et 3 et, par un bus d'adresses 802, au bloc 7, à la mémoire 9 et à un décodeur d'adresses 10. Ce dernier est relié aux blocs 2, 3, 7 et 9 et permet leur adressage.

- 5 - un circuit détecteur d'erreurs 11 et un bloc tampon de transmission 12, intercalés sur le bus de données entre le processeur 8 et l'interface 3.

Le processeur 8 acquiert des coordonnées XY de points (accompagnées d'un ordre d'inscription ou d'effacement),

10 en provenance soit de la tablette, soit d'une ligne téléphonique et les inscrit (ou les efface) dans la mémoire d'image 1 après un processus d'adressage réalisé par le bloc 7.

Le contenu de la mémoire d'image est affiché en permanence sur le moniteur de télévision.

15 A cet effet, le bloc 6 engendre, comme on l'expliquera dans la suite, un signal de synchronisation de télévision (forme d'onde A figure 2), des signaux d'adresse  $A_0 \dots A_n$ , puis  $A_{n+1} \dots A_{2n}$  etc (symbolisés en B) qui permettent la lecture, par le bloc 7, de la mémoire d'image. Le contenu ainsi lu (liaison 100) 20 est stocké dans le registre 4, où il est sérialisé sous la commande du bloc 6 (signaux "HPOINT").

Le signal de sortie du registre 4, représenté à titre d'exemple en C, constitue le signal de luminance.

25 L'interface 5 effectue la superposition des signaux A et C, pour donner un signal "vidéo-composite" D permettant la commande du moniteur de télévision.

30 Le micro-processeur inscrit par ailleurs les données dans une partie du type RAM de la mémoire 9, en vue d'un traitement ultérieur effectué suivant un programme contenu dans une partie du type ROM de ladite mémoire.

Après traitement approprié, les données en provenance de la tablette sont en outre transmises sur la ligne téléphonique 351 en vue d'un affichage à distance par un dispositif identique à celui de la figure 1..

35 La vitesse d'arrivée des informations graphiques (coordonnées XY) étant très grande (par exemple 1000 points par sec.) il est nécessaire, avant leur transmission sur la ligne, dont la capacité de transmission est faible, d'une part de les compacter (ce qui est effectué par le processeur 8 à l'aide d'un programme contenu dans la mémoire 9), d'autre part, de les faire

passer par le tampon 12, comme on l'expliquera dans la suite.

A la réception, les informations traversent le tampon 12 dans l'autre sens et ne sont effectivement acquises qu'après examen par un bloc 11 qui les invalide lorsque leur structure 5 n'est pas conforme à celle qui doit normalement résulter de l'opération de compactage. Celle-ci consiste à effectuer une certaine sélection des points dont les coordonnées seront effectivement transmises, en faisant application d'un algorithme déterminé, qui ne fait pas partie de l'invention.

10 A partir du moment où le bloc 11 détecte une erreur et jusqu'à l'arrivée d'une nouvelle information codée correspondant à l'indication que le stylo a cessé d'être en contact avec la tablette (fin de trait), l'information n'est plus affichée. Ce procédé évite l'affichage de tracés aberrants.

15 On notera que la mémoire 1 a, selon une particularité du dispositif décrit, une capacité suffisante pour contenir l'information correspondant à une image complète de télévision recouvrant tout l'écran d'un moniteur grand public. En pratique, on adoptera de préférence une capacité d'affichage correspondant 20 à 768 points X 512 lignes.

25 La figure 3 représente l'organisation de la mémoire 1. L'information à afficher correspond à 48 K octets (K = 1024). La mémoire 1 est décomposée en trois pages 101-102-103 de 16 K octets chacune. Chaque page comporte 16 K mots et on a représenté, dans les mots successifs, les octets correspondants d'une image de télévision décomposée en lignes numérotées de 0 à 511, chaque ligne étant elle-même décomposée en octets numérotés de 0 à 95.

30 On voit que les octets de la ligne 0 sont distribués de la manière suivante :

35 page 101 : octets 0, 3, 6, 9...93 ; page 102 : octets 1, 4, 7...94 ; page 103 : octets 2, 5, 8 etc..95. Les lignes sont elles-mêmes distribuées de la manière suivante : 0, 2, 4, 6 ; 1, 3, 5, 7 ; 8, 10, 12, 14 ; 9, 11, 13, 15 etc...L'intérêt de cette distribution sera expliqué dans la suite.

40 Le registre vidéo (4 figure 1) est décomposé en trois registres 401, 402, 403 (figure 3) respectivement reliés aux pages 101, 102, 103 et permettant la lecture en parallèle de trois octets dans les trois pages respectives, suivie de leur sérialisation par 24 coups d'horloge H POINT fournis par le bloc 6,

Comme on l'expliquera dans la suite les registres 401-402-403 reçoivent également des signaux de chargement CHGRV.

Par ailleurs, les pages 101, 102, 103 sont respectivement reliées à trois registres à verrouillage 104, 105, 106 qui permettent la lecture sélective page par page des octets sous la commande du micro-processeur. A cet effet, leurs entrées de commande 1040, 1050 et 1060 sont reliées à des sorties 1041, 1051 et 1061 respectivement, du décodeur 10. Le chargement de ces registres à verrouillage par le contenu de la mémoire s'effectue sous la commande de signaux CHGP élaborés par un circuit d'arbitrage 72, comme on le verra dans la suite.

Le bloc 7 (figure 1) comprend un multiplexeur 70 qui aiguille en parallèle vers les trois pages 101-102-103 (bus 71) des adresses provenant, soit du processeur 8 (bus 802), soit du dispositif de balayage 6 (bus 61). Ce multiplexeur est commandé par un signal Poub ("processeur ou balayage") fourni par un compteur de ligne 62 qui fait partie du bloc 6 et sera décrit dans la suite.

Le bus de données 801 est relié (en 8010-8011-8012) aux entrées des pages 101 à 103 pour l'inscription des données en mémoire. L'inscription est sélective et validée, page par page, par trois signaux WRITE  $P_1$ , WRITE  $P_2$  et WRITE  $P_3$  fournis aux sorties 1001, 1002 et 1003 du décodeur 10.

Les signaux sur les six sorties du décodeur 10 sont engendrées à la suite d'un décodage des quatorze adresses fournies à travers le bus 802 par le microprocesseur.

Les signaux d'écriture WRITE  $P_1$ , WRITE  $P_2$ , WRITE  $P_3$  sont validés par un premier signal auxiliaire (R/W : lecture-écriture) fourni par le microprocesseur et par un second signal auxiliaire CYMI fourni par le circuit d'arbitrage 72 qui fait partie du bloc 7. Le circuit 72 est lui-même commandé par un signal DAP fourni par le décodeur 10 et interprété comme une demande d'accès du processeur à la mémoire d'image. Le circuit 72 reçoit par ailleurs le signal Poub et fournit un signal MR (arrêt temporaire du microprocesseur), comme on l'expliquera plus loin.

Une horloge 6300, qui fait partie du bloc 6, excite le compteur de ligne 62 qui engendre, outre le signal A ci-dessus sur sa sortie 620, le signal Poub (figures 4 et 5), composé de créneaux d'égale durée (1/80ième de ligne de télévision par exem-

ple) alternativement positif et négatifs.

5 Les crêneaux positifs sont affectés à l'accès du système de balayage dans la mémoire d'image en vue de la lecture et du rafraîchissement de celle-ci, tandis que les crêneaux négatifs sont affectés à l'accès du microprocesseur 8. Néanmoins, le signal DAP peut arriver à tout moment.

10 A l'arrivée du signal DAP, le circuit 72 engendre un signal MR qui gèle l'action du microprocesseur jusqu'à l'arrivée du crêneau négatif suivant du signal Poub. A ce moment, le circuit 72 lance un cycle de mémoire d'image (CYMI) dont la disparition entraîne, à son tour, celle du signal MR, donc le dégel du microprocesseur. La mémoire 1 est réalisée avec des circuits intégrés du type mémoire dynamique et doit donc être rafraîchie périodiquement.

15 A cet effet, un circuit décodeur 73 qui fait partie du bloc 7 effectue une combinaison logique appropriée des états des étages intermédiaires du compteur 62 et engendre ainsi deux crêneaux RAS et CAS (figure 6), dont les fronts montants coïncident avec ceux du signal Poub et dont les durées sont respectivement de 1/4 et 3/8 de la durée des crêneaux du signal Poub. Ces signaux servent respectivement au rafraîchissement des rangées et des colonnes de la mémoire 1. Le circuit 73 fournit par ailleurs un signal FCM (fin de cycle mémoire : figure 6), comme on le verra dans la suite.

25 Le multiplexeur 70 reçoit les adresses 802 sur 14 bits et les transmet à la mémoire 1 sur un bus 71 de 7 bits (la mémoire n'ayant que sept entrées d'adresses) grâce à un séquencement dans le temps assuré par la valeur du signal RAS. Lorsque RAS = 1 le multiplexeur transmet les sept bits de poids 30 faibles des adresses. Lorsque RAS = 0, le multiplexeur transmet les sept bits de poids fort des adresses.

35 L'intérêt de constituer la mémoire 1 en trois pages est de pouvoir lire trois mots à la fois en parallèle, ce qui espace dans le temps les accès à la mémoire de l'organe de balayage, donc de donner au microprocesseur l'accès à la mémoire dans l'intervalle de temps libre entre deux accès de l'organe de balayage sans pour cela, altérer l'image visualisée. (Le temps d'accès usuel d'un octet dans une mémoire de ce genre est de l'ordre de 500 ns, ce qui correspond sensiblement à la durée affectée à 40 l'affichage de huit points de l'image de télévision).

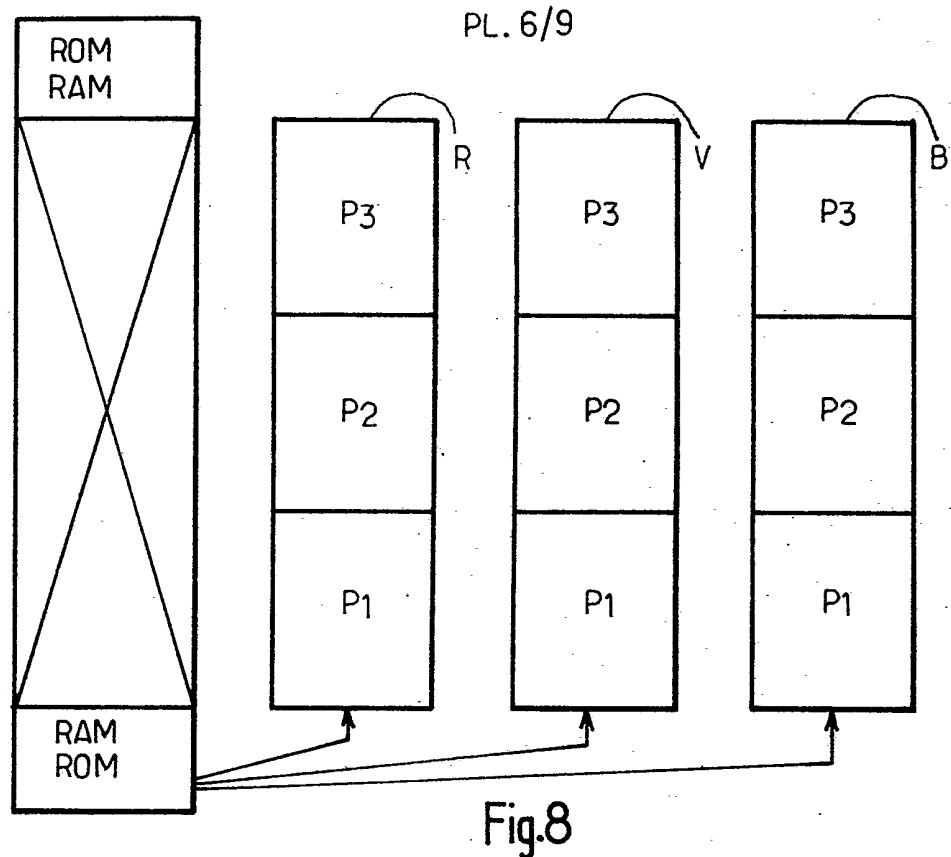

Vue de côté de l'organe de balayage, la mémoire d'image est ainsi organisée en mots de 24 bits, tandis que, vue du côté du microprocesseur (adressage sélectif), elle est organisée en mots de 8 bits. On a vu, en se référant à la figure 3, que chaque 5 page de la mémoire est organisée en 128 sous-pages, comportant chacune quatre blocs de 32 mots. A chaque bloc de 32 mots correspond un tiers d'une ligne de télévision. Dans chaque sous-page sont représentées quatre lignes successives paires ou im-paires. Cette organisation imbriquée de la mémoire est justifiée 10 par la nécessité de rafraîchir les mémoires dynamiques avec les-quelles la mémoire 1 est réalisée, sur les 7 bits de poids fai-ble (128 positions de mémoire), au moins toutes les 2 ms, résul-tat qui est obtenu automatiquement, car la durée d'une ligne de télévision est d'environ 64 microsecondes ( $4 \times 64 = 256 \mu\text{s} < 2\text{ms}$ ).

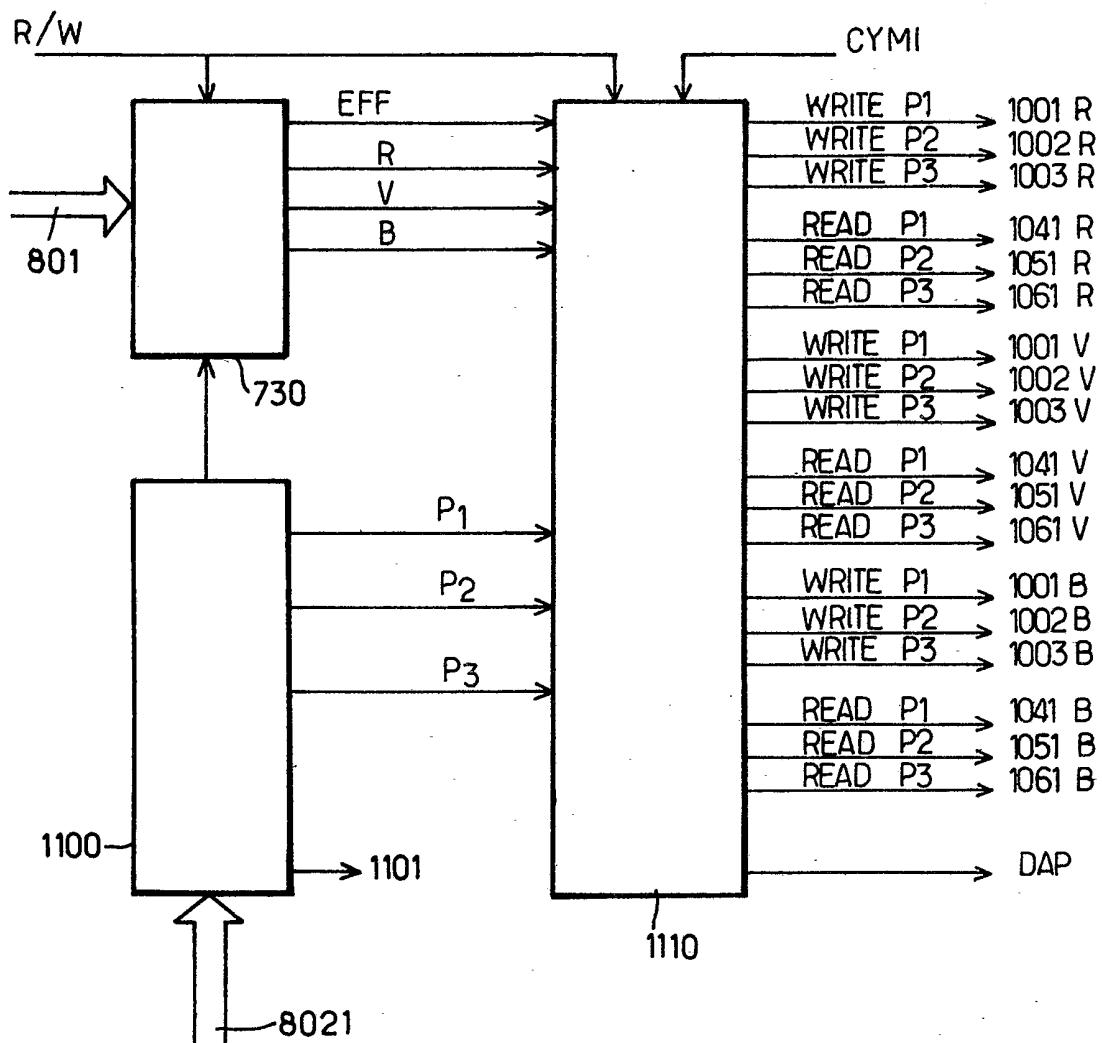

15 A la figure 7, on a représenté plus en détail le déco-deur 10 dans le cas où l'on utilise trois couleurs V (vert), B (bleu) et R (rouge) pour la constitution d'une image.

Un premier étage 1100 détecte l'intention d'accès du 20 microprocesseur dans l'une des trois pages de la mémoire 1 et éla-bore les signaux de sélection de divers organes, tels que les interfaces 2-3-10 (signaux symbolisés par une sortie 1101) et un signal de sélection d'un registre de commande 730 qui fait par-tie du bloc 7. Dans ce registre, le microprocesseur inscrit 25 (signal R/W) celui des plans de la mémoire d'image dans lequel il désire afficher. En effet, la mémoire 1 est alors réalisée en plusieurs plans comportant chacun trois pages organisées comme on l'a décrit ci-dessus. Dans l'exemple considéré, il y aura trois plans correspondant aux trois couleurs RBV. Les informa-tions RBV fournies par le registre 730 sont appliquées à un deux-ième étage 1110 du décodeur, qui reçoit par ailleurs les signaux 30 R/W, CYMI et de sélection de page ( $P_1$ ,  $P_2$ ,  $P_3$ ) et élabore, pour chaque plan de mémoire, des signaux de sélection en écriture, qui correspondent aux signaux fournis sur les sorties 1001 à 1003 à la figure 3, et des signaux de sélection en lecture des regis-tres à verrouillage, qui correspondent aux sorties 1041, 1051 et 35 1061 à la figure 3, étant entendu que, dans le dispositif de la figure 7, trois groupes de signaux sont fournis, par exemple 1001 R, 1001 V, 1001 B, correspondant aux trois couleurs respec-tives. L'étage 1110 élabore également le signal DAP déjà men-40 tionné et ce, que  $P_1$ ,  $P_2$  ou  $P_3$  soient actifs.

Le registre 730 reçoit également du microprocesseur, par le bus 801, un ordre d'effacement de la mémoire d'image et le transmet à l'étage 1110. L'activation de ce signal EFF provoque la validation en parallèle, en écriture, de tous les signaux de type 1001, 1002, 1003, ce qui permet, pour l'effacement de la mémoire d'image, l'inscription de l'information d'effacement (écriture de zéros), en parallèle dans les trois pages. Le temps d'effacement correspond ainsi à la durée de 16 K cycles seulement, au lieu de 48 K.

A la figure 8, on a représenté l'organisation de l'espace d'adressage du microprocesseur avec trois plans de mémoire d'image R V B constitués chacun de trois pages 101, 102, 103 de 16 K mots. On remarque que le microprocesseur, dont la capacité d'adressage est de 64 K mots de 8 bits, peut accéder dans les plans de couleurs de la mémoire d'image (après sélection par le registre de commande) comme dans son propre espace d'adressage RAM - ROM.

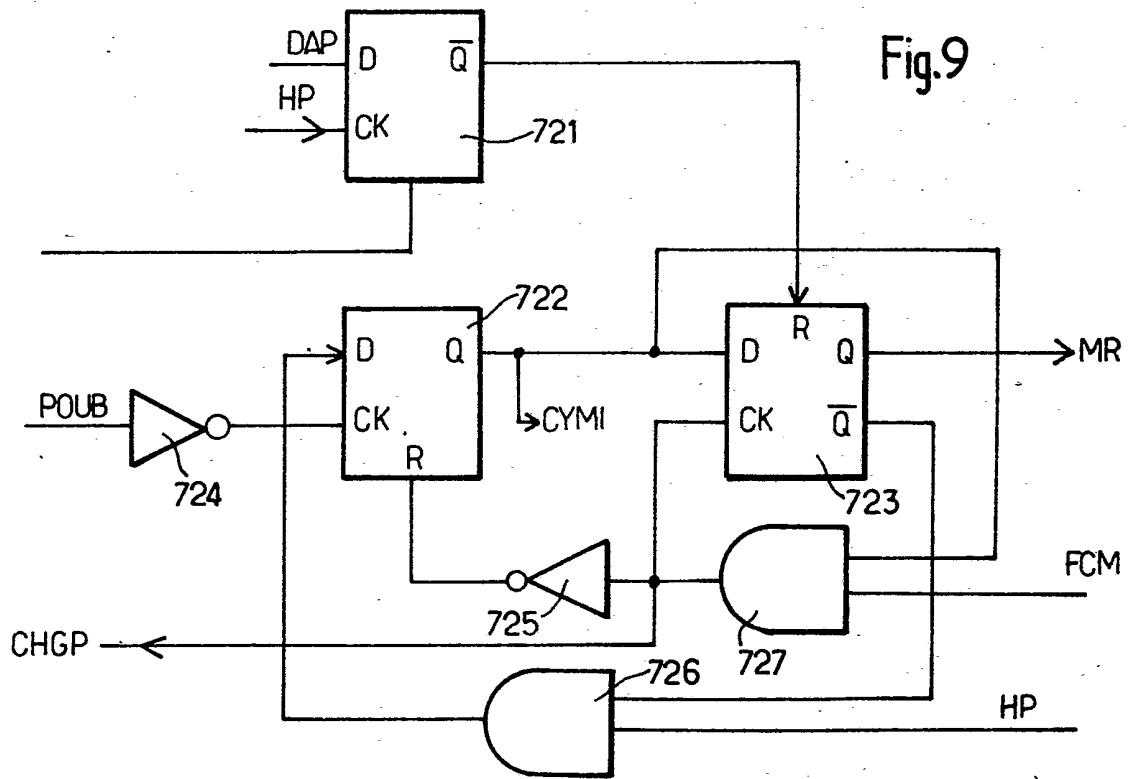

A la figure 9, on a représenté dans le détail un mode d'exécution préféré du circuit d'arbitrage 72 de la figure 3. Il comprend trois bascules type D 721 - 722 - 723, deux amplificateurs inverseurs 724 et 725 et deux portes OU 726 et 727.

La bascule 721 échantillonne la demande d'accès au processeur DAP au rythme de l'horloge HP du microprocesseur. La sortie  $\bar{Q}$  de cette bascule positionne à zéro la sortie MR de la bascule 723 et, par l'intermédiaire de la porte 726, présente un signal 1 à l'entrée D de la bascule 722. La sortie Q de cette dernière se trouve initialement à l'état 0. L'arrivée d'un front négatif du signal Poub fait monter la sortie Q de la bascule 722 à l'état 1 et signifie le lancement d'un cycle de mémoire d'image pour le processeur. L'arrivée ultérieure (par exemple, 600 nanosecondes plus tard) du signal FCM, dont la durée est très brève (par exemple 100 nanosecondes) permet, par l'intermédiaire de la porte 727 et de l'inverseur 725, d'une part, la remise à 1 de la sortie Q de la bascule 723, (remise en condition initiale de MR) d'autre part, la remise en condition initiale (0) de la sortie Q de la bascule 722.

Le signal CHGP issu de la porte 727 est appliqué aux registres 104 à 106 (figure 3) pour échantillonner les données présentées par la mémoire d'image en vue d'une sortie ultérieure sur le bus de données. La durée de ce signal dépend du temps de

transit dans les organes 723 et 727.

L'imbrication des octets et des lignes en mémoire d'image, telle que définie ci-dessus en se référant à la figure 3, est obtenue de la manière suivante :

5 On fait correspondre, aux adresses sur 14 bits (provenant du générateur de balayage ou du microprocesseur) à l'entrée du multiplexeur 70, des adresses de sortie (réparties comme on l'a indiqué ci-dessus, en deux séquences de sept adresses) destinées à la mémoire d'image, avec le tableau de correspondance suivant :

10-0 ; 1-1 ; 2-2 ; 3-3 ; 4-4 ; 5-7 ; 6-5 ; 7-6 ; 8-8 ; 9-9 ; 10-10 ; 11-11 ; 12-13 et 13-13, le premier chiffre représentant l'adresse d'entrée et le second, l'adresse de sortie.

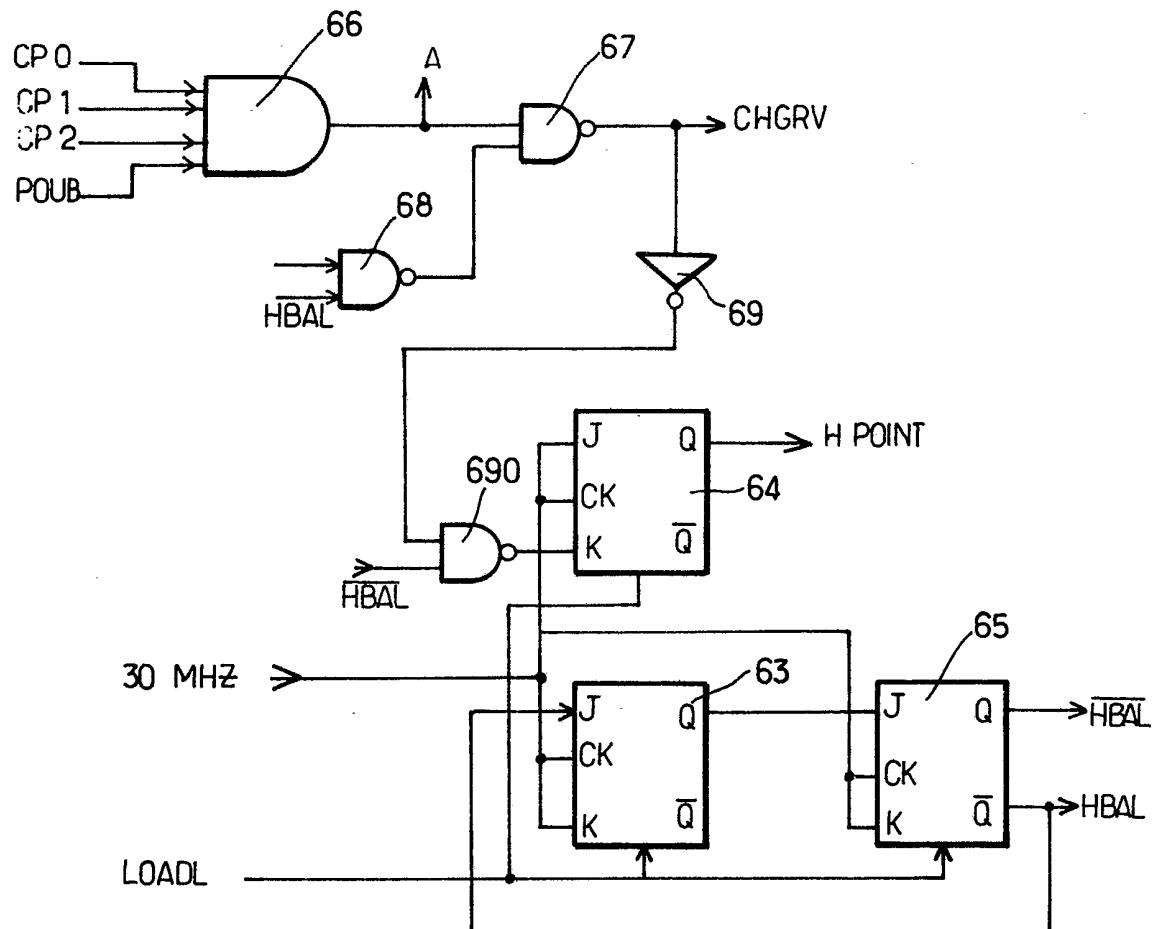

15 On va maintenant décrire, en se référant à la figure 10, le générateur d'horloge 6300 que comporte le bloc 6 de la figure 1. Un signal étalon de 30 MHz est appliqué à trois bascules type JK 64 et 63-65 qui fournissent respectivement des fréquences de 15 MHz et 10 MHz. La fréquence de 15 MHz est utilisée comme signaux d'horloge HPOINT (figure 3). La fréquence de 20 10 MHz, obtenue à la sortie de la bascule 65, est la fréquence HBA (figure 3), qui est utilisée dans le compteur de lignes 62 (figures 3 et 5), lequel fournit, en particulier, comme on l'expliquera plus loin, des signaux  $CP_0$ ,  $CP_1$ ,  $CP_2$  et POUR dont la coïncidence est réalisée par une porte ET 66. La sortie de la 25 porte 66 est appliquée à une porte NON ET 67 dont l'autre entrée est reliée à la sortie d'une porte NON ET 68 qui reçoit le signal  $Q_0$  issu de la bascule 63 et le signal HBAL. La sortie de la porte 67 est, après inversion en 69, appliquée à l'entrée d'une porte NON ET 690 qui reçoit par ailleurs le signal HBAL. La 30 sortie de la porte 690 est relié à l'entrée de la bascule 64.

A la sortie de la porte 67, on obtient le signal CHGRV (figure 3). Les organes 67, 69 et 690 assurent le calage de phase de HPOINT sur HBAL.

35 On notera que l'on pourrait également utiliser, pour obtenir les signaux HPOINT, la sortie HBAL. Dans ce cas, la ligne de télévision comportera 512 points au lieu de 768.

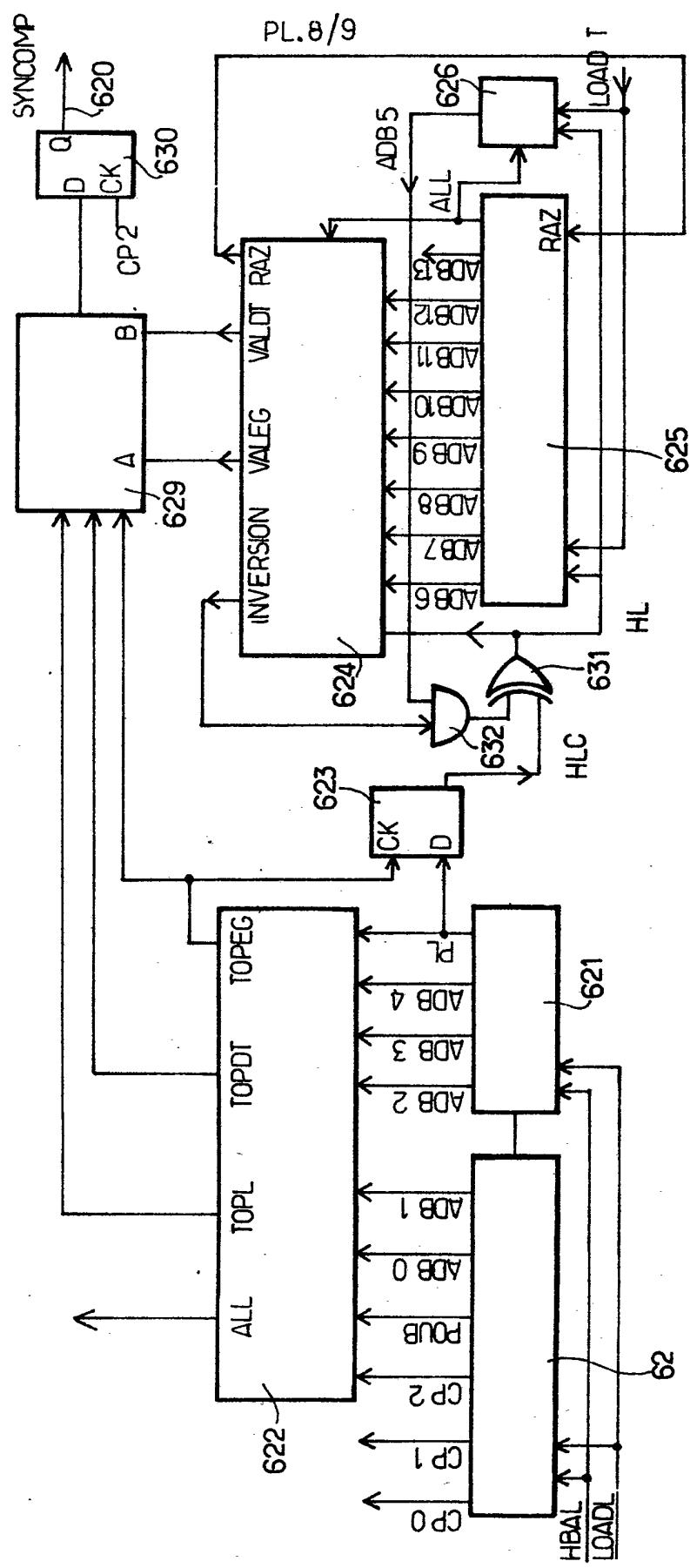

40 On va maintenant décrire, en se référant à la figure 11, le générateur de balayage que comporte le bloc 6 de la figure 1. On voit que le compteur désigné par le numéro 62 à la figure 3 reçoit des signaux HBAL et LOADL, qui sont également

appliqués à un compteur 621 ; les compteurs 62 et 621 sont de type synchrone et connectés en série.

Le compteur 62 fonctionne en diviseur par 64 et ses six étages de division fournissent respectivement des signaux  $CP_0$ ,  $CP_1$ ,  $CP_2$ , Poub, ADB0 et ADB1. Le compteur 621 fonctionne en diviseur par 10 et ses quatre étages fournissent respectivement des signaux ADB2, ADB3, ADB4 et PL. Les signaux ADB0 à ADB4 constituent les cinq premières adresses de poids faibles des octets dans la mémoire d'image, correspondant aux trente deux octets d'une ligne de télévision.

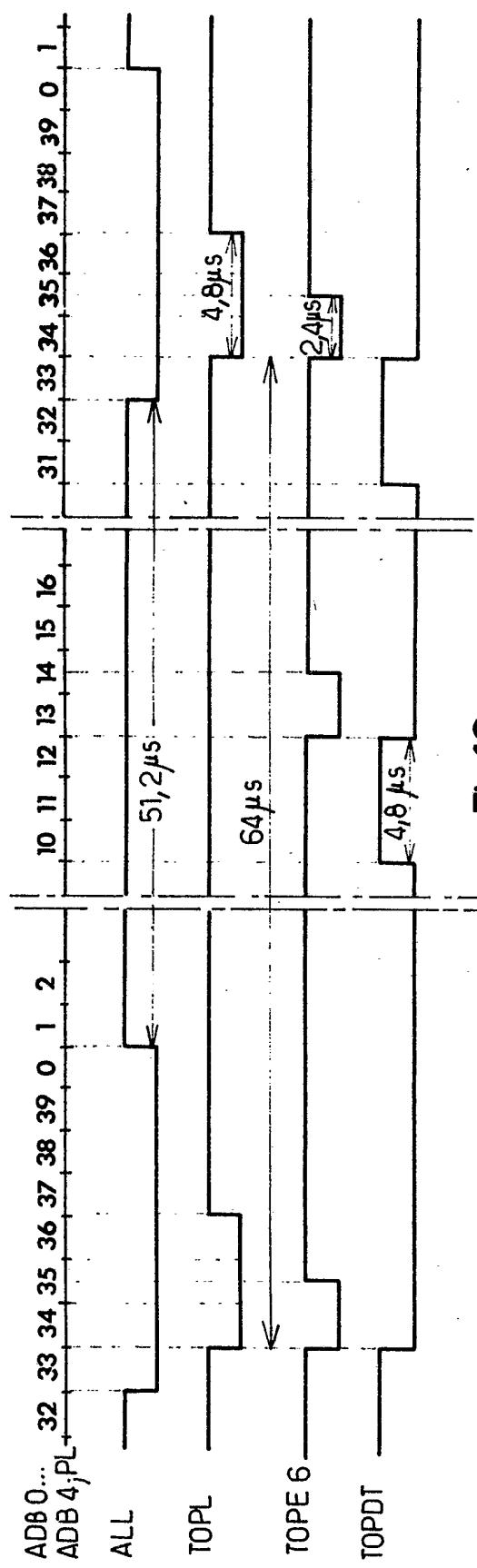

Si l'on considère les sorties ADB0 à PL incluses, on définit quarante états 0 à 39 qui sont représentés à la figure 12, sur la première ligne. Le décodeur 622, avantageusement réalisé à l'aide d'une mémoire programmable, permet la synthèse, à partir de ces états, des signaux complets correspondant à une ligne de télévision :

ALL : allumage de ligne (durée de lecture et d'affichage du contenu de la mémoire d'image sur une ligne)

20 TOP L : top de ligne (signal de période 64  $\mu$ s, ayant des créneaux négatifs de 4,8  $\mu$ s)

TOP EG : top d'égalisation ("pré" et "post" : signal de période 32  $\mu$ s correspondant à une demi-ligne et ayant des créneaux négatifs de 2,4  $\mu$ s)

25 TOP DT : signal de période 32  $\mu$ s, avec des créneaux positifs de 4,8  $\mu$ s.

Ces signaux, représentés à la figure 12, sont appliqués à un multiplexeur 629. Comme on l'expliquera plus loin, celui-ci permet, par leur multiplexage temporel adéquat, la réalisation d'un signal complet de synchronisation (SYNC COMP). Une bascule 630 sert à l'élimination des aléas.

30 Les signaux TOP EG et PL sont appliqués aux entrées respectives CK et D d'une bascule D 623 qui élabore, à sa sortie, un signal carré HLC.

35 Le multiplexeur 629 reçoit deux signaux VALEG et VALDT fournis par un décodeur 624, avantageusement réalisé sous la forme d'une mémoire programmable et recevant sept des sorties (à savoir ADB 6 à ADB 12), d'un compteur binaire 625 fonctionnant en diviseur par 512. Le décodeur 624 fournit en outre une sortie

INVERSION appliquée à une entrée d'une porte ET 632, dont la sortie est appliquée à une entrée d'une porte OU exclusive 631, dont l'autre entrée reçoit le signal HLC. La sortie de la porte 631 est reliée, d'une part à une entrée supplémentaire du décodeur 624, d'autre part, à une entrée d'un diviseur par deux 626 et enfin, à l'entrée d'horloge du compteur 625.

Un signal LOAD T est appliqué à une entrée de chargement du compteur 625 et au compteur 626. Une sortie RAZ du décodeur 624 est reliée à une entrée de remise à zéro du compteur 10 625. La sortie du compteur 626 fournit un signal ADB5 appliquée à l'autre entrée de la porte 632.

Les signaux LOAD L et LOAD T (figures 10 et 11) sont fournis par un circuit externe permettant l'asservissement du générateur de balayage de l'appareil sur un signal extérieur de 15 télévision, par le forçage des compteurs à des valeurs adéquates. Les sorties ADB 5 à ADB 12 constituent la partie "poids forts" 20 des adresses de balayage, l'affichage du contenu de la mémoire ne s'effectuant que sur 256 lignes, qui correspondent aux lignes visibles sur l'écran. Pour la réalisation d'une image de télévision, il est nécessaire d'effectuer une division par 625, correspondant aux deux trames paire et impaire chacune de 312,5 25 lignes. Cette division est obtenue au moyen du compteur 625 qui définit 313 états et dont le circuit d'entrée d'horloge 631 permet, par une inversion adéquate du signal HLC, le comptage de 313 périodes de lignes, suivi du comptage de 312 périodes seulement, bien que, dans les deux cas, le compteur passe par ses 30 313 états. Il suffit, pour cela, d'inverser la phase de HLC, puis de la ramener à la valeur initiale, comme le montre la figure 13, dans laquelle on voit que, sur une durée correspondant par exemple à quatorze impulsions ayant chacune la durée d'une ligne de télévision, l'horloge HL ayant subi le trucage de phase fournit quinze impulsions.

L'inversion de phase commandée par le signal INVERSION du décodeur 624 et par le signal ADB 5 indiquant la présence d'une 35 trame de numéro pair ou impair; le début et la fin du signal INVERSION doivent avoir lieu en dehors de la période d'affichage des lignes utiles et en dehors des impulsions de post et pré-égalisation spécifiques au signal de télévision.

Le signal VALEG correspond dans le temps aux impulsions de pré et post-égalisation, pendant lesquelles le multi-

plexeur 629 transmet à sa sortie le signal TOP EG. Le signal VALDT correspond aux impulsions de trame, pendant lesquelles le multiplexeur 629 transmet à sa sortie le signal TOP DT correspondant à l'impulsion de synchronisation dans la trame.

5 On notera qu'en écrivant différemment les contenus des mémoires programmables 622 et 624 il est possible de réaliser des signaux correspondant à différents standards de télévision.

10 On fera observer par ailleurs que le trucage de phase décrit ci-dessus permet de réaliser le compteur de trame au moyen d'un seul décodeur.

15 Le dispositif de balayage décrit permet le rafraîchissement permanent des mémoires dynamiques qui composent la mémoire d'image et ce, même pendant les durées correspondant aux lignes non visualisées et l'affichage permanent, avec rafraîchissement cyclique de l'image sur l'écran.

20 On voit, à la figure 11, que la dernière sortie du compteur 625 est reliée à une entrée V du décodeur 624. Ceci permet d'activer le décodeur 624 seulement pendant l'affichage de 256 lignes par trame ce qui réduit la taille du décodeur.

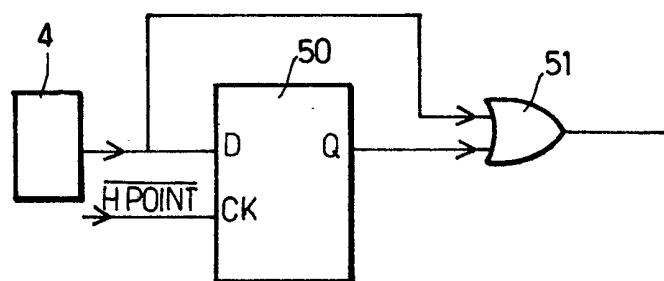

25 A la figure 14, on a représenté un circuit qui permet d'afficher simultanément deux (ou plusieurs) points contigus d'une même ligne en vue de réaliser des traits de largeur variable pour un seul point écrit dans la mémoire. Ce circuit fait partie de l'interface vidéo 5 (figure 1). Il comprend une bascule D 50 qui reçoit, sur une entrée d'horloge, le signal HPOINT déjà défini et, sur une entrée D, le signal provenant du registre vidéo 4 (luminance). Une porte OU 51 fournit à sa sortie une impulsion de largeur doublée.

30 Pour éviter le papillotement d'un trait affiché, chaque point à afficher est allumé simultanément sur la ligne considérée et sur la ligne suivante : chaque point est donc affiché sur une trame paire et impaire. Ce résultat est obtenu par une programmation convenable.

35 On a vu, en se référant à la figure 1, que les informations traversent un tampon 12 avant d'être transmises sur la ligne. La vitesse d'arrivée des informations dans le tampon est beaucoup plus élevée que la vitesse de transmission. Lorsque le microprocesseur donne l'ordre d'effacement de toute la mémoire d'image, celle-ci est effacée presque instantanément localement, 40 mais, à distance, seulement après un délai qui peut être gênant,

par suite de la transmission tardive de l'ordre d'effacement. Pour pallier ce défaut, le programme est agencé pour que, dès qu'un ordre d'effacement d'image est élaboré, il est tout de suite transmis sur la ligne téléphonique, les informations qui 5 le précédent étant annulées.

Il va de soi que diverses modifications pourront être apportées au montage décrit et représenté, sans s'écartez de l'esprit de l'invention.

REVENDICATIONS

1- Dispositif d'affichage et de transmission d'une information graphique engendrée par un appareil d'inscription et de numération automatique d'un tracé qui fournit des données numériques comportant les coordonnées des points successivement tracés manuellement par un opérateur, ledit dispositif comprenant une mémoire destinée à contenir ladite information graphique et des moyens d'affichage de ladite information graphique sur l'écran d'un récepteur de télévision et de transmission de ladite information graphique sur ligne téléphonique, caractérisé en ce que ladite mémoire est organisée pour avoir une capacité suffisante pour contenir l'information graphique correspondant à une image complète de télévision recouvrant tout l'écran d'un récepteur du type grand public, l'adressage de la mémoire étant effectué de manière qu'il existe une correspondance biunivoque entre les emplacements de la mémoire et les points du tracé et que lesdits moyens comprennent un microprocesseur, des interfaces entre le microprocesseur, l'appareil d'inscription et un modem associé à la ligne téléphonique, un organe de balayage apte à engendrer en permanence un signal de télévision dont l'information utile est fournie par lecture de ladite mémoire et des moyens d'interdire l'accès à la mémoire par le microprocesseur pendant des fractions prédéterminées de la durée de chaque ligne de télévision, suffisantes pour que l'accès de la mémoire par l'organe de balayage pendant lesdites fractions permette d'afficher en permanence l'information graphique sur ledit écran sans altération due aux accès du microprocesseur.

2- Dispositif selon la revendication 1, caractérisé en ce que sa capacité d'affichage correspond à 512 lignes de 768 points ou 512 lignes de 512 points.

3- Dispositif selon la revendication 2, caractérisé en ce que ladite mémoire est organisée en au moins un plan comportant trois pages de 16 K octets chacune, les octets 0 à 95 de chaque ligne de télévision étant distribués entre les trois pages, dans l'ordre 0, 3, 6...93 pour la première, 1, 4, 7...94 pour la seconde et 2, 5, 8...95 pour la troisième, l'organe de balayage effectuant la lecture en parallèle de trois octets à la fois dans les trois pages respectives, tandis que le microprocesseur effectue la lecture sélective de la mémoire page par page.

4- Dispositif selon la revendication 3, caractérisé en ce que dans chacune des pages de la mémoire, les lignes de télévision 0 à 511 sont distribuées dans l'ordre 0, 2, 4, 6 - 1, 3, 5, 7 - 8, 10, 12, 14 ..., c'est-à-dire de façon qu'un groupe de quatre lignes de numéros impairs successifs succède toujours à un groupe de quatre lignes de numéros pairs intercalés.

5- Dispositif suivant l'une des revendications 1 à 4, caractérisé en ce que lesdits moyens d'interdire périodiquement l'accès à la mémoire par le microprocesseur comprennent des moyens d'engendrer un premier signal (POUB) formé de créneaux positifs et de créneaux négatifs alternés ayant chacun la durée d'un quatre-vingtième de ligne de télévision, des moyens d'engendrer, à chaque arrivée d'une demande d'accès du processeur à la mémoire, un second signal (MR) qui gèle l'action du microprocesseur jusqu'à l'arrivée du créneau négatif suivant, pendant lequel l'accès à la mémoire sera réservé au microprocesseur et des moyens de lancer un cycle de mémoire (CYMI) dont la disparition entraîne à son tour celle dudit second signal (MR).

6- Dispositif suivant les revendications 4 et 5, caractérisé par des moyens d'engendrer un troisième et un quatrième signal en créneaux dont les fronts montants coïncident avec ceux dudit premier signal POUB et dont les durées sont respectivement égales à 1/4 et 3/8 de la durée des créneaux dudit premier signal, lesdits troisième et quatrième signaux servant respectivement au rafraîchissement des rangées et des colonnes de la mémoire d'image.

7- Dispositif suivant la revendication 3, caractérisé en ce que l'édit organe de balayage comprend, pour la génération d'un premier signal d'horloge (HPOINT) qui permet la sérialisation des trois octets lus en parallèle et d'un second signal d'horloge (HBAL) destiné à définir la cadence des lignes du balayage, une première bascule qui engendre un signal de 15 MHz par division par deux d'une fréquence étalon de 30 MHz, et une deuxième et une troisième bascules montées en cascade, la troisième bascule fournissant un signal de 10 MHz et un circuit logique permettant de réaliser un calage de phase entre les deux signaux à 10 et à 15 MHz.

8- Dispositif suivant l'une des revendications 1 à 7, caractérisé en ce que l'édit organe de balayage comprend : un compteur de ligne agencé pour fournir des signaux d'adresse

correspondant aux cinq premières adresses de poids faibles des octets dans la mémoire d'image ; un premier décodeur associé audit compteur de ligne et agencé pour fournir les signaux d'allumage de ligne (ALL), l'impulsion de ligne (TOPL), l'impulsion d'égalisation (TOP EG) et une impulsion (TOP DT) dans la trame d'une image de télévision; un multiplexeur qui effectue le multiplexage temporel des signaux issus du premier décodeur en vue d'engendrer un signal complet de synchronisation (SYNC COMP); un compteur de trame agencé pour fournir des signaux d'adresse correspondant aux poids forts des adresses de balayage ; un second décodeur associé audit compteur de trame et fournissant audit multiplexeur les signaux (VALEG et VALDT) nécessaires à l'exécution dudit multiplexage temporel et des moyens, associés audit compteur de trame, lequel est agencé pour définir 313 états successifs, en vue de lui permettre d'effectuer une division par 625 correspondant à deux trames, paire et impaire, de 312,5 lignes chacune.

9- Dispositif selon la revendication 8, caractérisé en ce que lesdits moyens associés au compteur de trame effectuent l'inversion de phase de l'entrée d'horloge dudit compteur et, respectivement, le rétablissement de la phase initiale, au début et à la fin d'un signal d'inversion fourni par le second décodeur.

10- Dispositif selon la revendication 9, caractérisé en ce que le compteur de trame et le second décodeur sont agencés pour que ce dernier ne soit actif que pour l'affichage de 256 lignes utiles par trame et que ledit début et ladite fin du signal d'inversion interviennent en dehors de la période d'affichage des lignes utiles et en dehors desdites impulsions d'égalisation.

11- Dispositif selon l'une des revendications 8 à 10, caractérisé en ce que lesdits premier et second décodeurs sont réalisés au moyen de mémoires programmables.

12- Dispositif selon l'une des revendications 1 à 11, caractérisé par des moyens d'afficher simultanément au moins deux points contigus d'une même ligne pour un seul point écrit dans la mémoire et d'allumer simultanément chaque point à afficher sur la ligne considérée et sur la ligne suivante.

13- Dispositif selon l'une des revendications 1 à 12, caractérisé par une mémoire tampon intercalée entre le micro-

processeur et l'interface de modem et par des moyens, lorsque le microprocesseur donne l'ordre d'effacement de toute la mémoire d'image, d'assurer la transmission immédiate dudit ordre sur la ligne téléphonique et l'annulation de toutes les informations qui le précèdent dans la mémoire tampon.

14- Dispositif selon l'une des revendications 1 à 13, caractérisé par des moyens d'effectuer une certaine sélection des points dont les coordonnées seront effectivement transmises sur la ligne téléphonique, en vue du compactage de l'information graphique et par des moyens, intercalés entre le microprocesseur et l'interface de modem, d'invalider l'information graphique reçue sur la ligne téléphonique lorsque sa structure n'est pas conforme à celle qui doit normalement résulter dudit compactage, lesdits moyens d'invalidation étant agencés pour que l'information ne soit plus affichée jusqu'à l'arrivée d'une information codée correspondant à une fin de trait.

PL. 1/9

2463555

PL. 2/9

Fig. 2

Fig. 6

PL. 3/9

Fig.3

2463555

PL.4/9

Fig.4

Fig.5

PL. 5/9

Fig. 7

2463555

PL. 7/9

Fig. 10

Fig. 14

2463555

Fig. 11

Fig.12

Fig.13