(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년12월26일

(11) 등록번호 10-0875731

(24) 등록일자 2008년12월17일

(51) Int. Cl.

H01F 27/24 (2006.01) H01F 27/28 (2006.01)

H01F 5/00 (2006.01)

(21) 출원번호 10-2006-0058329

(22) 출원일자 2006년06월27일

심사청구일자 2007년04월06일

(65) 공개번호 10-2007-0001010

(43) 공개일자 2007년01월03일

(30) 우선권주장

JP-P-2005-00188370 2005년06월28일 일본(JP)

(56) 선행기술조사문현

KR1019960032520 A

KR1020050034177 A

KR1020030007390 A

US0576405 A

전체 청구항 수 : 총 8 항

심사관 : 박근용

(54) 자성 소자

### (57) 요 약

실장 기판에 대한 소자의 배치 면적을 작게 하여 고밀도 실장을 달성할 수 있는 자성 소자를 제공하기 위한 것이다.

코일(6)과, 평판부(2a, 3a)에 외각부(外却部)(2b, 3b)와 상기 코일(6)에 삽입되는 중 각부(2c, 3c)를 가지는 제 1 코어(2) 및 제 2 코어(3)와, 상기 제 1 코어(2)와 상기 제 2 코어(3)와의 사이에 상기 제 1 코어(2) 및 상기 제 2 코어(3)와 연접(連接)하도록 배치된 폐자로(閉磁路) 회로를 구성하는 중간 코어(4)를 가지는 자성 소자(1)에 있어서, 상기 제 1 코어(2) 중각부(2c)의 상기 외각부(2b)가 연장되는 방향과 수직 방향의 단면적을 S1로 하고, 상기 중간 코어(4)의 상기 외각부(2b, 3b)가 연장되는 방향과 평행 방향의 단면적을 S2로 하고, 상기 제 2 코어(3) 중각부(3c)의 상기 외각부(3b)가 연장되는 방향과 수직 방향의 단면적을 S3으로 했을 때에,  $S1 \leq S3$ 이며, 동시에  $S1 \leq S2$ 의 관계를 가지는 구조으로 한다.

### 대 표 도

## 특허청구의 범위

### 청구항 1

코일과,

평판부에 외각부와 상기 코일에 삽입되는 중각부를 가지는 제 1 코어 및 제 2 코어와,

상기 제 1 코어와 상기 제 2 코어와의 사이에, 상기 제 1 코어 및 상기 제 2 코어와 연접하도록 배치된 폐자로 회로를 구성하는 중간 코어를 가지는 자성 소자에 있어서,

상기 제 1 코어의 중각부의 상기 외각부가 연장되는 방향과 수직 방향의 단면적을 S1로 하고,

상기 중간 코어의 상기 외각부가 연장되는 방향과 평행 방향의 단면적을 S2로 하고,

상기 제 2 코어의 중각부의 상기 외각부가 연장되는 방향과 수직 방향의 단면적을 S3로 했을 때에,

$S1 \leq S3$ 이며, 한편  $S1 \leq S2$ 의 관계인 것을 특징으로 하는 자성 소자.

### 청구항 2

제 1항에 있어서,

상기 중간 코어와 상기 중각부의 선단부와의 사이에 캡을 가지고 있는 것을 특징으로 하는 자성 소자.

### 청구항 3

제 2항에 있어서,

상기 캡은 스페이스를 두는 것에 의하여 구성되는 것을 특징으로 하는 자성 소자.

### 청구항 4

제 2항에 있어서,

상기 캡을 설치하는 대신에 중간 코어의 실효투자율을 제 1 코어 및 제 2 코어보다 낮게 설정하는 것에 의해 실질적인 캡을 설치하는 것을 특징으로 하는 자성 소자.

### 청구항 5

제 1항에 있어서,

지지 베이스는, 상기 제 1 코어, 상기 제 2 코어 및 상기 제 1 코어의 깊이 방향(짧은 측)내의 중간 코어에 형성된 두 개의 표면들중 제 1의 표면과, 상기 제 2 코어 및 상기 중간 코어를 따라 설치되며,

상기 지지 베이스에는, 실장기판(도시 안됨)에 실장되는 단자부재가 설치되는 것을 특징으로 하는 자성 소자.

### 청구항 6

제 1항에 있어서,

자기 실드판은, 상기 제 1 코어, 상기 제 2 코어 및 상기 제 1 코어의 깊이 방향(짧은 측)내의 중간 코어에 형성된 두 개의 표면들중 제 1의 표면과, 상기 제 2 코어 및 상기 중간 코어를 따라 설치되어, 자기가 누설되는 것을 방지하는 것을 특징으로 하는 자성 소자.

### 청구항 7

제 6항에 있어서,

상기 자기실드판은, 수지와 자성분이 혼합되어 있는 부재로 구성되어 있는 것을 특징으로 하는 자성소자.

### 청구항 8

제 1항에 있어서,

상기 코일은 평각선의 엣지 와이즈 권회 코일인 것을 특징으로 하는 자성 소자.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

##### 발명이 속하는 기술 및 그 분야의 종래기술

<23> 본 발명은 자성 소자에 관한 것으로, 특히 전원 용도에 이용되는 인덕턴스 소자에 관한 것이다.

<24> 근년, 고밀도 실장이나 다층 배열의 기판 구성 등에 의한 자성 소자의 소형화가 강하게 요구되고 있는 것과 동시에, 제품의 저비용화가 강하게 요구되고 있다.

<25> 종래의 자성 소자의 형태로서는, 페라이트 자성 코어로 이루어지는 차양부착 코어 및 링형 코어를 조합한 구성을 채용한 것이 알려져 있다(예를 들면, 일본특허 특개 2002-313635호 참조).

<26> 또한 이른바 E형 코어와 I형 코어를 조합한 자성 소자도 알려져 있다.

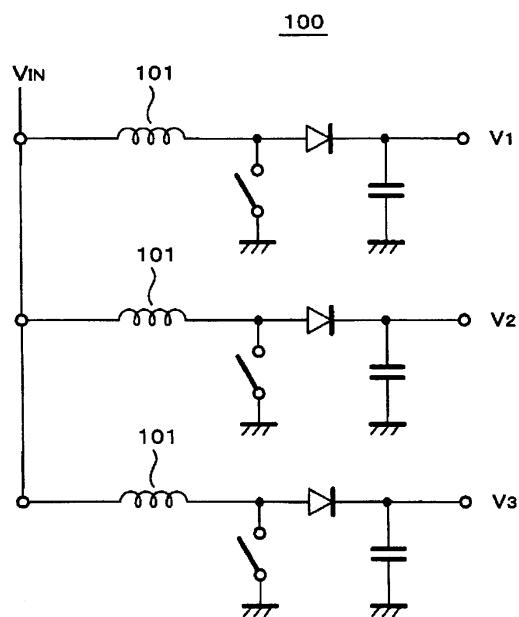

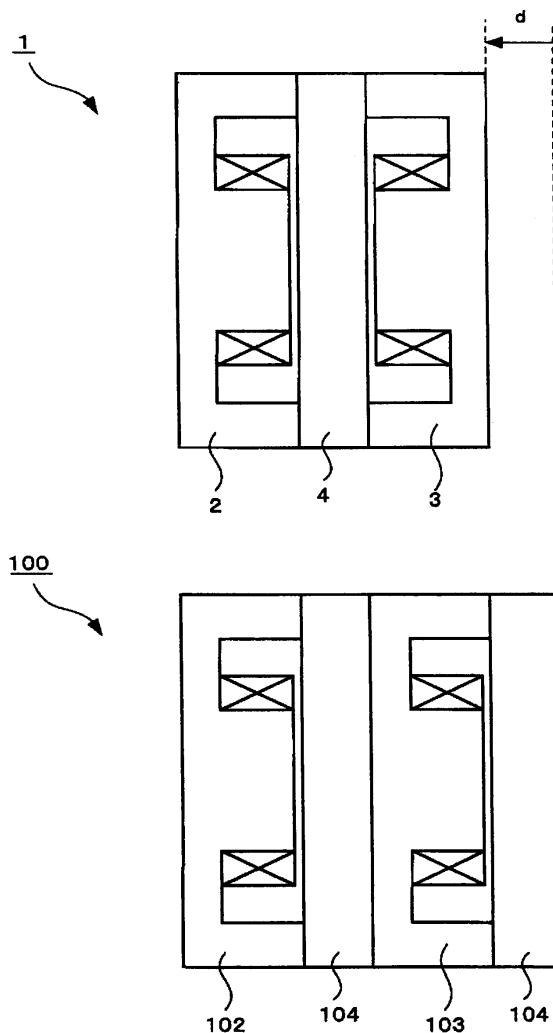

<27> 게다가, 도 8에 나타내는 바와 같이, 전기특성 또는 형상이 동일 또는 유사한 자성 소자(예를 들면, 인덕턴스 소자)(101)를, 실장 기판상에 복수 개 배치하는 회로 구성(100)이 알려져 있다.

##### 발명이 이루고자 하는 기술적 과제

<28> 그렇지만, 도 8에 나타내는 바와 같이, 전기특성 또는 형상이 동일 또는 유사한 복수의 인덕턴스 소자(101)를 실장 기판상에 배치하는 경우에는, 실장 기판상에 그 인덕턴스 소자의 배치 면적에 따른 실장 스페이스를 확보하는 것이 필요하여 실장 기판이 대형이 된다고 하는 문제가 생긴다.

<29> 게다가 인덕턴스 소자에 한정하지 않고, 실장 기판에 실장되는 실장 소자는 실장 작업 중에 있어서의 소자의 파손을 방지하기 위해서 인접하는 실장 소자와 적당 간격을 비울 필요가 있고, 근년의 고밀도 실장의 요구를 높은 수준으로 만족시키기 위해서는, 실장되는 인덕턴스 소자의 배치 면적을 한층 더 작게 해야 한다고 하는 문제가 생긴다.

<30> 본 발명은, 상술의 점을 고려하여 실장 기판에 대한 배치 면적을 작게 한 자성 소자를 제공하는 것이다.

#### 발명의 구성 및 작용

<31> 본 발명과 관련되는 자성 소자는, 코일과, 평판부에 외각부(外却部)와 상기 코일에 삽입되는 중각부를 가지는 제 1 코어 및 제 2 코어와, 상기 제 1 코어와 상기 제 2 코어와의 사이에 상기 제 1 코어 및 상기 제 2 코어와 연접(連接)하도록 배치된 폐자로(閉磁路) 회로를 구성하는 중간 코어를 가지는 자성 소자에 있어서, 상기 제 1 코어 중각부의 상기 외각부가 연장되는 방향과 수직 방향의 단면적을 S1로 하고, 상기 중간 코어의 상기 외각부가 연장되는 방향과 평행 방향의 단면적을 S2로 하고, 상기 제 2 코어 중각부의 상기 외각부가 연장되는 방향과 수직 방향의 단면적을 S3으로 했을 때에,  $S1 \leq S3$ 이며, 동시에  $S1 \leq S2$ 의 관계를 가지는 구성으로 한다.

<32> 바람직하게는, 본 발명과 관련되는 자성 소자는 상기 중간 코어와 상기 중각부의 선단부와의 사이에 캡을 가지고 있는 것이 적당하다.

<33> 한층 더 바람직하게는, 본 발명과 관련되는 자성 소자의 상기 코일은, 평각선(平角線)의 엣지와이즈 권회(edgewise winding) 코일인 것이 적당하다.

<34> 이상과 같이, 본 발명과 관련되는 자성 소자는, 복수의 코일로부터 생기는 자속을 흘리는 공통의 코어를 이용하여 실장 기판에 대한 자성 소자의 배치 면적을 작게 한다.

<35> (실시예)

<36> 이하, 본 발명을 실시하기 위한 최선의 형태의 예에 대해 도면을 참조해 설명하지만, 본 발명은 이하의 예에 한정되는 것은 아니다.

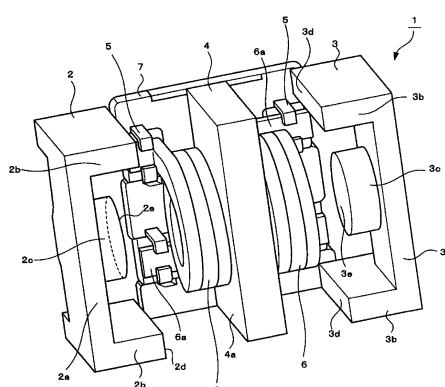

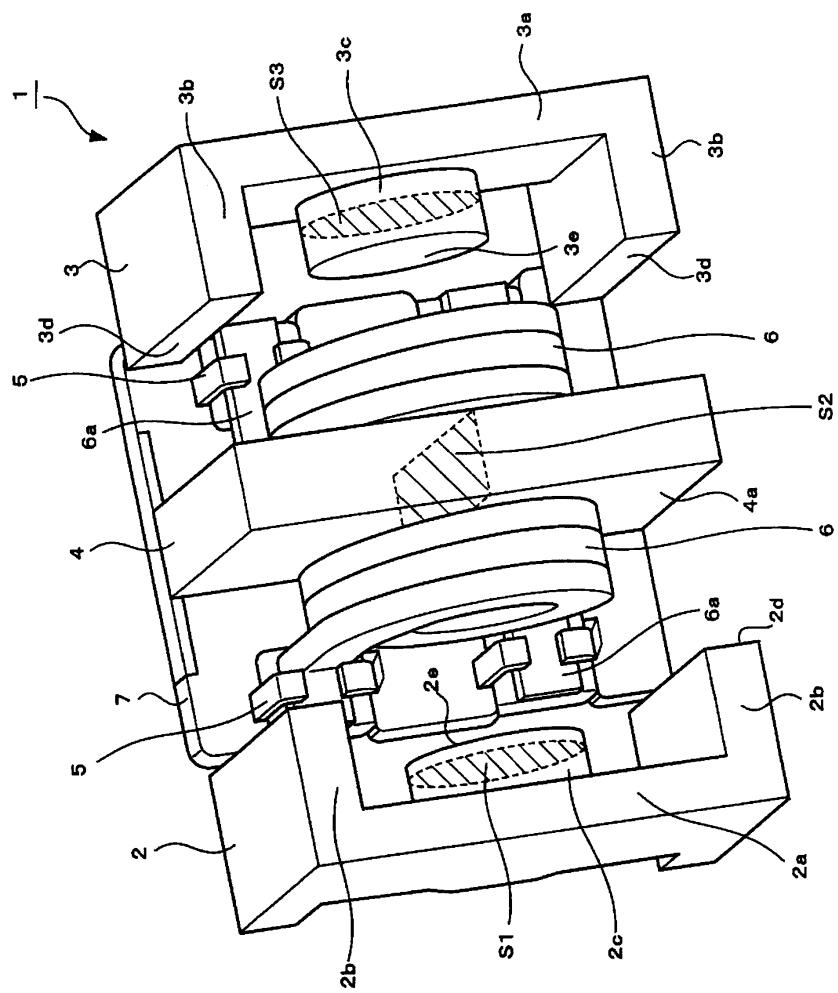

<37> 도 1은 본 발명에 의한 자성 소자의 분해 사시도이다.

<38> 도 1에 나타나듯이, 자성 소자로서의 인덕턴스 소자(1)는 제 1 코어(2)와 제 2 코어(3)와 중간 코어(4)와 단자 부재(5)와 코일(6)과 지지 베이스(7)로 구성되어 있다.

<39> 제 1 코어(2)는 구형(矩形) 모양의 평판(2a)과, 평판(2a)의 양단부에 형성된 외각(2b)과, 평판(2a)의 중앙부 부근에 설치된 중각(2c)으로 이루어져 있다.

<40> 평판(2a)의 짧은 방향에 있어서의 한편의 단부에는 인덕턴스 소자(1)가 완성되었을 때에 코일(6)의 단부(6a)를 분리하기 위한 절결부(2f)(도 2 참조)가 형성되어 있다.

<41> 평판(2a)의 긴 방향의 양단부에는, 평판(2a)에 대해서 수직 방향으로 연장되는 방향으로 외각(2b)이 형성되어 있고, 외각(2b)의 선단부에는 평판(2a)과 평행한 평면을 가지는 선단면(2d)이 형성되어 있다.

<42> 평판(2a)의 대략 중앙 부근에는 외각(2b)이 연장되는 방향과 같은 방향으로 연장되는 원주 모양의 중각(2c)이 형성되어 있고, 중각(2c)의 선단부에는 평판(2a)과 평행한 평면을 가지는 선단면(2e)이 형성되어 있다. 또, 중각(2c)의 길이는 중각의 선단면(2e)과 중간 코어(4)와의 사이에 캡을 형성하기 위하여 외각(2b)의 길이보다 짧게 되도록 설정되어 있다.

<43> 덧붙여 본 예에 있어서는 중각(2c)의 형상을 원주형으로 했지만, 중각(2c)의 형상은 이것으로 한정되는 것이 아니라, 예를 들면 구형(矩形) 모양의 것이어도 좋다.

<44> 제 1 코어(2)와 마찬가지로, 제 2 코어(3)는 구형(矩形) 모양의 평판부(3a)와, 평판부(3a)의 양단부에 형성된 외각(3b)과, 평판(3a)의 중앙부 부근에 설치된 중각(3c)으로 구성되어 있다.

<45> 또한, 제 2 코어(3)는 제 1 코어(2)와 동일한 구조를 가지도록 성형되어 있다.

<46> 평판(3a)의 긴 방향의 양단부에는 평판(3a)에 대해서 수직 방향으로 연장되는 방향에 외각(3b)이 형성되어 있고, 외각(3b)의 선단부에는 평판(3a)과 평행한 평면을 가지는 선단면(3d)이 형성되어 있다.

<47> 평판(3a)의 대략 중앙 부근에는 외각(3b)이 연장되는 방향과 같은 방향으로 연장되는 원주 모양의 중각(3c)이 형성되어 있고, 중각(3c)의 선단부에는 평판(3a)과 평행한 평면을 가지는 선단면(3e)이 형성되어 있다. 또한, 중각(3c)의 길이는 중각의 선단면(3e)과 중간 코어(4)와의 사이에 캡을 형성하기 위하여 외각(3b)의 길이보다 짧게 되도록 설정되어 있다.

<48> 덧붙여 본 예에서는 제 1 코어(2)와 제 2 코어(3)는 동일한 구조를 가지도록 형성했지만, 제 1 코어(2)와 제 2 코어(3)의 구조는 이것으로 한정되는 것이 아니라, 서로 다른 구조로 성형되어도 좋다.

<49> 또한, 제 1 코어(2) 및 제 2 코어(3)는 Mn-Zn계 페라이트를 이용한 자성 재료로 형성되어 있다.

<50> 중간 코어(4)는 구형(矩形) 모양의 평판으로 구성되어 있고, 제 1 코어(2)의 외각(2b)에 형성된 선단면(2d), 중각(2c)에 형성된 선단면(2e) 및 제 2 코어(3)의 외각(3b)에 형성된 선단면(3d), 중각(3c)에 형성된 선단면(3e)과 대향하는 평면(4a)을 가지고 있다. 또한, 중간 코어(4)는 중간 코어(4)의 긴 방향의 길이와 제 1 코어(2) 및 제 2 코어(3)의 긴 방향의 길이가 같게 되도록 형성되어 있다.

<51> 게다가 중간 코어(4)는 중간 코어(4)의 짧은 방향의 길이와 제 1 코어(2) 및 제 2 코어(3)의 짧은 방향의 길이가 같게 되도록 형성되어 있다.

<52> 덧붙여 중간 코어(4)는 Mn-Zn계 페라이트를 이용한 재료로 형성되며, 예를 들면 금형 프레스에 의해서 구형(矩形) 모양으로 프레스하여 성형된다.

<53> 코일(6)은 평각선의 엣지와이즈 권회 코일로, 공심을 가지도록 성형되어 있다.

<54> 즉, 절연층을 피복 한 평각선을 엣지와이즈로 권회함으로써 성형되어 있다.

<55> 또한, 코일(6)에는 인덕턴스 소자(1)가 실장되는 실장 기판으로부터 공급되는 전류를 코일에 흘리기 위한 코일 단부(6a)가 형성되어 있다.

<56> 지지 베이스(7)는 대략 정방형의 형상을 가지는 평판 모양의 부재로 성형되어 있다.

<57> 또한, 지지 베이스(7)에는 코일(6)의 단부(6a)를 보유하기 위해 지지부를 가지는 단자 부재(5)가 장착되어 있고, 지지 베이스(7)의 실장 기판에 실장되는 측에, 단자 부재(5)의 일부가 노출하도록 형성되어 있다.

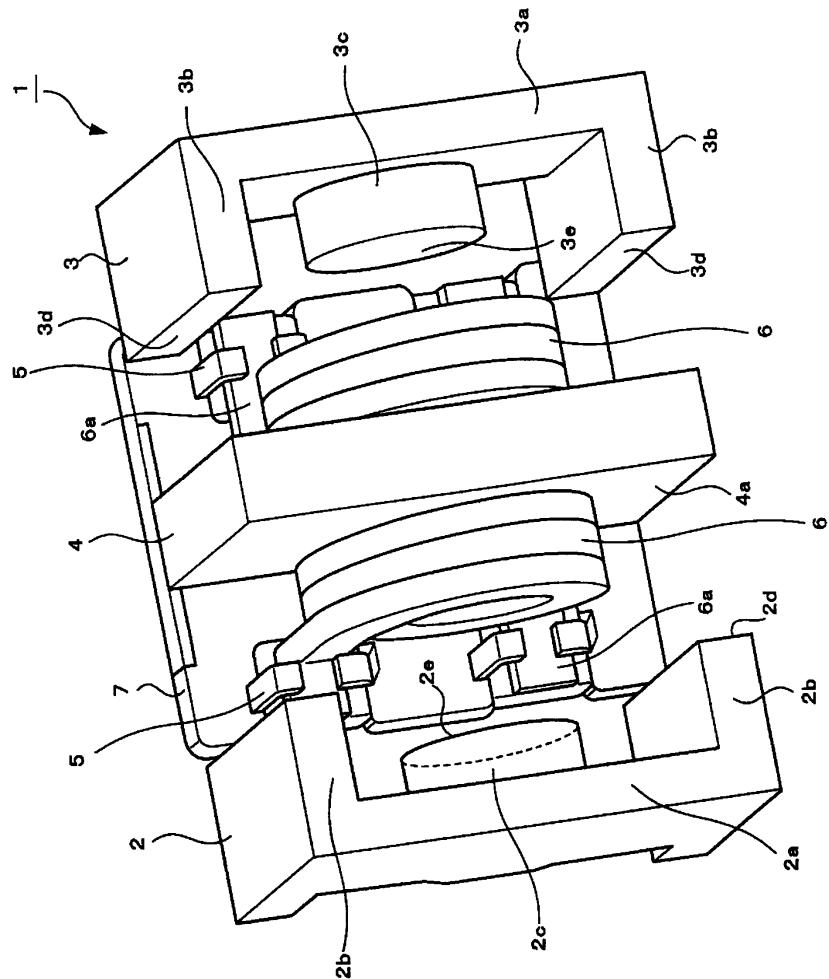

<58> 도 2는 본 발명에 의한 자성 소자의 사시도이다.

<59> 도 2에 나타나듯이, 구성된 인덕턴스 소자(1)에는 제 1 코어(2)의 외각(2b) 및 중각(2c)과 제 2 코어(3)의 외각(3b) 및 중각(3c)이 중간 코어(4)를 사이에 두고 서로 마주보도록 제 1 코어(2) 및 제 2 코어(3)가 배치되어 있다.

<60> 또한, 중간 코어(4)와 제 1 코어(2)의 평판(2a)과의 사이에는 코일(6)이 배치되어 있다.

<61> 이 때, 코일(6)의 공심에는 제 1 코어(2)의 중각(2c)이 삽입되어 있다.

<62> 동시에, 중간 코어(4)와 제 2 코어(3)의 평판(3a)과의 사이에도 코일(6)이 배치되어 있고, 코일의 공심에는 중각(3c)이 삽입되어 있다.

<63> 즉, 인덕턴스 소자(1)에 있어서는 제 1 코어(2)와 제 2 코어(3)와 중간 코어(4)에 의해서 폐자로 회로가 형성되어 있다.

<64> 한층 더 상세하게 말하면, 제 1 코어(2)가 가지는 중각(2c), 평판(2a), 외각(2b)과, 중간 코어(4)와, 후술하는 캡(g) 및 제 2 코어(3)가 가지는 중각(3c), 평판(3a), 외각(3b)과 중간 코어(4)와 후술하는 캡(g)으로 폐자로 회로가 형성되어 있다.

<65> 인덕턴스 소자(1)에 있어서는 제 1 코어의 외각(2b)의 선단면(2d) 및 제 2 코어의 외각(3b)의 선단면(3d)과 중간 코어(4)의 평면(4a)이 합침하도록 제 1 코어(2) 및 제 2 코어(3)와 중간 코어(4)가 구성되어 있다.

<66> 본 예에서는, 제 1 코어(2)의 평판(2a) 및 제 2 코어(3)의 평판(3a)의 짧은 방향의 길이와 중간 코어(4)의 짧은 방향의 길이가 같게 되도록 제 1 코어(2), 제 2 코어(3) 및 중간 코어(4)가 형성되어 있기 때문에, 제 1 코어(2), 제 2 코어(3) 및 중간 코어(4)가 조립된 때에는 짧은 방향에 대해 상하로 두 개의 평면이 형성된다.

<67> 이 두 개의 평면 가운데 제 1 코어(2)의 절결부(2f), 제 2 코어(3)의 절결부(3f)가 설치되어 있는 측에 형성되는 평면에 대해서 지지 베이스(7)가 장착되어 있다.

<68> 지지 베이스(7)에는, 4개의 단자 부재(5)가 장착되어 있고, 이 단자 부재(5)는 코일(6)이 중각(2c, 3c)에 삽입된 상태를 유지하면서 코일의 단부(6a)를 보유하고 있다.

<69> 또, 코일의 단부(6a)는 평판(2a)의 절결부(2f), 평판(3a)의 절결부(3f)에 대해서 형성된 공간에 위치하도록 배치되어 있다.

<70> 덧붙여 제 1 코어(2), 제 2 코어(3)와 중간 코어(4)를 조립할 때는, 외각(2b)의 선단면(2d) 및 외각(3b)의 선단면(3d)과 그 면에 대응하는 중간 코어의 평면(4a)에 접착제를 도포해 고정한다.

<71> 조립된 인덕턴스 소자(1)는 납땜에 대해서 지지 베이스(7)의 뒤편에 노출해 있는 단자 부재(5)와 실장 기판(도시하지 않음)과의 접촉이 유지된 상태로 실장 기판에 실장된다. 이것에 의해, 실장 기판으로부터 공급되는 전류는 단자 부재(5)를 통하여 인덕턴스 소자(1)에 공급된다.

<72> 본 예의 인덕턴스 소자(1)에 의하면, 제 1 코어(2), 제 2 코어(3) 및 중간 코어(4)와도 간소한 구성으로 성형되어 있으므로, 인덕턴스 소자의 제조를 용이하게 할 수 있다.

<73> 또, 도 5에 나타나듯이, 본 예의 인덕턴스 소자(1)와 인덕턴스 소자(101)를 2개 밀접한 종래의 구성과 비교하면, 길이 d 만큼 본 예의 인덕턴스 소자(1)의 배치 면적을 작게 할 수 있다.

<74> 즉, 본 예의 인덕턴스 소자(1)에 의하면, 종래 2개 이용하던 인덕턴스 소자(101)를 1개로 정리하는 것으로, 인덕턴스 소자 자체의 실장 기판에 대한 배치 면적을 작게 할 수 있다.

<75> 게다가 본 예의 인덕턴스 소자(1)는 자기 결합을 갖게 하지 않고, 1개의 소자 중에 2개의 코일(6)을 설치할 수 있다.

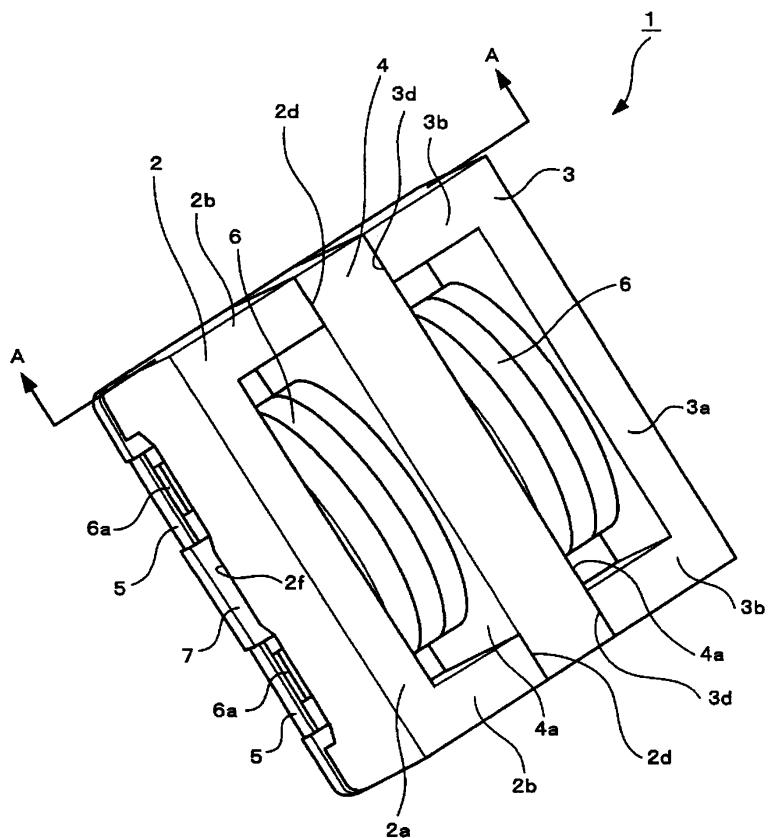

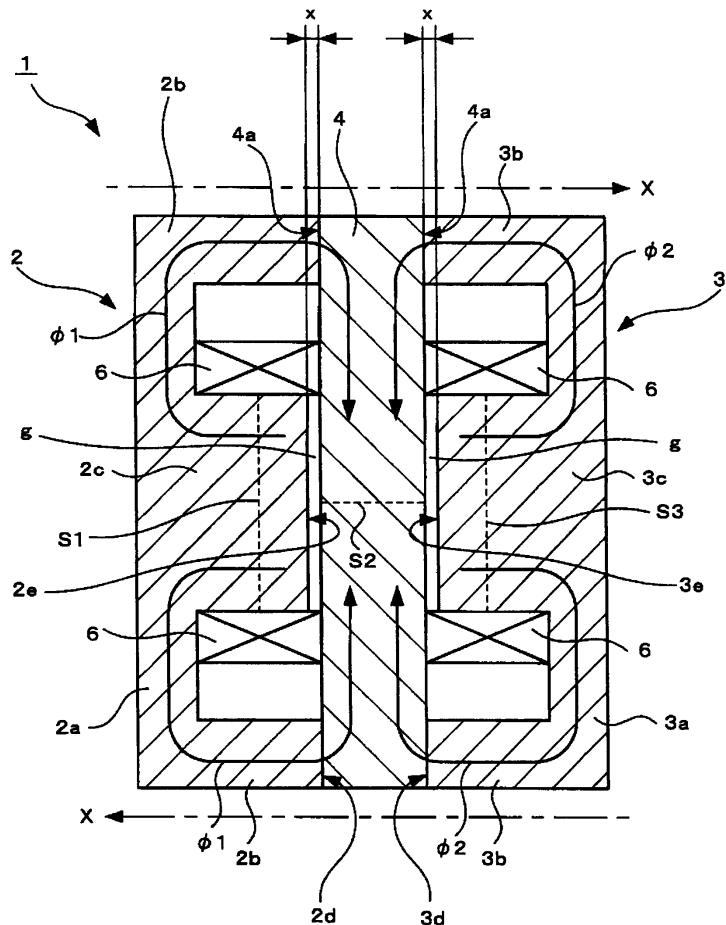

<76> 도 3은 본 발명에 의한 자성 소자의 도 2에 나타낸 A-A선상의 개략 단면도이다.

<77> 도 3에 나타나듯이, 코일(6)의 공심에는 각각 제 1 코어(2)의 중각(2c)과 제 2 코어(3)의 중각(3c)이 삽입되어 있다.

<78> 중각(2c)의 선단면(2e)과 중간 코어의 평면(4a)과의 사이 및 중각(3c)의 선단면(3e)과 중간 코어의 평면(4a)과의 사이에는 각각 간격X로 캡(g)이 형성되어 있다.

<79> 덧붙여 그 밖에 자로 중에 갭을 마련하는 방법으로서는 중간 코어(4)와 제 1 코어(2) 및 제 2 코어(3)와의 사이에 갭 형성용의 스페이서 부재를 배치함으로써 갭을 설치하도록 해도 괜찮다.

<80> 또한, 다른 방법으로는, 중간 코어(4)의 실효 투자율을 제 1 코어(2), 제 2 코어(3)의 실효 투자율보다 낮게 설정함으로써 실질적으로 갭으로서의 작용을 나타낼 수 있다.

<81> 덧붙여 그 방법을 이용하는 경우에는 투자율의 낮은 자성 재료를 이용하거나 수지와 자기성분을 혼합한 것을 코어재로 하거나 여러 가지 변경이 가능하다.

<82> 본 예의 인덕턴스 소자(1)에 의하면, 인덕턴스 소자를 대전류를 흘리는 전원 용도로서 이용하는 경우에 있어서도, 제 1 코어(2)와 중간 코어(4)와의 사이 및 제 2 코어(3)와 중간 코어(4)와의 사이에 갭(g)을 가지고 있으므로, 외각(2b), 외각(3b)과 중간 코어(4)와의 사이에 다시 갭을 마련할 필요가 없이 제 1 코어(2) 및 제 2 코어(3)와 중간 코어(4)와의 조립 강도를 유지한 채로 인덕턴스 소자(1)에 대전류를 흘릴 수 있다.

<83> 또, 본 예의 인덕턴스 소자(1)에 의하면, 코일(6)로서 평각선의 엣지 와이즈 권회 코일을 이용하고 있으므로, 코일의 단면적이 커져서 저항을 낮게 할 수 있고, 또한 코일에 불필요한 틈새가 없어지므로, 인덕턴스 소자를 소형으로 할 수 있다.

<84> 코일(6)에 전류를 흘리면, 도 3에 있어서 실선으로 표시한 화살표 방향으로, 제 1 코어(2)의 중각(2c), 평판(2a), 외각(2b)과 중간 코어(4)를 관통하는 자속 ( $\phi 1$ ) 및 제 2 코어(3)의 중각(3c), 평판(3a), 외각(3b)과 중간 코어(4)를 관통하는 자속( $\phi 2$ )이 발생한다.

<85> 또한, 폐자로 중에 발생하는 자속 ( $\phi 1$ ,  $\phi 2$ )의 방향은 코일(6)에 인가하는 전류의 종류나 코일이 감겨지는 방향에 의해서 변화한다.

<86> 여기서, 제 1 코어(2)의 중각(2c)에 있어서 외각(2b)이 연장되는 방향과 수직 방향의 단면적을 S1로 하고, 중간 코어(4)에 있어서 외각(2b, 3b)이 연장되는 방향과 평행 방향의 단면적 S2로 하고, 제 2 코어(3)의 중각(3c)에 있어서 외각(3b)이 연장되는 방향과 수직 방향의 단면적을 S3로 각각 정의한다.

<87> 또한, 도 3에 있어서 일점체선으로 나타난 화살표(X)는, 제 1 코어(2)에 설치된 외각(2b) 및 제 2 코어(3)에 설치된 외각(3b)이 연장되는 방향을 나타내고 있다.

<88> 도 4는 본 발명에 의한 자성 소자의 분해 사시도이며, 도 3에 나타낸 단면적 S1, S2, S3를 사시적으로 나타낸 것이다.

<89> 또한, 도 4에 있어서, 도 1과 대응하는 부분에는 동일 부호를 교부해 설명을 생략한다.

<90> 도 4에 나타나듯이, 제 1 코어(2)의 중각(2c)에 있어서의 단면적 (S1)은 중각(2c)의 선단면(2e)과 같은 면적을 가지고 있고, 마찬가지로 제 2 코어(3)의 중각(3c)에 있어서의 단면적 (S3)은 중각(3c)의 선단면(3e)과 같은 면적을 가지고 있다.

<91> 본 예에서는, 단면적 (S1)과 단면적 (S3)은 같은 면적을 가지고 형성되어 있지만, 예를 들면, 단면적 (S3)이 단면적 (S1)보다 커지도록 중각(2c), 중각(3c)을 형성해도 좋다.

<92> 중간 코어(4)에 있어서의 단면적 (S2)은 중간 코어(4)의 긴 방향의 중앙부에 있어서의 단면적이다.

<93> 또한, 중간 코어(4)의 형상이 본 예와 같이 균일 단면적을 가지는 형상이 아닌 경우에는, 두 개의 코일(6)의 공심의 중심점을 묶은 선으로 중간 코어(4)를 평행 방향으로 절단했을 때에 가능한 단면적을 S2로 한다.

<94> 본 예의 인덕턴스 소자(1)에 의하면, 제 1 코어(2)의 중각(2c)의 단면적을 S1, 제 2 코어(3)의 중각(3c)의 단면적을 S3로 하고, 중간 코어(4)의 단면적을 S2로 했을 때에,  $S1 \leq S3$ 이며, 한편  $S1 \leq S2$ 라고 규정하고 있으므로, 여러 가지의 용도에 대해서, 제 1 코어(2), 제 2 코어(3) 및 중간 코어(4)의 종합적인 자기 포화에 있어서의 균형을 유지할 수 있다.

<95> 또,  $S1 \leq S3$ 이며  $S1=S2$ 인 경우는, 제 1 코어(2)의 코일(6) 또는 제 2 코어(3)의 코일(6)의 어느 쪽이든 한편의 코일에 대해서 전류를 인가하는 경우에, 자기 포화를 일으키게 하지 않고, 또, 인덕턴스 소자(1)의 배치 면적을 작게 할 수 있다.

<96> 게다가  $S2=S1+S3$ 의 경우에는, 제 1 코어(2) 및 제 2 코어(3)의 코일(6)에 동시에 전류를 흘려서 2개의 인덕터를 동작시킬 수 있다.

또한,  $S1 \leq S3$ 이며  $S1 > S2$ 인 경우는, 중간 코어(4)의 단면적 ( $S2$ )은 실질적으로 제 1 코어(2)의 중각(2c)의 단면적 ( $S1$ )보다 작아지기 때문에, 적어도 한편의 코일(6)에 과전류가 인가되면, 먼저 중간 코어(4)에 자기 포화가 생기게 되어, 인덕턴스 소자(1)의 전기적 특성(대표적으로는 인덕턴스 $\chi$ )의 급격한 저하를 불러올 우려가 있다.

또, 중간 코어(4)의 단면적 S2가 작아지기 때문에, 인더티스 소자(1)의 기계 강도·강성이 저하될 우려가 있다.

이상의 고찰에 의해, 본 예의 인덕턴스 소자(1)에 있어서는, 제 1 코어(2)의 중각(2c)의 단면적을  $S_1$ , 중간 코어(4)의 단면적을  $S_2$ , 제 2 코어의 중각(3c)의 단면적을  $S_3$ 로 했을 때에,  $S_1 \leq S_3$ 이며, 한편  $S_1 \leq S_2$ 의 관계가 되도록 구성한 것이다.

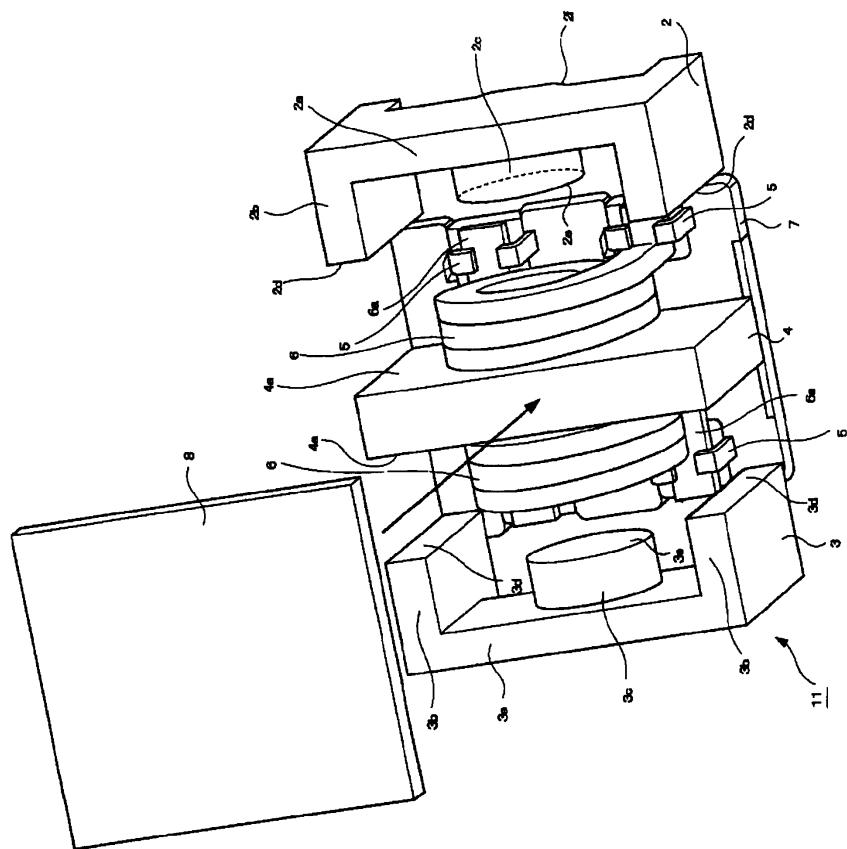

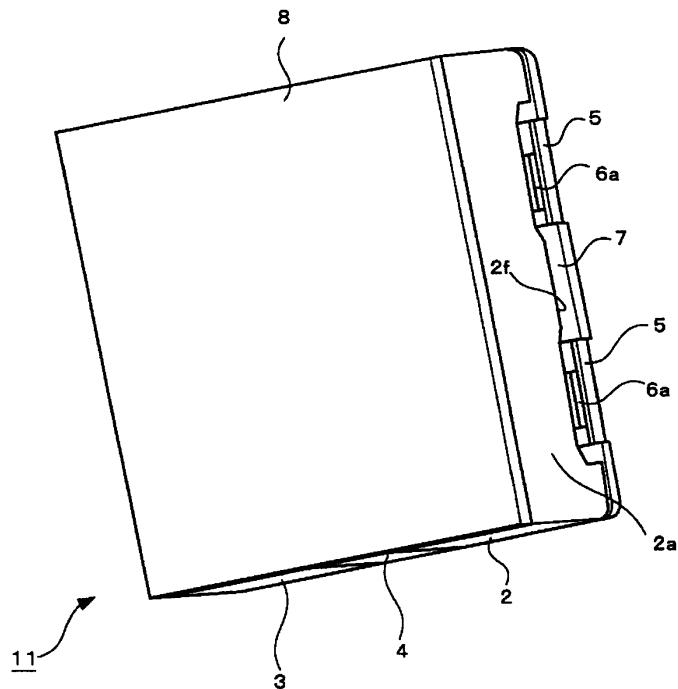

도 6은 본 발명에 의한 자성 소자의 다른 형태 예의 분해 사시도이다.

또한, 도 6에 있어서 도 1과 대응하는 부분에는 동일 부호를 교부해 중복 설명을 생략한다.

도 6에 나타나듯이, 본 예의 인더턴스 소자(11)에 있어서는, 제 1 코어(2), 제 2 코어(3) 및 중간 코어(4)의 위쪽에 자기 실드판(8)이 설치되어 있다.

자기 실드판(8)은 예를 들면, 고투자율의 자성판, 수지와 자성분(磁性粉)을 혼합한 판상 부재로 형성된다.

도 7은 본 발명에 의한 자성 소자의 다른 형태 예의 사시도이다.

또한, 도 7에 있어서, 도 1과 대응하는 부분에는 동일 부호를 교부해 중복 설명을 생략한다.

도 7에 나타나듯이, 본 예의 인더턴스 소자(11)에서는 제 1 코어(2)의 표면과 제 2 코어(3)의 표면과 중간 코어(14)의 표면이 인접하고 1개의 면을 형성하도록 구성되어 있지만, 이 면에 제 1 코어(2)와 중간 코어(4), 제 2 코어(3)와 중간 코어(4)와의 사이에 배치된 코일(6)을 가리도록 자기 실드판(8)이 장착되어 있다. 그리고, 납땜에 의해 인더턴스 소자(11)가 실장 기판에 실장된다.

본 예의 인더턴스 소자(11)에 의하면, 소자의 상부에 자기 실드판(8)을 갖추고 있으므로, 인더턴스 소자(11)의 상부로부터 자속이 누설하는 불편을 억제할 수 있어 실장된 다른 자성 소자에 영향을 주는 것이 적은 신뢰성이 높은 인더턴스 소자(11)를 제공할 수 있다.

또한, 제 1 코어, 제 2 코어 및 중간 코어의 형성에 이용하는 자성 재료는, Mn-Zn계 페라이트에 한정되는 것은 아니고 Ni-Zn계 페라이트나, 금속계 자성 재료, 어모퍼스(amorphous)계 자성 재료 등을 이용하는 것이 가능하다.

## 발명의 효과

본 발명과 관련되는 자성 소자에 의하면, 실장 기판에 대한 자성 소자의 배치 면적을 작게 할 수 있으므로, 실장 기판에 대해서 복수의 자성 소자를 고밀도에 설치할 수 있다.

### 도면의 간단한 설명

도 1은 본 발명에 의한 자성 소자의 분해 사시도이다.

도 2는 본 발명에 의한 자성 소자의 사시도이다.

도 3은 본 발명에 의한 자성 소자의 단면도이다.

도 4는 본 발명에 의한 자성 소자의 분해 사시도이다.

도 5는 종래의 자성 소자와 본 발명에 의한 자성 소자를 비교했을 때의 단면도이다.

도 6을 볼 발명에 의한 자성 소자의 다른 형태 예의 분해 사시도이다

도 7을 볼 박명에 의한 자성 소자의 다른 형태 예의 사시도이다.

도 8은 볼수의 자성 소자를 배치한 쪽래의 희로 구성은 나타내는 도면이다

\* 도면의 중요부분에 대한 복호의 설명

## 1. 11. 이더티스 솔자

22 평판론

2 제 1 코어

## 2b. 외각

|      |                     |                |

|------|---------------------|----------------|

| <12> | 2c. 중각              | 2d. 선단면        |

| <13> | 2e. 선단면             | 3. 제 2 코어      |

| <14> | 3a. 평판부             | 3b. 외각         |

| <15> | 3c. 중각              | 3d. 선단면        |

| <16> | 3e. 선단면             | 4. 중간 코어       |

| <17> | 4a. 평면              | 5. 단자 부재       |

| <18> | 6. 코일               | 6a. 코일 단부      |

| <19> | 7. 지지 베이스           | 8. 자기 실드판      |

| <20> | S1. 제 1 코어 중각부의 단면적 | S2. 중간 코어의 단면적 |

| <21> | S3. 제 2 코어 중각부의 단면적 | Φ1, Φ2. 자속선    |

| <22> | g. 캡                |                |

### 도면

#### 도면1

도면2

## 도면3

도면4

도면5

도면6

도면7

도면8