# MINISTERO DELLO SVILUPPO ECONOMICO DIREZIONE GENERALE PER LA LOTTA ALLA CONTRAFFAZIONE UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA DI INVENZIONE NUMERO | 102015000076200 |

|------------------------------|-----------------|

| Data Deposito                | 24/11/2015      |

| Data Pubblicazione           | 24/05/2017      |

# Classifiche IPC

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| Н       | 03     | K           | 3      | 356         |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppe |

| Н       | 03     | K           | 19     | 0185        |

# Titolo

CIRCUITO TRASLATORE DI LIVELLO, APPARECCHIATURA E PROCEDIMENTO CORRISPONDENTI

DESCRIZIONE dell'invenzione industriale dal titolo:

"Circuito traslatore di livello, apparecchiatura e procedimento corrispondenti"

di: STMicroelectronics S.r.l., di nazionalità italiana, Via C. Olivetti, 2 - 20864 Agrate Brianza (MB), Italia

Inventori designati: Dario BIANCHI, Federico GUANZIROLI, Davide Ugo GHISU

Depositata il: 24 novembre 2015

\*\*\*\*

#### TESTO DELLA DESCRIZIONE

#### Campo tecnico

La descrizione è relativa ai circuiti traslatori di livello.

Una o più forme di attuazione possono trovare uso in una varietà di applicazioni, quali per es. nei prodotti a ultrasuoni liberamente disponibili sul mercato.

Una unità di pilotaggio per generatori di impulsi ("pulser") a ultrasuoni è un esempio di una tale applicazione possibile.

# Sfondo tecnologico

Sebbene siano in grado di fornire prestazioni soddisfacenti, i tradizionali circuiti traslatori di livello possono presentare vari inconvenienti, per es.:

- una transizione lenta a causa delle capacità parassite per es. di un MOS ad alta tensione o HV MOS,

- un eventuale consumo statico rilevante.

- un valore elevato del resistore di pull-up eventualmente necessario per evitare un consumo elevato,

- una bassa immunità ad accoppiamenti indesiderati per

es. in ambienti rumorosi (vale a dire, in presenza di

alimentazioni rumorose ad in ambienti rumorosi),

- una robustezza ridotta rispetto a possibili perdite di dati, che può condurre ad eventi distruttivi (per es. a un' indesiderata corrente di uscita elevata).

# Scopo e sintesi

Uno scopo di una o più forme di attuazione è affrontare gli inconvenienti delineati in precedenza.

Secondo una o più forme di attuazione, tale scopo può essere raggiunto per mezzo di un circuito traslatore di livello avente le caratteristiche richiamate nelle rivendicazioni che seguono.

Una o più forme di attuazione possono anche riguardare una corrispondente apparecchiatura (per es. un prodotto a ultrasuoni quale un generatore di impulsi a ultrasuoni) così come un corrispondente procedimento.

Le rivendicazioni formano parte integrante della descrizione di una o più forme di attuazione come qui fornita.

Una o più forme di attuazione possono fornire per es. un traslatore di livello ad alta tensione comprendente una funzione di retroazione, per es. una retroazione capacitiva.

Una o più forme di attuazione possono fornire un variatore di segnale ad alta tensione, eventualmente con una differenza elevata tra il dominio di bassa tensione - per es. 3,3 V - e il dominio di alta tensione - per es. >100 V, con una corrente elevata e un basso consumo a riposo, adatto per un uso, per es. in applicazioni con transizioni veloci e alimentazioni rumorose.

Una o più forme di attuazione possono essere resistenti agli accoppiamenti indesiderati per es. in

ambienti rumorosi.

Una o più forme di attuazione possono comprendere un sistema di retroazione che verifica la coerenza dei dati di uscita traslati rispetto al segnale di ingresso di controllo per es. per un refresh nel caso di una transizione.

In una o più forme di attuazione, un tale sistema di retroazione può comprendere un condensatore, per traslare il livello di tensione dal dominio di alta tensione al dominio di bassa tensione, e un controllo logico sensibile al segnale di uscita per es. per effettuare il refresh del segnale di uscita.

Una o più forme di attuazione possono offrire uno o più dei seguenti vantaggi:

- elevata immunità alle alimentazioni rumorose e agli ambienti rumorosi.

- si evita in modo efficace una perdita di dati eventuale,

- transizione veloce,

- consumo statico ridotto.

# Breve descrizione delle figure

Una o più forme di attuazione saranno ora descritte, a puro titolo di esempio, con riferimento alle figure annesse, nelle quali:

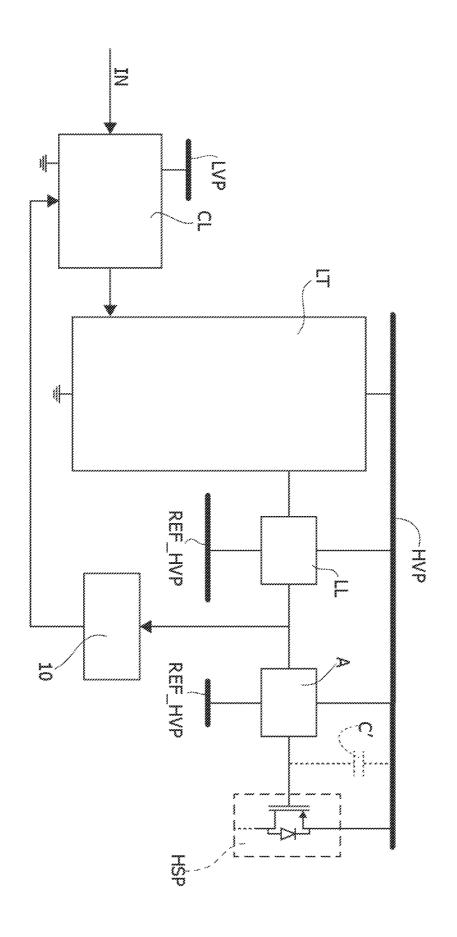

- la Figura 1 è uno schema a blocchi esemplificativo di forme di attuazione;

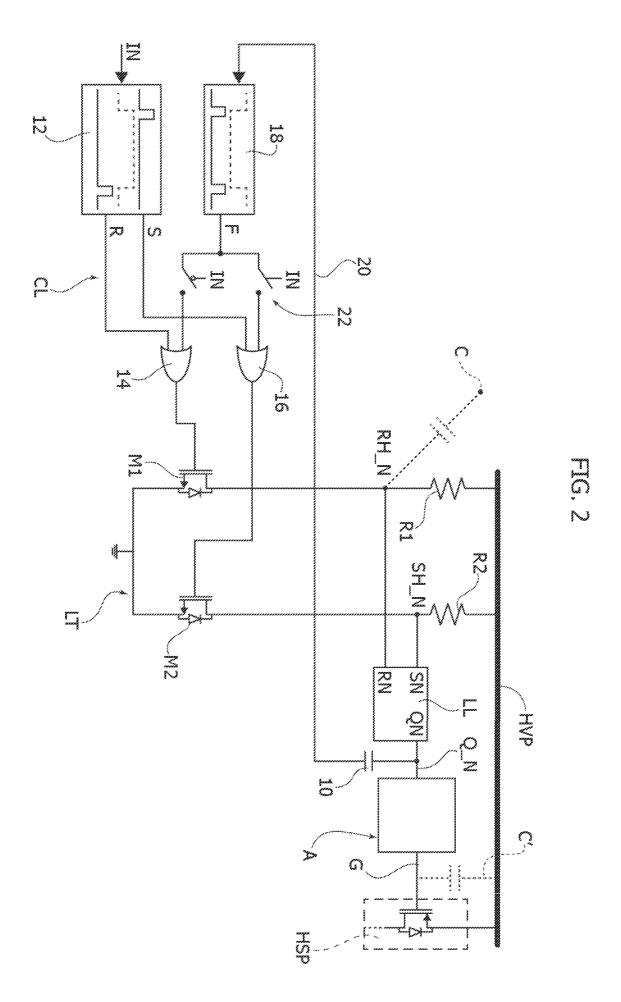

- la Figura 2 è uno schema circuitale esemplificativo di forme di attuazione; e

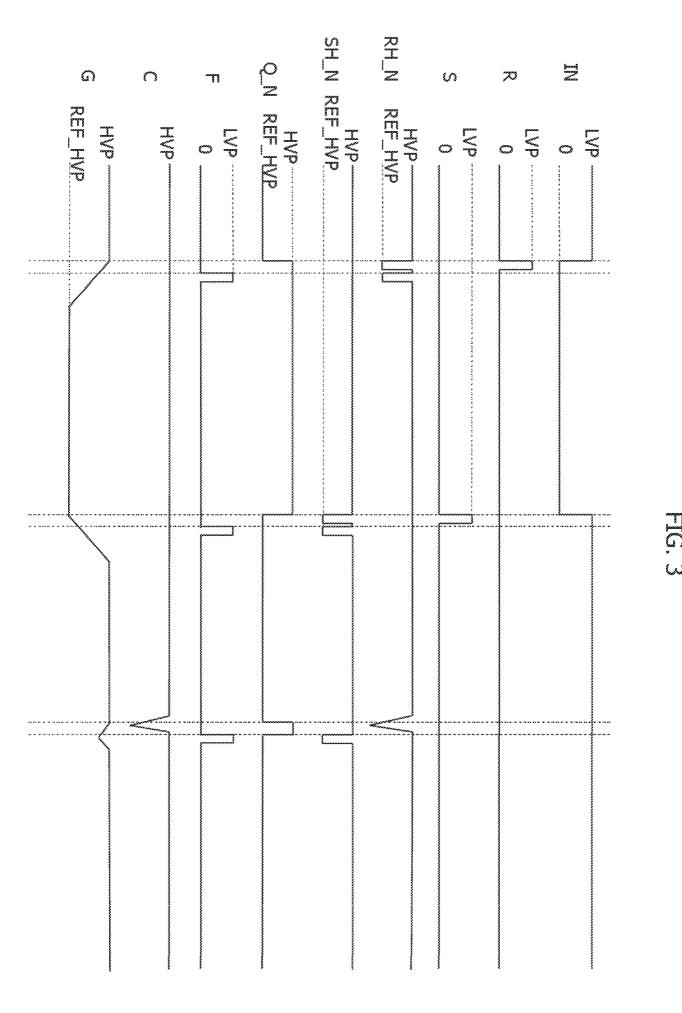

- la Figura 3 è illustrativa di certi segnali esemplificativi di un possibile funzionamento di forme di attuazione.

#### Descrizione dettagliata

Nella descrizione che segue sono illustrati uno o più dettagli specifici, allo scopo di fornire una comprensione approfondita degli esempi delle forme di attuazione. Le forme di attuazione possono essere ottenute senza uno o più dei dettagli specifici, o con altri procedimenti, componenti, materiali, ecc. In altri casi, operazioni, materiali o strutture note non sono illustrate o descritte in dettaglio in modo tale che certi aspetti delle forme di attuazione non saranno resi poco chiari.

Un riferimento a "una forma di attuazione" nel quadro della presente descrizione intende indicare che una particolare configurazione, struttura o caratteristica descritta con riferimento alla forma di attuazione è compresa in almeno una forma di attuazione. Per cui, le frasi come "in una forma di attuazione" che possono essere presenti in uno o più punti della presente descrizione non fanno necessariamente riferimento proprio alla stessa forma di attuazione. Inoltre, particolari conformazioni, strutture o caratteristiche possono essere combinate in un modo adequato qualsiasi in una o più forme di attuazione.

I riferimenti usati qui sono forniti semplicemente per convenienza e quindi non definiscono l'ambito di protezione o l'ambito delle forme di attuazione.

La descrizione si riferisce a circuiti traslatori di livello utilizzabili in apparecchiature che comportano tensioni elevate e correnti elevate. I sistemi per controllare gli attuatori con tensioni operative fino a 200 V e con correnti dell'ordine di alcuni ampere possono essere esemplificativi di tali apparecchiature.

Tali sistemi possono comprendere interfacce di

comunicazione in un dominio di bassa tensione (per es., da 1V a 2V) e possono pilotare carichi ad alta tensione, per cui un traslatore di livello, atto a "traslare" internamente i segnali da un dominio all'altro, può facilitare un funzionamento appropriato.

I traslatori di livello ("level shifter"), noti anche come variatori di livello ("level translator") possono così ricevere dati di ingresso, per es. a bassa tensione (per es., con valori GND = "0" logico o LVP = "1" logico) e traslare questi dati in segnali di uscita ad alta tensione (per es. segnali "intorno a" un'alta tensione, quali per es. REF\_HVP = "0" logico o HVP = "1" logico) in modo coerente ed univoco rispetto al segnale di ingresso, vale a dire fornendo una relazione corretta tra ingresso e uscita.

Una perdita di correlazione tra questi segnali può avere come risultato, per esempio, che una uscita di un MOS può essere attivata in modo indesiderato quando si desidera che sia disattivata. In presenza per es. di una uscita di un MOS di grandi dimensioni (vale a dire, atto a sostenere grandi correnti), ciò può produrre in modo indesiderato correnti elevate potenzialmente distruttive per un dispositivo.

Ottenere una correlazione desiderata può essere sempre più difficile all'aumentare della differenza di tensione tra i due domini (vale a dire, bassa tensione - per es. LVP - ed alta tensione - per es. HVP).

Un esempio di campo di applicazione sono i generatori di impulsi a ultrasuoni, dove un attuatore può essere pilotato per es. con onde quadre con un'ampiezza fino a 200 V, con fronti di uscita dell'ordine di 20 V/ns, e con correnti di commutazione dell'ordine di 2 A. In certe applicazioni si possono integrare molti generatori di

impulsi (per es., sedici generatori di impulsi), il che comporta correnti di commutazione abbastanza rilevanti (per es., alcune decine di ampere) e di conseguenza ambienti molto rumorosi.

Correnti di commutazione elevate, dinamiche di tensione elevate e fronti "veloci" che possono fare apparire sulle alimentazioni o sui nodi interni disturbi apprezzabili (ai quali il circuito deve essere immune) rappresentano pertanto fattori importanti per molte applicazioni.

Il consumo di potenza è un altro fattore che merita di essere preso in considerazione. In effetti, le piccole correnti consumate ad alte tensioni possono contribuire notevolmente al consumo di potenza totale. Un consumo statico ridotto (teoricamente nullo) è così una caratteristica auspicabile per di un variatore di livello, essendo peraltro apprezzato il fatto che ridurre il consumo può avere come risultato una immunità al rumore ridotta.

Vari circuiti traslatori di livello sono descritti in documenti come per es. US 2014/0247082 A1, US 8 044 699 B2, US 8 686 784 B2, o US 8 717 063 B2.

Come indicato, in questi documenti sono descritti dispositivi suscettibili di presentare certi inconvenienti, come per es. una transizione lenta a causa di una capacità parassita elevata di un dispositivo ad alta tensione, un consumo statico non trascurabile, una bassa immunità alle alimentazioni rumorose e la possibilità di perdita di dati.

Lo schema a blocchi della Figura 1 è esemplificativo di una o più forme di attuazione di un circuito traslatore di livello per pilotare un carico elettrico, per es. HSP.

In una o più forme di attuazione, questo può avvenire tramite uno stadio A quale per es. uno stadio di buffer, come una serie di porte logiche.

Un generatore di impulsi sul lato alto ("high-side") di un prodotto a ultrasuoni può essere un esempio di un tale carico. Si apprezzerà peraltro che il carico (per es. HSP) di per sé può non fare parte delle forme di attuazione.

In una o più forme di attuazione, un segnale di ingresso IN può essere applicato a una logica di controllo CL, che pilota a sua volta un variatore di livello (traslatore di livello) LT. Il variatore di livello LT pilota il carico HSP tramite un elemento logico LL (ed eventualmente lo stadio A).

A puro titolo di esempio non limitativo, un circuito traslatore di livello come qui esemplificato può funzionare tra un dominio di bassa tensione (LVP) per es. a 3,3 V e un dominio di alta tensione (HVP) a una tensione superiore a 100 V.

Si apprezzerà peraltro che, sebbene collocati nel dominio di alta tensione del circuito, l'elemento logico LL e lo stadio A possono di per sé non essere elementi ad alta tensione: per esempio, possono funzionare tra HVP e una tensione REF\_HVP con per es. REF\_HVP = HVP - 3,3 V.

In una o più forme di attuazione, si può fornire un percorso di retroazione 10 per trasferire su una linea di ingresso 20 alla logica di controllo CL un segnale rappresentativo del segnale di uscita (per es., "0" o "1" logico), ottenuto per es. all'uscita dell'elemento logico LL. Ricevendo il segnale di retroazione e il segnale di ingresso IN, la logica di controllo CL può rilevare un cambiamento nel segnale di uscita traslato, per es., per effettuare il refresh dei dati di uscita. A seconda che il segnale di uscita sia coerente oppure non coerente con il

segnale di ingresso, l'operazione di refresh conferma o corregge l'uscita.

In una o più forme di attuazione, un funzionamento veloce può essere facilitato (quanto più veloce è la retroazione, tanto più elevata è la frequenza dei segnali che possono essere trattati) fornendo al traslatore di livello un segnale di ingresso uguale al segnale di ingresso fornito nel caso di un fronte di IN (in modo coerente con l'effettivo il valore effettivo di IN effettivo).

Questa operazione di refresh produce una effettiva correzione dell'uscita ad alta tensione nel caso di una non-coerenza, mentre non si produce alcuna modifica nel caso di coerenza.

Per la logica di controllo CL sono possibili implementazioni diverse con la logica CL in grado di ricevere il segnale di retroazione, di verificarlo rispetto al valore atteso e di riconfermarlo (soltanto) se i due non differiscono.

In modo simile, con certi esempi di implementazione del percorso di retroazione 10, della logica di controllo CL e del variatore di livello LT ora descritti a titolo di esempio, gli esperti del settore possono prevedere altre implementazioni.

Per esempio, una o più forme di attuazione come esemplificate nello schema circuitale della Figura 2 possono comprendere:

- un percorso di retroazione capacitivo, comprendente un condensatore 10, che può avere un consumo di potenza statico molto piccolo (teoricamente zero),

- un variatore di livello LT comprendente uno stadio di commutazione posto tra HVP e massa (per es., switch

elettronici quali MOSFET M1, M2 con resistori di drain R1, R2), e

- un latch pilotato a impulsi LL.

In una o più forme di attuazione, il fatto che l'ingresso IN vada da 1 a 0 può far sì che un circuito monostabile 12 nella logica di controllo CL generi un impulso in corrispondenza di un nodo di uscita R. Questo impulso può essere applicato (per es., tramite una porta OR 14 discussa in seguito) all'elettrodo di controllo (gate) di M1, attivando così M1 (vale a dire, rendendolo conduttivo) per il tempo dell'impulso, mentre M2 rimane disattivato (vale a dire, non conduttivo).

La corrente risultante attraverso R1 genera così una caduta di tensione proporzionale al suo valore di resistenza e all'intensità della corrente.

La tensione RH\_N nel nodo tra M1 e R1 andrà così "bassa" per la durata dell'impulso di corrente e quindi ritornerà alta, mentre la tensione SH\_N nel nodo tra M2 e R2 rimarrà "alta" (per es., a HVP).

In una o più forme di attuazione, l'elemento logico LL può comprendere un latch set-reset equivalente avente le porte di ingresso SN e RN sensibili alle tensioni RH\_N e SH\_N, così come una porta di uscita QN per fornire un segnale di uscita Q N.

In una o più forme di attuazione, l'elemento logico LL può essere configurato secondo la tabella di verità rappresentata qui di seguito.

| SN | RN | ÕИ    |

|----|----|-------|

| 0  | 0  | Latch |

| 0  | 1  | 0     |

| 1  | 0  | 1     |

# 1 1 Latch

Nelle condizioni rappresentate in precedenza, l'elemento logico LL può così reagire e quindi avere la sua uscita QN, vale a dire la linea/nodo ("net") Q\_N verso il carico HSP, posta a un valore "alto", per es. HVP.

Il segnale nel nodo Q\_N (qui di seguito, per brevità, il segnale Q\_N) può propagarsi verso il carico HSF (per es., attraverso lo stadio A), al fine di produrre per es. un segnale in un nodo G accoppiato all'elettrodo di controllo (per es., il qate) di un PMOS nel carico HSP.

A titolo di caratteristica non limitativa, in una o più forme di attuazione come qui esemplificato, lo stadio A può comprendere una inversione logica, per cui (si vedano i diagrammi temporali nella Figura 2) il fatto che Q\_N salga da "basso" ad "alto" (per es., da REF\_HVF ad HVP) può avere come risultato che G commuta verso il basso da "alto" a "basso" (per es., da HVP a REF\_HVP) eventualmente con una velocità del fronte limitata dal suo elevato carico capacitivo parassita (in effetti, i MOSFET di uscita possono essere voluminosi per essere in grado di sopportare correnti di uscita elevate).

In una o più forme di attuazione, il segnale  $Q_N$  si propagherà anche verso la logica di controllo CL sul percorso di retroazione comprendente per es. un singolo condensatore 10.

In una o più forme di attuazione, il condensatore 10 può essere precaricato a un valore di precarica (questo può avere luogo in un modo noto di per sé).

La commutazione del nodo Q\_N accoppiato ad una estremità del condensatore 10 è così "riportata" dal nodo Q N al livello a bassa tensione sulla linea 20: una

variazione di tensione a un capo del condensatore 10 accoppiato con il nodo Q\_N sarà rispecchiata da una corrispondente variazione di tensione all'altro capo del condensatore 10 che è accoppiato all'ingresso di un ulteriore circuito monostabile 18 nella logica di controllo CL.

Il fronte di salita all'ingresso del circuito monostabile 18 produrrà all'uscita (nodo F) del circuito 18 un impulso di tensione. L'impulso nel nodo F è applicato ad uno switch 22 sensibile allo stato (vale a dire, al valore logico) del segnale di ingresso IN da inoltrare verso l'elettrodo di controllo (per es., il gate) di M1 o M2 a seconda dello stato di IN.

Nel caso esemplificativo appena considerato (un impulso nel nodo di uscita R applicato dal circuito monostabile 12 al primo ingresso della porta OR 14 come risultato del fatto che l'ingresso IN va da 1 a 0), lo switch 22 dirigerà l'impulso nel nodo F verso l'altro ingresso della porta OR 14, per es. attraverso il contatto inferiore dello switch 22 che viene chiuso, vale a dire reso conduttivo, dal complemento logico di IN. Un tale impulso diretto dal nodo F verso l'altro ingresso della porta OR 14 crea un nuovo impulso a 0 su RH\_N che conferma lo stato nel nodo Q\_N (vale a dire, il livello di Q\_N è mantenuto a "1" e le transizioni terminano).

Come descritto ulteriormente in dettaglio con riferimento ai diagrammi temporali della Figura 3, un'operazione perfettamente simile può essere ottenuta nel caso in cui IN commuti da 0 a 1.

In tal caso, in una o più forme di attuazione, il fatto che l'ingresso IN vada da 0 a 1 può far sì che il circuito monostabile 12 nella logica di controllo CL generi

un impulso in un nodo di uscita S. Questo impulso può essere applicato (tramite una porta OR 16) all'elettrodo di controllo (gate) di M2, attivando così M2 (vale a dire, rendendolo conduttivo) per il tempo dell'impulso, mentre M1 rimane disattivato (vale a dire, non conduttivo).

A parte il fatto che certi valori logici sono eventualmente invertiti (si veda per es. la Figura 3), il funzionamento dell'elemento logico LL e del percorso di retroazione 10 sarà così sostanzialmente simile a quello descritto precedentemente, con il condensatore 10 che "riporta" un segnale di retroazione dal nodo Q\_N al livello a bassa tensione e lo switch 22 che dirige l'impulso nel nodo F verso la porta OR 16 (per es., tramite il contatto superiore dello switch 22 che viene chiuso, vale a dire, reso conduttivo da IN). Un tale impulso diretto dal nodo F verso la porta OR 16 crea un nuovo impulso a 0 su SH\_N che conferma lo stato nel nodo Q\_N (vale a dire, il livello di Q N è mantenuto a "0" e le transizioni terminano).

Si apprezzerà che una o più forme di attuazione:

- possono essere teoricamente esenti da un consumo statico, a condizione che il variatore di livello LT possa essere implementato come uno stadio di commutazione (per es., in una certa misura equivalente a un raddrizzatore) comprendente switch elettronici, quali dei MOSFET M1, M2, pilotati da impulsi di corrente, con il consumo di corrente che avviene principalmente durante la commutazione, con gli altri blocchi logici che commutano soltanto mentre avviene tale commutazione,

- possono fornire un'immunità elevata al rumore e ad altri disturbi attraverso una retroazione.

- I diagrammi temporali della Figura 3 rappresentano possibili comportamenti nel tempo del segnale di ingresso

IN e dei segnali nei nodi R, S (le uscite dal circuito monostabile 12), RH\_N, SH\_N (le uscite dallo stadio variatore di livello LT), Q\_N (l'uscita dall'elemento logico LL), F, G più un segnale di disturbo (per es., un picco transitorio o spike verso il basso) da un accoppiamento parassita, per es. tra un nodo C e RH\_N (si veda la capacità illustrata a linee tratteggiate nella Figura 2).

Il lato di sinistra della Figura 3 è un esempio di un funzionamento "regolare" come discusso in precedenza, per es. una commutazione di IN da "1" (per es., LVP) a "0" (per es., massa o tensione zero) o viceversa, che produce una commutazione coerente, correlata di Q\_N (e G), per es. tra HVP e REF\_HVP, che è confermata per es. da un'azione di "refresh" come esemplificato dal secondo impulso verso il basso su RH N o SH N.

Il lato di destra della Figura 3 è un esempio del possibile funzionamento di una o più forme di attuazione in presenza di un disturbo come esemplificato dal picco transitorio verso il basso C, come discusso precedentemente.

Se di ampiezza sufficiente, tale impulso può essere letto come uno "0" logico all'ingresso RN di LL. Questo potrebbe far sì che il nodo Q\_N commuti (si veda il relativo diagramma temporale nella Figura 3). Tale commutazione sarà di nuovo "riportata" verso la logica di controllo CL attraverso il percorso di retroazione (per es., il condensatore 10), in modo tale che il circuito monostabile 18 generz un impulso nel nodo F.

Nel caso esemplificato nella Figura 3, IN = 1 (nessuna commutazione di IN quando si verifica il picco transitorio C), l'impulso su F sarà diretto al terminale di controllo

(gate) di M2 (per es., attraverso il contatto superiore dello switch 22 che viene chiuso, vale a dire, reso conduttivo da IN), forzando così SH\_N a 0 (per es., REF\_HVP). Questo provocherà una commutazione del nodo Q\_N a ritroso a 0, vale a dire il valore desiderato.

Considerando il carico capacitivo parassita nel nodo G (come rappresentato schematicamente dal condensatore C' a linee tratteggiate nelle Figure 1 e 2) e la velocità di azione del percorso di retroazione 10, il breve impulso su Q\_N (per es., da "0" a "1" e di nuovo a "0"), pur propagandosi verso il nodo G, non sarà in grado di sviluppare una tensione sufficiente da modificare il livello sul carico HSP (per es., per attivare il PMOS in esso).

In assenza del percorso di retroazione 10, si srebbe potuta verificare una commutazione (stabile) del valore di Q\_N, con Q\_N che rimane eventualmente a un valore errato fino a una nuova commutazione di IN (che potrebbe eventualmente avvenire soltanto dopo tempo prolungato). Una tale situazione può avere come risultato per es. che un PMOS nel carico HSP, che si prevede effettivamente essere in uno stato "disattivato", sia attivato in modo erroneo e senza controllo, con il rischio di generare in modo indesiderato correnti di uscita suscettibili di condurre a un consumo di potenza inatteso e/o di risultare dannose per il dispositivo o per un altro consumo inatteso.

Nelle applicazioni previste per pilotare piccoli carichi, per es. dei MOSFET con piccola uscita, il percorso da Q\_N a G può fornire un carico capacitivo corrispondentemente basso, realizzando così un'azione ridotta di filtraggio degli impulsi dovuti ai disturbi (per es., C) che si propagano sul percorso tra Q\_N e G, per cui

l'impulso di disturbo potrebbe produrre un corrispondente picco transitorio o corrente di ON-ON all'uscita per la durata di quell'impulso.

Una o più forme di attuazione possono affrontare questo problema fornendo appositamente un filtro (per es., passa-basso) nel percorso tra Q\_N e G, per es. nello stadio A, tale filtro essendo dimensionato al fine di evitare la propagazione dell'impulso verso G per il tempo durante il quale il percorso di retroazione fornisce la correzione di Q\_N, come esemplificato in precedenza.

Peraltro si apprezzerà che le forme di attuazione non sono limitate a dispositivi tali per cui, come esemplificato qui, una commutazione di IN da "1" a "0" ha come risultato che Q\_N commuta da "0" a "1" e una commutazione di IN da "0" a "1" ha come risultato che Q\_N commuta da "1" a "0" (vale a dire, con una inversione logica da ingresso a uscita).

In una o più forme di attuazione, una commutazione di IN da "1" a "0" può avere come risultato che Q\_N commuta identicamente da "1" a "0", mentre una commutazione di IN da "0" a "1" può avere come risultato che Q\_N commuta da "0" a "1" (vale a dire, senza alcuna inversione logica da ingresso a uscita).

In altre parole, in una o più forme di attuazione, indipendentemente dai valori logici coinvolti, si può riscontrare l'esistenza di "coerenza" o "correlazione" tra l'ingresso (per es., IN) e l'uscita (per es., Q\_N) quando la commutazione di uscita "concorda" in modo appropriato con una commutazione di ingresso, vale a dire quando si verifica in modo desiderato una commutazione di uscita in quanto si è verificata una commutazione di ingresso.

Analogamente, sebbene qui si sia esemplificata una

traslazione di livello "verso l'alto" (per es., da una bassa tensione LVP a un'alta tensione HVP), una o più forme di attuazione possono essere applicate a una traslazione di livello "verso il basso", per es. da una bassa tensione a un'alta tensione (negativa).

Analogamente, la relazione di inversione logica tra Q N e G qui esemplificato non è in alcun modo imperativa.

Adattare gli esempi di dispositivi qui descritti a una differente relazione logica tra ingresso e uscita e/o a una traslazione di livello verso il basso ricade entro le competenze degli esperti in questo campo, il che rende superfluo fornire qui una descrizione dettagliata.

Una o più forme di attuazione possono così fornire un circuito traslatore di livello per pilotare un carico (per es., HSP) tramite una linea di alimentazione HVP, il circuito comprendendo:

- uno stadio di ingresso per ricevere un segnale di ingresso (per es., IN) commutabile tra un primo e un secondo livello di ingresso (per es. 0, LVP),

- uno stadio di uscita accoppiato a detta linea di alimentazione per produrre un segnale di pilotaggio (per es. G, come eventualmente ottenuto da Q\_N attraverso lo stadio A) per detto carico, lo stadio di uscita essendo commutabile tra un primo e un secondo livello di uscita (per es. REF HVP, HVP),

- un variatore di livello posto tra lo stadio di ingresso e lo stadio di uscita, per cui una commutazione di detto segnale di ingresso tra detto primo e detto secondo livello si traduce in una commutazione di detto stadio di uscita tra detto primo e detto secondo livello di uscita (vale a dire, una commutazione del primo e del secondo livello di ingresso del segnale di ingresso fa sì che lo

stadio di uscita commuti in modo corrispondente tra detto primo e detto secondo livello di uscita),

- un elemento di retroazione (per es. 10) accoppiato a detto stadio di uscita per trasferire a detto stadio di ingresso un segnale di retroazione (per es. 20) rappresentativo del livello di uscita (per es. Q\_N) dello stadio di uscita,

in cui lo stadio di ingresso comprende circuiteria di controllo (per es. da 12 a 18, 22) sensibile a detto segnale di ingresso e detto segnale di retroazione per rilevare una commutazione indesiderata di detto stadio di uscita tra detto primo e detto secondo livello di uscita che si verifica in assenza di una commutazione del segnale di ingresso tra detto primo e detto secondo livello di ingresso, detta circuiteria di controllo configurata (per es. 22) per invertire (per es., cambiare da 0 a 1 o da 1 a 0) il livello di uscita di detto stadio di uscita risultante da detta commutazione indesiderata.

In una o più forme di attuazione, detta circuiteria di controllo sensibile a detto segnale di ingresso è configurata per rilevare una commutazione di detto stadio di uscita tra detto primo e detto secondo livello di uscita che si verifica come risultato di una commutazione del segnale di ingresso tra detto primo e detto secondo livello di ingresso (0, LVP) ed effettuare un refresh (si vedano per es. i secondi impulsi verso il basso suo RH\_N e SH\_N negli schemi della Figura 3) del livello di uscita risultante da tale commutazione.

In una o più forme di attuazione, il detto elemento di retroazione può comprendere un condensatore (per es. 10) posto tra detto stadio di uscita e detta circuiteria di controllo.

Una o più forme di attuazione possono comprendere un variatore di livello verso l'alto posto tra uno stadio di ingresso per ricevere un segnale di ingresso commutabile tra un primo e un secondo livello di ingresso a bassa tensione (per es. 0, LVP) e uno stadio di uscita per produrre un segnale di pilotaggio ad alta tensione (per es. REF HVP, HVP) per detto carico.

Una o più forme di attuazione possono comprendere un variatore di livello verso il basso posto tra uno stadio di ingresso a bassa tensione e uno stadio di uscita ad alta tensione negativa.

In una o più forme di attuazione, detto variatore di livello può comprendere uno stadio di commutazione, che comprende opzionalmente switch elettronici quali dei MOSFET (per es. M1, M2).

In una o più forme di attuazione, detto stadio di uscita può comprendere un elemento latch set-reset (per es. LL) che ha ingressi di set e di reset (per es. SN, RN) accoppiati (per es. SH\_N, RH\_N) a detto variatore di livello e una uscita commutabile tra detto primo e detto secondo livello di uscita (per es. REF\_HVP, HVP) in funzione di detti ingressi di set e di reset.

In una o più forme di attuazione, detta circuiteria di controllo può comprendere:

- un circuito a impulsi (per es. 18) pilotato da detto segnale di retroazione, detto circuito a impulsi accoppiabile (per es. tramite 14, 16, 22) a detto variatore di livello per applicare a detto variatore di livello degli impulsi di pilotaggio (per es. F) per commutare detto stadio di uscita tra detto primo e detto secondo livello di uscita,

- un circuito di accoppiamento (per es. 22) posto tra

detto circuito a impulsi e detto variatore di livello, detto circuito di accoppiamento sensibile a detto segnale di ingresso (IN) per accoppiare selettivamente detto circuito a impulsi a detto variatore di livello (LT) in una condizione di accoppiamento per applicare a detto variatore di livello impulsi di pilotaggio (per es. F) per invertire il livello di uscita di detto stadio di uscita risultante da detta commutazione indesiderata di detto stadio di uscita.

In una o più forme di attuazione, detto circuito di accoppiamento (per es. 22) può ammettere una ulteriore condizione di accoppiamento per accoppiare detto circuito a impulsi a detto variatore di livello in modo da applicare a detto variatore di livello impulsi di pilotaggio per mantenere il livello di uscita (per es. Q\_N) di detto stadio di uscita a uno tra detto primo e detto secondo livello di uscita traducendo una commutazione di detto segnale di ingresso tra detto primo e detto secondo di ingresso.

In una o più forme di attuazione, detto stadio di uscita (per es. A) può comprendere un filtro, opzionalmente del tipo passa-basso, per produrre detto segnale di pilotaggio (per es. G) per detto carico.

Fermi restando i principi di fondo, i dettagli e le forme di attuazione possono variare, anche in modo apprezzabile, rispetto a quanto è stato descritto puramente a titolo di esempio, senza uscire dall'ambito di protezione.

L'ambito di protezione è definito dalle rivendicazioni annesse.

#### RIVENDICAZIONI

- 1. Circuito traslatore di livello per pilotare un carico (HSP) tramite una linea di alimentazione (HVP), il circuito comprendendo:

- uno stadio di ingresso (CL) per ricevere un segnale di ingresso (IN) commutabile tra un primo e un secondo livello di ingresso (0, LVP),

- uno stadio di uscita (LL, A) accoppiato a detta linea di alimentazione (HVP) per produrre un segnale di pilotaggio (G) per detto carico (HSP), lo stadio di uscita (LL, A) commutabile tra un primo e un secondo livello di uscita (REF HVP, HVP),

- un variatore di livello (LT) posto tra lo stadio di ingresso (CL) e lo stadio di uscita (LL, A), per cui una commutazione di detto stadio di ingresso (IN) tra detto primo e detto secondo livello di ingresso (0, LVF) fa sì che detto stadio di uscita (LL, A) commuti tra detto primo e detto secondo livello di uscita (REF HVP, HVP),

- un elemento di retroazione (10) accoppiato a detto stadio di uscita (LL, A) per trasferire a detto stadio di ingresso (CL) un segnale di retroazione (20) rappresentativo del livello di uscita dello stadio di uscita (LL, A),

in cui lo stadio di ingresso (CL) comprende circuiteria di controllo (da 12 a 18, 22) sensibile a detto segnale di ingresso (IN) e a detto segnale di retroazione (20) e configurata per rilevare una commutazione indesiderata di detto stadio di uscita (LL, A) tra detto primo e detto secondo livello di uscita (REF\_HVP, HVP) che si verifica in assenza di una commutazione del segnale di ingresso (IN) tra detto primo e detto secondo livello di

ingresso (0, LVP) e per invertire il livello di uscita (Q\_N) di detto stadio di uscita (LL, A) risultante da detta commutazione indesiderata.

- 2. Circuito traslatore di livello secondo la rivendicazione 1, in cui detta circuiteria di controllo (da 12 a 18, 22) sensibile a detto segnale di ingresso (IN) è configurata per rilevare una commutazione di detto stadio di uscita (LL, A) tra detto primo e detto secondo livello di uscita (REF\_HVP, HVP) che si verifica come risultato di una commutazione del segnale di ingresso (IN) tra detto primo e detto secondo livello di ingresso (0, LVF) e per effettuare un refresh del livello di uscita (Q\_N) risultante da detta commutazione del segnale di ingresso.

- 3. Circuito traslatore di livello secondo la rivendicazione 1 o la rivendicazione 2, in cui detto elemento di retroazione comprende un condensatore (10) posto tra detto stadio di uscita (LL, A) e detta circuiteria di controllo (da 12 a 22).

- 4. Circuito traslatore di livello secondo una qualsiasi delle rivendicazioni precedenti, comprendente un variatore di livello (LT) posto tra uno stadio di ingresso (CL) per ricevere un segnale di ingresso (IN) commutabile tra un primo e un secondo livello di ingresso a bassa tensione (0, LVP) e uno stadio di uscita (LL, A) per produrre un segnale di pilotaggio ad alta tensione (G) per detto carico (HSP).

- 5. Circuito traslatore di livello secondo una qualsiasi delle rivendicazioni precedenti, in cui detto

variatore di livello (LT) comprende uno stadio di commutazione (M1, M2), che comprende preferibilmente switch elettronici quali MOSFET.

- 6. Circuito traslatore di livello secondo una qualsiasi delle rivendicazioni precedenti, in cui detto stadio di uscita (LL, A) comprende un elemento latch (LL) avente ingressi (SN, RN) accoppiati (SH\_N, RH\_N) a detto variatore di livello (LT) e una uscita (QN) commutabile tra detto primo e detto secondo livello di uscita (REF\_HVP, HVP) in funzione di detti ingressi (SN, RN).

- 7. Circuito traslatore di livello secondo una qualsiasi delle rivendicazioni precedenti, in cui detta circuiteria di controllo (da 12 a 18, 22) comprende:

- un circuito a impulsi (18) pilotato da detto segnale di retroazione (20), detto circuito a impulsi (18) accoppiabile (14, 16, 22) a detto variatore di livello (LT) per applicare a detto variatore di livello (LT) impulsi di pilotaggio (F) per commutare detto stadio di uscita (LL, A) tra detto primo e detto secondo livello di uscita (REF\_HVP, HVP),

- un circuito di accoppiamento (22) posto tra detto circuito a impulsi (18) e detto variatore di livello (LT), detto circuito di accoppiamento (22) sensibile a detto segnale di ingresso (IN) per accoppiare detto circuito a impulsi (18) in una condizione di accoppiamento a detto variatore di livello (LT) in modo da applicare a detto variatore di livello (LT) impulsi di pilotaggio (F) per invertire il livello di uscita (Q\_N) di detto stadio di uscita (LL, A) risultante da detta commutazione indesiderata di detto stadio di uscita (LL, A).

- 8. Circuito traslatore di livello secondo la rivendicazione 7, in cui detto circuito di accoppiamento (22) ammette una ulteriore condizione di accoppiamento per accoppiare detto circuito a impulsi (18) a detto variatore di livello (LT) in modo da applicare a detto variatore di livello (LT) impulsi di pilotaggio mantenendo il livello di uscita (Q\_N) di detto stadio di uscita (LL, A) a uno tra detto primo e detto secondo livello di uscita (REF\_HVP, HVP) risultante da una commutazione di detto segnale di ingresso (IN) tra detto primo e detto secondo livello di ingresso (0, LVP).

- 9. Traslatore di livello secondo una qualsiasi delle rivendicazioni precedenti, in cui detto stadio di uscita (LL, A) comprende un filtro, preferibilmente del tipo passa-basso, per produrre detto segnale di pilotaggio (G) per detto carico (HSP).

- 10. Apparecchiatura comprendente un circuito traslatore di livello secondo una qualsiasi delle rivendicazioni da 1 a 9.

- 11. Procedimento per pilotare un carico (HSP) tramite una linea di alimentazione (HVP), il procedimento comprendendo:

- ricevere un segnale di ingresso (IN) commutabile tra un primo e un secondo livello di ingresso (0, LVP),

- accoppiare a detta linea di alimentazione (HVP) uno stadio di uscita (LL, A) che produce un segnale di pilotaggio (G) per detto carico (HSP), lo stadio di uscita (LL, A) commutabile tra un primo e un secondo livello di

uscita (REF HVP, HVP),

- fornire un variatore di livello (LT) sensibile (S, R) a detto segnale di ingresso (IN) per pilotare detto stadio di uscita (LL, A), per cui una commutazione di detto segnale di ingresso (IN) tra detto primo e secondo livello di ingresso (0, LVP) fa sì che detto stadio di uscita (LL, A) commuti tra detto primo e detto secondo livello di uscita (REF HVP, HVP),

- trasferire a detto stadio di ingresso (CL) un segnale di retroazione (20) rappresentativo del livello di uscita dello stadio di uscita (LL, A),

- rivelare (da 12 a 18, 22) detto segnale di ingresso (IN) e detto segnale di retroazione (20) e rilevare una commutazione indesiderata di detto stadio di uscita (LL, A) tra detto primo e detto secondo livello di uscita (REF\_HVP, HVP) che si verifica in assenza di una commutazione del segnale di ingresso (IN) tra detto primo e detto secondo livello di ingresso (0, LVP),

- invertire il livello di uscita (Q\_N) di detto stadio di uscita (LL, A) risultante da detta commutazione indesiderata.