(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5079072号

(P5079072)

(45) 発行日 平成24年11月21日(2012.11.21)

(24) 登録日 平成24年9月7日(2012.9.7)

|              |                   |

|--------------|-------------------|

| (51) Int.Cl. | F 1               |

| G09F 9/30    | (2006.01)         |

| G09F 9/00    | (2006.01)         |

| G09G 3/20    | (2006.01)         |

| G09G 3/36    | (2006.01)         |

| G02F 1/133   | (2006.01)         |

| GO9F 9/30    | 9/30 3 4 9 Z      |

| G09F 9/00    | 9/30 3 3 8        |

| G09G 3/20    | 9/00 3 6 6 G      |

| G09G 3/36    | 3/20 6 1 1 A      |

| G02F 1/133   | 9/0G 3/20 6 7 0 E |

請求項の数 8 (全 45 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2010-278883 (P2010-278883)  |

| (22) 出願日     | 平成22年12月15日 (2010.12.15)      |

| (65) 公開番号    | 特開2011-145669 (P2011-145669A) |

| (43) 公開日     | 平成23年7月28日 (2011.7.28)        |

| 審査請求日        | 平成24年7月20日 (2012.7.20)        |

| (31) 優先権主張番号 | 特願2009-288511 (P2009-288511)  |

| (32) 優先日     | 平成21年12月18日 (2009.12.18)      |

| (33) 優先権主張国  | 日本国 (JP)                      |

早期審査対象出願

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査官       | 佐竹 政彦                                          |

最終頁に続く

(54) 【発明の名称】光センサを有する表示装置及びその駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

互いに向かい合って配置された第1の基板と第2の基板と、を有する表示装置であって

、

前記第1の基板上に、

端子部と、

酸化物半導体を有するスイッチングトランジスタと、

第1の光センサと、

第2の光センサと、

複数の画素を有する画素回路と、

前記画素回路と基板端部との間に駆動回路と、を有し、前記第1の光センサは、非晶質半導体を有する第1の光電変換素子と、第1の増幅回路と、を有し、前記第2の光センサは、多結晶半導体を有する第2の光電変換素子と、第2の増幅回路と、を有し、前記第2の基板は、対向電極を有し、

前記対向電極は、前記スイッチングトランジスタを介して前記端子部と電気的に接続されていることを特徴とする表示装置。

## 【請求項 2】

請求項1において、

10

20

前記第1の光電変換素子は、非晶質シリコンを有していることを特徴とする表示装置。

**【請求項3】**

請求項1または請求項2において、

前記第2の光電変換素子は、多結晶シリコンまたは微結晶シリコンを有していることを特徴とする表示装置。

**【請求項4】**

請求項1乃至請求項3のいずれか一項において、

前記酸化物半導体のキャリア濃度は、 $1 \times 10^{14} / \text{cm}^3$ 未満であることを特徴とする表示装置。

**【請求項5】**

10

請求項1乃至請求項4のいずれか一項において、

前記駆動回路は、単結晶半導体で作製されていることを特徴とする表示装置。

**【請求項6】**

請求項1乃至請求項5のいずれか一項において、

前記駆動回路は、COG法、ワイヤボンディング法、またはTAB法で接続されていることを特徴とする表示装置。

**【請求項7】**

請求項1乃至請求項6のいずれか一項において、

前記対向電極は、前記スイッチングトランジスタが非導通状態の時に、浮遊状態となることを特徴とする表示装置。

20

**【請求項8】**

請求項1乃至請求項7のいずれか一項において、

前記表示装置は液晶表示装置であることを特徴とする表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の一態様は、薄膜半導体を用いた光センサと、該光センサを内蔵した表示装置に関する。

**【背景技術】**

**【0002】**

30

近年、液晶表示装置に代表されるアクティブマトリクス型表示装置においては、画面サイズが対角20インチ以上と大型化する傾向にあり、さらには、対角100インチ以上の画面サイズも視野に入れた開発が行われている。加えて、画面の解像度も、ハイビジョン画質(HD、 $1366 \times 768$ )、フルハイビジョン画質(FHD、 $1920 \times 1080$ )と高精細化の傾向にあり、解像度が $3840 \times 2048$ または $4096 \times 2180$ といった、いわゆる4Kデジタルシネマ用表示装置の開発も急がれている。

**【0003】**

画面サイズの大型化や高精細化により、トランジスタには高い電界効果移動度が求められている。また、画面サイズが大きくなると消費電力の増加だけでなく、表示ムラや色調など表示品質が観察者に認識されやすくなる。

40

**【0004】**

加えて、観察者が感じる輝度や発色などの表示品質は、表示装置が設置されている環境の照度や色温度にも大きく左右される。例えば、特許文献1には、表示装置に入射する外光の強度(照度)に応じて、表示装置の発光強度を制御する表示装置が開示されている。

**【0005】**

また、表示装置を屋内だけでなく屋外でも使用する場合は、低照度から高照度までの変化量が大きいため、低照度用の光センサは、高照度下においては出力が飽和してしまい、高照度用の光センサは、低照度下において照度検出そのものが困難となる。特許文献2には、可視光域に光感度を持つ光センサと、赤外光域に光感度を持つ光センサを用いて屋内か屋外かを判別する表示装置が開示されているものの、低照度から高照度まで安定した出力

50

が得られる光センサについては示されていない。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000-112382号公報

【特許文献2】特開2003-29239号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

画面サイズの大型化や高精細化は、それにともなう配線抵抗や寄生容量の増加により、表示装置の表示品質の低下や、消費電力の増加を生じてしまう。特にアクティブマトリクス型表示装置においては、画面サイズが大きくなるほど、各画素に用いられるトランジスタのオフ電流や閾値などの特性バラツキが消費電力や表示品質などに大きく影響する。10

【0008】

また、画面サイズが大きくなると消費電力の増加だけでなく、表示ムラや色調などの表示品質が観察者に認識されやすくなるため、表示装置が設置されている環境の照度や色温度に応じて、表示映像を適正な発光強度や色調に補正することで、表示装置の電力消費を抑えつつ、周囲の環境に起因する表示品質低下の改善が求められている。

【0009】

本発明の一態様は、表示装置の省電力化を実現することを課題の一つとする。20

【0010】

また、本発明の一態様は、周囲の環境に応じて最適な表示品質を提供することを課題の一つとする。

【0011】

また、本発明の一態様は、室温から180 度の温度範囲で安定して動作するトランジスタ及びそれを用いた表示装置を提供することを課題の一つとする。

【課題を解決するための手段】

【0012】

本発明の一態様は、可視光に対して高い光感度を有する非晶質薄膜光センサと、非晶質薄膜光センサよりも可視光に対する光感度は低いが赤外光にも光感度を有する多結晶薄膜光センサを用いて、表示装置周囲の照度や色温度を検出し、検出結果をもとに表示映像の輝度や色調を調整することを特徴とする表示装置である。30

【0013】

また、本発明の一態様は、可視光に対して高い光感度を有する非晶質薄膜光センサと、非晶質薄膜光センサよりも可視光に対する光感度は低いが赤外光にも光感度を有する多結晶薄膜光センサを用いて、表示装置周囲の照度や色温度を検出し、検出結果をもとに表示映像の輝度や色調を調整し、静止画を表示する際の書き込み間隔を1秒以上とすることを特徴とする表示装置である。

【0014】

また、本発明の一態様は、第1の基板上に、端子部と、画素電極と、スイッチングトランジスタと、可視光に対して高い光感度を有する非晶質薄膜光センサと、赤外光に光感度を有し、非晶質薄膜光センサよりも可視光に対する光感度が低い多結晶薄膜光センサを有し、第2の基板上に対向電極を有し、端子部からスイッチングトランジスタを介して対向電極へ電位を供給し、光センサを用いて表示装置周囲の照度や色温度を検出し、検出結果をもとに表示映像の輝度や色調を調整し、静止画を表示する際は、スイッチングトランジスタを非導通状態として、対向電極の電位を浮遊状態とすることを特徴とする表示装置である。40

【0015】

また、本発明の一態様は、第1の基板上に、第1の光センサと、第2の光センサと、複数の画素を有する画素回路が形成され、第1の光センサは、非晶質半導体を有する第1の光50

電変換素子と、酸化物半導体を有するトランジスタで構成された第1の増幅回路を有し、第2の光センサは、多結晶半導体を有する第2の光電変換素子と、酸化物半導体を有するトランジスタで構成された第2の増幅回路を有し、画素回路は、画素電極と、酸化物半導体を有するトランジスタを有することを特徴とする表示装置である。

#### 【0016】

また、本発明の一態様は、互いに向かい合って配置された第1の基板と第2の基板を有し、第1の基板上に、端子部と、第1の光センサと、第2の光センサと、複数の画素を有する画素回路が形成され、第1の光センサは、非晶質半導体を有する第1の光電変換素子と、酸化物半導体を有するトランジスタで構成された第1の増幅回路を有し、第2の光センサは、多結晶半導体を有する第2の光電変換素子と、酸化物半導体を有するトランジスタで構成された第2の増幅回路を有し、画素回路は、画素電極と、酸化物半導体を有するトランジスタを有し、第2の基板は対向電極を有し、対向電極は、第1の基板上に形成された酸化物半導体を有するトランジスタを介して端子部と電気的に接続されていることを特徴とする表示装置である。 10

#### 【0017】

また、本発明の一態様は、互いに向かい合って配置された第1の基板と第2の基板を有し、第1の基板上に、端子部と、酸化物半導体を有するスイッチングトランジスタと、第1の光センサと、第2の光センサと、複数の画素を有する画素回路と、画素回路と基板端部の間に駆動回路が形成され、第1の光センサは、非晶質半導体を有する第1の光電変換素子と、酸化物半導体を有するトランジスタで構成された第1の増幅回路を有し、第2の光センサは、多結晶半導体を有する第2の光電変換素子と、酸化物半導体を有するトランジスタで構成された第2の増幅回路を有し、第2の基板は対向電極を有し、対向電極は、スイッチングトランジスタを介して端子部と電気的に接続され、スイッチングトランジスタと端子部を接続する配線は、駆動回路と基板端部の間に形成されていることを特徴とする表示装置である。 20

#### 【0018】

また、具体的には、キャリア密度を  $1 \times 10^{14} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{12} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満とした酸化物半導体を用いる。 30

#### 【0019】

非晶質半導体は、非晶質シリコンを用いることができる。多結晶半導体は、多結晶シリコンまたは微結晶シリコンを用いることができる。

#### 【0020】

静止画を表示する期間において、ゲート線駆動回路または信号線駆動回路からの信号を停止させることができる。

#### 【0021】

静止画を表示する期間において、スイッチングトランジスタを非導通状態として、対向電極を浮遊状態とすることができます。

#### 【発明の効果】

#### 【0022】

本発明の一態様により、消費電力が少なく、表示品質の良い表示装置を提供することができる。 40

#### 【図面の簡単な説明】

#### 【0023】

【図1】表示装置を説明する図。

【図2】光センサの光感度特性を示す図。

【図3】表示装置のブロック図。

【図4】表示装置の構成を説明する図。

【図5】表示装置の画素回路の構成を説明する図。

【図6】光センサ読み出し回路の構成を説明する図。 50

【図 7】光センサの読み出し動作を説明するタイミングチャート。

【図 8】トランジスタ及び光センサの作製工程を説明する図。

【図 9】トランジスタ及び光センサの作製工程を説明する図。

【図 10】トランジスタ及び光センサの作製工程を説明する図。

【図 11】画素スイッチ用トランジスタの構成を説明する図。

【図 12】トランジスタの構成を説明する図。

【図 13】表示装置の構成を説明する図。

【図 14】表示装置の動作を説明するタイミングチャート。

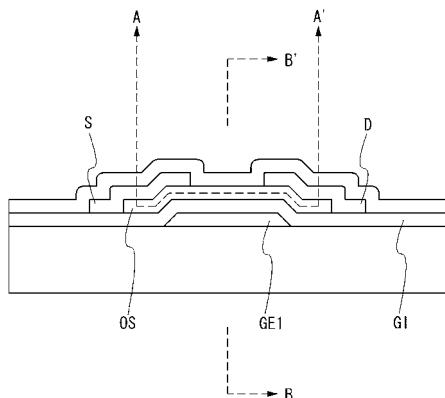

【図 15】逆スタガ型のトランジスタの縦断面図。

【図 16】図 15 における A - A' 断面のエネルギーバンド図。 10

【図 17】図 15 における B - B' 断面のエネルギーバンド図。

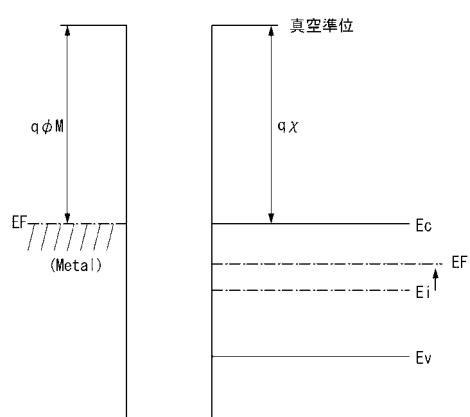

【図 18】真空準位と金属の仕事関数と酸化物半導体の電子親和力の関係を示す図。

【図 19】電子機器を説明する図。

【発明を実施するための形態】

【0024】

以下、本発明の実施の形態及び実施例について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施の形態及び実施例の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じ物を指し示す符号は異なる図面間において共通とする。 20

【0025】

なお、各実施の形態の図面等において示す各構成の、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されて表記している場合がある。よって、必ずしもそのスケールに限定されない。

【0026】

本明細書にて用いる第 1、第 2、第 3、乃至第 N (N は自然数) という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

【0027】

なお、電圧とは、ある電位と、基準の電位（例えばグラウンド電位）との電位差のこと 30 を示す場合が多い。よって、電圧、電位、電位差を、各々、電位、電圧、電圧差と言い換えることが可能である。

【0028】

トランジスタは半導体素子の一種であり、電流や電圧の増幅や、導通または非導通を制御するスイッチング動作などを実現することができる。本明細書におけるトランジスタは、IGFET (I n s u l a t e d G a t e F i e l d E f f e c t T r a n s i s t o r) や薄膜トランジスタ (TFT : T h i n F i l m T r a n s i s t o r) を含む。

【0029】

本明細書における回路図において、酸化物半導体層を用いるトランジスタと明確に判明できるように、酸化物半導体層を用いるトランジスタの記号には「OS」と記載している。 40

【0030】

(実施の形態 1)

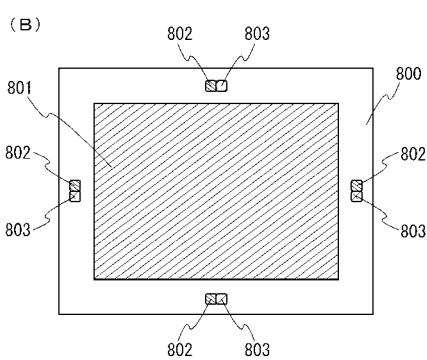

本実施の形態では、光センサを内蔵する表示装置の一形態について説明する。図 1 は光センサを内蔵する表示装置 800 を示している。図 1 (A) は、表示部 801 の外側上部に光センサ 802 及び光センサ 803 が設けられている。図 1 (B) は表示部 801 の周囲に光センサ 802 及び光センサ 803 が複数設けられている。

【0031】

光センサ 802 は光電変換素子が非晶質半導体で構成されており、光センサ 803 は光電変換素子が多結晶半導体で構成されている。光センサ 802 または光センサ 803 により 50

表示装置周囲の照度を検出し、表示装置の発光輝度を調整する。例えば、表示装置周囲の照度が強い場合は表示部 801 の発光輝度を大きくし、表示装置周囲の照度が弱い場合は表示部 801 の発光輝度を小さくすることで、使用者の体感上の輝度変化を軽減し、消費電力の増加を抑えることができる。

#### 【0032】

図1(B)に示したように、光センサ 802 及び光センサ 803 を複数配置することで、表示装置周囲の照度をより正確に検出することができる。また、例えば幾つかの光センサが隠された場合においても、残りの光センサにより表示装置周囲の照度を検出することができる。

#### 【0033】

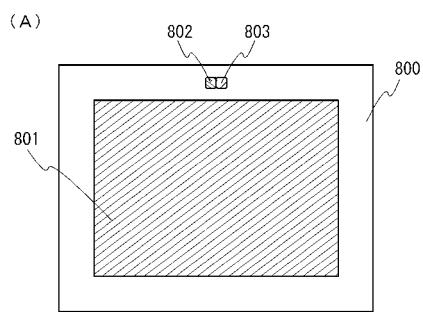

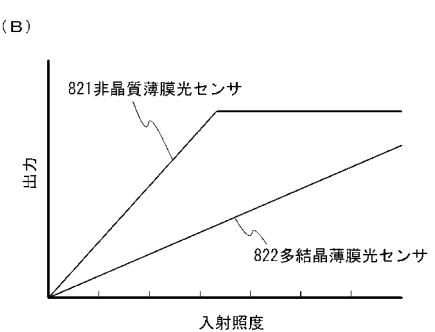

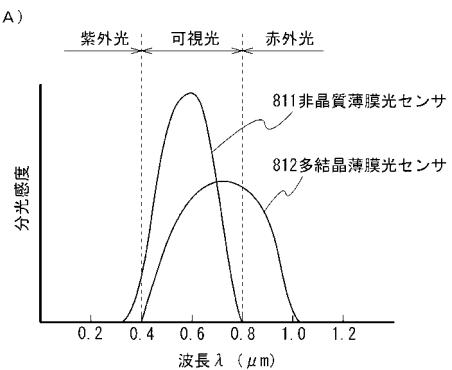

図2(A)は、光電変換素子に非晶質半導体として非晶質シリコン薄膜を用いた光センサ(以下、非晶質薄膜光センサという)と、光電変換素子に多結晶半導体として多結晶シリコン薄膜を用いた光センサ(以下、多結晶薄膜光センサという)の光感度特性を示す図である。図2(A)中、特性 811 は非晶質薄膜光センサの光感度特性を示し、特性 812 が多結晶薄膜光センサの光感度特性を示している。

#### 【0034】

非晶質薄膜光センサおよび多結晶薄膜光センサとも、波長 0.4 ~ 0.8 μm の可視光に対して光感度を有している。また、非晶質薄膜光センサは可視光に対しての光感度が大きく、波長 0.6 μm 付近に最大感度を有している。多結晶薄膜光センサは、可視光に対する光感度は非晶質薄膜光センサよりも小さいものの、波長 0.7 μm 付近に最大感度を有しており、また、赤外光の検出も可能である。

#### 【0035】

図2(B)は、入射照度に対する光センサの出力の関係を説明する図である。特性 821 は非晶質薄膜光センサの入射照度と出力の関係を示しており、特性 822 は多結晶薄膜光センサの入射照度と出力の関係を示している。非晶質薄膜光センサは可視光に対して光感度が大きいため、比較的暗い環境下においても正確に照度を測定することができるが、屋外などの照度が強いところでは出力が飽和してしまい、正確な照度を測定することができない。一方、多結晶薄膜光センサは、非晶質薄膜光センサよりも可視光に対して光感度が小さいため、入射照度が強くても出力が飽和しにくく、照度を正確に測定することができる。

#### 【0036】

可視光に対して異なる光感度を持つ光センサを用いることで、表示装置周囲の明るさをより正確に検出し、表示装置の輝度を最適な状態とすることができる。

#### 【0037】

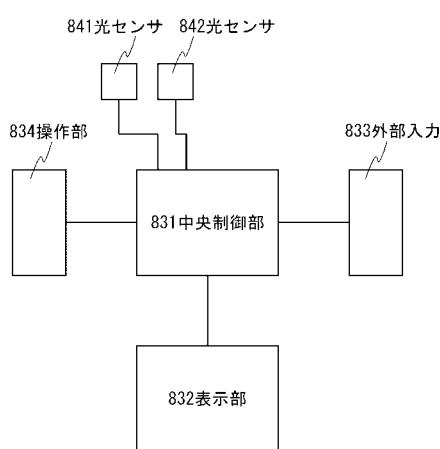

図3は、本実施の形態を適用した表示装置のブロック図である。中央制御部 831 は入出力ポート、メモリなどを有している。外部入力 833 は、外部からの映像信号の入り口であり、各種映像信号は外部入力 833 を通じて中央制御部 831 に入力される。使用者は操作部 834 において、輝度や色調などを別途設定することができる。光センサ 841 及び光センサ 842 は、可視光の検出感度が異なる光センサであり、例えば、光センサ 841 として非晶質薄膜光センサを用い、光センサ 842 として多結晶薄膜光センサを用いる。

#### 【0038】

中央制御部 831 は、操作部 834 で設定された輝度や色調などを基に、光センサ 841 及び光センサ 842 により検出された表示装置周囲の照度を考慮して、外部入力 833 から入力された映像信号を変換し、表示部 832 に映像を表示する。

#### 【0039】

中央制御部 831 は、光センサ 841 及び光センサ 842 の双方の信号出力を比較し、通常は信号強度の強い光センサ 841 (非晶質薄膜光センサ) の出力をもとに表示部 832 に表示する映像の輝度補正を行う。ただし、信号強度が強くても、信号出力が飽和している場合は、光センサ 842 (多結晶薄膜光センサ) の信号出力をもとに表示部 832 に表

10

20

30

40

50

示する映像の輝度補正を行う。このようにして、光センサ 841 と光センサ 842 を使い分けることで、表示装置周囲の照度変化が大きくて適切に輝度補正を行うことができる。

#### 【0040】

また、図 2 (A) で示した通り、非晶質薄膜光センサである光センサ 841 は赤外光を検出しないが、多結晶薄膜光センサである光センサ 842 は赤外光も検出する。この特性差を利用し、中央制御部 831 に予め記憶させた算出方法を用いて双方の出力差を検出することで、表示装置周囲の赤外光の照度を検出することができる。

#### 【0041】

例えば、通常は室内よりも屋外の方が赤外光の照度が強いため、赤外光の照度が強い場合は、可視光の照度を基にした輝度補正のみでなく、屋外使用を前提とした色調補正を同時にを行うことで、表示品質を改善することができる。

10

#### 【0042】

非晶質薄膜光センサは、例えば非晶質シリコン膜を用いた p-i-n 型のフォトダイオードを用いることができる。まず、第 1 の半導体層として p 型の導電型を有する半導体層を形成し、次に第 2 の半導体層として高抵抗な半導体層 (i 型半導体層) を形成し、次に第 3 の半導体層として n 型の導電型を有する半導体層を形成する。

#### 【0043】

第 1 の半導体層は p 型半導体層であり、p 型を付与する不純物元素を含む非晶質シリコン膜により形成することができる。第 1 の半導体層は、13 族の不純物元素（例えばボロン (B)）を含む半導体材料ガスを用いて、プラズマ CVD 法により形成する。半導体材料ガスとしてはシラン ( $\text{SiH}_4$ ) を用いればよい。または、 $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHC}_1{}_3$ 、 $\text{SiC}_1{}_4$ 、 $\text{SiF}_4$  等を用いてもよい。また、不純物元素を含まない非晶質シリコン膜を形成した後に、拡散法やイオン注入法を用いて該非晶質シリコン膜に不純物元素を導入してもよい。イオン注入法等により不純物元素を導入した後に加熱等を行うことで、不純物元素を拡散させるとよい。この場合に非晶質シリコン膜を形成する方法としては、LPCVD 法、気相成長法、又はスパッタリング法等を用いればよい。第 1 の半導体層の膜厚は 10 nm 以上 50 nm 以下となるよう形成することが好ましい。

20

#### 【0044】

第 2 の半導体層は、i 型半導体層（真性半導体層）であり、非晶質シリコン膜により形成する。第 2 の半導体層は、半導体材料ガスを用いて、非晶質シリコン膜を plasma CVD 法により形成する。半導体材料ガスとしては、シラン ( $\text{SiH}_4$ ) を用いればよい。または、 $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHC}_1{}_3$ 、 $\text{SiC}_1{}_4$ 、 $\text{SiF}_4$  等を用いてもよい。第 2 の半導体層の形成は、LPCVD 法、気相成長法、スパッタリング法等により行っても良い。第 2 の半導体層の膜厚は 200 nm 以上 1000 nm 以下となるように形成することが好ましい。

30

#### 【0045】

第 3 の半導体層は、n 型半導体層であり、n 型を付与する不純物元素を含む非晶質シリコン膜により形成する。第 3 の半導体層は、15 族の不純物元素（例えばリン (P)）を含む半導体材料ガスを用いて、プラズマ CVD 法により形成する。半導体材料ガスとしてはシラン ( $\text{SiH}_4$ ) を用いればよい。または、 $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHC}_1{}_3$ 、 $\text{SiC}_1{}_4$ 、 $\text{SiF}_4$  等を用いてもよい。また、不純物元素を含まない非晶質シリコン膜を形成した後に、拡散法やイオン注入法を用いて該非晶質シリコン膜に不純物元素を導入してもよい。イオン注入法等により不純物元素を導入した後に加熱等を行うことで、不純物元素を拡散させるとよい。この場合に非晶質シリコン膜を形成する方法としては、LPCVD 法、気相成長法、又はスパッタリング法等を用いればよい。第 3 の半導体層の膜厚は 20 nm 以上 200 nm 以下となるよう形成することが好ましい。

40

#### 【0046】

また、第 1 の半導体層、第 2 の半導体層、及び第 3 の半導体層として、非晶質半導体ではなく多結晶半導体もしくは微結晶半導体を用いることで、多結晶薄膜光センサを形成する

50

ことができる。また、第2の半導体層のみを多結晶半導体もしくは微結晶半導体で形成してもよい。

#### 【0047】

微結晶半導体は、ギブスの自由エネルギーを考慮すれば非晶質と単結晶の中間的な準安定状態に属するものである。すなわち、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する。柱状または針状結晶が基板表面に対して法線方向に成長している。微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルが単結晶シリコンを示す  $520\text{ cm}^{-1}$  よりも低波数側に、シフトしている。即ち、単結晶シリコンを示す  $520\text{ cm}^{-1}$  と非晶質シリコンを示す  $480\text{ cm}^{-1}$  の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手（ダングリングボンド）を終端するため水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体膜が得られる。

10

#### 【0048】

この微結晶半導体膜は、周波数が数十MHz～数百MHzの高周波プラズマCVD法、または周波数が1GHz以上のマイクロ波プラズマCVD装置により形成することができる。代表的には、 $\text{SiH}_4$ 、 $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ などの水素化珪素を水素で希釈して形成することができる。また、水素化珪素及び水素に加え、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して微結晶半導体膜を形成することができる。これらのときの水素化珪素に対して水素の流量比を5倍以上200倍以下、好ましくは50倍以上150倍以下、更に好ましくは100倍とする。さらには、シリコンを含む気体中に、 $\text{CH}_4$ 、 $\text{C}_2\text{H}_6$ 等の炭化物気体、 $\text{GeH}_4$ 、 $\text{GeF}_4$ 等のゲルマニウム化気体、 $\text{F}_2$ 等を混入させてよい。

20

#### 【0049】

また、光電効果で発生した正孔の移動度は電子の移動度に比べて小さいため、半導体層を積層して形成するpin型フォトダイオードの場合は、p型の半導体層側を受光面とするとい。

#### 【0050】

このようにして、可視光に対して異なる光感度を持つ非晶質薄膜光センサと多結晶薄膜光センサを用いることで、周囲の照度を正確に検出し、表示装置の発光輝度を最適な状態とすることで、使用者の体感上の輝度変化を軽減し、消費電力の増加を抑えることができる。また、非晶質薄膜光センサと多結晶薄膜光センサの出力差により赤外光の照度を検出し、表示部の色調補正を行うことで、表示品質を改善することができる。

30

#### 【0051】

##### (実施の形態2)

本実施の形態では、光センサを内蔵する表示装置の実施の形態1とは異なる形態について説明する。

#### 【0052】

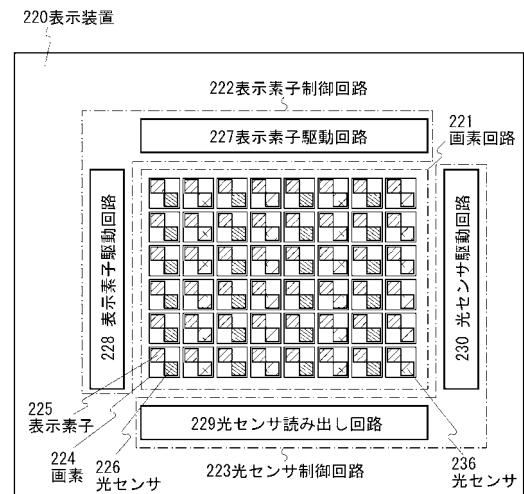

表示装置の一例として、本実施の形態では液晶表示装置を例として図4を参照して説明する。表示装置220は、画素回路221、表示素子制御回路222及び光センサ制御回路223を有する。画素回路221は、マトリクス状に配置された複数の画素224を有する。各々の画素224は、表示素子225と光センサ226もしくは光センサ236を有する。

40

#### 【0053】

光センサ226は、実施の形態1で説明した非晶質薄膜光センサであり、光センサ236は多結晶薄膜光センサである。図4では、光センサ226を有する画素と、光センサ236を有する画素が一列ずつ交互に配置する例が示されているが、特にこれに限定されない。例えば、すべての画素に光センサ226もしくは光センサ236が配置されていなくてよく、一画素おきまたは数画素おきに配置されていてもよい。

50

**【 0 0 5 4 】**

表示素子 225 は、トランジスタ、保持容量、液晶層を有する液晶素子などを有する。トランジスタは、保持容量への電荷の注入もしくは排出を制御する機能を有する。保持容量は、液晶層に印加する電圧に相当する電荷を保持する機能を有する。液晶層に電圧を印加することで偏光方向が変化する現象を利用して、液晶層を透過する光の明暗（階調）を作り、画像表示が実現される。液晶表示装置には、光源（バックライト）を液晶層の後面側に設け、光源から液晶層を透過してきた光で画像を表示する透過型液晶表示装置と、外光もしくは液晶層の前面側に設けた光源（フロントライト）の光を反射させて画像を表示する反射型液晶表示装置がある。

**【 0 0 5 5 】**

10

なお、カラー画像表示を行う方式として、カラーフィルタを用いる方式、所謂、カラーフィルタ方式がある。これは、液晶層を透過した光がカラーフィルタを通過することで、特定の色（例えば、赤（R）、緑（G）、青（B））の階調を作ることができる。ここで、カラーフィルタ方式を用いる際に、赤（R）、緑（G）、青（B）のいずれかの色を発光する機能を有する画素 224 を、各々、R 画素、G 画素、B 画素と呼ぶことにする。なお、白黒画像表示のみを行う場合は、カラーフィルタを用いなくてもよい。

**【 0 0 5 6 】**

また、カラー画像表示を行う別的方式として、バックライトを特定の色（例えば、赤（R）、緑（G）、青（B））の光源で構成して各色を順次点灯する方式、所謂、フィールドシーケンシャル方式がある。フィールドシーケンシャル方式では、各色の光源が点灯している期間に、液晶層を透過する光の明暗を作ることで、当該色の階調を作ることができる。

20

**【 0 0 5 7 】**

なお、表示素子 225 が液晶素子を有する場合について説明したが、発光素子などの他の素子を有していてもよい。発光素子は、電流または電圧によって輝度が制御される素子であり、具体的には発光ダイオード、EL 素子（有機 EL 素子（Organic Light Emitting Diode：OLED）、無機 EL 素子）などが挙げられる。

**【 0 0 5 8 】**

30

本実施の形態で示す光センサ 226 及び光センサ 236 は、フォトダイオードなど、受光することで電気信号を発する機能を有する素子（光電変換素子）と、トランジスタとを有する。

**【 0 0 5 9 】**

表示素子制御回路 222 は、表示素子 225 を制御するための回路であり、ビデオデータ信号線などの信号線（「ソース信号線」ともいう）を介して表示素子 225 に信号を入力する表示素子駆動回路 227 と、走査線（「ゲート信号線」ともいう）を介して表示素子 225 に信号を入力する表示素子駆動回路 228 を有する。例えば、表示素子駆動回路 228 は、特定の行に配置された画素が有する表示素子 225 を選択する機能を有する。また、表示素子駆動回路 227 は、選択された行の画素が有する表示素子 225 に任意の電位を与える機能を有する。なお、表示素子駆動回路 228 により高電位を印加された表示素子では、トランジスタが導通状態となり、表示素子駆動回路 227 により与えられる電位が供給される。

40

**【 0 0 6 0 】**

光センサ制御回路 223 は、光センサ 226 を制御するための回路であり、光センサ出力信号線、光センサ基準信号線などの光センサ読み出し回路 229 と、光センサ駆動回路 230 を有する。光センサ駆動回路 230 は、特定の行に配置された画素が有する光センサ 226 に対して、後述するリセット動作と選択動作とを行う機能を有する。また、光センサ読み出し回路 229 は、選択された行の画素が有する光センサ 226 の出力信号を取り出す機能を有する。なお、光センサ読み出し回路 229 は、アナログ信号である光センサの出力を、OP アンプを用いてアナログ信号のまま表示装置外部に取り出す構成や、A/D 変換回路を用いてデジタル信号に変換してから表示装置外部に取り出す構成としてもよ

50

い。

**【 0 0 6 1 】**

光センサを含む表示装置 220において、酸化物半導体を用いたトランジスタを有する回路を設ける構成とする。

**【 0 0 6 2 】**

光センサを含む表示装置 220に含まれる酸化物半導体層を用いるトランジスタは、その電気的特性変動を抑止するため、変動要因となる水素、水分、水酸基又は水素化物（水素化合物ともいう）などの不純物を酸化物半導体層より意図的に排除し、かつ不純物の排除工程によって同時に減少してしまう酸化物半導体を構成する主成分材料である酸素を供給することによって、酸化物半導体層を高純度化及び電気的に i 型（真性）化する。

10

**【 0 0 6 3 】**

よって酸化物半導体中の水素及びキャリアは少なければ少ないほどよく、本明細書に開示するトランジスタは、酸化物半導体に含まれる水素が  $5 \times 10^{19} / \text{cm}^3$  以下、好ましくは  $5 \times 10^{18} / \text{cm}^3$  以下、より好ましくは  $5 \times 10^{17} / \text{cm}^3$  以下か、または  $1 \times 10^{16} / \text{cm}^3$  未満として、酸化物半導体に含まれる水素をゼロに近いほど極力除去し、キャリア密度を  $1 \times 10^{14} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{12} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満とした酸化物半導体でチャネル形成領域が形成されるトランジスタである。

**【 0 0 6 4 】**

酸化物半導体を用いたトランジスタは、酸化物半導体中にキャリアが極めて少ない（ゼロに近い）ため、トランジスタのオフ電流を少なくすることができる。トランジスタのオフ電流は少なければ少ないほど好ましい。オフ電流とは、-1V ~ -10V の間のいずれかのゲート電圧を印加した場合のトランジスタのソース、ドレイン間を流れる電流のことであり、本明細書に開示する酸化物半導体を用いたトランジスタは、チャネル幅 (W) 1 μmあたりの電流値が 10aA / μm 以下、好ましくは 1aA / μm 以下、さらに好ましくは 1zA / μm 以下である。さらに、pn接合がなく、ホットキャリア劣化がないため、トランジスタの電気的特性がこれらの影響を受けない。

20

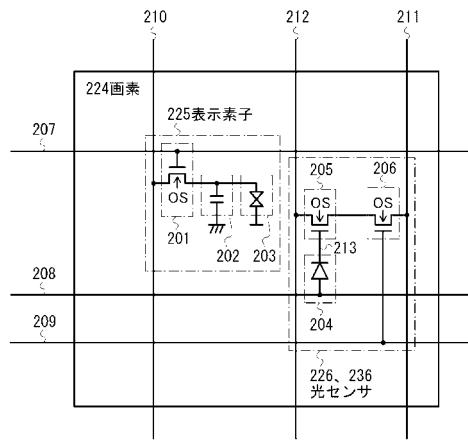

**【 0 0 6 5 】**

画素 224 の回路図の一例について、図 5 を用いて説明する。画素 224 は、トランジスタ 201、保持容量 202 及び液晶素子 203 を有する表示素子 225 と、フォトダイオード 204、トランジスタ 205 及びトランジスタ 206 を有する光センサ 226 もしくは光センサ 236 とを有する。

30

**【 0 0 6 6 】**

トランジスタ 201 は、ゲートがゲート信号線 207 に、ソース又はドレインの一方がビデオデータ信号線 210 に、ソース又はドレインの他方が保持容量 202 の一方の電極と液晶素子 203 の一方の電極に電気的に接続されている。保持容量 202 の他方の電極と液晶素子 203 の他方の電極は一定の電位に保たれている。液晶素子 203 は、一対の電極と、該一対の電極の間に液晶層を含む素子である。

**【 0 0 6 7 】**

トランジスタ 201 は、ゲート信号線 207 に "H" が印加されると、ビデオデータ信号線 210 の電位を保持容量 202 と液晶素子 203 に供給する。保持容量 202 は、供給された電位を保持する。液晶素子 203 は、供給された電位により、光の透過率を変更する。

40

**【 0 0 6 8 】**

酸化物半導体を用いたトランジスタであるトランジスタ 201、205、206 は、オフ電流が非常に小さいため、保持容量は非常に小さくてよく、また設けなくてもよい。

**【 0 0 6 9 】**

フォトダイオード 204 は、非晶質半導体、または多結晶半導体、または微結晶半導体で形成され、一方の電極がフォトダイオードリセット信号線 208 に、他方の電極がゲート信号線 213 を介してトランジスタ 205 のゲートに電気的に接続されている。トランジ

50

スタ 2 0 5 は、ソース又はドレインの一方が光センサ基準信号線 2 1 2 に、ソース又はドレインの他方がトランジスタ 2 0 6 のソース又はドレインの一方電気的に接続されている。トランジスタ 2 0 6 は、ゲートがゲート信号線 2 0 9 に、ソース又はドレインの他方が光センサ出力信号線 2 1 1 に電気的に接続されている。

#### 【 0 0 7 0 】

なお、トランジスタ 2 0 5 とトランジスタ 2 0 6 の配置は、図 5 の構成に限定されない。例えば、トランジスタ 2 0 6 のソース又はドレインの一方が光センサ基準信号線 2 1 2 に、他方がトランジスタ 2 0 5 のソース又はドレインの一方に電気的に接続され、トランジスタ 2 0 5 のゲートがゲート信号線 2 0 9 に、ソース又はドレインの他方が光センサ出力信号線 2 1 1 に電気的に接続される構成としてもよい。

10

#### 【 0 0 7 1 】

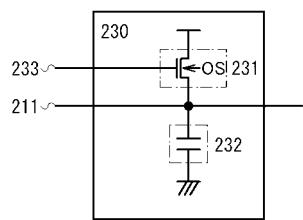

次に、光センサ読み出し回路 2 2 9 の構成の一例について、図 6 を用いて説明する。図 6 において、光センサ読み出し回路 2 2 9 が有する画素 1 列に対応する光センサ駆動回路 2 3 0 は、トランジスタ 2 3 1 と保持容量 2 3 2 を有する。また、2 1 1 は当該画素 1 列に対応する光センサ出力信号線、2 3 3 はプリチャージ信号線である。

#### 【 0 0 7 2 】

図 5 において、トランジスタ 2 0 5 、トランジスタ 2 0 6 、図 6 においてトランジスタ 2 3 1 は酸化物半導体層を用いるトランジスタである。

#### 【 0 0 7 3 】

図 4 に示した光センサ読み出し回路 2 2 9 が有する画素 1 列に対応する光センサ駆動回路 2 3 0 では、画素内における光センサの動作に先立ち、光センサ出力信号線 2 1 1 の電位を基準電位に設定する。光センサ出力信号線 2 1 1 に設定する基準電位は高電位でも低電位でもよい。図 6 では、プリチャージ信号線 2 3 3 を " H " とすることで、光センサ出力信号線 2 1 1 を基準電位である高電位に設定することができる。なお、保持容量 2 3 2 は、光センサ出力信号線 2 1 1 の寄生容量が大きい場合には、特別に設けなくても良い。

20

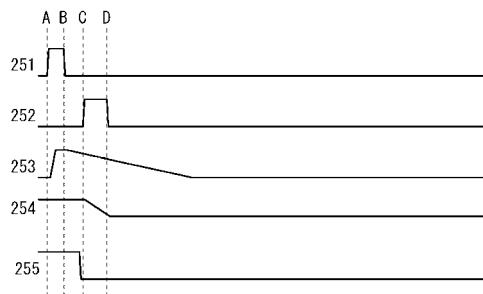

#### 【 0 0 7 4 】

次に、表示装置における光センサの読み出し動作の一例について、図 7 のタイミングチャートを用いて説明する。図 7 において、信号 2 5 1 ~ 信号 2 5 4 は、図 5 におけるフォトダイオードリセット信号線 2 0 8 、トランジスタ 2 0 6 のゲートが接続されたゲート信号線 2 0 9 、トランジスタ 2 0 5 のゲートが接続されたゲート信号線 2 1 3 、光センサ出力信号線 2 1 1 の電位に相当する。また、信号 2 5 5 は、図 6 におけるプリチャージ信号線 2 3 3 の電位に相当する。

30

#### 【 0 0 7 5 】

時刻 A において、フォトダイオードリセット信号線 2 0 8 の電位（信号 2 5 1 ）を " H " とする（リセット動作）と、フォトダイオード 2 0 4 が導通し、トランジスタ 2 0 5 のゲートが接続されたゲート信号線 2 1 3 の電位（信号 2 5 3 ）が " H " となる。また、プリチャージ信号線 2 3 3 の電位（信号 2 5 5 ）を " H " とすると、光センサ出力信号線 2 1 1 の電位（信号 2 5 4 ）は " H " にプリチャージされる。

#### 【 0 0 7 6 】

時刻 B において、フォトダイオードリセット信号線 2 0 8 の電位（信号 2 5 1 ）を " L " にする（累積動作）と、フォトダイオード 2 0 4 の光電流により、トランジスタ 2 0 5 のゲートが接続されたゲート信号線 2 1 3 の電位（信号 2 5 3 ）が低下し始める。フォトダイオード 2 0 4 は、光が照射されると光電流が増大するので、照射される光の量に応じてトランジスタ 2 0 5 のゲートが接続されたゲート信号線 2 1 3 の電位（信号 2 5 3 ）は変化する。すなわち、トランジスタ 2 0 5 のソースとドレイン間の電流が変化する。

40

#### 【 0 0 7 7 】

時刻 C において、ゲート信号線 2 0 9 の電位（信号 2 5 2 ）を " H " にする（選択動作）と、トランジスタ 2 0 6 が導通し、光センサ基準信号線 2 1 2 と光センサ出力信号線 2 1 1 とが、トランジスタ 2 0 5 とトランジスタ 2 0 6 とを介して導通する。すると、光センサ出力信号線 2 1 1 の電位（信号 2 5 4 ）は、低下していく。なお、時刻 C 以前に、プリ

50

チャージ信号線 233 の電位（信号 255）を”L”とし、光センサ出力信号線 211 のプリチャージを終了しておく。ここで、光センサ出力信号線 211 の電位（信号 254）が特定の電位に達するまでの時間（電位が変化する速さ）は、トランジスタ 205 のソースとドレイン間の電流に依存する。すなわち、フォトダイオード 204 に照射されている光の量に応じて変化する。

#### 【0078】

時刻 Dにおいて、ゲート信号線 209 の電位（信号 252）を”L”にすると、トランジスタ 206 が遮断され、光センサ出力信号線 211 の電位（信号 254）は、時刻 D以後、一定値となる。ここで、一定値となる電位は、フォトダイオード 204 に照射されている光の量に応じて変化する。したがって、光センサ出力信号線 211 の電位を取得することで、フォトダイオード 204 に照射されている光の量を知ることができる。10

#### 【0079】

上記のように、個々の光センサの動作は、リセット動作、累積動作、選択動作を繰り返すことで実現される。表示装置において高速撮像を実現するためには、全画素のリセット動作、累積動作、選択動作を高速に実行することが必要である。また、図 5 におけるトランジスタ 206 のオフリーク電流が大きいと、トランジスタ 205 を介して、光センサ出力信号線 211 から、光センサ基準信号線 212 ヘリーケ電流が流れてしまう。すると、リセット動作中にトランジスタ 205 のゲート電圧が所望の電圧に達しない、光センサ出力信号線 211 及び光センサ基準信号線 212 の電位が不安定になる、などの光センサ動作の不具合が生じる恐れがある。20

#### 【0080】

しかし、本明細書に開示する発明においては、トランジスタ 206 を、酸化物半導体を用いたトランジスタで形成しており、オフ電流が非常に小さいので上記不具合を低減することができる。

#### 【0081】

本実施の形態では、光センサを表示部外ではなく表示部内に設けることで、より正確に輝度や色調の補正が可能となる。また、光センサを表示部内に設けることで、光センサが隠される可能性が極めて低くなる。

#### 【0082】

また、画素内の光センサ上にカラーフィルタを設けることで、表示装置周囲の照度を R G B の各色成分に分光して検出することができる。表示装置周囲の照度を R G B に分光して検出することで、表示装置周囲の色温度や色度分布をより正確に検出し、表示映像の緻密な色調補正を実現することができる。30

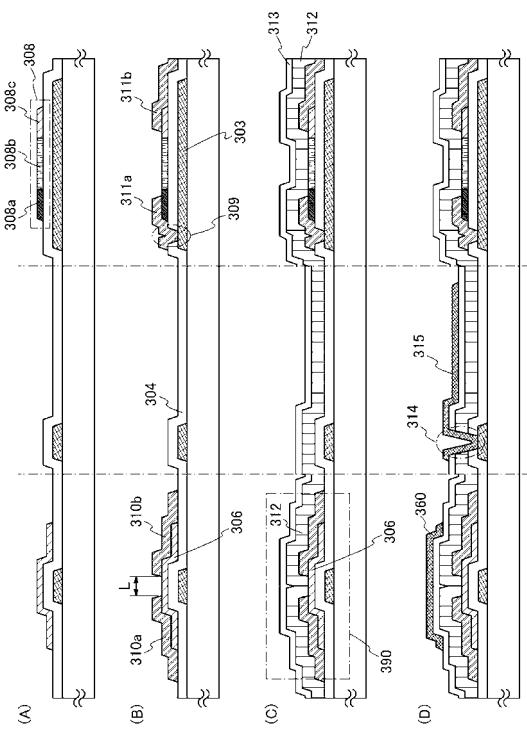

#### 【0083】

##### （実施の形態 3）

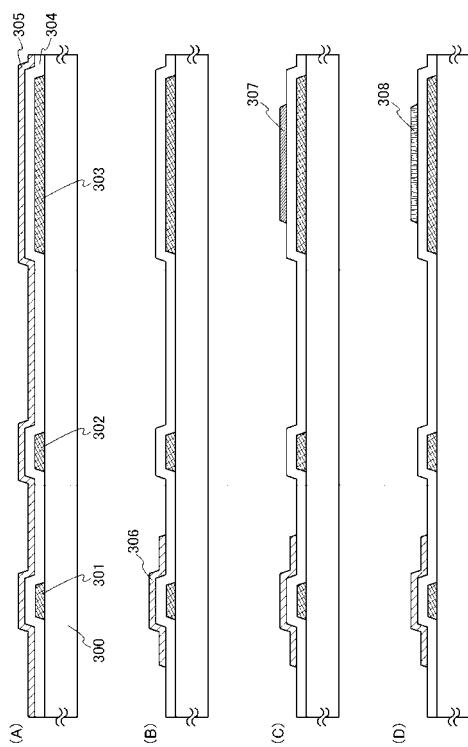

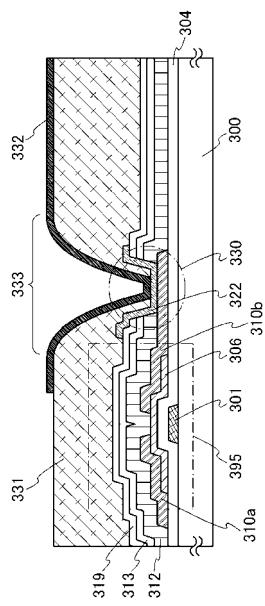

本実施の形態は、実施の形態 1 及び実施の形態 2 で説明したトランジスタ及び光センサの作製工程の一例を、図 8 乃至図 11 の断面図を参照して説明する。図 10 (B) に示すトランジスタ 390 はボトムゲート構造の一種であり、逆スタガ型トランジスタもしくはチャネルエッチ型トランジスタともいう。光センサ 391 は非晶質薄膜光センサであり、非晶質シリコンで形成した p 層、i 層、及び n 層を積層した p i n 型のフォトダイオードを有している。光センサ 392 は多結晶薄膜光センサであり、光電変換素子として一つの多結晶シリコンもしくは微結晶シリコン層中に、p 層、i 層、及び n 層を形成した p i n 型のフォトダイオードを有している。なお、光センサ 391 及び光センサ 392 は、基板側から入射する光ではなく、絶縁層 312 側から入射する外光 350 を検出することを前提としている。40

#### 【0084】

なお、本実施の形態で示す光センサ 391 及び光センサ 392 は、光センサの光電変換素子部分であるフォトダイオードの断面構造を示している。光センサのトランジスタ部分はトランジスタ 390 と同様に作製することができる。

#### 【0085】

10

20

30

40

50

また、トランジスタ390はシングルゲート構造のトランジスタを用いて説明するが、必要に応じて、チャネル形成領域を複数有するマルチゲート構造のトランジスタとして形成することもできる。

#### 【0086】

以下、図8乃至図10を用いて、基板300上にトランジスタ390を作製する工程を説明する。

#### 【0087】

まず、絶縁表面を有する基板300上に導電層を形成した後、第1のフォトリソグラフィ工程によりゲート電極層301、配線層302及び配線層303を形成する。形成されたゲート電極層及び配線層の端部がテーパー形状であると、上に積層するゲート絶縁層の被覆性が向上するため好ましい。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。10

#### 【0088】

基板300は、ガラス基板、セラミック基板、石英基板、サファイア基板の他、本作製工程の処理温度に耐えうる程度の耐熱性を有するプラスチック基板等を用いることができる。また、基板に透光性を要しない場合には、ステンレス合金等の金属の基板の表面に絶縁膜を設けたものを用いてもよい。他にも、結晶化ガラスなどを用いることができる。

#### 【0089】

ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730以上の中を用いると良い。また、ガラス基板には、例えば、バリウムホウケイ酸ガラス、アルミニウムホウケイ酸ガラス若しくはアルミニノケイ酸ガラス等の無アルカリガラス基板を用いるとよい。なお、酸化ホウ素( $B_2O_3$ )と比較して酸化バリウム(BaO)を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、 $B_2O_3$ よりBaOを多く含むガラス基板を用いることが好ましい。20

#### 【0090】

また、基板300として、第3世代(550mm×650mm)、第3.5世代(600mm×720mm、または620mm×750mm)、第4世代(680mm×880mm、または730mm×920mm)、第5世代(1100mm×1300mm)、第6世代(1500mm×1850mm)、第7世代(1870mm×2200mm)、第8世代(2200mm×2400mm)、第9世代(2400mm×2800mm、または2450mm×3050mm)、第10世代(2950mm×3400mm)等のガラス基板を用いることができる。30

#### 【0091】

基板300とゲート絶縁層304との間に、下地絶縁層を設けてもよい。下地絶縁層は、基板300からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。下地絶縁層は、スパッタリング法、CVD法、塗布法、印刷法等を適宜用いて形成することができる。下地絶縁膜の膜中にハロゲン元素、例えばフッ素、塩素等を少量添加し、ナトリウム等の可動イオンの固定化をさせてもよい。下地絶縁膜に含まれるハロゲン元素の濃度は、SIMS(二次イオン質量分析法)を用いた分析により得られる濃度ピークが $1 \times 10^{15} \text{ cm}^{-3}$ 以上 $1 \times 10^{20} \text{ cm}^{-3}$ 以下の範囲内とすることが好ましい。40

#### 【0092】

また、ゲート電極層301、配線層302及び配線層303(これと同じ層で形成される配線層や電極層を含む)の材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層又は積層して形成することができる。

#### 【0093】

例えば、ゲート電極層301、配線層302及び配線層303の2層の積層構造としては50

、アルミニウム層上にモリブデン層が積層された2層の積層構造、銅層上にモリブデン層を積層した2層構造、銅層上に窒化チタン層若しくは窒化タンタル層を積層した2層構造、窒化チタン層とモリブデン層とを積層した2層構造、又は窒化タンゲステン層とタンゲステン層とを積層した2層構造とすることが好ましい。3層の積層構造としては、タンゲステン層または窒化タンゲステン層と、アルミニウムとシリコンの合金層またはアルミニウムとチタンの合金層と、窒化チタン層またはチタン層とを積層した積層とすることが好ましい。

#### 【0094】

次いで、ゲート電極層301、配線層302及び配線層303上にゲート絶縁層304を形成する。

10

#### 【0095】

ゲート絶縁層304は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。スパッタリング法により酸化シリコン膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。

#### 【0096】

なお、後に形成する高純度化された酸化物半導体（不純物を除去することによりi型化又は実質的にi型化された酸化物半導体）は、界面準位、界面電荷に対して極めて敏感となるため、高純度化された酸化物半導体とゲート絶縁層（GI）の界面特性は特に重要である。そのため高純度化された酸化物半導体に接するゲート絶縁層は、高品質化が要求される。

20

#### 【0097】

例えば、μ波（2.45GHz）を用いた高密度プラズマCVD法は、緻密で絶縁耐圧の高い高品質な絶縁層を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁層とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

#### 【0098】

もちろん、ゲート絶縁層として良質な絶縁層を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理によってゲート絶縁層の膜質、酸化物半導体との界面特性が改質される絶縁層であっても良い。いずれにしても、ゲート絶縁層としての膜質が良好であることは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

30

#### 【0099】

さらに、トランジスタに対して行う85、 $2 \times 10^6$ V/cm、12時間のゲートバイアス・熱ストレス試験（BT試験）においては、酸化物半導体に不純物が含まれていると、不純物と酸化物半導体の主成分との結合手が、強電界（B：バイアス）と高温（T：温度）により切断され、生成された未結合手がしきい値電圧（Vth）のドリフトを誘発することとなる。

40

#### 【0100】

これに対して、本明細書に開示する発明は、酸化物半導体の不純物、特に水素や水等を極力除去し、上記のようにゲート絶縁層との界面特性を良好にすることにより、BT試験に対しても安定なトランジスタを得ることを可能としている。

#### 【0101】

ゲート絶縁層304は、ゲート電極層301側から窒化物絶縁層と、酸化物絶縁層との積層構造とすることもできる。例えば、第1のゲート絶縁層としてスパッタリング法により膜厚50nm以上200nm以下の窒化シリコン層（SiNy(y>0)）を形成し、第1のゲート絶縁層上に第2のゲート絶縁層として膜厚5nm以上300nm以下の酸化シリコン層（SiOx(x>0)）を積層して、膜厚100nmのゲート絶縁層とする。ゲ

50

ート絶縁層の膜厚は、トランジスタに要求される特性によって適宜設定すればよく 350 nm 乃至 400 nm 程度でもよい。

#### 【0102】

また、ゲート絶縁層 304 として、ハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムアルミネート ( $HfAl_xO_y$  ( $x > 0$ ,  $y > 0$ ))、酸化ハフニウム、酸化イットリウムなどの hight-k 材料を用いることでゲートリーク電流を低減できる。さらには、high-k 材料と、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、または酸化アルミニウムのいずれか一以上との積層構造とすることができる。

10

#### 【0103】

また、ゲート絶縁層 304 に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極層 301 が形成された基板 300、又はゲート絶縁層 304 までが形成された基板 300 を予備加熱し、基板 300 に吸着した水素、水分などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度としては、100 以上 400 以下 好ましくは 150 以上 300 以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。

#### 【0104】

次いで、ゲート絶縁層 304 上に、スパッタリング法により膜厚 2 nm 以上 200 nm 以下の酸化物半導体層 305 を形成する（図 8 (A) 参照。）。

20

#### 【0105】

酸化物半導体層 305 はスパッタリング法により成膜する。酸化物半導体層 305 としては、四元系金属酸化物である In - Sn - Ga - Zn - O 膜や、三元系金属酸化物である In - Ga - Zn - O 膜、In - Sn - Zn - O 膜、In - Al - Zn - O 膜、Sn - Ga - Zn - O 膜、Al - Ga - Zn - O 膜、Sn - Al - Zn - O 膜や、二元系金属酸化物である In - Zn - O 膜、Sn - Zn - O 膜、Al - Zn - O 膜、Zn - Mg - O 膜、Sn - Mg - O 膜、In - Mg - O 膜、In - Ga - O 膜や、In - O 膜、Sn - O 膜、Zn - O 膜などの酸化物半導体層を用いることができる。また、上記酸化物半導体層に SiO<sub>2</sub> を含んでもよい。

30

#### 【0106】

酸化物半導体層 305 をスパッタリング法で作製するためのターゲットとして、酸化亜鉛を主成分とする金属酸化物のターゲットを用いることができる。また、金属酸化物のターゲットの他の例としては、In、Ga、及び Zn を含む金属酸化物ターゲット（組成比として、 $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 1$  [mol 数比]、 $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 2$  [mol 数比]）を用いることができる。また、In、Ga、及び Zn を含む金属酸化物ターゲットとして、 $In_2O_3 : Ga_2O_3 : ZnO = 2 : 2 : 1$  [mol 数比]、または  $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 4$  [mol 数比] の組成比を有するターゲットを用いることもできる。金属酸化物ターゲットの充填率は 90% 以上 100% 以下、好ましくは 95% 以上 99.9% 以下である。充填率の高い金属酸化物ターゲットを用いて形成した酸化物半導体層 305 は緻密な膜となる。

40

#### 【0107】

本実施の形態では、酸化物半導体層 305 を In - Ga - Zn - O 系金属酸化物ターゲットを用いてスパッタリング法により成膜する。また、酸化物半導体層 305 は、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、又は希ガス（代表的にはアルゴン）及び酸素雰囲気下においてスパッタリング法により形成することができる。

#### 【0108】

酸化物半導体層の形成は、減圧状態に保持された処理室内に基板を保持し、基板を室温又は 400 未満の温度に加熱する。そして、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、In - Ga - Zn - O 系金属酸化物をターゲット

50

として基板 300 上に酸化物半導体層 305 を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水 (H<sub>2</sub>O) など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。また、クライオポンプにより処理室内に残留する水分を除去しながらスパッタ成膜を行うことで、酸化物半導体層 305 を成膜する際の基板温度は室温から 400 度満とすることができます。

## 【0109】

10

成膜条件の一例としては、基板とターゲットの間との距離を 100 mm、圧力 0.6 Pa、直流 (DC) 電源電力 0.5 kW、酸素（酸素流量比率 100%）雰囲気下の条件が適用される。なお、パルス直流 (DC) 電源を用いると、成膜時に発生する粉状物質（パーティクル、ゴミともいう）が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜の膜厚は好ましくは 5 nm 以上 30 nm 以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

## 【0110】

スパッタリング法にはスパッタ用電源に高周波電源を用いる RF スパッタリング法、直流電源を用いる DC スパッタリング法、さらにパルス的にバイアスを与えるパルス DC スパッタリング法がある。RF スパッタリング法は主に絶縁膜を成膜する場合に用いられ、DC スパッタリング法は主に金属膜を成膜する場合に用いられる。

20

## 【0111】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種類の材料を同時に放電させて成膜することもできる。

## 【0112】

また、チャンバー内部に磁石機構を備えたマグネットロンスパッタリング法を用いるスパッタ装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いる ECR スパッタリング法を用いるスパッタ装置がある。

## 【0113】

30

また、スパッタリング法を用いる成膜方法として、成膜中にターゲット物質とスパッタガス成分とを化学反応させてこれらの化合物薄膜を形成するリアクティブスパッタリング法や、成膜中に基板にも電圧をかけるバイアススパッタリング法もある。

## 【0114】

酸化物半導体膜を成膜する際に用いるスパッタガスとしては、水素、水、水酸基又は水素化物などの不純物が、濃度 ppm 程度、濃度 ppb 程度まで除去された高純度ガスが好ましい。

## 【0115】

次いで、酸化物半導体層 305 を第 2 のフォトリソグラフィ工程により島状の酸化物半導体層 306 に加工する（図 8 (B) 参照。）。また、島状の酸化物半導体層 306 を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

40

## 【0116】

なお、ここでの酸化物半導体層 305 のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてよい。

## 【0117】

ドライエッチングに用いるエッチングガスとしては、塩素を含むガス（塩素系ガス、例えば塩素 (Cl<sub>2</sub>)、三塩化硼素 (BCl<sub>3</sub>)、四塩化珪素 (SiCl<sub>4</sub>)、四塩化炭素 (CCl<sub>4</sub>) など）が好ましい。

## 【0118】

50

また、フッ素を含むガス（フッ素系ガス、例えば四弗化炭素（ $\text{C F}_4$ ）、六弗化硫黄（ $\text{S F}_6$ ）、三弗化窒素（ $\text{N F}_3$ ）、トリフルオロメタン（ $\text{C H F}_3$ ）など）、臭化水素（ $\text{H Br}$ ）、酸素（ $\text{O}_2$ ）、これらのガスにヘリウム（ $\text{He}$ ）やアルゴン（ $\text{Ar}$ ）などの希ガスを添加したガス、などを用いることができる。

#### 【0119】

ドライエッチング法としては、平行平板型 RIE (Reactive Ion Etching) 法や、ICP (Inductively Coupled Plasma: 誘導結合型プラズマ) エッチング法を用いることができる。所望の加工形状にエッチングできるように、エッチング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節する。

10

#### 【0120】

ウェットエッチングに用いるエッチング液としては、磷酸と酢酸と硝酸を混ぜた溶液や、アンモニア過水（31重量%過酸化水素水：28重量%アンモニア水：水 = 5 : 2 : 2 容量比）などを用いることができる。また、ITO-07N（関東化学社製）を用いてもよい。

#### 【0121】

また、ウェットエッチング後のエッチング液はエッチングされた材料とともに洗浄によって除去される。その除去された材料を含むエッチング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッチング後の廃液から酸化物半導体層に含まれるインジウム等の材料を回収して再利用することにより、資源を有効活用し低コスト化することができる。

20

#### 【0122】

所望の加工形状にエッチングできるように、材料に合わせてエッチング条件（エッチング液、エッチング時間、温度等）を適宜調節する。

#### 【0123】

次いで、ゲート絶縁層304の上に半導体層307を形成する。半導体層307としては、既知のCVD法、スパッタ法を用いて結晶構造が微結晶または多結晶である半導体層を形成することができる。CVD法で形成する場合の堆積性気体としては、シリコンまたはゲルマニウムを含むガスを用いることができる。シリコンを含む堆積性気体としては、シリラン（ $\text{SiH}_4$ ）、ジシリラン（ $\text{Si}_2\text{H}_6$ ）、ジクロロシリラン（ $\text{SiH}_2\text{Cl}_2$ ）、 $\text{SiHCl}_3$ 、塩化珪素（ $\text{SiCl}_4$ ）、フッ化珪素（ $\text{SiF}_4$ ）などを用いることができる。ゲルマニウムを含む堆積性気体としては、ゲルマン（ $\text{GeH}_4$ ）、ジゲルマン（ $\text{Ge}_2\text{H}_6$ ）、フッ化ゲルマン（ $\text{GeF}_4$ ）などを用いることができる。

30

#### 【0124】

また、多結晶半導体は、非晶質半導体または微結晶半導体を形成した後、600℃以上の加熱処理、RTA処理、またはレーザー光照射により形成することができる。RTA処理、レーザー光照射による結晶化は、半導体膜を瞬間に加熱することができるため、歪点が低い基板上に多結晶半導体を形成する場合に特に有効である。

#### 【0125】

また、非晶質半導体または微結晶半導体に、結晶化を助長する元素を接触もしくは添加することで、結晶化のための熱処理温度を450℃程度まで下げることができる。結晶化を助長する金属元素としては鉄（Fe）、ニッケル（Ni）、コバルト（Co）、ルテニウム（Ru）、ロジウム（Rh）、パラジウム（Pd）、オスニウム（Os）、イリジウム（Ir）、チタン（Ti）、白金（Pt）、銅（Cu）及び金（Au）から選ばれた一種又は複数種類を用いることができる。

40

#### 【0126】

本実施の形態では、半導体層307としてプラズマCVD法により非晶質シリコン層を形成し、第3のフォトリソグラフィ工程により島状の半導体層とする。また、結晶化を助長する金属元素として半導体層307にニッケル（Ni）を添加する。（図8（C）参照。）

50

## 【0127】

次いで、酸化物半導体層306の脱水化または脱水素化を行う。脱水化または脱水素化を行う第1の加熱処理の温度は、400以上750以下、好ましくは550以上600以下とする。この時、半導体層307の結晶化も同時に進行。なお、加熱処理時間は、1時間以上行うこととする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下において加熱処理を行った後、大気に触れることがなく、酸化物半導体層への水や水素の再混入を防ぐ。その後、同じ炉に高純度の酸素ガス、高純度のN<sub>2</sub>Oガス、又は超乾燥エア（露点が-40以下、好ましくは-60以下）を導入して冷却を行う。酸素ガスまたはN<sub>2</sub>Oガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する酸素ガスまたはN<sub>2</sub>Oガスの純度を、6N（99.9999%）以上、好ましくは7N（99.9999%）以上、（即ち酸素ガスまたはN<sub>2</sub>Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下）とすることが好ましい。10

## 【0128】

なお、加熱処理装置は電気炉に限られず、例えば、G R T A（G a s R a p i d T h e r m a l A n n e a l）装置、L R T A（L a m p R a p i d T h e r m a l A n n e a l）装置等のRTA（R a p i d T h e r m a l A n n e a l）装置を用いることができる。L R T A装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。また、L R T A装置、ランプだけでなく、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。G R T Aとは高温のガスを用いて加熱処理を行う方法である。ガスには、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。RTA法を用いて、600～750で数分間加熱処理を行ってもよい。20

## 【0129】

また、脱水化または脱水素化を行う第1の加熱処理後に200以上400以下、好ましくは200以上300以下の温度で酸素ガスまたはN<sub>2</sub>Oガス雰囲気下での加熱処理を行ってもよい。

## 【0130】

以上の工程を経ることによって、酸化物半導体層306及び半導体層307が多結晶化した半導体層308を得る。（図8（D）参照。）30

## 【0131】

本実施の形態では、半導体層308を酸化物半導体層306と同様にゲート絶縁層304上に形成しているが、半導体層308と酸化物半導体層306は異なる層位置となるように形成してもよい。例えば、半導体層307を酸化物半導体層306の下層に形成し、第1の加熱処理を行っても、酸化物半導体層306の脱水化または脱水素化と、半導体層307の多結晶化を同時に進行ことができる。

## 【0132】

なお、本実施の形態で用いる酸化物半導体は、酸化物半導体に含まれる水素が $5 \times 10^{-9} / \text{cm}^3$ 以下、好ましくは $5 \times 10^{-8} / \text{cm}^3$ 以下、より好ましくは $5 \times 10^{-7} / \text{cm}^3$ 以下か、または $1 \times 10^{-6} / \text{cm}^3$ 未満であり、酸化物半導体に含まれる水素が除去されている。即ち、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化されている。なお、酸化物半導体層中の水素濃度測定は、二次イオン質量分析法（S I M S : Secondary Ion Mass Spectroscopy）で行えばよい。40

## 【0133】

また、キャリア密度は、ホール効果（H a l l e f f e c t）測定や、C V（C a p a c i t a n c e V o l t a g e）測定により測定することができる。ホール効果測定やC V測定により測定される酸化物半導体のキャリア密度は、シリコンの真性キャリア密度50

$1.45 \times 10^{10} / \text{cm}^3$  と同等、もしくはそれ以下である。なお、フェルミディラックの分布則に従って計算すると、シリコンの真性キャリア密度は  $10^{10} / \text{cm}^3$  であるのに対し、エネルギーギャップが 3 eV 以上ある酸化物半導体の真性キャリア密度は  $10^{-7} / \text{cm}^3$  である。即ち、酸化物半導体の真性キャリア密度は、限りなくゼロに近い。

#### 【0134】

エネルギーギャップは 2 eV 以上、好ましくは 2.5 eV 以上、より好ましくは 3 eV 以上として、ドナーを形成する水素等の不純物を極力低減し、キャリア密度を  $1 \times 10^{14} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{12} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満となるようにする。即ち、酸化物半導体層のキャリア密度を限りなくゼロに近くすることができる。また、エネルギーギャップの広い酸化物半導体層を用いることで、室温から 180 度程の実用的な範囲で温度特性を安定化させることができる。

10

#### 【0135】

また、本実施の形態に係る酸化物半導体は、n 型不純物である水素を酸化物半導体から除去し、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより真性 (i 型) とし、または真性型とせんとしたものである。すなわち、不純物を添加して i 型化するのではなく、水素、水、水酸基または水素化物などの不純物を極力除去することにより、高純度化された i 型 (真性半導体) またはそれに近づけることを特徴としている。そうすることにより、フェルミ準位 ( $E_f$ ) は真性フェルミ準位 ( $E_i$ ) と同じレベルにまですることができる。

#### 【0136】

20

このように酸化物半導体に含まれる水素を徹底的に除去することにより高純度化された酸化物半導体をトランジスタのチャネル形成領域に用いることで、チャネル幅が 10 mm の場合でさえも、ドレイン電圧が 1 V 及び 10 V の場合において、ゲート電圧が -5 V から -20 V の範囲において、トランジスタのドレイン電流を  $1 \times 10^{-13} \text{ A}$  以下とすることができる。

#### 【0137】

上述の酸化物半導体を具備するトランジスタは、チャネル幅 1  $\mu\text{m}$ あたりのオフ電流を  $10 \text{ aA} / \mu\text{m}$  ( $1 \times 10^{-17} \text{ A} / \mu\text{m}$ ) 以下、好ましくは  $1 \text{ aA} / \mu\text{m}$  ( $1 \times 10^{-18} \text{ A} / \mu\text{m}$ ) 以下、さらに好ましくは  $1 \text{ zA} / \mu\text{m}$  ( $1 \times 10^{-21} \text{ A} / \mu\text{m}$ ) 以下とすることができる。このように、酸化物半導体の主成分以外の不純物、代表的には水素、水、水酸基または水素化物などが極力含まれないように高純度化することにより、トランジスタの動作を良好なものとすることができる。

30

#### 【0138】

ここで、酸化物半導体を用いたトランジスタの電導機構につき、図 15 乃至図 18 を用いて説明する。なお、以下の説明では、理解の容易のため理想的な状況を仮定しており、そのすべてが現実の様子を反映しているとは限らない。また、以下の説明はあくまでも一考察に過ぎず、発明の有効性に影響を与えるものではないことを付記する。

#### 【0139】

図 15 は、酸化物半導体を用いたトランジスタ（薄膜トランジスタ）の断面図である。ゲート電極 (G E 1) 上にゲート絶縁層 (G I) を介して酸化物半導体層 (O S) が設けられ、その上にソース電極 (S) およびドレイン電極 (D) が設けられ、ソース電極 (S) およびドレイン電極 (D) を覆うように絶縁層が設けられている。

40

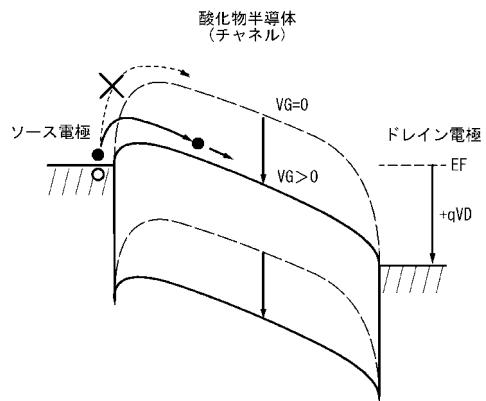

#### 【0140】

図 16 には、図 15 の A - A' 断面におけるエネルギーバンド図（模式図）を示す。また、図 16 中の黒丸 ( ) は電子を示し、白丸 ( ) は正孔を示し、それぞれは電荷 (-q, +q) を有している。ドレイン電極に正の電圧 ( $V_D > 0$ ) を印加した上で、破線はゲート電極に電圧を印加しない場合 ( $V_G = 0$ )、実線はゲート電極に正の電圧 ( $V_G > 0$ ) を印加する場合を示す。ゲート電極に電圧を印加しない場合は高いポテンシャル障壁のために電極から酸化物半導体側へキャリア（電子）が注入されず、電流を流さないオフ状態を示す。一方、ゲートに正の電圧を印加するとポテンシャル障壁が低下し、電流を流す

50

オン状態を示す。

**【0141】**

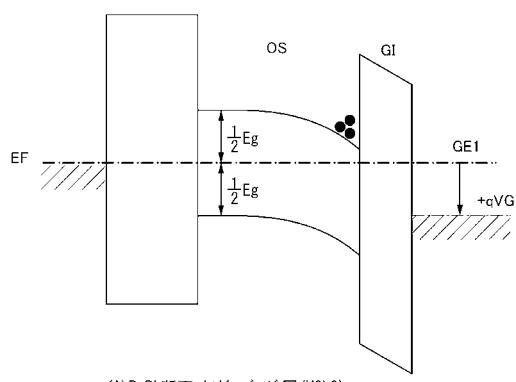

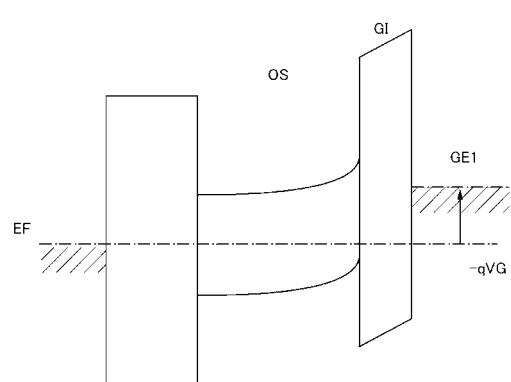

図17には、図15におけるB-B'の断面におけるエネルギー・バンド図（模式図）を示す。図17（A）は、ゲート電極（GE1）に正の電圧（ $V_G > 0$ ）が与えられた状態であり、ソース電極とドレイン電極との間にキャリア（電子）が流れるオン状態を示している。また、図17（B）は、ゲート電極（GE1）に負の電圧（ $V_G < 0$ ）が印加された状態であり、オフ状態（少数キャリアは流れない状態）である場合を示す。

**【0142】**

図18は、真空準位と金属の仕事関数（ $\phi_M$ ）、酸化物半導体の電子親和力（ $E_A$ ）の関係を示す。常温において金属中の電子は縮退しており、フェルミ準位は伝導帯内に位置する。一方、従来の酸化物半導体はn型であり、そのフェルミ準位（ $E_F$ ）は、バンドギャップ中央に位置する真性フェルミ準位（ $E_i$ ）から離れて、伝導帯寄りに位置している。なお、酸化物半導体において水素の一部はドナーとなりn型化する要因の一つであることが知られている。

10

**【0143】**

これに対して開示する発明の一態様に係る酸化物半導体は、n型化の要因である水素を酸化物半導体から除去し、酸化物半導体の主成分以外の元素（不純物元素）が極力含まれないように高純度化することにより真性（i型）とし、または真性とせんとしたものである。すなわち、不純物元素を添加してi型化するのではなく、水素や水等の不純物を極力除去することにより、高純度化されたi型（真性半導体）またはそれに近づけることを特徴としている。これにより、フェルミ準位（ $E_F$ ）は真性フェルミ準位（ $E_i$ ）と同程度とすることができる。

20

**【0144】**

酸化物半導体のバンドギャップ（ $E_g$ ）は3.15eVで、電子親和力（ $E_A$ ）は4.3Vと言われている。ソース電極およびドレイン電極を構成するチタン（Ti）の仕事関数は、酸化物半導体の電子親和力（ $E_A$ ）とほぼ等しい。この場合、金属-酸化物半導体界面において、電子に対してショットキー型の障壁は形成されない。

**【0145】**

このとき電子は、図17（A）で示すように、ゲート絶縁層と高純度化された酸化物半導体との界面付近（酸化物半導体のエネルギー的に安定な最低部）を移動する。

30

**【0146】**

また、図17（B）に示すように、ゲート電極（GE1）に負の電位が与えられると、少数キャリアであるホールは実質的にゼロであるため、電流は限りなくゼロに近い値となる。

**【0147】**

このように酸化物半導体の主成分以外の元素（不純物元素）が極力含まれないように高純度化することにより、真性（i型）とし、または実質的に真性となるため、ゲート絶縁層との界面特性が顕在化する。そのため、ゲート絶縁層には、酸化物半導体と良好な界面を形成できるものが要求される。具体的には、例えば、VHF帯～マイクロ波帯の電源周波数で生成される高密度プラズマを用いたCVD法で作製される絶縁層や、スパッタリング法で作製される絶縁層などを用いることが好ましい。

40

**【0148】**

酸化物半導体を高純度化しつつ、酸化物半導体とゲート絶縁層との界面を良好なものとすることにより、例えば、トランジスタのチャネル幅（W）が $1 \times 10^4 \mu m$ 、チャネル長（L）が $3 \mu m$ の場合には、 $10^{-13} A$ 以下のオフ電流、 $0.1 V / dec.$ のサブスレッショルドスイング値（S値）（ゲート絶縁層の厚さ：100nm）が実現され得る。

**【0149】**

このように、酸化物半導体の主成分以外の元素（不純物元素）が極力含まれないように高純度化することにより、トランジスタの動作を良好なものとすることができます。

**【0150】**

10

20

30

40

50

従って、単にバンドギャップの広い酸化物半導体をトランジスタに適用するのではなく、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより、キャリア密度を  $1 \times 10^{14} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{12} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満となるようにすることで、実用的な動作温度で熱的に励起されるキャリアを排除して、ソース側から注入されるキャリアのみによってトランジスタを動作させることができる。それにより、オフ電流を  $1 \times 10^{-17} \text{ A}$  以下にまで下げると共に、温度変化によってオフ電流がほとんど変化しない極めて安定に動作するトランジスタを得ることができる。

#### 【0151】

本発明の技術思想の一つは、酸化物半導体中に、更に加えることをせずに逆に不本意に存在する水、水素という不純物を除去することにより、酸化物半導体自体を高純度化することにある。すなわち、ドナー準位を構成する水または水素を除去することにより、更に酸素欠損を除去するために酸素を十分に供給することにより、酸化物半導体自体を高純度化することを特徴としている。

#### 【0152】

酸化物半導体は成膜直後ですら  $10^{20} / \text{cm}^3$  のレベルの水素が SIMS (二次イオン質量分析法) で観察される。このドナー準位を作る水または水素という不純物を意図的に除去し、更に水または水素の除去に伴い同時に減少してしまう酸素 (酸化物半導体の成分の一つ) を酸化物半導体に加えることにより、酸化物半導体を高純度化し、電気的に i 型 (真性) 半導体とすることを技術思想の一つとしている。

#### 【0153】

結果として、水素の量は少なければ少ないほど良く、酸化物半導体中のキャリアも少なければ少ないほど良い。酸化物半導体は、絶縁ゲート型トランジスタに用いる場合に半導体としてのキャリアを意図的に有するというよりも、逆に酸化物半導体のキャリアは無くしてしまい、半導体としてはキャリアを通過させる通路としての意味を与えた、いわゆる高純度化した i 型 (真性) 半導体である。

#### 【0154】

その結果、酸化物半導体中にキャリアが無い、または極めて少なくさせることにより、絶縁ゲート型トランジスタではオフ電流が少なくなるというのが本発明の一態様における技術思想である。すなわち、その指標として、キャリア密度は  $1 \times 10^{14} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{12} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満が求められる。本発明の技術思想的には、ゼロまたはゼロに近いことが理想である。

#### 【0155】

また結果として、酸化物半導体は通路 (パス) として機能し、酸化物半導体自体がキャリアを有さない、または極めて少ないように高純度化した i 型 (真性) とし、キャリアはソース側となる電極により供給される。供給の程度は、酸化物半導体の電子親和力、フェルミレベル、理想的には真性フェルミレベルと一致したフェルミレベル、及びソース、ドレインの電極の仕事関数より導かれるバリアハイド (障壁高さ) で決められる。

#### 【0156】

このため、オフ電流は少なければ少ないほど良く、ドレイン電圧を  $1 \sim 10 \text{ V}$  のいずれかの電圧とした場合の絶縁ゲート型トランジスタ特性において、オフ電流を  $10 \text{ aA} / \mu\text{m}$  (チャネル幅  $1 \mu\text{m}$  当たりの電流) 以下、好ましくは  $1 \text{ aA} / \mu\text{m}$  以下とすることができる。

#### 【0157】

次に、半導体層 308 中にドナーまたはアクセプタとなる不純物元素を添加し、n 型不純物領域 308a、p 型不純物領域 308c を形成する。不純物元素の添加は、イオンドーピング装置を用いて実現することができる。イオンドーピング装置は、ソースガスを励起してプラズマを生成し、プラズマ中からイオンを引き出し、質量分離せずにイオンを被処理物に導入する。イオンドーピング装置を用いることにより、半導体層 308 中に均一にイオンを導入することができる。なお、質量分離装置を備えているイオンドーピング装置

10

20

30

40

50

では、質量分離を伴うイオン注入を行うことができる。

**【0158】**

まず、第4のフォトリソグラフィ工程により、n型不純物領域308aとなる領域以外にレジストマスクを形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

**【0159】**

次に、本実施の形態では不純物元素を含むソースガスとしてホスフィン( $\text{PH}_3$ )を用い、n型不純物領域308aにn型を付与する不純物元素が $1 \times 10^{19} \sim 5 \times 10^{20}$ /cm<sup>3</sup>程度の濃度で含まれるように添加する。本実施の形態では、n型を付与する不純物元素としてリン(P)を用いる。

**【0160】**

次に、第5のフォトリソグラフィ工程により、p型不純物領域308cとなる領域以外にレジストマスクを形成する。

**【0161】**

次に、本実施の形態では不純物元素を含むソースガスとしてジボラン( $\text{B}_2\text{H}_6$ )を用い、p型不純物領域308cにp型を付与する不純物元素が $1 \times 10^{19} \sim 5 \times 10^{20}$ /cm<sup>3</sup>程度の濃度で含まれるように添加する。本実施の形態では、p型を付与する不純物元素としてボロン(B)を用いる。

**【0162】**

n型不純物領域308aとp型不純物領域308cに挟まれた、i型領域308bは真性半導体として機能する。真性半導体は、理想的には、不純物を含まずにフェルミレベルが禁制帯のほぼ中央に位置する半導体であるが、ドナーとなる不純物(例えば、リン(P)など)またはアクセプタとなる不純物(例えば、ボロン(B)など)を添加して、フェルミレベルが禁制帯の中央に位置するように調整してもよい。(図9(A)参照。)

**【0163】**

本実施の形態では、第1の加熱処理の後に半導体層308中に不純物を添加するが、第1の加熱処理の前に不純物を添加してもよい。

**【0164】**

なお、配線層303は基板側から入射する光が、半導体層308に当たらないようにするための遮光膜としても機能する。さらに、半導体層308を透過した外光350を反射させ、再度、半導体層308に入射させることで、光センサ392の検出感度を良好なものとすることができます。

**【0165】**

次いで、第6のフォトリソグラフィ工程によりレジストマスクを形成し、配線層303と重なるゲート絶縁層の一部を選択的にエッチング除去して、コンタクトホール309を形成した後、レジストマスクを除去する。

**【0166】**

次いで、ゲート絶縁層304、及び酸化物半導体層306上に、ソース電極層またはドレイン電極層として機能する電極層310aおよび電極層310bを形成するための導電層を形成する。導電層はスパッタリング法や真空蒸着法で形成すればよい。ソース電極層及びドレイン電極層(これと同じ層で形成される配線層や電極層を含む)となる導電層の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、Al、Cuなどの金属層の一方または双方にCr、Ta、Ti、Mo、Wなどの高融点金属層を積層させた構成としても良い。また、Si、Ti、Ta、W、Mo、Cr、Nd、Sc、YなどAl膜に生ずるヒロックやウィスカーの発生を防止する元素をAl材料に添加することで、Al材料の耐熱性を向上させることが可能となる。

**【0167】**

また、導電層は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを

10

20

30

40

50

含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、Ti膜と、そのTi膜上に重ねてアルミニウム膜を積層し、さらにその上にTi膜を成膜する3層構造などが挙げられる。

#### 【0168】

また、ソース電極層及びドレイン電極層（これと同じ層で形成される配線層を含む）となる導電層としては導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム（In<sub>2</sub>O<sub>3</sub>）、酸化スズ（SnO<sub>2</sub>）、酸化亜鉛（ZnO）、酸化インジウム酸化スズ合金（In<sub>2</sub>O<sub>3</sub>–SnO<sub>2</sub>、ITOと略記する）、酸化インジウム酸化亜鉛合金（In<sub>2</sub>O<sub>3</sub>–ZnO）または前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

10

#### 【0169】

第7のフォトリソグラフィ工程により導電層上にレジストマスクを形成し、選択的にエッチングを行って電極層310a、電極層310b、電極層311a、電極層311bを形成した後、レジストマスクを除去する（図9（B）参照。）。電極層311aは、n型不純物領域308aに接続し、コンタクトホール309を介して配線層303と接続されている。電極層311bは、p型不純物領域308cに接続し、図示していない共通配線層に接続している。また、酸化物半導体層306に接続する電極層310aおよび電極層310bのどちらか一方は、トランジスタのソース電極層として機能し、他方はトランジスタのドレイン電極層として機能する。

#### 【0170】

第7のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いる。トランジスタのチャネル長Lは、酸化物半導体層306上で隣り合い、かつ、酸化物半導体層306と接する電極層310aの端部と、酸化物半導体層306と接する電極層310bの端部までの距離によって決定される。なお、チャネル長L = 25nm未満の露光を行う場合には、数nm~数10nmと極めて波長が短い超紫外線（Extreme Ultraviolet）を用いて第7のフォトリソグラフィ工程でのレジストマスク形成時の露光を行う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化でき、さらにオフ電流値が極めて小さいため、低消費電力化も図ることができる。

20

#### 【0171】

なお、導電層のエッチングの際に、酸化物半導体層306は除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。

#### 【0172】

本実施の形態では、導電層としてTi膜を用いて、酸化物半導体層306にはIn-Ga-Zn-O系酸化物半導体を用いて、エッチャントとしてアンモニア過水を用いる。

#### 【0173】

なお、第7のフォトリソグラフィ工程では、酸化物半導体層306は一部のみがエッチングされ、溝部（凹部）を有する酸化物半導体層となることもある。また、電極層310a、電極層310bを形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

40

#### 【0174】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ

50

、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

#### 【0175】

第7のフォトリソグラフィ工程終了後、レジストマスクを除去した後にN<sub>2</sub>O、N<sub>2</sub>、またはArなどのガスを用いたプラズマ処理によって露出している酸化物半導体層の表面に付着した吸着水などを除去してもよい。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

#### 【0176】

プラズマ処理を行った場合、大気に触れることなく、酸化物半導体層の一部に接する保護絶縁膜となる酸化物絶縁層として絶縁層312を形成する（図9（C）参照。）。本実施の形態では、酸化物半導体層306が電極層310a、電極層310bと重ならない領域において、酸化物半導体層306と絶縁層312とが接するように形成する。10

#### 【0177】

本実施の形態では、絶縁層312として、基板300を室温又は100℃未満の温度に加熱し、シリコン半導体のターゲットを用いて、スパッタガスとして水素及び水分が除去された高純度酸素を含むガスを導入し、スパッタリング法により欠陥を含む酸化シリコン層を成膜する。

#### 【0178】

例えば、純度が6Nであり、ボロンがドープされたシリコンターゲット（抵抗値100Ω・m）を用い、基板とターゲットの間との距離（T-S間距離）を89mm、圧力0.4Pa、直流（DC）電源電力6kW、酸素（酸素流量比率100%）雰囲気下でパルスDCスパッタリング法により酸化シリコン膜を成膜する。膜厚は300nmとする。なお、シリコンターゲットに代えて石英（好ましくは合成石英）を酸化シリコン膜を成膜するためのターゲットとして用いることができる。なお、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。20

#### 【0179】

この場合において、処理室内の残留水分を除去しつつ絶縁層312を成膜することが好ましい。これは、酸化物半導体層306及び絶縁層312に水素、水酸基又は水分が含まれないようにするためである。

#### 【0180】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。30

例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水（H<sub>2</sub>O）など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した絶縁層312に含まれる不純物の濃度を低減できる。

#### 【0181】

なお、絶縁層312として、酸化シリコン層に代えて、酸化窒化シリコン層、酸化アルミニウム層、または酸化窒化アルミニウム層などを用いることもできる。

#### 【0182】

さらに、絶縁層312と酸化物半導体層306とを接した状態で100℃乃至400℃で加熱処理を行ってもよい。本実施の形態における絶縁層312は欠陥を多く含むため、この加熱処理によって酸化物半導体層306中に含まれる水素、水分、水酸基又は水素化物などの不純物を絶縁層312に拡散させ、酸化物半導体層306中に含まれる該不純物をより低減させることができる。40

#### 【0183】

酸化物絶縁層上に保護絶縁層を設けてもよい。本実施の形態では、保護絶縁層313を絶縁層312上に形成する。保護絶縁層313としては、窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、又は窒化酸化アルミニウム膜などを用いる。

#### 【0184】

保護絶縁層313として、絶縁層312まで形成された基板300を100℃～400℃

50

の温度に加熱し、水素及び水分が除去された高純度窒素を含むスパッタガスを導入しシリコンターゲットを用いて、スパッタリング法により窒化シリコン膜を成膜する。この場合においても、絶縁層312と同様に、処理室内の残留水分を除去しつつ保護絶縁層313を成膜することが好ましい。

#### 【0185】

保護絶縁層313を形成する場合、保護絶縁層313の成膜時に100～400に基板300を加熱することで、酸化物半導体層中に含まれる水素若しくは水分を酸化物絶縁層に拡散させることができる。この場合上記絶縁層312の形成後に加熱処理を行わなくてもよい。

#### 【0186】

絶縁層312として酸化シリコン層を形成し、保護絶縁層313として窒化シリコン層を積層する場合、酸化シリコン層と窒化シリコン層と同じ処理室において、共通のシリコンターゲットを用いて成膜することができる。先に酸素を含むエッチングガスを導入して、処理室内に装着されたシリコンターゲットを用いて酸化シリコン層を形成し、次にエッチングガスを、窒素を含むエッチングガスに切り替えて同じシリコンターゲットを用いて窒化シリコン層を成膜する。酸化シリコン層と窒化シリコン層とを大気に曝露せずに連続して形成することができるため、酸化シリコン層表面に水素や水分などの不純物が吸着することを防止することができる。この場合、絶縁層312として酸化シリコン層を形成し、保護絶縁層313として窒化シリコン層を積層した後、酸化物半導体層中に含まれる水素若しくは水分を酸化物絶縁層に拡散させるための加熱処理（温度100乃至400）20を行うといい。

#### 【0187】

保護絶縁層313の形成後、さらに大気中、100以上200以下、1時間以上30時間以下の加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。また、この加熱処理を、酸化物絶縁層の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。この加熱処理によって、ノーマリーオフとなるトランジスタを得ることができる。よって表示装置の信頼性を向上できる。

#### 【0188】

また、ゲート絶縁層上にチャネル形成領域とする酸化物半導体層を成膜するに際し、反応雰囲気中の残留水分を除去することで、該酸化物半導体層中の水素及び水素化物の濃度を低減することができる。

#### 【0189】

上記の工程は、液晶表示パネル、エレクトロルミネセンス表示パネル、電子インクを用いた表示装置などのバックプレーン（トランジスタが形成された基板）の製造に用いることができる。

#### 【0190】

以上の工程で、水素、水分、水酸基又は水素化物の濃度が低減された酸化物半導体層306を有するトランジスタ390を形成することができる（図9（C）参照。）。

#### 【0191】

次に、第8のフォトリソグラフィ工程により、レジストマスクを形成し、絶縁層312および保護絶縁層313を選択的にエッチング除去することにより、コンタクトホール314を形成する。

#### 【0192】

次いで、ゲート電極層301と同様の材料を用いて導電層を形成し、第9のフォトリソグラフィ工程によりレジストマスクを形成し、導電層を選択的にエッチング除去することにより、電極層315を形成する。ここでは電極層315としてチタンを単層で形成し、BCl<sub>3</sub>とCl<sub>2</sub>の混合ガスを用いてドライエッチングを行う。電極層315は、コンタクトホール314を介して配線層302と接続されている（図9（D）参照。）。

10

20

30

40

50

**【 0 1 9 3 】**

この時、酸化物半導体層 306 と重畠するように導電層を残し、ゲート電極層 360 を形成してもよい。本実施の形態において、ゲート電極層 360 はいわゆるバックゲートとして機能する。ゲート電極層 360 を有することで、酸化物半導体層 306 中の電界を制御することが可能であり、これによって、トランジスタ 390 の電気的特性を制御することができる。なお、ゲート電極層 360 は、他の配線層や電極などと電気的に接続されて何らかの電位が与えられても良いし、絶縁されてフローティング状態であっても良い。

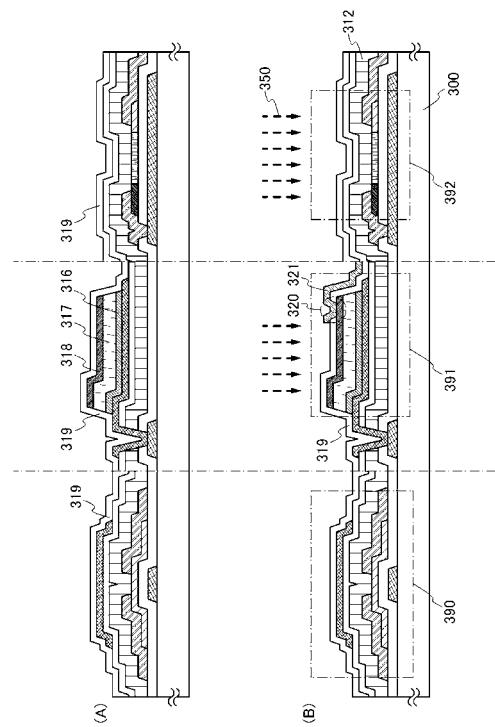

**【 0 1 9 4 】**

次に、電極層 315 上に第 1 半導体膜、第 2 半導体膜、第 3 半導体膜を順次積層する。ここでは、第 1 半導体膜は、n 型半導体層であり、n 型を付与する不純物元素を含む非晶質シリコン膜により形成する。第 1 半導体膜は、15 族の不純物元素（例えばリン（P））を含む半導体材料ガスを用いて、プラズマ CVD 法により形成する。半導体材料ガスとしてはシラン（SiH<sub>4</sub>）を用いればよい。または、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub> 等を用いてもよい。また、不純物元素を含まない非晶質シリコン膜を形成した後に、拡散法やイオン注入法を用いて該非晶質シリコン膜に不純物元素を導入してもよい。イオン注入法等により不純物元素を導入した後に加熱等を行うことで、不純物元素を拡散させるとよい。この場合に非晶質シリコン膜を形成する方法としては、LPCVD 法、気相成長法、又はスパッタリング法等を用いればよい。第 1 半導体膜の膜厚は 20 nm 以上 200 nm 以下となるよう形成することが好ましい。

**【 0 1 9 5 】**

第 2 半導体膜は、i 型半導体層（真性半導体層）であり、非晶質シリコン膜により形成する。第 2 半導体膜は、半導体材料ガスを用いて、非晶質シリコン膜をプラズマ CVD 法により形成する。半導体材料ガスとしては、シラン（SiH<sub>4</sub>）を用いればよい。または、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub> 等を用いてもよい。第 2 半導体膜の形成は、LPCVD 法、気相成長法、スパッタリング法等により行ってもよい。第 2 半導体膜の膜厚は 200 nm 以上 1000 nm 以下となるよう形成することが好ましい。

**【 0 1 9 6 】**

第 3 半導体膜は p 型半導体層であり、p 型を付与する不純物元素を含む非晶質シリコン膜により形成する。第 3 半導体膜は 13 族の不純物元素（例えばボロン（B））を含む半導体材料ガスを用いて、プラズマ CVD 法により形成する。半導体材料ガスとしてはシラン（SiH<sub>4</sub>）を用いればよい。または、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub> 等を用いてもよい。また、不純物元素を含まない非晶質シリコン膜を形成した後に、拡散法やイオン注入法を用いて該非晶質シリコン膜に不純物元素を導入してもよい。イオン注入法等により不純物元素を導入した後に加熱等を行うことで、不純物元素を拡散させるとよい。この場合に非晶質シリコン膜を形成する方法としては、LPCVD 法、気相成長法、又はスパッタリング法等を用いればよい。第 3 半導体膜の膜厚は 10 nm 以上 50 nm 以下となるよう形成することが好ましい。

**【 0 1 9 7 】**

また、第 1 半導体膜、及び第 3 半導体膜は、非晶質半導体ではなく、多結晶半導体または微結晶半導体を用いて形成してもよい。

**【 0 1 9 8 】**

次に、第 9 のフォトリソグラフィ工程を行い、レジストマスクを形成し、第 1 半導体膜、第 2 半導体膜、および第 3 半導体膜の不要な部分を選択的にエッチング除去して、第 1 半導体層 316、第 2 半導体層 317、第 3 半導体層 318 を形成する（図 10（A）参照）。なお、ここでは CF<sub>4</sub> と Cl<sub>2</sub> の混合ガス、CF<sub>4</sub> と O<sub>2</sub> の混合ガス、CHF<sub>3</sub> と He の混合ガス等を用いてドライエッチングを行い、テーパー部にエッチング残渣が残らないようにする。

**【 0 1 9 9 】**

なお、電極層 315 は基板側から入射する光が、第 2 半導体層 317 に当たらないように

10

20

30

40

50

するための遮光膜としても機能する。さらに、第1半導体層316、第2半導体層317、第3半導体層318を透過した外光350を反射させ、再度、第2半導体層317に入射させることで、光センサ391の検出感度を良好なものとすることができます。

#### 【0200】

次に、絶縁層319を形成する。絶縁層319は窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。ここでは、絶縁層319として、酸化シリコン膜を形成する。

#### 【0201】

次に、第10のフォトリソグラフィ工程により、レジストマスクを形成し、第3半導体層318上の絶縁層319を選択的にエッチング除去することにより、コンタクトホール320を形成する。

#### 【0202】

次いで、ゲート電極層301と同様の材料を用いて導電膜を成膜し、第11のフォトリソグラフィ工程により、レジストマスクを形成し、導電膜の不要な部分を選択的にエッチング除去して電極層321を形成する。ここでは、導電膜としてアルミニウムを主成分とする膜とチタン膜をスパッタリング法により積層して成膜する。

#### 【0203】

電極層321は、コンタクトホール320を介して第3半導体層318と接続し、図示していない共通配線層に接続している。

#### 【0204】

上記の作製工程により、基板上にトランジスタおよび光センサを形成することができる。本実施の形態では、光センサ392が有するp-i-n型フォトダイオードを、p層、i層、及びn層を横に並べて配置する横型のp-i-n型フォトダイオードで説明したが、光センサ391が有するp-i-n型フォトダイオードの様に、p層、i層、及びn層を縦方向に積層形成する構成としてもよい。

#### 【0205】

図11は、上記の工程で作製したトランジスタを、画素スイッチ用トランジスタとして用いる一例を示している。トランジスタ395は、酸化物半導体層306を有するトランジスタであり、図8乃至図10で説明したトランジスタ390とほぼ同様に作製することができる。トランジスタ395はバックゲートとして機能するゲート電極層360を有していないが、必要であれば適宜バックゲートを形成してもよい。

#### 【0206】

図11では、トランジスタ395上に平坦化絶縁層として絶縁層331が形成されており、絶縁層331の上に画素電極層332が形成されている。絶縁層331としてはポリイミド、アクリル樹脂、ベンゾシクロブテン系樹脂、ポリアミド、エポキシ樹脂等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(LOW-k材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶縁層を複数積層することで、絶縁層331を形成してもよい。

#### 【0207】

画素電極層332としては、前述したゲート電極層や、ソース電極層、ドレイン電極層と同様の材料を用いることができる。

#### 【0208】

次に、トランジスタ395形成後から、画素電極層332を形成するまでの工程について説明する。絶縁層319を形成した後、第10のフォトリソグラフィ工程により、コンタクトホール320を形成するが、この時同時に電極層310b上の絶縁層312、保護絶縁層313、絶縁層319、を選択的にエッチング除去し、コンタクトホール330を形成する。

#### 【0209】

10

20

30

40

50

次いで、第11のフォトリソグラフィ工程により、レジストマスクを形成し、導電膜の不要な部分を選択的にエッティング除去して電極層321を形成するが、電極層321の形成と同時にコンタクトホール330を覆う電極層322を形成する。

#### 【0210】

次いで、平坦化絶縁層として機能する絶縁層331を形成する。本実施の形態では、感光性ポリイミド樹脂を用いて、第12のフォトリソグラフィ工程により、電極層322上のポリイミド樹脂を選択的に除去し、コンタクトホール333を形成する。感光性材料を用いることで、レジストマスクの形成を省略することができる。

#### 【0211】

次いで、絶縁層331上に画素電極を形成するための導電層を形成する。本実施の形態では、導電層としてITOを形成する。その後、第13のフォトリソグラフィ工程により、レジストマスクを形成し、導電層の不要な部分を選択的にエッティング除去して画素電極層332を形成する。画素電極層332は電極層322を介して電極層310bと接続されている。

#### 【0212】

上記の作製工程により、基板上に画素スイッチ用トランジスタを形成することができる。

#### 【0213】

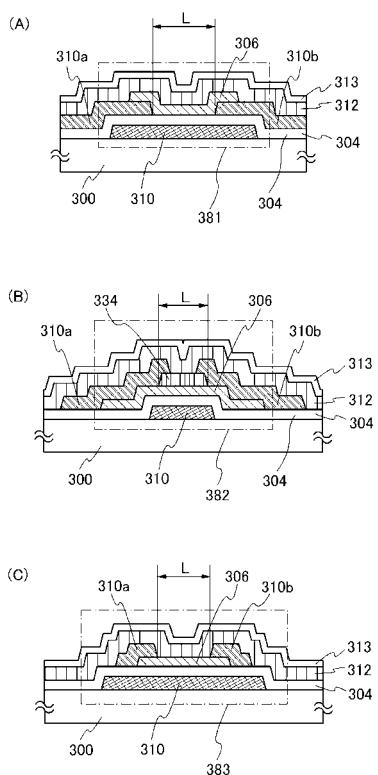

また、本実施の形態では、ボトムゲート構造のチャネルエッチ型のトランジスタ395の作製方法について説明したが、本実施の形態の構成はこれに限られるものではない。図12(A)に示すような、ボトムゲート構造のボトムコンタクト型(逆コプラナ型とも呼ぶ)のトランジスタ381や、図12(B)に示すような、チャネル保護層334を有するチャネル保護型(チャネルリストップ型ともいう)のトランジスタ382等も同様の材料、方法を用いて形成することができる。図12(C)は、トランジスタ395とは異なるチャネルエッチ型トランジスタの例を示している。図12(C)に示すトランジスタ383は、ゲート電極層310が酸化物半導体層306の端部よりも外側に伸びた構造となっている。

#### 【0214】

なお、トランジスタのチャネル長Lは、チャネルエッチ型のトランジスタの場合は、前述したように電極層310aと電極層310bとの距離で定義されるが、チャネル保護型のトランジスタのチャネル長は、キャリアの流れる方向と平行な方向の、酸化物半導体層306と接するチャネル保護層334の長さで定義される。

#### 【0215】

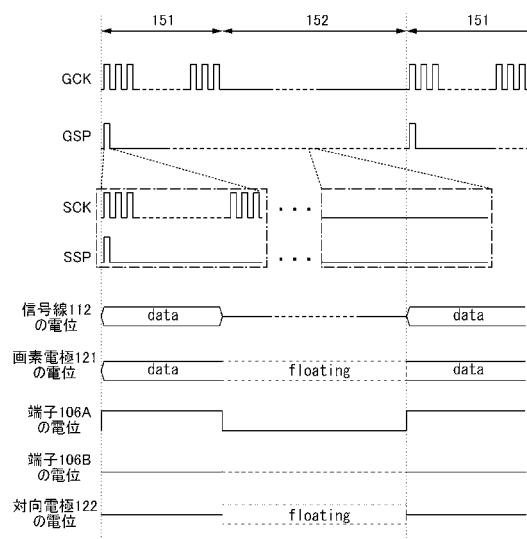

##### (実施の形態4)

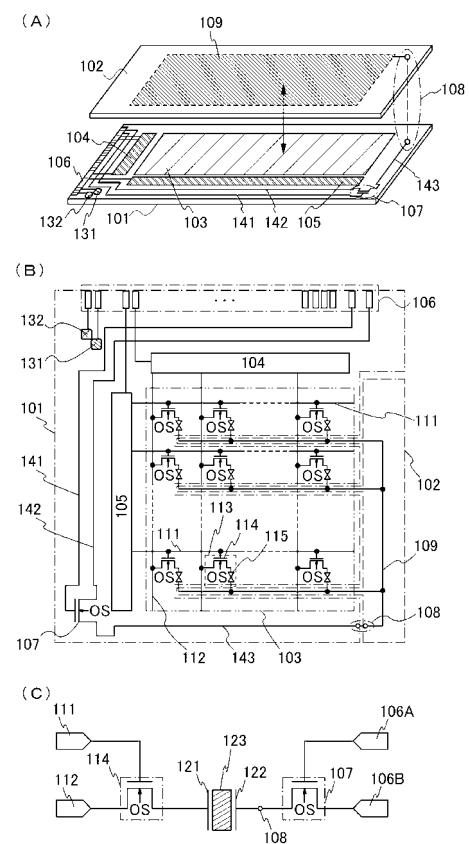

本実施の形態では、図13及び図14を用いて、液晶表示装置の概略図、回路図、及びタイミングチャート等について示し、本実施の形態の構成とすることによる効果について説明することにする。まず図13を用いて、液晶表示装置の概略図について説明を行う。

#### 【0216】

図13(A)で示す液晶表示装置は、第1の基板101、第2の基板102で構成される。第1の基板101には、画素回路103、ゲート線駆動回路104、信号線駆動回路105、端子部106、スイッチングトランジスタ107を有する。第2の基板102には、共通接続部108(コモンコンタクトともいう)、対向電極109を有する。

#### 【0217】

第1の基板101上には、実施の形態1で説明した光センサが設けられ、端子部106に接続されている。光センサ131は、非晶質薄膜光センサであり、光センサ132は、多結晶薄膜光センサである。

#### 【0218】

第1の基板101及び第2の基板102は、透光性を有し、且つ後の加熱処理に耐えうる程度の耐熱性を有している必要がある。アルミニシリケートガラス、アルミニホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われるガラス基板(「無アルカリガラス基板」とも呼ばれる)、石英基板、セラミック基板、プラスチック基板等を用

10

20

30

40

50

いることができる。

**【0219】**

なお図13(A)に示す画素回路103、ゲート線駆動回路104、信号線駆動回路105、及びスイッチングトランジスタ107は、第1の基板101上に形成されるトランジスタにより回路が構成されるものでもよい。なお、表示装置の大型化や高精細化に伴い、ゲート線駆動回路104や、信号線駆動回路105、また、他の実施の形態で説明した、光センサ駆動回路や、光センサ読み出し回路などの駆動回路に対して、さらなる高速動作などが求められる場合は、必要に応じて、駆動回路の機能の一部または全部を、例えば単結晶半導体を用いて別途基板上に作製し、第1の基板101上に単数もしくは複数に分けて接続してもよい。

10

**【0220】**

なお、別途基板上に形成した駆動回路の接続方法は特に限定されるものではなく、COG法、ワイヤボンディング法、或いはTAB法などを用いることができる。本実施の形態では、ゲート線駆動回路104及び信号線駆動回路105を、単結晶半導体で作製したいわゆるIC(Integrated Circuit)またはLSI(Large Scale Integration)を用いて、COG法にて接続する。

**【0221】**

なお画素回路103には、ゲート線駆動回路104及び信号線駆動回路105より延在して、複数のゲート線及び信号線が設けられ、ゲート線及び信号線に環囲された複数の画素が設けられる。そして複数の信号線には、各画素の画素電極に供給する画像信号が供給され、複数のゲート線は、信号線より供給される画像信号を選択して各画素の画素電極に供給するよう画素トランジスタを制御する。またゲート線駆動回路104及び信号線駆動回路105は、それぞれゲート線、信号線に供給する信号を生成し出力するための回路である。

20

**【0222】**

なお、画素回路103における画像の表示方式は、プログレッシブ方式やインターレース方式等を用いることができる。また、カラー表示する際に画素で制御する色要素としては、RGB(Rは赤、Gは緑、Bは青を表す)の三色に限定されない。例えば、RGBW(Wは白を表す)、又はRGBに、イエロー、シアン、マゼンタ等を一色以上追加したものがある。なお、色要素のドット毎にその表示領域の大きさが異なっていてもよい。ただし、本発明の一態様はカラー表示の液晶表示装置に限定されるものではなく、モノクロ表示の液晶表示装置に適用することもできる。

30

**【0223】**

なお本明細書で述べるスイッチングトランジスタとは、ゲートに印加する電位に応じて、ソース端子及びドレイン端子間の二端子間の導通または非導通を選択して、スイッチング動作を実現しうるトランジスタによる素子を意味する。一例としては、トランジスタが線形領域で動作するようゲート端子に印加する電位を調整して動作させた素子であればよい。なおスイッチングトランジスタ107のゲートに印加する電位は、端子部106より配線141を介して供給される構成とすればよい。また、配線142を介して端子部106に接続される、スイッチングトランジスタ107のソース端子またはドレイン端子の一方の端子を第1の端子、配線143及び共通接続部108を介して対向電極109に接続される、スイッチングトランジスタ107のソース端子またはドレイン端子の他方の端子を第2の端子と呼ぶこととする。なおスイッチングトランジスタ107の第1の端子には、対向電極109に供給する共通電位(コモン電位ともいう)が供給され、ゲート端子に印加される電位によりスイッチングトランジスタ107の導通または非導通が制御されることとなる。

40

**【0224】**

配線141及び配線142は、ゲート線駆動回路104及び信号線駆動回路105の外側、つまり、画素回路103が無い側の、ゲート線駆動回路104と基板端部の間、及び信号線駆動回路105と基板端部の間を通って端子部106に接続する。このように、配線

50

141及び配線142を、ゲート線駆動回路104及び信号線駆動回路105を囲うように配置することで、外部ノイズの進入や、静電気による破壊などを防ぐことができる。また、配線は、配線141及び配線142だけでなく、Vdd電位線や、Vss電位線、グラウンド電位線などを用いても構わない。

【0225】

なおスイッチングトランジスタの構造については逆スタガ型の構造でもよいし、順スタガ型の構造でもよい。または、チャネル領域が複数の領域に分かれて直列に接続された、ダブルゲート型の構造でもよい。または、ゲート電極がチャネル領域の上下に設けられたデュアルゲート型の構造でもよい。また、スイッチングトランジスタを構成する半導体層を複数の島状の半導体層にわけて形成し、スイッチング動作を実現しうるトランジスタ素子としてもよい。

10

【0226】

また端子部106には、ゲート線駆動回路104、及び信号線駆動回路105より、画素回路103で表示を行うパルス信号を出力するための信号（スタートパルスSP、クロック信号等）、画像信号（ビデオ電圧、ビデオ信号、ビデオデータともいう）、電源電圧である高電源電位Vdd及び低電源電位Vss、対向電極109に供給する共通電位、並びにスイッチングトランジスタ107を動作させるための信号等が供給されることとなる。

【0227】

なお高電源電位Vddとは、基準電位より高い電位のことであり、低電源電位とは基準電位以下の電位のことをいう。なお高電源電位及び低電源電位とともに、トランジスタが動作できる程度の電位であることが望ましい。

20

【0228】

共通電位は、画素電極に供給される画像信号の電位に対して基準となる電位であればよく、一例としてはグラウンド電位であってもよい。

【0229】

共通接続部108は、第1の基板101でのスイッチングトランジスタ107の第2の端子と、第2の基板102での対向電極109との電気的な接続を図るために設けられており、配線142、スイッチングトランジスタ107、配線143及び共通接続部108を介して、端子部106より共通電位が対向電極109に供給されることとなる。共通接続部108の具体的な一例としては、金属薄膜が被覆された導電粒子により、配線143と対向電極109との電気的な接続を図ればよい。なお、スイッチングトランジスタ107及び共通接続部108は、第1の基板101及び第2の基板102の間で複数箇所設けられる構成としてもよい。

30

【0230】

対向電極109は、画素回路103が有する画素電極と重畠して設けられることが好ましい。また対向電極109及び画素回路103が有する画素電極は、多様な開口パターンを有する形状としてもよい。

【0231】

また、第1の基板101上には、実施の形態1で説明した光センサが設けられ、端子部106に接続されている。光センサ131は、非晶質薄膜光センサであり、光センサ132は、多結晶薄膜光センサである。

40

【0232】

また画素回路103及びスイッチングトランジスタ107を第1の基板101に形成する場合、各回路を構成するトランジスタは、高純度化された酸化物半導体をチャネル形成領域に用いたトランジスタを用いる。高純度化された酸化物半導体を用いたトランジスタは、オフ電流値が極めて小さいトランジスタである。

【0233】

このようにオフ電流値が極めて小さいトランジスタを用いて、スイッチング素子などを作製した場合、オフ電流値が小さくほとんどリークがないため、当該スイッチング素子に接続されるノードの電荷のリークを限りなく低減することができ、当該ノードでの電位の保

50

持時間(保持時間)を長くすることができる。

#### 【0234】

上述の酸化物半導体を用いたトランジスタは、チャネル幅 $1 \mu m$ あたりのオフ電流を $1 aA / \mu m$  ( $1 \times 10^{-18} A / \mu m$ ) 以下にすること、さらには $1 zA / \mu m$  ( $1 \times 10^{-21} A / \mu m$ ) 以下とすることができます。一方低温ポリシリコンを用いたトランジスタでは、オフ電流が $1 \times 10^{-12} A$ 相当であると見積もって設計等を行うこととなっている。そのため、酸化物半導体を用いたトランジスタでは、電位の保持期間を低温ポリシリコンを用いたトランジスタの $10000$ 倍程度に引き延ばすことができる。また、アモルファスシリコンを用いたトランジスタの場合、チャネル幅 $1 \mu m$ あたりのオフ電流は、 $1 \times 10^{-13} A / \mu m$ 以上である。したがって、保持容量が同等 (0.1 pF程度) である際、高純度の酸化物半導体を用いたトランジスタの方が、電圧の保持期間をアモルファスシリコンを用いたトランジスタの $10^4$ 倍以上に引き延ばすことができる。10

#### 【0235】

具体的には、酸化物半導体を用いたトランジスタでは、各画素での画像信号の保持時間を長くすることができるため、例えば、静止画を表示する際の書き込みの間隔は1秒以上、好みは10秒以上、さらに好みは30秒以上、より好みは1分以上10分未満とすることができる。すなわち、保持期間を長くとれることで、特に静止画の表示を行う際に、画素電極及び対向電極への画像信号及び共通電位の供給を行う頻度を低減することができる。そのため、低消費電力化を図ることができる。

#### 【0236】

なお、静止画表示において、保持期間中の液晶素子に印加されている電圧の保持率を考慮して、適宜リフレッシュ動作してもよい。例えば、液晶素子の画素電極に信号を書き込んだ直後における電圧の値(初期値)に対して所定のレベルまで電圧が下がったタイミングでリフレッシュ動作を行えばよい。所定のレベルとする電圧は、初期値に対してチラツキを感じない程度に設定することが好み。具体的には、表示対象が映像の場合、初期値に対して1.0%低い状態、好みは0.3%低い状態となる毎に、リフレッシュ動作(再度の書き込み)を行うのが好み。また、表示対象が文字の場合、初期値に対して10%低い状態、好みは3%低い状態となる毎に、リフレッシュ動作(再度の書き込み)を行うのが好み。20

#### 【0237】

なお、一例として、通常、低温ポリシリコンを用いたトランジスタを有する画素では表示を60フレーム/秒 (1フレームあたり $16 \text{ msec}$ ) で行っている。これは静止画であっても同じで、レートを低下させる(書き込みの間隔を伸ばす)と、画素の電圧が低下して表示に支障をきたすためである。一方、上述の酸化物半導体を用いたトランジスタを用いた場合、オフ電流が小さいため、1回の信号書き込みによる保持期間を $10^4$ 倍の160秒程度とすることができる。30

#### 【0238】

そして、少ない画像信号の書き込み回数でも、表示部での静止画の表示を行うことができる。保持期間を長くとれるため、特に静止画の表示を行う際に、信号の書き込みを行う頻度を低減することができる。例えば、一つの静止画像の表示期間に画素に書き込む回数は、1回またはn回とすることができます。なお、nは2以上 $10^3$ 回以下とする。こうして、表示装置の低消費電力化を図ることができる。40

#### 【0239】

なお、トランジスタのオフ電流の流れ難さをオフ抵抗率として表すことができる。オフ抵抗率とは、トランジスタがオフのときのチャネル形成領域の抵抗率であり、オフ抵抗率はオフ電流から算出することができる。

#### 【0240】

具体的には、オフ電流とドレイン電圧との値が分かれればオームの法則からトランジスタがオフのときの抵抗値(オフ抵抗R)を算出することができる。そして、チャネル形成領域の断面積Aとチャネル形成領域の長さ(ソースドレイン電極間の距離に相当する)Lが分50

かれば  $= R A / L$  の式 (R はオフ抵抗) からオフ抵抗率 を算出することができる。

**【0241】**

ここで、断面積 A は、チャネル形成領域の膜厚を d とし、チャネル幅を W とするとき、 $A = d W$  から算出することができる。また、チャネル形成領域の長さ L はチャネル長 L である。以上のように、オフ電流からオフ抵抗率を算出することができる。

**【0242】**

本実施の形態の酸化物半導体を用いるトランジスタのオフ抵抗率は  $1 \times 10^9 \cdot m$  以上が好ましく、 $1 \times 10^{10} \cdot m$  以上がより好ましい。

**【0243】**

なお、静止画と動画像が交互に切り替わって表示を行う液晶表示装置の場合には、ゲート線駆動回路 104、及び信号線駆動回路 105 への画素回路 103 で表示を行うパルス信号を出力するための信号の供給、及びスイッチングトランジスタの導通または非導通を制御し、各駆動回路からのパルス信号の供給または停止、及びスイッチングトランジスタの導通または非導通を繰り返すことで低消費電力化を図ることができる。10

**【0244】**

なお動画像は、複数のフレームに時分割した複数の画像を高速に切り替えることで人間に動画像として認識される画像のことをいう。具体的には、1秒間に 60 回 (60 フレーム) 以上画像を切り替えることで、人間の目にはちらつきが少なく動画像と認識される、連続する画像信号のことである。一方静止画は、動画像と異なり、複数のフレーム期間に時分割した複数の画像を高速に切り替えて動作させるものの、連続するフレーム期間、例えば n フレーム目と、(n + 1) フレーム目とで画像信号が変化しない画像信号のことをいう。20

**【0245】**

なお静止画と動画像が交互に切り替わって表示を行う液晶表示装置の場合、動画像か静止画かの判定については、別の基板等でフレーム間の画像の比較を行い、動画像か静止画かの判定を行う構成とすればよい。一例としては記憶回路及び比較回路を設け、フレーム毎に画像信号を記憶するために別途設けた記憶回路より連続するフレーム期間の画像信号を選択的に読み出して、比較回路にて当該画像信号の比較を行い、差分を検出した際には動画像、検出されない際には静止画と判定する回路を設ければよい。具体的な動作としては、比較回路により動画像と判断、すなわち連続フレーム期間の画像信号の差分が抽出された場合には、画像信号、共通電位が画素回路 103 の各画素、対向電極に供給される。一方、比較回路により静止画と判断、すなわち連続フレーム期間の画像信号の差分を抽出しない場合には、画素回路 103 の各画素、対向電極への画像信号、共通電位を停止することとなる。また静止画の場合に画像信号の停止とともに、高電源電位 Vdd、低電源電位 Vss 等の電源電圧の停止を行わない構成とすることで、さらなる低消費電力化を図ることができる。30

**【0246】**

なお画像信号、電源電圧、共通電位の供給とは、配線に所定の電位を供給することをいう。また電源電圧の停止とは、配線への所定の電位、例えば高電源電位 Vdd の供給を停止し、他の固定電位が供給される配線、例えば低電源電位 Vss や共通電位が供給された配線に接続することで、配線が接続された回路または回路を構成する素子に、動作可能となる電位を生じさせないことをいう。また画像信号、共通電位の停止とは、所定の電位を供給されている配線との電気的な接続を切断し、配線を浮遊状態とすることをいう。40

**【0247】**

なお画像信号、共通電位の停止は、画素回路 103 の各画素で画像信号を保持できる期間にわたって行なうことが望ましく、各画素での保持期間の後に再度画像信号及び共通電位を供給する構成とすればよい。

**【0248】**

次いで図 13 (B) に、図 13 (A) での液晶表示装置の概略図について、特に画素回路 103 の構成を詳細にした回路図について示す。50

## 【0249】

図13(B)に示す液晶表示装置は、図13(A)と同様に、第1の基板101、第2の基板102が設けられている。また第1の基板101には、画素回路103、ゲート線駆動回路104、信号線駆動回路105、端子部106、スイッチングトランジスタ107を有する。第2の基板102には、共通接続部108、対向電極109を有する。

## 【0250】

図13(B)においては、画素回路103において、複数のゲート線111、複数の信号線112が縦横に設けられており、ゲート線111及び信号線112には、画素トランジスタ114、第1の電極と第2の電極との間に液晶が挟持されて形成される液晶素子115を有する画素113が設けられている様子を示している。図13(B)において、画素トランジスタ114のソース端子またはドレイン端子の一方を第1の端子、ソース端子またはドレイン端子の他方を第2の端子といい、第1の端子が信号線112に接続され、ゲート端子がゲート線111に接続され、第2の端子が液晶素子115の第1の電極に接続される。なお、液晶素子115の第1の電極は、画素電極に相当する。なお液晶素子115の第2の電極は、前述の対向電極109に相当する。

10

## 【0251】

なお、画素を構成する画素トランジスタ114は、スイッチングトランジスタ107と同様に、半導体層として酸化物半導体を用いて形成される。酸化物半導体を用いることにより、画素トランジスタを流れるオフ電流を大幅に低減し、画素電極に供給される画像信号に応じた電位の保持期間を長くすることができる。

20

## 【0252】

次いで、画素電極を有する画素の一画素についての回路図を図13(C)に示す。図13(C)には、画素トランジスタ114、スイッチングトランジスタ107に着目して示しており、画素トランジスタ114のゲート端子がゲート線111に接続され、画素トランジスタ114の第1の端子が信号線112に接続され、画素トランジスタ114の第2の端子が画素電極121に接続される。またスイッチングトランジスタ107のゲート端子が端子部106の端子106Aに接続され、スイッチングトランジスタ107の第1の端子が端子部106の端子106Bに接続され、スイッチングトランジスタ107の第2の端子が共通接続部108を介して電気的に対向電極122に接続される。なお画素電極121と対向電極122との間には、液晶123が挟持され、画素電極121、対向電極122、及び液晶123を併せて液晶素子と呼ぶこともある。

30

## 【0253】

なお図13(C)では、液晶素子に保持容量を並列に接続しても良い。なお、保持容量の大きさは、画素部に配置されるトランジスタのリーク電流等を考慮して、所定の期間の間電荷を保持できるように設定すればよい。保持容量の大きさは、トランジスタのオフ電流等を考慮して設定すればよい。本実施の形態では、トランジスタとして高純度の酸化物半導体を有するトランジスタを用いていることにより、各画素における液晶容量に対して1/3以下、好ましくは1/5以下の容量の大きさを有する保持容量を設ければ充分である。

40

## 【0254】

液晶123としては、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いる。これらの液晶材料は、条件により、コレステリック相、スマートチック相、キューピック相、カイラルネマチック相、等方相等を示す。

## 【0255】

また、液晶123の固有抵抗は、 $1 \times 10^{10} \Omega \cdot m$ 以上であり、好ましくは $1 \times 10^9 \Omega \cdot m$ を越えていることであり、さらに好ましくは $1 \times 10^{12} \Omega \cdot m$ を越えていることである。なお、本明細書における固有抵抗の値は、20で測定した値とする。なお液晶の固有抵抗は、電極間に挟持して液晶素子(液晶セルともいう)とした際、固有抵抗が配向膜、シール材等の部材に起因して不純物の混入もあり得るため、 $1 \times 10^9 \Omega \cdot m$ 以

50

上、より好ましくは  $1 \times 10^{-10}$  m を越えていることとなることがある。

#### 【0256】

液晶材料の固有抵抗が大きいほど液晶材料を介して漏れる電荷を減らすことができ、液晶素子の動作状態を保持する電圧が経時に低下する現象を緩和できる。その結果、保持期間を長くとれるため、信号の書き込みを行う頻度を低減でき、液晶表示装置の低消費電力化を図ることができる。

#### 【0257】

また、液晶 123 としてブルー相を示す液晶材料を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために 5 重量 % 以上のカイラル剤を混合させた液晶組成物を用いて液晶層に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が 1 msec 以下と短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。また配向膜を設けなくてもよいのでラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中の液晶表示装置の不良や破損を軽減することができる。よって液晶表示装置の生産性を向上させることができるとなる。特に、酸化物半導体を用いるトランジスタは、静電気の影響によりトランジスタの電気的な特性が著しく変動して設計範囲を逸脱する恐れがある。よって酸化物半導体を用いるトランジスタを有する液晶表示装置にブルー相の液晶材料を用いることはより効果的である。

#### 【0258】

また、本実施の形態の構成は、液晶表示装置に限定されず、表示素子としてエレクトロルミネッセンス素子（EL 素子ともいう）などの発光素子を用いた自発光型の表示装置にも適用可能である。自発光型の表示装置の場合は、画像表示時に発光素子へ常に電荷を供給する必要があるが、静止画を表示する際に、駆動回路に供給するクロック信号、及びスタートパルスを停止することにより駆動回路を停止させ、低消費電力化を図ることができる。

#### 【0259】

また図 14においては、図 13 (C) に示す回路図での各端子、ゲート線駆動回路 104、信号線駆動回路 105 に供給する信号の様子について表すタイミングチャート図を示している。なお一例として説明をするために、図 14 に示す期間 151 は動画像書き込み期間、期間 152 は静止画表示期間に相当し、前述の動画像または静止画の判定の結果によつて、いずれかの期間とすればよい。また図 14 中で GCK はゲート線駆動回路 104 に供給するクロック信号であり、GSP はゲート線駆動回路 104 に供給するスタートパルスであり、SCK は信号線駆動回路 105 に供給するクロック信号であり、SSP は信号線駆動回路 105 に供給するスタートパルスである。また、図 14 では併せて、信号線 112 の電位、画素電極 121 の電位、端子 106A の電位、端子 106B の電位、対向電極 122 の電位、について示したものである。

#### 【0260】

なお期間 151 の動画像書き込み期間は、前述の連続するフレーム期間の画像信号の比較を行い、差分を検出した際の期間に相当する。また、期間 152 の静止画書き込み期間は、前述の連続するフレーム期間の画像信号の比較を行い、差分を検出しない際の期間に相当する。従つて、期間 151 では、画像信号、共通電位が画素回路 103 の各画素、対向電極に供給されるように動作することとなる。一方、期間 152 では、画素回路 103 の各画素、対向電極への画像信号、共通電位を停止することとなる。

#### 【0261】

具体的には図 14 に示すように期間 151 において、クロック信号 GCK は常時クロック信号を供給することとなる。また図 14 に示すように、スタートパルス GSP は、垂直同期周波数に応じてパルスを供給することとなる。また図 14 に示すように期間 151 において、クロック信号 SCK は常時クロック信号を供給することとなる。また図 14 に示すようにスタートパルス SSP は、1 ゲート選択期間に応じてパルスを供給することとなる。

10

20

30

40

50

。また図14に示すように、信号線112には各行の画素に供給するための画像信号dataが供給され、ゲート線111の電位に応じて画素内の画素電極121に信号線112の電位が供給されることとなる。また図14に示すように、スイッチングトランジスタ107のゲート端子にあたる端子106Aの電位は、スイッチングトランジスタ107を導通状態とする電位を供給し、端子106Bの電位である共通電位が、対向電極122に供給されることとなる。

#### 【0262】

また図14に示すように期間152において、クロック信号GCK及びスタートパルスGSPは共に停止する。また図14に示すように、クロック信号SCK及びスタートパルスSSPも共に停止する。また図14に示すように信号線112に供給していた画像信号dataも停止する。また図14に示すように、クロック信号GCK及びスタートパルスGSPは共に停止するため、画素トランジスタ114が非導通状態となり画像信号dataの供給が停止して、画素電極121が浮遊状態(フローティング)となる。また、スイッチングトランジスタ107のゲート端子にあたる端子106Aの電位は、スイッチングトランジスタ107を非導通状態とする電位を供給し、端子106Bの電位である共通電位の供給が停止して、対向電極122が浮遊状態となる。

10

#### 【0263】

すなわち、期間152では、液晶123の両端の電極、即ち画素電極121及び対向電極122を浮遊状態とすることで新たに電位を供給することなく、静止画の表示を行うことができる。ゲート線駆動回路104、信号線駆動回路105に供給するクロック信号、及びスタートパルスを停止することにより低消費電力化を図ることができる。

20

#### 【0264】

また、画素トランジスタ114及びスイッチングトランジスタ107を、オフ電流を著しく低減することのできる酸化物半導体を用いたトランジスタで形成することで、液晶素子の両端を非導通状態とした時の液晶素子の電位変動を著しく低減することができる。

#### 【0265】

上述のように酸化物半導体を用いるトランジスタは、オフ電流が $0.1\text{fA}$ 以下とすることができます。そのため、非晶質シリコン等を半導体層に用いたトランジスタに比べ、画素電極121及び対向電極122を浮遊状態とする期間となる保持期間を大きくとることができます。そのため、本実施の形態における静止画の表示を行う際に低消費電力化を図るうえでの相乗効果が見込めることがある。

30

#### 【0266】

なお図13(C)での液晶123の抵抗率は、およそ $1 \times 10^{10} \text{ [ } \cdot \text{ m] }$ 程度である。図14での期間152では、液晶123の両端の電極、即ち画素電極121及び対向電極122を、オフ電流のほとんどないトランジスタによって浮遊状態とすることにより、液晶123の両端に印加される電圧による液晶123を流れるオフ電流を低減することができる。

#### 【0267】

その結果、静止画表示を行う際、低消費電力化を図りつつ、且つ画像の乱れの低減された液晶表示装置とすることができます。

40

#### 【0268】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0269】

##### (実施の形態5)

本実施の形態においては、上記実施の形態で説明した表示装置を具備する電子機器の例について説明する。

#### 【0270】

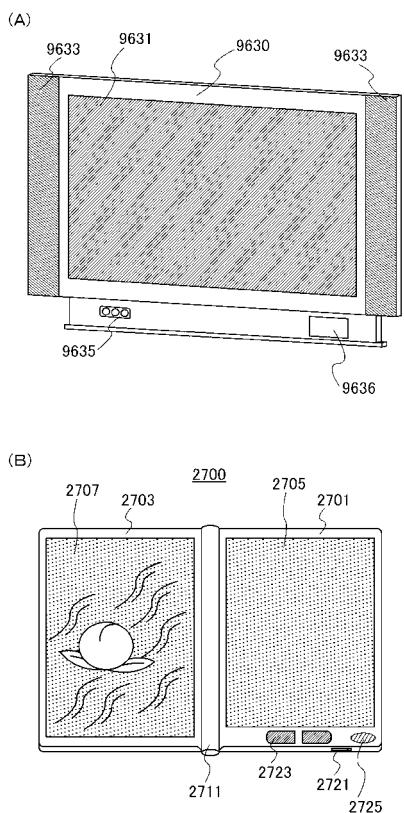

図19(A)はテレビ受像器であり、筐体9630、表示部9631、スピーカ9633、操作キー9635、接続端子9636、等を有することができる。図19(A)に示す

50

テレビ受像機は、テレビ用電波を処理して画像信号に変換する機能、画像信号を処理して表示に適した信号に変換する機能、画像信号のフレーム周波数を変換する機能、等を有することができる。なお、図示していないが、表示部 9631 は、実施の形態 2 で説明した構成を適用し、光センサを有する。図 19 (A) に示すテレビ受像機が有する機能はこれに限定されず、様々な機能を有することができる。前述の実施の形態で説明した構成を用いることで、周囲の光量や色温度を検出し、常に見やすい表示状態とすることができます。また、低消費電力化を図りつつ、画像の乱れの低減された、安定した画像が得られる。

#### 【0271】

このようにして、可視光に対して異なる光感度を持つ非晶質薄膜光センサと多結晶薄膜光センサを用いることで、周囲の照度を正確に検出し、表示装置の発光輝度を最適な状態とすることで、使用者の体感上の輝度変化を軽減し、消費電力の増加を抑えることができる。また、非晶質薄膜光センサと多結晶薄膜光センサの出力差により赤外光の照度を検出し、表示部の色調補正を行うことで、表示品質を改善することができる。

10

#### 【0272】

図 19 (B) は、電子書籍 2700 の一例を示している。例えば、電子書籍 2700 は、筐体 2701 および筐体 2703 の 2 つの筐体で構成されている。筐体 2701 および筐体 2703 は、軸部 2711 により一体とされており、該軸部 2711 を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

20

#### 【0273】

筐体 2701 には表示部 2705 が組み込まれ、筐体 2703 には表示部 2707 が組み込まれている。図示していないが、表示部 2705 および表示部 2707 は実施の形態 2 で説明した構成を適用し、光センサを有する。表示部 2705 および表示部 2707 は、継ぎ画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成とすることで、例えば右側の表示部 (図 19 (B) では表示部 2705) に文章を表示し、左側の表示部 (図 19 (B) では表示部 2707) に画像を表示することができる。

20

#### 【0274】

また、図 19 では、筐体 2701 に操作部などを備えた例を示している。例えば、筐体 2701 において、電源 2721、操作キー 2723、スピーカ 2725 などを備えている。操作キー 2723 により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングディバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子 (イヤホン端子、USB 端子、または AC アダプタおよび USB ケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍 2700 は、電子辞書としての機能を持たせた構成としてもよい。

30

#### 【0275】

また、電子書籍 2700 は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

40

#### 【0276】

前述の実施の形態で説明した構成を用いることで、周囲の光量や色温度を検出し、常に見やすい表示状態とすることができます。また、低消費電力化を図りつつ、画像の乱れの低減された、安定した画像が得られる。

#### 【符号の説明】

#### 【0277】

101 基板

102 基板

103 画素回路

104 ゲート線駆動回路

50

|       |                 |    |

|-------|-----------------|----|

| 1 0 5 | 信号線駆動回路         |    |

| 1 0 6 | 端子部             |    |

| 1 0 7 | スイッチングトランジスタ    |    |

| 1 0 8 | 共通接続部           |    |

| 1 0 9 | 対向電極            |    |

| 1 1 1 | ゲート線            |    |

| 1 1 2 | 信号線             |    |

| 1 1 3 | 画素              |    |

| 1 1 4 | 画素トランジスタ        | 10 |

| 1 1 5 | 液晶素子            |    |

| 1 2 1 | 画素電極            |    |

| 1 2 2 | 対向電極            |    |

| 1 2 3 | 液晶              |    |

| 1 3 1 | 光センサ            |    |

| 1 3 2 | 光センサ            |    |

| 1 4 1 | 配線              |    |

| 1 4 2 | 配線              |    |

| 1 4 3 | 配線              |    |

| 1 5 1 | 期間              |    |

| 1 5 2 | 期間              | 20 |

| 2 0 1 | トランジスタ          |    |

| 2 0 2 | 保持容量            |    |

| 2 0 3 | 液晶素子            |    |

| 2 0 4 | フォトダイオード        |    |

| 2 0 5 | トランジスタ          |    |

| 2 0 6 | トランジスタ          |    |

| 2 0 7 | ゲート信号線          |    |

| 2 0 8 | フォトダイオードリセット信号線 |    |

| 2 0 9 | ゲート信号線          |    |

| 2 1 0 | ビデオデータ信号線       | 30 |

| 2 1 1 | 光センサ出力信号線       |    |

| 2 1 2 | 光センサ基準信号線       |    |

| 2 1 3 | ゲート信号線          |    |

| 2 2 0 | 表示装置            |    |

| 2 2 1 | 画素回路            |    |

| 2 2 2 | 表示素子制御回路        |    |

| 2 2 3 | 光センサ制御回路        |    |

| 2 2 4 | 画素              |    |

| 2 2 5 | 表示素子            |    |

| 2 2 6 | 光センサ            | 40 |

| 2 2 7 | 表示素子駆動回路        |    |

| 2 2 8 | 表示素子駆動回路        |    |

| 2 2 9 | 回路              |    |

| 2 3 0 | 光センサ駆動回路        |    |

| 2 3 1 | トランジスタ          |    |

| 2 3 2 | 保持容量            |    |

| 2 3 3 | プリチャージ信号線       |    |

| 2 3 6 | 光センサ            |    |

| 2 5 1 | 信号              |    |

| 2 5 2 | 信号              | 50 |

|       |          |    |

|-------|----------|----|

| 2 5 3 | 信号       |    |

| 2 5 4 | 信号       |    |

| 2 5 5 | 信号       |    |

| 3 0 0 | 基板       |    |

| 3 0 1 | ゲート電極層   |    |

| 3 0 2 | 配線層      |    |

| 3 0 3 | 配線層      |    |

| 3 0 4 | ゲート絶縁層   |    |

| 3 0 5 | 酸化物半導体層  |    |

| 3 0 6 | 酸化物半導体層  | 10 |

| 3 0 7 | 半導体層     |    |

| 3 0 8 | 半導体層     |    |

| 3 0 9 | コンタクトホール |    |

| 3 1 0 | ゲート電極層   |    |

| 3 1 2 | 絶縁層      |    |

| 3 1 3 | 保護絶縁層    |    |

| 3 1 4 | コンタクトホール |    |

| 3 1 5 | 電極層      |    |

| 3 1 6 | 半導体層     |    |

| 3 1 7 | 半導体層     | 20 |

| 3 1 8 | 半導体層     |    |

| 3 1 9 | 絶縁層      |    |

| 3 2 0 | コンタクトホール |    |

| 3 2 1 | 電極層      |    |

| 3 2 2 | 電極層      |    |

| 3 3 0 | コンタクトホール |    |

| 3 3 1 | 絶縁層      |    |

| 3 3 2 | 画素電極層    |    |

| 3 3 3 | コンタクトホール |    |

| 3 3 4 | チャネル保護層  | 30 |

| 3 5 0 | 外光       |    |

| 3 6 0 | ゲート電極層   |    |

| 3 8 1 | トランジスタ   |    |

| 3 8 2 | トランジスタ   |    |

| 3 8 3 | トランジスタ   |    |

| 3 9 0 | トランジスタ   |    |

| 3 9 1 | 光センサ     |    |

| 3 9 2 | 光センサ     |    |

| 3 9 5 | トランジスタ   |    |

| 8 0 0 | 表示装置     | 40 |

| 8 0 1 | 表示部      |    |

| 8 0 2 | 光センサ     |    |

| 8 0 3 | 光センサ     |    |

| 8 1 1 | 特性       |    |

| 8 1 2 | 特性       |    |

| 8 2 1 | 特性       |    |

| 8 2 2 | 特性       |    |

| 8 3 1 | 中央制御部    |    |

| 8 3 2 | 表示部      |    |

| 8 3 3 | 外部入力     | 50 |

|         |         |

|---------|---------|

| 8 3 4   | 操作部     |

| 8 4 1   | 光センサ    |

| 8 4 2   | 光センサ    |

| 2 7 0 0 | 電子書籍    |

| 2 7 0 1 | 筐体      |

| 2 7 0 3 | 筐体      |

| 2 7 0 5 | 表示部     |

| 2 7 0 7 | 表示部     |

| 2 7 1 1 | 軸部      |

| 2 7 2 1 | 電源      |

| 2 7 2 3 | 操作キー    |

| 2 7 2 5 | スピーカ    |

| 9 6 3 0 | 筐体      |

| 9 6 3 1 | 表示部     |

| 9 6 3 3 | スピーカ    |

| 9 6 3 5 | 操作キー    |

| 9 6 3 6 | 接続端子    |

| 1 0 6 A | 端子      |

| 1 0 6 B | 端子      |

| 3 0 8 a | n型不純物領域 |

| 3 0 8 b | i型領域    |

| 3 0 8 c | p型不純物領域 |

| 3 1 0 a | 電極層     |

| 3 1 0 b | 電極層     |

| 3 1 1 a | 電極層     |

| 3 1 1 b | 電極層     |

【図1】

【図2】

【図3】

【図4】

【 図 5 】

【 四 6 】

【図8】

【 义 7 】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

(A) B-B'断面におけるn'端子図 ( $VG > 0$ )

【図18】

(B) B-B'断面におけるn'端子図 ( $VG < 0$ )

## 【図19】

---

フロントページの続き

(51)Int.Cl.

**G 0 2 F 1/1368 (2006.01)**

F I

|         |        |         |

|---------|--------|---------|

| G 0 9 G | 3/20   | 6 4 2 A |

| G 0 9 G | 3/20   | 6 4 2 L |

| G 0 9 G | 3/20   | 6 2 1 M |

| G 0 9 G | 3/36   |         |

| G 0 9 G | 3/20   | 6 4 2 F |

| G 0 9 G | 3/20   | 6 2 4 B |

| G 0 2 F | 1/133  | 5 5 0   |

| G 0 2 F | 1/1368 |         |

(56)参考文献 特開2009-128835(JP,A)

特開2009-140193(JP,A)

特開2008-235756(JP,A)

特開平05-224626(JP,A)

(58)調査した分野(Int.Cl., DB名)

|         |                   |

|---------|-------------------|

| G 0 9 F | 9 / 0 0 - 9 / 4 6 |

| G 0 2 F | 1 / 1 3 3         |

| G 0 9 G | 3 / 2 0、3 / 3 6   |