(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5157427号

(P5157427)

(45) 発行日 平成25年3月6日(2013.3.6)

(24) 登録日 平成24年12月21日(2012.12.21)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 25/065 | (2006.01) | HO1L 25/08 | B    |

| HO1L 25/07  | (2006.01) | HO1L 21/92 | 602P |

| HO1L 25/18  | (2006.01) | HO1L 21/60 | 311Q |

| HO1L 21/60  | (2006.01) |            |      |

請求項の数 15 (全 11 頁)

(21) 出願番号

特願2007-336212 (P2007-336212)

(22) 出願日

平成19年12月27日 (2007.12.27)

(65) 公開番号

特開2009-158764 (P2009-158764A)

(43) 公開日

平成21年7月16日 (2009.7.16)

審査請求日

平成22年12月27日 (2010.12.27)

(73) 特許権者 000004112

株式会社ニコン

東京都千代田区有楽町1丁目12番1号

(74) 代理人 110000246

特許業務法人O F H 特許事務所

(72) 発明者 岡本 和也

東京都千代田区丸の内3丁目2番3号 株式会社ニコン内

(72) 発明者 松岡 新吾

東京都千代田区丸の内3丁目2番3号 株式会社ニコン内

審査官 今井 拓也

最終頁に続く

(54) 【発明の名称】積層型半導体装置、半導体基板及び積層型半導体装置の製造方法。

## (57) 【特許請求の範囲】

## 【請求項 1】

所定分布密度のバンプが形成された回路領域を有する半導体基板同士が、前記バンプを接合することにより積層されて形成された積層型半導体装置であって、前記半導体基板の周辺部には、前記回路領域のバンプの分布密度より高い分布密度でダミーバンプが形成され、前記半導体基板同士において、前記ダミーバンプ同士の接合がなされていることを特徴とする積層型半導体装置。

## 【請求項 2】

前記ダミーバンプは、前記半導体基板に埋め込まれ前記半導体基板を貫通した、電気的接続を目的としないダミー T S V (Through Si Via) の先端部に形成されていることを特徴とする請求項 1 に記載の積層型半導体装置。 10

## 【請求項 3】

前記ダミーバンプは、前記半導体基板上に形成されたバリアメタルの上に形成されていることを特徴とする請求項 1 に記載の積層型半導体装置。

## 【請求項 4】

前記半導体基板の周辺部に形成された前記ダミーバンプは、前記半導体基板同士の接合用の接点としてのみ用いられるものであることを特徴とする請求項 1 から請求項 3 のうちいずれか 1 項に記載の積層型半導体装置。

## 【請求項 5】

前記ダミーバンプの分布密度は、前記回路領域に形成されたバンプの分布密度の 1.5 倍

から 3 倍とされていることを特徴とする特徴とする請求項 1 から請求項 4 のうちいずれか 1 項に記載の積層型半導体装置。

【請求項 6】

前記ダミーバンプの分布密度は、2 % ~ 30 % であることを特徴とする特徴とする請求項 1 から請求項 5 のうちいずれか 1 項に記載の積層型半導体装置。

【請求項 7】

所定分布密度のバンプが形成された回路領域を有する半導体基板であって、前記半導体基板の周辺部には、前記回路領域のバンプの分布密度より高い分布密度でダミーバンプが形成されていることを特徴とする半導体基板。

【請求項 8】

前記ダミーバンプは、前記半導体基板に埋め込まれ前記半導体基板を貫通した、電気的接続を目的としないダミー T S V (Through Si Via) の先端部に形成されていることを特徴とする請求項 7 に記載の半導体基板。

【請求項 9】

前記ダミーバンプは、前記半導体基板上に形成されたバリアメタルの上に形成されていることを特徴とする請求項 7 に記載の半導体基板。

【請求項 10】

前記半導体基板の周辺部に形成された前記ダミーバンプは、前記半導体基板同士の接合用の接点としてのみ用いられるものであることを特徴とする請求項 7 から請求項 9 のうちいずれか 1 項に記載の半導体基板。

【請求項 11】

前記ダミーバンプの分布密度は、前記回路領域に形成されたバンプの分布密度の 1.5 倍から 3 倍とされていることを特徴とする特徴とする請求項 7 から請求項 10 のうちいずれか 1 項に記載の半導体基板。

【請求項 12】

前記ダミーバンプの分布密度は、2 % ~ 30 % であることを特徴とする請求項 7 から請求項 11 のうちいずれか 1 項に記載の半導体基板。

【請求項 13】

所定分布密度のバンプが形成された回路領域を有する 2 つの半導体基板を、前記バンプ同士を接合して積層する工程を有する積層型半導体装置の製造方法であって、前記半導体基板の周辺部に前記所定分布密度のバンプより高い分布密度でダミーバンプが形成された半導体基板を用い、前記所定密度のバンプを有する回路領域のバンプ同士を接合すると共に、前記ダミーバンプ同士を接合する工程を有することを特徴とする積層型半導体装置の製造方法。

【請求項 14】

半導体基板上に所定分布密度のバンプを有する回路領域を形成するステップと、前記半導体基板上の回路領域の周辺部に前記所定分布密度より高い分布密度のダミーバンプを形成するステップと、前記所定分布密度のバンプを有する回路領域のバンプ同士を接合するステップと、前記ダミーバンプ同士を接合するステップとを有することを特徴とする積層型半導体装置の製造方法。

【請求項 15】

さらに、前記回路領域のバンプバンプ同士と、ダミーバンプ同士が接合された半導体基板の一方の非接合側の面を研磨して、研磨面の前記回路領域には前記所定分布密度のバンプ、その周辺部には前記所定分布密度より高い分布密度のダミーバンプを形成するステップと、前記所定分布密度のバンプが形成された回路領域を有し、その周辺領域には前記所定分布密度のバンプより高い分布密度のダミーバンプが形成された別の半導体基板を用意するステップと、当該別の半導体基板の前記バンプと前記研磨された面に形成された前記バンプ、当該別の半導体基板の前記ダミーバンプと前記研磨された面に形成された前記ダミーバンプとを接合するステップとを有することを特徴とする請求項 13 又は請求項 14 に記載の積層型半導体装置の製造方法。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、積層型半導体装置、半導体基板、及び積層型半導体装置の製造方法に関するものである。

**【背景技術】****【0002】**

半導体装置においては、その集積度を上げる技術が日夜進歩しており、これまで、主として回路パターンの微細化の促進により集積度が高められてきた。しかしながら、論文(岡本和也:電子情報通信学会論文誌 J88-C pp.839-850 (2005))に記述されているように、(1)トランジスタの物理限界、(2)半導体システムとしての性能限界、(3)装置、マスク等の高騰に起因する経済性限界、により、微細化そのものが限界を迎える、それ以上集積度を上げるために、従来の2次元から3次元構造へ展開することが一つの解として期待されている。

**【0003】**

3D-LSIを大きく分類すると、KGD(Known-Good-Die)のみを低精度のダイボンダで積層しワイヤボンドで半導体チップ間を接続する「簡易Chip積層」、バーンイン・テストを行った良品パッケージを積層する「パッケージ型積層」、そして、Siウェハ上に素子間の貫通電極を設けウェハもしくは半導体チップ同士を直接接続して形成する「貫通電極型積層(以下、TSV:Through Si Via積層と称する)」に分類できる。

**【0004】**

前2者は既に実用化の域にあり、TSV積層が最終的な形態として期待されている。例えば、DRAMの場合、高度な微細化を待たずにメモリセルアレイウェハの単純な積層により、チップサイズや設計線幅の変更なく容量を増大できるためである。

**【0005】**

さて、TSV積層を以下の3つの方法に分類する。

(1) Chip-to-Chip(C2C): KGD(Known-Good-Die)同士を積層する簡便な手法である。

(2) Chip-to-Wafer(C2W): ウエハ上にKGDを搭載するもので(1)と類似の系といえる。

(3) Wafer-to-Wafer(W2W): 高歩留まりウェハを前提とし、ウェハ同士を直接張り合わせる方式であり最終的な積層形態といえる。

**【0006】**

本発明の実施の形態としては、(3)のW2W方式のプロセスの一つを例にとりあげるが、本発明は、C2Cでの背面研磨での薄化にも適用できる技術である。

**【0007】**

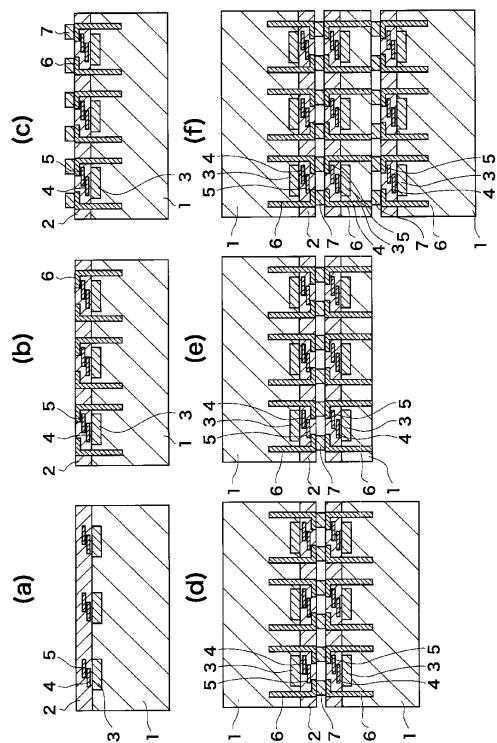

W2Wプロセスには様々な方法が存在するが、その代表例を図6に示す。表面にSiO<sub>2</sub>、Si<sub>3</sub>N<sub>4</sub>、ポリイミド等の絶縁層2が形成されたSi基板1の内部に公知の方法によりトランジスタ回路3を形成する。そして、絶縁層2内に、AIパッド4、5を形成し、単位回路とする。これを表面から見たものが単位回路領域となる(a)。なお、以下の説明においては、一つの単位回路領域のみを示しているが、全ての作業は、半導体基板全体に対して同時に行われる。

**【0008】**

次にRIE(Reactive-Ion-Etching)により絶縁層2とSi基板1とに穴あけを行い、その中に導電体(例えばCu)を充填する。この導電体は、後に積層される半導体基板同士の電気接続を行うためのものでありTSV(Through-Si-Via)6と呼ばれる。なお、TSV6の周りには、SiO<sub>2</sub>等からなる絶縁膜と、TiN等からなるバリアメタルが形成され、Si基板1との絶縁を図るようになっているが図示を省略している(b)。

**【0009】**

10

20

30

40

50

次に T S V 6 の露出部分にバンプ 7 を形成する ( c )。バンプ 7 は例えば SnAgCu 等で形成されており、半導体基板同士の T S V 6 の電気的接続と、ウエハ間接合の機械的強度を増すという役割をもっている。通常、バンプ 7 は T S V 6 に対応して形成されるが、機械的強度を増すために、T S V 6 の無い部分にも形成される場合がある。

【 0 0 1 0 】

続いて ( c ) のようにして形成された半導体基板の表面同士が相対するようにして向き合わせ、バンプ 7 同士を接合する ( d )。接合されたバンプ 7 の厚みは、1 つの半導体基板に形成されたものの厚さの 2 倍となるはずであるが、接合に際して押圧されるので、一般にそれよりも少し薄くなる。 ( d ) においては、バンプ 7 の厚さを実際より薄めに描いている。

10

【 0 0 1 1 】

次に、このようにして接合された 2 つの半導体基板の一方の裏面を C M P 等により研磨し、T S V 6 を露出させる ( e )。続いて、( c ) と同じ構造を有する半導体基板のバンプ 7 を、露出した T S V 6 に接合することにより、3 枚の半導体基板同士を接合する ( f )。このとき、露出した T S V 6 の表面に新たにバンプ 7 を形成し、このバンプ 7 と、3 枚目の基板のバンプ 7 とを接合させるようにしてもよい。

【 0 0 1 2 】

以下、3 枚目の基板の裏面を研磨して T S V 6 を露出させ、図 6 ( c ) と同じ構造を有する半導体基板のバンプ 7 を、露出した T S V 6 に接合することにより、4 枚の半導体基板同士を接合する。これを繰り返して、多数層の積層を有する積層型半導体装置が形成される。

20

【発明の開示】

【発明が解決しようとする課題】

【 0 0 1 3 】

このようにして製造される積層型半導体装置において、T S V 6 の深さはなるべく浅いことが要求される。その理由の一つとして、この深さが深いと、R I E の際に穴を開ける時間がかかり、その分、スループットが低下することがあげられる。

【 0 0 1 4 】

従って、図 6 ( e ) に示されるように、T S V 6 の表面を露出させるために半導体基板の研磨を行ったとき、残る半導体基板の厚さは非常に薄いものとなる ( 50  $\mu$ m 以下となる場合が多くある )。このような薄い半導体基板の研磨を行うとき、その周辺部 ( ベベル部 ) の強度が耐えきれず、チッピングという現象が発生する。これは、半導体基板がベベル部で特に薄くされているために、機械的強度が研磨力に耐えきれずエッジ部が撓み、エッジ部が欠ける現象である。チッピングが起こるとベベル部の乱れを起こすと共に、破片が単位回路領域に入り、研磨装置との間に挟まり、単位回路領域をも破損させるという問題が発生する。

30

【 0 0 1 5 】

なお、従来から、ベベル部にバンプが形成されたものが存在するが、従来のバンプの分布密度では、必要とされる機械的強度が得られず、かえってバンプ自体が剥離して、散逸し、半導体チップの歩留まりを著しく劣化させていた。

40

【 0 0 1 6 】

本発明はこのような事情に鑑みてなされたものであり、製造工程においてチッピングが発生しにくい積層型半導体装置、それに使用する半導体基板、及びその積層型半導体装置の製造方法を提供することを課題とする。

【課題を解決するための手段】

【 0 0 1 7 】

前記課題を解決するための第 1 の手段は、所定分布密度のバンプが形成された回路領域を有する半導体基板同士が、前記バンプを接合することにより積層されて形成された積層型半導体装置であって、前記半導体基板の周辺部には、前記回路領域のバンプの分布密度より高い分布密度でダミーバンプが形成され、前記半導体基板同士において、前記ダミー

50

バンプ同士の接合がなされていることを特徴とする積層型半導体装置である。

【0018】

前記課題を解決するための第2の手段は、前記第1の手段であって、前記ダミーバンプは、前記半導体基板に埋め込まれ前記半導体基板を貫通した、電気的接続を目的としないダミーT S V (Through Si Via) の先端部に形成されていることを特徴とするものである。

【0019】

前記課題を解決するための第3の手段は、前記第1の手段であって、前記ダミーバンプは、前記半導体基板上に形成されたバリアメタルの上に形成されていることを特徴とするものである。

10

【0020】

前記課題を解決するための第4の手段は、前記第1の手段から第3の手段のいずれかであって、前記半導体基板の周辺部に形成された前記ダミーバンプは、前記半導体基板同士の接合用の接点としてのみ用いられるものであることを特徴とするものである。

【0021】

前記課題を解決するための第5の手段は、前記第1の手段から第4の手段のいずれかであって、前記ダミーバンプの分布密度は、前記回路領域に形成されたバンプの分布密度の1.5倍から3倍とされていることを特徴とするものである。

【0022】

前記課題を解決するための第6の手段は、前記第1の手段から第5の手段のいずれかであって、前記第の手段であって、前記ダミーバンプの分布密度は、2%～30%であることを特徴とする。

20

【0023】

前記課題を解決するための第7の手段は、所定分布密度のバンプが形成された回路領域を有する半導体基板であって、前記半導体基板の周辺部には、前記回路領域のバンプの分布密度より高い分布密度でダミーバンプが形成されていることを特徴とする半導体基板である。

【0024】

前記課題を解決するための第8の手段は、前記第7の手段であって、前記ダミーバンプは、前記半導体基板に埋め込まれ前記半導体基板を貫通した、電気的接続を目的としないダミーT S V (Through Si Via) の先端部に形成されていることを特徴とするものである。

30

【0025】

前記課題を解決するための第9の手段は、前記第7の手段であって、前記ダミーバンプは、前記半導体基板上に形成されたバリアメタルの上に形成されていることを特徴とするものである。

【0026】

前記課題を解決するための第10の手段は、前記第7の手段から第9の手段のいずれかであって、前記半導体基板の周辺部に形成された前記ダミーバンプは、前記半導体基板同士の接合用の接点としてのみ用いられるものであることを特徴とするものである。

40

【0027】

前記課題を解決するための第11の手段は、前記第7の手段から第10の手段のいずれかであって、前記ダミーバンプの分布密度は、前記回路領域に形成されたバンプの分布密度の1.5倍から3倍とされていることを特徴とするものである。

【0028】

前記課題を解決するための第12の手段は、前記第7の手段から第11の手段のいずれかであって、前記ダミーバンプの分布密度は、2%～30%であることを特徴とするものである。

【0029】

前記課題を解決するための第13の手段は、所定分布密度のバンプが形成された回路領

50

域を有する2つの半導体基板を、前記バンプ同士を接合して積層する工程を有する積層型半導体装置の製造方法であって、前記半導体基板の周辺部に前記所定分布密度のバンプより高い分布密度でダミーバンプが形成された半導体基板を用い、前記所定密度のバンプを有する回路領域のバンプ同士を接合すると共に、前記ダミーバンプ同士を接合する工程を有することを特徴とする積層型半導体装置の製造方法である。

#### 【0030】

前記課題を解決するための第14の手段は、半導体基板上に所定分布密度のバンプを有する回路領域を形成するステップと、前記半導体基板上の回路領域の周辺部に前記所定分布密度より高い分布密度のダミーバンプを形成するステップと、前記所定分布密度のバンプを有する回路領域のバンプ同士を接合するステップと、前記ダミーバンプ同士を接合するステップとを有することを特徴とする積層型半導体装置の製造方法である。

10

#### 【0031】

前記課題を解決するための第15の手段は、前記第13の手段又は第14の手段であって、さらに、前記回路領域のバンプバンプ同士と、ダミーバンプ同士が接合された半導体基板の一方の非接合側の面を研磨して、研磨面の前記回路領域には前記所定分布密度のバンプ、その周辺部には前記所定分布密度より高い分布密度のダミーバンプを形成するステップと、前記所定分布密度のバンプが形成された回路領域を有し、その周辺領域には前記所定分布密度のバンプより高い分布密度のダミーバンプが形成された別の半導体基板を用意するステップと、当該別の半導体基板の前記バンプと前記研磨された面に形成された前記バンプ、当該別の半導体基板の前記ダミーバンプと前記研磨された面に形成された前記ダミーバンプとを接合するステップとを有することを特徴とするものである。

20

#### 【発明の効果】

#### 【0032】

本発明によれば、製造工程においてチッピングが発生しにくい積層型半導体装置、それに使用する半導体基板、及びその積層型半導体装置の製造方法を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0033】

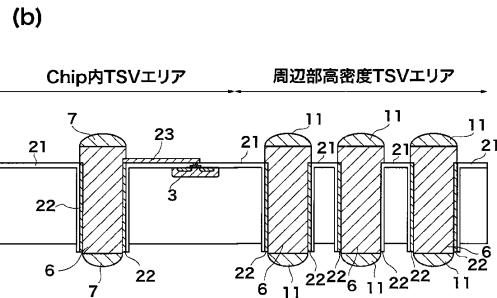

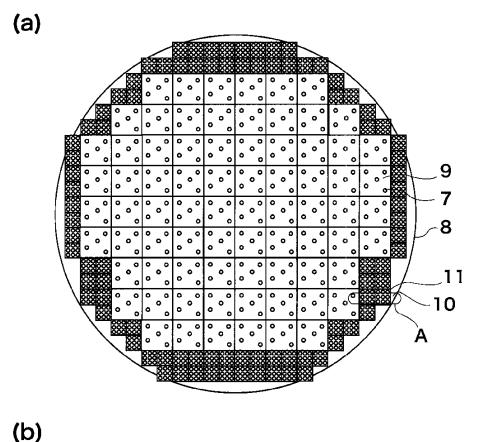

以下、本発明の実施の形態の例を、図を用いて説明する。図1は、本発明の実施の形態である積層型半導体装置を構成する1枚のウエハ8(半導体基板)の概要を示す図であり、(a)は全体を示す平面図、(b)は、(a)におけるA部付近を示す概念断面図である。この断面図は、回路領域9(1つの大きな正方形で示される)に形成されたTSV6の中心部で切断した断面図と、高密度バンプエリア10(1つの小さな正方形で示される)に形成されたTSV6の中心部で切断した断面図とが組み合わさって図示されている。

30

#### 【0034】

このウエハ8の中央部には、回路領域9が複数形成されており、回路領域9には前述のバンプ7が形成されている。回路領域9の周辺部には、高密度バンプエリア10(1つの小さな正方形で示される)が複数形成されており、高密度バンプエリア10内には、ダミーバンプ11が多数形成されている。ダミーバンプ11は、バンプ7と同じようにして、例えばSnAgCu等で形成されるが、後に示すようにTSV6を使用しないで形成される場合もある。

40

#### 【0035】

本発明の1つの特徴は、回路領域9内に形成されるバンプ7の分布密度よりも、高密度バンプエリア10内に形成されるダミーバンプ11の分布密度が高いことである。積層工程において、ダミーバンプ11は、他のウエハ8に形成されたダミーバンプ11、又は研磨されたSi基板1面に形成されたダミーバンプ11と接合されるが、回路領域9内に形成されるバンプ7の分布密度よりも高い分布密度を持つので、高い接着力を有し、研磨を行うときにも、従来のように脱落する可能性が少ない。又、ウエハ8のベベル部の強度を高くする役割を有する。よって、チッピングが発生する可能性も少なくなる。

50

## 【0036】

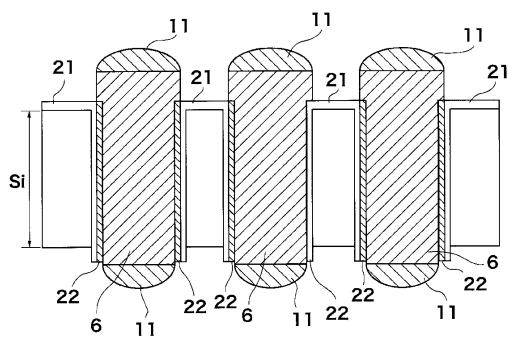

これらのダミーバンプ11は、通常は図1(b)の概念断面図に示すような構造をしている。回路領域9(Chip内TSVエリア)に形成されたTSV6は、アルミ薄膜配線23を介して、トランジスタ回路3と接続され、回路の電気接続を行う役割を果たしているが、その両端部にバンプ7が形成される。なお、図1(b)において、21は、 $\text{SiO}_2$ により形成される絶縁膜であり、22は、TiN等から形成されるバッファメタルである。

## 【0037】

高密度バンプエリア10(周辺部高密度TSV)エリア内に形成されるダミーバンプ11も同様にして形成されている。すなわち高密度バンプエリア10内にも、電気的配線接続の役割を果たしていないが、ダミーバンプ11を形成するためのTSV6が高密度に設けられている。しかし、このTSV6は、アルミ薄膜配線23によりトランジスタ回路3と接続されることはなく、単にその両端にダミーバンプ11を形成する役割を負っているだけである。しかし、TSV6の構造は両者同じであり、単に配線接続の役割をはたしているかどうかが異なっているだけである。回路領域9内にも機械的強度の観点からダミーバンプ11が形成されることがあるが、その場合には、ダミーバンプ11が形成される位置に対応してTSV6を形成するようにしておく。

## 【0038】

ダミーバンプ11は、他の目的にも使用してもよいが、他のウエハ8との接合にのみ使用するようにしてもよい。

## 【0039】

又、ダミーバンプ11の分布密度は、回路領域9に形成されたバンプ7の分布密度の1.5倍から3倍とすることが好ましい。接着力及び強度の面からは、分布密度が高い方が望ましいが、1.5倍あれば十分な効果が得られる。又、3倍を超えるとウエハ8を積層後に注入する接着剤がウエハ8間の内部まで入りにくくなるので好ましくない。

## 【0040】

別の観点からは、ダミーバンプ11の分布密度は、2%~30%であることが好ましい。接着力及び強度の面からは、分布密度が高い方が望ましいが、2%あれば十分な効果が得られる。又、30%を超えるとウエハ8を積層後に注入する接着剤がウエハ8間の内部まで入りにくくなるので好ましくない。

## 【0041】

以上の説明においては、回路領域9の周辺部に上述のような高密度バンプエリア10が形成され、その中にダミーバンプ11が回路領域9中のバンプ7よりも高い分布密度で配置されていること、ウエハ8同士の接合に際し、ダミーバンプ11同士が接合されることを説明したが、その他の積層型半導体装置の製造工程は、図6を用いて説明した従来の積層型半導体装置の製造工程と変わることはないので、その説明を省略する。上記のような高密度バンプエリア10とダミーバンプ11を設けることにより、周辺部に特殊なシールをせずに、また背面研磨条件を変更することなく、良好なベベル部を形成することができる。

## 【0042】

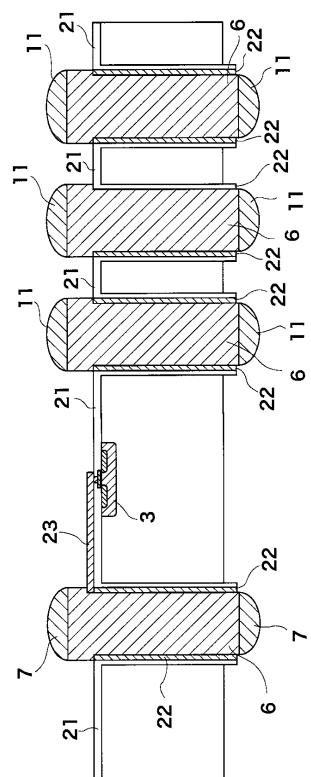

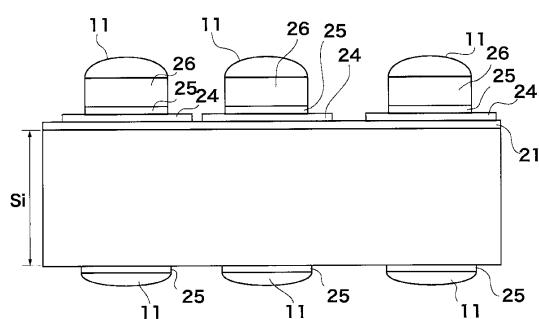

図2は、図1(b)の拡大図である。TSV6とSi層の間には、 $\text{SiO}_2$ からなる絶縁層21と、TiNからなるバッファメタル22が嵌り込んで、TSV6とSi層との絶縁が図られている。なお、Si基板の表面は21で覆われて、その上に必要なアルミ薄膜配線23が形成されている。

## 【0043】

図3は、回路領域9に形成されたTSV6の近傍を、図4は、高密度バンプエリア10内に形成されたTSV6(ダミーTSV)の近傍を、さらに拡大して示す図である。

## 【0044】

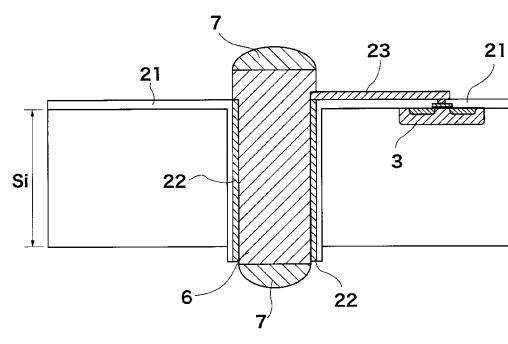

以上示した例においては、バンプ7やダミーバンプ11は、予め形成されたTSV6の両端に形成されたが、ダミーバンプ11を形成するためには必ずしもTSV6を必要としない。特に、積層後TSV6を露出させるために研磨されたSi基板1の表面にダミーバン

10

20

30

40

50

プ11を形成する場合には、Si基板1の表面にダミーバンプ11を形成するようにするこ

とが、ダミーTSVを形成する必要がないので好ましい。

【0045】

その例を図5に示す。図5のSi層の上側表面側には絶縁層21が形成されているが、そ

の上にバッファメタル25を形成する。そしてその上にダミーバンプ11を形成する。(\*

\*注意：24は不要です)

図5において、Si基板の下側表面はSiがむき出しになっており、丁度、研磨を終了した

状態に相当する。この表面上にTiN等で直接バッファメタル25を形成する。そして、バ

ッファメタル25の上にダミーバンプ11を形成する。このようにすると、高密度バンプ

エリア10や回路領域9にダミーとなるTSV6を形成しなくても、ダミーバンプ11を

高密度で形成することができる。なお、図5において、上側表面と下側表面とに、それ

ぞれダミーバンプ11と形成しているが、これらは独立であり、上側表面と下側表面のダミ

ーバンプ11間に特別の関係はない。単に、別々の表面を使用して、説明を行っただけで

ある。

【実施例】

【0046】

背面研磨工程は通常、粗研磨と仕上げ研磨で形成される。ここでは簡便のため粗研磨に

ついて説明するが、仕上げ研磨、ならびに最終段階である破碎層（破碎層の10倍～20

×倍程度の20μm程度）除去のための鏡面研磨についても同様に理解される。

【0047】

ここでの粗研磨は、砥石外径350mm、回転速度を1750rpmとし周速度を1920m/min程度に

設定した。一方、ワークチャックの回転速度を300rpmとし、砥石の送り速度を50μm/

min程度以上に可変的に設定し、ウエハベベル部の状態を観察した。

【0048】

この場合、支配的な因子はウエハベベルに印加される横方向せん断応力である。発明者

らはこの応力を研磨装置の実機上で精密に測定し、最大10N/cm<sup>2</sup>程度に設定、かつバン

プとなる金属材料の機械的破壊とSi基板の脆性破壊について事前に有限要素法解析を施

し、それらの相関関係から本発明に至った。

【0049】

まず、比較例として、高密度バンプエリア10とダミーバンプ11を形成しないウエハ

8について研磨を行った。バンプ7内の金属バンプ（Sn-Ag-Cu系）の分布密度は、1.2%

、直径は200μmである。このウエハ8のバンプ7と、全面にCu膜を成膜したウエハを接

合した後、一方のウエハを100μmまで薄化した状態において、X線透視像を観察するこ

とで評価をおこなった。その結果、強い横方向せん断応力を受け、バンプ7の一部は破損

し、かつ周辺部へ散逸していた。

【0050】

実施例として、研磨条件を比較例と同じとし、比較例で使用した回路領域9の周辺に5

mmの高密度バンプエリア10を形成し、この中に、分布密度5%のダミーバンプ11を

形成した。ダミーバンプ11の直径は200μmである。このウエハ8のバンプ7、ダミー

バンプ11と、全面にCu膜を成膜したウエハを接合した後、一方のウエハを100μm以下

まで薄化した場合について、チッピングの発生、バンプ7とダミーバンプ11の剥離の状

態を調べた。その結果、チッピング、バンプ7とダミーバンプ11の剥離とも発生しない

こと、また有限要素法解析どおり、Siの脆性破壊も生じないことを確認した。

【図面の簡単な説明】

【0051】

【図1】本発明の実施の形態である積層型半導体装置を構成する1枚のウエハ（半導体基

板）の概要を示す平面図である。

【図2】図1（b）の拡大図である。

【図3】回路領域に形成されたTSVの近傍を、さらに拡大して示す図である。

【図4】高密度バンプエリア内に形成されたTSV（ダミーTSV）の近傍を、さらに拡

大して示す図である。

10

20

30

40

50

大して示す図である。

【図5】Si基板の表面にダミーバンプを形成した例を示す図である。

【図6】W2Wプロセスの代表例を示す図である。

【符号の説明】

【0052】

1...Si基板、2...絶縁層、3...トランジスタ回路、4...Alパッド、5...Alパッド、6...TSV、7...バンプ、8...ウェハ、9...回路領域、10...高密度バンプエリア、11...ダミーバンプ、21...絶縁層、22...バッファメタル、23...アルミ薄膜配線、24...アルミ配線層、25...バッファメタル、26...シード層

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

---

フロントページの続き

(56)参考文献 特開2002-076247(JP, A)

国際公開第2006/011477(WO, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 25/065

H01L 25/07

H01L 25/18

H01L 21/60