(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5799167号

(P5799167)

(45) 発行日 平成27年10月21日(2015.10.21)

(24) 登録日 平成27年8月28日(2015.8.28)

(51) Int.Cl.

F 1

|                   |                  |             |              |              |

|-------------------|------------------|-------------|--------------|--------------|

| <b>H03K 19/00</b> | <b>(2006.01)</b> | <b>H03K</b> | <b>19/00</b> | <b>A</b>     |

| <b>G06F 1/32</b>  | <b>(2006.01)</b> | <b>G06F</b> | <b>1/32</b>  | <b>A</b>     |

| <b>G06F 1/04</b>  | <b>(2006.01)</b> | <b>G06F</b> | <b>1/04</b>  | <b>5 7 5</b> |

請求項の数 17 (全 15 頁)

(21) 出願番号 特願2014-519292 (P2014-519292)

(86) (22) 出願日 平成24年7月5日 (2012.7.5)

(65) 公表番号 特表2014-526175 (P2014-526175A)

(43) 公表日 平成26年10月2日 (2014.10.2)

(86) 國際出願番号 PCT/US2012/045559

(87) 國際公開番号 WO2013/006702

(87) 國際公開日 平成25年1月10日 (2013.1.10)

審査請求日 平成27年6月26日 (2015.6.26)

(31) 優先権主張番号 13/176,842

(32) 優先日 平成23年7月6日 (2011.7.6)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVICES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンノイベイル、ビィ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・ブレイス、メイル・ストップ

・68 (番地なし)

(74) 代理人 100108833

弁理士 早川 裕司

(74) 代理人 100111615

弁理士 佐野 良太

最終頁に続く

(54) 【発明の名称】パイプライン方式のパワーゲーティング

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のソース記憶素子と、

複数のデスティネーション記憶素子と、

前記複数のソース記憶素子の間に接続された複数のパワーゲーティングされたゲートであって、前記デスティネーション記憶素子へ供給する複数のパワーゲーティングされたゲートと、

パワー供給ノードと、前記パワーゲーティングされたゲートとの間に直列に接続された1つ以上のパワーゲートであって、デアサートされた、スリープ状態を示す制御信号に応じて、前記パワーゲーティングされたゲートを通る電流フローを低減し、アサートされた、ウェイク状態を示す制御信号に応じて、前記パワーゲーティングされたゲートを通る電流フローを可能にする1つ以上のパワーゲートと、

1つ以上の前記ソース記憶素子をクロッキング可能にする1つ以上のソースクロックイネーブル信号を受信し、少なくとも1つのデスティネーションクロックイネーブル信号を受信するように接続された制御ロジックであって、前記ソースクロックイネーブル信号の何れかのアサーションに応じて、前記制御信号が前記ウェイク状態を示すように構成されている、制御ロジックと、を備え、

前記制御ロジックは、前記1つ以上のソースクロックイネーブル信号のすべてがデアサートされ、且つ、前記デスティネーションクロックイネーブル信号がアサートされた後にのみ、前記制御信号が前記スリープ状態を示すように構成されており、これによって、前

10

20

記パワーゲーティングされたゲートにより供給された値を処理するために、前記デスティネーション記憶素子がクロックされるのを可能にする、

装置。

**【請求項 2】**

前記制御ロジックは状態機械を含み、

状態機械は、アサートされた前記ソースクロックイネーブル信号の何れかに応じて、新たなソースイネーブル制御信号を、前記1つ以上のソースクロックイネーブル信号が有効にされていることを示す前記状態機械の第1の状態にアサートし、前記ソース記憶素子の前記ソースクロックイネーブル信号のすべてがデアサートされ、且つ、前記少なくとも1つのデスティネーションクロックイネーブル信号がアサートされているのに応じて、前記新たなソースイネーブルを前記状態機械の第2の状態にデアサートし、前記状態機械の前記第2の状態に移行した後にのみ、前記パワーゲートのための前記制御信号をデアサートする、請求項1に記載の装置。10

**【請求項 3】**

第1のデスティネーションクロックイネーブル信号を前記新たなソースイネーブル信号と組み合わせて、前記デスティネーションクロックイネーブル信号を生成するためのロジックゲートを備える、請求項2に記載の装置。

**【請求項 4】**

前記制御ロジックは、デスティネーション記憶素子のためのデスティネーションクロックイネーブル信号を、前記1つ以上のソースクロックイネーブル信号がアサートされた後の少なくとも1クロックサイクルの間遮断することによって、パワーゲーティングされたロジックが完全に充電されるまでデスティネーション記憶素子がクロックされないことを確保する、請求項1に記載の装置。20

**【請求項 5】**

前記1つ以上のパワーゲートは、前記パワーゲーティングされたゲートとグランドとの間ににおいて直列の1つ以上のN M O Sトランジスタを含む、請求項1に記載の装置。

**【請求項 6】**

前記1つ以上のパワーゲートは、前記パワーゲーティングされたゲートと電源電圧との間ににおいて直列の1つ以上のP M O Sトランジスタを含む、請求項1に記載の装置。

**【請求項 7】**

前記制御ロジックは、遮断信号を供給して、前記デスティネーション記憶素子のクロッキングを、前記ソース記憶素子がクロックされた後まで遮断するように構成されている、請求項1に記載の装置。30

**【請求項 8】**

前記遮断信号は、前記デスティネーション記憶素子のクロッキングを有効にするために、第1のデスティネーションクロックイネーブル信号と論理的に組み合わされている、請求項7に記載の装置。

**【請求項 9】**

前記ソース記憶素子と前記デスティネーション記憶素子との間に接続された少なくとも1つのゲートであって、前記ソース記憶素子に対してより近い位置に存在する少なくとも1つのゲートをさらに備え、40

前記少なくとも1つのゲートは、前記デスティネーション記憶素子のみに供給する出力信号を有し、前記ソース記憶素子と前記デスティネーション記憶素子との間の他のゲートがパワーゲーティングされるのに対し、前記少なくとも1つのゲートは、パワーゲーティングから除外されている、請求項1に記載の装置。

**【請求項 10】**

制御信号にしたがって1つ以上のパワーゲートを制御することによって、1つ以上のソース記憶素子と、1つ以上のデスティネーション記憶素子との間に接続された複数のパワーゲーティングされたゲートにおける電流フローを低減するステップと、

前記1つ以上のソース記憶素子のクロッキングを有効にする1つ以上のソースイネーブル

50

ル信号を受信し、前記 1 つ以上のソースイネーブル信号の何れかのアサーションに応じて、前記制御信号が前記 1 つ以上のパワーゲートにウェイク状態を示すようにするステップと、

デスティネーションクロックイネーブル信号を受信し、第 1 及び第 2 の条件が真であるのに応じて、前記制御信号にスリープ状態を示させるステップと、を含み、

前記第 1 の条件は、前記 1 つ以上のソースイネーブル信号のすべてがデアサートされるということであり、前記第 2 の条件は、前記デスティネーションクロックイネーブル信号がアサートされているということであり、これによって、前記デスティネーション記憶素子がクロックされて、前記パワーゲーティングされたゲートによって供給された入力を記憶するのを可能にする、

10

方法。

#### 【請求項 1 1】

前記 1 つ以上のソースイネーブル信号がアサートされるのに応じて、状態機械の第 1 の状態に移行し、新たなソースイネーブル制御信号を、前記状態機械の前記第 1 の状態にアサートするステップと、

前記ソース記憶素子のすべての前記ソースイネーブル信号がデアサートされ、且つ、少なくとも 1 つの前記デスティネーションクロックイネーブル信号がアサートされるのに応じて、第 2 の状態に移行し、前記新たなソースイネーブルを、前記状態機械の前記第 2 の状態にデアサートするステップと、を含む、

請求項 1 0 に記載の方法。

20

#### 【請求項 1 2】

前記デスティネーションクロックイネーブル信号を生成するために、第 1 のデスティネーションクロックイネーブル信号を前記新たなソースイネーブル信号と論理的に組み合わせるステップをさらに含む、

請求項 1 1 に記載の方法。

#### 【請求項 1 3】

前記パワーゲーティングされたゲートとグランドとの間において直列の 1 つ以上の NMOS トランジスタに前記制御信号を供給するステップであって、前記 1 つ以上のパワーゲートは前記 NMOS トランジスタで構成されているステップをさらに含む、

請求項 1 0 に記載の方法。

30

#### 【請求項 1 4】

前記パワーゲーティングされたゲートと電源電圧との間において直列の 1 つ以上の PMOS トランジスタに前記制御信号を供給するステップであって、前記 1 つ以上のパワーゲートは前記 PMOS トランジスタで構成されているステップをさらに含む、

請求項 1 0 に記載の方法。

#### 【請求項 1 5】

遮断信号を供給して、前記デスティネーション記憶素子のクロッキングを、前記ソース記憶素子がクロックされた後まで遮断するステップをさらに含む、

請求項 1 0 に記載の方法。

#### 【請求項 1 6】

前記遮断信号を第 1 のデスティネーションクロックイネーブル信号と組み合わせて、前記デスティネーションクロックイネーブル信号を生成するステップをさらに含む、

請求項 1 5 に記載の方法。

#### 【請求項 1 7】

集積回路のコンピュータ可読表現を記憶する有形のコンピュータ可読媒体であって、前記コンピュータ可読表現は、

複数のソース記憶素子と、

複数のデスティネーション記憶素子と、

前記複数のソース記憶素子の間に接続された複数のパワーゲーティングされたゲートであって、前記デスティネーション記憶素子へ供給する複数のパワーゲーティングされたゲ

40

50

一トと、

パワー供給ノードと、前記パワーゲーティングされたゲートとの間に直列に接続された1つ以上のパワーゲートであって、デアサートされた、スリープ状態を示す制御信号に応じて、前記パワーゲーティングされたゲートを通る電流フローを低減し、アサートされた、ウェイク状態を示す制御信号に応じて、前記パワーゲーティングされたゲートを通る電流フローを可能にする1つ以上のパワーゲートと、

1つ以上の前記ソース記憶素子をクロッキング可能にする1つ以上のソースクロックイネーブル信号を受信し、1つ以上のデスティネーションクロックイネーブル信号を受信するように接続された制御ロジックであって、前記ソースクロックイネーブル信号の何れかのアサーションに応じて、前記制御信号が前記ウェイク状態を示すように構成されている、制御ロジックと、を備え、

前記制御ロジックは、前記1つ以上のソースクロックイネーブル信号のすべてがデアサートされ、且つ、前記デスティネーションクロックイネーブル信号がアサートされた後にのみ、前記制御信号が前記スリープ状態を示すように構成されており、これによって、前記パワーゲーティングされたゲートにより供給された値を処理するために、前記デスティネーション記憶素子がクロックされるのを可能にする、

という表現を含む、

コンピュータ可読媒体。

**【発明の詳細な説明】**

**【技術分野】**

10

**【0001】**

本発明は、集積回路における省電力に関し、より具体的には、ランタイム中の漏洩電流の低減に関する。

**【背景技術】**

**【0002】**

集積回路における電力消費は、アクティブ状態でスイッチングしている回路と、アイドル状態の回路との両方に起因し得る。回路がアイドル状態の場合であっても、トランジスタからの漏洩電流は、望ましくない電力消費をもたらす。省電力に対する従来の解決方法では、長期間アイドル状態にある規模の大きいアーキテクチャ機構を特定し、使用されていない回路機構に対して供給される電圧と、供給されるクロック信号との周波数の両方、又は何れか一方を低減することによって、特定した回路に省電力機能を実装している。例えば、マルチコアプロセッサでは、例えば入出力ブロックなどの他の機能ブロックをアクティブ状態に維持しながら、1つ以上のコアが、供給される周波数及び/又は電圧を低減することによって、より低い消費電力状態に置かれる場合がある。しかしながら、特に、例えば携帯機器、ラップトップ及びタブレットなどのバッテリ駆動式装置においては、省電力のためのさらなる方法を見出すことによって、電池の寿命を延ばし、熱の発生を低減し、冷却要求を緩和することが望ましい。デスクトップやサーバシステムでも、電力消費を低減することは、熱の発生の低減、電力使用の低減によるコスト節減及び冷却要求の低減につながる。省電力の問題は、集積回路及びシステム設計の重要な側面であり続ける。

20

30

**【発明の概要】**

**【0003】**

集積回路の小さい機構に焦点を当てることにより、さらなる省電力が達成される。

**【課題を解決するための手段】**

**【0004】**

一実施形態では、ソース記憶素子とデスティネーション記憶素子との間に接続された複数のゲートにおける漏洩電流を減らす方法を提供する。本方法は、1つ以上のソースクロックイネーブル信号の何れかのアサーションに応じて、複数のゲートをウェイク状態にして、電流フローを可能にするステップを含む。複数のゲートは、スリープ条件に応じてスリープ状態にされており、電流フローを抑制して複数のゲートの漏洩電流を低減する。ス

40

50

リープ条件は、デスティネーションクロックイネーブル信号のアサーションを含む。

**【0005】**

一実施形態では、スリープ条件は、1つ以上のソースクロックイネーブル信号のすべてがデアサーントされたことを含む。

**【0006】**

一実施形態では、本方法は、第1の値の制御信号を1つ以上のパワーゲートに供給することにより、複数のゲートをウェイク状態にするステップと、第2の値の制御信号を前記1つ以上のパワーゲートに供給することにより、前記複数のゲートをスリープ状態にするステップとを含む。

**【0007】**

他の実施形態では、装置は、複数のソース記憶素子と、複数のデスティネーション記憶素子とを含む。複数のパワーゲーティングされたゲートは、ソース記憶素子とデスティネーション記憶素子との間に接続されており、デスティネーション記憶素子への供給を行う。1つ以上のパワーゲートは、パワー供給ノードと、パワーゲーティングされたゲートとの間に直列に接続されている。パワーゲートは、デアサーントされた、スリープ状態を示す制御信号に応じて、パワーゲーティングされたゲートを通る電流フローを低減し、アサーントされた、ウェイク状態を示す制御信号に応じて、パワーゲーティングされたゲートを通る電流フローを可能にする。制御ロジックは、1つ以上のソース記憶素子をクロッキング可能にする1つ以上のソースクロックイネーブル信号を受信するように接続される。また、制御ロジックは、少なくとも1つのデスティネーションクロックイネーブル信号を受信する。制御ロジックは、何れかのソースクロックイネーブル信号のアサーションに応じて、制御信号がウェイク状態を示すようになっている。また、制御ロジックは、1つ以上のソースクロックイネーブル信号のすべてがデアサーントされ、且つ、少なくとも1つのデスティネーションクロックイネーブル信号がアサーントされた後にのみ、制御信号がスリープ状態を示すように構成されており、これによって、デスティネーション記憶素子がクロックされて、パワーゲーティングされたゲートによって供給された値を処理するのを可能にする。

**【0008】**

一実施形態では、制御ロジックは、状態機械を含み、状態機械が、アサーントされたソースイネーブルの何れかに応じて、新たなソースイネーブル制御信号を、1つ以上のソースイネーブルがアサーントされていることを示す状態機械の第1の状態にアサーントし、ソース記憶素子のイネーブルのすべてがデアサーントされ、且つ、少なくとも1つのデスティネーションクロックイネーブル信号が有効にされているのに応じて、新たなソースイネーブルを、状態機械の第2の状態にデアサーントし、状態機械の第2の状態に移行するのに応じて、制御信号をデアサーントする。

**【0009】**

一実施形態では、装置は、ロジックゲートを含み、第1のデスティネーションクロックイネーブル信号を新たなソースイネーブル信号と組み合わせて、デスティネーションクロックイネーブル信号を生成する。

**【0010】**

一実施形態では、制御ロジックは、デスティネーション記憶素子のためのデスティネーションクロックイネーブル信号を、1つ以上のソースイネーブル信号がアサーントされた後の少なくとも1クロックサイクルの間遮断することによって、パワーゲーティングされたロジックが完全に充電されるまでデスティネーション記憶素子がクロックされないことを確保する。

**【0011】**

一実施形態では、1つ以上のパワーゲートは、パワーゲーティングされたゲートと、グランドとの間において直列の1つ以上のN M O Sトランジスタを含む。

**【0012】**

一実施形態では、1つ以上のパワーゲートは、パワーゲーティングされたゲートと、電

10

20

30

40

50

源電圧との間において直列の 1 つ以上の PMOS トランジスタを含む。

**【 0 0 1 3 】**

一実施形態では、制御ロジックは、遮断信号を供給して、ソースフリップフロップがクロックされた後までデスティネーションフリップフロップのクロッキングを遮断するよう構成されている。一実施形態では、遮断信号は、デスティネーションフリップフロップのクロッキングを有効にするのに用いられるデスティネーションクロックイネーブル信号と論理的に組み合わされている。

**【 0 0 1 4 】**

一実施形態では、装置は、ソース記憶素子とデスティネーション記憶素子との間に接続された少なくとも 1 つのゲートであって、ソース記憶素子の近くに位置する少なくとも 1 つのゲートを含み、少なくとも 1 つのゲートは、デスティネーション記憶素子のみに供給する出力信号を有し、ソース記憶素子とデスティネーション記憶素子との間の他のゲートがパワーゲーティングされる一方で、パワーゲーティングから除外されている。

10

**【 0 0 1 5 】**

他の実施形態では、制御信号を用いて 1 つ以上のパワーゲートを制御することによって、1 つ以上のソース記憶素子と 1 つ以上のデスティネーション記憶素子との間に接続された、複数のパワーゲーティングされたゲートにおける電流フローを制御するステップを含む方法が提供される。1 つ以上のソース記憶素子のクロッキングを有効にする 1 つ以上のソースイネーブル信号は、受信され、1 つ以上のソースイネーブル信号の何れかのアサーションに応じて、制御信号が、1 つ以上のパワーゲートにウェイク状態を示すようにし、これによって、複数のパワーゲーティングされたゲートを通る電流フローを可能にする。制御信号は、第 1 及び第 2 の条件が真であるのに応じてスリープ状態を示し、第 1 の条件は、1 つ以上のソースクロックイネーブル信号のすべてがデアサートされることであって、第 2 の条件は、デスティネーションクロックイネーブル信号がアサートされていることであって、これによって、デスティネーション記憶素子がクロックされて、パワーゲーティングされたゲートによって供給された値を処理するのを可能にし、スリープ状態は、複数のパワーゲーティングされたゲートの電流フローを阻む。

20

**【 0 0 1 6 】**

本方法は、1 つ以上のソースイネーブルがアサートされるのに応じて、状態機械の第 1 の状態に移行し、新たなソースイネーブル制御信号を、状態機械の第 1 の状態にアサートするステップと、ソース記憶素子のすべてのソースイネーブルがデアサートされ、且つ、少なくとも 1 つのデスティネーションクロックイネーブル信号がアサートされるのに応じて、第 2 の状態に移行し、新たなソースイネーブル制御信号を、状態機械の第 2 の状態にデアサートするステップとをさらに含んでもよい。

30

**【 0 0 1 7 】**

本方法は、第 1 のデスティネーションクロックイネーブル信号を、新たなソースイネーブル制御信号と論理的に組み合わせて、デスティネーションクロックイネーブル信号を生成するステップをさらに含んでもよい。

**【 0 0 1 8 】**

本方法は、制御信号を、パワーゲーティングされたゲートと、グランドとの間で直列の 1 つ以上の NMOS トランジスタに供給するステップをさらに含み、1 つ以上のパワーゲートは、NMOS トランジスタから構成されていてもよい。

40

**【 0 0 1 9 】**

本方法は、制御信号を、パワーゲーティングされたゲートと、電源電圧との間で直列の 1 つ以上の PMOS トランジスタに供給するステップをさらに含み、1 つ以上のパワーゲートは、PMOS トランジスタから構成されていてもよい。

**【 0 0 2 0 】**

本方法は、遮断信号を供給して、ソース記憶素子がクロックされた後までデスティネーション記憶素子のクロッキングを遮断するステップをさらに含んでもよい。

**【 0 0 2 1 】**

50

本方法は、遮断信号を、第1のデスティネーションクロックイネーブル信号と組み合わせて、デスティネーションクロックイネーブル信号を生成するステップをさらに含んでもよい。

#### 【0022】

添付の図面を参照することにより、当業者には、本発明がより良く理解され、その無数の目的、特徴及び利点が明らかにされる。

#### 【図面の簡単な説明】

#### 【0023】

【図1】本発明の実施形態を用いるのに適する集積回路のハイレベル図である。

【図2】本発明の一実施形態によるパワーゲーティングロジックゲートを示すハイレベル図である。 10

【図3】図2の実施形態と関連するタイミングダイアグラムである。

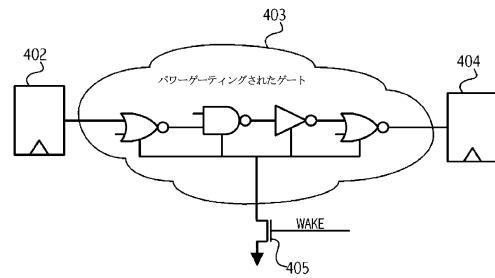

【図4A】例示的なパワーゲーティング手法を示す図である。

【図4B】追加のパワーゲートを用いる、例示的なパワーゲーティング手法を示す図である。

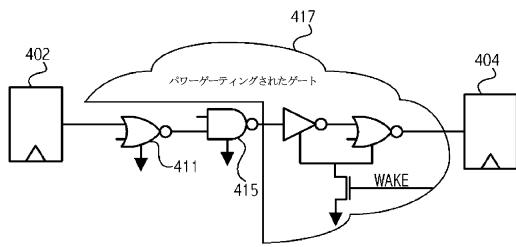

【図4C】ゲートをパワーゲーティングされないようにすることによって、タイミング制約が緩和される、例示的なパワーゲーティング手法を示すハイレベル図である。

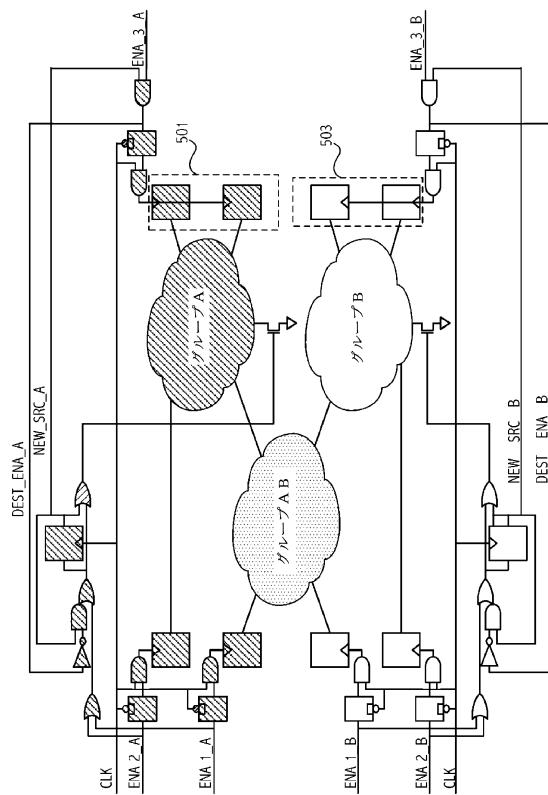

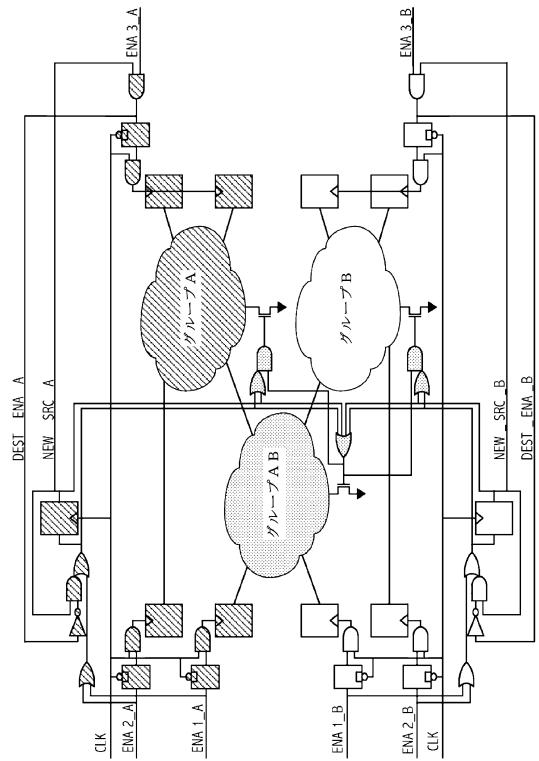

【図5】構成を示す図である。ここでは、グループAのゲート及びグループBのゲートがパワーゲーティングされており、グループA Bのゲートがパワーゲーティングされていない。 20

【図6】論理カバレッジが図5の構成を上回っている構成を示す図である。

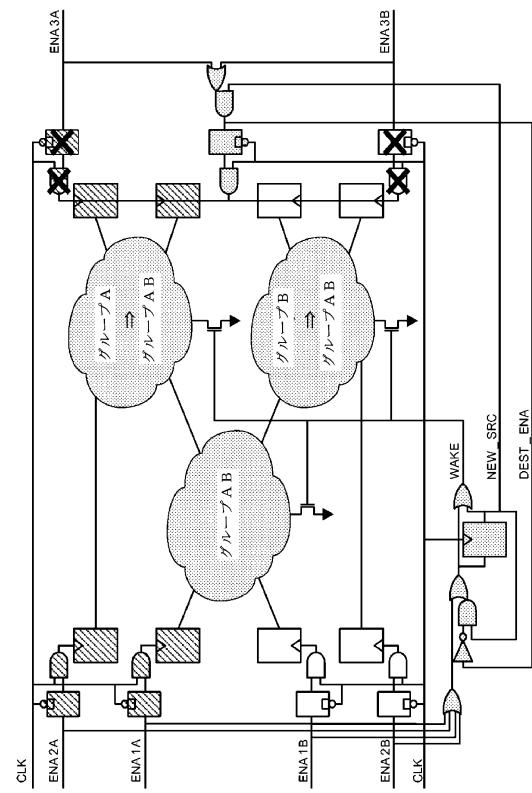

【図7】図5の構成と比べて論理カバレッジが改善され、図6の構成と比べて省電力が改善されている、複数のグループのための他の構成を示す図である。

#### 【発明を実施するための形態】

#### 【0024】

異なる図面において同じまたは類似の参照記号が使用される場合、同じまたは類似の項目を示す。

#### 【0025】

ゲートのグループをパワーゲーティングすることは、ゲートのトランジスタの漏洩電流を低減することによって、ランタイム動作中のさらなる省電力を達成する。1つの実施形態では、パワーゲートは、パワーゲーティングされたゲートと、その電源VDD及び/又はGNDとの間で直列のトランジスタ（若しくは多数の並列のトランジスタ）によって形成されている。次いで、パワーゲートは、ゲートが使用されていない場合に漏洩電流が低減され得るようにゲートをVDD及び/又はGNDから切り離すために、選択的に制御される。 30

#### 【0026】

図1を参照すると、ハイレベルブロック図は、例えばマイクロプロセッサなどの集積回路101を示している。集積回路101は、例えば処理コアなどの複数のマクロアーキテクチャ機構102を含み、これらの電力は、各マクロアーキテクチャ機構102を、シリープ状態から完全に電力を供給された状態まで、様々なレベルの性能を提供するパワー状態に置くことによって制御され得る。加えて、1つ以上のマクロアーキテクチャ機構は、ランタイム中、完全な（又は低減された）動作状態中での電力消費を低減するように制御し得るゲートのグループ103を有する。 40

#### 【0027】

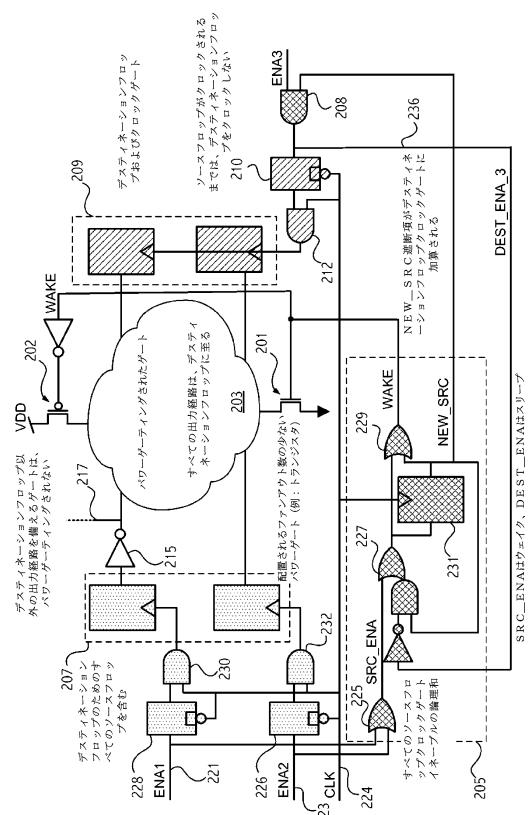

図2は、電力消費を減らすための、ランタイム中のゲートのグループの制御方法の例示的な実施形態を示す。図2を参照すると、nFETパワーゲート201は、パワーゲーティングされたゲート203とGNDとの間で直列に設けられている。パワーゲーティングされたゲート203は、図1のゲートのグループ103に対応している。パワーゲーティングされたゲートは、一般に、AND、OR、NOR、NAND及び類似のロジックゲートであり、パワーゲーティングされたゲート203として図2に表されている。ゲート 50

203がアイドル状態の場合には、パワーゲート201はオフにされて、ゲート間電圧を低減する。これによって、ゲートからの漏洩電流を低減することができる。また、nFET201を用いる代わりに、pFET202をVDDと直列に接続するように用いることが可能であり、オフにされるとゲート間電圧を低減し、これによって漏洩電流を低減することができる。

#### 【0028】

ランタイムパワーティングに関わる重要な問題は、ゲートをスリープ状態から電力が完全に供給された状態まで移行させるのに十分な時間を設けること、すなわち、ウェイク状態になるのに十分な時間を設けることである。換言すれば、パワーゲート201がオンにされた場合には、パワーゲート201(又は202)がオンになるのに応じて、パワーティングされたゲートが、完全に電力供給された状態になるように完全に充電されるまでに時間がかかる。1つの手法は、ゲートが完全に充電されるのを確実にするために、設計において十分なタイミングマージン、例えばタイミング設計においてガードバンド、を含むことである。しかしながら、このようなタイミングペナルティは、マイクロプロセッサなどの高性能集積回路では一般に許容されない。10

#### 【0029】

制御ロジック205は、ソースフリップフロップ207のクロックゲートイネーブル221, 223を監視して、パワーティングされたゲートをウェイク状態にする場合と、スリープ状態にする場合とを判定する。本明細書において詳述するように、ANDゲート208は、制御ロジック205の一部とみなされてよく、デスティネーションフリップフロップのクロッキングの制御を助けることに留意されたい。フリップフロップが図2に示される一方で、例えばラッチなどの任意のソース及びデスティネーション記憶素子が、図2のフリップフロップの代わり又はこれに追加して用いられてもよいことに留意されたい。20

#### 【0030】

図2は、例示的な実施形態の基本的な動作及び構成を示す。選ばれた一群のデスティネーションフリップフロップ209は、パワーティングされ得る一群のゲート203を判定する。換言すると、ゲートの出力経路のすべてが、デスティネーションフリップフロップ209のうち1つだけに終端する場合には、ゲートがパワーティングされ得る。デスティネーションフリップフロップ以外の場所に行く出力経路を有するゲートは、パワーティングされない。例えば、インバータ215は、デスティネーションフリップフロップ209以外のどこかへ行く出力経路217を有している。したがって、インバータ215は、パワーティングされたゲート203の一部には含まれない。制御ロジック205は、パワーゲートを制御し、クロックゲートイネーブルを監視し、パワーティングされたゲートがウェイク状態になる場合及びスリープ状態になる場合を判定する状態機械を含む。30

#### 【0031】

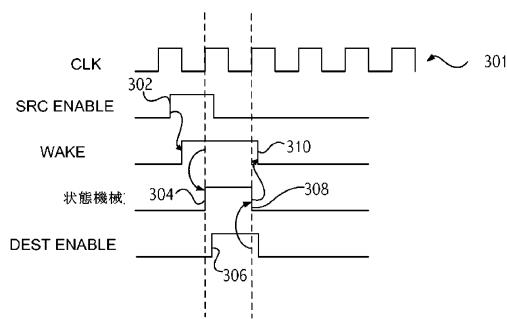

スリープの初期状態を考える。図2に示された初期のスリープ状態では、デスティネーションフリップフロップ209はクロッキングから遮断されており、パワーティングされたゲート203はスリープ状態にある。スリープ状態という語は、漏洩電流を低減するために、パワーゲート201(又は202)がオフにされていることを指す。スリープ状態では、制御ロジック205の状態機械は、WAKE信号がデアサーントされる第1の状態にある。図3は、図2の回路と関連するタイミングダイアグラムを示す。40

#### 【0032】

図3を参照し、クロック信号線224上のクロック信号CLK301を想定する。ラッチ226, 228は、イネーブル信号ENA1 221, ENA2 223を、ソースフリップフロップ207用のクロック信号のために供給するのに用いられる。イネーブル信号は、ANDゲート230, 232において、クロック信号との論理積をとられる。ゲート203は、ソースフリップフロップクロックゲートイネーブル221又は223のアサーションに応じて、ORゲート225, 227, 229による遅延の後にウェイク状態に50

なる（302に示す）。状態機械フリップフロップ231は、304における次のサイクルの立ち上がりエッジでその出力をアサートし、このようにして、第2の状態に変わる。フリップフロップ231の出力のアサーションは、遅延の後に、306における、ANDゲート208の出力でのDEST\_ENA\_3信号のアサーションとなる。次いで、ラッチ210及びANDゲート212における遅延の後に、デスティネーションフリップフロップ209がクロックされる。デスティネーションフリップフロップのためのイネーブル（ENA3）は、このときにアサートされることが仮定される。状態機械を用いると、302におけるソースイネーブルのアサートと、306におけるデスティネーションイネーブルのアサートとの間には、少なくとも1サイクルの遅延があり、デスティネーションフリップフロップクロックが遮断解除されてクロックされる前に、パワーゲーティングされたゲートが完全に充電するための時間を取ることができる。10

#### 【0033】

パワーゲーティングされたゲート203は、デスティネーションフリップフロップがクロックされるまで、制御ロジック205によってウェイク状態に保たれる。306においてDEST\_ENA\_3 236がアサートされ、ソースイネーブル221, 223がデアサートされた後に、デスティネーションフリップフロップがクロックされると、状態機械フリップフロップの出力は、308においてクロックの立ち上がりエッジをデアサートし、第1の状態に戻る。そして、310におけるWAKE信号のデアサーションによって、パワーゲーティングされたゲートをスリープ状態にする。デスティネーションフリップフロップ209用のさらなるクロックは、ソースフリップフロップが再びクロックされるまで、ANDゲート208によって遮断される。当然のことながら、ソースフリップフロップが変化しなければ、デスティネーションフリップフロップは変化しない。遮断機能は、デスティネーションフリップフロップ入力が処理される前に全クロック周期を確保する。20

#### 【0034】

一実施形態では、複数のデスティネーションイネーブルを有してもよい。この場合には、すべてのデスティネーションクロックイネーブル信号がアサートされるまで待機した後、パワーゲーティングされたゲートをスリープ状態にする必要がある。デスティネーションイネーブルは、様々なときに到達し得ることが考えられることから、当該信号は、フリップフロップに記憶された後に、すべてのビットが少なくとも一度アサートされ、ロジックに供給されてフリップフロップ231を介してスリープ状態にされる場合に、リセットされてもよい。一実施形態では、ビットは、エンコードされて、多数のフリップフロップ上に保存されてもよい。30

#### 【0035】

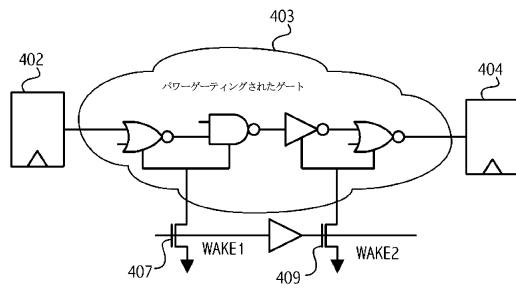

図4Aは、ソースフリップフロップ402とデスティネーションフリップフロップ404との間のパワーゲーティングされたゲート403が、単一のパワーゲート405に接続されている実施形態を示す。図4Bでは、複数のパワーゲート407, 409が使用されている。多数のパワーゲーティングされたゲートが存在する場合には、パワーゲートへのWAKEの分配は、数段のバッファを取りることもある。図4Bは、ゲートを、クリティカルタイミングゲート（WAKE1に備わっている）と、非クリティカルタイミングゲート（WAKE2に備わる）とに分割することによって、タイミング要求を緩和し得る方法を示している。このようにして、パワーゲート407はWAKE1を受信し、パワーゲート409はWAKE2を受信する。ソースフリップフロップに時間的に最も近いゲートが、最も重要である。図4Bに示される実施形態では、クリティカルゲート用のパワーゲートは、WAKE2と比べて、バッファを使うことなく（又はわずかなバッファで）WAKE1を受信する。説明を容易にするために、WAKE2は、1つのバッファで生成されるように示され、WAKE1はバッファなしで生成されるように示されている。その他の多くのバッファは、具体的な実装及びウェイク信号の各々によって駆動されるパワーゲートの数に応じて必要とされることもある。40

#### 【0036】

タイミング要求は積極的であるが、緩和し得る。ソースフリップフロップのイネーブルの論理和は、状態機械フリップフロップ 231 に供給する。しかしながら、フリップフロップ 231 用のクロックは、当該クロックがウェイク状態にするのではなく、スリープ状態にする機能を起動することから、遅延し得る。

#### 【0037】

第2のタイミング制約は、ゲートの使用時には、電力が完全に供給されていなければならないということであり、そうでないとタイミングが損なわれ得る。ゲートは、ソースフリップフロップ出力が遷移し得るときには、ウェイク状態にされていなければならない。このタイミング制約は、ソースフリップフロップの直後のゲートの段をパワーゲーティングしないことにより緩和し得る。図4Cを参照すると、ゲート 411, 415 は、パワーゲーティングされず、又はパワーゲーティングされたゲート 417 に含まれておらず、制御信号 WAKE 用の追加的なタイミングマージンを提供して、パワーゲーティングされたロジックゲートをウェイク状態にする。図4B 及び図4C に示されるこれらのタイミング緩和技術の何れも、漏れを節減させる。図4C に示されるように、設定要求は、パワーゲーティングの影響下にあるゲートの数がいくつであるかというカバレッジと引き換えにすることにより、緩和され得る。

#### 【0038】

本明細書で説明される動的なパワーゲーティング手法は、マイクロプロセッサの設計に適用できるが、回路設計一般に幅広く適用できる。本明細書における技術は一般にデジタル回路に適用し得ることから、本明細書で説明される動的なパワーゲーティングは高いカバレッジを達成でき、これは同様にさらなる省電力を意味する。タイミングの影響は控えめである。タイミングの影響は、クロックイネーブル経路における AND ゲート 208において論理積をとられたときから生じ、1つ以上のソースイネーブル信号に対する論理和ツリーからの追加的な負荷が存在する。従来の手法よりもクロックゲーティング効率が改善されるため、本明細書における動的なパワーゲーティングは、その漏れの節減への影響に関して自動的に改善される。

#### 【0039】

本明細書において説明されるパワーゲーティングは、漏れ電力が選択的且つ過渡的に低減されることから、パワーゲーティングされたドメイン内の低閾値電圧 (LVT) ゲート又は超低閾値電圧 (ULVT) ゲートのより高頻度の利用につながり得る。動的モードパワーゲーティングは、性能とパワーのトレードオフを行うときに、漏れ電力を動的電力と同じ水準にする。

#### 【0040】

図2に記載された手法の追加的な利点は、デスティネーションフリップフロップのクロック上のAND ゲート 208 によるクロック遮断機能のために、動的電力も低減される可能性があるということである。換言すると、デスティネーションクロックが制御ロジック 205 により遮断される場合には、さらに省電力になるということである。

#### 【0041】

これまで説明してきたように、パイプライン方式のパワーゲーティング (PPG) は、ランタイム中の非アクティブ状態の回路の漏れを低減する。特定の実施形態では、元の省電力を維持しながら PPG の論理カバレッジを拡大して、漏れの節減を高めることができる。

#### 【0042】

図5を参照して図示の構成を考える。ここでは、デスティネーションフリップフロップ 501 に供給するグループ A のゲートと、デスティネーションフリップフロップ 503 に供給するグループ B のゲートとがパワーゲーティングされている。グループ A B のゲートはパワーゲーティングされていないが、これは、これらが 2 つ以上のデスティネーション、すなわち、グループ A デスティネーションフリップフロップおよびグループ B デスティネーションフリップフロップの両方で終端しているためである。グループ A B ゲートは、グループ A 又はグループ B のデスティネーションフロップがクロックされている場合には

10

20

30

40

50

常にウェイク状態でなければならない。

#### 【0043】

他の重要な問題は、パワーゲーティングされたドメインの出力が、分離ゲートの無い状態で、完全に電力を供給されたゲートを駆動してはならないということである。結果は、クロスオーバー電流であり、信頼性の予測される妥協である。分離ゲートは、選択的に入力を無視するように構成されるゲートであり、これを制御するためにはフルレールの信号を要する。グループAおよびグループBのゲートでは、分離ゲートはデスティネーションフロップであり、分離制御手段はクロックである。分離ゲートをグループA Bゲートの出力に加えることは、一般に適用されるならば、タイミングに影響を与える。

#### 【0044】

図6に示すように、論理カバレッジは、デスティネーションフリップフロップの複数の群を単一のデスティネーションフロップの群として組み合わせることにより拡大し得る。図6に示されるように、ゲートのグループA, Bは、より大きなグループA Bに組み込まれている。図6の回路は、論理カバレッジを拡大するが、この手法の主要な問題は、静的及び動的省電力が実際に低減され得るということである。ここでは、グループAゲートは、グループA及びグループBのソースイネーブルの何れかによってもウェイク状態にされることから、元の構成よりもスリープ状態にされる頻度が下がる可能性がある。同様に、E N A 3 Aだけではなく、E N A 3 A又はE N A 3 BがアサートされるときにグループAデスティネーションフロップがクロックされることから、動的電力が増加する可能性がある。同様の静的及び動的な不利益がグループBゲートに当てはまる。

10

20

#### 【0045】

加えて、図6の手法には他に2つの問題がある。第1に、3つ以上のデスティネーションの群がある場合には、どのゲートのグループを組み合わせるべきか不明である。グループC, A C, B C, A B Cゲートが存在する場合を考える。すべてのグループがグループA B Cに組み込まれる場合には、上述した省電力問題が悪化する。グループA Bが形成される場合には、グループA C, B C, A B Cは(ロジックの重複なしに)論理カバレッジに含まれない。第2の問題は、グループが組み合わされるときに、レジスタ転送言語(R T L)記述を書き換えて、ロジックを再構築しなければならないことである。

#### 【0046】

図7は、改善された論理カバレッジ及び省電力を提供する、パワーゲーティングされたグループを組み合わせるための例示的な手法を示す。図6の回路とは異なり、図7では、グループAおよびグループBゲートは、元の図5の構成にあるのと同じ頻度でパワーゲーティングされる。さらに、グループA及びグループBデスティネーションフリップフロップは、元の構成にあるのと同じ頻度でクロックされる。したがって、図7では、グループA Bゲートは、漏れの節減を向上させる。この手法では、グループA又はグループBゲートがウェイク状態にされている場合には、グループA Bゲートが常にウェイク状態にされる。グループAパワーゲートを駆動するANDゲートの機能は、グループAゲートがウェイク状態にされる前にグループA Bゲートがウェイク状態にしていることを確保することであり、すなわち、論理積は、電力軽減のためにある。同じ原理は、グループBパワーゲートを駆動するANDゲートに適用される。

30

40

#### 【0047】

図7で説明された手法は、いかなるグループの形成もその他のグループの形成を妨げないという別の利点がある。さらにグループC, A C, B C, A B Cゲートが存在する場合には、これらのすべては、別個に類似のロジックを用いてパワーゲーティングされ得る。

#### 【0048】

1つの好ましい手法は、パワーゲートイネーブル経路にANDゲート遅延を加えることによって、タイミングマージンを低減することに留意されたい。さらに、組み合わせたグループが加えられる場合には、回路のレジスタ転送言語(R T L)記述が更新されなければならない。しかし、図7の手法は、論理カバレッジを拡大し、動的な省電力を損ねることなくパイプライン方式のパワーゲーティングからの漏れの節減を増加し、すべてのグル

50

ープの組み合わせに対して拡張可能である。

【 0 0 4 9 】

本発明の実施形態を説明するために回路及び物理的構造を概して仮定してきたが、現代の半導体設計及び製造において、物理的構造及び回路は、その後の設計、シミュレーション、試験又は製造段階での使用に適するコンピュータ可読記述形式で実施され得ることが良く認識されている。

【 0 0 5 0 】

例示的な構成において個別の部品として表された構造及び機能は、組み合わされた構造又は部品として実装されてもよい。本発明の様々な実施形態は、本明細書において説明したような回路、回路のシステム、関連の方法及びそのような回路、システム並びに方法のエンコーティングをそれ自体に備えるコンピュータ可読媒体（例えば、HDL、Verilog、GDSIIデータ）を含むように企図される。コンピュータ可読媒体は、有形のコンピュータ可読媒体、例えば、ディスク、テープ又はその他の磁気、光学若しくは電子記憶媒体を含む。回路、システム及び方法のエンコーティングをそれ自体に備えるコンピュータ可読媒体に加えて、コンピュータ可読媒体は、本発明を実装するために使用され得る命令及びデータを記憶してもよい。本明細書において説明された構造は、プロセッサ上で実行されるソフトウェアを用いて、ハードウェア上で実行されるファームウェアを用いて、又はソフトウェア、ファームウェア及びハードウェアの組み合わせによって実装されてもよい。

( 0 0 5 1 )

本明細書において説明された本発明の記述は、説明のためのものであり、以下の特許請求の範囲で説明されるような本発明の範囲を限定するように意図されない。本明細書において開示された実施形態のその他の変形及び変更は、以下の特許請求の範囲で説明されるような本発明の範囲から逸脱することなしに、本明細書において説明された記述に基づいてなされ得る。

【図2】

FIG. 1

【図3】

【図4 B】

【図4 A】

【図4 C】

【図5】

【図6】

【図7】

---

フロントページの続き

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 ダニエル ダブリュ . ベイリー

アメリカ合衆国 78750 テキサス州、オースティン、ツリー ベンド ドライブ 9716

(72)発明者 アーロン エス . ロジャース

アメリカ合衆国 78660 テキサス州、フラッガービル、プラムベイゴー ドライブ 203

(72)発明者 ジェイムズ ジェイ . モンタナーロ

アメリカ合衆国 78746 テキサス州、オースティン、ダイアモンド ヘッド サークル 6

205

(72)発明者 ブラッドリー ジー . バージェス

アメリカ合衆国 78745 テキサス州、オースティン、サンセット トレイル 21

(72)発明者 ピーター ジェイ . ハンナン

アメリカ合衆国 78735 テキサス州、オースティン、サクレッド アロー ドライブ 44

05

審査官 柳下 勝幸

(56)参考文献 特開2002-110920(JP,A)

特開2007-53680(JP,A)

特開2007-335980(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 19/00

G06F 1/04

G06F 1/32