(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5073741号

(P5073741)

(45) 発行日 平成24年11月14日(2012.11.14)

(24) 登録日 平成24年8月31日(2012.8.31)

(51) Int.Cl.

H01L 31/10 (2006.01)

F 1

H01L 31/10

A

G02F 1/1345 (2006.01)

G02F 1/1345

G02F 1/1365 (2006.01)

G02F 1/1365

請求項の数 17 (全 32 頁)

(21) 出願番号 特願2009-515226 (P2009-515226)

(86) (22) 出願日 平成20年5月19日 (2008.5.19)

(86) 国際出願番号 PCT/JP2008/059134

(87) 国際公開番号 WO2008/143213

(87) 国際公開日 平成20年11月27日 (2008.11.27)

審査請求日 平成21年7月31日 (2009.7.31)

(31) 優先権主張番号 特願2007-133508 (P2007-133508)

(32) 優先日 平成19年5月18日 (2007.5.18)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 110000338

特許業務法人原謙三國際特許事務所

(72) 発明者 佐藤 昌和

日本国大阪府大阪市阿倍野区長池町22番

22号 シャープ株式会社内

(72) 発明者 加藤 浩巳

日本国大阪府大阪市阿倍野区長池町22番

22号 シャープ株式会社内

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項1】

表示パネルに配置された光電変換素子を用いて表示面側の周囲光の強度を光電変換して検出する周囲光センサを備え、前記周囲光センサによって検出された周囲光の強度に応じて前記表示面での表示の輝度を調節する表示装置であつて、

前記光電変換素子の出力を伝達する配線に対して前記表示パネルの背面側に、電界に対するシールドとしての第1シールド電極を備えていることを特徴とする表示装置。

## 【請求項2】

前記配線の両側方に、電界に対するシールドとしての第2シールド電極を備えていることを特徴とする請求の範囲第1項に記載の表示装置。 10

## 【請求項3】

前記配線に対して前記表示面側に、電界に対するシールドとしての第3シールド電極を備えていることを特徴とする請求の範囲第1項に記載の表示装置。

## 【請求項4】

前記配線の両側方に設けられるとともに、前記第1シールド電極に接続された第2シールド電極と、

前記配線に対して前記表示面側に設けられるとともに、前記第2シールド電極に接続された第3シールド電極とを備えていることを特徴とする請求の範囲第1項に記載の表示装置。

## 【請求項5】

前記周囲光センサにおいて、

前記光電変換素子の2つの電流输出端子のうちの一方の前記電流输出端子は基準電位の電源に接続されており、

前記第1シールド電極に、他方の前記電流输出端子の電位と同じ電位が与えられることを特徴とする請求の範囲第1項から第4項までのいずれか1項に記載の表示装置。

【請求項6】

前記周囲光センサは、

前記光電変換素子として、周囲光が照射される第1光電変換素子と、基準の明るさの環境下に置かれた、前記第1光電変換素子と同じ構成の第2光電変換素子とを備えており、

前記第1光電変換素子に、前記第2光電変換素子が発生する開放電圧がバイアス電圧として印加され、前記第1光電変換素子の出力電流から、周囲光の強度を検出することを特徴とする請求の範囲第5項に記載の表示装置。 10

【請求項7】

前記光電変換素子は、少なくとも、複数の同じ光電変換素子エレメントが直列に接続された構成であることを特徴とする請求の範囲第6項に記載の表示装置。

【請求項8】

前記光電変換素子は、同じ光電変換素子エレメントが1つ以上の同じ数だけ直列接続された直列回路が複数並列に接続された構成であることを特徴とする請求の範囲第1項に記載の表示装置。

【請求項9】

前記光電変換素子は、PINフォトダイオードからなる光電変換素子エレメントを1つ以上組み合わせた構成であることを特徴とする請求の範囲第1項に記載の表示装置。 20

【請求項10】

前記PINフォトダイオードはラテラルPINフォトダイオードであることを特徴とする請求の範囲第9項に記載の表示装置。

【請求項11】

前記光電変換素子は、フォトトランジスタからなる光電変換素子エレメントを1つ以上組み合わせた構成であることを特徴とする請求の範囲第1項に記載の表示装置。

【請求項12】

前記表示パネルはTFT液晶パネルであり、

前記配線は、TFT基板の額縁領域にTFTのソース電極と同じ層を用いて形成されており、

前記第1シールド電極は、前記額縁領域にTFTのゲート電極と同じ層を用いて形成されていることを特徴とする請求の範囲第1項に記載の表示装置。 30

【請求項13】

前記表示パネルはTFT液晶パネルであり、

前記配線および前記第2シールド電極は、TFT基板の額縁領域にTFTのソース電極と同じ層を用いて形成されていることを特徴とする請求の範囲第2項に記載の表示装置。

【請求項14】

前記表示パネルはTFT液晶パネルであり、

前記配線は、TFT基板の額縁領域にTFTのソース電極と同じ層を用いて形成されており、

前記第3シールド電極は、前記額縁領域に画素電極と同じ層を用いて形成されていることを特徴とする請求の範囲第3項に記載の表示装置。 40

【請求項15】

前記表示パネルはTFT液晶パネルであり、

前記配線は、TFT基板の額縁領域にTFTのソース電極と同じ層を用いて形成されており、

前記第1シールド電極は、前記額縁領域にTFTのゲート電極と同じ層を用いて形成されており、 50

前記第2シールド電極は、前記額縁領域にTFTのソース電極と同じ層を用いて形成されており、

前記第3シールド電極は、前記額縁領域に画素電極と同じ層を用いて形成されていることを特徴とする請求の範囲第4項に記載の表示装置。

**【請求項16】**

前記表示パネルは、前記画素電極上に直接積層された、反射型表示用の反射電極を備えており、

前記第3シールド電極上に、前記反射電極と同じ層を用いて形成された第4シールド電極が設けられていることを特徴とする請求の範囲第15項に記載の表示装置。

**【請求項17】**

前記周囲光センサによって検出された前記周囲光の強度に応じて、バックライト光源の輝度を調節することにより、前記表示面での表示の輝度を調節することを特徴とする請求の範囲第12項から第16項までのいずれか1項に記載の表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、周囲光センサを備えた表示装置に関するものである。

**【背景技術】**

**【0002】**

液晶ディスプレイを備えた携帯電話やPDAなどの携帯端末として、周囲の明るさに応じて液晶ディスプレイのバックライト輝度を調節する周囲光センサ(Ambient Light Sensor)システムを備えたものが普及している。周囲光センサシステムでは、透過型液晶モード動作が可能なディスプレイに対して、パネル周囲に設けられた周囲光センサで周囲光の強度を検出し、周囲光強度が弱いときにはバックライト輝度を小さくし、周囲光強度が強いときにはバックライト輝度を大きくする制御を行うことにより、使用者に視認の快適性を提供する。また、このバックライト輝度の調節は、当該携帯端末に備えられたキーボードの透過光へも適用される。

**【0003】**

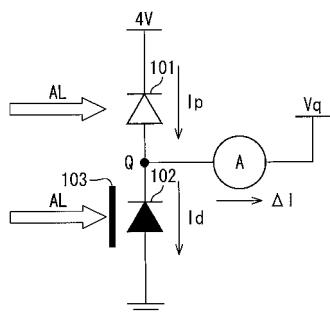

周囲光センサとしては、液晶パネル上に低温多結晶シリコンプロセスによって表示用素子とモノリシックに作り込むことのできるPINフォトダイオードが一般的に用いられる。図8に、非特許文献1に記載された、PINフォトダイオードを用いる周囲光センサの構成を示す。

**【0004】**

この周囲光センサでは、2つのPINフォトダイオード101・102が逆バイアス状態に直列接続されている。PINフォトダイオード101のカソードは+4Vの電源に接続されており、PINフォトダイオード102のアノードはGNDに接続されている。これにより、PINフォトダイオード101・102のそれぞれに、2Vずつの逆バイアスが印加された状態となっている。PINフォトダイオード101は周囲光ALを検出し、その周囲光ALの強度に応じた光電流Ipを出力する。PINフォトダイオード102は参照用フォトダイオードであって、周囲光ALが受光部に照射されるのを防止するシールド103を備えており、暗電流Idを出力する。光電流Ipにも暗電流Idが含まれており、PINフォトダイオード101のアノードとPINフォトダイオード102のカソードとの接続点Q(Vq)からは、 $I = I_p - I_d$ の差分電流が出力され、このIから、周囲光ALの強度を検出することができる。

**【特許文献1】**日本国公開特許公報「特開2004-119719号公報(公開日:2004年4月15日)」

**【特許文献2】**日本国公開特許公報「特開昭63-207183号公報(公開日:1988年8月26日)」

**【特許文献3】**WO2006/104204(2006年10月5日国際公開)

**【非特許文献1】**S.Koide et al., "LTPS Ambient Light Sensor with Temperature Comp

10

20

30

40

50

ensation", IDW'06, pp.689-690(2006)

### 【発明の開示】

#### 【0005】

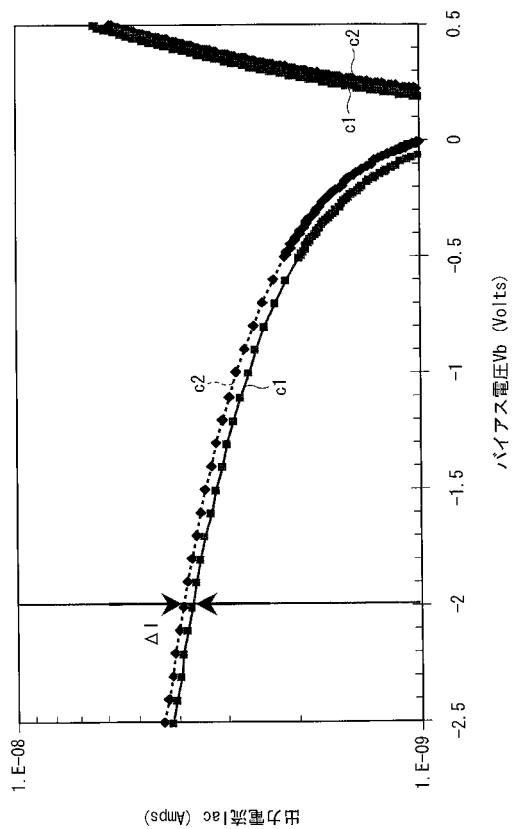

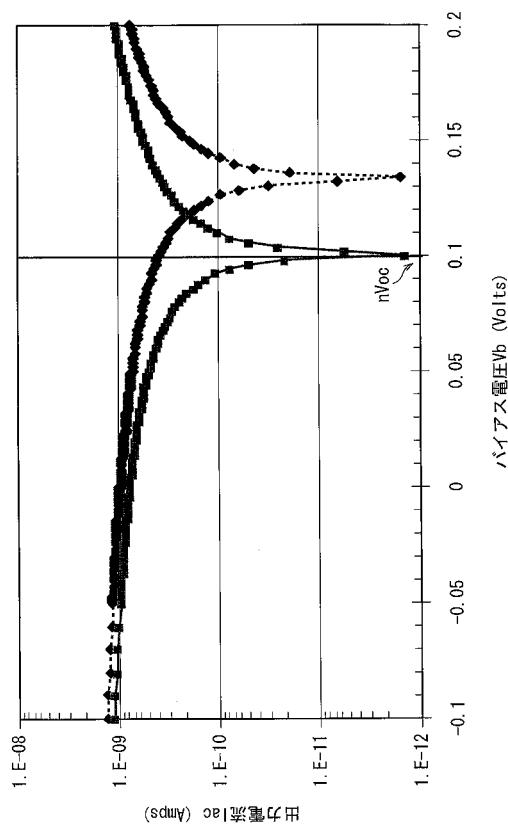

上述した非特許文献1の構成は、図9に示す、PINフォトダイオードの出力電流とバイアス電圧との関係に基づいている。曲線c1は周囲光ALが無い場合の曲線であり、曲線c2は所定強度の周囲光ALが有る場合の曲線である。両曲線とも0V付近の開放電圧よりも小さなバイアス電圧では、PINフォトダイオードの逆方向に電流が流れ、開放電圧よりも大きなバイアス電圧では、PINフォトダイオードの順方向に電流が流れることを示している。また、マイナス符号のバイアス電圧は、逆バイアスが印加されていることを示している。

10

#### 【0006】

図8の周囲光センサでは、PINフォトダイオード101が、ある周囲光ALの強度で曲線c2のバイアス電圧が-2Vである点の電流を出し、PINフォトダイオード102が曲線c1のバイアス電圧が-2Vである点の電流を出力する状態に相当している。この場合に、図9ではバイアス電圧が-2Vである点での両曲線の電流の差が、周囲光ALの検出電流Iとなる。

#### 【0007】

しかし、図9の曲線c1・c2のように、互いに接近している曲線上のあるバイアス点で差分電流Iを求めようとすると、暗電流Idを示す曲線c1の出力電流が差分電流Iに比して非常に大きいため、差分電流Iを周囲光ALの強度に正確に対応させるのが難しい。すなわち、差分電流IのSN比が悪いことと、PINフォトダイオードの製造ばらつきによって曲線c1・c2がばらつくことにより、差分電流Iが安定しづらい。

20

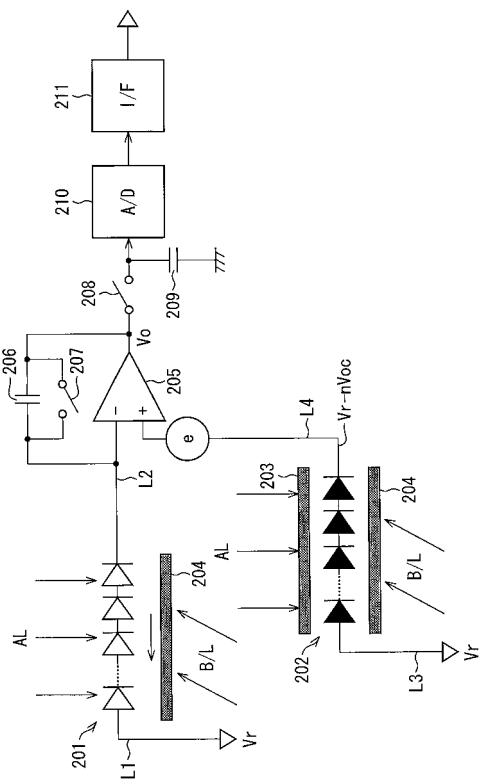

#### 【0008】

そこで、図10に示すような周囲光センサの構成が考えられる。図10の構成では、検出用素子(第1光電変換素子)201と参照用素子(第2光電変換素子)202とに、それぞれn個( $n > 1$ )のPINフォトダイオード(光電変換素子エレメント)を直列に接続したものを用いる。nは例えば10や100などで、大きさに制限はない。検出用素子201は周囲光ALを検出するとともに、液晶表示装置のバックライト光B/Lが迷光となって照射されるのを防止する光シールド204を備えている。光シールド204は、検出用素子201と参照用素子202とのそれぞれに対して、表示パネル(図14では表示パネル251に相当)の背面側に設けられている。参照用素子202は、周囲光ALが照射されるのを防止する光シールド203と、上記バックライト光B/Lが迷光となって照射されるのを防止する光シールド204とを備えており、基準の明るさの環境下に置かれている。そして、検出用素子201および参照用素子202のアノード端(電流出力端子)は、それぞれ、基準電位Vrの電源配線である配線L1、配線L3に接続されている。検出用素子201のカソード端(電流出力端子)は配線L2を介して演算増幅器205の反転入力端子に接続されており、参照用素子202のカソード端(電流出力端子)は配線L4を介して演算増幅器205の非反転入力端子に接続されている。また、演算増幅器205の出力端子と反転入力端子との間には積分コンデンサ206が接続されている。積分コンデンサ206に並列に、スイッチ207が接続されている。

30

#### 【0009】

演算増幅器205の出力端子には、スイッチ208の一端が接続されている。スイッチ208の他端は、ホールドコンデンサ209の一端に接続されている。ホールドコンデンサ209の他端はGNDに接続されている。ホールドコンデンサ209の電圧は、A/D変換器210の入力となっている。A/D変換器210の出力はインタフェース211を介してCPUやマイクロコントローラで制御されるコンピュータシステムへと接続される。

40

#### 【0010】

上記の構成の周囲光センサでは、参照用素子202に流れる電流がゼロとなるよう、参

50

照用素子 202 には、周囲光 A/L およびバックライト光 B/L が遮光された暗状態で開放電圧  $V_{oc}$  を印加する。なお開放電圧  $V_{oc}$  を印加する理由については、後述する。このように開放電圧  $V_{oc}$  が印加されるように、参照用素子 202 のアノード端の電位を  $V_r$ 、カソード端の電位が  $V_r - V_{oc}$  となるように設定する。従って、検出用素子 201 のカソード端の電位も  $V_r - V_{oc}$  となり、検出用素子 201 には上記開放電圧  $V_{oc}$  に等しいバイアス電圧が印加される。

#### 【0011】

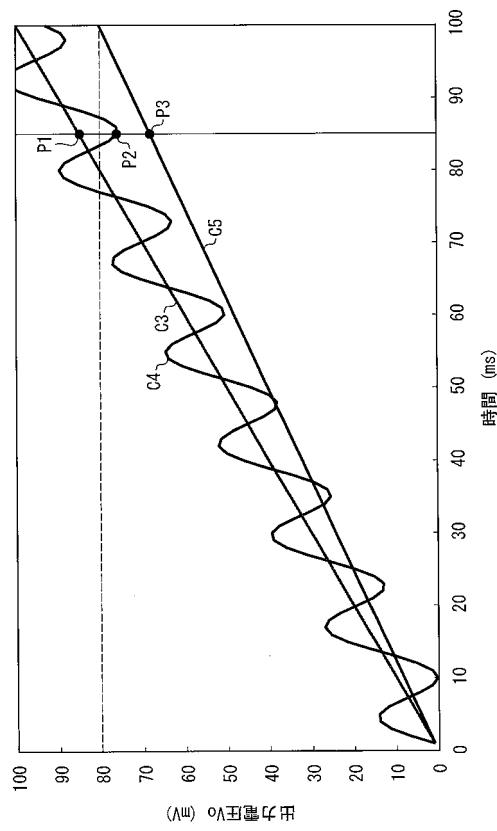

これにより、検出用素子 201 にはカソードからアノードに向かって開放電圧  $V_{oc}$  に等しいバイアス電圧が印加されているときの周囲光 A/L の強度に対応した電流が流れ、スイッチ 207 を OFF、スイッチ 208 を ON とした状態では、積分コンデンサ 206 に時間とともに電荷が蓄積された結果の出力電圧  $V_o$  が現れ、所定時間後にスイッチ 208 を OFF とすることで、ホールドコンデンサ 209 に出力電圧  $V_o$  がホールドされる。このときの積分コンデンサ 206 の電圧変化の様子を図 17 に直線 c3 で示す。積分期間中、例えば 8.5 msec でスイッチ 208 を OFF とすれば、点 P1 の電圧 8.5 mV がホールドされることになる。このホールド電圧を A/D 変換器 210 で A/D 変換してインターフェース 211 を介してコンピュータシステムに出力する。また、スイッチ 207・208 を同時に ON とすることにより、積分コンデンサ 206 が初期化されるとともに、ホールドコンデンサ 209 に電圧  $V_r - V_{oc}$  をホールドすることができる。この電圧の A/D 変換結果を、前記検出光電流の積分時のホールド電圧の A/D 変換結果から差し引けば、光電流による正味の電圧増加分を求めることができる。ホールド電圧自身の差を A/D 変換する構成にすればなお正確な結果が得られる。10 20

#### 【0012】

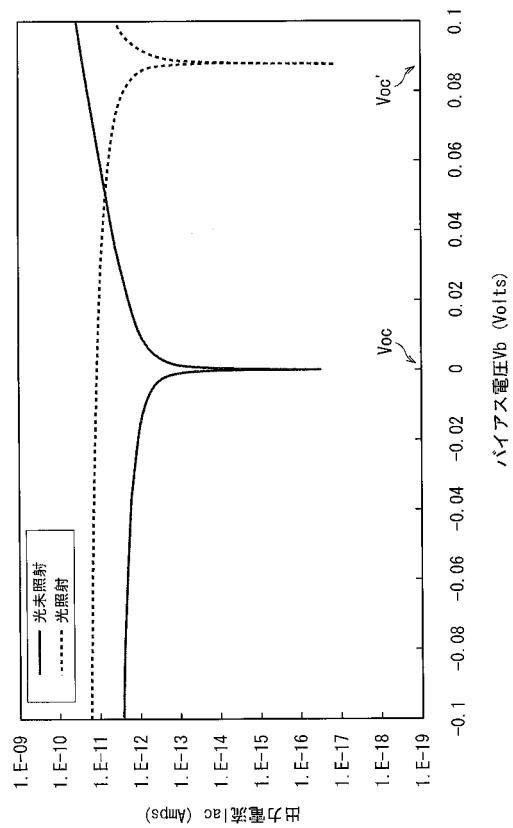

図 11 に、1つの PIN フォトダイオードの出力電流  $I_{ac}$  とバイアス電圧  $V_b$  との関係を示す曲線を、光未照射の場合（実線）と光照射の場合（点線）とのそれについて示す。これらの曲線は、図 9 の曲線 c1・c2 のバイアス電圧  $V_b = 0$  V の付近を拡大したものに相当する。図 11 に  $V_{oc}'$  で示すように、光未照射の場合の開放電圧  $V_{oc}$  はほぼ 0 V であり、光照射の場合は、未照射の場合よりも正側にシフトする。

#### 【0013】

従って、光検出用素子 201 に開放電圧  $V_{oc}$  が印加された状態で出力電流を引き出せば、このバイアス状態での暗電流はほとんどゼロに近い非常に小さな値であるので、光電流のみによる積分結果が得られ、出力電圧  $V_o$  の SN 比が非常に良好になる。また、微弱光から強度の大きい光まで検出可能であるので、検出のダイナミックレンジが広い。30

#### 【0014】

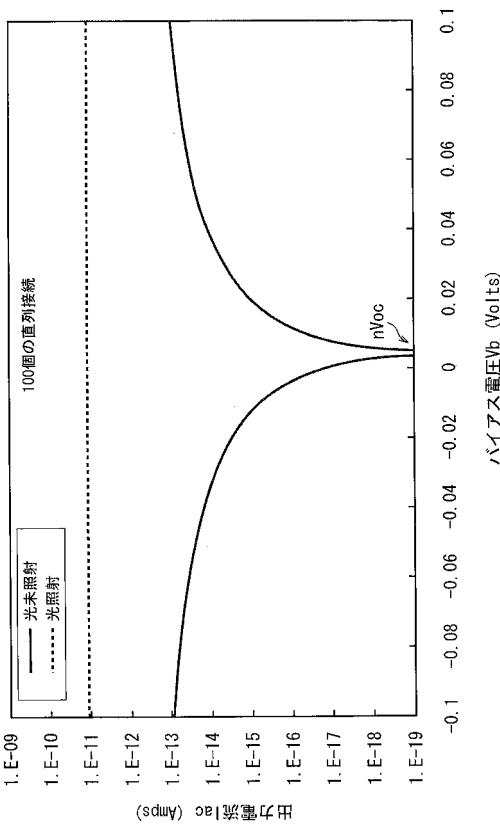

そして、さらに、n 個の PIN フォトダイオードの直列接続により構成することにより、図 12 に示すように、光未照射の場合の直列接続全体の開放電圧は、1 個の場合の開放電圧  $V_{oc}$  を n 倍した  $nV_{oc}$  になる。図 12 では表されていないが、光照射の場合の直列接続全体の開放電圧も 1 個の場合の開放電圧  $V_{oc}'$  の n 倍になる。図 12 では  $n = 100$  の場合が示されている。この場合には、出力電流  $I_{ac}$  とバイアス電圧  $V_b$  との関係を示す曲線が水平方向に引き伸ばされた状態となるので、開放電圧  $nV_{oc}$  付近の出力電流  $I_{ac}$  の変化が緩やかであり、出力電流  $I_{ac}$  が小さい値となるバイアス電圧  $V_b$  の範囲が広がる。従って、この直列接続の構成を図 10 のように適用することにより、参照用素子 202 に開放電圧  $nV_{oc}$  が現れ、光検出用素子 201 にこの開放電圧  $nV_{oc}$  に等しいバイアス電圧  $V_b$  が印加される。この開放電圧  $nV_{oc}$  は、図 13 に示すように  $n = 7$  で約 0.1 V であり、光検出用素子 201 にはこの 0.1 V のバイアス電圧に対応した電流が流れる。40

#### 【0015】

このようにすると、PIN フォトダイオードおよび演算増幅器 205 などに特性ばらつきがあることによって、図 12 から分かるように光照射状態での曲線が当該バイアス電圧付近では十分に平坦であるので、光検出用素子 201 の出力電流はほとんど変化しない。また、当該バイアス電圧付近では光検出素子 201 の暗電流の変化がほとんどなく、小さ50

いため、出力電圧V<sub>o</sub>のS/N比は非常に良好な状態に保たれる。図10では、このような、光検出用素子201側と参照用素子202側との状態の誤差をeとして非反転入力に含ませてある。PINフォトダイオードの直列接続構成を用いれば、誤差eがあっても、これを吸収して正確な周囲光ALの強度の検出が可能になる。なお、PINフォトダイオードの直列接続構成を複数並列に接続した構成も可能であり、光検出用素子202から得ようとする出力電流に応じて並列数が設定される。

#### 【0016】

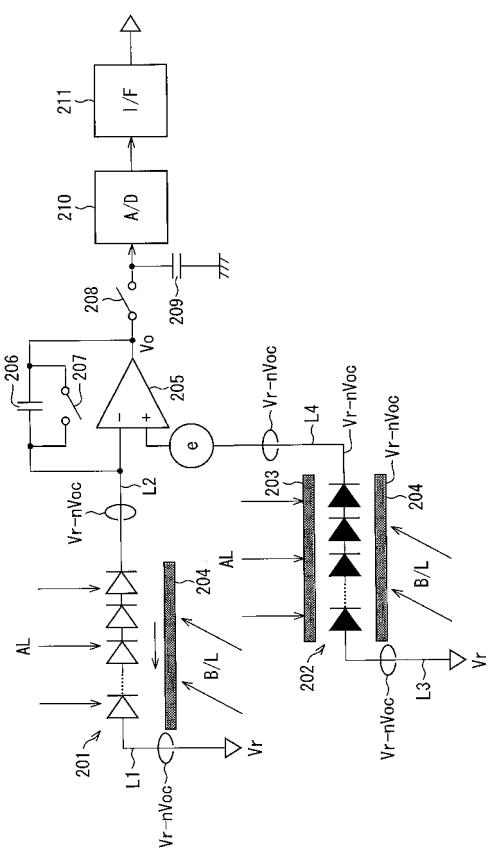

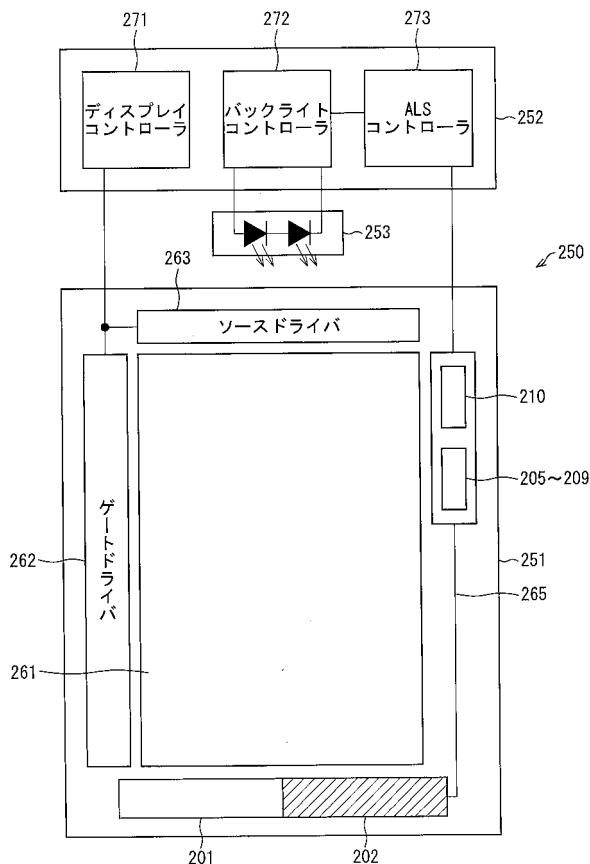

次に、図14に、このような構成の周囲光センサを備えた液晶表示装置250の構成例を示す。

#### 【0017】

液晶表示装置250は、例えば携帯電話の表示装置であり、表示パネル251、コントロール基板252、および、バックライト253を備えている。

#### 【0018】

表示パネル251は、マトリクス表示部261、ゲートドライバ262、ソースドライバ263、および、図10で説明した周囲光センサを備えている。マトリクス表示部261は縦長画面であって、ゲートドライバ262は縦方向の額縁領域の一方に配置されており、ソースドライバ263は横方向の額縁領域の一方に配置されている。ゲートドライバ262およびソースドライバ263としては、IC実装、COG実装、表示パネル251へのモノリシックによる作り込みなど種々の実現形態が可能である。この他に、ゲートドライバ262およびソースドライバ263を、フレキシブルプリント基板などの外部基板上に実装して、表示パネル251と接続する形態も可能である。

#### 【0019】

また、横方向の額縁領域の他方には、周囲光センサの検出用素子201と参照用素子202とが横方向に隣接して配置されている。検出用素子201および参照用素子202は表示パネル251に配置されている。また、縦方向の額縁領域の他方には、周囲光センサの演算増幅器205、積分コンデンサ206、スイッチ207・208、ホールドコンデンサ209、および、A/D変換器210が、ソースドライバ263に近接するように設けられているが、これらはソースドライバ263と同じ横方向の額縁領域に設けられている場合もある。これらはCOGを含めたディスクリート素子やICの実装や、表示パネル251へのモノリシックによる作り込みが可能であるが、ドライバと同様に外部基板上に実装する方法も可能である。

#### 【0020】

コントロール基板252は、ディスプレイコントローラ271、バックライトコントローラ272、および、ALSコントローラ273を備えている。ディスプレイコントローラ271は、表示パネル251のゲートドライバ262およびソースドライバ263の動作を制御する。バックライト253はLEDや冷陰極管などで構成される。バックライトコントローラ272は、バックライト253の点灯駆動を制御する。ALSコントローラ273は、表示パネル251の周囲光センサから送られた周囲光の検出強度に基づいて、バックライトコントローラ272にバックライト253の輝度を調節する制御信号を出力する。例えばバックライト253がLEDである場合には、LEDに流す電流や、LEDの点灯個数を変える。また、バックライト253が冷陰極管である場合には、冷陰極管の点灯本数を変える。なお、周囲光センサのインターフェース211は、A/D変換器210に併設して設けられていてもよいし、ALSコントローラ273側に設けられていてもよく、デジタルデータを伝送するバスの敷設範囲に応じて適宜決められる。

#### 【0021】

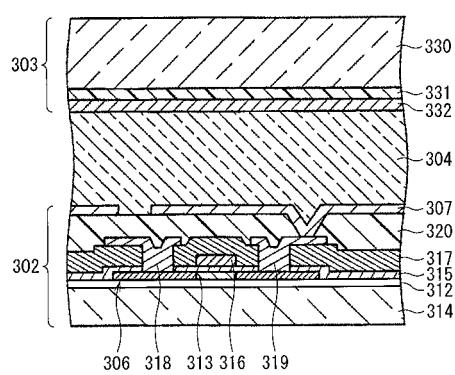

図15に、マトリクス表示部261の断面構成を示す。

#### 【0022】

マトリクス表示部261は、アクティブマトリクス基板302、対向基板303、および、アクティブマトリクス基板302と対向基板303とに挟持された表示媒体（液晶）304を備えている。

10

20

30

40

50

## 【0023】

アクティブマトリクス基板302は、ガラス基板314上に、ベースコート312、TFT306、層間絶縁膜320、および、画素電極307を備えている。TFT306は、ベースコート312上に、多結晶シリコン膜313、ゲート絶縁膜315（酸化シリコン膜、窒化シリコン膜など）、ゲート電極316（Al、Mo、Ti、W、それらの合金など）、層間絶縁膜317（酸化シリコン膜、窒化シリコン膜など）、ソース電極318（Al、Mo、Ti、W、それらの合金など）、および、ドレイン電極319（Al、Mo、Ti、W、それらの合金など）が順次、積層およびパターン形成された構成となっている。

## 【0024】

10

多結晶シリコン膜313は、チャネル領域と、その両側に不純物が高濃度にドープされた $n^+$ 層からなるソース領域およびドレイン領域とからなる。ソース電極318およびドレイン電極319は、ゲート絶縁膜315および層間絶縁膜317に設けられたコンタクトホールを介して層間絶縁膜317上に引き出されている。層間絶縁膜320（アクリル、ポリイミド、BCB(Benzo-Cyclo-Butene)、といった感光性を有する有機絶縁膜など）はTFT306を覆うように形成されている。画素電極307（ITO(Indium-Tin-Oxide)、IZO(Indium-Zinc-Oxide)など）は層間絶縁膜320上に形成されており、層間絶縁膜320に設けられたコンタクトホールを介してドレイン電極319に接続されている。また、この他に補助容量なども設けられる。

## 【0025】

20

対向基板303は、ガラス基板330上に、カラーフィルタ331および対向電極332を順次積層されるように有する構成である。この他にブラックマトリクスなども適宜設けられる。

## 【0026】

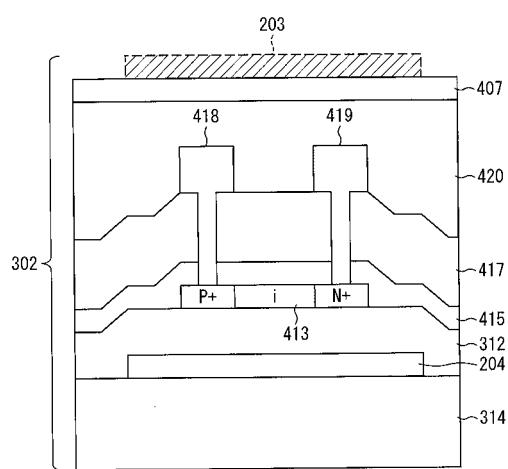

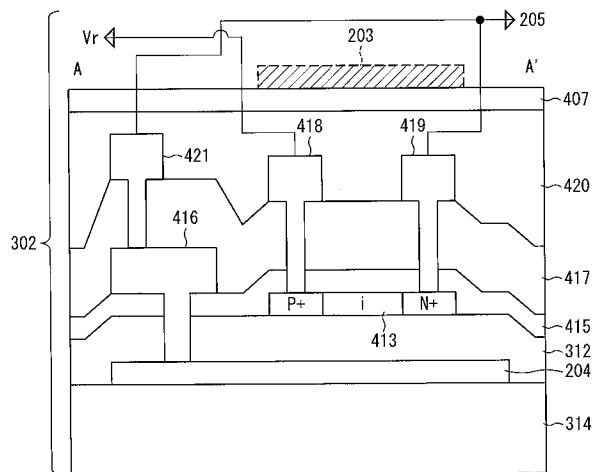

図16に、周囲光センサの検出用素子201および参照用素子202に用いられるPINフォトダイオードの構成を示す。

## 【0027】

この構成はアクティブマトリクス基板302上に形成されており、ガラス基板314上に、光シールド204、ベースコート312、PINフォトダイオード413、絶縁膜415、層間絶縁膜417、アノード電極418、カソード電極419、層間絶縁膜420、および、シールド（電界に対するシールド）407が順次積層およびパターン形成されたものである。参照用素子202の場合には、さらに、光シールド203をシールド407上に備えていてもよい。

## 【0028】

光シールド204は、PINフォトダイオード413に対して表示パネルの背面側に設けられており、アニール工程、活性化工程を考慮して、高融点の金属であるMo、Wなどが適しているが、ゲート電極やソース電極およびドレイン電極と同じ金属材料といった、透過率の低い状態に形成された導電体膜で形成可能である。PINフォトダイオード413は多結晶シリコン膜からなるラテラル構造のフォトダイオードであり、中央の1層領域の両側に、高濃度にドープされた $p^+$ 層領域および $n^+$ 層領域を備えている。この多結晶シリコン膜は、TFT306の多結晶シリコン膜313と同じ層から形成可能である。

## 【0029】

絶縁膜415は酸化シリコン膜や窒化シリコン膜からなり、TFT306のゲート絶縁膜315と同じ層を使用することが可能である。層間絶縁膜417は酸化シリコン膜や窒化シリコン膜からなり、TFT306の層間絶縁膜417と同じ層を使用することが可能である。アノード電極418およびカソード電極419は層間絶縁膜417上から、層間絶縁膜417および絶縁膜415に形成されたコンタクトホールを介して、順に、PINフォトダイオード413の $p^+$ 層領域、 $n^+$ 層領域にコンタクトしている。層間絶縁膜420は有機絶縁膜などからなり、マトリクス表示部261の層間絶縁膜320と同じ層を使用することが可能である。

## 【0030】

シールド407は導電体膜からなり、マトリクス表示部261の画素電極307と同じ層を使用することが可能である。シールド407は一定電位の電源に接続されており、対向電極332の電位変動駆動による電界の影響がPINフォトダイオード413に及ぶのを防止する。光シールド203は、検出用素子201のPINフォトダイオード413...へ液晶表示装置250の筐体の窓を通して照射される周囲光ALが、参照用素子202のPINフォトダイオード413...へ反射・拡散によって届くのを防止する遮光膜であり、透過率の低い状態に形成された導電体膜で形成可能である。または、対向基板側にプラックマトリクスでも形成可能である。

## 【0031】

10

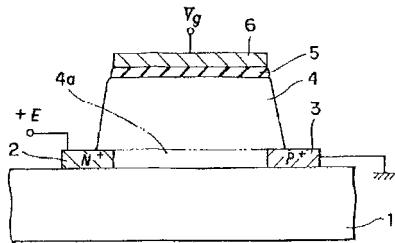

図19に、特許文献1に記載された光センサ用ダイオードの断面構成を示す。

## 【0032】

ガラス基板101上にシリコン膜102が形成されており、シリコン膜102上に多結晶シリコンによる半導体層110が形成されている。半導体層110は、p領域111とi領域112とn領域113とが順に隣接配置された構成である。シリコン膜102上には酸化シリコン膜103が形成されており、酸化シリコン膜103上にゲート電極114が形成されている。また、ゲート電極114が形成された酸化シリコン膜103上に酸化シリコン膜104が形成されている。酸化シリコン膜104上には、p領域111に対応する位置にアノード電極115、n領域に対応する位置にカソード電極116がそれぞれ形成されている。アノード電極115、カソード電極116は、酸化シリコン膜103・104に空けられたコンタクトホールを介してp領域111、n領域113にそれぞれ接触している。カソード電極116は接地されている。アノード電極115およびカソード電極116が形成された酸化シリコン膜104上には窒化シリコン膜105が形成されている。

20

## 【0033】

上記図19の構成は、ゲート電極114にゲート電圧を供給することにより、光センサ用ダイオードの電流電圧特性をえるものである。このゲート電圧は、光センサ用ダイオードに光を照射しない場合と光を照射した場合とで電流電圧特性が異なることを補償し、適切なゲート電圧を設定すれば、光を照射した場合に発生するリーク電流を抑制することができる。従って、受光部への光照射経路外であって受光分に対する遮光とも関係のない位置に設けられたゲート電極114からは、光センサ用ダイオードの内部に、絶縁膜103を介した静電容量を用いて電界作用が及ぶようになっている。

30

## 【0034】

図20に、特許文献2に記載されたフォトセンサの断面構成を示す。

## 【0035】

このフォトセンサは、絶縁基板1上に、N<sup>+</sup>型半導体領域2、P<sup>+</sup>型半導体領域3、および、N<sup>+</sup>型半導体領域2とP<sup>+</sup>型半導体領域3との間の部分上に形成されたI型半導体領域4を備えている。半導体領域4上には絶縁層5が形成されており、絶縁層5上には分光特性制御用の制御電極6が形成されている。N<sup>+</sup>型半導体領域2には正の電位(+E)が与えられ、P<sup>+</sup>型半導体領域3は接地される。分光特性制御用の制御電極6には分光特性制御用電圧Vgが印加される。

40

## 【0036】

制御電極6に分光特性制御用電圧Vgを印加することにより、フォトセンサの内部に及ぶ電界の作用が変化するため、これによってフォトセンサ内部のポテンシャル分布をえて分光特性を変化させる。特許文献2の技術も、受光部への光照射経路外であって受光分に対する遮光とも関係のない位置に設けられた制御電極6によって、I型半導体領域4を用いた静電容量を介した電界の作用を利用するものである。

## 【0037】

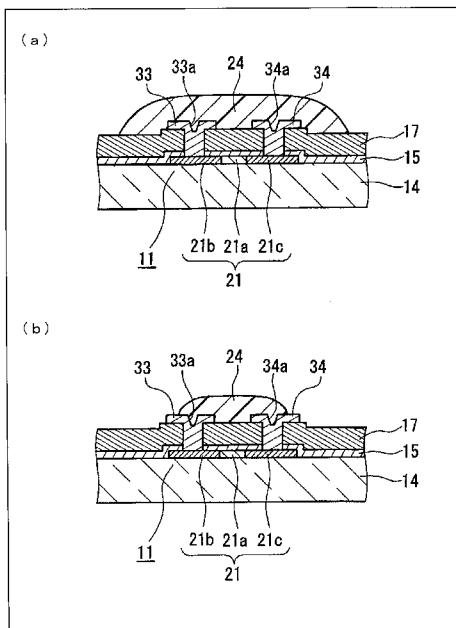

図21の(a)・(b)に、特許文献3に記載された光センサの断面構成を示す。

## 【0038】

50

この光センサ 11 は、TFT が形成されている基板と共に基板であるガラス基板 14 上に多結晶 Si 膜 21 による PIN ダイオードが形成されたものである。PIN 接合は、p<sup>+</sup> 層である領域 21b と、n<sup>+</sup> 層である領域 21c と、i 層である領域 21a とによって形成されている。さらに、多結晶 Si 膜 21 を覆うように、ゲート絶縁膜 15 と第 1 層間絶縁膜 17 とが形成されている。また、第 1 層間絶縁膜 17 上には、第 1 層間絶縁膜 17 およびゲート絶縁膜 15 を貫通するコンタクトホールを介して、多結晶 Si 21 の p<sup>+</sup> 領域 21b に電気的に接続された p 側電極 33 と、上記コンタクトホールを介して n<sup>+</sup> 領域 21c に電気的に接続された n 側電極 34 とが形成されている。

#### 【0039】

そして、図 21 の (a) では、光センサ 11 の上層、すなわち p 側電極 33 および n 側電極 34 とそれらの近傍の第 1 層間絶縁膜 17 の表面とを覆うように、保護膜 24 が設けられている。保護膜 24 は、光センサ 11 が受光する波長域に対する透明性と、紫外線に対する耐性とを有しており、フッ素系樹脂、シリコーン樹脂、エポキシ樹脂、アクリル樹脂などの材料が使用可能である。また、図 21 の (b) では、保護膜 24 は、光センサ 11 に対して光が入射する位置を少なくとも覆うように形成されている。

#### 【0040】

このように、特許文献 3 には、光センサの電極上に、センサの特性劣化を防止する絶縁性保護膜を形成する技術が開示されている。

#### 【0041】

以上の構成の液晶表示装置 250 においては、以下のような問題点が生じる。

10

#### 【0042】

(1) 図 16 の構成の検出用素子 201 および参照用素子 202 では、シールド 407 が設けられているため、表示面側から発生されるノイズに対してはシールドされているが、対向電極 332 の電位やデータ信号電位の変動など、液晶表示装置 250 の動作に関わるものとして発生する電界が、検出用素子 201 および参照用素子 202 の周囲から回り込んで、ガラス基板 314 側からも PIN フォトダイオード 413 に到達して誘導ノイズを発生させる。また、バックライトから発生されるノイズ（電磁波、輻射、うなり音など）も、ガラス基板 314 側から PIN フォトダイオード 413 に到達する誘導ノイズ源として挙げられる。さらに PIN フォトダイオード 413 の背面側に形成される光シールド 204 の電位がフローティングになっていると、PIN フォトダイオード 413 の出力電流が安定しない原因となる。

20

30

#### 【0043】

これらの誘導ノイズはコモンモードノイズとして配線 L2・L4 を介して演算増幅器 205 に伝達される。しかし、配線 L2・L4 を含む配線 265 は、基板間配線とは異なり、薄膜プロセスで製造される上に、図 14 に示すように表示パネル 251 の額縁領域を通る長い経路として形成されているために抵抗値が大きい。また、周辺との寄生容量も存在する。すなわち、図 10 に記載した回路素子以外の寄生素子が存在し、これらのインピーダンスが周波数によって異なるため、前記電位変動が基本波成分とその高調波成分とからなることを考慮すると、コモンモードノイズを各周波数に対して減衰させるための平衡回路の条件を設定することが難しい。また、IC チップなどと比較すると相当大きな面積の基板上にフォトリソグラフィプロセスで製造されるために、パターン寸法や膜質の面内ばらつきや製造ロットばらつきも加わって、平衡回路の条件設定がさらに困難となる。さらに、演算増幅器 205 の同相信号除去比 CMRR が高周波成分に対して低くなることを、コモンモードノイズ除去において考慮する必要があり、対策が複雑になる。

40

#### 【0044】

この結果、周囲光センサが備える演算増幅器 205 の出力電圧 V<sub>o</sub> は、図 17 に示す曲線 c4 のように、主としてコモンモードノイズによる振動誤差を受けながら変化することにより、積分がリニアに行えず、積分時間の終了時に、誤差を含んだ点 P2 の電圧をホールドしてしまう。A/D 変換器 210 が内部に備える比較器が、ある量子化レベルを判別するのに例えば 80 mV の閾値を有しているとすると、点 P1 のホールド電圧と点 P2 の

50

ホールド電圧とでは量子化結果が相違する。この結果、周囲光 A L の強度の検出誤差が発生する。このように、PIN フォトダイオード 413...に誘導ノイズが発生した場合には、周囲光 A L の強度を正確に検出することができないという問題がある。

#### 【0045】

(2) 配線 265についても、PIN フォトダイオード 413...と同じようにマトリクス表示部 261 の画素電極 307 と同じ層を用いた電界に対するシールドを施したとしても、ガラス基板 314 側からの誘導ノイズが生じた場合には、周囲光 A L の強度を正確に検出することができないという問題がある。

#### 【0046】

(3) 図 16 に示すように、検出用素子 201 および参照用素子 202 の各 PIN フォトダイオード 413 には光シールド 204 が設けられているが、光シールド 204 によってバックライト光 B / L の遮光を完全に行なうことは困難であり、いくらかの迷光が PIN フォトダイオード 413 に届いてしまう。図 14 に示す検出用素子 201 と参照用素子 202 との配置は、表示パネル 251 の縦中心線に対して対称であるので、上記迷光は検出用素子 201 と参照用素子 202 とに等しく届きやすいが、PIN フォトダイオード 413...の特性に面内ばらつきや製造ロットばらつきが存在するため、等しい迷光が届いても、検出用素子 201 と参照用素子 202 とでバイアス条件が揃いにくい。

10

#### 【0047】

図 10 の構成では、検出用素子 201 および参照用素子 202 を PIN フォトダイオード 413 の直列接続とすることにより、ある程度の PIN フォトダイオードの製造ばらつきを吸収することができるが、直列接続数や並列接続数を増やすことにより PIN フォトダイオードの数が増えると、その分、PIN フォトダイオードの占有面積が増加して特性ばらつきが大きくなる。従って、PIN フォトダイオードの特性ばらつきが非常に大きいときには、直列接続を増加させることによっても特性ばらつきを十分吸収しきれず、図 17 の直線 c5 に示すように演算增幅器 205 の出力電圧 V<sub>o</sub> が直線 c3 からはずれて点 P<sub>3</sub> の電圧でホールドされてしまい、周囲光 A L の強度の正確な検出が困難になるという問題がある。

20

#### 【0048】

本発明は、上記(2)の問題点に鑑みてなされたものであり、その目的は、周囲光センサに用いられる光電変換素子の出力を伝達する配線への誘導ノイズをさらに低減することができる表示装置を実現することにある。

30

#### 【0049】

本発明の表示装置は、上記課題を解決するために、表示パネルに配置された光電変換素子を用いて表示面側の周囲光の強度を光電変換して検出する周囲光センサを備え、前記周囲光センサによって検出された周囲光の強度に応じて前記表示面での表示の輝度を調節する表示装置であって、前記光電変換素子の出力を伝達する配線に対して前記表示パネルの背面側に、電界に対するシールドとしての第 1 シールド電極を備えていることを特徴としている。

#### 【0050】

上記の発明によれば、光電変換素子の出力を伝達する配線に対して表示パネルの背面側に、電界に対するシールドとしての第 1 シールド電極を備えているので、光電変換素子の出力を伝達する配線に表示パネルの背面側からノイズが誘導されることを防止することができる。

40

#### 【0051】

以上により、周囲光センサに用いられる光電変換素子の出力を伝達する配線への誘導ノイズをさらに低減することのできる表示装置を実現することができるという効果を奏する。

#### 【0052】

本発明の表示装置は、上記課題を解決するために、前記配線の両側方に、電界に対するシールドとしての第 2 シールド電極を備えていることを特徴としている。

50

**【 0 0 5 3 】**

上記の発明によれば、第2シールド電極が電界に対するシールドとして加わるので、配線への誘導ノイズをさらに低減することができるという効果を奏する。

**【 0 0 5 4 】**

本発明の表示装置は、上記課題を解決するために、前記配線に対して前記表示面側に、電界に対するシールドとしての第3シールド電極を備えていることを特徴としている。

**【 0 0 5 5 】**

上記の発明によれば、第3シールド電極が電界に対するシールドとして加わるので、配線への誘導ノイズをさらに低減することができるという効果を奏する。

**【 0 0 5 6 】**

本発明の表示装置は、上記課題を解決するために、前記配線の両側方に設けられるとともに、前記第1シールド電極に接続された第2シールド電極と、前記配線に対して前記表示面側に設けられるとともに、前記第2シールド電極に接続された第3シールド電極とを備えていることを特徴としている。

**【 0 0 5 7 】**

上記の発明によれば、第2シールド電極および第3シールド電極が電界に対するシールドとして第1シールド電極に接続された状態で加わるので、配線の周囲が電界に対するシールドで囲まれた状態に近くなり、あるいは囲まれた状態になり、配線への誘導ノイズを特に大きく低減することができるという効果を奏する。

**【 0 0 5 8 】**

本発明の表示装置は、上記課題を解決するために、前記周囲光センサにおいて、前記光電変換素子の2つの電流出力端子のうちの一方の前記電流出力端子は基準電位の電源に接続されており、前記第1シールド電極に、他方の前記電流出力端子の電位と同じ電位が与えられることを特徴としている。

**【 0 0 5 9 】**

上記の発明によれば、光電変換素子の一方の電流出力端子が基準電位の電源に接続されているので、他方の電流出力端子が光電変換素子の出力に応じて上記基準電位を基準にした電位を取るときに、第1シールド電極と同じ電位となることにより、第1シールド電極と他方の電流出力端子に接続されている配線との間の寄生容量を介した電位変動を受けずに済む。従って、光電変換素子の他方の電流出力端子に接続されている配線の電位が安定するという効果を奏する。

**【 0 0 6 0 】**

本発明の表示装置は、上記課題を解決するために、前記周囲光センサは、前記光電変換素子として、周囲光が照射される第1光電変換素子と、基準の明るさの環境下に置かれた、前記第1光電変換素子と同じ構成の第2光電変換素子とを備えており、前記第1光電変換素子に、前記第2光電変換素子が発生する開放電圧がバイアス電圧として印加され、前記第1光電変換素子の出力電流から、周囲光の強度を検出することを特徴としている。

**【 0 0 6 1 】**

上記の発明によれば、第2光電変換素子に発生する開放電圧、および、第1光電変換素子に印加される上記開放電圧に等しいバイアス電圧を、第1シールド電極を他方の電流出力端子と同じ電位とすることが、周囲光の強度の検出を精度よく行うことによく寄与するという効果を奏する。

**【 0 0 6 2 】**

本発明の表示装置は、上記課題を解決するために、前記光電変換素子は、少なくとも、複数の同じ光電変換素子エレメントが直列に接続された構成であることを特徴としている。

**【 0 0 6 3 】**

上記の発明によれば、第2光電変換素子に発生する開放電圧を個々の光電変換素子エレメントの開放電圧の和とすることで、第1光電変換素子の出力電流の検出に誤差が生じにくくなるため、第1シールド電極を他方の電流出力端子と同じ電位とすることにより開放

10

20

30

40

50

電圧を安定して第1光電変換素子に印加することが、周囲光の強度の検出を精度よく行うことによく寄与するという効果を奏する。

【0064】

本発明の表示装置は、上記課題を解決するために、前記光電変換素子は、同じ光電変換素子エレメントが1つ以上の同じ数だけ直列接続された直列回路が複数並列に接続された構成であることを特徴としている。

【0065】

上記の発明によれば、光電変換素子エレメントの直列回路が複数並列に接続されているので、光電変換素子の単位照射光量当たりの出力電流が大きくなり、周囲光の強度の検出精度が高まるという効果を奏する。

10

【0066】

本発明の表示装置は、上記課題を解決するために、前記光電変換素子は、PINフォトダイオードからなる光電変換素子エレメントを1つ以上組み合わせた構成であることを特徴としている。

【0067】

上記の発明によれば、表示パネルにモリシックに形成しやすいPINフォトダイオードを用いた周囲光センサに対して、PINフォトダイオードへの誘導ノイズを低減することができるという効果を奏する。

【0068】

本発明の表示装置は、上記課題を解決するために、前記PINフォトダイオードはラテラルPINフォトダイオードであることを特徴としている。

20

【0069】

上記の発明によれば、表示パネルへのモリシック形成に特にプロセスが適しているラテラルPINフォトダイオードを用いた周囲光センサに対して、ラテラルPINフォトダイオードへの誘導ノイズを低減することができるという効果を奏する。

【0070】

本発明の表示装置は、上記課題を解決するために、前記光電変換素子は、フォトトランジスタからなる光電変換素子エレメントを1つ以上組み合わせた構成であることを特徴としている。

【0071】

上記の発明によれば、フォトトランジスタを用いた周囲光センサに対して、フォトトランジスタへの誘導ノイズを低減することができるという効果を奏する。

30

【0072】

本発明の表示装置は、上記課題を解決するために、前記表示パネルはTFT液晶パネルであり、前記配線は、TFT基板の額縁領域にTFTのソース電極と同じ層を用いて形成されており、前記第1シールド電極は、前記額縁領域にTFTのゲート電極と同じ層を用いて形成されていることを特徴としている。

【0073】

上記の発明によれば、配線および第1シールド電極をTFT液晶パネルのプロセスを用いて容易に製造することができるという効果を奏する。

40

【0074】

本発明の表示装置は、上記課題を解決するために、前記表示パネルはTFT液晶パネルであり、前記配線および前記第2シールド電極は、TFT基板の額縁領域にTFTのソース電極と同じ層を用いて形成されていることを特徴としている。

【0075】

上記の発明によれば、配線および第2シールド電極をTFT液晶パネルのプロセスを用いて容易に製造することができるという効果を奏する。

【0076】

本発明の表示装置は、上記課題を解決するために、前記表示パネルはTFT液晶パネルであり、前記配線は、TFT基板の額縁領域にTFTのソース電極と同じ層を用いて形成

50

されており、前記第3シールド電極は、前記額縁領域に画素電極と同じ層を用いて形成されていることを特徴としている。

【0077】

上記の発明によれば、配線および第3シールド電極をTFT液晶パネルのプロセスを用いて容易に製造することができるという効果を奏する。

【0078】

本発明の表示装置は、上記課題を解決するために、前記表示パネルはTFT液晶パネルであり、前記配線は、TFT基板の額縁領域にTFTのソース電極と同じ層を用いて形成されており、前記第1シールド電極は、前記額縁領域にTFTのゲート電極と同じ層を用いて形成されており、前記第2シールド電極は、前記額縁領域にTFTのソース電極と同じ層を用いて形成されており、前記第3シールド電極は、前記額縁領域に画素電極と同じ層を用いて形成されていることを特徴としている。10

【0079】

上記の発明によれば、配線および第1～第3シールド電極をTFT液晶パネルのプロセスを用いて容易に製造することができるという効果を奏する。

【0080】

本発明の表示装置は、上記課題を解決するために、前記表示パネルは、前記画素電極上に直接積層された、反射型表示用の反射電極を備えており、前記第3シールド電極上に、前記反射電極と同じ層を用いて形成された第4シールド電極が設けられていることを特徴としている。20

【0081】

上記の発明によれば、第3シールド電極と第4シールド電極とが積層されてシールド電極としてのシート抵抗が小さくなるため、反射電極の層という既存の層を用いて電界に対するシールド効果を高めることができるという効果を奏する。

【0082】

本発明の表示装置は、上記課題を解決するために、前記周囲光センサによって検出された前記周囲光の強度に応じて、バックライト光源の輝度を調節することにより、前記表示面での表示の輝度を調節することを特徴としている。

【0083】

上記の発明によれば、周囲光の強度に応じてバックライト光源の輝度を調節する表示装置において、光電変換素子への誘導ノイズを低減することができるという効果を奏する。30

【0084】

本発明の他の目的、特徴、および優れた点は、以下に示す記載によって十分分かるであろう。また、本発明の利点は、添付図面を参照した次の説明によって明白になるであろう。

【図面の簡単な説明】

【0085】

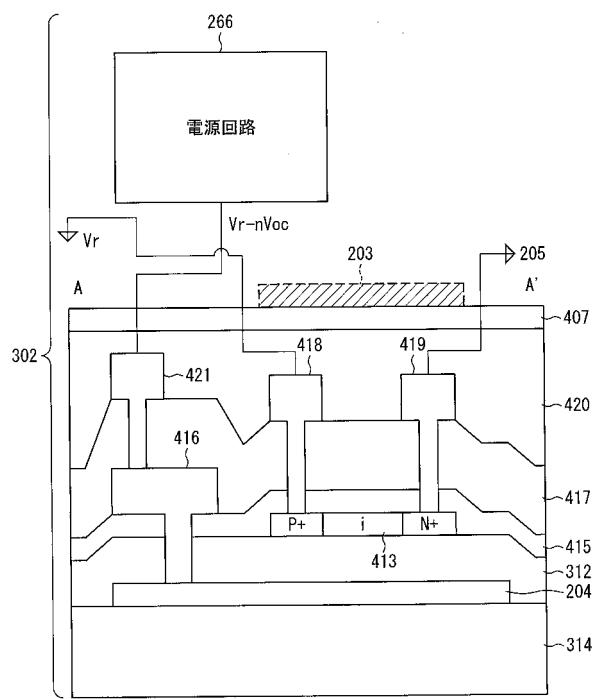

【図1】本発明の実施形態を示すものであり、表示装置に備えられる周囲光センサのPINフォトダイオードおよびその周辺の構成を示す断面図である。

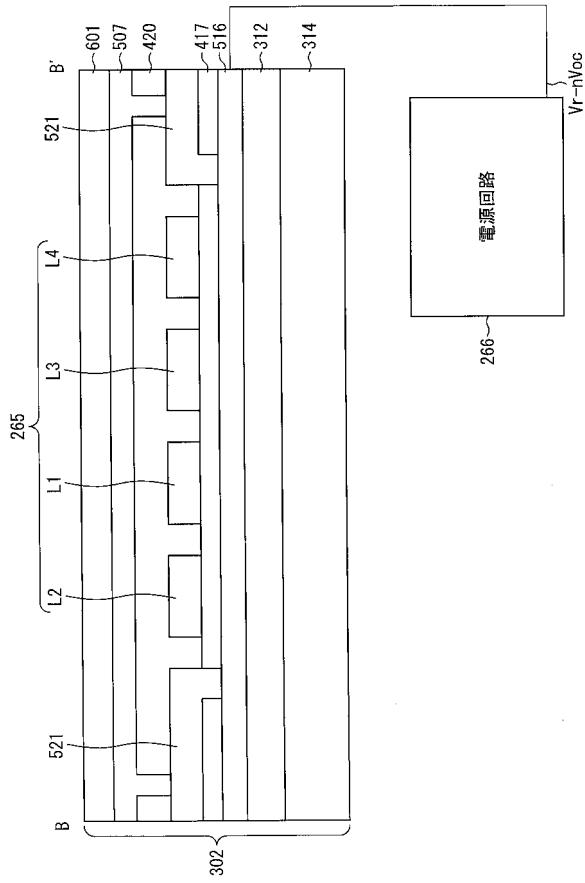

【図2】周囲光センサの配線およびその周辺の構成を示す断面図である。40

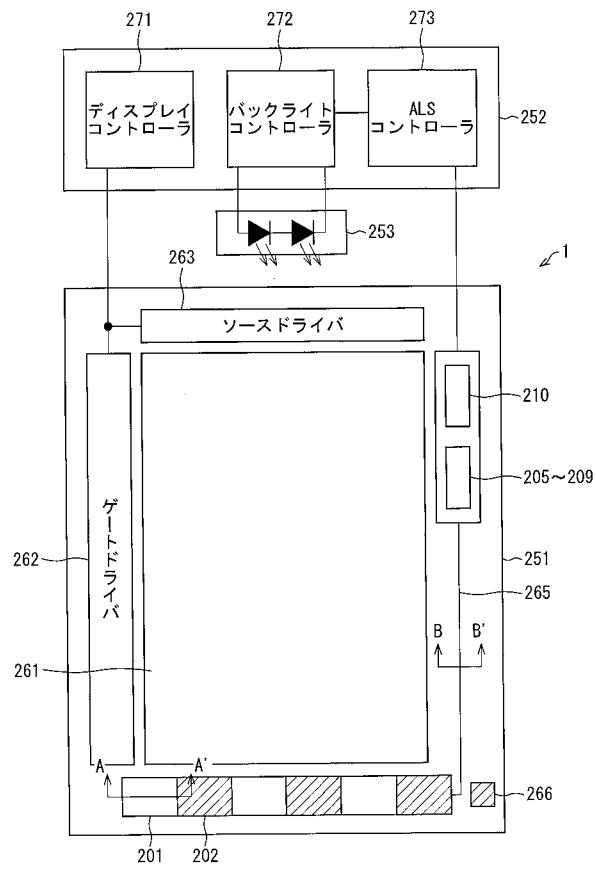

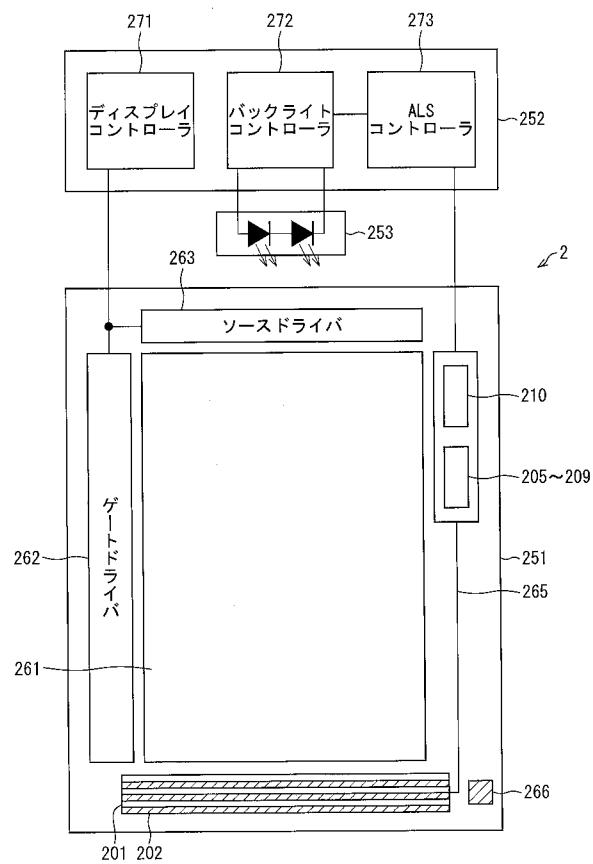

【図3】本発明の実施形態を示すものであり、表示装置の第1の構成を示すブロック図である。

【図4】周囲光センサの構成を示す回路ブロック図である。

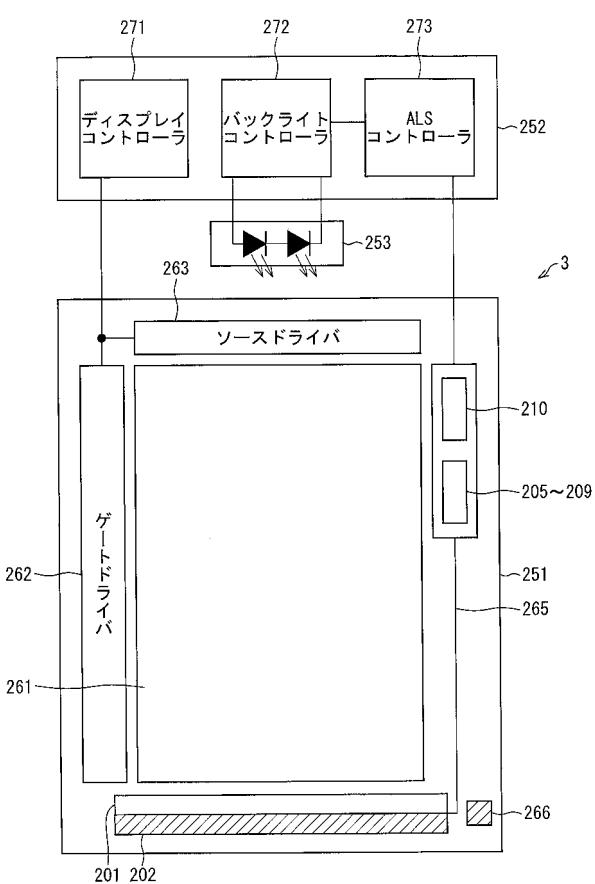

【図5】本発明の実施形態を示すものであり、表示装置の第2の構成を示すブロック図である。

【図6】本発明の実施形態における比較例を示すものであり、表示装置の第3の構成を示すブロック図である。

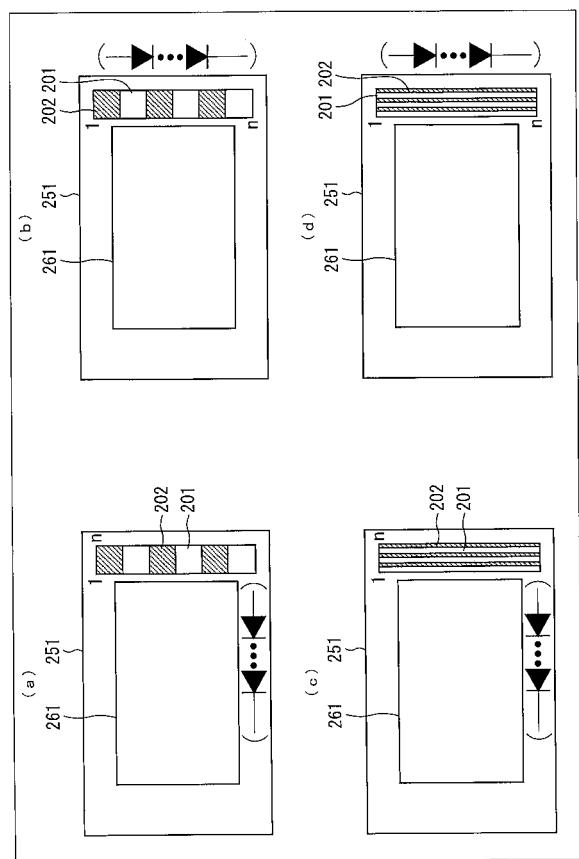

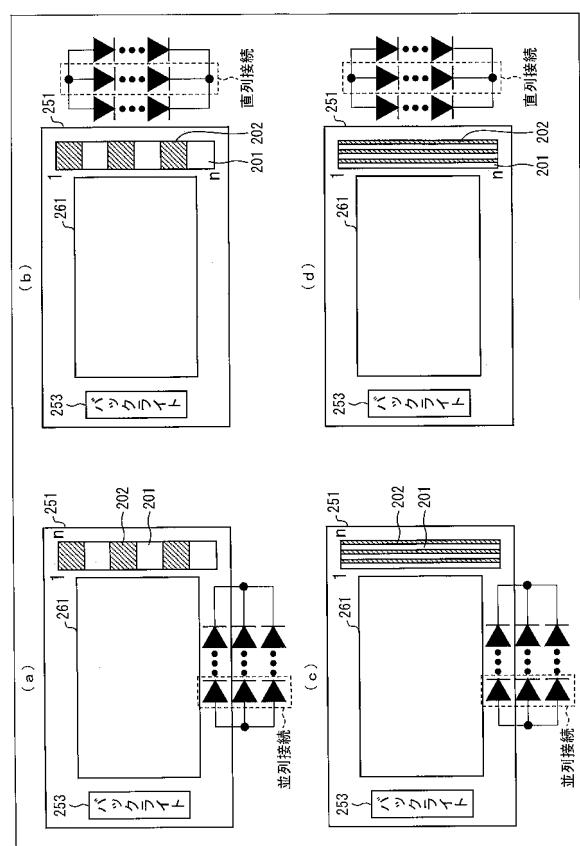

【図7】周囲光センサの配置とPINフォトダイオードの向きとの組み合わせ例を示す平面図であり、(a)ないし(d)のそれぞれは異なる組み合わせを示している。

【図8】従来技術を示すものであり、周囲光センサの第1の構成を示す回路図である。50

【図9】1つのPINフォトダイオードの出力電流とバイアス電圧との関係を示す第1のグラフである。

【図10】従来技術を示すものであり、周囲光センサの第2の構成を示す回路図である。

【図11】1つのPINフォトダイオードの出力電流とバイアス電圧との関係を示す第2のグラフである。

【図12】複数個のPINフォトダイオードが直列接続された構成の出力電流とバイアス電圧との関係を示す第1のグラフである。

【図13】複数個のPINフォトダイオードが直列接続された構成の出力電流とバイアス電圧との関係を示す第2のグラフである。

【図14】従来技術を示すものであり、表示装置の構成を示すプロック図である。 10

【図15】図14の表示装置に備えられるマトリクス表示部の構成を示す断面図である。

【図16】図14の表示装置に備えられる周囲光センサのPINフォトダイオードおよびその周辺の構成を示す断面図である。

【図17】図10の周囲光センサの出力電圧の時間変化を示すグラフである。

【図18】図1の周囲光センサの変形例の構成を示す断面図である。

【図19】従来技術を示すものであり、光センサ用ダイオードの構成を示す断面図である。

【図20】従来技術を示すものであり、フォトセンサの構成を示す断面図である。

【図21】従来技術を示すものであり、光センサの構成を示す断面図である。

【図22】周囲光センサの配置とPINフォトダイオードの向きとの組み合わせ例を詳細に示す平面図であり、(a)ないし(d)のそれぞれは異なる組み合わせを示している。 20

#### 【符号の説明】

##### 【0086】

|       |                          |

|-------|--------------------------|

| 1 ~ 3 | 表示装置                     |

| 201   | 検出用素子（光電変換素子、第1光電変換素子）   |

| 202   | 参照用素子（光電変換素子、第2光電変換素子）   |

| 204   | 光シールド                    |

| 266a  | 電源電圧発生素子（第3光電変換素子）       |

| 413   | PINフォトダイオード（光電変換素子エレメント） |

| 516   | 第1シールド電極（シールド電極）         |

| 521   | 第2シールド電極（シールド電極）         |

| 507   | 第3シールド電極（シールド電極）         |

| 601   | 第4シールド電極（シールド電極）         |

#### 【発明を実施するための最良の形態】

##### 【0087】

本発明の一実施形態について図1ないし図7および図22に基づいて説明すると以下の通りである。

##### 【0088】

図3に、本実施形態に係る液晶表示装置1の構成を示す。

##### 【0089】

液晶表示装置1は、図14の液晶表示装置250において、周囲光センサが備える検出用素子（第1光電変換素子）201および参照用素子（第2光電変換素子）202の構造および配置を変えるとともに、検出用素子201に接続されている配線および参照用素子202に接続されている配線からなる配線265の構造を変え、さらに、電源回路266を追加した構成である。マトリクス表示部261の画素構成は、図15と同様である。 40

##### 【0090】

図4に、上記液晶表示装置250の周囲光センサの構成を示す。

##### 【0091】

この周囲光センサは、図10の周囲光センサにおいて、まず、光シールド（迷光に対する光シールド）204を、導電体膜で形成するとともに基準電位V<sub>r-nVoc</sub>を出力す 50

る電源回路 266 に接続して、電界に対するシールドとしても機能させるようにした構成である。そして、さらに、検出用素子 201 のアノード端（電流出力端子）に接続されている基準電位  $V_{r-nVoc}$  の配線 L1、検出用素子 201 のカソード端（電流出力端子）に接続されている配線 L2、参照用素子 202 のアノード端（電流出力端子）に接続されている基準電位  $V_{r-nVoc}$  の配線 L3、および、参照用素子 202 のカソード端（電流出力端子）に接続されている配線 L4 からなる配線 265 全体の周囲に導電体膜を配置して、これを上記電源回路 266 に接続して電界に対するシールドとした構成である。

#### 【0092】

図 1 に、検出用素子 201 および参照用素子 202 の A-A' 線断面図を示す。

#### 【0093】

図 1 の構成は、図 16 の構成において、光シールド 204 を透過率の低い状態に形成された導電体膜で形成したものである。このような導電体膜としては、アニール工程、活性化工程を考慮して、高融点の金属である Mo、W などが適している。図 15 に示した TFT 306 のゲート電極 316 やソース電極 318 およびドレイン電極 319 などに用いられている材料と同じ材料の導電体膜も使用可能である。また、絶縁膜 415 上には、ベースコート 312 および絶縁膜 415 に形成されたコンタクトホールを介して光シールド 204 に接続された第 1 接続電極 416 が設けられている。この第 1 接続電極 416 は、TFT 306 のゲート電極 316 と同じ層からパターン形成可能である。さらに、層間絶縁膜 417 上には、層間絶縁膜 417 に形成されたコンタクトホールを介して第 1 接続電極 416 に接続された第 2 接続電極 421 が設けられている。第 2 接続電極 421 は、TFT 306 のソース電極 318 およびドレイン電極 319 と同じ層からパターン形成可能である。この第 2 接続電極 421 は、後述の電源回路 266 に接続されている。

#### 【0094】

また、アノード端となるアノード電極 418 は電位  $V_r$  の配線 L1 または L3 に接続されており、カソード端となるカソード電極 419 は演算増幅器 205 の入力端子に接続される配線 L2 または L4 に接続されている。

#### 【0095】

電源回路 266 は、例えば図 3 に示すように検出用素子 201 および参照用素子 202 の形成領域および配線 265 に近接して設けられている。電源回路 266 は、基準電位  $V_{r-nVoc}$  を生成して第 2 接続電極 421 に与える。

#### 【0096】

このように、光シールド 204 を所定の電位とすることにより、光シールド 204 を電界に対するシールドとしても機能させることができる。この場合に、PIN フォトダイオード 413 ... にガラス基板 314 側から、すなわち表示パネルの背面側から到達しようとする電界については光シールド 204 で電気力線を終端させることができる。また、光シールド 204 に、電界に対するシールドの機能を持たせたので、電磁シールドの効果もある程度は見込める。

#### 【0097】

また、光シールド 204 がフローティングとなって検出用素子 201 および参照用素子 202 のダイオード特性が不安定になることを防ぐことができる。

#### 【0098】

また、光シールド 204 の電位は必ずしも PIN フォトダイオード 413 のカソード電位と同じでなくてもよいが、上記のように同じ  $V_{r-nVoc}$  とすることにより、カソードと光シールド 204 との間の寄生容量が低減されるので、カソード電位が光シールド 204 から全く影響を受けなくすることができる。

#### 【0099】

また、上記のように電源回路 266 を設ける代わりに、図 18 に示すように、第 2 接続電極 421 を参照用素子 202 のカソード電極 419 に接続することにより、光シールド 204 に電位  $V_{r-nVoc}$  を与えるようにしてもよい。

#### 【0100】

10

20

30

40

50

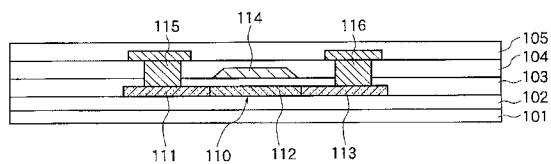

図2に、図3のB-B'線断面図を示す。

#### 【0101】

この断面構成は、ガラス基板314上に、ベースコート312、第1シールド電極516、層間絶縁膜417、配線265(L1・L2・L3・L4)、第2シールド電極521、層間絶縁膜420、および、第3シールド電極507が順次積層されてパターン形成されたものである。また、液晶表示装置250が反射型モードでの表示を行ふことができる構成である場合には、第4シールド電極601が設けられていてもよい。

#### 【0102】

第1シールド電極516は、少なくとも配線265の下方、すなわち配線265に対して表示パネルの背面側に位置する領域に設けられており、図15に示したTFT306のゲート電極316と同じ層から形成可能である。また、第1シールド電極516は、前述した電源回路266から基準電位V<sub>r-nVoc</sub>を与えられている。配線265および第2シールド電極521は、TFT306のソース電極318およびドレイン電極319と同じ層から形成可能である。配線265は両側を第2シールド電極521で挟まれるように配置されている。また、ここでは、配線265の中で、配線L2・L4を外側に配置し、配線L1を配線L2の内側隣に、配線L3を配線L4の内側隣に、それぞれ配置している。また、第2シールド電極521は、層間絶縁膜417に形成されたコンタクトホールを介して第1シールド電極516に接続されている。

#### 【0103】

第3シールド電極507は、少なくとも配線265の上方に位置する領域に設けられており、図15に示した画素電極307と同じ層から形成可能である。また、第3シールド電極507は、層間絶縁膜420に形成されたコンタクトホールを介して第2シールド電極521に接続されている。第4シールド電極601が設けられる場合には、第4シールド電極601は、極力広い面積で第3シールド電極507と接するように設けられ、第3シールド電極507上に反射電極と同じ層から形成可能である。

#### 【0104】

上記の構成とすることにより、配線265は、第1シールド電極516と第3シールド電極507(および第4シールド電極601)とによって上下を挟まれ、第2シールド電極521によって両側方を挟まれた状態となる。特に、第1シールド電極516が設けられることにより、配線265にガラス基板314側から到達しようとする電界による電気力線を第1シールド電極516で終端させることができる。これらのシールド電極は全て電源回路266によって電位V<sub>r-nVoc</sub>となっているので、シールド効果は大きく、電界による配線265への誘導ノイズはかなり低減される。さらに、第2シールド電極521を第1シールド電極516に接続するためのコンタクトホール、および、第3シールド電極507を第2シールド電極521に接続するためのコンタクトホールを、極力、配線265の側方にあるシールド間隙を埋めるように設ければ、配線265は周囲を全てシールド電極で囲まれた状態となり、シールド効果は非常に高まる。

#### 【0105】

シールド電極の電位を配線L2・L4の電位と等しくなるようにしたので、配線L2・L4とシールド電極との間に形成された寄生容量は低減される。

#### 【0106】

また、上記のように電源回路266を設ける代わりに、図18に示したのと同様に、第1シールド電極516～第4シールド電極601に、参照用素子202のカソード電極419から電位V<sub>r-nVoc</sub>を与えるようにしてもよい。

#### 【0107】

次に、液晶表示装置1における検出用素子201および参照用素子202の配置について説明する。

#### 【0108】

図3に示すように、液晶表示装置1では、検出用素子201が設けられている領域と、参照用素子202が設けられている領域とが、額縁に沿って交互に繰り返し並ぶように分

10

20

30

40

50

割配置されている。各領域において、PINフォトダイオード413...は所定数だけ直列接続および並列接続され、検出用素子201の全領域と、参照用素子202の全領域とのそれそれで、n個の直列接続および規定数の並列接続による構成とされる。この場合のnは1でもよいし、2以上でもよい。また、並列接続の数も1または複数でよい。これにより、PINフォトダイオード413の特性に大きな面内ばらつきが生じても、検出用素子201の全領域と検出用素子201の全領域とのそれぞれについて平均化された特性が検出用素子201および参照用素子202の特性となるために、検出用素子201の特性と参照用素子202の特性とをほぼ等しくすることができる。そして、検出用素子201の各領域間で、到達する迷光に差があり、また、参照用素子202の各領域間で、到達する迷光に差があっても、検出用素子201の全体と参照用素子202の全体とでは、迷光から受ける影響がほぼ等しくなるため、迷光の差による周囲光ALの検出誤差を、図14の場合よりも小さくすることができる。10

#### 【0109】

図5に、検出用素子201および参照用素子202の他の配置をとる液晶表示装置2の構成を示す。

#### 【0110】

液晶表示装置2では、検出用素子201が設けられている領域と、参照用素子202が設けられている領域とが、額縁に直交する方向に沿って交互に繰り返し並ぶように分割配置されている。この場合においても、各領域において、PINフォトダイオード413...は所定数だけ直列接続および並列接続され、検出用素子201の全領域と、参照用素子202の全領域とのそれそれで、n個の直列接続および規定数の並列接続による構成とされる。nは1でもよい。これによっても、検出用素子201の特性と参照用素子202の特性とをほぼ等しくすることができる。そして、同様に、迷光の差による周囲光ALの検出誤差を、図14の場合よりも小さくすることができる。20

#### 【0111】

図6に、比較例として、検出用素子201および参照用素子202のさらに他の配置をとる液晶表示装置3の構成を示す。

#### 【0112】

液晶表示装置3では、検出用素子201が設けられている領域と、参照用素子202が設けられている領域とが、1つずつ、額縁に直交する方向に沿って並ぶように配置されている。この場合には、額縁に沿う方向の長い距離に対しても検出用素子201の領域と参照用素子202の領域とが並行して設けられているために、図14の場合よりも検出用素子201の特性と参照用素子202の特性との差が縮小され、迷光の差による周囲光ALの検出誤差も縮小する。しかし、額縁に直交する方向には領域が分割されないので、図4および図5の構成の方が、これらの効果は大きい。30

#### 【0113】

図7の(a)および(b)に、図3の構成におけるPINフォトダイオード413...の形成および接続方向の例を示す。ここでは特にnが2以上である場合の利点を考慮しているがn=1も可能である。図7の(a)では、アノードとカソードとを結ぶ方向が額縁に直交する方向であり、n個の直列接続もこの方向に行われる。並列接続は、各領域および全領域で、額縁に沿う方向に、n個の直列接続を1つの並列枝路とする並列接続として行われる。図7の(b)では、アノードとカソードとを結ぶ方向が額縁に沿う方向であり、各領域での直列接続および全領域でのn個の直列接続もこの方向に行われる。並列接続は、各領域で額縫に直交する方向に、各直列接続を1つの並列枝路とする並列接続として行われる。40

#### 【0114】

図7の(c)および(d)に、図5の構成におけるPINフォトダイオード413...の形成および接続方向の例を示す。図7の(c)では、アノードとカソードとを結ぶ方向が額縫に直交する方向であり、各領域での直列接続および全領域でのn個の直列接続もこの方向に行われる。並列接続は、各領域で額縫に沿う方向に、各直列接続を1つの並列枝路50

とする並列接続として行われる。図 7 の ( d ) では、アノードとカソードとを結ぶ方向が額縁に沿う方向であり、n 個の直列接続もこの方向に行われる。並列接続は、各領域および全領域で額縁に直交する方向に、各直列接続を 1 つの並列枝路とする並列接続として行われる。

#### 【 0 1 1 5 】

特に、図 7 の ( b ) では、参照用素子 202 の各領域において、PIN フォトダイオード 413 … の各直列接続のアノード端とカソード端とで到達する迷光がほぼ等しく、また PIN フォトダイオード 413 の特性はほぼ揃っているため、各 PIN フォトダイオード 413 での発生キャリア数が揃い、個々の開放電圧  $V_{oc}$  が揃う。従って、図 7 の ( b ) の構成は、この点で、図 7 の ( a ) ・ ( c ) ・ ( d ) の構成よりも好ましい。10

#### 【 0 1 1 6 】

なお、図 7 の ( a ) ~ ( d ) で、直列接続の方向と並列接続の方向とが上記のように定められていれば、PIN フォトダイオード 413 … の個々のアノードとカソードとを結ぶ方向は、上述したものと直交する方向など、他の任意の方向でもよい。

#### 【 0 1 1 7 】

また、図 1 および図 2 で説明した電源電圧発生素子 266a についても、形成領域を参照用素子 202 と同じ位置に分割配置すれば、参照用素子 202 と電源電圧発生素子 266a とで開放電圧  $nV_{oc}$  がほぼ同じになる。

#### 【 0 1 1 8 】

また、レーザアニール方向はチャネル方向と同じになるほうが電流が流れやすい。従って、図 7 の ( a ) ・ ( b ) ・ ( c ) ・ ( d ) においてレーザアニール方向が額縁に沿う方向である場合には、チャネル方向が額縁に沿っている図 7 の ( b ) ・ ( d ) の構成のほうが、チャネル方向が額縁に直交する図 7 の ( a ) ・ ( c ) の構成よりも好ましい。逆に、レーザアニール方向が額縁に直交する場合には、図 7 の ( a ) ・ ( c ) の構成のほうが、チャネル方向が額縁に直交する図 7 の ( b ) ・ ( d ) の構成よりも好ましい。20

#### 【 0 1 1 9 】

図 7 をさらに詳細に記載した図を図 22 に示す。図 22 の ( a ) ・ ( b ) では PIN フォトダイオード 413 が、横方向に直列接続、縦方向に並列接続されている。図 22 の ( c ) ・ ( d ) では、PIN フォトダイオード 413 が、縦方向に直列接続、横方向に並列接続されている。30

#### 【 0 1 2 0 】

図 22 の ( a ) ・ ( b ) ・ ( c ) ・ ( d ) において、検出用素子 201 が設けられている領域、および、参照用素子 202 が設けられている領域の、バックライト 253 からの離間方向が、表示パネル 251 のパネル面への投影において額縁に直交する方向である場合には、図 22 の ( a ) ・ ( b ) では、検出用素子 201 が設けられている領域に到達する迷光と、参照用素子 202 が設けられている領域に到達する迷光とが、全体で互いに等しいので、検出用素子 201 と参照用素子 202 とで開放電圧  $nV_{oc}$  が互いに等しい。特に、図 22 の ( b ) では、検出用素子 201 と参照用素子 202 とのそれぞれについて、直列接続された箇所のそれぞれにおける初段から最終段までの各 PIN フォトダイオード 413 のバックライト 253 からの距離が互いに等しい。この場合には、直列接続された箇所のそれぞれにおける初段から最終段までの各 PIN フォトダイオード 413 に、バックライト 253 からの迷光が等しく届くので、各 PIN フォトダイオード 413 の開放電圧  $V_{oc}$  を揃えることができる。40

#### 【 0 1 2 1 】

さらに図 22 の ( c ) ・ ( d ) でも、検出用素子 201 が設けられている領域に到達する迷光と、参照用素子 202 が設けられている領域に到達する迷光とが、全体で互いに等しいので、検出用素子 201 と参照用素子 202 とで開放電圧  $nV_{oc}$  が互いに等しい。特に図 22 の ( d ) では、検出用素子 201 と参照用素子 202 とのそれぞれについて、並列接続された箇所のそれぞれにおける初段から最終段までの各 PIN フォトダイオード 413 のバックライト 253 からの距離が互いに等しい。この場合には、並列接続された

箇所のそれぞれにおける初段から最終段までの各PINフォトダイオード413のアノード端またはカソード端に、バックライト253からの迷光が等しく届くので、並列接続されるPINフォトダイオード413どうしのアノード端とカソード端とに迷光が等しく届くことになる。検出用素子201と参照用素子202との各領域において、PINフォトダイオード413の特性はほぼ揃っているため、各PINフォトダイオード413での発生キャリア数が揃い、個々の開放電圧 $V_{oc}$ が揃う。

#### 【0122】

従って、(b) > (a)、(d) > (c)の順に好ましい構成となる。

#### 【0123】

逆に、図22の(a)・(b)・(c)・(d)において、検出用素子201が設けられている領域、および、参照用素子202が設けられている領域の、バックライト253からの離間方向が、表示パネル251のパネル面への投影において額縁に沿う方向である場合には、図22の(c)・(d)では、検出用素子201が設けられている領域に到達する迷光と、参照用素子202が設けられている領域に到達する迷光とが、全体で互いに等しいので、検出用素子201と参照用素子202との間で開放電圧 $nV_{oc}$ がほぼ同じになる。

10

#### 【0124】

さらに図22の(a)・(b)でも、検出用素子201が設けられている領域に到達する迷光と、参照用素子202が設けられている領域に到達する迷光とが、全体で互いに等しいので、検出用素子201と参照用素子202とで開放電圧 $nV_{oc}$ が互いに等しい。

特に図22(a)では、検出用素子201と参照用素子202とのそれについて、並列接続された箇所のそれにおける初段から最終段までの各PINフォトダイオード413のバックライト253からの距離が互いに等しい。この場合には、並列接続された箇所のそれにおける初段から最終段までの各PINフォトダイオード413のアノード端とカソード端とに、バックライト253からの迷光が等しく届くので、並列接続されるPINフォトダイオード413どうしのアノード端とカソード端とに迷光が等しく届くことになる。検出用素子201と参照用素子202との各領域において、PINフォトダイオード413の特性はほぼ揃っているため、各PINフォトダイオード413での発生キャリア数が揃い、個々の開放電圧 $V_{oc}$ が揃う。従って、(c) > (a)、(d) > (b)の順に好ましい構成となる。

20

#### 【0125】

以上、本実施形態について説明した。

#### 【0126】

なお、本実施形態では、周囲光センサの構成の一例として図4の構成を挙げたが、PINフォトダイオード413のアノードとカソードとの位置を入れ替えても同様の検出が行えることは自明である。また、この場合にカソード端を基準電位としてのGNDに接続するなど、配線L1・L3の電位を適宜選択することができることはもちろんある。演算増幅器を用いた積分演算なども、積分とともに出力電圧 $V_o$ を減少させる方向に変化させたり、後段にさらに反転増幅器・非反転増幅器などの増幅器や、加算回路・減算回路などを接続したりするなど、構成は自由に設計することができる。

30

40

#### 【0127】

また、本実施形態では、検出用素子201および参照用素子202を表示パネルにモノリシックに形成したが、これに限らず、COGの形態などで表示パネルに配置してもよい。そして、この場合に、光シールド203・204を検出用素子201および参照用素子202のチップ上やチップ内部に形成するようにしてよい。

#### 【0128】

また、光電変換素子エレメントとして、PINフォトダイオードの他に、フォトトランジスタなども使用可能である。

#### 【0129】

また、図1の光シールド204を、図8の周囲光センサの光シールド103などを初め

50

とする、一般的の参照用PINフォトダイオードの光シールドに適用することも可能である。従って、周囲光を、積分せずに、電流増幅を行ったり、電流 - 電圧変換したりすることにより検出するなど、検出方法も任意である。

#### 【0130】

また、表示装置としては液晶表示装置に限らず、周囲光センサを用いて表示の明るさを調節することのできるものであれば任意でよく、例えばEL表示装置やプラズマディスプレイなどに適用可能である。また、携帯電話やPDAなどの携帯端末に限らず、小型から大型まであらゆるサイズの表示パネルを備えた表示装置が可能である。

1. なお、表示装置としては以下のようなものも可能である。

(1)

10

表示パネルに配置された光電変換素子を用いて表示面側の周囲光の強度を光電変換して検出する周囲光センサを備え、前記周囲光センサによって検出された周囲光の強度に応じて前記表示面での表示の輝度を調節する表示装置であって、前記光電変換素子に対して前記表示パネルの背面側に、導電体からなる、迷光に対する光シールドを備え、前記迷光に対する光シールドに所定の電位が与えられることを特徴とする表示装置。

#### 【0131】

上記の発明によれば、光電変換素子に対して表示パネルの背面側に備えられた、導電体からなる、迷光に対する光シールドに、所定の電位を与えるので、迷光に対する光シールドは電界に対するシールドとしても機能する。従って、光電変換素子に表示パネルの背面側からノイズが誘導されることを防止することができる。また、光シールドがフローティングとなって光電変換素子の特性、例えばダイオード特性が不安定になることを防ぐことができる。

20

#### 【0132】

以上により、周囲光センサに用いられる光電変換素子への誘導ノイズをさらに低減することのできる表示装置を実現することができるという効果を奏する。

#### 【0133】

また、上記電界に対するシールドを迷光に対する光シールドが兼ねるので、電界に対するシールドを設けるための追加部材の数を抑制することができるという効果を奏する。

(2)

30

前記周囲光センサにおいて、前記光電変換素子の2つの電流出力端子のうちの一方の前記電流出力端子は基準電位の電源に接続されており、前記所定の電位は、他方の前記電流出力端子の電位と同じに設定されていることを特徴とする表示装置。

#### 【0134】

上記の発明によれば、光電変換素子の一方の電流出力端子が基準電位の電源に接続されているので、他方の電流出力端子が光電変換素子の出力に応じて上記基準電位を基準にした電位を取るときに、迷光に対する光シールドと同じ電位となることにより、迷光に対する光シールドと他方の電流出力端子との間の寄生容量を介した電位変動を受けずに済む。従って、光電変換素子の他方の電流出力端子の電位が安定するという効果を奏する。

(3)

40

前記周囲光センサは、前記光電変換素子として、周囲光が照射される第1光電変換素子と、基準の明るさの環境下に置かれた、前記第1光電変換素子と同じ構成の第2光電変換素子とを備えており、前記第1光電変換素子に、前記第2光電変換素子が発生する開放電圧がバイアス電圧として印加され、前記第1光電変換素子の出力電流から、周囲光の強度を検出することを特徴とする表示装置。

#### 【0135】

上記の発明によれば、第2光電変換素子に発生する開放電圧、および、第1光電変換素子に印加される上記開放電圧に等しいバイアス電圧を、迷光に対する光シールドを他方の電流出力端子と同じ電位とすることが、周囲光の強度の検出を精度よく行うことに大きく寄与するという効果を奏する。

(4)

50

前記光電変換素子は、少なくとも、複数の同じ光電変換素子エレメントが直列に接続された構成であることを特徴とする表示装置。

【0136】

上記の発明によれば、第2光電変換素子に発生する開放電圧を個々の光電変換素子エレメントの開放電圧の和とすることで、第1光電変換素子の出力電流の検出に誤差が生じにくくなるため、迷光に対する光シールドを他方の電流出力端子と同じ電位とすることにより開放電圧を安定して第1光電変換素子に印加することが、周囲光の強度の検出を精度よく行うことに大きく寄与するという効果を奏する。

(5)

前記光電変換素子は、同じ光電変換素子エレメントが1つ以上の同じ数だけ直列接続された直列回路が複数並列に接続された構成であることを特徴とする表示装置。 10

【0137】

上記の発明によれば、光電変換素子エレメントの直列回路が複数並列に接続されているので、光電変換素子の単位照射光量当たりの出力電流が大きくなり、周囲光の強度の検出精度が高まるという効果を奏する。

(6)

前記光電変換素子は、PINフォトダイオードからなる光電変換素子エレメントを1つ以上組み合わせた構成であることを特徴とする表示装置。

【0138】

上記の発明によれば、表示パネルにモノリシックに形成しやすいPINフォトダイオードを用いた周囲光センサに対して、PINフォトダイオードへの誘導ノイズを低減することができるという効果を奏する。 20

(7)

前記PINフォトダイオードはラテラルPINフォトダイオードであることを特徴とする表示装置。

【0139】

上記の発明によれば、表示パネルへのモノリシック形成に特にプロセスが適しているラテラルPINフォトダイオードを用いた周囲光センサに対して、ラテラルPINフォトダイオードへの誘導ノイズを低減することができるという効果を奏する。

(8)

前記光電変換素子は、フォトトランジスタからなる光電変換素子エレメントを1つ以上組み合わせた構成であることを特徴とする表示装置。 30

【0140】

上記の発明によれば、フォトトランジスタを用いた周囲光センサに対して、フォトトランジスタへの誘導ノイズを低減することができるという効果を奏する。

(9)

前記表示パネルはTFT液晶パネルであり、前記光電変換素子はTFT基板の額縁領域に、TFTの活性層と同じ層を用いて形成されていることを特徴とする表示装置。

【0141】

上記の発明によれば、光電変換素子をTFT液晶パネルのプロセスを用いて容易に製造することができるという効果を奏する。 40

(10)

前記迷光に対する光シールドは、前記額縁領域にTFTのゲート電極の層よりも積層方向下方に形成されており、前記迷光に対する光シールドに接続されているとともに、前記額縁領域に前記ゲート電極と同じ層から形成された第1接続電極と、前記第1接続電極に接続されているとともに、前記額縁領域にTFTのソース電極と同じ層から形成された第2接続電極とを備えており、前記第2接続電極は、前記所定の電位を与える電源に接続されていることを特徴とする表示装置。

【0142】

上記の発明によれば、迷光に対する光シールドに所定の電位を与えるための配線を、T 50

TFT 液晶パネルのプロセスを用いて容易に製造することができるという効果を奏する。

(11)

前記光電変換素子に対して、前記表示パネルの表示面側に、電界に対するシールドを備えていることを特徴とする表示装置。

【0143】

上記の発明によれば、光電変換素子に対して、表示パネルの表示面側にも電界に対するシールドを備えることにより光電変換素子への誘導ノイズを非常に小さくすることができるという効果を奏する。

(12)

前記光電変換素子に対して、前記表示パネルの表示面側に、画素電極と同じ層から形成した電界に対するシールドを備えていることを特徴とする表示装置。 10

【0144】

上記の発明によれば、光電変換素子に対して、表示パネルの表示面側に備えられる電界に対するシールドを、TFT 液晶パネルのプロセスを用いて容易に製造することができるという効果を奏する。

(13)

前記周囲光センサによって検出された前記周囲光の強度に応じて、バックライト光源の輝度を調節することにより、前記表示面での表示の輝度を調節することを特徴とする表示装置。 20

【0145】

上記の発明によれば、周囲光の強度に応じてバックライト光源の輝度を調節する表示装置において、光電変換素子への誘導ノイズを低減することができるという効果を奏する。

(14)

前記所定の電位は、他方の前記電流出力端子から与えられることを特徴とする表示装置。

。

【0146】

上記の発明によれば、迷光に対する光シールドに、容易に所定の電位を与えることができるという効果を奏する。

2. また、表示装置として、さらに以下のようなものが可能である。

(1)

表示パネルに配置された光電変換素子を用いて表示面側の周囲光の強度を光電変換して検出する周囲光センサを備え、前記周囲光センサによって検出された周囲光の強度に応じて前記表示面での表示の輝度を調節する表示装置であって、前記周囲光センサは、前記光電変換素子として、周囲光が照射される第1光電変換素子と、基準の明るさの環境下に置かれた、前記第1光電変換素子と同じ構成の第2光電変換素子とを備えているとともに、前記第2光電変換素子の出力を基準に用いて前記第1光電変換素子の出力から前記周囲光の強度を検出し、前記第1光電変換素子と前記第2光電変換素子とのそれぞれの形成領域が、前記表示パネル面内で交互に繰り返して並ぶように分割配置されていることを特徴とする表示装置。 30

【0147】

上記の発明によれば、第1光電変換素子と前記第2光電変換素子とのそれぞれの形成領域が、表示パネル面内で交互に繰り返して並ぶように分割配置されているので、光電変換素子を構成する光電変換素子エレメントの特性に大きな面内ばらつきが生じていても、第1光電変換素子の全領域と第2光電変換素子の全領域とのそれぞれについて平均化された特性が第1光電変換素子および第2光電変換素子の特性となるために、第1光電変換素子の特性と第2光電変換素子の特性とをほぼ等しくすることができる。そして、第1光電変換素子の各領域間で、到達する迷光に差があり、また、第2光電変換素子の各領域間で、到達する迷光に差があっても、第1光電変換素子の全体と第2光電変換素子の全体とでは、迷光から受ける影響がほぼ等しくなるため、迷光の差による周囲光の検出誤差を小さくすることができる。 40

50

**【 0 1 4 8 】**

以上により、光電変換素子を構成する光電変換素子エレメントの表示パネル上における特性ばらつきが大きくても、周囲光の強度を正確に検出することのできる表示装置を実現することができるという効果を奏する。

( 2 )

前記第1光電変換素子と前記第2光電変換素子とのそれぞれの形成領域が、前記表示パネルの額縁領域で額縁に沿って交互に繰り返して並ぶように分割配置されていることを特徴とする表示装置。

**【 0 1 4 9 】**

上記の発明によれば、光電変換素子エレメントの特性を平均化する第1光電変換素子および第2光電変換素子の配置を容易に実現することができるという効果を奏する。 10

( 3 )

前記第1光電変換素子と前記第2光電変換素子とのそれぞれの形成領域が、前記表示パネルの額縁領域で額縁に直交する方向に沿って交互に繰り返して並ぶように分割配置されていることを特徴とする表示装置。

**【 0 1 5 0 】**

上記の発明によれば、光電変換素子エレメントの特性を平均化する第1光電変換素子および第2光電変換素子の配置を容易に実現することができるという効果を奏する。

( 4 )

前記第1光電変換素子と前記第2光電変換素子とのそれぞれの形成領域において、額縁に直交する方向は、複数の同じ光電変換素子エレメントが直列に接続された1つの直列回路からなり、前記第1光電変換素子の各形成領域間と前記第2光電変換素子の各形成領域間とのそれぞれで、前記直列回路が並列に接続されていることを特徴とする表示装置。 20

**【 0 1 5 1 】**

上記の発明によれば、光電変換素子エレメントの特性を平均化する第1光電変換素子および第2光電変換素子の配置を容易に実現することができるという効果を奏する。

( 5 )

前記第1光電変換素子と前記第2光電変換素子とのそれぞれの形成領域において、額縁に直交する方向は、複数の同じ光電変換素子エレメントが直列に接続された複数の直列回路からなるとともに、額縁に沿う方向は、前記複数の直列回路が互いに並列に接続された並列回路からなり、前記第1光電変換素子の各形成領域間と前記第2光電変換素子の各形成領域間とのそれぞれで、前記並列回路が互いに並列に接続されていることを特徴とする表示装置。 30

**【 0 1 5 2 】**

上記の発明によれば、光電変換素子エレメントの特性を平均化する第1光電変換素子および第2光電変換素子の配置を容易に実現することができるという効果を奏する。

( 6 )

前記第1光電変換素子と前記第2光電変換素子とのそれぞれの形成領域において、額縁に沿う方向は、複数の同じ光電変換素子エレメントが直列に接続された1つの直列回路からなり、前記第1光電変換素子の各形成領域間と前記第2光電変換素子の各形成領域間とのそれぞれで、前記直列回路どうしが直列に接続されていることを特徴とする表示装置。 40

**【 0 1 5 3 】**

上記の発明によれば、光電変換素子エレメントの特性を平均化する第1光電変換素子および第2光電変換素子の配置を容易に実現することができるという効果を奏する。

( 7 )

前記第1光電変換素子と前記第2光電変換素子とのそれぞれの形成領域において、額縁に沿う方向は、複数の同じ光電変換素子エレメントが直列に接続された複数の直列回路からなるとともに、額縁に直交する方向は、前記複数の直列回路が互いに並列に接続された並列回路からなり、前記第1光電変換素子の各形成領域間と前記第2光電変換素子の各形成領域間とのそれぞれで、前記並列回路どうしが直列に接続されていることを特徴とする 50

表示装置。

【0154】

上記の発明によれば、光電変換素子エレメントの特性を平均化する第1光電変換素子および第2光電変換素子の配置を容易に実現することができるという効果を奏する。

(8)

前記第1光電変換素子と前記第2光電変換素子とのそれぞれの形成領域において、額縁に沿う方向は、複数の同じ光電変換素子エレメントが並列に接続された1つの並列回路からなり、前記第1光電変換素子の各形成領域間と前記第2光電変換素子の各形成領域間とのそれぞれで、前記並列回路が直列に接続されていることを特徴とする表示装置。

【0155】

10

上記の発明によれば、光電変換素子エレメントの特性を平均化する第1光電変換素子および第2光電変換素子の配置を容易に実現することができるという効果を奏する。

(9)

前記第1光電変換素子と前記第2光電変換素子とのそれぞれの形成領域において、額縁に直交する方向は、複数の同じ光電変換素子エレメントが直列に接続された複数の直列回路からなるとともに、額縁に沿う方向は、前記複数の直列回路が互いに並列に接続された並列回路からなり、前記第1光電変換素子の各形成領域間と前記第2光電変換素子の各形成領域間とのそれぞれで、前記並列回路が互いに直列に接続されていることを特徴とする表示装置。

【0156】

20

上記の発明によれば、光電変換素子エレメントの特性を平均化する第1光電変換素子および第2光電変換素子の配置を容易に実現することができるという効果を奏する。

(10)

前記第1光電変換素子と前記第2光電変換素子とのそれぞれの形成領域において、額縁に沿う方向に、複数の同じ光電変換素子エレメントが直列に接続された1つの直列回路からなり、前記第1光電変換素子の各形成領域間と前記第2光電変換素子の各形成領域間とのそれぞれで、前記直列回路どうしが並列に接続されていることを特徴とする表示装置。

【0157】

上記の発明によれば、光電変換素子エレメントの特性を平均化する第1光電変換素子および第2光電変換素子の配置を容易に実現することができるという効果を奏する。

30

(11)

前記第1光電変換素子と前記第2光電変換素子とのそれぞれの形成領域において、額縁に沿う方向は、複数の同じ光電変換素子エレメントが直列に接続された複数の直列回路からなるとともに、額縁に直交する方向は、前記複数の直列回路が互いに並列に接続された並列回路からなり、前記第1光電変換素子の各形成領域間と前記第2光電変換素子の各形成領域間とのそれぞれで、前記並列回路どうしが並列に接続されていることを特徴とする表示装置。

【0158】

上記の発明によれば、光電変換素子エレメントの特性を平均化する第1光電変換素子および第2光電変換素子の配置を容易に実現することができるという効果を奏する。

40

(12)

前記周囲光センサは、前記第1光電変換素子に、前記第2光電変換素子が発生する開放電圧がバイアス電圧として印加され、前記第1光電変換素子の出力電流から周囲光の強度を検出することにより、前記第2光電変換素子の出力を基準に用いて前記第1光電変換素子の出力から前記周囲光の強度を検出することを特徴とする表示装置。

【0159】

上記の発明によれば、第2光電変換素子が発生する開放電圧は微弱であって、この開放電圧が第1光電変換素子にバイアス電圧として印加されて出力電流に影響を与えるので、第1光電変換素子および第2光電変換素子の特性を平均化する事が、周囲光の正確な検出に大きく寄与するという効果を奏する。

50

( 1 3 )

前記第1光電変換素子と前記第2光電変換素子とが形成された前記表示パネルの額縁辺において、レーザアニール方向が前記表示パネルの額縁に沿う方向に設定されていることを特徴とする表示装置。

【 0 1 6 0 】

上記の発明によれば、レーザアニール方向が前記表示パネルの額縁に沿う方向に設定されているので、第1光電変換素子と前記第2光電変換素子とのそれぞれのチャネル方向に、額縁に沿う方向が含まれている場合に、その部分の第1光電変換素子と第2光電変換素子とに電流が流れやすくなるという効果を奏する。

( 1 4 )

10

前記第1光電変換素子と前記第2光電変換素子とが形成された前記表示パネルの額縁辺において、レーザアニール方向が前記表示パネルの額縁に直交する方向に設定されていることを特徴とする表示装置。

【 0 1 6 1 】

上記の発明によれば、レーザアニール方向が前記表示パネルの額縁に直交する方向に設定されているので、第1光電変換素子と前記第2光電変換素子とのそれぞれのチャネル方向に、額縁に直交する方向が含まれている場合に、その部分の第1光電変換素子と第2光電変換素子とに電流が流れやすくなるという効果を奏する。

( 1 5 )

前記第1光電変換素子と前記第2光電変換素子とのそれぞれのチャネル方向が、レーザアニール方向と平行になるように、前記第1光電変換素子と前記第2光電変換素子とが前記表示パネルの額縁辺に配置されていることを特徴とする表示装置。

20

【 0 1 6 2 】

上記の発明によれば、第1光電変換素子と第2光電変換素子とのそれぞれのチャネル方向がレーザアニール方向と平行であるので、第1光電変換素子と第2光電変換素子とに電流が流れやすくなるという効果を奏する。

( 1 6 )

前記第1光電変換素子の各形成領域と前記第2光電変換素子の各形成領域との間で、それぞれのバックライトからの平均距離が互いに等しいことを特徴とする表示装置。

【 0 1 6 3 】

30

上記の発明によれば、バックライトからの迷光が第1光電変換素子と第2光電変換素子とに等しく届くので、それぞれの開放電圧を容易に等しくすることができるという効果を奏する。

( 1 7 )

前記第1光電変換素子に複数の光電変換素子エレメントが直列接続された箇所と、前記第2光電変換素子に前記第1光電変換素子の前記光電変換素子エレメントと同数の前記光電変換素子エレメントが直列接続された箇所とが、それぞれ形成されており、前記第1光電変換素子と前記第2光電変換素子とのそれぞれについて、前記直列接続された箇所のそれぞれにおける初段から最終段までの各前記光電変換素子エレメントのバックライトからの距離が互いに等しいことを特徴とする表示装置。

40

【 0 1 6 4 】

上記の発明によれば、直列接続された箇所のそれぞれにおける初段から最終段までの各光電変換素子エレメントに、バックライトからの迷光が等しく届くので、各光電変換素子エレメントの開放電圧を揃えることができるという効果を奏する。

( 1 8 )

前記第1光電変換素子に複数の光電変換素子エレメントが並列接続された箇所と、前記第2光電変換素子に前記第1光電変換素子の前記光電変換素子エレメントと同数の前記光電変換素子エレメントが並列接続された箇所とが、それぞれ形成されており、前記第1光電変換素子と前記第2光電変換素子とのそれぞれについて、前記並列接続された箇所のそれぞれにおける初段から最終段までの各前記光電変換素子エレメントのバックライトから

50

の距離が互いに等しいことを特徴とする表示装置。

【0165】

上記の発明によれば、並列接続された箇所のそれぞれにおける初段から最終段までの各光電変換素子エレメントの両端部に、バックライトからの迷光が等しく届くので、当該光電変換素子エレメントどうしで開放電圧を揃えることができるという効果を奏する。

(19)

前記光電変換素子は、PINフォトダイオードからなる光電変換素子エレメントを1つ以上組み合わせた構成であることを特徴とする表示装置。

【0166】

上記の発明によれば、表示パネルにモノリシックに形成しやすいPINフォトダイオードを用いた周囲光センサに対して、PINフォトダイオードへの誘導ノイズを低減することができるという効果を奏する。

(20)

前記PINフォトダイオードはラテラルPINフォトダイオードであることを特徴とする表示装置。

【0167】

上記の発明によれば、表示パネルへのモノリシック形成に特にプロセスが適しているラテラルPINフォトダイオードを用いた周囲光センサに対して、ラテラルPINフォトダイオードへの誘導ノイズを低減することができるという効果を奏する。

(21)

前記光電変換素子は、フォトトランジスタからなる光電変換素子エレメントを1つ以上組み合わせた構成であることを特徴とする表示装置。

【0168】

上記の発明によれば、フォトトランジスタを用いた周囲光センサに対して、フォトトランジスタへの誘導ノイズを低減することができるという効果を奏する。

(22)

前記表示パネルは液晶パネルであり、前記周囲光センサによって検出された前記周囲光の強度に応じて、バックライト光源の輝度を調節することにより、前記表示面での表示の輝度を調節することを特徴とする表示装置。

【0169】

本発明は上述した実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能である。すなわち、請求項に示した範囲で適宜変更した技術的手段を組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。

【0170】

本発明の表示装置は、以上のように、表示パネルに配置された光電変換素子を用いて表示面側の周囲光の強度を光電変換して検出する周囲光センサを備え、前記周囲光センサによって検出された周囲光の強度に応じて前記表示面での表示の輝度を調節する表示装置であって、前記光電変換素子に対して前記表示パネルの背面側に、導電体からなる、迷光に対する光シールドを備え、前記迷光に対する光シールドに所定の電位が与えられる。

【0171】

以上により、周囲光センサに用いられる光電変換素子への誘導ノイズをさらに低減することのできる表示装置を実現することができるという効果を奏する。

【0172】

発明の詳細な説明の項においてなされた具体的な実施形態または実施例は、あくまでも、本発明の技術内容を明らかにするものであって、そのような具体例にのみ限定して狭義に解釈されるべきものではなく、本発明の精神と次に記載する請求の範囲内において、いろいろと変更して実施することができるものである。

【産業上の利用可能性】

【0173】

本発明は、携帯型の液晶表示装置に特に好適に使用することができる。

10

20

30

40

50

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 7】

【図18】

【図20】

【図19】

【図21】

【図22】

---

フロントページの続き

(72)発明者 ベンジャミン ジェイムズ ハドウェン

イギリス オーエックス4 4ジーピー, オックスフォードシャー, オックスフォード, オックス

フォード サイエンス パーク, エド蒙ド ハリー ロード (番地なし) シャープ ラボラ

トリーズ オブ ヨーロッパ リミテッド内

審査官 吉野 三寛

(56)参考文献 特開2006-3857 (JP, A)

特開昭64-9655 (JP, A)

特開平7-335932 (JP, A)

特開2003-273361 (JP, A)

特開2004-54281 (JP, A)

国際公開第2006/117956 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 31/10 - 31/119

G02F 1/1343 - 1/1345

1/135 - 1/1368