(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6930858号

(P6930858)

(45) 発行日 令和3年9月1日 (2021.9.1)

(24) 登録日 令和3年8月16日 (2021.8.16)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 29/739 | (2006.01) |

| HO 1 L 29/78  | (2006.01) |

| HO 1 L 21/336 | (2006.01) |

| HO 1 L 29/41  | (2006.01) |

| HO 1 L 21/28  | (2006.01) |

| HO 1 L        | 29/78     |

請求項の数 5 (全 11 頁) 最終頁に続く

|           |                               |                                                           |

|-----------|-------------------------------|-----------------------------------------------------------|

| (21) 出願番号 | 特願2017-102542 (P2017-102542)  | (73) 特許権者 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号           |

| (22) 出願日  | 平成29年5月24日 (2017.5.24)        | (73) 特許権者 317011920<br>東芝デバイス&ストレージ株式会社<br>東京都港区芝浦一丁目1番1号 |

| (65) 公開番号 | 特開2018-198266 (P2018-198266A) | (74) 代理人 100108062<br>弁理士 日向寺 雅彦                          |

| (43) 公開日  | 平成30年12月13日 (2018.12.13)      | (72) 発明者 小倉 常雄<br>東京都港区芝浦一丁目1番1号 株式会社<br>東芝内              |

| 審査請求日     | 令和1年8月9日 (2019.8.9)           | (72) 発明者 末代 知子<br>東京都港区芝浦一丁目1番1号 株式会社<br>東芝内              |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1電極と、

第2電極と、

前記第1電極と前記第2電極との間に設けられた半導体層と、

前記半導体層内に設けられ、第1方向に延びる複数のゲート電極と、

前記半導体層内に設けられ、前記第1方向に対して交差する第2方向に延び、前記ゲート電極と接続された複数のゲート配線と、

前記ゲート電極と前記半導体層との間、および前記ゲート配線と前記半導体層との間に設けられた絶縁膜と、

前記ゲート電極と前記第2電極との間、および前記ゲート配線と前記第2電極との間に設けられた層間絶縁膜と、

を備え、

前記半導体層は、

前記第1電極上に設けられた第1半導体層と、

前記第1半導体層上に設けられた第1導電型の第2半導体層と、

前記第2半導体層上に設けられた第2導電型の第3半導体層と、

前記第3半導体層上に設けられ、前記第2電極と接続された第1導電型の第4半導体層と、

を有し、

10

20

前記ゲート電極の幅と前記ゲート配線の幅は略等しい半導体装置。

【請求項 2】

前記ゲート配線の上に設けられたゲートパッドと、

前記ゲートパッドと前記ゲート配線との間に設けられ、前記ゲートパッドと前記ゲート配線とを接続するスルーレ電極と、

をさらに備えた請求項 1 記載の半導体装置。

【請求項 3】

前記ゲートパッドは、前記第 2 電極に重ならない領域における、前記ゲート配線の前記第 2 方向の端部の上に配置されている請求項 2 記載の半導体装置。

【請求項 4】

前記複数のゲート配線が配置されたゲート配線領域で前記ゲート配線のボトムよりも深い位置に設けられた第 2 導電型の第 5 半導体層をさらに備えた請求項 1 ~ 3 のいずれか 1 つに記載の半導体装置。

【請求項 5】

前記第 5 半導体層は、前記第 2 電極と電気的に接続されている請求項 4 記載の半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

実施形態は、半導体装置に関する。

【背景技術】

【0002】

近年、600V 以上の耐圧のパワー半導体デバイスとして IGBT (Insulated Gate Bipolar Transistor) が広く用いられている。このパワー半導体デバイスは、一般的にスイッチとして用いられるので、オン電圧が低く、スイッチング速度が速いことが望まれている。これに加えて、高電圧、大電流のスイッチとして高信頼性化が特に望まれている。

【先行技術文献】

【特許文献】

【0003】

【特許文献 1】特開 2002 - 368221 号公報

【特許文献 2】特開 2002 - 373988 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

実施形態は、高い信頼性を有する半導体装置を提供する。

【課題を解決するための手段】

【0005】

実施形態によれば、半導体装置は、第 1 電極と、第 2 電極と、前記第 1 電極と前記第 2 電極との間に設けられた半導体層と、前記半導体層内に設けられ、第 1 方向に延びる複数のゲート電極と、前記半導体層内に設けられ、前記第 1 方向に対して交差する第 2 方向に延び、前記ゲート電極と接続された複数のゲート配線と、前記ゲート電極と前記半導体層との間、および前記ゲート配線と前記半導体層との間に設けられた絶縁膜と、前記ゲート電極と前記第 2 電極との間、および前記ゲート配線と前記第 2 電極との間に設けられた層間絶縁膜と、を備える。前記半導体層は、前記第 1 電極上に設けられた第 1 半導体層と、前記第 1 半導体層上に設けられた第 1 導電型の第 2 半導体層と、前記第 2 半導体層上に設けられた第 2 導電型の第 3 半導体層と、前記第 3 半導体層上に設けられ、前記第 2 電極と接続された第 1 導電型の第 4 半導体層と、を有する。前記ゲート電極の幅と前記ゲート配線の幅は略等しい。

【図面の簡単な説明】

【0006】

10

20

30

40

50

- 【図1】実施形態の半導体装置の模式平面図。

【図2】図1における一部領域Sの拡大平面図。

【図3】図2におけるA-A'断面図。

【図4】図2におけるB-B'断面図。

【図5】図2におけるC-C'断面図。

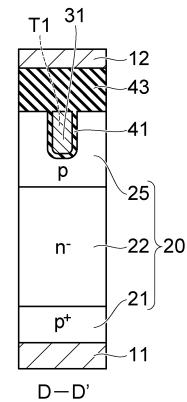

【図6】図2におけるD-D'断面図。

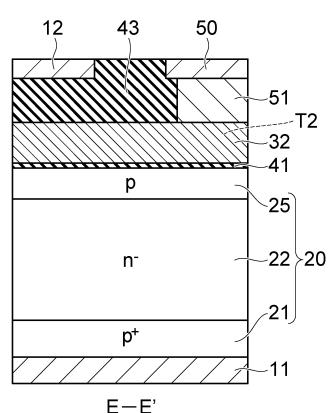

【図7】図1におけるE-E'断面図。

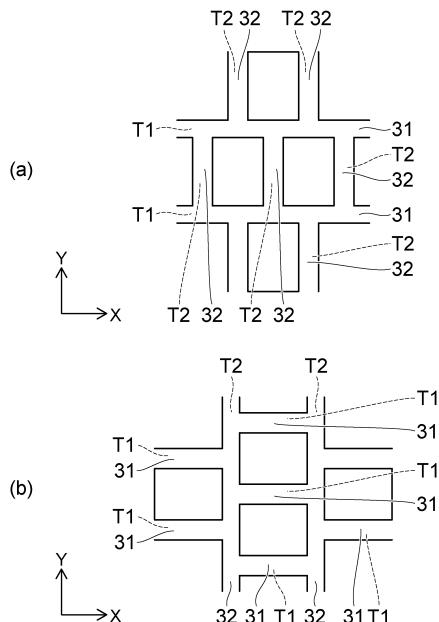

【図8】(a)および(b)は、実施形態のゲート電極とゲート配線との接続レイアウトの他の例を示す模式平面図。

【図9】IGBTの回路図。

10

【発明を実施するための形態】

【0007】

以下、図面を参照し、実施形態について説明する。なお、各図面中、同じ要素には同じ符号を付している。

【0008】

以下の実施形態では第1導電型をn型、第2導電型をp型として説明するが、第1導電型をp型、第2導電型をn型としてもよい。

【0009】

また、実施形態では半導体材料はシリコンとするが、半導体材料は、シリコンに限らず、例えば、炭化シリコン、窒化ガリウム、酸化ガリウムなどであってもよい。

20

【0010】

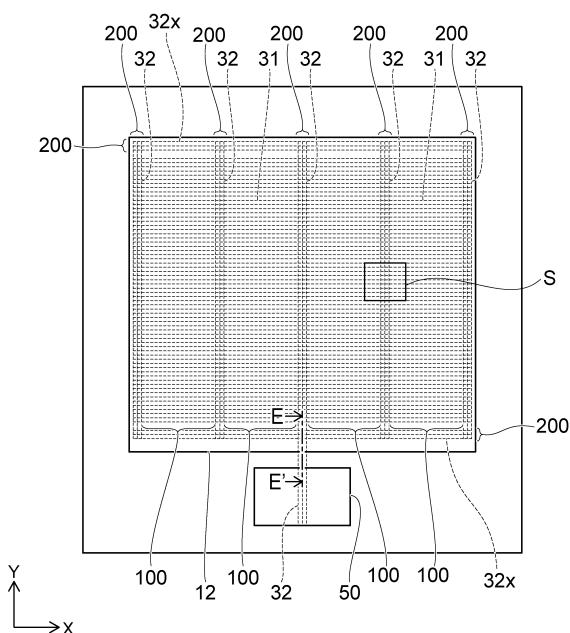

図1は、実施形態の半導体装置(半導体チップ)の模式平面図である。

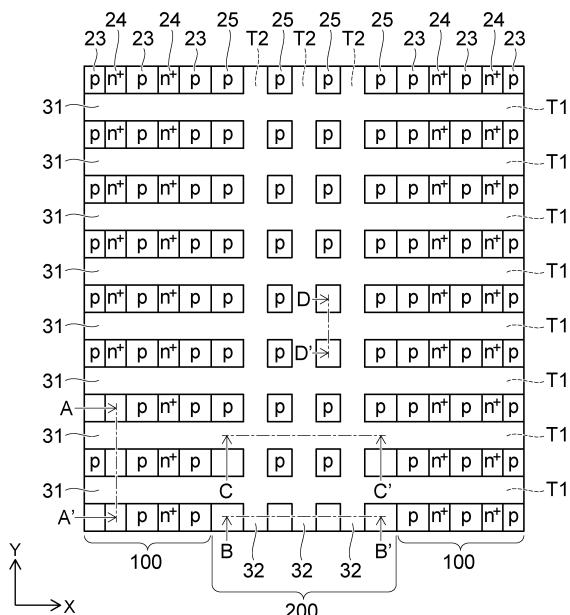

図2は、図1における一部領域Sの拡大平面図である。

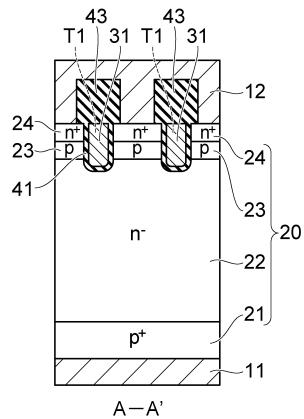

図3は、図2におけるA-A'断面図である。

【0011】

実施形態の半導体装置は、第1電極としてのコレクタ電極11と、第2電極としてのエミッタ電極12との間に半導体層20が設けられ、コレクタ電極11とエミッタ電極12とを結ぶ方向(縦方向)に電流が流れる縦型IGBT構造のデバイスである。

【0012】

または、半導体装置は、以下で説明するp<sup>+</sup>型の層21をn<sup>+</sup>型の層に置き換えたMOSFET(Metal Oxide Semiconductor Field Effect Transistor)構造のデバイスでもよい。

30

【0013】

半導体層20は、不純物がドープされたシリコン層である。図3に示すように、半導体層20は、p<sup>+</sup>型のコレクタ層(第1半導体層)21と、n<sup>-</sup>型のベース層またはドリフト層(第2半導体層)22と、p型のベース層(第3半導体層)23と、n<sup>+</sup>型のエミッタ層(第4半導体層)24とを有する。

【0014】

一般にコレクタ層21のp型不純物濃度はp型ベース層23のp型不純物濃度よりも高い。また、一般にエミッタ層24のn型不純物濃度はn<sup>-</sup>型ベース層22のn型不純物濃度よりも高い。

40

【0015】

コレクタ層21は、コレクタ電極11上に設けられ、コレクタ電極11に接している。コレクタ層21上にn<sup>-</sup>型ベース層22が設けられている。n<sup>-</sup>型ベース層22上にp型ベース層23が設けられている。p型ベース層23上にエミッタ層24が設けられている。

【0016】

図2に示すように、複数のエミッタ層24は、X方向に互いに離間してp型ベース層23の表面に選択的に形成され、Y方向に延びている。X方向およびY方向は、半導体層20の正面に対して平行な面内で互いに直交する方向を表す。

50

## 【0017】

実施形態の半導体装置は、トレンチゲート構造のゲート電極31を有する。図3に示すように、半導体層20内にゲート電極31が設けられている。ゲート電極31の側面と半導体層20との間、およびゲート電極31のボトムと半導体層20との間に、絶縁膜41が設けられている。絶縁膜41は、例えばシリコン酸化膜である。

## 【0018】

半導体層20の表面側に形成されたトレンチT1の内壁に例えば熱酸化法で絶縁膜41が形成され、その絶縁膜41の内側にゲート電極31として例えば多結晶シリコンが埋め込まれる。

## 【0019】

図1および図2に示すように、複数のゲート電極31が、X方向に延び、Y方向に互いに離間している。

## 【0020】

図3に示すように、ゲート電極31は、エミッタ層24およびp型ベース層23を貫通して、n<sup>-</sup>型ベース層22に達する。ゲート電極31の下端は、p型ベース層23のボトム(p型ベース層23とn<sup>-</sup>型ベース層22とのpn接合)よりも下方(コレクタ層21側)に位置する。ゲート電極31の側面は、絶縁膜41を介して、エミッタ層24およびp型ベース層23に対向している。

## 【0021】

ゲート電極31上に層間絶縁膜43が設けられている。層間絶縁膜43は例えばシリコン酸化膜である。層間絶縁膜43を覆うように、エミッタ層24上にエミッタ電極12が設けられている。エミッタ電極12は、エミッタ層24に接している。

## 【0022】

また、エミッタ電極12は、エミッタ層24が形成されていない領域(図2におけるX方向に離間したエミッタ層24間の領域)のp型ベース層23の表面にも接している。

## 【0023】

図1に示すように、エミッタ電極12は複数に分割されず、1つのチップにつき1つのエミッタ電極12がチップの上面の大部分を占めて形成されている。そのエミッタ電極12の下で、複数のゲート電極31がX方向に延びている。

## 【0024】

エミッタ電極12の下の半導体層20内には、複数のゲート配線32も配置されている。図2に示すように、複数のゲート配線32が配置されたゲート配線領域には、エミッタ層24およびp型ベース層23は設けられず、p型半導体層(第5半導体層)25が設けられている。

## 【0025】

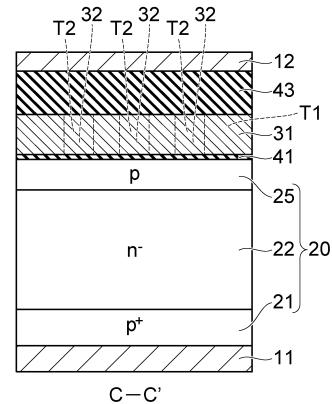

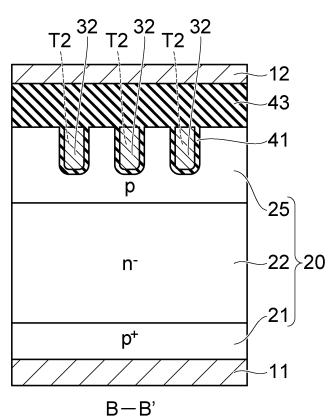

図4は、図2におけるB-B'断面図である。

図5は、図2におけるC-C'断面図である。

図6は、図2におけるD-D'断面図である。

## 【0026】

図4に示すように、ゲート配線32は、ゲート電極31と同様、半導体層20内に形成されたトレンチT2内に絶縁膜41を介して埋め込まれる。図2に示すように、複数のトレンチT2が、Y方向に延び、X方向に互いに離間している。したがって、複数のゲート配線32は、Y方向に延び、X方向に互いに離間している。

## 【0027】

トレンチT1とトレンチT2は、例えばRIE(Reactive Ion Etching)法で同時に形成される。トレンチT1とトレンチT2は互いに交差(例えば直交)している。トレンチT1の幅とトレンチT2の幅とは略等しく、トレンチT1の深さとトレンチT2の深さとは略等しい。

## 【0028】

それらトレンチT1、T2の内壁に絶縁膜41を形成した後、ゲート電極31およびゲ

10

20

30

40

50

ート配線 3 2 の材料として例えば多結晶シリコンがトレンチ T 1、T 2 内に埋め込まれる。したがって、ゲート電極 3 1 とゲート配線 3 2 は、同じ材料で一体に設けられ、互いに交差（例えば直交）している。その交差部分で、ゲート電極 3 1 とゲート配線 3 2 は一体に接続している。

【 0 0 2 9 】

ゲート電極 3 1 の幅とゲート配線 3 2 の幅とは略等しく、たとえば 1  $\mu\text{m}$  前後であり、ゲート電極 3 1 の深さとゲート配線 3 2 の深さとは略等しく、たとえば 5  $\mu\text{m}$  前後である。

【 0 0 3 0 】

複数のゲート配線 3 2 が配置されたゲート配線領域に設けられた図 4 に示す p 型半導体層 2 5 のボトムは、図 3 に示すセル領域の p 型ベース層 2 3 のボトムよりも深い位置（コレクタ層 2 1 側）にある。図 4 に示すように、p 型半導体層 2 5 は、絶縁膜 4 1 を介して、ゲート配線 3 2 のボトムのコーナーを覆っている。ゲート配線 3 2 と p 型半導体層 2 5 との間に絶縁膜 4 1 が設けられている。 10

【 0 0 3 1 】

p 型半導体層 2 5 は、エミッタ電極 1 2 と電気的に接続される。または、p 型半導体層 2 5 は電気的にフローティングでもよい。このような p 型半導体層 2 5 は、電界が集中しやすいトレンチ構造のゲート配線 3 2 のボトムのコーナーの電界を緩和する。

【 0 0 3 2 】

ゲート電極 3 1 において、複数のゲート配線 3 2 が配置されたゲート配線領域を X 方向に横切る部分の下にも、図 5 および図 6 に示すように、p 型半導体層 2 5 が設けられている。 20

【 0 0 3 3 】

図 4 に示すように、ゲート配線 3 2 の上にもエミッタ電極 1 2 が広がり、そのエミッタ電極 1 2 とゲート配線 3 2 との間に層間絶縁膜 4 3 が設けられている。

【 0 0 3 4 】

図 1 に示すように、複数のゲート電極 3 1 の数は、複数のゲート配線 3 2 の数よりも多い。図 2 に示す領域 S が 1 つのチップにおいて X 方向及び Y 方向に繰り返されている。

【 0 0 3 5 】

すなわち、p 型ベース層 2 3 およびエミッタ層 2 4 が配置されたセル領域 1 0 0 と、p 型半導体層 2 5 および複数のゲート配線 3 2 が配置されたゲート配線領域 2 0 0 とが X 方向に交互に並んでいる。図 1 に示すように、複数のゲート配線領域 2 0 0 が X 方向に離間して配置されている。セル領域 1 0 0 の面積（X 方向の長さ）は、ゲート配線領域 2 0 0 の面積（X 方向の長さ）よりも大きい。 30

【 0 0 3 6 】

ゲート配線領域 2 0 0 は 1 つでもよい。例えば、図 1 においてチップ横方向（X 方向）の中央に配置され、Y 方向に延びる 1 つのゲート配線領域 2 0 0 だけでもよい。

【 0 0 3 7 】

また、Y 方向に延びる複数のゲート配線領域 2 0 0 を接続するゲート配線領域 2 0 0 が X 方向に形成されている。図 1 に示す例では、Y 方向の両端に、X 方向に延びるゲート配線領域 2 0 0 が配置されている。 40

【 0 0 3 8 】

X 方向に延びるゲート配線領域 2 0 0 は、X 方向に延びる複数のゲート配線 3 2 x を有する。複数のゲート配線 3 2 x は、Y 方向に互いに離間している。ゲート配線 3 2 x も、ゲート配線 3 2 やゲート電極 3 1 と同様に、半導体層 2 0 に形成されたトレンチ内に埋め込まれた例えば多結晶シリコンで形成されている。Y 方向に延びる複数のゲート配線 3 2 の両端が、X 方向に延びるゲート配線 3 2 x に接続されている。

【 0 0 3 9 】

図 1 に示すように、チップの上面には、ゲートパッド 5 0 が設けられている。ゲートパッド 5 0 は、チップ上面におけるエミッタ電極 1 2 が形成されていない領域に、エミッタ

電極 1 2 に対して離間して配置されている。ゲートパッド 5 0 の面積は、エミッタ電極 1 2 の面積よりも小さい。エミッタ電極 1 2 およびゲートパッド 5 0 はともに金属材料からなり、例えばアルミニウムからなる。

【 0 0 4 0 】

図 7 は、図 1 における E - E ' 断面図である。

【 0 0 4 1 】

図 1 に示すように、Y 方向に延びる複数のゲート配線 3 2 は X 方向に延びる複数のゲート配線 3 2 x に電気的に接続され、例えば X 方向の中央に位置するゲート配線領域 2 0 0 の複数のゲート配線 3 2 はゲートパッド 5 0 の下の領域にも延びている。ゲートパッド 5 0 は、そのゲート配線 3 2 の Y 方向の端部の上に配置されている。そのゲート配線 3 2 とゲートパッド 5 0 との間に、図 7 に示すように、スルーホール 5 1 が設けられている。スルーホール 5 1 は、ゲートパッド 5 0 とゲート配線 3 2 とを接続している。これにより、ゲートパッド 5 0 は、ゲート配線 3 2 、ゲート配線 3 2 x を介して、チップ内のすべてのゲート電極 3 1 に電気接続され、ゲート信号を供給できる。

【 0 0 4 2 】

エミッタ電極 1 2 とゲートパッド 5 0 は、略同じ高さに配置されている。エミッタ電極 1 2 とゲートパッド 5 0 との間には層間絶縁膜 4 3 が設けられている。

【 0 0 4 3 】

ゲート電極 3 1 は、ゲート配線 3 2 、3 2 x およびスルーホール 5 1 を通じて、ゲートパッド 5 0 と電気的に接続されている。ゲートパッド 5 0 には例えばワイヤがボンディングされ、ゲートパッド 5 0 はそのワイヤを通じて外部回路と接続される。

【 0 0 4 4 】

または、スルーホール 5 1 を図 1 において X 方向に延在させ、そのスルーホール 5 1 に、Y 方向に延びる複数のゲート配線領域 2 0 0 のそれぞれのゲート配線 3 2 を接続させてもよい。これにより、ゲートパッド 5 0 は、より低抵抗でチップ内のすべてのゲート電極 3 1 に電気接続され、ゲート信号を供給でき、よりバランスの改善された素子動作が可能となる。

【 0 0 4 5 】

エミッタ電極 1 2 上には例えば板状のコネクタが接合され、エミッタ電極 1 2 はそのコネクタを通じて外部回路と接続される。コレクタ電極 1 1 は、リードフレーム上に接合される。

【 0 0 4 6 】

以上説明した I G B T において、コレクタ電極 1 1 とエミッタ電極 1 2 との間に電圧が印加される。コレクタ電極 1 1 に与えられる電位は、エミッタ電極 1 2 に与えられる電位よりも高い。

【 0 0 4 7 】

I G B T のオン動作時には、ゲート電極 3 1 にしきい値以上の電位が与えられ、p 型ベース層 2 3 におけるゲート電極 3 1 に対向する領域に反転層 (n 型のチャネル) が形成される。そして、コレクタ層 2 1 、n - 型ベース層 2 2 、チャネル、およびエミッタ層 2 4 を通じて、コレクタ電極 1 1 とエミッタ電極 1 2 との間を電子電流が流れる。このとき、コレクタ層 2 1 から n - 型ベース層 2 2 に正孔が供給され、n - 型ベース層 2 2 に電子および正孔の高密度状態が作り出され、低いオン抵抗が得られる。

【 0 0 4 8 】

トレンチゲート構造の I G B T において、チップ上面でエミッタ電極とほぼ同じ高さに配置された金属のゲート配線が、複数に分割されたエミッタ電極の間を延びてゲートパッドに接続された構造が、現在広く用いられている。トレンチゲートの多結晶シリコンの一部が上方に引き出されて、金属ゲート配線と接続される。

【 0 0 4 9 】

このような、チップ上面にエミッタ電極と金属ゲート配線がほぼ同一の高さに形成される構造は電気絶縁上の信頼性が問題になり得る。また、ゲート配線をポリイミドなどの絶

縁膜で覆った上で、チップ上面のエミッタ電極形成領域の全面にめっき法などにより金属電極を形成する構造の場合、長期の高温動作でポリイミド絶縁膜が劣化する問題が懸念される。

【0050】

実施形態によれば、ゲート配線32は、チップ上面のエミッタ電極形成領域ではなく、ゲート電極31と同様、半導体層20内に形成され、チップ上面に金属ゲート配線が形成されない。この結果、長期の高温動作でも十分な絶縁信頼性を有するIGBT素子を提供できる。

【0051】

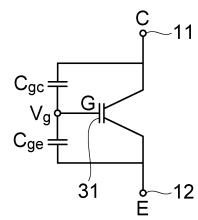

図9は、IGBTの回路図である。

10

【0052】

コレクタ電極11とゲート電極31との間に容量C<sub>gc</sub>が存在し、エミッタ電極12とゲート電極31との間に容量C<sub>ge</sub>が存在する。

【0053】

実施形態のようにゲート配線32を複数に分ける構造は、それら複数のゲート配線32を分けずにX方向につなげた幅広のゲート配線構造(比較例)よりも、C<sub>ge</sub>が大きくなる。これは、図4に示す複数のゲート配線32と、エミッタ電位と同電位のp型半導体層25との間に大きな容量成分を形成することによる。したがって、実施形態では、比較例よりもC<sub>gc</sub> / C<sub>ge</sub>を小さくできる。C<sub>gc</sub> / C<sub>ge</sub>を小さくすることは、ゲート電位V<sub>g</sub>を安定させ、外部の電圧変化に対して誤点弧を防止することを可能にする。

20

【0054】

また、ゲート電極用のトレンチとゲート配線用のトレンチとを同時にRIE法で形成するにあたって、トレンチ間で幅が大きく異なると、トレンチの深さや形状がばらつきやすくなる。これはデバイス特性のばらつきにつながり得る。

【0055】

これに対して実施形態によれば、ゲート電極31用のトレンチT1とゲート配線32用のトレンチT2は幅が略等しいため、それらトレンチT1とトレンチT2を同時にRIE法で形成するにあたって、トレンチT1、T2の深さや形状のばらつきを抑制できる。

【0056】

図8(a)および(b)は、ゲート電極31とゲート配線32との接続レイアウトの他の例を示す模式平面図である。

30

【0057】

図8(a)では、トレンチT1(ゲート電極31)はX方向に一直線状に延びている。これに対して、共通のトレンチT1(ゲート電極31)に接続する複数のトレンチT2(ゲート配線32)のうち、その共通のトレンチT1(ゲート電極31)の一方の側面側に接続する複数のトレンチT2(ゲート配線32)と、他方の側面側に接続する複数のトレンチT2(ゲート配線32)とは、X方向の位置がずれている。

【0058】

図8(b)では、トレンチT2(ゲート配線32)はY方向に一直線状に延びている。これに対して、共通のトレンチT2(ゲート配線32)に接続する複数のトレンチT1(ゲート電極31)のうち、その共通のトレンチT2(ゲート配線32)の一方の側面側に接続する複数のトレンチT1(ゲート電極31)と、他方の側面側に接続する複数のトレンチT1(ゲート電極31)とは、Y方向の位置がずれている。

40

【0059】

図8(a)および(b)のいずれの場合も、トレンチT1(ゲート電極31)と、トレンチT2(ゲート配線32)とはT字状に接続している。

【0060】

図2に示すような、トレンチT1とトレンチT2とが十字状に接続するレイアウトでは、トレンチT1とトレンチT2との接続部(交差部)の中心から見て四方向にエッチングすべき領域が広がっている。

50

## 【0061】

これに対して、図8(a)および(b)に示すような、トレンチT1とトレンチT2とがT字状に接続するレイアウトでは、トレンチT1とトレンチT2との接続部(交差部)の中心から見て三方向にエッティングすべき領域が広がっている。このようなT字状交差部は、トレンチT1とトレンチT2を同時にエッティングするとき、十字状交差部よりも、交差部の中心付近にエッティングされない部分が残りにくくできる。

## 【0062】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

10

## 【符号の説明】

## 【0063】

11...コレクタ電極、12...エミッタ電極、21...コレクタ層、22...n<sup>-</sup>型ベース層、23...p型ベース層、24...エミッタ層、25...p型半導体層、31...ゲート電極、32...ゲート配線、50...ゲートパッド、51...スルーホール

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(51)Int.Cl.

F I

|        |       |         |

|--------|-------|---------|

| H 01 L | 29/78 | 6 5 2 Q |

| H 01 L | 29/78 | 6 5 8 F |

| H 01 L | 29/44 | P       |

| H 01 L | 21/28 | 3 0 1 A |

審査官 恩田 和彦

(56)参考文献 特開2009-146994 (JP, A)

特開2011-228719 (JP, A)

特開2016-040807 (JP, A)

特表2009-522807 (JP, A)

特開2000-101076 (JP, A)

特開平09-270512 (JP, A)

国際公開第2016/047438 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

|        |             |

|--------|-------------|

| H 01 L | 2 9 / 7 3 9 |

| H 01 L | 2 1 / 2 8   |

| H 01 L | 2 1 / 3 3 6 |

| H 01 L | 2 9 / 4 1   |

| H 01 L | 2 9 / 7 8   |