(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5103660号

(P5103660)

(45) 発行日 平成24年12月19日(2012.12.19)

(24) 登録日 平成24年10月12日(2012.10.12)

(51) Int.Cl.

F 1

G 11 C 16/06 (2006.01)

G 11 C 16/04 (2006.01)G 11 C 17/00 634 G

G 11 C 17/00 622 E

G 11 C 17/00 636 Z

請求項の数 25 (全 39 頁)

|              |                               |           |                                                                                                                                                           |

|--------------|-------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2005-315094 (P2005-315094)  | (73) 特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路 129<br>129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic of Korea |

| (22) 出願日     | 平成17年10月28日(2005.10.28)       |           |                                                                                                                                                           |

| (65) 公開番号    | 特開2006-127749 (P2006-127749A) |           |                                                                                                                                                           |

| (43) 公開日     | 平成18年5月18日(2006.5.18)         |           |                                                                                                                                                           |

| 審査請求日        | 平成20年10月28日(2008.10.28)       |           |                                                                                                                                                           |

| (31) 優先権主張番号 | 10-2004-0086450               | (74) 代理人  | 100086368<br>弁理士 萩原 誠                                                                                                                                     |

| (32) 優先日     | 平成16年10月28日(2004.10.28)       | (72) 発明者  | 季 城 秀<br>大韓民国京畿道城南市盆唐区金谷洞 盆唐<br>ドーサンウップアパート 109 棟 1304<br>号                                                                                               |

| (33) 優先権主張国  | 韓国(KR)                        |           |                                                                                                                                                           |

| (31) 優先権主張番号 | 10-2004-0086451               |           |                                                                                                                                                           |

| (32) 優先日     | 平成16年10月28日(2004.10.28)       |           |                                                                                                                                                           |

| (33) 優先権主張国  | 韓国(KR)                        |           |                                                                                                                                                           |

前置審査

最終頁に続く

(54) 【発明の名称】ページバッファおよびページバッファを含む不揮発性メモリ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

不揮発性メモリ装置において、複数の不揮発性メモリセル、複数のワードラインおよび第1方向に延在する複数のビットラインを含むメモリセルアレイと；前記メモリセルアレイから読み出されるデータを出力する内部データ出力ラインと；複数の内部データ入力ラインと前記内部データ出力ラインとに連結されるデコーダ回路と；前記メモリセルアレイと前記内部データ出力ラインとの間にそれぞれ動作可能に連結される複数のページバッファとを備え、

前記複数のページバッファは、第1方向に対応する複数のページバッファ領域を定義するように並置配列され、前記内部データ出力ラインは、隣接した前記複数のページバッファの前記第1方向に延在することを特徴とする、不揮発性メモリ装置。

## 【請求項 2】

前記デコーダ回路は、アドレス信号およびグローバルデータ入力信号を受信し、前記アドレス信号および前記グローバルデータ入力信号によって、内部入力データを前記複数の内部データ入力ライン上に出力することを特徴とする、請求項1に記載の不揮発性メモリ装置。

## 【請求項 3】

前記デコーダ回路は、

10

20

前記アドレス信号によって、前記内部データ出力ラインをグローバルデータ出力ラインに選択的に連結することを特徴とする、請求項2に記載の不揮発性メモリ装置。

**【請求項 4】**

不揮発性メモリ装置において、

複数の不揮発性メモリセルを含むメモリセルアレイと；

ローカルデータ入力ラインと、前記メモリセルアレイの前記不揮発性メモリセルから読み出されるデータおよび前記不揮発性メモリセルにプログラムされるデータを一時的に記憶するように、前記ローカルデータ入力ラインに応答するラッチ回路とを含むページバッファと；

前記メモリセルアレイをプログラムするためのプログラミング信号および前記メモリセルアレイを読み出すための制御信号を含む外部入力信号を供給するグローバルデータ入力ラインと；

供給されるアドレス信号によって前記ローカルデータ入力ラインに前記外部入力信号を選択的に出力するゲート回路を備えることを特徴とする、不揮発性メモリ装置。 10

**【請求項 5】**

前記ローカルデータ入力ラインは、前記ページバッファの前記ラッチ回路のラッチ状態を制御することを特徴とする、請求項4に記載の不揮発性メモリ装置。

**【請求項 6】**

前記ローカルデータ入力ラインは、前記ラッチ回路の第1ラッチノードと基準電位との間に直列に連結される第1トランジスタのゲートに連結される第1ローカル入力ラインと、前記ラッチ回路の第2ラッチノードと前記基準電位との間に直列に連結される第2トランジスタのゲートに連結される第2ローカル入力ラインとを含むことを特徴とする、請求項5に記載の不揮発性メモリ装置。 20

**【請求項 7】**

前記基準電位と前記第1および第2トランジスタのそれぞれとの間に直列に連結される第3トランジスタをさらに備え、

前記第3トランジスタのゲートは、第1アドレス信号ラインに連結されることを特徴とする、請求項6に記載の不揮発性メモリ装置。 30

**【請求項 8】**

前記ゲート回路は、第2アドレス信号ラインに連結されるデコーダ回路の一部を形成することを特徴とする、請求項7に記載の不揮発性メモリ装置。 30

**【請求項 9】**

不揮発性メモリ装置において、

複数の不揮発性メモリセル、複数のワードラインおよび複数のビットラインを持つメモリセルアレイと；

前記メモリセルアレイから読み出されるデータを出力する内部データ出力ラインと；

前記メモリセルアレイと前記内部データ出力ラインとの間に動作可能に連結される複数のページバッファと；

前記複数のページバッファの少なくとも一つのゲート回路に動作可能に連結される複数のアドレスラインとを備え、 40

前記少なくとも一つのゲート回路は、第1アドレスゲートを含み、

前記ページバッファのそれぞれは、前記メモリセルアレイから読み出されるデータを一時的に記憶するラッチ回路と、基準電位と前記内部データ出力ラインとの間に連結されるアドレスゲートとを含み、

それぞれのページバッファを通じて延在する前記アドレスラインは、前記それぞれのページバッファの前記第1アドレスゲートに連結されることを特徴とする、不揮発性メモリ装置。

**【請求項 10】**

前記少なくとも一つのゲート回路は、前記ラッチ回路と前記基準電位との間に連結された第2アドレスゲートをさらに備え、 50

それぞれのページバッファを通じて延在する前記アドレスラインは、前記それぞれのページバッファの前記第2アドレスゲートにさらに連結されることを特徴とする、請求項9に記載の不揮発性メモリ装置。

**【請求項11】**

前記ページバッファは、第1方向に並置された対応する複数のページバッファ領域に配列され、

前記複数のアドレスラインは、前記第1方向に垂直な第2方向に延在されることを特徴とする、請求項9に記載の不揮発性メモリ装置。

**【請求項12】**

不揮発性半導体メモリ装置において、

10

電気的にプログラムおよび消去可能な複数のメモリセル、複数のワードライン、および複数のビットラインを持つメモリセルアレイと；

複数のページバッファと内部データ出力ラインとを持つ少なくとも一つのページバッファブロックであって、前記ページバッファのそれぞれはビットラインに連結され、複数のバッファ選択信号のなかの少なくとも一つに応答してイネーブルされ、前記ページバッファのそれぞれはビットライン上のデータに対応して、自分のラッチノードに記憶し、前記内部データ出力ラインは前記複数のページバッファに共有され、イネーブルされるページバッファのラッチノード上のデータによってドライビングされ、前記内部データ出力ラインは前記ページバッファのラッチノードから電気的に隔離されるようになった、前記少なくとも一つのページバッファブロックとを備えることを特徴とする、不揮発性半導体メモリ装置。

20

**【請求項13】**

前記ページバッファのそれぞれは、

前記ラッチノードを持つラッチユニットと；

前記バッファ選択アドレスのなかの前記少なくとも一つに応答してイネーブルされ、前記ラッチノードに記憶されたデータに対応して前記内部データ出力ラインにドライビングする出力ドライビングユニットとを備えることを特徴とする、請求項12に記載の不揮発性半導体メモリ装置。

**【請求項14】**

前記ページバッファのそれぞれは、

30

第1および第2内部データ入力ラインと；

前記第1および第2内部データ入力ラインにそれぞれゲートされる第1および第2ラッチ伝送トランジスタを含むラッチ伝送ユニットとをさらに備え、

前記第1および第2ラッチ伝送トランジスタは、前記ページバッファの前記ラッチノードおよび反転されたラッチノードのそれぞれの電圧を設定するように、前記第1および第2内部データ入力ラインにそれぞれ応答することを特徴とする、請求項13に記載の不揮発性半導体メモリ装置。

**【請求項15】**

前記ページバッファのそれぞれは、

前記バッファ選択アドレスに応答してゲートされ、所定のバッファ入力パスを介して、ラッチドライビング電圧を前記ラッチ伝送ユニットに提供するラッチドライビングユニットをさらに備え、

40

前記バッファ入力パスは、前記内部データ出力ラインから電気的に隔離されることを特徴とする、請求項14に記載の不揮発性半導体メモリ装置。

**【請求項16】**

前記ページバッファのそれぞれは、

前記ビットライン上のデータに応答して所定のセンシング応答電圧を前記ラッチ伝送ユニットに提供するセンシング応答ユニットを備え、

前記センシング応答電圧は、前記ラッチノードに記憶されるデータのフリップを誘発するのに十分な電圧であることを特徴とする、請求項15に記載の不揮発性半導体メモリ装

50

置。

**【請求項 17】**

前記ラッチ伝送ユニットは、

前記第1内部データ入力ライン上の前記データに応答して、前記ラッチユニットに前記ラッチドライビング電圧または前記センシング応答電圧を選択的に提供する第1ラッチ伝送トランジスタと；

前記第2内部データ入力ライン上のデータに応答して、前記ラッチユニットに前記ラッチドライビング電圧または前記センシング応答電圧を選択的に提供する第2ラッチ伝送トランジスタとを備えることを特徴とする、請求項16に記載の不揮発性半導体メモリ装置。

10

**【請求項 18】**

前記センシング応答ユニットは、

前記ビットライン上のデータに応答してゲートされるセンシング応答トランジスタと；

前記センシング応答トランジスタに直列に連結される出力センシングトランジスタとを備え、

前記出力センシングトランジスタは、

前記ページバッファを選択するのに使用される読み出しラッチ信号に応答して、前記ラッチノードに記憶される前記ビットライン上のデータに対応するデータを制御することを特徴とする、請求項17に記載の不揮発性半導体メモリ装置。

20

**【請求項 19】**

前記ページバッファのそれぞれは、

前記ビットライン上の前記データに対応するデータを前記センシング応答ユニットに提供する前記ビットラインに連結されるセンシングノードと；

前記センシングノードをセッティング電圧に調節するためのセンシングセッティングユニットとをさらに備えることを特徴とする、請求項17に記載の不揮発性半導体メモリ装置。

20

**【請求項 20】**

同一のページバッファブロック内に含まれる前記複数のページバッファは第1方向に並置され、

前記内部データ出力ラインは前記第1方向に延在することを特徴とする、請求項12に記載の不揮発性半導体メモリ装置。

30

**【請求項 21】**

第1グローバルデータ入力ラインと；

特定動作区間で、前記第1グローバルデータ入力ラインの論理状態と反対の論理状態を持つ第2グローバルデータ入力ラインと；

メイン選択アドレスおよびサブ選択アドレスに応答してイネーブルされるページバッファデコーダとをさらに備え、

前記ページバッファデコーダは、イネーブルされる時、前記第1および第2グローバルデータ入力ライン上のデータに対応するデータをそれぞれ前記第1および第2内部データ入力ラインに提供するページバッファデコーダをさらに備えることを特徴とする、請求項12に記載の不揮発性半導体メモリ装置。

40

**【請求項 22】**

前記ページバッファデコーダは、

前記メイン選択アドレスと前記サブ選択アドレスの論理演算を行い、前記メイン選択アドレスと前記サブ選択アドレスとがともにアクティブ状態である時、アクティブになるブロックデコーディング信号を出力する第1デコーダ論理ゲートと；

前記ブロックデコーディング信号に応答してイネーブルされ、論理演算結果を前記第1グローバルデータ入力ラインのデータに応答して前記第1内部データ入力ラインに提供する第2デコーダ論理ゲートと；

前記ブロックデコーディング信号に応答してイネーブルされ、前記第2グローバルデータ

50

タ入力ライン上のデータに応答して論理演算結果を前記第2内部データ入力ラインに提供する第3デコーダ論理ゲートとを備えることを特徴とする、請求項2\_1に記載の不揮発性半導体メモリ装置。

#### 【請求項2\_3】

前記第1デコーダ論理ゲートはNANDゲートであり、

前記第2および第3デコーダ論理ゲートはNORゲートであることを特徴とする、請求項2\_2に記載の不揮発性半導体メモリ装置。

#### 【請求項2\_4】

グローバル出力ラインと；

メイン選択アドレスとサブ選択アドレスとに応答してイネーブルされるページバッファデコーダとをさらに備え、

前記ページバッファデコーダは、イネーブルされる時、前記内部データ出力ライン上のデータをグローバルデータ出力ラインに提供することを特徴とする、請求項1\_2に記載の不揮発性半導体メモリ装置。

#### 【請求項2\_5】

前記ページバッファデコーダは、

前記メイン選択アドレスと前記サブ選択アドレスの論理演算を行い、前記メイン選択アドレスと前記サブ選択アドレスとがともにアクティブ状態である時、アクティブになるブロックデコーディング信号を出力するための第1デコーダ論理ゲートと；

前記ブロックデコーディング信号に応答して前記内部データ出力ライン上のデータを前記グローバルデータ出力ラインに提供するためのデコーダトランジスタとを備えることを特徴とする、請求項2\_4に記載の不揮発性半導体メモリ装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は半導体メモリ装置に係り、特に、不揮発性メモリ装置に使用されるページバッファ回路およびその他の回路に関するものである。

##### 【背景技術】

##### 【0002】

最近、電気的プログラム(program)および電気的消去(erase)が可能な不揮発性半導体メモリ装置に対する需要が急激に増加している。このような装置は、少なくとも供給電源のない状態で記憶されたデータを保持することができる能力によって部分的な特徴がある。いわゆる、フラッシュメモリは、特にデジタルカメラ、携帯電話(cel1 phone)、PDA(personal data assistant)、およびラップトップコンピュータ(laptop computer)のようなポータブル装置に広く利用されているが、これらに限定されるものではない。フラッシュメモリ、たとえばNAND型フラッシュメモリは、比較的小さな面積に多量のデータを記憶することができる。

##### 【0003】

従来技術の考察として、フラッシュメモリセルとフラッシュメモリ装置の基礎を成す基本的動作原理を以下に提示する。しかし、以下に提示する説明はただ一例であり、本発明の範囲を決して制限および/または限定するものではないことを明確に理解しなければならない。

##### 【0004】

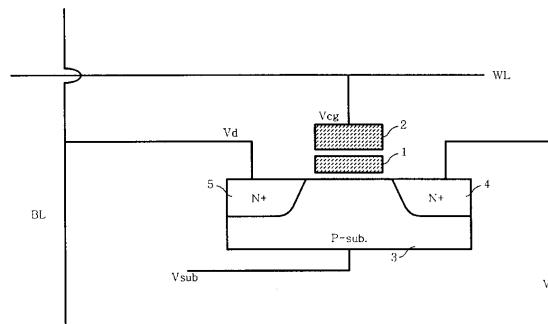

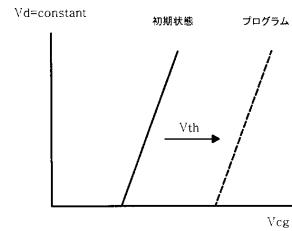

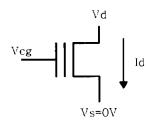

まず、フラッシュメモリセル(flash memory cell)の動作原理を図1a～図1cに基づいて説明する。図1aはメモリ装置のワードラインとビットラインとに連結される一つのフラッシュメモリセルトランジスタの典型的な構造を示し、図1bは一つのフラッシュメモリセルトランジスタの等価回路を示し、そして、図1cは一つのフラッシュメモリセルトランジスタのスレショルド電圧(threshold voltage)特性を示す。

10

20

30

40

50

## 【0005】

図1a～図1cをともに参照すれば、一つのフラッシュメモリセルトランジスタは、基板3の表面上に位置するソース領域(source region)4と、ドレイン領域(drain region)5とを含む。本実施例において、基板3はP型であり、ソース領域4とドレイン領域5はN+型である。ゲート構造は、ソース領域4と前記ドレイン領域5との間に決まるチャンネル領域(channel region)の上部に整列される。ゲート構造は、フローティングゲート(floating gate)1と制御ゲート(control gate)2とを含む。図示されていないが、トンネリング誘電体層(tunneling dielectric layer)がフローティングゲートと基板の表面との間に挿入され、ほかの薄膜酸化層(thin oxide layer)(あるいは、制御誘電体層)がフローティングゲート1と制御ゲート2との間に挿入される。図示の例において、ドレイン電圧(Vd)はビットライン(BL)から供給され、制御ゲート電圧(Vcg)はワードライン(WL)から供給され、ソース電圧(Vs)は接地のような基準電位に連結される。

10

## 【0006】

フラッシュメモリセルトランジスタのスレショルド電圧は、その記憶された論理値を定義する。すなわち、フラッシュメモリセルトランジスタが初期状態(また“消去”状態ともいう)にある場合には、スレショルド電圧(Vth)は、図1cに示すように、比較的低い。このような状態は、セルトランジスタは論理値“1”を有すると定義され、一般的に通常のトランジスタ素子のオン(ON)状態に相当する。一方、セルトランジスタがプログラムされた状態(PGM)にある場合は、前記スレショルド電圧(Vth)は比較的高い。このような高いスレショルド電圧状態は論理値“1”を有すると指定し、一般的に通常のトランジスタ素子のオフ(OFF)状態に相当する。

20

## 【0007】

セルトランジスタを初期状態からプログラムされた状態に変換(プログラム)するために、ファウラー・ノルドハイムトンネリング(Fowler-Nordheim tunneling、以下“FNトンネリング”という)として広く知られたプロセスが用いられる。このプロセスを簡略に説明すれば、比較的大きい正(+)の電位差が制御ゲート2と基板(Psub)との間に生成され、基板(Psub)上のチャンネル内に励起された電子(excited electron)は透過されてフローティングゲート1にトラップされる。このような負(-)でチャージされた電子は制御ゲート2と基板(Psub)との間の障壁として作用し、よって、図1cに示すように、セルトランジスタのスレショルド電圧を増加させる。制御ゲート2と基板(Psub)との間に大きい負(-)の電位差を形成することによって、セルトランジスタは初期状態に復元できる。そして、結果として生ずるFNトンネリングは、トラップされた電子を、薄膜酸化層を横切ってフローティングゲート1から基板(Psub)に返し、電子障壁を除去しスレショルド電圧(Vth)を低下させる。

30

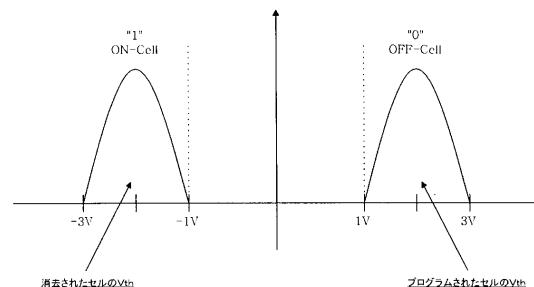

## 【0008】

図2を参照すれば、フラッシュメモリ装置内に発見される相当数のフラッシュセルトランジスタのオン(ON)およびオフ(OFF)スレショルド電圧(Vth)は、一般にベルカーブ(bell curve)分布を呈する。たとえば、消去されたセルトランジスタ(論理値“1”を有する)のスレショルド電圧(Vth)は-3vと-1vとの間に分布され、一方、プログラムされたセルトランジスタ(論理値“0”を有する)のスレショルド電圧(Vth)は+1vと+3vとの間に分布される。

40

## 【0009】

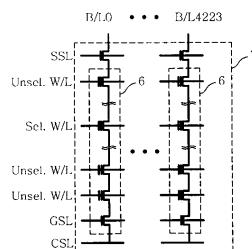

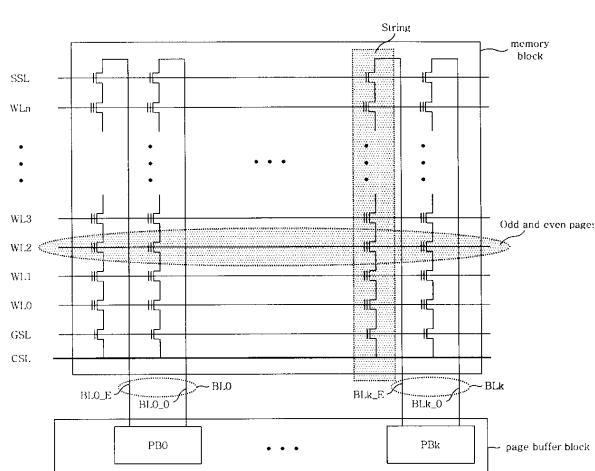

図3aを参照すれば、NANDフラッシュメモリは直列に連結されるフラッシュメモリセルトランジスタの“ストリング6”に特徴があるが、ここで、多数の並列ストリング6がフラッシュメモリのメモリブロック7を構成する。図示のように、各ストリング6は、メモリブロック7のビットライン(BL)に沿って直列に連結された複数のフラッシュメモリセルトランジスタからなる。ワードライン(WL)は、メモリブロック7のそれぞれ

50

の対応列のセルトランジスタの制御ゲートに連結される。たとえば、フラッシュメモリ装置は、それぞれのストリング6内に16個～32個のセルトランジスタを含み、それぞれのメモリブロック7内に4224個のストリング(B/L0、...、B/L4223)を含む。

#### 【0010】

各ストリング6の両端には、ストリング選択信号(SSL)およびグラウンド選択信号(GSL)を受信する制御ゲートを持つストリング選択トランジスタ(select transistor)がある。一般に、選択信号(SSL及びGSL)はセルトランジスタの読み出し(reading)とプログラミング(programming)とに用いられる。さらに、それぞれのストリング端には、各メモリブロック7のセルトランジスタストリング6のソースライン電圧を案内する共通ソースライン(CSL)がある。10

#### 【0011】

図3bの表は、消去、プログラムおよび読み出し動作に対し、図3aに示す信号の多様な電圧条件を一般的に示す。この表で、“Sel.W/L”はプログラムまたは読み出し動作が行われる選択されたワードラインを意味し、“Unsel.W/L”はメモリブロックの残りのワードラインを意味する。消去動作の場合、“Sel.W/L”は消去動作が行われる選択されたメモリブロックのワードラインを意味し、“Unsel.W/L”はメモリセルアレイ内の残りのメモリブロックのワードラインを意味する。

#### 【0012】

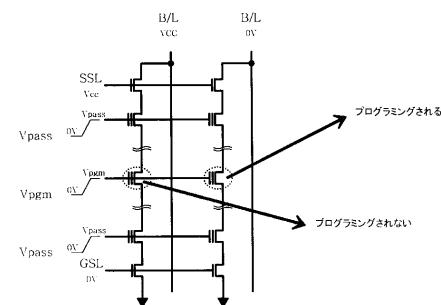

次に、NANDフラッシュプログラミング動作を図3bないし図4に基づいて説明する。ここで、ストリング選択信号(SSL)は電源電圧(VDD)に設定され、グラウンド選択信号(GSL)は0Vに設定され、共通ソースライン(CSL)電圧は接地電圧(VSS)と電源電圧(VDD)との間(たとえば、1.5V)に設定され、バルク(bulk)電圧は0Vに設定される。一般に、プログラミングは1回に1本のワードラインで起こり、よって、各プログラミング動作に対して一つのメモリブロック当たり1本のワードラインが選択される。ここで、選択されたワードライン(W/L)はプログラミング電圧(Vpgm)を受信し、一方、残りの選択されなかったワードライン(W/L)はバス電圧(Vpass)を受信する。ここで、プログラミング電圧(Vpgm)はバス電圧(Vpass)より大きい。プログラミング電圧(Vpgm)は、選択されたワードラインのあるセルトランジスタのビットライン(BL)電圧が0Vである時、FNトンネリングが結果として生ずる充分に高い電圧(たとえば、18V)である。すなわち、選択されたワードラインのあるセルトランジスタのビットライン(B/L)電圧が0Vである時、プログラム電圧(Vpgm)はFNトンネリングを始めるのに十分な電圧差を生成して、セルトランジスタをプログラミング状態に置かれるようにする。一方、あるセルトランジスタのビットライン(B/L)電圧が電源電圧(VDD)である時、FNトンネリングは不十分な電圧差(たとえば、10V)の結果として抑制される。よって、セルは“プログラム禁止”と呼ばれる。一方、バス電圧(Vpass)は選択されなかったトランジスタが導電状態に置かれるように充分に高いが、FNトンネリングを起こすほど高くはない。30

#### 【0013】

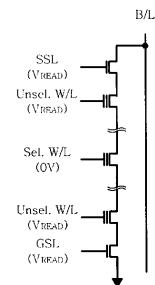

次に、図3bおよび図5を参照して、読み出し動作(reading operation)を説明する。この場合、ストリング選択信号(SSL)は読み出し電圧(Vread)に、グラウンド選択信号(GSL)は読み出し電圧(Vread)に、共通ソースライン(CSL)電圧は0Vに、かつバルク(bulk)電圧は0Vに設定される。プログラミング動作と同様に、読み出し動作は1回に典型的に1本のワードラインで起こり、よって、各読み出し動作に対して各メモリブロック当たり1本のワードラインが選択される。ここで、選択されたワードライン(W/L)は0Vに設定される。一方、残りの選択されなかったワードラインが読み出し電圧(Vread)を受信する。本実施例において、読み出し電圧(Vread)は4.5Vで、“1”と“0”セルトランジスタのスレショルド電圧分布を超過する。したがって、選択されなかったワードラインに連結されたセルトラン4050

ジスタは導電状態になる。一方、選択されたワードラインに印加された 0 V 電圧は“ 1 ”と“ 0 ”セルトランジスタのスレショルド電圧分布の間である。したがって、選択されたワードラインに連結された“ 1 ”セルトランジスタは導電性になり、一方、選択されたワードラインの残りのセルトランジスタは非導電性になる。その結果は、メモリブロックのビットライン (B / L) 間の電圧差である。

#### 【 0 0 1 4 】

図 3 b に示す表の例において、およそ 1.2 V のビットライン (B / L) 電圧は選択されたワードラインで“ 0 ”状態のセルトランジスタを有すると読まれ、0.8 V より小さなビットライン電圧は選択されたワードラインで“ 1 ”状態のセルトランジスタを有すると読まれる。

10

#### 【 0 0 1 5 】

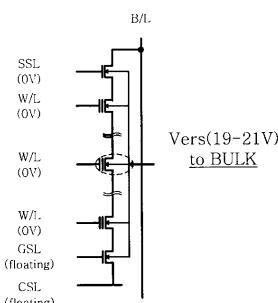

次に、図 3 b および図 6 を参照して、消去動作を説明する。この場合、ビットライン (B / L)、ストリング選択信号 (SSL)、グラウンド選択信号 (GSL)、共通ソースライン (CSL)、および選択されなかったメモリブロックのワードラインはすべてフローティング状態に設定される。一方、選択されたワードライン電圧は 0 V に設定され、バルク電圧は V<sub>erase</sub> (たとえば、19 ~ 21 V) に設定される。このようにして、ネガティブ電圧差が制御ゲートとバルクとの間に形成され、その結果、フローティングゲートと基板との間のゲート酸化層にわたって FN トンネリングが発生する。結果として、スレショルド電圧分布はプログラムされた“ 0 ”状態から消去された“ 1 ”状態に減少する。消去動作後には、選択されたメモリブロックのすべてのセルトランジスタは消去された“ 1 ”状態であることを念頭に留めおかなければならぬ。

20

#### 【 0 0 1 6 】

前述したように、メモリブロックの読み出しおよびプログラミングは 1 回に 1 本のワードラインで実行される。しかし、ある応用では、このような動作がメモリブロック内のページごとに実行されるというのがより正確である。このような概念を図 7 に一般的に示す。図示の例において、ビットライン (BL < k : 0 >) は偶数 (even) および奇数 (odd) ビットライン (BL\_E < k : 0 > および BL\_O < k : 0 >) に分けられる。各ワードラインのセルトランジスタはメモリブロックのページを構成し、図 7 の例で、各ワードラインはメモリブロックの偶数ページおよび奇数ページに連結される。後にもっと詳細に説明するように、ページバッファブロックに含まれるページバッファ (PB < k : 0 >) はフラッシュメモリブロックからの読み出しデータを伝送し、フラッシュメモリブロックにプログラムデータを伝送するために用いられる。通常、一つのページバッファ (PB) はそれぞれ奇数および偶数ビットライン対に備えられる。

30

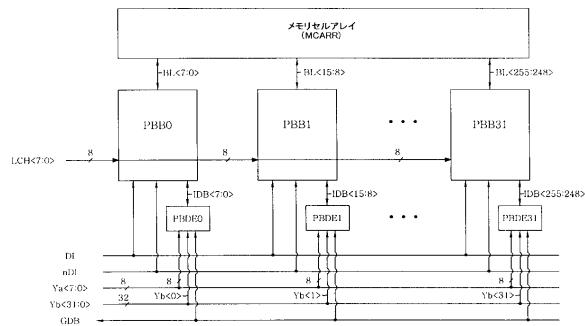

#### 【 0 0 1 7 】

図 8 は一例の NAND 型フラッシュメモリのコア要素を示すブロック図で、メモリのビットラインをアクセスするために、いわゆる“ Y-gating ” 技術が用いられる。図示のように、複数のページバッファブロック (PBB < 31 : 0 >) がビットライン (BL < 255 : 0 >) を介してメモリセルアレイ (MCCR) に連結される。それぞれのページバッファブロック (PBB) は 8 本のビットラインとインターフェースする。図 8 には示されていないが、図 7 に基づいて前述したように、各ビットライン (BL) は実際に一対の奇数および偶数ビットラインからなる。

40

#### 【 0 0 1 8 】

複数のページバッファデコーダ (PBDE < 31 : 0 >) は、対応するページバッファブロック (PBB < 31 : 0 >)、y アドレスライン (Ya < 7 : 0 >)、y アドレスライン (Yb < 31 : 0 >)、およびグローバルデータバス (GDB) に実効的に連結される。後にもっと詳細に説明するように、y アドレスライン (Ya < 7 : 0 >) は共通的にすべてのページバッファデコーダ (PBDE < 31 : 0 >) に印加され、一方、y アドレスライン (Yb < 31 : 0 >) のそれぞれは、対応するページバッファデコーダ (PBDE < 31 : 0 >) に印加される。すなわち、ページバッファデコーダ (PBDE0) は y アドレス (Ya < 7 : 0 > 及び Yb0) を受信し、ページバッファデコーダ (PBDE1)

50

) は  $y$  アドレス ( $Y_a < 7 : 0 >$  及び  $Y_b 1$ ) を受信する。そして、残りのページバッファに対しても、同一方式によりなされる。内部データライン ( $IDB < 255 : 0 >$ ) はページバッファブロック ( $PBB < 31 : 0 >$ ) とページバッファデコーダ ( $PBDE < 31 : 0 >$ )との間に連結される。図 8 の例では、8 本の内部データライン ( $IDB$ ) はそれぞれ対応ページバッファブロック ( $PBB$ ) 対とページバッファデコーダ ( $PBDE$ )との間に提供される。

#### 【0019】

また、データ入力選択信号 ( $DI$  及び  $nDI$ ) とラッチ信号 ( $LCH < 7 : 0 >$ ) とがページバッファブロック ( $PBB < 31 : 0 >$ ) に印加されるが、これらの機能は図 9 に基づいて後述する。

10

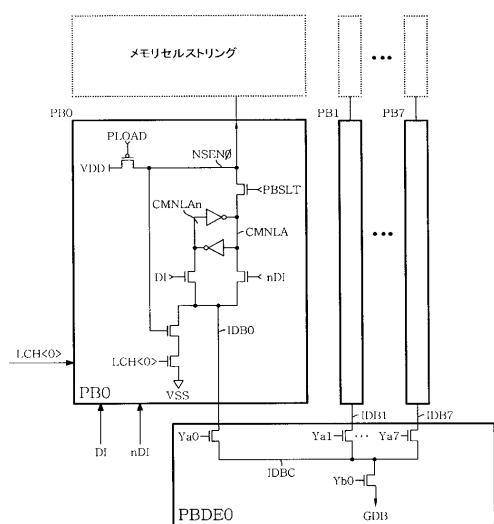

#### 【0020】

図 9 は図 8 に示すページバッファ ( $PB$ ) およびページバッファデコーダ ( $PBDE$ ) を説明するための回路図である。説明の便宜上、図 9 は並んでいる配置 (すなわち、ワードライン方向に並置された) ページバッファ ( $PB < 7 : 0 >$ ) を示す。しかし、実際には、ページバッファは、ほかのページバッファの上部に積層された構造となる (すなわち、ビットライン方向に並置される)。

#### 【0021】

図 9 のページバッファデコーダ ( $PBDE0$ ) は、グローバルデータバス ( $GDB$ ) と共に内部データライン ( $IDBC$ ) との間に連結された第 1 トランジスタと、共通内部データラインとページバッファ ( $< 7 : 0 >$ ) のそれぞれの内部ライン ( $IDB < 7 : 0 >$ ) との間に連結された複数の第 2 トランジスタとを含む。図示のように、第 1 トランジスタゲートは  $y$  アドレス信号 ( $Yb0$ ) を受信し、第 2 トランジスタの各ゲートは  $y$  アドレス信号 ( $Yb < 7 : 0 >$ ) を受信する。それで、 $y$  アドレス ( $Yb < 31 : 0 >$ ) はページバッファブロック ( $PBB < 31 : 0 >$ ) のなかでいずれか一つを選択するのに使用され、 $y$  アドレス ( $Ya < 7 : 0 >$ ) は選択されたページバッファブロック ( $PBB$ ) 内部のビットライン ( $BL$ ) を選択するのに使用されることは明白である。

20

#### 【0022】

ページバッファ ( $PB0$ ) は、ラッチノード ( $CMLA$ ) と反転されたラッチノード ( $CMLAn$ ) とを有するラッチ回路を含む。ページバッファ ( $PB0$ ) の第 1 および第 2 トランジスタデータ入力選択信号 ( $DI$  及び  $nDI$ ) によってそれぞれ制御され、このようなトランジスタは、内部データライン ( $IDB0$ ) と反転されたラッチノード ( $CMLAn$ ) およびラッチノード ( $CMLA$ ) との間にそれぞれ連結される。また、ほかのトランジスタはページバッファ選択信号 ( $PBSLT$ ) によって制御され、ラッチノード ( $CMLA$ ) とセンスノード ( $NSEN0$ ) との間に連結される。メモリセルアレイのメモリセルストリングに連結されるセンスノード ( $NSEN0$ ) は、ロード ( $load$ ) 制御信号 ( $LOAD$ ) によって制御されるほかのトランジスタの動作によって、選択的に電源電圧 ( $VDD$ ) に連結される。最後に、二つのトランジスタが内部データライン ( $IDB$ ) と基準電圧 ( $VSS$ ) との間に直列に連結される。このような二つのトランジスタのなかで、一つはセンスノード ( $NSEN0$ ) 上の電圧によって制御され、ほかの一つはラッチ信号 ( $LCH < 0 >$ ) によって制御される。

30

#### 【0023】

要約すれば、プログラミング動作において、ページバッファ ( $PB0$ ) のラッチ回路は、データ入力選択信号 ( $DI$  及び  $nDI$ ) と内部データライン ( $IDB$ ) の電圧によって指示される論理値を記憶し、その後、このような論理値 (すなわち、ラッチノード ( $CMLA$ ) で現れる電圧) はプログラミングのためにメモリセルストリングのビットラインに伝送される。これと類似の方式では、読み出し動作において、センスノード上の感知された電圧は一時的にラッチ回路に記憶され、ついで内部データライン ( $IDB$ ) を介してグローバルデータバス ( $GDB$ ) に伝送される。内部データライン ( $IDB$ ) は共有入力および出力ラインとして作用することを念頭に留めおかなければならない。

40

#### 【0024】

50

前記のような従来の不揮発性メモリ装置は多くの欠点を持っている。メモリ装置が高容量メモリに対する要求を満足するためにさらに集積されることによって、多様な回路のレイアウト面積が減少するため、このような従来の不揮発性メモリ装置の欠点は目立つ。このような欠点の全体リストを提供しないで、このような欠点の例を提示する。

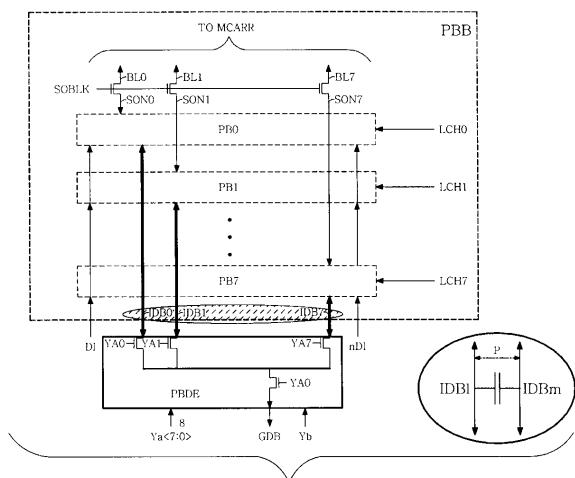

#### 【0025】

隣接した内部データライン間に寄生容量性カップリング (parasitic coupling) は、図10に示すような結果となることができる。前述したように、かつ図10に示すように、各ページバッファブロック (PBB) のページバッファ (PB <7:0>) はビットライン方向に、すなわち、ページバッファデコーダ (PBD E) とメモリセルアレイ (MCARR)との間に、積層される。たとえば、ページバッファデコーダ (PBD E) とメモリセルアレイ (MCARR)との間に配列される。また、センスノード遮断信号 (SOLK) によって制御され、センスノード (SON <7:0>) をビットライン (BL <7:0>) にそれぞれ選択的に連結させる多数のトランジスタが示されている。10

#### 【0026】

それぞれのページバッファ (PB) の内部データライン (IDB) のすべてはページバッファブロック (PBB) 内に互いに並列に延長される。ページバッファ (PB) のレイアウト面積が減少するにしたがい、隣接した内部データライン (IDB) のピッチ (P) がますます狭くなり、これにより、容量性カップリングが内部データライン (IDB) 間で増加する。隣接した内部データライン (IDB) 間で結果的に発生するカップリングノイズは信号の歪みとデータエラーとをもたらす。20

#### 【0027】

また、内部データライン (IDB) の大きい寄生性容量 (capacitance) は各ページバッファのラッチ回路の低い容量性ラッチノードとの電荷共有 (charge sharing) 条件を生成する場合もある。ある場合に、これは、データがフリップされる (flipped) 現象を誘発する。さらに、内部データライン (IDB) の高い出力負荷はページバッファの出力ドライビング能力の増加を要することになり、これは、空間と電圧源が制限されることを考慮する時、非常に深刻な問題となる。

#### 【0028】

また、図8を参照すれば、前述した例のバス領域は40本のyアドレスラインを含む。このように比較的多数のラインは、装置のバス領域に大きいレイアウト面積が伴わなければならない。30

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0029】

本発明の目的は、従来の不揮発性半導体メモリ装置の問題点を改善するためのもので、隣接した内部データ線間のカップリングノイズによる内部データ線のデータ歪み現象を減少させることができる不揮発性半導体メモリ装置およびこれに適用されるページバッファを提供することにある。

#### 【0030】

本発明のほかの目的は、カラムアドレスバスラインの数を減らして、必要なレイアウト面積を減少させる不揮発性半導体メモリ装置およびこれに適用されるページバッファを提供することにある。

#### 【課題を解決するための手段】

#### 【0031】

本発明の一面によれば、プログラムモードおよび読み出しモードで動作可能な不揮発性メモリ装置が提供される。前記メモリ装置は、複数の不揮発性メモリセル、複数のワードラインおよび複数のビットラインを持つメモリセルアレイを含む。前記メモリ装置は、前記メモリセルアレイのビットラインから読み出されるデータを出力するための内部データ出力ライン、および前記メモリセルアレイと前記内部データ出力ラインとの間に動作可能50

に連結されるページバッファをさらに含む。前記ページバッファは、前記ビットラインに選択的に連結されるセンシングノード；前記センシングノードに選択的に連結されるラッチノードを持つラッチ回路；前記ラッチノードの論理電圧を設定するラッチ入力バス；および前記ラッチ入力バスから分離され、前記ラッチノードの前記論理電圧による前記内部データ出力ラインの論理電圧を設定するラッチ出力バスを含む。

#### 【0032】

本発明のほかの一面によれば、複数の不揮発性メモリセルを含むメモリセルアレイ；前記メモリセルアレイの前記不揮発性メモリセルから読み出されるデータおよび前記メモリセルアレイの前記不揮発性メモリセルにプログラムされるデータを一時的に記憶するためのラッチ回路を含むページバッファ；前記メモリセルアレイから読み出されて前記ページバッファに一時的に記憶されるデータを出力する内部データ出力ライン；および前記内部データ出力ラインから分離され、データが前記メモリセルアレイの前記不揮発性メモリセルにプログラムされる時、およびデータが前記メモリセルアレイの前記不揮発性メモリセルから読み出される時、前記ラッチ回路を設定するラッチ入力バスを含む、不揮発性メモリ装置が提供される。10

#### 【0033】

本発明のさらにはかの一面によれば、複数の不揮発性メモリセルを含むメモリセルアレイ；前記メモリセルアレイの不揮発性メモリセルにプログラムされるデータを入力する入力データバス；前記入力データバスから分離され、前記メモリセルアレイの前記不揮発性メモリセルから読み出されるデータを出力する出力データバス；前記メモリセルアレイの前記不揮発性メモリセルから読み出されるデータおよび前記不揮発性メモリセルにプログラムされるデータを一時的に記憶するためのラッチ回路；前記出力データバスに連結される内部データ出力ライン；前記入力データバスに連結され、データが前記メモリセルアレイの前記不揮発性メモリセルにプログラムされる時、前記ラッチ回路を設定するラッチ入力バス；および前記ラッチ回路に一時的に記憶された読み出しデータを前記内部データ出力ラインに伝送する出力ドライブ回路を含む、不揮発性メモリ装置が提供される。20

#### 【0034】

本発明のさらにはかの一面によれば、不揮発性メモリ装置は、複数の不揮発性メモリセル、複数のワードラインおよび複数のビットラインを含むメモリセルアレイを含む。前記メモリ装置は、内部データ出力ライン、および前記メモリセルアレイと前記内部データ出力ラインに連結される複数のページバッファをさらに含む。前記ページバッファは、複数の並置されたページバッファを定義するために順次配列され、前記ページバッファのそれぞれは、前記メモリセルアレイから読み出されるデータを一時的に記憶するラッチ回路を含み、前記ラッチ回路と前記内部データ出力ラインとの間に連結されるアドレスゲートを含む。前記アドレスゲートは、前記内部データ出力ラインに前記各ページバッファのラッチ回路からのデータを選択的に出力するために、アドレス信号に応答する。30

#### 【0035】

本発明のさらにはかの一面によれば、不揮発性メモリ装置は、複数の不揮発性メモリセル、複数のワードラインおよび複数のビットラインを含むメモリセルアレイを含み、前記複数のビットラインは第1方向に長く延長される。前記メモリ装置は、前記メモリセルアレイから読み出されるデータを出力する、共有内部データ出力ライン；および前記メモリセルアレイ、前記共有内部データ出力ラインおよび前記複数の内部データ入力ライン間にそれぞれ動作可能に連結される複数のページバッファをさらに含む。40

#### 【0036】

本発明のさらにはかの一面によれば、不揮発性メモリ装置は、複数の不揮発性メモリセルを含むメモリセルアレイ、およびローカルデータ入力ラインとラッチ回路を含むページバッファを含む。前記ラッチ回路は、前記メモリセルアレイの前記不揮発性メモリセルから読み出されるデータおよび前記不揮発性メモリセルにプログラムされるデータを一時的に記憶するように、前記ローカルデータ入力ラインに応答する。前記メモリ装置は、外部入力信号を供給するグローバルデータ入力ラインをさらに含み、前記外部入力信号は前記50

メモリセルアレイをプログラムするためのプログラミング信号と前記メモリアレイを読み出すための制御信号を含み、前記ゲート回路に供給されるアドレス信号によって、前記ローカルデータ入力ラインに前記外部入力信号を選択的に出力するゲート回路を含む。

#### 【0037】

本発明のさらにはかの一面によれば、複数の不揮発性メモリセル、複数のワードラインおよび複数のビットラインを持つメモリセルアレイを含む不揮発性メモリ装置が提供される。前記メモリ装置は、前記メモリセルアレイから読み出されるデータを出力する内部データ出力ライン；前記メモリセルアレイと前記内部データ出力ラインとの間に動作可能に連結される複数のページバッファ；および前記複数のページバッファの少なくとも一つのゲート回路に動作可能に連結される複数のアドレスラインをさらに含む。

10

#### 【0038】

本発明のさらにはかの一面によれば、不揮発性メモリ装置のページバッファが提供される。前記ページバッファは、ラッチノードを含むラッチ回路；前記ラッチノードの電圧を制御する内部データ入力ライン；前記ラッチノードから電気的に隔離される内部データ出力ライン；および前記ラッチノードの前記電圧によって前記内部出力ラインの電圧を制御する出力ドライブ回路を含む。

#### 【0039】

本発明のさらにはかの一面によれば、電気的にプログラムおよび消去可能な複数のメモリセル、複数のワードライン、および複数のビットラインを持つメモリセルアレイを含む不揮発性半導体メモリ装置が提供される。前記メモリ装置は、複数のページバッファを含む少なくとも一つのページバッファブロックと内部データ出力ラインをさらに含む。前記ページバッファはそれぞれビットラインに連結され、それぞれは複数のバッファ選択信号のなかで少なくとも一つに応答してイネーブルされる。前記ページバッファのそれぞれはビットライン上のデータに対応して、自分のラッチノードに記憶する。前記内部データ出力ラインは前記複数のページバッファに共有され、イネーブルされるページバッファのラッチノード上のデータによってドライビングされる。前記内部データ出力ラインは前記ページバッファのラッチノードから電気的に隔離される。

20

#### 【発明の効果】

#### 【0040】

前記のような本発明の不揮発性半導体メモリ装置とこれに適用されるページバッファにおいて、内部出力ライン（I D O U T 0）はラッチノード（N L A T）およびバッファ入力バス（R B I N 1、R B I N 2）と電気的に隔離される。したがって、内部出力ライン（I D O U T 0）によってチャージされるほかのページバッファ（N W B U F < 7 : 1 >）のデータによって選択されるページバッファ（N W B U F 0）のラッチノード（N L A T）に記憶されるデータが歪む現象を根本的に遮断することができる。

30

#### 【0041】

本発明の不揮発性半導体メモリ装置においては、ビットライン遮断トランジスタがページバッファ（N W B U F 0）に含まれるように実現される。したがって、本発明の不揮発性半導体メモリ装置においては、各ページバッファのセンシングノード（N S E N 0）間の寄生キャパシタが発生する余地が著しく減少するので、センシングノード（N S E N 0）間のカップリングノイズが非常に小さくなる。また、各ページバッファのセンシングノードの長さがほぼ同一であるので、センシングノード間のセンシングマージンの均一性は著しく改善される。

40

#### 【0042】

一方、本発明の不揮発性半導体メモリ装置においては、512本のビットラインおよびページバッファをデコードしてデータの入出力を制御するが、必要なカラムアドレスのバスラインの数は合計24本である。従来技術と比較すると、本発明の不揮発性半導体メモリ装置で必要なカラムアドレスのためのバスラインの数は著しく減少する効果が発生する。よって、カラムアドレスのバスラインのためのレイアウト面積も著しく減少する。

#### 【0043】

50

また、本発明の不揮発性半導体メモリ装置において、内部出力ライン( I D O U T 0 )はページバッファ( N W B U F < 7 : 0 > )によって共有される。したがって、従来技術の各ページバッファの内部出力ライン( I D B < 7 : 0 > )間のライン対ラインキャパシタによるカップリングノイズ問題を除去することができる。

#### 【 0 0 4 4 】

本発明の不揮発性半導体メモリ装置によれば、内部出力ライン( D O U T 0 )がページバッファ( N W B U F < 7 : 0 > )の積層方向に伸張される。したがって、本発明の不揮発性半導体メモリ装置においては、内部出力ライン( I D O U T 0 )から各ページバッファ( N W B U F < 7 : 0 > )までの距離の差がほとんど消滅される。したがって、本発明の不揮発性半導体メモリ装置によれば、各ページバッファ( N W B U F < 7 : 0 > )間のデータローディングの均一性が著しく改善されて、センシングマージンの均一性が著しくよくなる。10

#### 【発明を実施するための最良の形態】

#### 【 0 0 4 5 】

本発明および本発明の動作上の利点および本発明の実施によって達成される目的を充分に理解するためには、本発明の好適な実施例を例示する添付図面および添付図面に記載された内容を参照しなければならない。各図面を理解するに際して、同一部材はできるだけ同一参照符号で示される。また、下記の説明で、具体的な処理流れのような多くの特定の詳細内容を本発明のより全般的な理解を提供するために説明する。しかし、これらの特定の詳細内容がなくても、本発明を実施することができるというには、当該技術分野で通常の知識を持った者には自明な事実である。そして、本発明の要旨を必要にあいまいにし得ると判断される公知機能および構成についての詳細な説明は省略する。20

#### 【 0 0 4 6 】

以下、添付した図面を参照して本発明の好適な非限定実施例を説明することにより、本発明を詳しく説明する。

図 1 1 は本発明の一実施例による不揮発性半導体メモリ装置の概略的なブロックダイアグラムである。

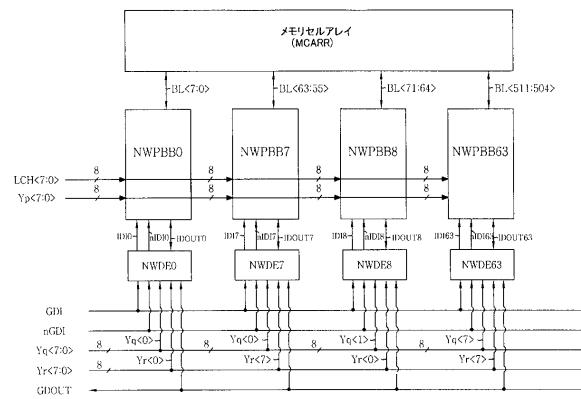

図 1 1 を参照すれば、本実施例の不揮発性半導体メモリ装置は、メモリセルアレイ( M C A R R )、ページバッファブロック( N W P B B < 6 3 : 0 > )、第 1 および第 2 グローバル入力ライン( G D I / n G D I )、グローバル出力ライン( G D O U T )、y アドレスライン( Y p < 7 : 0 > 、 Y q < 7 : 0 > および Y r < 7 : 0 > )、読み出しラッチ信号( L C H < 7 : 0 > )、およびページバッファデコーダ( N W D E < 6 3 : 0 > )を含む。30

#### 【 0 0 4 7 】

メモリセルアレイ( M C A R R )は、メモリセルのマトリックスアレイ、ワードライン( W L )( 図 1 1 には図示せず ) およびビットライン( B L < 5 1 1 : 0 > )を含む。本実施例において、メモリセルはフラッシュメモリセルトランジスタである。

内部入力ライン( I D I < 6 3 : 0 > および n I D I < 6 3 : 0 > )、および内部出力ライン( I D O U T < 6 3 : 0 > )は、ページバッファデコーダ( N W E D < 6 3 : 0 > )と対応ページバッファブロック( N W P B B < 6 3 : 0 > )との間に連結される。40

#### 【 0 0 4 8 】

第 1 グローバル入力ライン( G D I )と第 2 グローバル入力ライン( n G D I )は、所定の動作区間、たとえば読み出しモード( r e a d m o d e )、プログラムモード( p r o g r a m m o d e )、および消去モード( e r a s e m o d e )の間に相反した論理状態の入力データを伝送する。

後にもっと詳細に説明するように、ページバッファデコーダ( N W D E < 6 3 : 0 > )のそれぞれは、内部入力ライン( I D I < 6 3 : 0 > および n I D I < 6 3 : 0 > )のデータを出力するために、入力データ( G D I 及び n G D I )を y アドレスデータ( Y q < 7 : 0 > / Y r < 7 : 0 > )とともにデコードする。

また、ページバッファデコーダ( N W E D < 6 3 : 0 > )のそれぞれは内部出力ライン50

( I D O U T < 6 3 : 0 > ) 上のデータに対応するデータをグローバル出力ライン ( G D O U T ) に提供する。

#### 【 0 0 4 9 】

ページバッファブロック ( N W P B B < 6 3 : 0 > ) はラッチ信号ライン ( L C H < 7 : 0 > ) と y アドレス ( Y p < 7 : 0 > ) に応答する。後述するように、ページバッファブロック ( N W P B B < 6 3 : 0 > ) は、内部入力ライン ( I D I < 6 3 : 0 > および n I D I < 6 3 : 0 > ) 上に対応する入力データを一時的に記憶してからビットライン ( B L < 5 1 1 : 0 > ) に伝送し、また、ビットライン ( B L < 5 1 1 : 0 > ) 上のデータに対応する出力データを一時的に記憶してから内部出力ライン ( I D O U T < 6 3 : 0 > ) に伝送する機能をする。

10

#### 【 0 0 5 0 】

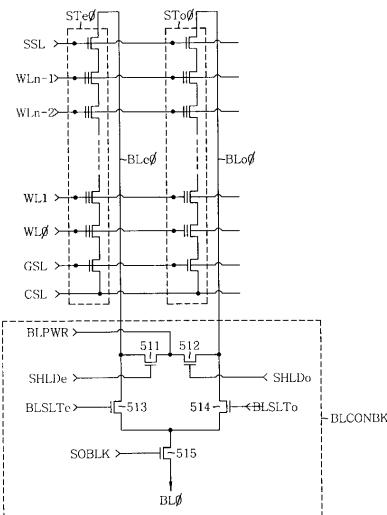

図 1 2 は本実施例による図 1 1 のメモリセルアレイ ( M C A R R ) の一部を示す図である。特に、図 1 2 は図 1 1 の第 1 ビットライン ( B L 0 ) のメモリセルストリングに関連した回路を示す。ビットライン ( B L < 5 1 1 : 1 > ) は同様に実現される。

前述したように、メモリセルアレイ ( M C A R R ) は、一般に、メモリセル ( M C ) のマトリックスアレイ、複数のワードライン ( W L < n - 1 : 0 > ) 、および複数のビットライン ( B L < 5 1 1 : 0 > ) を含む。前記実施例の不揮発性半導体メモリ装置のメモリセル ( M C ) は N A N D 型フラッシュメモリセルである。

#### 【 0 0 5 1 】

図 1 2 は図 1 1 のビットライン ( B L 0 ) を付勢する偶数および奇数ビットライン ( B L e 0 及び B L o 0 ) に連結される第 1 および第 2 ストリング ( S T e 0 及び S T o 0 ) を示す。各ストリング ( S T e 0 及び S T o 0 ) は、選択ライン ( S S L 及び G S L ) に連結されるメモリセルの両端に位置するトランジスタを含む。図示のように、選択ライン ( S S L 及び G S L ) は、ワードライン ( W L < n - 1 : 0 > ) に平行に伸びる。また、各ストリング ( S T e 0 及び S T o 0 ) は共通ソースライン ( C S L ) で終端される。

20

#### 【 0 0 5 2 】

偶数および奇数ビットラインはビットライン制御ブロック ( B L C O N B K ) に連結される。前述した図 1 1 の説明の便宜および簡便化のために、ビットライン制御ブロック ( B L C O N B K ) がメモリセルアレイ ( M C A R R ) の一部を形成すると説明した。しかし、ビットライン制御ブロック ( B L C O N B K ) はメモリセルアレイ ( M C A R R ) から分離されて区別される回路として示すこともできる。

30

#### 【 0 0 5 3 】

読み出し、プログラムおよび消去動作モードのそれぞれにおいて、ビットライン制御ブロック ( B L C O N B K ) は偶数ビットラインおよび奇数ビットライン ( B L e 0 及び B L o 0 ) のなかで一つを選択し、選択されたビットラインをビットライン ( B L 0 ) に連結する。このような動作は、センスノードブロッキング信号 ( S O B L K ) によって制御されるトランジスタ 5 1 5 、および偶数ビットライン選択信号 ( B L S L T e ) および奇数ビットライン選択信号 ( B L S L T o ) によってそれぞれ制御されるトランジスタ 5 1 3 、 5 1 4 によって行われる。

#### 【 0 0 5 4 】

40

さらに、ビットライン制御ブロック ( B L C O N B K ) は、読み出し、プログラムモードおよび消去動作モードで、偶数ビットライン ( B L e 0 ) および奇数ビットライン ( B L o 0 ) の電圧をプレチャージするか調節するように動作する。トランジスタ 5 1 1 、 5 1 2 をこのような目的で提供する。すなわち、トランジスタ 5 1 1 は、ビットラインパワー電圧 ( B L P W R ) を偶数ビットライン ( B L e 0 ) に選択的に連結するための偶数遮断信号 ( S H L D e ) に応答し、トランジスタ 5 1 2 はビットラインパワー電圧 ( B L P W R ) を奇数ビットライン ( B L o 0 ) に選択的に連結するための奇数遮断信号 ( S H L D o ) に応答する。

#### 【 0 0 5 5 】

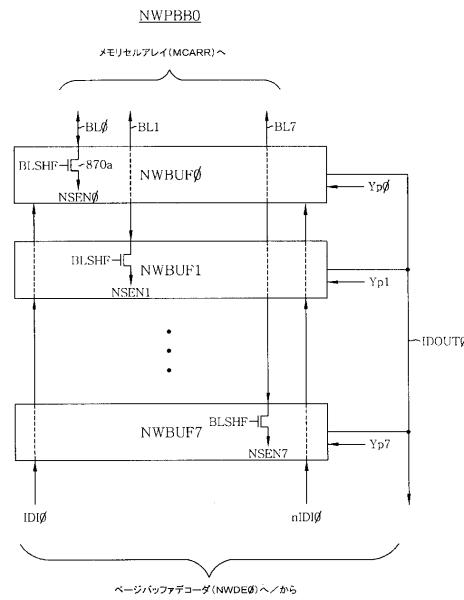

図 1 3 は図 1 1 に示すページバッファブロック ( N W P B B 0 ) の例を示す。残りのペ

50

ページバッファブロック (NWPBB < 63 : 1 >) も類似の構成を持つ。

図13のページバッファブロック (NWPBB0) は、複数のページバッファ (NWB

UF < 7 : 0 >)、内部出力ライン (IDOUT0)、第1内部入力ライン (IDI0)

および第2内部入力ライン (nIDI0) を含む。ページバッファ (NWB

UF < 7 : 0 >) は、ビットライン (BL < 7 : 0 >) に伝送されるデータおよびビットライン (BL

< 7 : 0 >) から受信されるデータをそれぞれ記憶する。

#### 【0056】

内部出力ライン (IDOUT0) はページバッファブロック (NWPBB0) に対する

共通内部出力ラインであって、ページバッファ (NWB

UF < 7 : 0 >) のなかでいずれか一つに記憶されたデータに対応する出力データを伝送する。

10

第1内部入力ライン (IDI0) および第2内部入力ライン (nIDI0) は、入力データに基づいて、ページバッファ (NWB

UF < 7 : 0 >) でのデータ記憶を制御する信号を供給する。

所要レイアウト面積を最小化するため、ページバッファブロック (NWPBB0) に含まれるページバッファ (NWB

UF < 7 : 0 >) は、積層構造、すなわちページバッファ

デコーダ (NWDE0) とメモリセルアレイ (MCARR) との間に並置される構造に配置される。

#### 【0057】

ページバッファブロック (NWPBB) のページバッファ (NWB

UF < 7 : 0 >) のそれは、内部入力ライン (IDI0 及び nIDI0) とビットライン (BL < 7 : 0

>) のなかで対応する一つとの間に連結される。また、前記ページバッファ (NWB

UF < 7 : 0 >) のそれは、対応するビットライン (BL < 7 : 0 >) をそれぞれのセン

スノード (NSEN < 7 : 0 >) に連結するビットライン遮断信号 (BLSHF) に応答

するトランジスタ (870a) を備える。

20

#### 【0058】

また、ページバッファ (NWB

UF < 7 : 0 >) のそれは、それぞれの y アドレス

信号 (Yp < 7 : 0 >) を受信する。従来のメモリ装置とは異なり、本実施例において、

このようなアドレス信号 (Yp < 7 : 0 >) はそれぞれのページバッファ (NWB

UF < 7 : 0 >) に直接的に連結される (図11参照)。後述するように、これは、メモリのバ

ス領域に提供されるラインの数を減らし、前記メモリの前記 y アドレスラインの総数を減

らす二重の利点をもたらす。ここで、アドレス信号 (Yp < 7 : 0 >) はバッファ選択信

号という。

30

#### 【0059】

図13に示すように、望ましくは、内部出力ライン (IDOUT0) は、ページバッファ

(NWB

UF < 7 : 0 >) が積層された方向に延長される。これにより、それぞれのペ

ージバッファ (NWB

UF < 7 : 0 >) から内部出力ライン (IDOUT0) までの伝送

ラインの距離の偏差が最小化される。これは、ページバッファ (NWB

UF < 7 : 0 >) から内部出力ライン (IDOUT0) にデータがロードされる時、信号の均一性を向上さ

せて、不揮発性メモリのセンシングマージン (sensing margin) を強化さ

せる。

40

#### 【0060】

また、本実施例では、内部出力ライン (IDOUT0) がページバッファ (NWB

UF < 7 : 0 >) によって共有される。このような構造による一つの利点は、従来のメモリ (図10

参照) での内部データライン (IDB < 7 : 0 >) の寄生的なカップリング (parasitic coupling) に関連する問題点を回避することができる

ある。

#### 【0061】

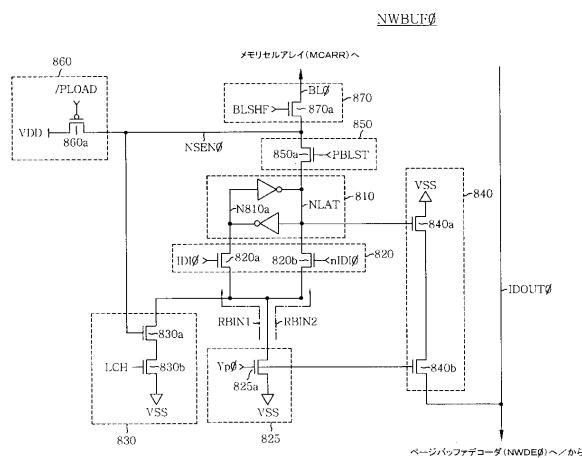

図14は図13のページバッファ (NWB

UF0) の一例を示す。残りのページバッファ (NWB

UF < 7 : 1 >) も同様に構成される。

図14に示すように、ページバッファ (NWB

UF0) は、センシングノード (NSE

50

N 0 )、ラッチユニット 8 1 0 、ラッチ伝送ユニット 8 2 0 、ラッチドライビングユニット 8 2 5 、センシング応答ユニット 8 3 0 、出力ドライビングユニット 8 4 0 、バッファ選択ユニット 8 5 0 、センシングセッティングユニット 8 6 0 、ピットライン遮断ユニット 8 7 0 、および内部出力ライン ( I D O U T 0 ) を含む。センシングノード ( N S E N 0 ) は、ピットライン ( B L 0 ) から提供されたデータを受信し、ピットライン遮断ユニット 8 7 0 を介してピットライン ( B L 0 ) に連結される。

#### 【 0 0 6 2 】

ピットライン遮断ユニット 8 7 0 は、ピットライン遮断信号 ( B L S H F ) に応答して、ピットライン ( B L 0 ) とセンシングノード ( N S E N 0 ) との連結を制御する。望ましくは、ピットライン遮断ユニット 8 7 0 はピットライン遮断トランジスタ 8 7 0 a を使用して実現され、ピットライン遮断トランジスタ 8 7 0 a はピットライン遮断信号 ( B L S H F ) に応答してゲートされる低電圧のN M O S トランジスタである。10

#### 【 0 0 6 3 】

ラッチユニット 8 1 0 は、ピットライン ( B L 0 ) のデータに対応するデータを記憶するラッチノード ( N L A T ) を含む。

ラッチドライビングユニット 8 2 5 は、所定のラッチドライビング電圧を提供するためには、バッファ選択アドレス ( Y p 0 ) に応答してイネーブルされる。本実施例で、ラッチドライビング電圧は接地電圧 ( V S S ) で、ラッチ伝送ユニット 8 2 0 に提供される第 1 および第 2 内部入力ライン ( I D I 0 および n I D I 0 ) 上のデータに独立的である。本実施例のラッチドライビングユニット 8 2 5 はラッチドライビングトランジスタ 8 2 5 a を含む。望ましくは、ラッチドライビングトランジスタ 8 2 5 a はバッファ選択アドレス ( Y p 0 ) に応答してゲートされ、接地 ( G R O U N D ) 電圧 ( V S S ) に連結されるソース端子を持つN M O S トランジスタである。20

#### 【 0 0 6 4 】

本実施例のラッチ伝送ユニット 8 2 0 は、第 1 および第 2 ラッチ伝送トランジスタ 8 2 0 a および 8 2 0 b を含む。第 1 ラッチ伝送トランジスタ 8 2 0 a は、第 1 内部入力ライン ( I D I 0 ) に応答して、ラッチドライビングトランジスタ 8 2 5 a から提供されるラッチドライビング電圧をラッチユニット 8 1 0 のノード N 8 1 0 a に提供する。望ましくは、第 1 ラッチ伝送トランジスタ 8 2 0 a はラッチドライビングトランジスタ 8 2 5 a に連結され、第 1 内部入力ライン ( I D I 0 ) 上のデータに応答してゲートされる。したがって、バッファ選択アドレス ( Y p 0 ) が論理 “ H ” 状態にある時、論理 “ H ” 状態のデータが第 1 内部入力ライン ( D I O ) に印加されれば、第 1 ラッチ伝送トランジスタ 8 2 0 a は、接地電圧 ( V S S ) をラッチユニット 8 1 0 のラッチノード N 8 1 0 a に提供する。30

#### 【 0 0 6 5 】

本実施例の第 2 ラッチ伝送トランジスタ 8 2 0 b は、第 2 内部入力ライン ( n I D I 0 ) に応答して、ラッチドライビングトランジスタ 8 2 5 a から提供されるラッチドライビング電圧をラッチユニット 8 1 0 のラッチノード ( N L A T ) に提供する。望ましくは、第 2 ラッチ伝送トランジスタ 8 2 0 b はラッチドライビングトランジスタ 8 2 5 a に直列に連結され、第 2 内部入力ライン ( n I D I 0 ) 上のデータに応答してゲートされる。したがって、バッファ選択アドレス ( Y p 0 ) が論理 “ H ” 状態にある時、論理 “ H ” 状態のデータが第 2 内部入力ライン ( n I D I 0 ) に印加されれば、第 2 ラッチ伝送トランジスタ 8 2 0 b は接地電圧 ( V S S ) をラッチユニット 8 1 0 のラッチノード ( N L A T ) に提供する。40

#### 【 0 0 6 6 】

すなわち、本実施例では、第 1 ラッチ伝送トランジスタ 8 2 0 a がターンオン ( O N ) になる時、論理 “ H ” のデータがラッチノード ( N L A T ) 上に記憶される。一方、第 2 ラッチ伝送トランジスタ 8 2 0 b がターンオン ( O N ) になる時、論理 “ L ” のデータがラッチノード ( N L A T ) 上に記憶される。

#### 【 0 0 6 7 】

50

図14において、参照符号R B I N 1およびR B I N 2は、ラッチドライビング電圧がラッチユニット810に伝送されるバッファ入力バスを示す。すなわち、ラッチドライビングトランジスタ825aおよび第1ラッチ伝送トランジスタ820aを通じてラッチノード(N L A T)に至る伝送バスは第1バッファ入力バス(R B I N 1)で示し、ラッチドライビングトランジスタ825aおよび第1ラッチ伝送トランジスタ820bを通じてラッチノード(N L A T)に至る伝送バスは第2バッファ入力バス(R B I N 2)で示す。

#### 【0068】

本実施例のセンシング応答ユニット830は、センシング応答電圧をラッチ伝送ユニット820に伝送するようにセンシングノード(N S E N O)によって駆動されて、ラッチノードに記憶されるデータを制御する。望ましくは、センシング応答電圧は接地電圧である。センシング応答ユニット830は、例として、センシング応答トランジスタ830aおよび出力センシングトランジスタ830bを含む。10

#### 【0069】

望ましくは、センシング応答トランジスタ830aは、センシングノード(N S E N O)上のデータに応答してゲートされるN M O Sトランジスタである。出力センシングトランジスタ830bはセンシング応答トランジスタ820aに直列に配列されるN M O Sトランジスタであり、接地電圧(V S S)に連結されるソース端子を持つ。センシング応答トランジスタ830aがターンオンされる時、出力センシングトランジスタ830bは、センシング応答電圧を、ラッチ伝送ユニット820を介してラッチユニット810に提供するように、読み出しラッチ信号(L C H)に応答する。また、ラッチノード(N L A T)は、センシング応答電圧に応答してセンシングノード(N S E N O)に対応するデータを記憶する。20

#### 【0070】

センシングセッティングユニット860は、センシングノード(N S E N O)を所定のセッティング電圧に設定する。本実施例において、セッティング電圧は電源電圧(V D D)であり、センシングセッティングユニット860はセンシングセッティングトランジスタ860aを含む。望ましくは、センシングセッティングトランジスタ860aは電源電圧に連結されるソース端子を持つP M O Sトランジスタであり、センシングセッティング信号(/ P L O A D)に応答してゲートされる。30

#### 【0071】

出力ドライビングユニット840は、バッファ選択アドレス(Y p 0)に応答してイネーブルされる。出力ドライビングユニット840は、イネーブルされる時、ラッチノード(N L A T)上に記憶されたデータに応答して内部出力ライン(I D O U T 0)を所定のドライブ電圧でドライブする。図14に示すように、内部出力ライン(I D O U T 0)は、ラッチノード(N L A T)およびバッファ入力バス(R B I N 1及びR B I N 2)から分離して電気的に隔離される。

#### 【0072】

出力ドライビングユニット840は、たとえば、第1出力ドライビングトランジスタ840aおよび第2出力ドライビングトランジスタ840bを含む。第1出力ドライビングトランジスタ840aは、ラッチユニット810のラッチノード(N L A T)上に記憶されたデータによってゲートされる。本実施例では、ラッチユニット810のラッチノード(N L A T)上に記憶されたデータが論理“H”である時、第1出力ドライビングトランジスタ840aはターンオン(O N)される。第2出力ドライビングトランジスタ840bは、第1出力ドライビングトランジスタ840aに直列に連結される。第2出力ドライビングトランジスタ840bは、内部出力ライン(I D O U T 0)をドライブ電圧でドライブするように、バッファ選択アドレス(Y p 0)に応答してゲートされる。本実施例において、ドライブ電圧は第1出力ドライビングトランジスタ840aのソース端子に連結される接地電圧(V S S)である。そこで、本実施例によれば、ラッチノード(N L A T)に記憶されたデータが論理“H”状態である時、内部出力ライン(I D O U T 0)は、4050

バッファ選択アドレス (Y p 0) が論理 “H” 状態に遷移されることに応答して、接地電圧 (V S S) にドライビングされる。

#### 【0073】

本実施例におけるバッファ選択ユニット 850 は、ラッチノード (N L A T) とのセンシングノード (N S E N 0) の連結を制御する。本実施例において、バッファ選択ユニット 850 はバッファ選択トランジスタ 850a を含み、バッファ選択トランジスタ 850a は、バッファ選択信号 (P B S L T) に応じてゲートされる N M O S トランジスタである。バッファ選択信号 (P B S L T) の電圧レベルが論理 “H” 状態に遷移される時、ラッチノード (N L A T) 上のデータはバッファ選択トランジスタ 850a を介してセンシングノード (N S E N 0) に伝送され、さらにビットライン (B L 0) に伝送される。

10

#### 【0074】

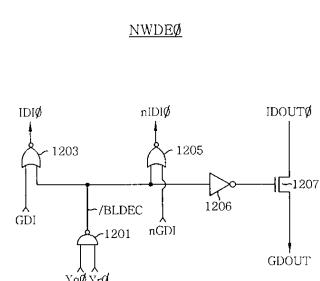

図 15 は図 11 に示すページバッファデコーダ (N W D E 0) の一例を示す。残りのページバッファデコーダ (N W D E <63:1>) も同様に構成できる。

ページバッファデコーダ (N W D E 0) は、二つの主な機能を持つ。一つ目、ページバッファデコーダ (N W D E 0) は、内部出力ライン (I D O U T 0) 上のデータに対応する出力データをグローバル出力ライン (G D O U T) に選択的に伝送する。二つ目、ページバッファデコーダ (N W D E 0) は、第 1 グローバル入力ライン (G D I) および第 2 グローバル入力ライン (n G D I) 上の入力データに対応するデータを第 1 内部入力ライン (I D I 0) および第 2 内部入力ライン (n I D I 0) にそれぞれ伝送する。

#### 【0075】

20

図 15 の例において、ページバッファデコーダ (N W D E 0) は、第 1 ~ 第 3 デコーダ論理ゲート 1201、1203 および 1205、インバータ 1206 およびデコーダトランジスタ 1207 を含む。

ここでは、y アドレス信号 (Y q <7:0>) はメイン選択アドレスといい、y アドレス信号 (Y p <7:0>) はサブアドレスという（図 11 参照）。

#### 【0076】

第 1 デコーダ論理ゲート 1201 は、メイン選択アドレス (Y q 0) とサブ選択アドレス (Y r 0) との論理演算を行い、論理演算の結果をブロックデコーディング信号 (/ B L D E C) で出力する。本実施例において、第 1 デコーダ論理ゲート 1201 は、メイン選択アドレス (Y q 0) とサブ選択アドレス (Y r 0) との N A N D 演算を行い、N A N D 演算の結果をブロックデコーディング信号 (/ B L D E C) として出力する。この場合、記メイン選択アドレス (Y q 0) とサブ選択アドレス (Y r 0) がともに論理 “H” 状態にアクティブになる時、ブロックデコーディング信号 (/ B L D E C) は論理 “L” 状態にアクティブになる。

30

#### 【0077】

第 2 デコーダ論理ゲート 1203 は、ブロックデコーディング信号 (/ B L D E C) に応答してイネーブルされ、第 1 グローバル入力ライン (G D I) 上のデータによる論理演算の結果を内部入力ライン (I D I 0) に提供する。本実施例において、第 2 デコーダ論理ゲート 1203 は、ブロックデコーディング信号 (/ B L D E C) と第 1 グローバル入力ライン (G D I) 上のデータに N O R 演算を行う N O R ゲートである。この場合、ブロックデコーディング信号 (/ B L D E C) が論理 “L” 状態である時（たとえば、メイン選択アドレス (Y q 0) とサブ選択アドレス (Y r 0) がともに論理 “H” 状態である時）、第 2 デコーダ論理ゲート 1203 は第 1 グローバル入力ライン (G D I) 上のデータを反転し、反転された結果を第 1 内部入力ライン (I D I 0) に提供する。

40

#### 【0078】

第 3 デコーダ論理ゲート 1205 はブロックデコーディング信号 (/ B L D E C) に応じてイネーブルされ、第 2 グローバル入力ライン (n I D I 0) 上のデータによる論理演算結果を第 2 内部入力ライン (n I D I 0) に提供する。本実施例において、第 3 デコーダ論理ゲート 1205 は、ブロックデコーディング信号 (/ B L D E C) と第 2 グローバル入力ライン (n G D I) 上のデータに N O R 演算を行う N O R ゲートである。この場合

50

、ブロックデコーディング信号が論理“L”状態である時（メイン選択アドレス（Y<sub>q</sub>0）とサブ選択アドレス（Y<sub>r</sub>0）がともに論理“H”状態である時）、第3デコーダ論理ゲート1205は第2グローバル入力ライン（nGDI）上のデータを反転し、反転されたデータを第2内部入力ライン（nIDI0）に提供する。

#### 【0079】

インバータ1206は、ブロックデコーディング信号（/BLDEC）を反転してデコーダトランジスタ1207をゲートする。本実施例において、デコーダトランジスタ1207は、ブロックデコーディング信号（/BLDEC）が論理“L”状態にアクティブになる時、内部出力ライン（IDOUT0）上のデータをグローバル出力ライン（GDOU10）に提供する。

#### 【0080】

本実施例において、不揮発性メモリは64個のページバッファデコーダ（NWE<63:0>）を含む。ページバッファデコーダ（NWE<63:0>）は、メイン選択アドレス（Y<sub>q</sub><7:0>）とサブ選択アドレス（Y<sub>r</sub><7:0>）の組合せに基づいて個別的に選択される。メイン選択アドレス（Y<sub>q</sub><7:0>）は、64個のページバッファデコーダ（NWE<63:0>）のなかで、それぞれが8個のバッファデコーダを持つ8グループの一つを選択するのに使用され、サブ選択アドレス（Y<sub>r</sub><7:0>）は、選択されたグループに含まれた8個のページバッファデコーダのなかでいずれか一つを選択するのに使用される。また、前述したように、バッファ選択アドレス（Y<sub>p</sub><7:0>）は、選択されたバッファデコーダと関連した8個のページバッファのなかで自分のものを選択するのに使用される。

#### 【0081】

このように、本実施例においては、カラムアドレスバスラインの総数が24本であるが、これは、図8に示す従来のメモリ装置の40本のカラムアドレスラインに比べて非常に有利である。

また、前述したように、内部出力ライン（IDOUT0）は、ラッチノード（NLAT）およびバッファ入力バス（RBIN1及びRBIN2）から電気的に隔離される。したがって、そうでなければほかのページバッファ（たとえば、“NWBUF<7:1>”）に記憶されたデータおよび内部出力ライン（IDOUT0）にチャージされたデータによって発生し得る、選択されたページバッファ（たとえば、“NWBUF0”）のラッチノード（NLAT）上に記憶されたデータの歪みが最小化できる。

#### 【0082】

前述した実施例の読み出し、プログラムおよび消去動作モードの例を説明する。下記の説明において、前述の図面を参照する。

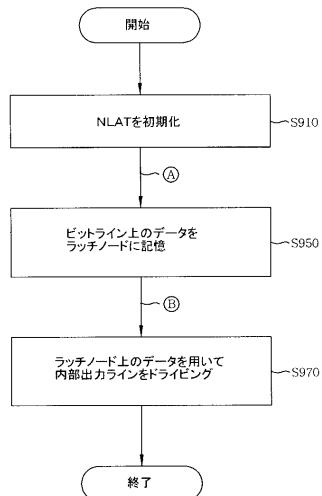

まず、読み出し動作モードを図16aおよび図16bに基づいて説明する。

図16aは選択されるメモリセル（MCsel）に記憶されたデータを出力するためのページバッファ（NWBUF）の駆動方法を説明するためのフローチャートである。（図12参照）

S910段階で、ラッチノード（NLAT）は論理“H”状態（“第1論理状態”）または論理“L”状態（“第2論理状態”）のデータに初期化される。ラッチノード（NLAT）の初期化は、第1内部入力ライン（IDI0）と第2内部入力ライン（nIDI0）のいずれか一つによって行うことができる。

#### 【0083】

本実施例のノーマル読み出し動作上のモードで、ラッチノード（NLAT）は第2論理状態のデータに初期化される。ラッチノードの第2論理状態への初期化のために、バッファ選択アドレス（Y<sub>p</sub>0）は論理“H”パルスになり、第2内部入力ライン（nIDI0）も論理“H”パルスになる。この際、第1内部入力ライン（IDI0）は論理“L”状態を維持する。すると、ラッチノード（NLAT）は、論理“L”状態、すなわち第2論理状態のデータに初期化される。

#### 【0084】

一方、本発明の実施例の消去確認読み出し動作モードで、ラッチノード（N L A T）は第1論理状態のデータに初期化される。ラッチノード（N L A T）の第1論理状態への初期化のために、バッファ選択アドレス（Y p 0）は論理“H”パルスになり、第1内部入力ライン（I D I 0）も論理“H”状態になる。この際、第2内部入力ライン（n I D I 0）は論理“L”状態を維持する。すると、ラッチノード（N L A T）は論理“H”状態、すなわち第1論理状態のデータに初期化される。

S 9 5 0 段階で、選択されるメモリセル（M C s e l）の記憶されるデータに対応して、ビットライン（B L 0）上でデベロープされる（d e v e l o p e d）データが、ラッチノード（N L A T）に記憶される。

#### 【0 0 8 5】

10

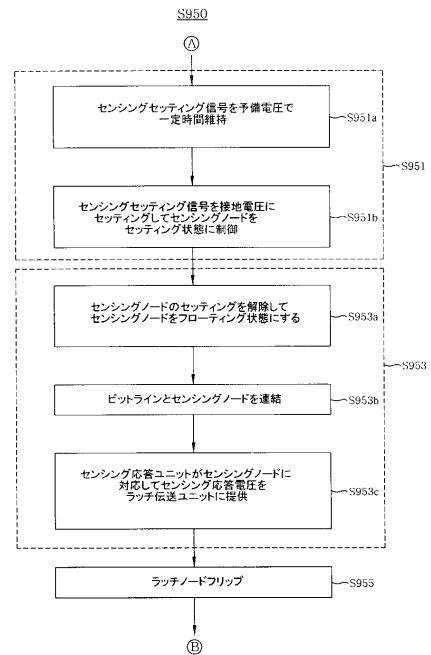

図16bは図16aのS 9 5 0 段階で実行できるS 9 5 1 段階、S 9 5 3 段階およびS 9 5 5 段階を説明するためのフローチャートである。本実施例において、S 9 5 1 a 段階の実行は望ましいと考えられるが、省略することもできる。

S 9 5 1 段階で、センシングノード（N S E N 0）は、センシングセッティングユニット8 6 0のセンシングセッティングトランジスタ8 6 0 aによって電源電圧（V D D）、すなわちセッティング電圧に制御される。セッティング電圧は、センシング応答電圧をラッチ伝送ユニット8 2 0に提供するように、センシング応答ユニット8 3 0を制御する。また、ビットライン遮断信号（B L S H F）は論理“L”状態に変化される。

#### 【0 0 8 6】

20

本実施例において、S 9 5 1 段階は、S 9 5 1 a 段階およびS 9 5 1 b 段階を含む。S 9 5 1 a 段階で、センシングセッティング信号（/ P L O A D）の電圧レベルは電源電圧（V D D）のアンダーシューティング（u n d e r s h o o t i n g）を防止するため、所定の時間の間、第1予備電圧（V P R E 1）に維持される。S 9 5 1 b 段階で、センシングセッティング信号（/ P L O A D）は論理“L”状態に遷移される。

#### 【0 0 8 7】

S 9 5 3 段階で、センシング応答ユニット8 3 0は、センシング応答電圧を、ビットライン（B L 0）上でデベロープされたデータに応答してラッチ伝送ユニット（8 2 0）に提供する。本実施例において、S 9 5 3 段階は、S 9 5 3 a 段階、S 9 5 3 b 段階およびS 9 5 3 c 段階を含む。

S 9 5 3 a 段階で、センシングセッティング信号（/ P L O A D）は論理“H”状態になる。これにより、センシングノード（N S E N 0）のセッティング状態は解除され、センシングノード（N S E N 0）はフローディング状態に遷移される。また、S 9 5 3 b 段階で、ビットライン遮断トランジスタ（8 7 0 a）はターンオンされ、フローディングされるセンシングノード（N S E N 0）はビットライン（B L 0）に連結される。したがって、センシングノード（N S E N 0）はビットライン（B L 0）上のデベロープされたデータを受信する。

#### 【0 0 8 8】

30

結果的に、選択されるメモリセル（M C s e l）が“オフセル”（O F F c e l l）の場合、センシングノード（N S E N 0）の電圧レベルはおよそ電源電圧（V D D）に維持される。一方、選択されるメモリセル（M C s e l）が“オンセル”（O N c e l l）の場合、センシングノード（N S E N 0）の電圧レベルはおよそ接地電圧（V S S）で維持される。

40

#### 【0 0 8 9】

S 9 5 3 c 段階で、センシング応答ユニット8 3 0は、センシングノード（N S E N 0）によってセンシング応答電圧をラッチ伝送ユニット（8 2 0）に選択的に提供する。すなわち、選択されるメモリセル（M C s e l）が“オフセル”（O F F c e l l）であり、センシングノード（N S E N 0）の電圧レベルがおよそ電源電圧（V D D）に維持される時、読み出しラッチ信号（L C H）が“H”パルスで発生されれば、センシング応答ユニット8 3 0はセンシング応答電圧（本実施例においては、“V S S”）をラッチ伝送ユニット8 2 0に伝送する。一方、選択されるメモリセル（M C s e l）が“オンセル”

50

(ONcel1)であり、センシングノード(SEN0)の電圧レベルがおよそ接地電圧(VSS)に維持される時、センシング応答電圧は、読み出しラッチ信号(LCH)が“H”パルスで発生しても、ラッチ伝送ユニット820に提供されない。

#### 【0090】

S955段階で、ラッチノード(NLAT)は、ラッチ伝送ユニット820に供給されるセンシング応答電圧に応答してフリップされる。

S910段階と関連して前述したように、ノーマル読み出し動作モードで、ラッチノード(NLAT)は第2論理状態のデータに初期化される。この際、S955段階で、第1内部入力ライン(IDI0)は論理“H”状態であり、第2内部入力ライン(nIDI0)は論理“L”状態である。したがって、選択されるメモリセル(MCsel)が“オフセル”、すなわちプログラムされたセルである時、ラッチノード(NLAT)は論理“L”状態(第2論理状態)から論理“H”状態(第1論理状態)にフリップされる。しかし、選択されるメモリセル(MCsel)が“オンセル”(ONcel1)、すなわち消去されたセルの場合、ラッチノード(NLAT)は論理“L”状態(第2論理状態)をそのまま維持する。10

#### 【0091】

一方、S910段階と関連して前述したように、消去確認読み出し動作モードで、ラッチノード(NLAT)は第1論理状態のデータに初期化される。この際、S955段階では、第1内部入力ライン(IDI0)は論理“L”状態であり、第2内部入力ライン(nIDI0)は論理“H”状態である。したがって、選択されるメモリセル(MCsel)が“オフセル”、すなわち、消去されなかったセルの場合、ラッチノード(NLAT)は論理“H”状態から論理“L”状態にフリップされる。一方、選択されるメモリセルが“オンセル”的場合、すなわち消去されたセルの場合、ラッチノード(NLAT)は論理“H”状態(第1論理状態)をそのまま維持する。20

#### 【0092】

また、図16aを参照すれば、S970段階で、出力ドライビングユニット840は、ラッチノード(NLAT)上に記憶されたデータによって制御される。したがって、内部出力ライン(IDOUT0)は、ドライブ電圧、すなわち接地電圧(VSS)に選択的にドライビングされる。すなわち、ラッチノード(NLAT)上に記憶されたデータが論理“H”的場合、内部出力ライン(IDIOUT0)は、バッファ選択アドレス(Yp0)に応答して接地電圧(VSS)にドライビングされる。しかし、ラッチノード(NLAT)上に記憶されるデータが論理“L”的場合には、内部出力ライン(IDIOUT0)は、バッファ選択アドレス(Yp0)が論理“H”状態に変化しても、初期論理状態の電源電圧(VDD)を維持する。30

ノーマル読み出し動作モードの例は、図17のタイミングダイアグラムを参照して以下にもっと詳細に説明する。

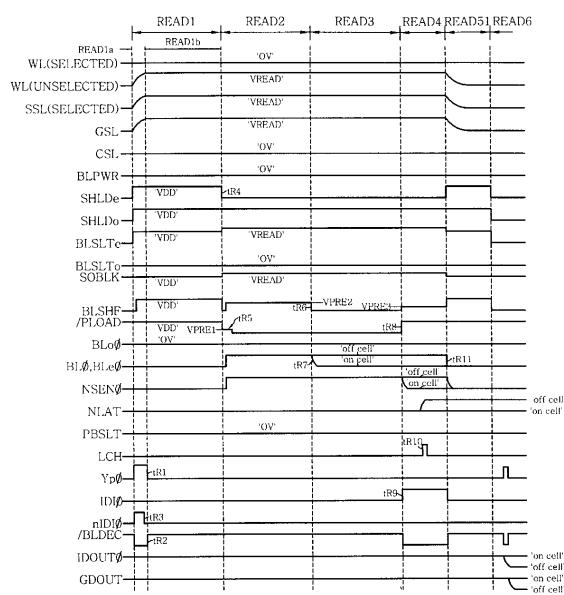

#### 【0093】

図17は図11～図15の実施例で示す不揮発性メモリ装置の多様な信号電圧およびノード電圧を示すノーマル読み出し動作モード(読み出しモード)のタイミングダイアグラムである。以下の説明でも、前述の図面を参照する。40

読み出しモードでは、選択されるメモリセル(MCsel)に記入されたデータが引き出され、そして引き出されたデータが出力される。

#### 【0094】

説明の目的上、図17に示す読み出しモードは6区間、すなわちビットラインディスチャージおよびページバッファリセット区間(以下、“READ1区間”という)、ビットラインプレチャージ区間(以下、“READ2区間”という)、ビットラインデベロープ区間(以下、“READ3区間”という)、センシング区間(以下、“READ4区間”という)、回復区間(以下、“READ5区間”という)、データ引き出し区間(以下、“READ6区間”という)の6個の区間に分けられる。

#### 【0095】

10

20

30

40

50

また、説明の目的上、“READ1区間”はページバッファリセット区間（以下、“READ1a区間”という）およびビットラインディスチャージ区間（以下、“READ1b区間”という）に分けられる。READ1a区間では、ページバッファのラッチノード（NLAT）が論理“L”状態、すなわち接地電圧（VSS）にリセットされる。以後、READ1b区間では、偶数ビットライン（BLE0）、奇数ビットライン（BLO0）およびビットライン（BL0）が接地電圧（VSS）、すなわち論理“L”状態のデータにディスチャージされる。

#### 【0096】

READ1a区間でのラッチノード（NLAT）のリセットは次のように起こる。READ1a区間で、バッファ選択アドレス（Yp0）は論理“H”状態であるので、ラッチドライビングトランジスタ825aは“ターンオン”である（tR1）。そして、メイン選択アドレス（Yq0）とサブ選択アドレス（Yr0）がともに論理“H”であるので、ロックデコーディング信号（/BLDEC）は論理“L”的状態に遷移される（tR2）。この際、第1グローバル入力ライン（GDI）は論理“H”であり、第2グローバル入力ライン（nGDI）は論理“L”である。したがって、第1内部入力ライン（IDI0）は論理“L”であり、第2内部入力ライン（nIDI0）は論理“H”である（tR3）。したがって、第1ラッチ伝送トランジスタ820aはターンオフされ、第2ラッチ伝送トランジスタ820bはターンオンされる。よって、ラッチユニット810のノードN810aは論理“H”に遷移され、ラッチノード（NLAT）は論理“L”状態にリセットされる。

#### 【0097】

READ1b区間でのビットライン（BLE0、BLO0及びBL0）のディスチャージを説明する。ここで、説明の便宜上、図12の左側メモリセルストリング（STE0）で最上位のメモリセル（MCsel）が選択されると仮定する。

“READ1b区間”では、読み出し電圧（VREAD、たとえば5V）が選択されないワードライン（WL<n-2:0>）に印加され、接地電圧（VSS）が選択されるワードライン（WLn-1）に印加される。そして、読み出し電圧（VREAD）がストリング選択ライン（SSL）およびグラウンド選択ライン（GSL）の両方に印加され、接地電圧（VSS）が共通ソースライン（CSL）に印加される。

#### 【0098】

そして、ビットライン電圧ライン（BLPWR）は接地電圧（VSS）を維持し、偶数シールディング信号（SHLD e）、奇数シールディング信号（SHLD o）、前記偶数ビットライン選択信号（BLSLT e）の電圧レベル、およびセンシングノードブロッキング信号（SOBLK）は電源電圧（VDD）に変化される。よって、ビットライン（BLE、BLO及びBL）は接地電圧（VSS）、すなわち論理“L”状態のデータにディスチャージされる。

ついで、READ2区間で、偶数ビットライン（BLE0）とビットライン（BL0）は、選択されるメモリセル（MCsel）のデータ値を感知するために、所定のプレチャージ電圧（たとえば、0.8V）にプレチャージされる。

#### 【0099】

そして、READ2区間で、第1電圧が選択されるワードライン（WLn-1）に印加され、第2電圧が残りの選択されないワードライン（WL<n-2:0>）に印加される。本実施例では、第1電圧は接地電圧（VSS）であり、第2電圧は前記読み出し電圧（VREAD）である。したがって、選択されるメモリセル（MCsel）のオン／オフの状態は自分に記憶されたデータによる。すなわち、選択されるメモリセル（MCsel）に記憶されたデータが論理“1”的場合、選択されるメモリセル（MCsel）は“オン”状態であり、記憶されたデータが論理“0”的場合、選択されるメモリセル（MCsel）は“オフ”状態である。

#### 【0100】

READ2区間で、偶数シールディング信号（SHLD e）は、偶数ビットライン（B

10

20

30

40

50

$L_{e0}$ )をビットライン電圧ライン( $B_{LPWR}$ )と連結するNMOSトランジスタ511を“ターンオフ”させるために、論理“L”になる( $tR4$ )。したがって、偶数ビットライン( $B_{Le0}$ )およびビットライン( $B_{L0}$ )のディスチャージ状態は解除される。この際、奇数シールディング信号( $SHLD_o$ )は電源電圧( $VDD$ )に維持され、NMOSトランジスタ512が“オン”状態を維持する。したがって、奇数ビットライン( $B_{Lo0}$ )は接地電圧( $VSS$ )に維持され、偶数ビットライン間の遮断ライン( $shielding$ )として機能する。

#### 【0101】

そして、センシングセッティング信号( $/LOAD$ )の電圧は電源電圧( $VDD$ )から所定の時間の間に第1予備電圧( $VPRE1$ )に下降し、以後、接地電圧( $VSS$ )に下降する( $tR5$ )。したがって、センシングセッティングトランジスタ860aはターンオンされ、センシングノード( $NSEN0$ )はセッティング電圧である電源電圧( $VDD$ )になる。10

#### 【0102】

本実施例によれば、センシングセッティング信号( $/LOAD$ )の予備電圧( $VPRE1$ )はおよそ1.0Vで、接地電圧( $VSS$ )と電源電圧( $VDD$ )との間の電圧である。センシングセッティング信号( $/LOAD$ )は、所定時間の間にアンダーシューティングにより招来されるパワーノイズ( $power noise$ )を減少させるために、第1予備電圧( $VPRE1$ )に維持される。

#### 【0103】

この際、ビットライン遮断信号( $BLSHF$ )は、電源電圧( $VDD$ )と接地電圧( $VSS$ )との間の電圧である第2予備電圧( $VPRE2$ )に遷移される。したがって、センシングノード( $NSEN0$ )とビットライン( $B_{L0}$ )は互いに電気的に連結される。前述したように、ビットライン遮断信号( $BLSHF$ )はビットライン遮断トランジスタ870aを第2予備電圧( $VPRE2$ )でゲートする。したがって、ビットライン( $B_{L0}$ 、 $B_{Le0}$ )は、センシングセッティングトランジスタ860aから提供される電流による特定レベルにプレチャージされる。ここで、特定レベルは、ビットライン遮断トランジスタ870aのスレショルド電圧の分だけ、第2予備電圧( $VPRE2$ )より低い。

#### 【0104】

また、ビットライン遮断トランジスタ870aを通じて十分な電流が流れるように、偶数ビットライン選択信号( $BLSLT_e$ )およびセンシングノードブロッキング信号( $SOLBK$ )の電圧レベルは読み出し電圧( $READ$ )に変化される。30

ついで、 $READ$ 3区間で、選択されるメモリセル( $MCell$ )に記憶されたデータを感知し、データをデベロープする過程が行われる。

#### 【0105】

より正確にいうと、 $READ$ 3区間で、ビットライン遮断信号( $BLSHF$ )は、ビットライン遮断トランジスタ870aを“ターンオフ”させるために、接地電圧( $VSS$ )である( $tR6$ )。したがって、ビットライン( $B_{L0}$ )は前記センシングノード( $NSEN0$ )から電気的に隔離され、ビットライン( $B_{L0}$ )はデータをデベロープするよう進行する。40

#### 【0106】

選択されるメモリセル( $MCell$ )が“オンセル”( $ONcell$ )の場合には、ビットライン( $B_{L0}$ )上のデータは共通ソースライン( $CSL$ )にディスチャージされる。したがって、ビットライン( $B_{L0}$ )の電圧レベルは接地電圧( $VSS$ )に近接する。一方、選択されるメモリセル( $MCell$ )が“オフセル”( $OFFcell$ )の場合には、ビットライン( $B_{L0}$ )の電圧レベルは実質的に変化しない(漏洩電流による影響は除外)。

#### 【0107】

センシングセッティングトランジスタ860aは $READ$ 3区間の大部分で“オン”( $ON$ )状態を維持するが、 $READ$ 3区間の終了直前にターンオフになる( $tR8$ )。こ50

の場合、センシングノード (NSENO) は電源電圧 (VDD) を維持している途中、フローティング状態になる。

ついで、READ4区間で、ビットライン (BL0) 上にデベロープされるデータ、すなわちビットラインの電圧レベルに対応するデータをページバッファ (NWBUF0) のラッチノード (NLAT) に記憶する過程が行われる。まず、“READ3”区間で生成されたセンシングノード (NSENO) のフローティング状態がそのまま維持される

ここで、READ3区間で生成されるセンシングノード (NSENO) のフローティング状態は、ビットライン遮断信号 (BLSHF) が第3予備電圧 (VPRE3) に変化されてビットライン遮断トランジスタ (870a) をターンオンさせる間、維持される。

#### 【0108】

本実施例によれば、第3予備電圧 (VPRE3) は接地電圧 (VSS) と電源電圧 (VDD) との間の電圧であり、センシングマージンに対応する所定の電圧差で、第2予備電圧 (VPRE2) より低い。したがって、センシングノード (NSENO) の電圧レベルはビットライン (BL0) 上にデベロープされる電圧レベルによって決定される。

この際、第1内部入力ライン (IDI0) 上のデータ値は論理 “H” 状態に遷移され (tR9)、第1ラッチ伝送トランジスタ (820a) は “ターンオン” される。

#### 【0109】

読み出しラッチ信号 (LCH) に応答して (tR10)、ラッチノード (NLAT) は、ビットライン (BL0) 上の電圧レベルによって決定されるセンシングノード (NSENO) 上のデータ、すなわち選択されるメモリセル (MCsel) に記憶されたデータに対応するデータを記憶する。

すなわち、選択されたメモリセル (MCsel) が “オンセル (ONcel1)” の場合には、ビットライン (BL0) とセンシングノード (NSENO) の電圧レベルはほぼ接地電圧 (VSS) である。したがって、読み出しラッチ信号 (LCH) が論理 “H” 状態にイネーブルされても、ラッチノード (NLAT) 上のデータは論理 “L” 状態を維持する。

#### 【0110】

一方、選択されたメモリセル (MCsel) が “オフセル (OFFcel1)” の場合には、ビットライン (BL0) とセンシングノード (NSENO) の電圧レベルが、漏洩電流によって、プレチャージ電圧から少し下降するかも知れないが、ビットライン遮断トランジスタ 870a は、第2および第3予備電圧 (VPRE2 及び VPRE3) との間の電圧差によって “ターンオン” することができないので、電圧レベルは論理 “H” 状態で維持される。したがって、読み出しラッチ信号 (LCH) が論理 “H” 状態にイネーブルされれば、ラッチノード (NLAT) 上のデータは論理 “H” 状態にフリップされる。

ついで、“READ5区間” で、ビットライン (BL0) とセンシングノード (NSENO) がリセットされる過程が行われる。

#### 【0111】

“READ5区間” で、偶数シールディング信号 (SHLD e) は電源電圧 (VDD) に変化され、偶数ビットライン選択信号 (BLSLT e) およびセンシングブロッキング信号 (SOBLK) はともに読み出し電圧 (VREAD) で電源電圧 (VDD) に変化される。したがって、ビットライン (BL0) とセンシングノード (NSENO) は接地電圧 (VSS) にリセットされる (tR11)。

#### 【0112】

そして、選択されなかったワードライン (WL<n-2:0>)、ストリング選択ライン (SSL)、グラウンド選択ライン (GSL) はすべて読み出し電圧 (VREAD) から接地電圧 (VSS) に遷移される。

ついで、READ6区間で、ラッチノード (NLAT) に対応するデータ (“READ4区間” で記憶されたデータ) が内部出力ライン (IDOUT0) を介してグローバル出力ライン (GDOU T) に出力される過程が行われる。

#### 【0113】

10

20

30

40

50

“READ 6 区間”で、バッファ選択アドレス (Yp0) およびロックデコーディング信号 (/BLDEC) はそれぞれのパルス形態に活性化される。そして、ラッチノード (NLAT) に対応するデータが内部出力ライン (IDOUT0) を介してグローバル出力ライン (GDOU1T) に伝送される。

#### 【0114】

本実施例で、グローバル出力ライン (GDOU1T) は、ロックデコーディング信号 (/BLDEC) が活性化される以前に、出力ラインプレチャージ回路 (図示せず) によって電源電圧 (VDD) にプレチャージされる。

選択されるメモリセル (MCsel) が“オンセル”(ONcel1) の場合には、ラッチノード (NLAT) 上のデータは論理 “L” であり、よって、グローバル出力ライン (GDOU1T) に伝送されたデータは論理 “H” 状態になる。一方、選択されるメモリセル (MCsel) が“オフセル”(OFFcel1) の場合には、ラッチノード (NLAT) のデータは論理 “H” であり、よって、グローバル出力ライン (GDOU1T) に伝送されたデータは論理 “L” 状態にディスチャージされる。

10

#### 【0115】

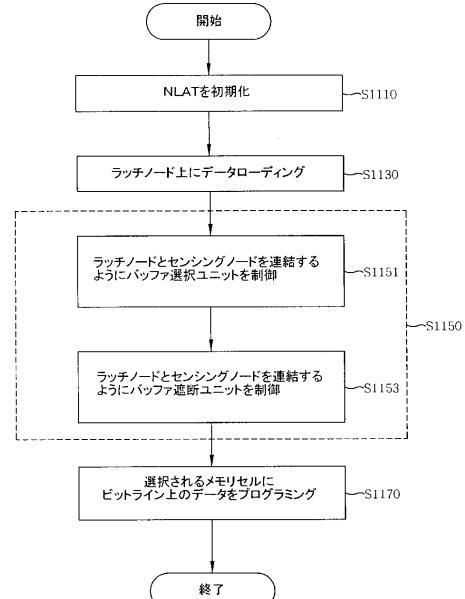

本発明の実施例によるプログラム動作上のモードを図18のフローチャートを参照して説明する。プログラムモードは、メモリセルアレイの選択されるメモリセル (MCsel) に入力データをロードする過程が行われる。

S1110段階で、ラッチノード (NLAT) が初期化される。ラッチノード (NLAT) は、第1内部入力ライン (IDI0) と第2内部入力ライン (nIDI0) のいずれか一つによって、第1論理状態 (すなわち、論理 “H” 状態) または第2論理状態 (すなわち、論理 “L” 状態) のデータに初期化される。本実施例で、ラッチノード (NLAT) は、第1内部入力ライン (IDI0) によって、第1論理状態 (すなわち、論理 “H” 状態) であるプログラム禁止 (inhibit) 状態に初期化される。

20

#### 【0116】

S1130段階で、第1内部入力ライン (IDI0) と第2内部入力ライン (nIDI0) のいずれか一つによって、ラッチ伝送ユニット820がラッチドライビングユニット825から提供される接地電圧 (VSS) であるラッチドライビング電圧をラッチユニット810に提供する。そして、ラッチユニット810はラッチドライビング電圧を用い、第1論理状態 (すなわち、論理 “H” 状態) または第2論理状態 (すなわち、論理 “L” 状態) のデータをラッチノード (NLAT) にロードする。

30

#### 【0117】

S1130段階でのデータローディング過程を詳細に説明すると、入力データが論理 “H” の場合には、バッファ選択アドレス (Yp0) が “H” パルスになり、第1内部入力ライン (IDI0) も “H” パルスになる。この際、第2内部入力ライン (nIDI0) は論理 “L” 状態を維持する。すると、ラッチノード (NLAT) は、論理 “H” 状態である、プログラム禁止状態を維持する。

#### 【0118】

一方、格納データが論理 “L” の場合には、バッファ選択アドレス (Yp0) は論理 “H” パルスになり、第2内部入力ライン (nIDI0) も “H” パルスになる。この際、第1内部入力ライン (IDI0) は論理 “L” 状態を維持する。すると、ラッチノード (NLAT) も論理 “H” 状態から論理 “L” 状態に変化される。

40

#### 【0119】

結果として、本実施例で、データローディングが行われる時、第1内部入力ライン (IDI0) と第2内部入力ライン (nIDI0) は相反する論理状態を持つ。バッファ選択アドレス (Yp0) が論理 “H” 状態である時、論理 “H” 状態のデータが第1内部入力ライン (IDI0) に伝送されれば、論理 “H” 状態のデータはラッチユニット810のラッチノード (NLAT) に記憶される。一方、論理 “H” 状態のデータが第2内部入力ライン (nIDI0) に伝送されれば、論理 “L” 状態のデータはラッチユニット810のラッチノード (NLAT) に記憶される。

50

## 【0120】

S1150段階で、ラッチノード(NLAT)にロードされるデータがビットライン(BL0)に伝送される。このような過程は、下記のS1151段階とS1153段階でより詳しく説明する。

S1151段階で、バッファ選択ユニット850は、ラッチノード(NLAT)をセンシングノード(SEN0)、究極にはビットライン(BL0)に連結するように制御される。すなわち、バッファ選択信号(PBSLT)は、バッファ選択トランジスタ850aをターンオンするために、論理“H”レベルになる。すると、ラッチノード(NLAT)上のデータはセンシングノード(SEN0)に伝送される。

## 【0121】

10

S1153段階で、ビットライン遮断ユニット870は、センシングノード(SEN0)をビットライン(BL0)に連結するように制御される。より詳しく説明すれば、本実施例で、ビットライン遮断信号(BLSHF)は、ビットライン遮断トランジスタ870aをターンオンするために論理“H”レベルになる。すると、前記センシングノード(SEN0)のデータがビットライン(BL0)に伝送される。

S1170段階で、ビットライン(BL0)に伝送されるデータに対応して、選択されるメモリセル(MCsel)はプログラムされる。

## 【0122】

プログラムモードの例は図19のタイミングダイアグラムを参照して以下にもっと詳細に説明する。

20

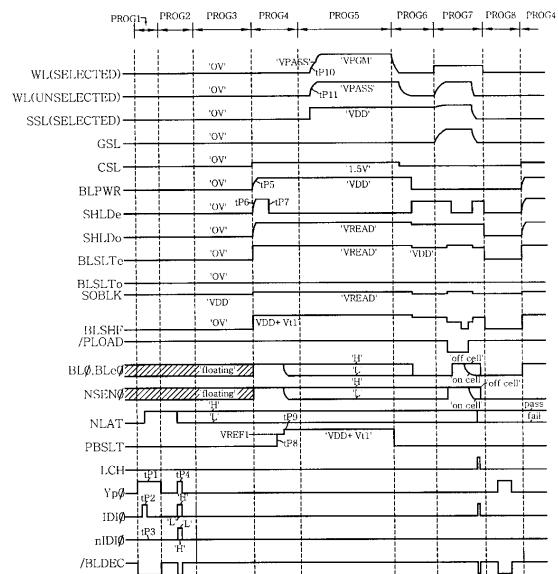

図19は、図11～図15に示す不揮発性メモリ装置の多様な信号電圧とノード電圧を示すプログラムモードタイミングダイアグラムである。以下の説明でも、前述の図面を参考する。

## 【0123】

説明の目的上、図19のタイミングダイアグラムは8個の区間、すなわち、ページバッファセットアップ区間(以下、“PROG1区間”という)、データローディング区間(以下、“PROG2区間”という)、高電圧イネーブル区間(以下、“PROG3区間”という)、ビットラインセットアップ区間(以下、“PROG4区間”という)、プログラム実行区間(以下、“PROG5区間”という)、回復区間(以下、“PROG6区間”という)、確認読み出し区間(以下、“PROG7区間”という)およびY-スキャン区間(以下、“PROG8区間”という)に分けられる。

30

## 【0124】

“PROG1区間”では、外部から印加されるデータをロードする以前に、ラッチノード(NLAT)はプログラム禁止状態に制御される。本実施例で、“プログラム禁止状態”は、外部から印加される特定データに対しては、セルプログラミング(cell\_programming)の実行が要求されない状態をいう。本実施例では、論理“H”状態のデータが外部から入力される場合には、セルプログラミングが要求されない。

## 【0125】

本実施例で、“PROG1区間”で、バッファ選択アドレス(Yp0)は、ラッチドライビングトランジスタ825aをターンオンするため、論理“H”状態である(tP1)。そして、メイン選択アドレス(Yq0)とサブ選択アドレス(Yr0)がともに論理“H”状態であるので、ロックデコーディング信号(/BLDEC)は論理“L”状態にアクティブになる。この際、第1グローバル入力ライン(GDI)は論理“L”状態を持つアクティブパルスであり、第2グローバル入力ライン(nGDI)は論理“H”状態である。したがって、第1内部入力ライン(IDI0)は論理“H”状態を持つアクティブパルスであり(tP2)、第2内部入力ライン(nIDI0)は論理“L”状態である。したがって、第1ラッチ伝送トランジスタ820aは一時的にターンオンされ、第2ラッチ伝送トランジスタ820bは“オフ(off)”状態になる。このような方法により、ラッチノード(NLAT)は“プログラム禁止状態”、たとえば、論理“H”状態に設定される。

40

50

## 【0126】

ついで、“PROG2区間”で、外部から印加されるデータが前記ページバッファ(NWBUFF0)のラッチノード(NLAT)上にロードされる過程が行われる。

“PROG2区間”では、第1内部入力ライン(IDI0)または第2内部入力ライン(nIDI0)に応答して、外部から入力されるデータに対応するデータがラッチノード(NLAT)に記憶される。そして、ラッチノード(NLAT)に記憶されるデータはバッファ入力バス(RBIN1、RBIN2)を通じて提供される。第1内部入力ライン(IDI0)に応答してラッチノード(NLAT)上に記憶されるデータの論理状態は、第2内部入力ライン(nIDI0)に応答してラッチノード(NLAT)上に記憶されるデータの論理状態と相反する。すなわち、本実施例において、第1内部入力ライン(IDI0)に応答してラッチノード(NLAT)に記憶されるデータは論理“H”であり、第2内部入力ライン(nIDI0)に応答して前記ラッチノード(NLAT)に記憶されるデータは論理“L”である。10

## 【0127】

“PROG2区間”の時点“tP4”で、バッファ選択アドレス(Yp0)は論理“H”である。メイン選択アドレス(Yq0)およびサブ選択アドレス(Yr0)がともに論理“H”であるので、ブロックデコーディング信号(/BLEDCE)は論理“L”である。この際、第1グローバル入力ライン(GDI)または第2グローバル入力ライン(nGDI)は論理“H”状態に遷移される。

すなわち、入力データが論理“L”であれば、第1グローバル入力ライン(GDI)は論理“H”状態に変化される。より正確にいうと、第1内部入力ライン(IDI0)は論理“L”状態に変化され、第2内部入力ライン(nIDI0)は論理“H”状態に変化される。したがって、論理“L”状態のデータが前記ラッチノード(NLAT)上に記憶される。20

## 【0128】

一方、入力されるデータが論理“H”であれば、第2グローバル入力ライン(GDI)は論理“L”状態に変化される。より正確にいうと、第2内部入力ライン(nIDI0)は論理“L”状態に変化され、第1内部入力ライン(IDI0)は論理“H”状態に変化される。したがって、論理“H”状態のデータがラッチノード(NLAT)上に記憶される。30

## 【0129】

ついで、“PROG3区間”が行われる。ここで、不揮発性半導体メモリ装置に内蔵される高電圧ポンピング回路のグループがイネーブルされる。一般に、このような回路は、電源電圧(VDD)より非常に高い電圧を発生するためのものである。本実施例において、高電圧ポンピング回路グループは、プログラム電圧(VPGM、たとえば20V)、バス電圧(VPASS、たとえば7~9V)、読み出し電圧(VREAD、たとえば5V)などを発生する回路を含む。そして、高電圧ポンピング回路グループは、ローデコーダ(図示せず)によって用いられるブースティング電圧を発生する回路を含むこともできる。参考として、本実施例で、電源電圧(VDD)はおよそ2.2Vである。

## 【0130】

“PROG4区間”では、選択されるメモリセル(MCsel)に連結される偶数ビットライン(BLe0)、すなわち選択されるビットラインがラッチノード(NLAT)に記憶されるデータに対応する電圧レベルに制御される。そして、選択されるメモリセル(MCsel)に連結されない奇数ビットライン(BLo0)、すなわち選択されないビットラインはプログラム禁止状態に制御される。40

## 【0131】

また、“PROG4区間”で、ビットライン電圧ライン(BLPWR)の電圧レベルは前記電源電圧(VDD)に上昇する(tP5)。そして、前記偶数シールディング信号(SHLDe)と奇数シールディング信号(SHLDo)の電圧レベルは読み出し電圧(VREAD)に上昇する(tP6)。したがって、電圧降下(voltage drop)50

なしに、偶数ビットライン（B L e 0）と奇数ビットライン（B L o 0）の電圧レベルは、ビットライン電圧ライン（B L P W R）の電圧である、電源電圧（V D D）に変化される。

#### 【0132】

そして、偶数ビットライン選択信号（B L S L T e）およびセンシングノードブロッキング信号（S O B L K）も読み出し電圧（V R E A D）に上昇する。ビットライン遮断信号（B L S H F）の電圧レベルは“V D D + V t 1”に上昇する。本実施例で、“V t 1”はおよそ1.5Vの所定の電圧である。

そして、“PROG4区間”の時点（t P 7）で、所定の時間が経過した後、偶数シールディング信号（S H L D e）の電圧レベルはさらに接地電圧（V S S）に低下する。

10 そして、バッファ選択信号（P B S L T）は第1基準電位（V R E F 1）に変化された後（t P 8）、さらに第5電圧に変化される（t P 9）。本実施例において、第5電圧は“V D D + V t 1”と同一であり、第1基準電位（V R E F 1）はおよそ1.3Vで、接地電圧（V S S）と第5電圧との間の電圧である。

#### 【0133】

ラッチノード（N L A T）上に記憶されるデータは、選択されるメモリセル（M C s e 1）に連結される偶数ビットライン（B L e 0）に伝送される。すなわち、ラッチノード（N L A T）上に記憶されるデータが論理“L”的場合、偶数ビットライン（B L e 0）は“0V”になる。そして、ラッチノード（N L A T）上に記憶されるデータが論理“H”的場合、偶数ビットライン（B L e 0）は電源電圧（V D D）を維持する。

20

ついで、“PROG5区間”で、偶数ビットライン（B L e 0）に伝送されるデータを選択されるメモリセル（M C s e 1）に記憶する過程が行われる。

#### 【0134】

バス電圧（V P A S S）が所定の時間の間に選択されたワードライン（W L n - 1）に印加された後、第3電圧であるプログラム電圧（V P G M）が選択されたワードライン（W L n - 1）に印加される（t P 10）。プログラム電圧（V P G M）は、偶数ビットライン（B L e 0）、すなわちビットライン（B L 0）の電圧レベルに対応するデータを、選択されるメモリセル（M C s e 1）にプログラムされるようとする。そして、バス電圧（V P A S S）が選択されないワードライン（W L < n - 2 : 0 >）に印加される（t P 11）。したがって、選択されないメモリセル（M C）はプログラミングなしに“オン”状態を維持する。

30

#### 【0135】

“PROG5区間”で、偶数ビットライン（B L e 0）に伝送されるデータが“H”的場合には、プログラム禁止状態が維持される。一方、偶数ビットライン（B L e 0）に伝送されるデータが論理“L”的場合には、選択されるメモリセル（M C s e 1）はF Nトンネリングによってプログラムされる。したがって、本実施例において、論理“L”状態のデータが記憶されるメモリセル（M C s e 1）は“プログラムされたセル”として設計できる。

#### 【0136】

また、“PROG5区間”で、ストリング選択ライン（S S L）は電源電圧（V D D）、グラウンド選択ライン（G S L）は接地電圧（V S S）、そして共通ソースライン（C S L）はおよそ1.5Vの電圧を持つ。

40

ついで、“PROG6区間”で、ワードライン（W L < n - 1 : 0 >）、ビットライン（B L 0、B L e 0、B L o 0）およびセンシングノード（N S E N O）が接地電圧（V S S）にディスチャージされる過程が行われる。

#### 【0137】

すなわち、“PROG6区間”で、ビットライン電圧ライン（B L P W R）は接地電圧（V S S）を維持する。また、偶数シールディング信号（S H L D e）、奇数シールディング信号（S H L D o）、偶数ビットライン選択信号（B L S L T e）、センシングノードブロッキング信号（S O B L K）およびビットライン遮断信号（B L S H F）は電源電

50

圧( V D D )に変化される。したがって、ワードライン( W L < n - 1 : 0 >)、ピットライン( B L 0 、 B L e 0 および B L o 0 )およびセンシングノード( N S E N 0 )は接地電圧( V S S )にディスチャージされる。

そして、バッファ選択信号( P B S L T )が接地電圧( V S S )に変化されるように、ピットライン( B L 0 )とラッチノード( N L A T )は電気的に隔離される。

#### 【 0 1 3 8 】

“ P R O G 7 区間 ” では、メモリセル( M C s e l )にプログラムされるデータを感知するための過程が行われる。

“ P R O G 7 区間 ” で行われる動作は、前述した読み出しモードで行われる動作とほぼ同一である。しかし、“ P R O G 7 区間 ” は、所定の確認読み出し電圧が前記選択されるワードライン( W L n - 1 )に印加されるという点と、ページバッファ( N W B U F 0 )のリセットされる動作が省略できるという点で、読み出しモードと異なる。“ P R O G 7 区間 ” で行われる残りの動作は読み出しモードの動作に似ているので、それについての説明は、重複内容の説明を避けるために省略する。

10

#### 【 0 1 3 9 】

ついで、“ P R O G 8 区間 ” では、“ P R O G 7 区間 ” でラッチノード( N L A T )上に記憶されるデータを用いて、選択されるメモリセル( M C s e l )が正しくプログラムされたかを確認する過程が行われる。

すなわち、“ P R O G 8 区間 ” では、ラッチノード( N L A T )上に記憶されるデータが論理 “ H ” の場合には、論理 “ L ” 状態のデータがグローバル出力ライン( G D O U T )に出力されて、バス( p a s s )信号が発生する。そして、ラッチノード( N L A T )上のデータが論理 “ L ” の場合には、論理 “ H ” 状態のデータがグローバル出力ライン( G D O U T )に出力されて、不良( f a i l )信号が発生する。

20

#### 【 0 1 4 0 】

不良信号が“ P R O G 8 区間 ” で発生する時、“ P R O G 4 区間 ” から“ P R O G 8 区間 ”までのプログラムループが繰り返される。結果として、バス信号が発生する時、プログラムモードが完了する。

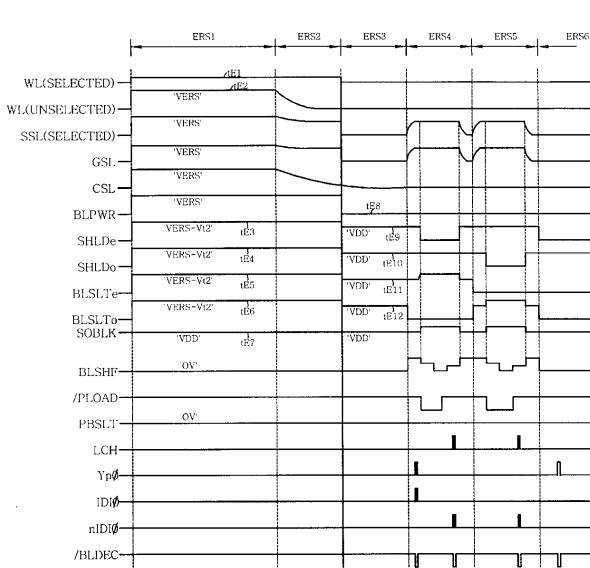

消去動作上のモード( 消去モード )の例を図 2 0 のタイミングダイアグラムに基づいて以下に説明する。

#### 【 0 1 4 1 】

図 2 0 は、図 1 1 ~ 図 1 5 の例で示す前記不揮発性半導体メモリ装置の多様な信号電圧とノード電圧とを示す消去モードタイミングダイアグラムである。以下の説明でも、前述の図面を参照する。

30

説明の目的上、図 2 0 の消去モードタイミングダイアグラムは 6 区間、すなわち消去実行区間( 以下、“ E R S 1 区間 ” という )、第 1 回復区間( 以下、“ E R S 2 区間 ” という )、第 2 回復区

間( 以下、“ E R S 3 区間 ” という )、第 1 確認読み出し区間( 以下、“ E R S 4 区間 ” という )、第 2 確認読み出し区間( 以下、“ E R S 5 区間 ” という )および Y - スキャン区間( 以下、“ E R S 6 区間 ” という )に分けられる。

40

#### 【 0 1 4 2 】

“ E R S 1 区間 ” では、消去電圧( V E R S )がメモリセル( M C )のバルク( b u l k )に印加され、第 6 電圧は選択される対応メモリセルからのデータを消去するためにワードラインに印加される。本実施例で、消去電圧( V E R S )はおよそ 2 0 V であり、第 6 電圧は約 0 . 3 V である( t E 1 )。そして、選択されないワードラインはフローティング状態に制御される。このような選択されないワードラインの電圧はバルク上のカップリングによってほぼ消去電圧( V E R S )になる( t E 2 )。したがって、消去動作は前記選択されないワードラインに連結されるメモリセルでは行われない。

#### 【 0 1 4 3 】

また、“ E R S 1 区間 ” で、偶数シールディング信号( S H L D e )、奇数シールディング信号( S H L D o )、偶数ビットライン選択信号( B L S L T e )および奇数ビット

50

ライン選択信号 (BLSLT<sub>0</sub>) は “VERS-Vt2” になり (tE3 ~ tE6) 、センシングノードブロック信号 (SOBLK) は電源電圧 (VDD) を維持する (tE7) 。この際、 “Vt2” は、高電圧NMOSトランジスタスレショルド電圧を意味する。本実施例では、 “Vt2” がおよそ 1.3V である。

#### 【0144】

ついで、“ERS2区間”と“ERS3区間”では、選択されるメモリセルに記憶される前記データを感知するために、メモリセル (MC) のバルク (bulk) とビットライン (BL0) の電圧が制御される。

すなわち、“ERS2区間”では、共通ソースライン (CSL) がディスチャージされる。より正確にいうと、“ERS2区間”は、メモリセル (MC) のバルク (bulk) がフローティングされ、共通ソースライン (CSL) にチャージされる “VERS-Vt” の電圧が接地電圧 (VSS) にディスチャージされる区間である。

10

#### 【0145】

そして、“ERS3区間”では、バルク (bulk) とビットライン (BL0、BLE0、BL00) とがディスチャージされる。すなわち、ビットライン電圧ライン (BLPWR) は接地電圧 (VSS) に遷移され (tE8) 、偶数シールディング信号 (SHLD<sub>e</sub>) 、奇数シールディング信号 (SHLD<sub>o</sub>) 、偶数ビットライン選択信号 (BLSLT<sub>e</sub>) および奇数ビットライン選択信号 (BLSLT<sub>o</sub>) は電源電圧 (VDD) に遷移される (tE9 ~ tE12) 。したがって、ビットライン (BL0、BLE0、BL00) は接地電圧 (VSS) にディスチャージされる。

20

#### 【0146】

ついで、“ERS4区間”と“ERS5区間”では、メモリセル (MC) の消去されないデータを感知するように、ラッチノード (NLAT) がセットされる過程が行われる。そして、メモリセルのデータがラッチノード (NLAT) 上に感知されて記憶される。

すなわち、“ERS4区間”では、ラッチノード (NLAT) が論理 “H” にセットされた後、“ERS1区間”で消去されなかった偶数ビットライン (BLE0) に連結されるメモリセル (MC) のデータを感知する。“ERS4区間”での動作は、ノーマル読み出しモードで行われる動作とほぼ類似している。しかし、読み出しモードと関連して前述したように、“ERS4区間”とノーマル読み出しモードは、ラッチノード (NLAT) 上にリセットされる値が違う。すなわち、ノーマル読み出しモードでのラッチノード (NLAT) は論理 “L” 状態にリセットされる一方、“ERS4区間”で行われる動作はラッチノード (NLAT) を論理 “H” 状態にリセットする。

30

#### 【0147】

そして、“ERS4区間”で行われる動作は、読み出されるデータのセンシングが “ERS4区間”での第2内部入力ライン (nIDI0) の活性化によって行われるという点で、ノーマル読み出しモードと違う。ここで、“ERS4区間”で行われる残りの動作は読み出しモードで行われる動作とほぼ類似しているので、それについての具体的な説明は、重複説明を避けるために省略する。

#### 【0148】

“ERS5区間”は、前記 “ERS1区間” で消去されなかった奇数ビットライン (BL00) に連結されるメモリセル (MC) のデータを感知する区間である。“ERS5区間”で行われる動作は、ラッチノード (NLAT) をセットする動作が実行されないという点で、“ERS4区間”的動作と違いがある。“ERS5区間”で行われる残りの動作は “ERS4区間”的動作とほぼ同一であるので、それについての具体的な説明は、重複説明を避けるために省略する。

40

ついで、“ERS6区間”では、“ERS4区間”と“ERS5区間”で感知されるデータを利用してメモリセル (MC) の消去動作が正しく実行されたかを確認する過程が行われる。

#### 【0149】

“ERS6区間”でラッチノード (NLAT) が論理 “H” の場合、論理 “L” 状態の

50

データがグローバル出力ライン( G D O U T )に出力されて、バス信号が発生する。一方、ラッチノード( N L A T )が論理“ L ”の場合、論理“ H ”状態のデータがグローバル出力ライン( G D O U T )に出力されて、不良信号が発生する。

したがって、バス信号が発生する時、消去モードが完了する。

#### 【 0 1 5 0 】

“ E R S 6 区間 ” で、メモリセル( M C )が、“ E R S 4 区間 ” と “ E R S 5 区間 ” とともに “ オンセル ” ( O N c e l l ) として感知される時、ラッチノード( N L A T )は論理 “ H ” 状態を維持する。

偶数ビットライン( B L e 0 )が “ オフセル ” ( 消去されなかったセル ) に連結された場合には、“ E R S 4 区間 ” で、ラッチノード( N L A T )は接地電圧( V S S )にディスチャージされる。したがって、“ E R S 5 区間 ” で、奇数ビットライン( B L o 0 )に連結されるメモリセル( M C )が “ オンセル ” として感知されても、ラッチノード( N L A T )上のデータは論理 “ L ” である。10

#### 【 0 1 5 1 】

同様に、奇数ビットライン( B L o 0 )が “ オフセル ” に連結される場合は、偶数ビットライン( B L e 0 )に連結されるメモリセル( M C )が “ オンセル ” であっても、“ E R S 5 区間 ” で、ラッチノード( N L A T )のデータは論理 “ L ” になる。

したがって、バス信号は、偶数ビットライン( B L e 0 )および奇数ビットライン( B L o 0 )がともに “ オンセル ” に連結されているものとして感知される場合にだけ、発生する。20

#### 【 0 1 5 2 】

以上、本発明の好適な実施例を説明したが、本発明の技術分野で通常の知識を持った者であれば、本発明の思想および範囲内で多様な変形、追加および代替が可能であることが理解できる。本明細書では、一例として、 N A N D 型不揮発性半導体メモリ装置を図示し説明したが、本発明の技術的思想は不揮発性半導体メモリ装置のほかの形態、たとえば A N D 型半導体メモリ装置にも適用できることは当業者には自明である。したがって、本発明の技術的保護範囲は本発明の請求範囲の技術的思想によって定義されなければならない。一方、“ 連結される ” およびこれと類似の語句は要素間の直接的連結を規定するものとして解釈してはならない。

#### 【 産業上の利用可能性 】

#### 【 0 1 5 3 】

本発明は、内部出力が前記ラッチ端子およびバッファ入力バスから電気的に隔離され、ページバッファのラッチ端子に記憶されるデータが歪む現象を遮断するもので、不揮発性半導体メモリ装置とこれに用いられるページバッファに適用可能である。

また、本発明は、カラムアドレスのための所要バスラインの数が著しく減少してレイアウト面積が減少するもので、不揮発性半導体メモリ装置に適用可能である。

#### 【 図面の簡単な説明 】

#### 【 0 1 5 4 】

【 図 1 a 】 フラッシュメモリセルの概略的な断面図である。

【 図 1 b 】 フラッシュメモリセルの等価回路図である。

【 図 1 c 】 フラッシュメモリセルのスレショルド電圧の特徴を示す図である。

【 図 2 】 フラッシュメモリセルのスレショルド電圧分布を示す図である。

【 図 3 a 】 N A N D フラッシュメモリセルブロックの概略図である。

【 図 3 b 】 N A N D フラッシュメモリセルブロックの消去、プログラムおよび読み出し電圧を示すテーブルである。

【 図 4 】 図 3 に示す N A N D フラッシュメモリセルブロックのプログラミング動作を説明するための図である。

【 図 5 】 図 3 に示す N A N D フラッシュメモリセルブロックの読み出し動作を説明するための図である。

【 図 6 】 図 3 に示す N A N D フラッシュメモリセルブロックの消去動作を説明するための

10

20

30

40

50

図である。

【図 7】メモリブロックとページバッファブロックの概略図である。

【図 8】従来の不揮発性メモリ装置の概略図である。

【図 9】図 8 の不揮発性メモリ装置に含まれたページバッファとページバッファデコーダの概略図である。

【図 10】図 8 の不揮発性メモリ装置に含まれたページバッファブロックのページバッファのレイアウトを示す図である。

【図 11】本発明の一実施例による不揮発性半導体メモリ装置のブロック図である。

【図 12】図 11 の不揮発性メモリに含まれたメモリアレイの一例を概略的に示す図である。

10

【図 13】図 11 の不揮発性メモリに含まれたページバッファブロックの一例を示す図である。

【図 14】図 13 のページバッファブロックに含まれたページバッファの一例を概略的に示す図である。

【図 15】図 11 の不揮発性メモリに含まれたページバッファデコーダの一例を概略的に示す図である。

【図 16 a】本発明の実施例による不揮発性メモリの読み出しモードを説明するためのフローチャートである。

【図 16 b】図 16 a の S 9 5 0 段階で実行できる段階を説明するためのフローチャートである。

20

【図 17】本発明の実施例による不揮発性メモリの読み出しモードを説明するためのタイミング図である。

【図 18】本発明の実施例による不揮発性メモリのプログラミングモードを説明するためのフローチャートである。

【図 19】本発明の実施例による不揮発性メモリのプログラミングモードを説明するためのタイミング図である。

【図 20】本発明の実施例による不揮発性メモリの消去モードを説明するためのタイミング図である。

#### 【符号の説明】

##### 【 0 1 5 5 】

30

|       |                 |

|-------|-----------------|

| 8 1 0 | ラッチユニット         |

| 8 2 0 | ラッチ伝送ユニット       |

| 8 2 5 | ラッチドライビングユニット   |

| 8 3 0 | センシング応答ユニット     |

| 8 4 0 | 出力ドライビングユニット    |

| 8 5 0 | バッファ選択ユニット      |

| 8 6 0 | センシングセッティングユニット |

| 8 7 0 | ピットライン遮断ユニット    |

Y p バッファ選択アドレス

Y q メイン選択アドレス

Y r サブ選択アドレス

M C A R R メモリアレイ

B L C O N B K ピットライン制御ブロック

P B B 、 N W P B B ページバッファブロック

N W D E ページバッファデコーダ

N W B U F ページバッファ

I D O U T 0 内部出力ライン

G D O U T グローバル出力ライン

I D I 0 第 1 内部入力ライン

n I D I 0 第 2 内部入力ライン

40

50

|                     |                  |    |

|---------------------|------------------|----|

| G D I               | 第1グローバル入力ライン     |    |

| n G D I             | 第2グローバル入力ライン     |    |

| B L、B L 0           | ビットライン           |    |

| W L                 | ワードライン           |    |

| B L e 0             | 偶数ビットライン         |    |

| B L o 0             | 奇数ビットライン         |    |

| S H L D e           | 偶数シールディング信号      |    |

| B L S L T e         | 偶数ビットライン選択信号     |    |

| B L S L T o         | 奇数ビットライン選択信号     |    |

| S O B L K           | センシングノードブロッキング信号 | 10 |

| V P G M             | プログラム電圧          |    |

| V P A S S           | パス電圧             |    |

| V R E A D           | 読み出し電圧           |    |

| V E R S             | 消去電圧             |    |

| V D D               | 電源電圧             |    |

| V S S               | 接地電圧             |    |

| N L A T             | ラッチノード           |    |

| N S E N 0           | センシングノード         |    |

| P B S L T           | バッファ選択信号         |    |

| B L S H F           | ビットライン遮断信号       | 20 |

| L C H               | 読み出しラッチ信号        |    |

| / P L O A D         | センシングセッティング信号    |    |

| / B L D E C         | ロックデコーディング信号     |    |

| R B I N 1、R B I N 2 | バッファ入力パス         |    |

【図 1 a】

【図 1 c】

【図 1 b】

【図 2】

【図3a】

【図3b】

|            | Erase  | Program      | Read  |

|------------|--------|--------------|-------|

| Sel. W/L   | 0      | Vpgm         | 0     |

| Unsel. W/L | Float  | Vpass        | VREAD |

| SSL        | Float  | Vcc          | VREAD |

| GSL        | Float  | 0            | VREAD |

| CSL        | Float  | 1.5          | 0     |

| *0* B/L    | Float  | 0(program)   | 1.2   |

| *1* B/L    | Float  | Vcc(inhibit) | <0.8  |

| Bulk       | Verase | 0            | 0     |

Cell Vth

-1 ~ -3V "ON"

1 ~ 3V "OFF"

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【 図 1 3 】

【 図 1 4 】

【 図 1 5 】

【図16a】

【図16b】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

(72)発明者 林瀛湖

大韓民国京畿道龍仁市駒城面賣亭里1161番地 三星水枝5次アパート512棟1201号

(72)発明者 趙顯哲

大韓民国京畿道龍仁市豊徳川洞 シンジュンマウル ヒュンダイサンウーアパート808棟101号

(72)発明者 蔡東ヒュク

大韓民国ソウル特別市冠岳区新林9洞 グンヨン3次アパート1棟405号

審査官 園田 康弘

(56)参考文献 特開平09-180477(JP,A)

特開2004-186501(JP,A)

特開平11-330426(JP,A)

特開2001-229684(JP,A)

特開平08-255496(JP,A)

特開2003-141882(JP,A)

特開2004-192780(JP,A)

特開平09-204788(JP,A)

特開平11-144482(JP,A)

特開平09-231770(JP,A)

特開平10-144892(JP,A)

特開2003-173688(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/06

G11C 16/04