**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

|                                                                                                                                                            |                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| (51) Int. Cl. <sup>6</sup><br>H01L 21/76                                                                                                                   | (45) 공고일자<br>1999년02월01일      |

| (21) 출원번호<br>1994-034941                                                                                                                                   | (11) 등록번호<br>특0167813         |

| (22) 출원일자<br>1994년 12월 19일                                                                                                                                 | (24) 등록일자<br>1998년09월30일      |

| (30) 우선권주장<br>8/173,396 1993년 12월 23일 미국(US)                                                                                                               | (65) 공개번호<br>특 1995-021405    |

| (43) 공개일자<br>1995년07월26일                                                                                                                                   |                               |

| (73) 특허권자<br>인터내셔널 비지네스 머신즈 코포레이션<br>미합중국 뉴욕 10504 아몬크<br>캐롤 칼리                                                                                            | 월리암 티. 엘리스                    |

| (72) 발명자<br>미합중국 머릴랜드 21113 오덴튼 시로 리지 코트 307-202<br>루이스 루첸 쿠<br>미합중국 뉴욕 12524 피쉬킬 크로스비 코트 7<br>조셉 프란시스 쉐파드<br>미합중국 뉴욕 12533 호프웰 정션 컨트리 클럽 로드 36<br>세이키 오구라 |                               |

| (74) 대리인<br>김창세, 김영, 장성구                                                                                                                                   | 미합중국 뉴욕 12533 호프웰 정션 롱힐 로드 50 |

**심사관 : 김용정**

---

**(54) 집적회로 장치 제조 및 반도체 구조 제조 방법**

---

**요약**

얕은 트렌치 절연 구조(shallow trench isolation structure)는 절연 반도체 산화물(insulating semiconductor oxide)의 액상 침착(liquid phase deposition)에 의해 트렌치(trench)를 충전하고, 상체 침착물을 열처리(heat treating)하여, 침착된 산화물을 증과 트렌치가 확장해 들어가는 반도체 재료의 본체(예를들면, 기판)간의 경계에 고 품질의 열적 산화물층(a layer of high quality thermal oxide)을 형성하는, 단계의 횟수 및 열처리 경비가 감소된 (a reduced number of steps and thermal budget) 프로세스에 의해 형성된다. 이 프로세스는 스트레스가 감소되고 전하 누설 발생 경향이 감소된 절연 구조를 생성한다.

이 구조는 특히, 폴리싱-차단 층(poliish-stop layer)이 반도체 재료의 본체 상에 제공된 경우에 쉽게 평탄화 되어질 수 있으며, 침착된 산화물의 공극 및 오염(voids and contamination of the deposited oxide)은 트렌치 형성에 사용된 레지스트 상의 구멍의 용적(volume of apertures)만큼 트렌치상의 자기 정렬 침착(self-aligned deposition)에 의해 실질적으로 제거될 수 있다.

**대표도**

**영세서**

[발명의 명칭]

집적회로 장치 제조 방법 및 반도체 구조 제조 방법

[도면의 간단한 설명]

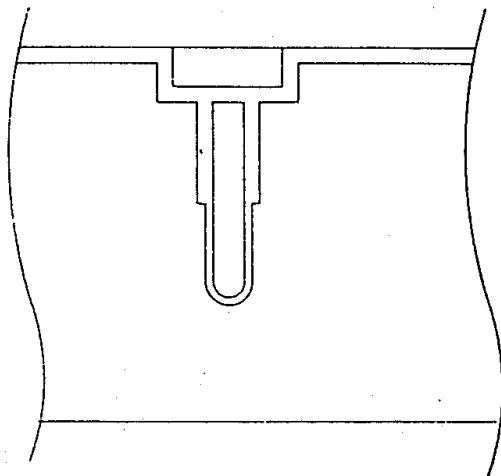

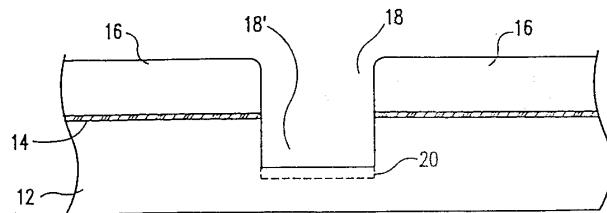

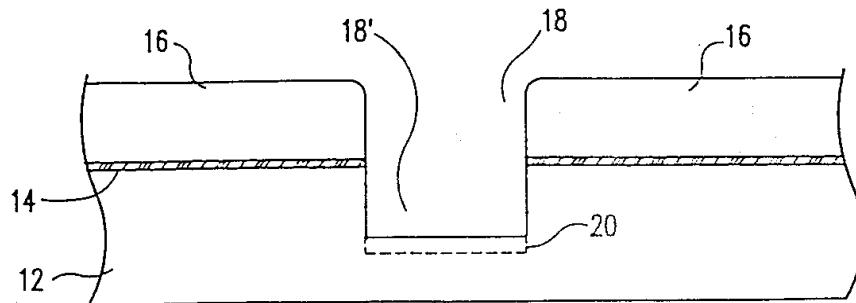

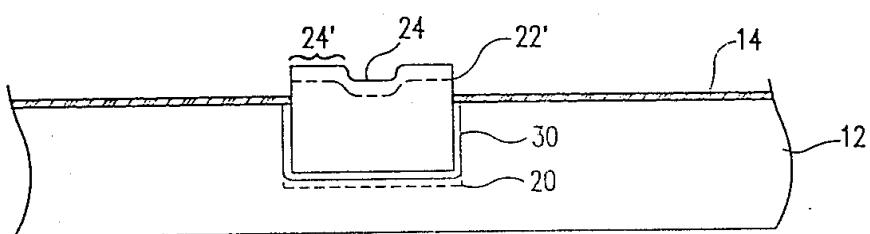

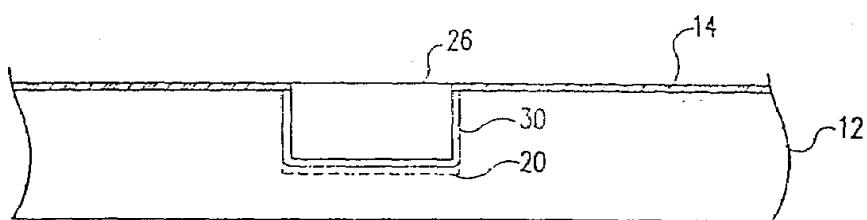

제1 내지 제3도는 본 발명에 다른 얕은 트렌치 절연 구조 형성 단계의 단면도.

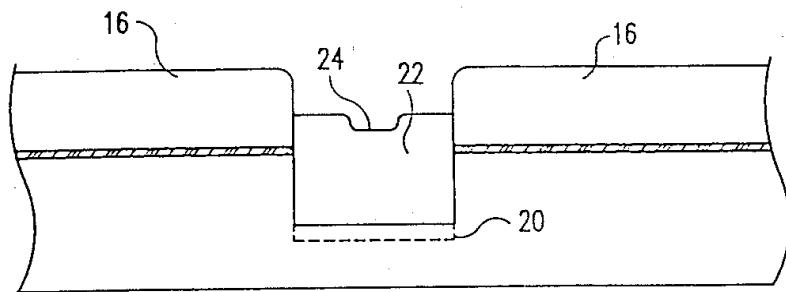

제4도는 본 발명에 따라 완성된 얕은 트렌치 절연 구조의 단면도.

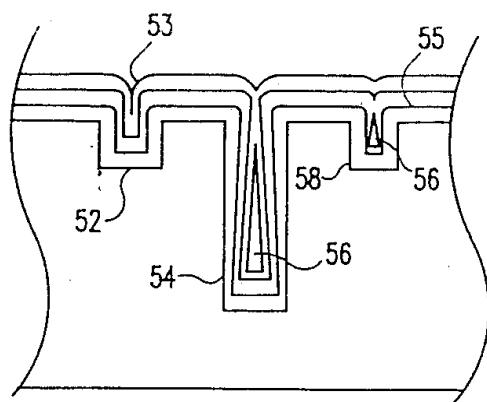

제5, 6a 및 제6b도는 제각기 크기가 다른 얕은 트렌치 구조들의 단면을 도시한 것으로서, 액상 산화물 침착 기법과 고온 침착 기법간의 침착 프로파일 비교를 위한 도면.

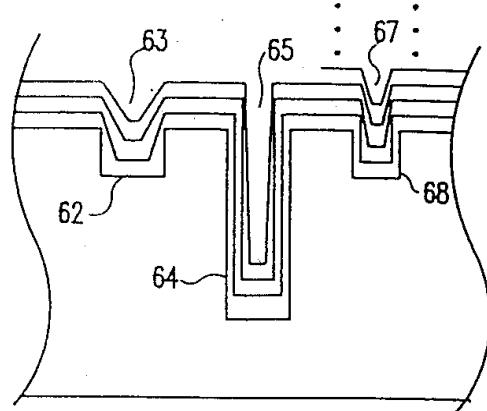

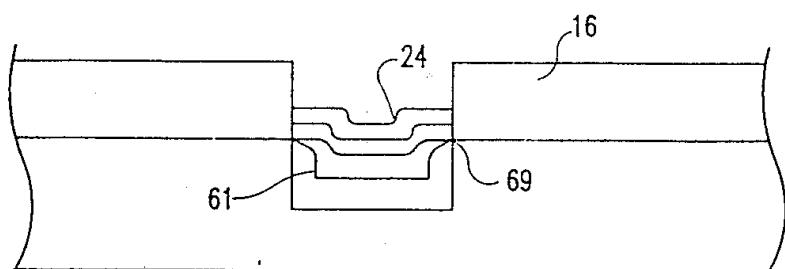

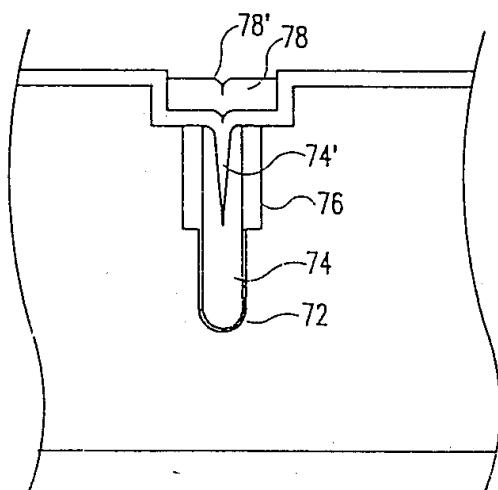

제7도 및 제8도는 액상 침착 기법과 고온 침착 기법에 따라 형성되는 깊은 트렌치 캐퍼시터 구조들의 비

교를 위한 단면도.

\* 도면의 주요부분에 대한 부호의 설명

|                   |                      |

|-------------------|----------------------|

| 12 : 기판           | 14 : 폴리싱 차단 층        |

| 16 : 블랭킷 포토레지스트 층 | 18 : 구멍              |

| 18', 52 : 얕은 트렌치  | 20 : 채널 차단 영역        |

| 22 : 침착물          | 24, 53 : 오목부         |

| 30 : 열적 산화물       | 54 : 트렌치             |

| 56 : 키-홀 결합       | 63, 65, 67 : 개방된 오목부 |

| 72 : 노드 산화물       | 74 : 다결정 실리콘 플레이트    |

| 74', 78' : 틈새     | 76 : 칼라 산화물          |

| 78 : 실리콘 캡        |                      |

[발명의 상세한 설명]

본 발명은 전반적으로 집적 회로(integrated circuit)의 절연 구조(isolation structure)에 관한 것으로, 특히, 고 집적도(high integration density)의 집적 회로에서 얕은 트렌치 절연(shallow trench isolation : STI) 구조를 형성하는 것에 관한 것이다.

다수의 상호 접속된 회로 장치들이 단일 칩(single chip)상에 형성되는 집적 회로는 다양한 전자 장치에 이용되고 있다. 특히, 데이터 프로세서(data processors)에서는 장치간의 접속 길이가 프로세서 사이를 시간 및 프로세서 속도를 감소시키는데 있어 제약요인(a limiting facto)으로 인식되고 있기 때문에, 가능한 한 많은 회로 장치를 단일 칩상에 제공하고자 하는 생각이 매우 강렬했다. 또한, 만약 칩 설계의 집적 회로 제조 수율(yields)이 적당한 레벨(level)로 유지될 수 있다면, 높은 회로 집적도(high degree of circuit integration)는 그러한 고 집적도의 집적 회로를 포함하는 전자 장치의 제조에 있어서 상당한 경제성을 창출하게 된다.

따라서, 집적 회로 설계에 있어서 현재의 추세는 각각의 칩상에 더 많은 장치의 집적을 수행하는 방향으로 발전하고 있다.

집적도가 증가하고 칩상에 배치된 장치간의 거리가 점점 더 짧아짐에 따라, 장치간의 상호 작용(interaction)의 가능성은 더욱 증가하게 된다. 따라서, 캐패시턴스(capacitances) 같은 기생 회로 성분(parasitic circuit elements)의 형성은 현재의 집적 회로 설계에 있어서 주요 문제점으로 대두되고 있다. 따라서, 최근, 많은 집적 회로 설계에 있어서는, 동일 칩상에서 회로 소자간의 문제로 되는 상호 작용을 저지할 목적으로 절연 구조를 포함할 필요성이 생기게 되었다.

절연 구조의 한 가지 일반적인 형식으로는 리세스형 산화물 절연(recessed oxide isolation : ROI) 구조가 있는데, 이 ROI 구조는 예상되는 회로 상호영향(circuit interaction) 형태에 따라 다양한 깊이 혹은 종횡비(aspect ratio)를 가질 수 있다. 소위 깊은 트렌치 구조(deep trench structures)는 일반적으로 약 4 : 1의 비교적 큰 종횡비(깊이 대폭)를 갖는데, 이 구조는 주로 과거 몇 년간 널리 행해지고 있는 최소 배선폭 방식(feature size regimes)을 가진 바이폴라 소자의 설계시에, 반도체 기판의 벌크(bulk)내의 전자 이동을 저지하는 데 매우 효과적이다. 그러나, 이들 형식의 구조는, 절연 및 기타 다른 소자의 제조 요건을 충족시키면서, 현재 수준의 집적회로 기술에서 당장 가능한 최소 배선폭으로 스케일(scale)될 수 없다.

구체적으로 말해서, 이들 구조가 더욱 작아져 산화물이 더욱 얇아질수록, 산화물 양단간의 용량성 결합(capacitive coupling)이 증가한다.

또한, ROI 프로세스에서는, 실리콘 산화물(silicon oxide)이 질화물 마스크(nitride mask) 아래에서 성장하여 능동 소자 영역(active device areas)으로 잠식(encroach)해 들어가는 열적 산화물 성장(thermal oxide growth)동안 소위 새 부리(bird's beak) 형상이 발생하는 경향이 있다.

이 새 부리 형상은 ROI 구조의 설정 경계(intended boundary) 너머로  $0.1\text{ }\mu\text{m}$  보다 크게 확장하여 장치 형성을 위해 설정해 놓은 영역을 침범할 수도 있다. ROI 구조가 매우 얕은 구성을 가짐에도 불구하고 이러한 침범이나 잠식은,  $0.5$  미크로( $\mu\text{m}$ ) 설계의 기본적인 룰(half-micron design ground rule) 하에서도 장치 분리 거리(device separation distance)의 상당한 부분을 점유하므로  $0.25$  미크론 설계의 기본적인 룰 하에서는 수용될 수 없다는 것을 쉽게 알 수 있다. 또한 새 부리 형상의 형성으로 인해 질화물 마스크와 그의 하부층들(underlying layers) 사이에 고 스트레스 영역(a region of high stress)(응력을 많이 받는 영역)이 발생되고, 이러한 고 스트레스 영역도 역시 새 부리 형상 부분에 의해 실제로 점유되는 영역 너머의 능동 소자 영역을 잠식할 수 있다. 능동 장치의 전기적인 특성에 유해하게 될 결정 전위(crystal dislocation)의 형성에 의해 능동 소자가 사용상태로 된 후에 이들 고 스트레스 영역이 경감될 수도 있다.

이에 대한 대안으로서, 소위 얕은 트렌치 절연(shallow trench isolation : STI) 구조가 개발되었다. 얕은 트렌치는 특히 MOSFET 소자에서 반도체 표면에서의 전자 이동을 제어하는데 주로 사용된다. 전술한 ROI 구조와 비교할 때, STI 구조는 종횡비가 감소하며, 상부 표면이 편평하게 되는데, 이 표면상에는 도전체(conductor)가 용이하게 형성될 수 있다. 또한, 조점이 맞추어진 화상을 유지하기 위한 별도의 부가적인 피사계 심도(depth of field)를 필요로 하는 일 없이 보다 양호한 해상도를 얻을 수 있으므로, 리소그래픽 노출(lithographic exposures)에 있어 상당히 유리하다.

그러나, STI 구조를 생성하기 위해 현재 사용되고 있는 프로세스는 매우 복잡하고 많은 비용이 소모된다.

전형적인 프로세스 순서로서는, 레지스트 패터닝(resist patterning), 테이퍼(taper) 비티아퍼 형의 리세스를 기판에 형성하기 위한 반응성 이온 에칭(RIE), 트렌치의 측벽 및 바닥면에 채널 차단부(channel stop)의 주입, 레지스트의 스트리핑(striping), 트렌치 측벽 산화물을 형성하기 위한 트렌치 내의 기판 산화, 화학적 증착법(chemical vapor deposition : CVD)에 의한 산화물 충전(fill), 블록-아웃 레지스트 패터닝(black-out resist patterning), 평탄화를 위한 건식(dry) 에칭 및 트렌치 측벽상 산화물에 대한 화학적-기계적인 폴리싱(chemical-mechanical polishing) 및 어닐링(annealing)이 포함된다. 상기 및 이와 유사한 공자의 프로세서도 인접한 소자 영역에 고 스트레스 영역을 생성하는 경향이 있는데, 이것은 결국 반도체 기판의 결정 격자에 있어 자연 발생적인 전위 루프(dislocation loops)의 형성에 의해 해소된다. STI 구조를 가지는 집적 회로 장치 영역내에 생기는 소자로 부터의 전하 누설(charge leakage)은 이러한 전위 루프와 연관이 있다.

STI 구조에서 직면하는 다른 문제점은 CVD 산화물을 좁은 트렌치(narrow trench)를 충전하는 프로세스(공정)에 있다. 이 충전 공정은 다소 공형적으로(conformally) 진행되므로,(예를들면, 트랜치 측면의 침착은 트랜치 바닥의 침착보다 다소 천천히 진행되나 일반적으로 그 차이는 트렌치의 종횡비보다는 작음), 좁은 트렌치의 하부 영역이 채워지기 전에 상부 영역이 채워짐으로써 공극(void)이 형성될 수도 있다.

또한, 트렌치 종횡비가 작은 STI 구조에서도, 일반적으로 공형 침착에 의해 트렌치의 상부에 표면 공극 혹은 오목부(dimple)가 형성되므로, (습식) 화학적 및 / 또는 기계적인 폴리싱과 같은 공정에 의한 복잡한 평탄화가 필요할 수도 있으며, 또한 오목부에 오염 물질이 들어 갈 수도 있다.

현재, 트렌치 충전과 관련된 문제점을 완화시키고 스트레스를 감소시키는 유일한 기법은 광범위한 공간을 필요로 하는 트렌치 데이퍼팅(tapering) 공정과 트렌치 바닥면의 라운딩(rounding) 공정을 포함하고 있다. 그러나, 이러한 기법들은 단독으로 혹은 조합하여 사용되더라도, 고 집적도를 유지하면서, 전술한 스트레스 감소 및 트렌치 충전 문제에 대한 해결책을 제시하지 못했다.

최근에, 액상 침착(liquid phase deposition : LPD) 프로세스가 개발되어 낮은 온도에서 기판 표면상에 실리콘 이산화물(silicon dioxide)을 성공적으로 침착시키고 있다. 구체적으로, 실리콘 산화물을 실리카( $\text{SiO}_2$ )로 과포화된(supersaturated) 봉소 산(boric acid :  $\text{H}_3\text{BO}_3$ )과 플루 오로실리 산( $\text{H}_2\text{SiF}_6$ , 종종 다양하게 하이드로 플루오로실리 산, 하이드로 혼사 플루오로실리 산, 하이드로 플루오실리 산 혹은 플루오실리 산으로 언급됨)의 용액을 사용하여 35°C에서 표면상에 침착된다.

이러한 사항은, 히로추가 나가야마등이 1988년 8월에 Journal of Electrochemical Society의 pp.2013-2016에 발표한 새로운 실리카 코팅의 프로세스(A New Process for Silica Coating)란 제목의 논문에 모두 개시되어 있다. 요약하여 말하자면, 실리카의 용해도는 온도의 증가에 따라 감소하며, 포화된 용액은 온도를 증가시키거나 혹은 다른 방법에 의해 일시적으로 과포화될 수 있다. 그 후, 과잉의 실리카(excess silica)는 용액속에 잠겨진 표면에 침착되어, 최종적인 플루오로화 수소산의 농도(concentration)가 봉소 산과 반응함에 따라 최소화된다.

이러한 저온 프로세스는 상호 접속 층들사이에 절연체를 형성하는데, 특히 유용하며, 측벽 스페이서(sidewall spacer)의 사용에 관한 보고(K. 칸바등에 의한 액상 선택적 산화물 침착을 활용한 7 마스크 CMOS 기법(A 7MASK CMOS Technology Utilizing Liquid Phase Selective Oxide Deposition) IEDM 91, pp25.1.1-25.1.4 참조)가 있었지만, 지금까지도, 엄밀한 토플로지(severe topologies)상의 액상 침착 혹은 선택적인 침착에 의한 리세스의 충전에 대한 보고는 없다. 그러나, T. 흄마등이 1990년 VLSI 기법 심포지움에서 발표한 LPN을 사용하여 완전히 평탄화된 멀티레벨 상호 접속의 새로운 내부층 형성 기법(A New Interlayer Formation Technology of completely planarized Multilevel Interconnection by using LPN)에서는 레지스트와 소기 침착 표면 사이(intended deposition surface)의 습윤도(wettability) 차이가 레지스트 패턴내 구멍에서의 선택적인 침착을 향상시킬 수 있음이 제안되었다.

액상 실리카 침착에 의한 저온 산화물 침착 방법은 상호접속 층들사이에 절연체를 형성하는데 상당히 유용하는데, 이 때 집적 회로 장치가 사실상 완성되어 열 처리 경비가 적게 든다. 그러나, 500°C에서의 열 처리(밀도가 증가된 보다 질서정연한 실리카 망상조직(orderly silica network)을 형성하기 위한 필수적인 어닐링 프로세스)가 침착된 산화물의 절연품질을 향상시킨다는 것을 알게 되었다.

하지만, 이러한 열처리는 도전체나 도핑된 혹은 주입된 반도체 영역이 존재하는 경우에는 종종 적당하지 않다. 예를 들면, 증가된 온도에 의해서 도펀트 혹은 불순물(dopants or impurities)의 확산 속도가 급격히 증대한다.

또한, 금속성 도전체가 존재하므로 도전체에 대한 손상을 피하기 위해 그 이상의 열처리는 일반적으로 350°C로 제한되어야 한다.

또한, 열 처리에 의한 산화물의 절연 특성 향상으로 인해 침착된 산화물층의 밀도가 증가하고 용적이 감소하는데, 이것은 산화물 및 / 또는 그 산화물이 위에 침착되는 물질에 스트레스를 야기할 수도 있다. 이 같은 스트레스는 절연 구조물에 인접한 소자들간에 전하 트랩(charge traps) 혹은 누설 경로(leaky paths)를 형성할 수 있는 격자 전위(lattice dislocation)의 원인으로 될 수 있다.

따라서, 스트레스 및 전위의 발생으로 인해 산화물의 어닐링 및 이에 따른 개선된 절연 특성의 개발의 결과를 활용할 수 없게 된다.

따라서, 본 발명의 목적은 잔류(residual) 스트레스가 감소된 얇은 트렌치 절연 구조를 형성하는 방법을 제공하는데 있는 것으로, 이러한 방법에 의하면 복잡성이 감소되고 경비가 절감되며, 프로세싱 단계들의 수가 감소하게 된다.

본 발명의 다른 목적은 전자(electronic) 집적회로에 있어서 초 고집적 밀도(extremely high integration density) 설계에 적합한 개선된 얇은 트렌치 절연 구조를 제공하는 데 있다.

본 발명의 또 다른 목적은, 반도체 재료상에 실리콘 산화물의 침착물을 포함하는 반도체 구조에서 다른 방법에 비해, 잔류 스트레스 레벨이 감소시키는데 있다.

상기의 목적들을 달성하기 위하여, 본 발명의 특징에 의하면, 절연 구조를 포함하는 반도체 소자는 반도체 재료의 본체내로 확장하는 트렌치, 액상 침착에 의해 침착되어 실질적으로 트렌치를 충전하는 절연 산화물의 침착물, 그리고 반도체 재료의 본체, 트렌치내의 절연 산화물의 침착물 간의 경계(interface)에서 열적으로 성장한 산화물층을 포함한다.

본 발명의 다른 특징에 의하면, 집적 회로 장치를 형성하는 방법은, 반도체 재료의 본체내로 확장하는 트렌치를 형성하는 단계, 액상 침착 단계에 의해 절연 산화물로 트렌치를 실질적으로 충전하는 단계, 반도체 재료 및 트렌치내의 절연 산화물을 충분히 가열하여 반도체 재료 본체 및 절연 산화물의 경계에 열적 산화물층(a layer of thermal oxide)을 형성하는 단계를 포함한다.

본 발명의 또 다른 특징에 의하면, 반도체 구조를 형성하는 방법은, 실리카를 함유하는 과포화된 액상 용액으로 반도체 재료상에 실리콘 산화물을 침착시키는 단계, 상기 침착 단계에 의해 침착된 실리콘 산화물의 밀도를 증가시키는 단계와 상기 밀도를 증가시키는 단계동안 실리콘 산화물의 용적 변화를 대략 보상하기에 충분한 용적으로 실리콘 산화물과 반도체 재료 사이의 경계에서 열적 산화물을 성장시킴으로써, 상기 경계에서의 스트레스를 완화시키는 단계를 포함한다.

본 발명의 상술한 목적 및 특징과 그 밖의 장점들은 첨부된 도면을 참조하여, 후술되는 본 발명의 바람직한 실시예의 상세한 설명으로 더 잘 이해할 수 있을 것이다.

이하, 본 발명의 실시예를 도면을 참조하여 설명한다.

제1도를 참조하면, 본 발명에 따른 얇은 절연 트렌치 제조의 초기 단계의 단면도가 도시된다. 이 단계에서, 산화물 / 질화물의 혼합물질(oxide/nitride composite material)과 같은 단단한 폴리싱-차단 물질(a hard polish-stop material)의 얇은 블랭킷 층(a thin blanket layer)(14)이 기판(12)상에 침착된다. 폴리싱-차단 물질상에는 블랭킷 포토레지스트 층(blanket photoresist layer)(16)이 침착되고, 노출되며(exposed)노출 패턴이 현상되어 레지스트 내에 구멍(opening)(18)이 형성된다. 그후, 폴리싱-차단 물질이  $\text{CF}_4$  반응성 이온 에칭(RIE)에 의해 개방되고  $\text{Cl}_2$  RIE에 의해서 얇은 트렌치(18')가 형성된다.

이같은 패터닝(patterning) 및 얇은 트렌치(18')의 형성에 따라, 이온 주입이 가능하게 되어 공지의 자기 정렬 방식(self-aligned manner)으로 채널 차단 영역(channel stop region)(20)이 형성된다.

본 발명에 의한 구조는, 절연 트렌치들 사이(예를 들면, 도시한 대표적인 절연 트렌치의 오른쪽 및 / 혹은 왼쪽에 있음)의 능동 소자 영역에 형성될 장치의 형태에 따라, 목적하는 대로 선택되고 변경될 수 있는 도편트와 불순물의 도전형과는 완전히 무관하게 형성된다는 것도 잘 이해할 수 있을 것이다. 경우에 따라서는, 도전형이 다른 반도체 재료의 블랭킷 층 혹은 우물(well)과 같은 또 다른 구조를 기판상에 제공하여, (기판에 도달되는지의 여부에 관계없이) 반도체 구조의 본체내로 트랜치를 형성함으로써 절연 구조를 형성하는 것도 가능하며, 이것이 어떠한 상황에서는 유리할 수도 있다.

일단 채널 차단 영역의 주입이 완료되면, 산화물이 성장하는 동안 발생하는 하이드로 플루오로 산(hydrofluoric acid)을 제거하기에 효과적인 양의 봉소 산(boric acid)을 바람직하게 함유한 과포화된 플루오로규산(fluorosilicic acid)의 실리카 용액으로부터, 액상 침착에 의한 실리콘 산화물(silicon oxide)(예를 들면, 실리카)의 침착에 의해 구멍(18, 18')이 부분적으로 채워진다. 능동 소자 혹은 도전체의 형성전에 절연 구조를 형성하는 것이 특히 바람직하므로, 침착의 온도는 중요하지 않다. 따라서, 집적 회로 소자의 제조중 이 단계에서의 열처리 경비(heat budgets)가 근본적으로 필요하지 않다. 침착 프로세스는 제2도에 (22)로 도시한 바와 같이, 산화물 성장에 의해 포토레지스터내의 제1도의 얇은 트렌치(18') 및 구멍(18)의 상당 부분이 충전될 때까지 계속되는 것이 바람직하다. 산화물의 성장은 이상적인 공형성(conformal)의 성장이 아니고, 또한 이상적인 등방성(isotropic)의 성장도 아니다. 즉, 트렌치 측벽으로부터의 성장 속도는 트렌치 바닥면으로부터의 성장 속도보다 현저히 느리므로, 침착된 산화물 표면에 오목부(dimple)(24)가 형성된다. 이같은 오목부(24) 때문에, 또한 밀도를 높이는 동안(제3도에 (22')를 도시한 프로파일로의)의 프로파일의 변화 때문에, 후술할 평탄화 공정(planarization)에 의해 완전하고도 확실하게 오목부가 제거되도록, 밀도를 높이는 동안의 오목부 위치 변화분 보다 큰 거리 만큼 폴리싱-차단 층(14)의 상부 표면위쪽으로 오목부의 바닥면이 확실하게 상승될 때 까지 산화물 침착을 계속하는 것이 바람직하다.

다음에는 제5 및 제6도를 참조하여, 액상 침착 기법과 고온 CVD 침착 기법간의 침착 프로파일의 상이점을 간결하게 설명하기로 한다. 제5도에 도시한 바와 같이, 화학적 증착법(CVD)에 의하면, 산화물층이 트렌치내에 거의 공형적으로 침착하여 형성된다. 그러나, 트렌치의 크기 및 종횡비 때문에, 산화물층의 두께에 차이가 발생한다. 구체적으로 제5도에서 작은 종횡비의 트렌치에서는 산화물 층들이 사실상 공형적으로 침착될 수 있다(이는 산화물층이 침착되는 동안 전반적으로 동일한 정도 증가됨을 뜻한다). 그러나, 공형 침착의 두께가 두꺼워지면 유효 종횡비가 커지게 되어, 트렌치 바닥면에서의 침착 속도는 느려질 것이라는 사실에 주목할 필요가 있다. 얇은 트렌치(52)에서는 이러한 사실이 중요하지 않을 수도 있으므로, 얇은 트렌치를 적당히 충전할 수도 있다. 그러나, 얇은 트렌치를 적당히 충전할 수 있다고는 하더라도, 오목부(53)가 상당히 깊으므로, 차후의 평탄화 공정동안 오염 물질이 들어갈 수도 있다.

공형적인 CVD를 수행함에 따라 종횡비 증가에 기인한 두께 변화의 영향은 트렌치(54)에서 더욱 뚜렷하다. 이 경우, 침착은 트렌치 상부 근처에서 더욱 급속하게 수행되어, 트렌치 하부(lower levels of the trench)에서의 침착 속도를 제한한다. 이러한 현상은 침착이 진행될수록 더욱 심해진다. 결국 트렌치 상부는 충전 공정이 완료되기 전에 폐쇄되어(closed), 커다란 키 홀(key-hole) 결함(56)이 생기게 된다. 전술한 바와 같이, 이러한 현상은 바깥쪽으로 경사진 측벽(outwardly inclined walls)을 가진 트렌치를 형성하여 트렌치 바닥면에서의 침착 속도 제한을 자연시킴으로써 없앨 수 있다. 그러나, 이러한 조치는 트렌치의 상단 폭을 증가시켜야 하는 학생을 치루어야만 이용가능한 것으로, 이렇게 하면, 성취 가능한 집적 밀도가 제한된다.

이러한 현상은 도면에서 (58)로 도시된 것과 같이, 좁은 폭으로 형성된 비교적 작은 종횡비의 트렌치에서도 또한 동일하게 발생한다. 도면에서 선(55)으로 도시된 침착 프로파일의 유효 종횡비는 실질적으로 원

래의 트렌치의 종횡비의 3배로 된다는 사실에 주목할 필요가 있다.

침착의 초기 단계에서는 거의 공형적인 침착이 이루어지나, 점차 유효 종횡비가 매우 급속히 변하여, 트렌치(54)내에 형성되는 키 훌 결함(56)과 유사한 형식으로 공극(56')이 형성될 수도 있다.

이와는 대조적으로, 제6a도에 도시된 바와같이, 액상 침착은 트렌치 측벽상의 침착 속도는 크게 감소시키면서 트렌치 바닥면으로 부터의 침착속도는 크게 증가시킨다는 것을 알게되었다. 어떤 특정한 이론에 국한하려는 것은 아니나, 실리카의 과포화된 용액에서 침착이 수행되므로, 침착은 침전(precipitation)의 임계 레벨에서 발생한다.

따라서, 침착은 이방성(anisotropic)이며, 침착 표면에 대해 수직인 방향의 침착 두께가 우선적으로 더 커지게 된다. 따라서, 침착이 진행됨에 따라, 더욱 개방적인(오픈(open)되는) 오목부(63, 65, 67)가 형성되는데, 이같은 오목부는 트렌치 바닥면의 침착을 방해하지 않으며 또한 CVD에 의해 형성되는 깊은 오목부(53)에 비해 오염 물질을 보유할 가능성이 작다.

액상 침착은 또한 비교적 높은 선택도로 수행될 수 있다. 만약, 바람직스러운 것으로서 제1 및 제6b도에 도시된 바와 같이, 레지스트(16)를 트렌치 구멍(61)과 거의 조화시켜 제공하면, 트렌치의 충전 공정동안 레지스트 표면상의 침착을 거의 혹은 완전히 피할 수 있다. 측벽상의 느린 침착은 또한 트렌치가 실질적으로 충전될 때까지 침착된 산화물상의 견부(shoulder)의 성장을 지연시킨다. 그 후, 침착을 레지스트(16)의 두께 범위내로 계속함에 따라, 침착은 더욱 거의 공형적으로 이루어지고, 그 결과로 기판 표면쪽에 우물과 같은 얇은 개방적인 오목부(24)가 형성된다. 따라서, 분명히 알 수 있듯이, 액상 침착은 특히 아주 작은 크기를 갖는 절연 구조내의 트렌치를 충전시키는데 적합하고, 전도체 층 절연과 같은 공지의 응용에 한정되지 않는다.

또한, 액상 침착에 의해 생기는 침착 프로파일은 CVD에 의해 작은, 혹은 큰 종횡비의 트렌치(small or high aspect ratio trench)를 채우는 것과 연관된 공극 및 다른 결함의 발생 성향을 상당히 감소시킨다.

전술한 바와 같이, 액상 침착이 완료된 후에, 제3도에 도시된 것처럼 레지스트(16)가 제거되며, 웨이퍼(wafer)는 산소로(oxygen furnace)내에서 세척되고 건조되며 어닐링한다. 어닐링 프로세스의 시간 및 온도는 기판과 침착된 산화물간의 경계에서 산화물의 얇은 층(thin layer)이 성장하기에 충분할 정도로 결정하는 것이 바람직하다. (약 100 옹스트롬의 열적 산화물은 전하 및 경계 상태(charge and interface stated)의 견자에서 전기적인 경계를 제공하기에 충분하다).

산화 조건은 온도 보다는 상대적으로 덜 중요한데, 그 이유는 경계의 전하 밀도는 가장 최근에 전자장치에 가해진 어닐링 온도에 의해 설정되기 때문이다. 이러한 열적 산화물은 0.25 미크론 내지 0.5 미크론 설계 기본 률에 따라 형성된 절연 구조의 경우, 30분 ± 15분의 기간동안  $800^{\circ}\text{C} \pm 100^{\circ}\text{C}$  dpj 포스트-어닐링 프로세스(post-anneal process)로 성장시키는 것이 바람직하다. 또한 산화물에 다소의 어닐링을 행하는 것에 의해 침착된 산화물의 밀도가 증가되고 절연 상수가 감소될 것이라고는 하지만, 이같은 산화물의 어닐링은 경계에서의 열적 산화물 형성보다 덜 중요하다는 사실을 알게 되었다. (또한, 침착된 산화물의 밀도 증가 때문에, 열처리 이후에 오목부(24)의 바닥면이 폴리싱-차단 층(14)의 상부면 혹은 그 위쪽에 유지될 때까지 침착을 계속하는 것이 바람직하다).

전술한 바와 같이, 침착된 산화물과 기판사이의 불량한 경계 특성은 전하 트랩(charge trap) 형상을 일으켜 산화물과 기판이 전기적으로 접속되게 한다는 것을 알게 되었다. 즉, 이같은 경계특성에는, 트렌치의 측벽 주위로의 채널링(channeling)을 야기할 수도 있는 전하 및 / 또는 경계 상태가 포함될 수도 있다.

따라서, 열적 산화물의 형성은 본 발명에서 중요하게 생각되는데, 그 이유는 캡을 충전함으로써, 또한 산화물의 밀도를 증가시키는 동안 생길 수도 있는 전위를 완화시킴으로써 경계특성을 향상시킬 뿐만 아니라, 액상 침착에 의해 침착된 산화물의 절연 특성을 향상시키기 때문이다.

또한, 이같은 열적 산화물의 형성이 본 발명에서 중요하게 생각되는 또 다른 이유는 이동 전하(mobile charge)를 끌어당겨 인접한 장치들 사이에 누설 경로(leaky path)를 생성하는 맹글링 본드(dangling bonds)의 포화(saturation)에 부가하여, 밀도 증가 및 산화가 공극 및 전하 집중을 제거할 수 있기 때문이다.

열적 산화는 또한 밀도 증가에 의해 야기된 LPD 산화물의 수축을 보상하여, 측벽으로부터 트렌치 충전물이 분리되는 것을 방지한다. 따라서, 본 발명에 따르는 절연 구조에 의해 제공되는 전기적인 절연 및 전하 누설방지는 주로 열처리 동안 성장하는 열적 산화물의 기능이다.

또한, 열적 산화물의 성장은 침전된 산화물의 밀도가 비교적 높으며, 잔류 스트레스를 수용할 수 있어야만 하는 다른 산화물 침착 프로세스에서는 가능하지 않은 스트레스 완화 메카니즘을 제공한다. 따라서, 반도체 장치 구조에서의 스트레스를 최소화하는 점까지 열적 산화물을 성장시키는 것이 바람직하며, 이렇게 하면 또한 열적 산화물 두께가 적당하게 되어 전기적 특성이 양호하게 된다.

제4도에 도시한 바와 같이, 절연 구조는 가벼운 화학-기계적 폴리싱(chemical-mechanical polish)에 폴리싱-차단 층(14)의 표면 위쪽으로 돌출된 산화물 부분을 제거하여, 산화물 침착물(24)의 최종적인 상부 표면이 층(14)의 상부 표면과 동일 평면상에 놓이게 함으로써 완성된다.

폴리싱-차단 층은 폴리싱 프로세스를 촉진하고, 반도체 재료의 본체(예를 들면, 기판(12))에 대한 손상을 방지하도록 제공하는 것이 바람직하다.

종래의 리세스형 산화 절연 프로세스에서 경험한 바와 같이, 액상 침착에 의해 트렌치를 충전하는 동안 질화물 마스크의 에지 아래에 새 부리 형태가 생성되지 않으므로, 이전에는 가능하지 않았던 깊은 서브 기판 절연구조(deep sub-surface isolation structures)가 형성 될 수 있음에 주목할 필요가 있다. 또한, 오목부(24)의 모든 오염물질이나 이 위치에서 형성되는 모든 공극은 평탄화 공정동안 제거된다.

다음에 제7 및 8도를 참조하여, 절연 구조와는 다른, 본 발명의 특별한 응용예를 설명하기로 한다.

구체적으로 말해서, 우수한 절연 성능 및 트렌치의 충전 능력 덕분에, 본 발명의 방법론은 또한 컴퓨터

부품으로 알려진 고 용량 다이나믹 랜덤 액세스 메모리(hight capacitor dynamic random access memory) 등에 사용되는 바와 같은 작은 밑넓이(footprint)의 깊은 트렌치 저장 캐피시터(deep trench storage capacitor)의 형성에 적용될 수 있다. 이러한 캐피시터의 구조는, 노드 산화물(node oxide)(72), 다결정 실리콘 플레이트(policrystalline silicon plate)(풀리-플레이트)(74), 칼러 산화물(collar oxide)(76) 및 열적 산화물에 의해 둘러싸인 실리콘 캡(silicon cap)(78)을 포함하는데, 일반적으로 당업자에게 익숙하므로, 이를 구조적 특징의 기능은 더 이상 설명하지 않겠다.

제7도는 고온 화학 증착에 의해 형성된 통상적인 깊은 트렌치 커패시터의 단면도이다. 각종 구조적 특징은 소정의 물질로 트렌치를 충전하고, 침착물과 기판간의 경계에 산화물을 제공하는 것에 관련된다. 깊은 트렌치에 대한 종래의 물질 침착 방법에서는 본 발명에 의해 해결되는 문제점과 유사한 두 가지 문제점이 절연 구조에 있다. 그 중의 하나는 폴리-플레이트(74) 및 캡(78)이 각기, 제5도의 깊은 오목부(53)와 유사하고, 전술한 것과 동일한 침착 메카니즘에 기인한 틈새(seam)(74', 78')를 갖는다는 것이다. 따라서, 열적 산화물이 경계면에서 성장할 때, 그 열적 산화물은 또한 틈새에서도 성장하여 스트레스를 야기한다(이 스트레스는, 차후 전위의 형성에 의해 해소될 수도 있다). 다른 문제점은, CVD와 같은 고온 침착 프로세스는 또한 스트레스에 의해 야기되는 결함 및 전위를 더 많이 생성하는 것이다.

제8도에 도시한 바와 같이, 액상 침착에 의한 개량된 충전공정 및 어닐링에 의한 밀도 증가는 열적 산화물이 성장할 수도 있는 틈새의 생성을 저지한다. 침착이 저온에서 이루어지므로, 스트레스에 의해 야기되는 전위는 발생하지 않는다. 또한, 밀도 증가는 제어가능하고, 예측가능하며 반복적인 방법으로 침착된 물질의 용적을 감소시키고, 열처리에 의해 야기된 스트레스는 완화되며, 전위 및 공극은 열적 산화물의 성장에 의해 충전된다. 또한, 절연 트렌치의 경우와 마찬가지로, 침착된 산화물은 절연 특성이 앙호하고, 절연 상수가 증가됨으로써, 캐피시턴스의 감소없이 트렌치 캐피시터의 크기가 축소될 수 있다.

따라서, 본 발명에 따르면, 열적 산화물의 성장(이것은 어느정도 밀도를 증가시켜, 열적 산화물 증가로 인해 생길 수도 있는 스트레스를 감소시킨다)과 저온 침착(이것은 어느 정도의 열적 밀도 증가를 제공할 수도 있고, 제공하지 않을 수도 있다)을 조합하는 것에 의해, 개선된 품질의 절연 구조, 제조 수율(manufacturing yield) 및 트렌치 같은 배선의 충정 공정을 필요로 하는 여러 구조의 구조적인 특징을 제공할 수 있다.

전술한 바로 알 수 있듯이, 본 발명은 간단한 STI 구조 및 그의 형성 방법을 제공한다. 이 방법은 아주 간단한 자기 정렬 프로세스 단계들만을 포함하는데, 이를 단계는 비교적 저가의 장비로 수행될 수 있다. 상기 구조는 평탄화를 용이하게 하며, 비교적 큰 종횡비의 트렌치에 대한 충전을 가능하게 한다.

또한, 상기 구조는 누설이 매우 작으며 시간과 전기적 및 열적 스트레스 사이클에 걸쳐 매우 안정적이다.

이는 액상 침착 프로세스에 의해 구조내에 야기되는 스트레스가 거의 존재하지 않으며, 또한, 고유 스트레스의 크기가 본 발명의 설명에 대한 참조로부터 당업자에게 명백한 기법으로 산화 및 열처리 조건을 선택함으로써, 매우 낮은 레벨로 유지될 수 있기 때문이다. 또한, 절연 구조를 형성한 다음에 집적회로의 능동 장치의 어떤 부분을 형성하는 경우에는 덜 중요할 수도 있으나, 열적 산화물(30)을 성장시키는데 필요한 열적 사이클은 매우 짧게 되어, 금속성 도선이 존재하지 않는 한 다양한 형태의 전자장치 및 그의 부분들을 형성하는데 허용된 열처리 경비의 범주내에 들어 맞을 것이다.

초기 레지스트 노출 이 후에 프로세스가 전체적으로 자기 정렬되므로, 본 발명의 프로세스 및 구조는, 어떤 이용가능한 수준의 리소그라픽 기법 및 어떤 이용가능한 수준의 리소그라픽 정밀도로 이를 수 있는 어떠한 설계를 및 최소의 배선폭에도 적합하다. 본 발명은 실리콘 기판에 한정되지 않고, 액상으로부터 침착된 실리카에 의해 기판들 또는 다른 물질의 충돌, 예를 들면, 게르마늄, 인듐 및 칼륨 / 칼륨 아세나이드(germanium, indium and gallium / gallium arsenide)에 대한 경계에서 실리콘 산화물이 열적으로 성장될 수 있게 된다는 것도 인식되어야 한다.

본 발명은 비록 한 가지의 바람직한 실시예로 설명되었지만, 당업자라면 침부된 특허 청구 범위의 사상 및 범주를 벗어남이 없이 다양한 변경이 이루어질 수 있음을 명백히 이해할 것이다.

## (57) 청구의 범위

### 청구항 1

집적회로 장치를 제조하는 방법(a method of forming an integrated circuit device)에 있어서, 반도체 재료의 본체내로 확장하는 트렌치를 형성하는 단계와, 상기 트렌치를 과포화 용액 프로세스(supersaturated solution process)로부터의 액상 침착에 의해 절연 산화물로 실질적으로 충전시키는 단계와, 상기 반도체 재료 및 상기 트렌치내의 상기 절연 산화물을 열처리 하여, 상기 반도체 재료 본체와 상기 절연 산화물간의 경계에 열적 산화물 층을 형성하는 단계를 포함하는 집적회로 장치의 제조 방법.

### 청구항 2

제1항에 있어서, 상기 트렌치를 형성하는 단계는, 상기 반도체 재료의 본체 상에 패터닝된 레지스트 층(a patterned layer of resist)을 도포하는 단계와, 상기 패터닝된 레지스트 층을 통해 상기 반도체 재료의 본체를 에칭(etching)하는 단계를 더 포함하는 집적회로 장치 제조방법.

### 청구항 3

제2항에 있어서, 상기 에칭 단계는 반응성 이온 에칭(reactive ion etching)에 의해 수행되는 집적회로 장치 제조 방법.

### 청구항 4

제2항에 있어서, 상기 패터닝된 레지스트 층을 도포하는 단계는, 블랭킷 레지스트 층(a blanket layer of resist)을 도포하는 단계와, 상기 블랭킷 레지스트 층내의 구멍 패팅(a pattern of apertures)을 개방하

는 단계를 더 포함하는 집적회로 장치 제조방법.

#### 청구항 5

제1항에 있어서, 상기 트렌치를 형성하는 단계는, 상기 반도체 재료의 본체 상에 폴리싱-차단층을 도포하는 단계와, 상기 폴리싱-차단층 상에 패터닝된 레지스트 층을 도포하는 단계와, 상기 패터닝된 레지스트 층을 통해 상기 폴리싱-차단층 및 상기 반도체 재료의 본체를 에칭하는 단계를 더 포함하는 집적회로 장치 제조 방법.

#### 청구항 6

제5항에 있어서, 상기 에칭 단계는 반응성 이온 에칭에 의해 수행되는 집적회로 장치 형성 방법.

#### 청구항 7

제5항에 있어서, 상기 패터닝된 레지스트 층을 도포하는 단계는 블랭킷 레지스트 층을 도포하는 단계와, 상기 블랭킷 레지스트 층 내의 구멍 패턴을 개방하는 단계를 더 포함하는 집적회로 장치 제조 방법.

#### 청구항 8

제2항에 있어서, 상기 실질적으로 상기 트렌치를 충전시키는 단계는 상기 패터닝된 레지스트 층 내의 구멍 부분을 충전시키는 단계를 더 포함하는 집적회로 장치 제조 방법.

#### 청구항 9

제8항에 있어서, 상기 패터닝된 레지스트 층을 제거하는 단계와, 상기 절연 산화물을 평탄화 하는 단계를 더 포함하는 집적회로 장치 제조방법.

#### 청구항 10

제5항에 있어서, 상기 실질적으로 상기 트렌치를 충전시키는 단계는 상기 패터닝된 레지스트 층 내의 구멍 부분을 충전시키는 단계를 더 포함하는 집적회로 장치 제조 방법.

#### 청구항 11

제10항에 있어서, 상기 패터닝된 레지스트 층을 제거하는 단계와, 상기 폴리싱-차단 층의 표면 높이로 절연 산화물을 평탄화하는 단계를 더 포함하는 집적회로 장치 제조방법.

#### 청구항 12

제1항에 있어서, 상기 트렌치의 바닥면에 채널 차단 영역을 형성하는 단계를 더 포함하는 집적회로 장치 제조방법.

#### 청구항 13

반도체 구조를 제조하는 방법에 있어서, ① 실리카를 함유하는 과포화된 액상 용액으로 반도체 구조상의 리세스(recess)내에 실리콘 산화물을 침착시키는 단계와, ② 상기 침착 단계에 의해 침착된 실리콘 산화물의 밀도를 증가시키는(densifying)단계와, ③ 상기 밀도 증가 단계동안 상기 침착 단계에 의해 침착된 상기 실리콘 산화물의 용적 변화(change of volume)를 보상하기에 충분한 용적으로, 상기 침착 단계에 의해 침착된 상기 실리콘 산화물(silicon oxide)과 상기 반도체 재료 사이의 경계면에서 열적 산화물을 성장시킴으로써, 상기 경계에서의 스트레스(stress)를 완화시키는 단계를 포함하는 반도체 구조 제조방법.

### 도면

#### 도면1

도면2

도면3

도면4

도면5

도면6a

도면6b

도면7

도면8