(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5849981号

(P5849981)

(45) 発行日 平成28年2月3日(2016.2.3)

(24) 登録日 平成27年12月11日(2015.12.11)

(51) Int.Cl.

F 1

|             |              |                  |             |              |             |

|-------------|--------------|------------------|-------------|--------------|-------------|

| <b>G09F</b> | <b>9/302</b> | <b>(2006.01)</b> | <b>G09F</b> | <b>9/302</b> | <b>C</b>    |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  | <b>680H</b> |

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  | <b>611A</b> |

| <b>G09F</b> | <b>9/30</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  | <b>611H</b> |

| <b>H01L</b> | <b>27/32</b> | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  | <b>641Q</b> |

請求項の数 13 (全 46 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2013-62650 (P2013-62650)    |

| (22) 出願日  | 平成25年3月25日 (2013.3.25)        |

| (65) 公開番号 | 特開2014-186258 (P2014-186258A) |

| (43) 公開日  | 平成26年10月2日 (2014.10.2)        |

| 審査請求日     | 平成27年2月13日 (2015.2.13)        |

|           |                                        |

|-----------|----------------------------------------|

| (73) 特許権者 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号 |

| (74) 代理人  | 110001357<br>特許業務法人つばさ国際特許事務所          |

| (72) 発明者  | 甚田 誠一郎<br>東京都港区港南1丁目7番1号 ソニー株式会社内      |

| (72) 発明者  | 泉 岳<br>東京都港区港南1丁目7番1号 ソニー株式会社内         |

審査官 謹園 信博

最終頁に続く

(54) 【発明の名称】表示装置および電子機器

## (57) 【特許請求の範囲】

## 【請求項1】

第1の基本色光を発する第1の画素と、第2の基本色光を発する第2の画素と、基本色光以外の一の色光を発する非基本色画素との組み合わせから構成される第1の画素セットと、

前記第1の基本色光を発する第1の画素と、第3の基本色光を発する第3の画素と、前記一の色光を発する非基本色画素との組み合わせから構成される第2の画素セットと、

第1の方向に延伸する複数の信号線と

を備え、

前記第1の画素セットおよび前記第2の画素セットは、前記第1の方向および前記第1の方向と交差する第2の方向のいずれか一方または双方において、交互に配置され、

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は、それぞれ、画素電極を含む発光素子を有し、

前記第1の画素の画素電極は、前記複数の信号線のうちの、その第1の画素が属する画素セットの配置領域内に配置された所定数の信号線のいずれとも重なるように配置され、

前記非基本色画素の画素電極は、前記複数の信号線のうちの、その非基本色画素が属する画素セットの配置領域内に配置された所定数の信号線のいずれとも重なるように配置されている

表示装置。

## 【請求項2】

10

20

前記第2の画素の画素電極および前記第3の画素の画素電極は、前記複数の信号線のいずれとも重ならないように配置されている

請求項1に記載の表示装置。

**【請求項3】**

前記信号線に画素信号を印加する駆動部をさらに備え、

前記画素信号では、各画素の輝度を画定する輝度信号部分が時間軸上で連なっている

請求項1または請求項2に記載の表示装置。

**【請求項4】**

前記第2の基本色光に対応する第1の輝度情報マップに対してフィルタ処理を行うとともに、前記第3の基本色光に対応する第2の輝度情報マップに対してフィルタ処理を行うフィルタ部と、

フィルタ処理された第1の輝度情報マップから、前記第1の画素セットに対応する位置の第1の輝度情報を抽出するとともに、フィルタ処理された第2の輝度情報マップから、前記第2の画素セットに対応する位置の第2の輝度情報を抽出する輝度情報抽出部と

をさらに備え、

前記駆動部は、前記第1の輝度情報に基づいて前記第2の画素に対応する前記輝度信号部分を生成するとともに、前記第2の輝度情報に基づいて前記第3の画素に対応する前記輝度信号部分を生成する

請求項3に記載の表示装置。

**【請求項5】**

前記第1の画素セットが、第1の画素セル内に配置され、

前記第2の画素セットが、第2の画素セル内に配置され、

前記第1の画素セルにおいて、前記第1の画素および前記非基本色画素は、前記第1の方向に配列されるとともに、前記第2の画素と前記第2の方向において配列され、

前記第2の画素セルにおいて、前記第1の画素および前記非基本色画素は、前記第1の方向に配列されるとともに、前記第3の画素と前記第2の方向において配列されている

請求項1から請求項4のいずれか一項に記載の表示装置。

**【請求項6】**

前記第1の画素セットが、第1の画素セル内に配置され、

前記第2の画素セットが、第2の画素セル内に配置され、

前記第1の画素セルにおいて、前記第1の画素、前記第2の画素、および前記非基本色画素は、前記第2の方向に配列され、

前記第2の画素セルにおいて、前記第1の画素、前記第3の画素、および前記非基本色画素は、前記第2の方向に配列されている

請求項1から請求項4のいずれか一項に記載の表示装置。

**【請求項7】**

前記第1の画素セットが、第1の画素セル内に配置され、

前記第2の画素セットが、第2の画素セル内に配置され、

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素の開口部は円形または橢円形であり、

前記第1の画素セルにおいて、前記第1の画素、前記第2の画素、および前記非基本色画素は、互いに隣り合うように配置されるとともに、そのうちの2つは、前記第2の方向に配列され、

前記第2の画素セルにおいて、前記第1の画素、前記第3の画素、および前記非基本色画素は、互いに隣り合うように配置されるとともに、そのうちの2つは、前記第2の方向に配列されている

請求項1から請求項4のいずれか一項に記載の表示装置。

**【請求項8】**

前記第1の画素セットは、複数の第1の画素セル内に、互いに異なる配置パターンとなるように配置され、

10

20

30

40

50

前記第2の画素セットは、複数の第2の画素セル内に、互いに異なる配置パターンとなるように配置されている

請求項5から請求項7のいずれか一項に記載の表示装置。

【請求項9】

前記第2の画素における開口領域、および前記第3の画素における開口領域は、前記第1の画素における開口領域、および前記非基本色画素における開口領域のいずれよりも大きい

請求項1から請求項8のいずれか一項に記載の表示装置。

【請求項10】

前記第1の画素における開口領域は、前記非基本色画素の開口領域以上の大きさである

請求項9に記載の表示装置。 10

【請求項11】

前記第1の基本色光は緑色光であり、

前記第2の基本色光は青色光であり、

前記第3の基本色光は赤色光である

請求項1から請求項10のいずれか一項に記載の表示装置。

【請求項12】

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は、それ

ぞれ、

容量素子と、

ドレンと、前記容量素子の一端に接続されたゲートと、前記容量素子の他端に接続さ

れたソースとを含むトランジスタと

を有する

請求項1から請求項11のいずれか一項に記載の表示装置。

【請求項13】

表示装置と

前記表示装置に対して動作制御を行う制御部と

を備え、

前記表示装置は、

第1の基本色光を発する第1の画素と、第2の基本色光を発する第2の画素と、基本色

光以外の一の色光を発する非基本色画素との組み合わせから構成される第1の画素セット

と、

前記第1の基本色光を発する第1の画素と、第3の基本色光を発する第3の画素と、前

記一の色光を発する非基本色画素との組み合わせから構成される第2の画素セットと、

第1の方向に延伸する複数の信号線と

を備え、

前記第1の画素セットおよび前記第2の画素セットは、前記第1の方向および前記第1

の方向と交差する第2の方向のいずれか一方または双方において、交互に配置され、

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は、それ

ぞれ、画素電極を含む発光素子を有し、

前記第1の画素の画素電極は、前記複数の信号線のうちの、その第1の画素が属する画

素セットの配置領域内に配置された所定数の信号線のいずれとも重なるように配置され、

前記非基本色画素の画素電極は、前記複数の信号線のうちの、その非基本色画素が属す

る画素セットの配置領域内に配置された所定数の信号線のいずれとも重なるように配置さ

れている

電子機器。

【発明の詳細な説明】

【技術分野】

10

20

30

40

50

## 【0001】

本開示は、電流駆動型の表示素子を有する表示装置、およびそのような表示装置を備えた電子機器に関する。

## 【背景技術】

## 【0002】

近年、画像表示を行う表示装置の分野では、発光素子として、流れる電流値に応じて発光輝度が変化する電流駆動型の光学素子、例えば有機EL (Electro Luminescence) 素子を用いた表示装置（有機EL表示装置）が開発され、商品化が進められている。発光素子は、液晶素子などと異なり自発光素子であり、別に光源（バックライト）を設ける必要ない。そのため、有機EL表示装置は、光源を必要とする液晶表示装置と比べて画像の視認性が高く、消費電力が低く、かつ素子の応答速度が速いなどの特徴を有する。

10

## 【0003】

表示装置は、例えば、赤色（R）、緑色（G）、および青色（B）の光（基本色光）を組み合わせて、任意の色の光を生成する。例えば、特許文献1, 2には、赤色（R）と青色（B）のサブ画素を、緑色（G）のサブ画素よりも大きく形成した有機EL表示装置が開示されている。

## 【先行技術文献】

## 【特許文献】

## 【0004】

【特許文献1】特開2011-034050号公報

20

【特許文献2】特開2011-249334号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0005】

ところで、電子機器は、一般に低い消費電力が望まれておらず、表示装置についても、消費電力の低減が期待されている。また、表示装置では、一般に高画質が望まれており、さらなる画質の向上が期待されている。

## 【0006】

本開示はかかる問題点に鑑みてなされたもので、その目的は、消費電力を低減するとともに画質を高めることができる表示装置および電子機器を提供することにある。

30

## 【課題を解決するための手段】

## 【0007】

本開示の表示装置は、第1の画素セットと、第2の画素セットと、複数の信号線とを備えている。第1の画素セットは、第1の基本色光を発する第1の画素と、第2の基本色光を発する第2の画素と、基本色光以外の一の色光を発する非基本色画素との組み合わせから構成されるものである。第2の画素セットは、第1の基本色光を発する第1の画素と、第3の基本色光を発する第3の画素と、一の色光を発する非基本色画素との組み合わせから構成されるものである。複数の信号線は、第1の方向に延伸するものである。上記第1の画素セットおよび第2の画素セットは、第1の方向および第1の方向と交差する第2の方向のいずれか一方または双方において、交互に配置されている。上記第1の画素、第2の画素、第3の画素、および非基本色画素は、それぞれ、画素電極を含む発光素子を有し、第1の画素の画素電極は、複数の信号線のうちの、その第1の画素が属する画素セットの配置領域内に配置された所定数の信号線のいずれとも重なるように配置され、非基本色画素の画素電極は、複数の信号線のうちの、その非基本色画素が属する画素セットの配置領域内に配置された所定数の信号線のいずれとも重なるように配置されている。

40

## 【0008】

本開示の電子機器は、上記表示装置を備えたものであり、例えば、テレビジョン装置、デジタルカメラ、パソコンコンピュータ、ビデオカメラあるいは携帯電話等の携帯端末装置などが該当する。

## 【0009】

50

本開示の表示装置および電子機器では、第1の画素、第2の画素、および非基本色画素の組み合わせから構成される第1の画素セットと、第1の画素、第3の画素、および非基本色画素の組み合わせから構成される第2の画素セットとが並設される。その際、この第1の画素セットおよび第2の画素セットは、第1の方向および第2の方向のいずれか一方または双方において交互に配置される。

【発明の効果】

【0010】

本開示の表示装置および電子機器によれば、第1の画素セットおよび第2の画素セットが、第1の方向および第2の方向のいずれか一方または双方において、交互に配置されるようにしたので、消費電力を低減することができるとともに、画質を高めることができる

10

。 【図面の簡単な説明】

【0011】

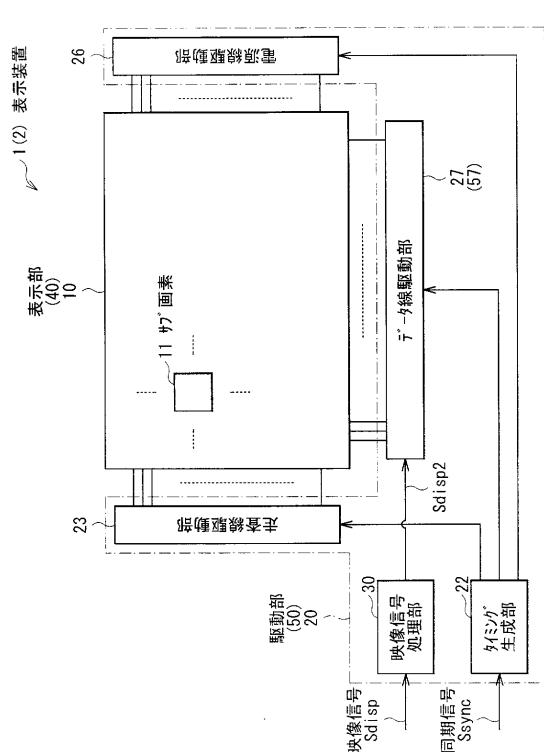

【図1】本開示の実施の形態に係る表示装置の一構成例を表すブロック図である。

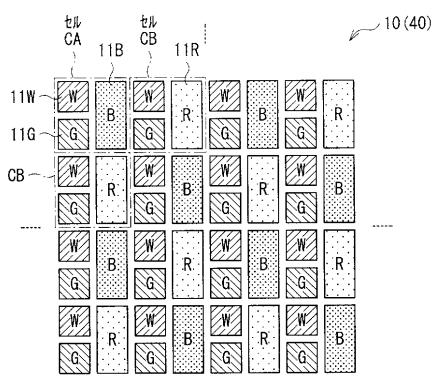

【図2】図1に示した表示部におけるサブ画素の配置例を表す模式図である。

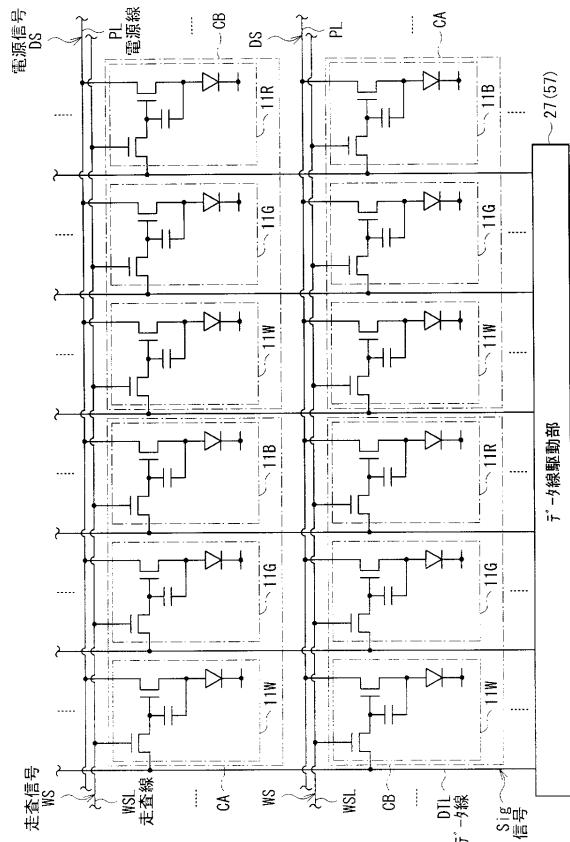

【図3】図1に示した表示部の一構成例を表す回路図である。

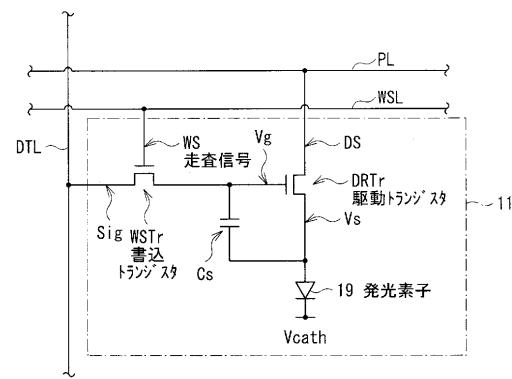

【図4】図1に示したサブ画素の一構成例を表す回路図である。

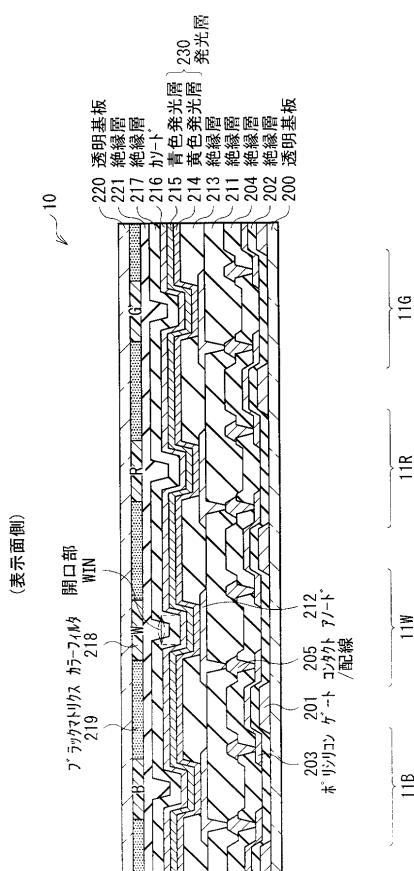

【図5】図1に示した表示部の一構成例を表す断面図である。

【図6A】図2に示した一のセルの一構成例を表す模式図である。

【図6B】図2に示した他のセルの一構成例を表す模式図である。

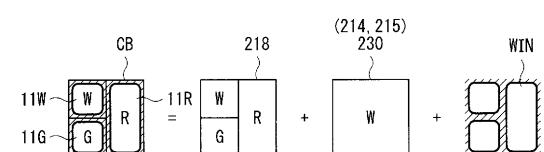

【図7】図2に示した表示部におけるアノードの配置の一例を表す平面図である。

20

【図8】図1に示した映像信号処理部の一構成例を表すブロック図である。

【図9A】図8に示した輝度情報抽出部の一動作例を表す説明図である。

【図9B】図8に示した輝度情報抽出部の一動作例を表す他の説明図である。

【図10】図1に示した表示装置の一動作例を表すタイミング波形図である。

【図11】比較例に係る表示部におけるサブ画素の配置を表す模式図である。

【図12】図11に示した表示部の一構成例を表す回路図である。

【図13】他の比較例に係る表示部におけるサブ画素の配置を表す模式図である。

【図14】他の比較例に係るアノードの配置を表す平面図である。

【図15】第1の実施の形態の変形例に係る表示部の一構成例を表す模式図である。

30

【図16】第1の実施の形態の他の変形例に係るサブ画素の一配置例を表す模式図である。

。 【図17】第1の実施の形態の他の変形例に係るサブ画素の一配置例を表す模式図である

。 【図18】第1の実施の形態の他の変形例に係るサブ画素の一配置例を表す模式図である

。 【図19】第1の実施の形態の他の変形例に係るサブ画素の一配置例を表す模式図である

。 【図20】第1の実施の形態の他の変形例に係るサブ画素の一配置例を表す模式図である

40

。 【図21】第1の実施の形態の他の変形例に係るサブ画素の一配置例を表す模式図である

。 【図22】第1の実施の形態の他の変形例に係るアノードの一配置例を表す平面図である

。 【図23】第1の実施の形態の他の変形例に係るアノードの一配置例を表す平面図である

。 【図24】第1の実施の形態の他の変形例に係るサブ画素の一配置例を表す模式図である

。 【図25】第1の実施の形態の他の変形例に係るサブ画素の一配置例を表す模式図である

50

【図26】第1の実施の形態の他の変形例に係るサブ画素の一配置例を表す模式図である。

【図27】第1の実施の形態の他の変形例に係るアノードの一配置例を表す平面図である。

【図28】第1の実施の形態の他の変形例に係るアノードの一配置例を表す平面図である。

【図29】第1の実施の形態の他の変形例に係る表示部の一構成例を表す断面図である。

【図30A】第1の実施の形態の他の変形例に係る一のセルの一構成例を表す模式図である。

【図30B】第1の実施の形態の他の変形例に係る他のセルの一構成例を表す模式図である。 10

【図31A】第1の実施の形態の他の変形例に係る一のセルの一構成例を表す模式図である。

【図31B】第1の実施の形態の他の変形例に係る他のセルの一構成例を表す模式図である。

【図32A】第1の実施の形態の他の変形例に係る一のセルの一構成例を表す模式図である。

【図32B】第1の実施の形態の他の変形例に係る他のセルの一構成例を表す模式図である。

【図33】第1の実施の形態の他の変形例に係るサブ画素の一配置例を表す模式図である。 20

【図34】第1の実施の形態の他の変形例に係る開口部の一構成例を表す説明図である。

【図35】図34に示した開口部における光線を示す説明図である。

【図36】第1の実施の形態の他の変形例に係る開口部の一配置例を表す平面図である。

【図37】図36に示した表示部の一構成例を表す断面図である。

【図38】第1の実施の形態の他の変形例に係る表示部の一構成例を表す回路図である。

【図39】図38に示した表示部におけるアノードの一配置例を表す平面図である。

【図40】図38に示した表示部の一動作例を表すタイミング波形図である。

【図41】第2の実施の形態に係る表示装置におけるアノードの一配置例を表す平面図である。 30

【図42】第2の実施の形態に係る信号の一例を表す波形図である。

【図43】第2の実施の形態に係る表示装置の一動作例を表すタイミング波形図である。

【図44】第2の実施の形態に係る表示装置の動作を説明するための説明図である。

【図45】第2の実施の形態に係る表示装置の動作を説明するための他の説明図である。

【図46】第2の実施の形態に係る表示装置の一動作例を表すタイミング波形図である。

【図47】第2の実施の形態に係る表示装置の動作を説明するための説明図である。

【図48】第2の実施の形態に係る表示装置の動作を説明するための他の説明図である。

【図49】第2の実施の形態の変形例に係る表示装置の一動作例を表すタイミング波形図である。

【図50】実施の形態に係る表示装置が適用されたテレビジョン装置の外観構成を表す斜視図である。 40

【図51】変形例に係るサブ画素の一構成例を表す回路図である。

【図52】変形例に係るサブ画素の他の構成例を表す回路図である。

【発明を実施するための形態】

【0012】

以下、本開示の実施の形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

1. 第1の実施の形態

2. 第2の実施の形態

3. 適用例

## 【0013】

&lt;1. 第1の実施の形態&gt;

## [構成例]

図1は、第1の実施の形態に係る表示装置の一構成例を表すものである。表示装置1は、有機EL素子を用いた、アクティブマトリックス方式の表示装置である。

## 【0014】

表示装置1は、表示部10と、駆動部20とを備えている。駆動部20は、映像信号処理部30と、タイミング生成部22と、走査線駆動部23と、電源線駆動部26と、データ線駆動部27とを有している。

## 【0015】

表示部10は、複数のサブ画素11が配置されたものである。具体的には、表示部10には、赤色(R)、緑色(G)、青色(B)、白色(W)の4つのサブ画素11R, 11G, 11B, 11Wが配置されている。以下、4つのサブ画素11R, 11G, 11B, 11Wのうちの任意の1つを表すものとしてサブ画素11を適宜用いるものとする。

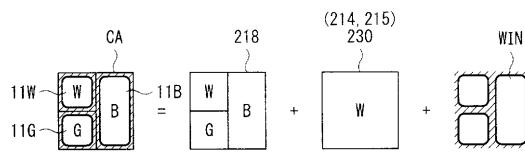

## 【0016】

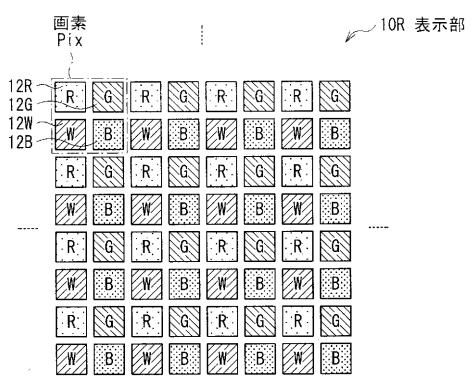

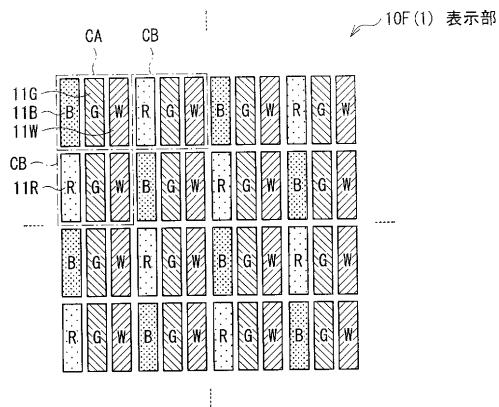

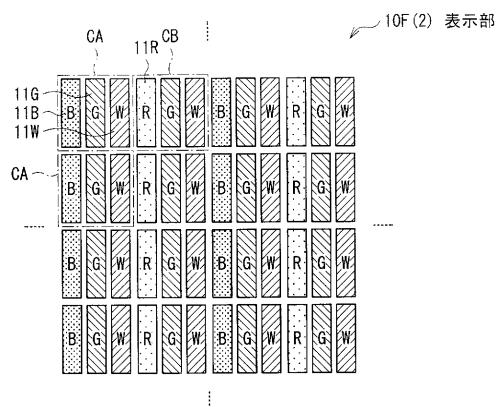

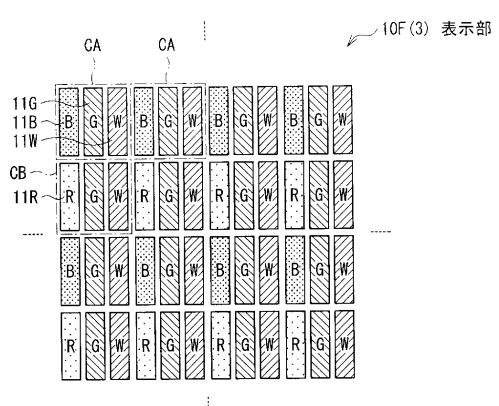

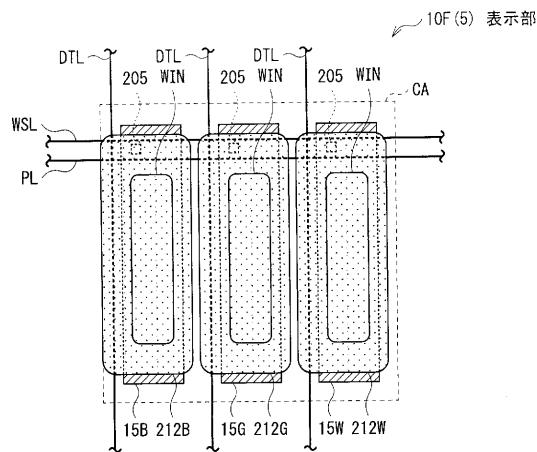

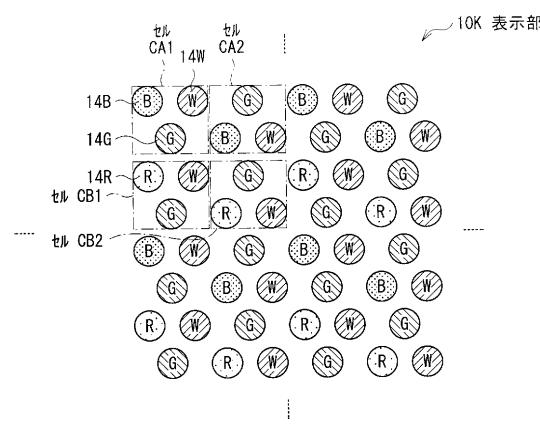

図2は、表示部10におけるサブ画素11の配置の一例を模式的に表すものである。図2において、網掛け部分は、4つのサブ画素11R, 11G, 11B, 11Wの開口部WINを表している。表示部10には、3つのサブ画素11W, 11G, 11Bにより構成されるセルCAと、3つのサブ画素11W, 11G, 11Rにより構成されるセルCBが並設されている。すなわち、セルCAは、4色のサブ画素11のうちの赤色のサブ画素11Rを省いたものであり、セルCBは、4色のサブ画素11のうちの青色のサブ画素11Bを省いたものである。セルCAにおいて、この例では、白色(W)のサブ画素11Wは左上に配置され、緑色(G)のサブ画素11Gは左下に配置され、青色(B)のサブ画素11Bは右側に配置されている。同様に、セルCBにおいて、この例では、白色(W)のサブ画素11Wは左上に配置され、緑色(G)のサブ画素11Gは左下に配置され、赤色(R)のサブ画素11Rは右側に配置されている。これにより、表示部10では、サブ画素11R, 11Bが、サブ画素11W, 11Gよりも少なく形成されるとともに、サブ画素11R, 11Bの開口部WINが、サブ画素11W, 11Gの開口部WINよりも大きく形成されるようになっている。

## 【0017】

図2に示すように、セルCAおよびセルCBは、列方向(垂直方向)に交互に配置されるとともに、行方向(水平方向)に交互に配置されている。これにより、白色のサブ画素11Wおよび緑色のサブ画素11Gは、列方向において交互に配置される。そして、赤色のサブ画素11Rおよび青色のサブ画素11Bは、列方向において交互に配置されるとともに、行方向において交互に配置される。すなわち、表示部10におけるサブ画素11Rの配置パターンおよびサブ画素11Bの配置パターンは、それぞれ市松模様を構成するようになっている。

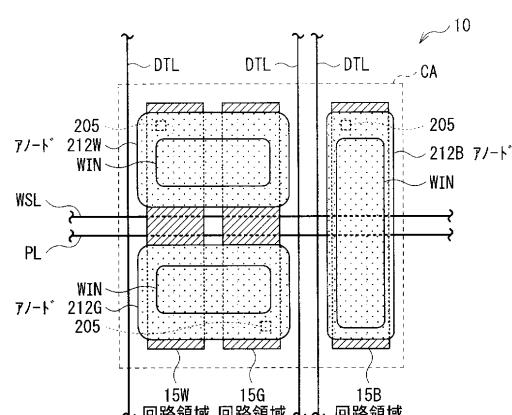

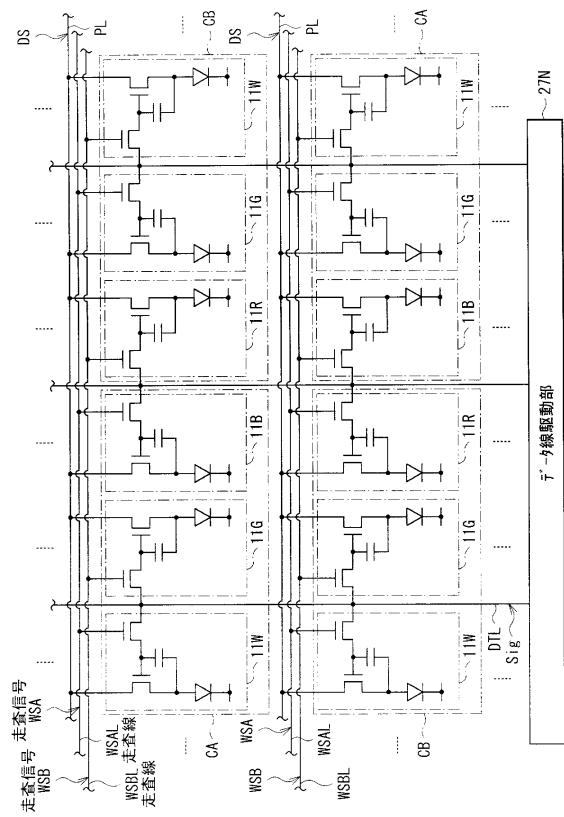

## 【0018】

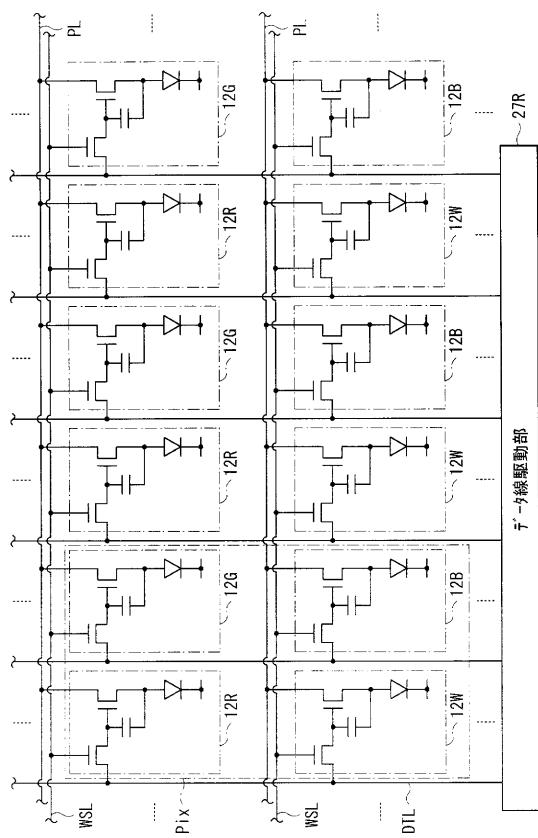

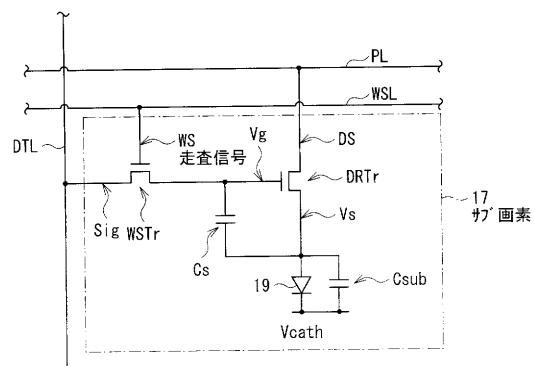

図3は、表示部10の回路構成の一例を表すものである。表示部10は、行方向に延伸する複数の走査線W<sub>SL</sub>および複数の電源線P<sub>L</sub>と、列方向に延伸する複数のデータ線D<sub>TL</sub>とを有している。データ線D<sub>TL</sub>の一端はデータ線駆動部27に接続されている。また、図示していないが、走査線W<sub>SL</sub>の一端は走査線駆動部23に接続され、電源線P<sub>L</sub>の一端は電源線駆動部26に接続されている。各サブ画素11は、走査線W<sub>SL</sub>とデータ線D<sub>TL</sub>との交差部に配置されている。1つのセルCAに属するサブ画素11W, 11G, 11Bは、同じ走査線W<sub>SL</sub>および同じ電源線P<sub>L</sub>に接続されるとともに、互いに異なるデータ線D<sub>TL</sub>に接続されている。同様に、1つのセルCBに属するサブ画素11W, 11G, 11Rは、同じ走査線W<sub>SL</sub>および同じ電源線P<sub>L</sub>に接続されるとともに、互いに異なるデータ線D<sub>TL</sub>に接続されている。

## 【0019】

図4は、サブ画素11の回路構成の一例を表すものである。サブ画素11は、書き込みトランジ

10

20

30

40

50

ンジスタW S T rと、駆動トランジスタD R T rと、発光素子1 9と、容量素子C sとを備えている。すなわち、この例では、サブ画素1 1は、2つのトランジスタ（書込トランジスタW S T r、駆動トランジスタD R T r）および1つの容量素子C sを用いて構成される、いわゆる「2 T r 1 C」の構成を有するものである。

## 【0020】

書込トランジスタW S T rおよび駆動トランジスタD R T rは、例えば、NチャネルM O S (Metal Oxide Semiconductor)型のT F T (Thin Film Transistor; 薄膜トランジスタ)により構成されるものである。書込トランジスタW S T rは、ゲートが走査線W S Lに接続され、ソースがデータ線D T Lに接続され、ドレインが駆動トランジスタD R T rのゲートおよび容量素子C sの一端に接続されている。駆動トランジスタD R T rは、ゲートが書込トランジスタW S T rのドレインおよび容量素子C sの一端に接続され、ドレインが電源線P Lに接続され、ソースが容量素子C sの他端および発光素子1 9のアノードに接続されている。

10

## 【0021】

容量素子C sは、一端が駆動トランジスタD R T rのゲート等に接続され、他端は駆動トランジスタD R T rのソース等に接続されている。発光素子1 9は、有機E L素子を用いて構成された発光素子であり、アノードが駆動トランジスタD R T rのソースおよび容量素子C sの他端に接続され、カソードには、駆動部2 0によりカソード電圧V cathが供給されている。

## 【0022】

20

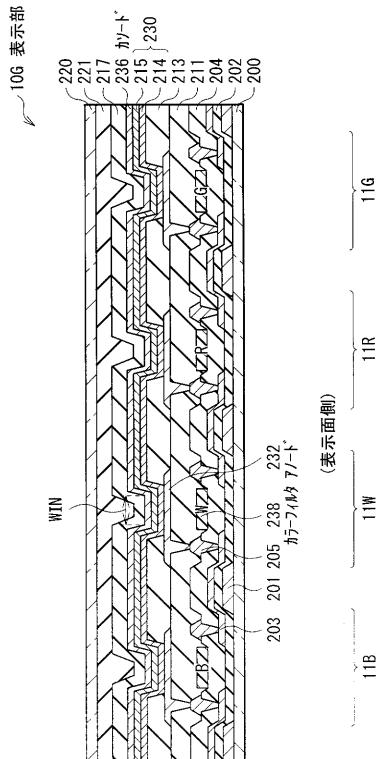

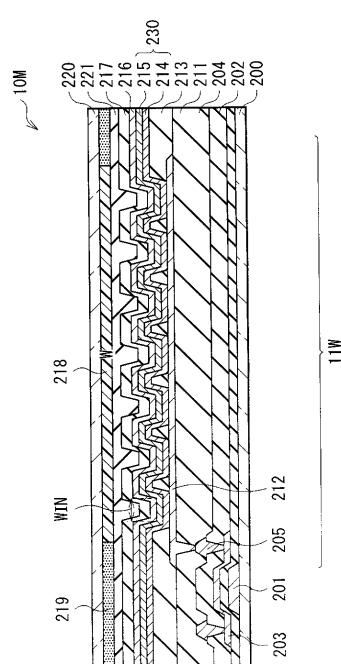

図5は、表示部1 0の断面図を表すものである。表示部1 0は、透明基板2 0 0と、ゲート2 0 1と、ポリシリコン2 0 3と、アノード2 1 2と、発光層2 3 0と、カソード2 1 6と、カラーフィルタ2 1 8とを有している。

## 【0023】

透明基板2 0 0は、表示部1 0の支持基板であり、例えば、ガラスやプラスチックなどにより構成されている。透明基板2 0 0上には、ゲート2 0 1が形成されている。このゲート2 0 1は、例えばモリブデン(Mo)などにより構成される。透明基板2 0 0およびゲート2 0 1の上には絶縁層2 0 2が形成されている。この絶縁層2 0 2は、例えば、酸化シリコン(SiO<sub>2</sub>)や、窒化シリコン(SiNx)などにより構成される。この絶縁層2 0 2の上には、ゲート2 0 1に対応する領域にポリシリコン2 0 3が形成されている。ゲート2 0 1およびポリシリコン2 0 3は、駆動トランジスタD R T rなどを構成するものである。なお、この例では、ゲート2 0 1の上部にポリシリコン2 0 3を形成する、いわゆるボトムゲート構造によりトランジスタを構成したが、これに限定されるものではなく、ゲートの下部にポリシリコンを形成する、いわゆるトップゲート構造によりトランジスタを構成してもよい。ポリシリコン2 0 3および絶縁層2 0 2の上には、絶縁層2 0 4が形成されている。この絶縁層2 0 4は、例えば絶縁層2 0 2と同様の材料により構成される。また、ポリシリコン2 0 3が形成された領域の一部には、絶縁層2 0 4を貫通するように、コンタクト/配線2 0 5が形成されている。配線2 0 5は、例えば、チタン(Ti) / アルミニウム(A1) / チタン(Ti)の3層により構成することができる。

30

## 【0024】

40

絶縁層2 0 4の上には、絶縁層2 1 1が形成されている。絶縁層2 1 1は、例えば、ポリイミドやアクリル樹脂などにより構成される。絶縁層2 1 1の上には、アノード2 1 2が形成されている。アノード2 1 2は、絶縁層2 1 1を貫通して、駆動トランジスタD R T rのソースに係るコンタクト/配線2 0 5と接続されている。アノード2 1 2は、例えば、ITO / A1合金、A1合金、ITO / Ag、ITO / Ag合金などにより構成されている。すなわち、アノード2 1 2は、光を反射する性質を有することが望ましい。アノード2 1 2および絶縁層2 1 1の上には、絶縁層2 1 3が形成されている。絶縁層2 1 3は、例えば絶縁層2 1 1と同様の材料により構成される。この絶縁層2 1 3には、アノード2 1 2が形成された領域の一部に開口部WINが設けられている。アノード2 1 2および絶縁層2 1 3の上部には、黄色発光層2 1 4および青色発光層2 1 5からなる発光層2

50

30 が一様に形成されている。黄色発光層214は、黄色(Y)の光を発する有機EL層であり、青色発光層215は、青色(B)の光を発する有機EL層である。この黄色発光層214は、黄色に光る材料により構成してもよいし、または、緑色(G)に光る材料に赤色(R)に光る材料をドープして構成してもよい。青色発光層215は、例えば、青色に光る材料により構成することができる。青色発光層215の上には、カソード216が一様に形成されている。カソード216は、透明または半透明の電極であり、例えば、マグネシウム銀(MgAg)や、IZO(登録商標)により構成することができる。マグネシウム銀で構成した場合には、膜厚を例えば数nm程度にすることにより半透明にすることができる。IZOで構成した場合には、例えば数十nm~数千nmの膜厚で形成することができる。すなわち、IZOは透明な材料であるため、所望の低いシート抵抗値を実現できるようにやや厚く形成することができる。カソード216の上には、この例では絶縁層217が形成されている。絶縁層217は、例えば窒化シリコン(SiNx)などにより構成される。絶縁層217は、発光層230に水分が侵入し、発光効率などの特性が変化するのを防止するために設けられるものである。なお、この水分の侵入に起因する諸問題が他の技術により解決できる場合、この絶縁層217を省いてもよい。この絶縁層217には、封止用の樹脂である絶縁層221を介して、カラーフィルタ218やブラックマトリクス219が表面に形成された透明基板220が貼り合わせられている。赤色(R)のカラーフィルタ218は、サブ画素11Rに対応する部分に配置され、緑色(G)のカラーフィルタ218はサブ画素11Gに対応する部分に配置され、青色(B)のカラーフィルタ218はサブ画素11Bに対応する部分に配置され、白色(W)のカラーフィルタ218はサブ画素11Wに対応する部分に配置されている。

10

#### 【0025】

この構成により、黄色発光層214から射出した黄色の光と、青色発光層215から射出した青色の光は、混ざり合って白色光となり、支持基板である透明基板200とは反対の方向に進む。すなわち、発光素子19は、いわゆるトップエミッション型の発光素子である。そして、この白色光は、カラーフィルタ218を介して表示面より出力される。具体的には、サブ画素11R, 11G, 11Bでは、赤色(R)、緑色(G)、青色(B)のカラーフィルタ218により、白色光から赤色成分、緑色成分、青色成分がそれぞれ分離され出力される。また、サブ画素11Wでは、白色(W)のカラーフィルタ218により白色光の色域が調整される。なお、画質(色域)に対する要求がさほど高くないアプリケーションなどにおいては、白色(W)のカラーフィルタ218を設けなくてもよい。

20

#### 【0026】

図6Aは、セルCAにおける3つのサブ画素11の構成を模式的に表すものであり、図6Bは、セルCBにおける3つのサブ画素11の構成を模式的に表すものである。セルCAにおける3つのサブ画素11W, 11G, 11Bでは、図6Aに示すように、発光層230(黄色発光層214および青色発光層215)の開口部WINから射出した白色(W)の光が、白色(W)、緑色(G)、および青色(B)のカラーフィルタ218をそれぞれ通過する。同様に、セルCBにおける3つのサブ画素11W, 11G, 11Rでは、図6Bに示すように、発光層230の開口部WINから射出した白色(W)の光が、白色(W)、緑色(G)、および赤色(R)のカラーフィルタ218をそれぞれ通過するようになっている。

30

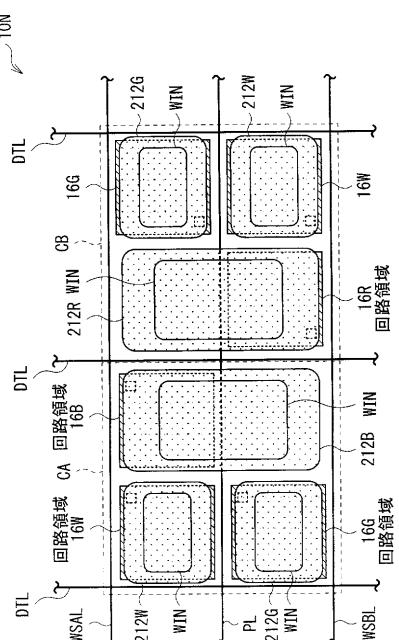

#### 【0027】

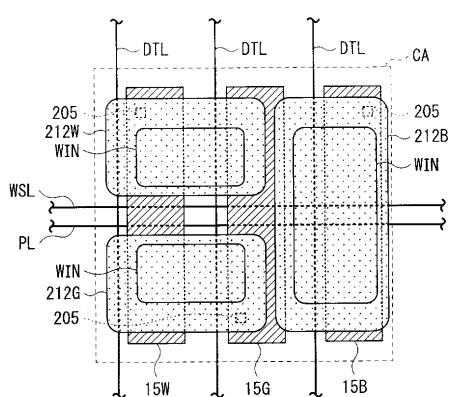

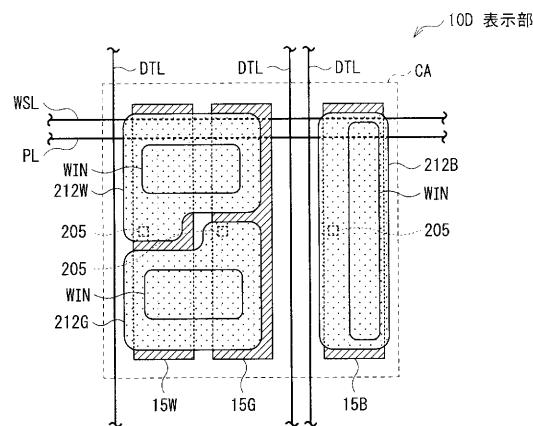

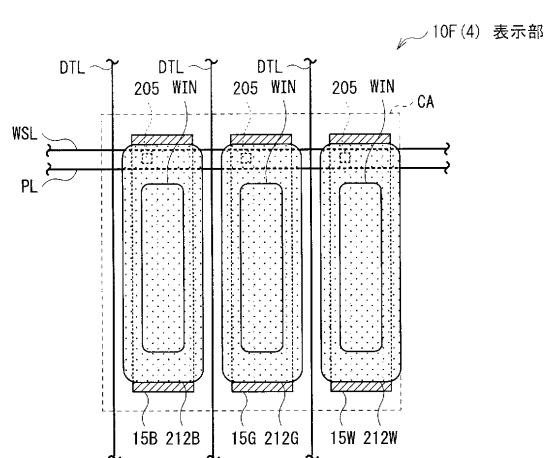

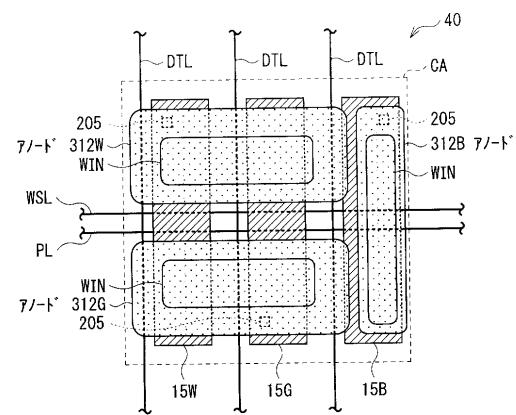

図7は、セルCAにおけるアノード212の配置を表すものである。セルCAには、3つの回路領域15W, 15G, 15Bと、3つのアノード212W, 212G, 212Bが設けられている。

#### 【0028】

回路領域15Wは、サブ画素11Wにおける発光素子19以外の素子(書込トランジスタWSTr、駆動トランジスタDRT<sub>r</sub>、および容量素子Cs)が配置される領域である。同様に、回路領域15Gは、サブ画素11Gにおける発光素子19以外の素子が配置される領域であり、回路領域15Bは、サブ画素11Bにおける発光素子19以外の素子が

40

配置される領域である。これらの回路領域 15W, 15G, 15B には、書込トランジスタ WSTR、駆動トランジスタ DRT、および容量素子 Cs が同じようにレイアウトされている。この例では、回路領域 15G のレイアウトは、回路領域 15W, 15B のレイアウトを 180 度回転し、走査線 WSL および電源線 PL との接続部分を修正したものである。なお、回路領域 15G のレイアウトは、回路領域 15W, 15B のレイアウトを上下反転し、これらの配線との接続部分を修正したものであってもよいし、全く異なる別のレイアウトであってもよい。このように、同じレイアウトを回転または反転して流用することにより、レイアウト作業の効率を高めることができる。この例では、3 つの回路領域 15W, 15G, 15B は、セル CA において、データ線 DTL の延伸方向（列方向）に延伸するとともに、データ線 DTL の延伸方向と直交する方向（行方向）に並設されている。具体的には、この例では、セル CA において、1 本のデータ線 DTL、回路領域 15W、回路領域 15G、2 本のデータ線 DTL、および回路領域 15B が、左から右へこの順に配置されている。このように、回路領域 15 を列方向に延伸するように設けることにより、例えば、駆動トランジスタ DRT のチャネル長（L）を長くすることができ、これにより、サブ画素 11 の特性ばらつきを抑えることができるようになっている。

#### 【0029】

アノード 212W はサブ画素 11W のアノード 212 であり、アノード 212G はサブ画素 11G のアノード 212 であり、アノード 212B はサブ画素 11B のアノード 212 である。これらのアノード 212W, 212G, 212B は、回路領域 15W, 15G, 15B に形成された駆動トランジスタ DRT のソースと、それぞれコンタクト 205 を介して接続されている。セル CA において、アノード 212W は左上に配置され、アノード 212G は左下に配置され、アノード 212B は右側に配置されている。これらのアノード 212W, 212G, 212B は、データ線 DTL と重ならないように配置されている。そして、アノード 212W, 212G, 212B 上の開口部 WIN において、発光層 230 が白色光を発光するようになっている。

#### 【0030】

以上、セル CA について説明したが、セル CB についても同様である。すなわち、セル CB には、3 つの回路領域 15W, 15G, 15R と、3 つのアノード 212W, 212G, 212R が設けられている。回路領域 15R は、サブ画素 11R における発光素子 19 以外の素子が配置される領域であり、アノード 212R は、サブ画素 11R のアノード 212 である。セル CB において、1 本のデータ線 DTL、回路領域 15W、回路領域 15G、2 本のデータ線 DTL、および回路領域 15R が、左から右へこの順に配置されている。また、セル CB において、アノード 212W は左上に配置され、アノード 212G は左下に配置され、アノード 212R は右側に配置されている。これらのアノード 212W, 212G, 212R は、データ線 DTL と重ならないように配置されている。

#### 【0031】

図 1 において、映像信号処理部 30 は、外部から供給される映像信号 Sdisp に対して、RGBW 変換やガンマ変換などを行い、映像信号 Sdisp2 を生成するものである。映像信号 Sdisp は、赤色 (R)、緑色 (G)、および青色 (B) の輝度情報 I を有する RGB 信号である。

#### 【0032】

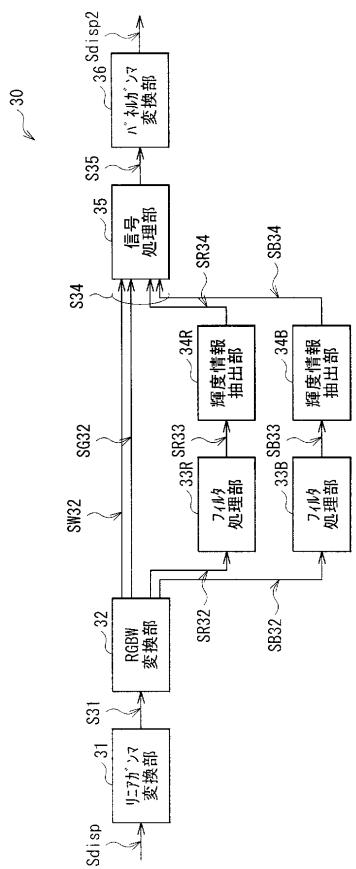

図 8 は、映像信号処理部 30 の一構成例を表すものである。映像信号処理部 30 は、リニアガンマ変換部 31 と、RGBW 変換部 32 と、フィルタ処理部 33R, 33B と、輝度情報抽出部 34R, 34B と、信号処理部 35 と、パネルガンマ変換部 36 とを有している。

#### 【0033】

リニアガンマ変換部 31 は、入力された映像信号 Sdisp を、線形なガンマ特性を有する映像信号 S31 に変換するものである。すなわち、外部から供給される映像信号は、一般的な表示装置の特性を考慮した非線形なガンマ特性を有している。よって、このリニアガンマ変換部 31 は、RGBW 変換部 32 や信号処理部 35 などにおける処理を容易にする

10

20

30

40

50

ため、このような非線形なガンマ特性を線形なガンマ特性に変換する。ガンマ変換部31は、例えばルックアップテーブルを有しており、このルックアップテーブルを用いてこのようなガンマ変換を行うようになっている。

【0034】

R G B W変換部32は、映像信号S31に対してR G B W変換を行うものである。具体的には、R G B W変換部32は、赤色、緑色、および青色の輝度情報Iを有するR G B信号を、赤色(R)、緑色(G)、青色(B)、および白色(W)の輝度情報Iを有するR G B W信号に変換する。そして、R G B W変換部32は、赤色(R)の輝度情報Iを信号S R 3 2として出力し、緑色(G)の輝度情報Iを信号S G 3 2として出力し、青色(B)の輝度情報Iを信号S B 3 2として出力し、白色(W)の輝度情報Iを信号S W 3 2として出力するようになっている。10

【0035】

フィルタ処理部33Rは、信号S R 3 2に対してフィルタ処理を行うものである。このフィルタ処理部33Rは、この例では、低域通過フィルタとして機能するF I R (Finite impulse response) フィルタにより構成されるものである。フィルタ処理部33Rは、入力された信号S R 3 2に基づいて、赤色(R)の輝度情報Iのマップを作成し、そのマップに対してフィルタ処理を行う。そして、フィルタ処理部33Rは、フィルタ処理を行った輝度情報Iを信号S R 3 3として出力するようになっている。

【0036】

フィルタ処理部33Bは、信号S B 3 2に対してフィルタ処理を行うものである。このフィルタ処理部33Bは、フィルタ処理部33Rと同様に、低域通過フィルタとして機能するF I R フィルタにより構成されるものである。フィルタ処理部33Bは、入力された信号S B 3 2に基づいて、青色(B)の輝度情報Iのマップを作成し、そのマップに対してフィルタ処理を行う。そして、フィルタ処理部33Bは、フィルタ処理を行った輝度情報Iを信号S B 3 3として出力するようになっている。20

【0037】

輝度情報抽出部34Rは、信号S R 3 3に含まれる赤色(R)の輝度情報Iから、表示部10に表示する輝度情報Iを抽出するものである。

【0038】

輝度情報抽出部34Bは、信号S B 3 3に含まれる青色(B)の輝度情報Iから、表示部10に表示する輝度情報Iを抽出するものである。30

【0039】

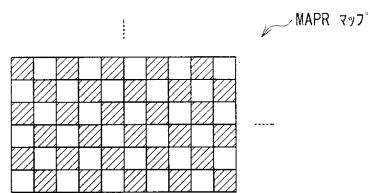

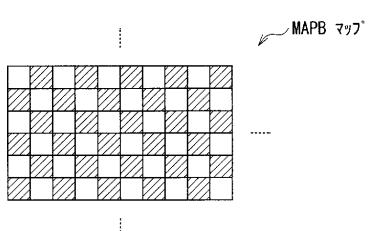

図9Aは、輝度情報抽出部34Rの一動作例を表すものであり、図9Bは、輝度情報抽出部34Bの一動作例を表すものである。輝度情報抽出部34Rは、信号S R 3 3に基づいて、赤色(R)の輝度情報IのマップMAPRを生成する。そして、輝度情報抽出部34Rは、図9Aに示すように、そのマップMAPRから、表示部10における赤色のサブ画素11Rの配置パターン(図2)に応じた座標における輝度情報I(図9Aにおける斜線部)を抽出する。すなわち、輝度情報抽出部34Rは、抽出パターンが市松模様になるように、輝度情報Iを抽出する。そして、輝度情報抽出部34Rは、抽出した輝度情報Iを、信号S R 3 4として出力するようになっている。同様に、輝度情報抽出部34Bは、信号S B 3 3に基づいて、青色(B)の輝度情報IのマップMAPBを生成し、そのマップMAPBから、表示部10における青色のサブ画素11Bの配置パターン(図2)に応じた座標における輝度情報I(図9Bにおける斜線部)を抽出する。そして、輝度情報抽出部34Bは、抽出した輝度情報Iを、信号S B 3 4として出力するようになっている。40

【0040】

このように、映像信号処理部30では、フィルタ処理部33R, 33Bが輝度情報Iに対してフィルタ処理を行う。輝度情報抽出部34R, 34Bは、そのフィルタ処理を行った輝度情報Iから、表示部10に表示する輝度情報Iを抽出している。これにより、表示装置1では、赤色および青色の成分に対してのみ、画像の解像度(エッジの尖銳度)を下げるとともに、抽出された赤色および青色の輝度情報Iが、表示部10におけるサブ画素50

11R, 11Bの位置を反映するようになっている。

【0041】

信号処理部35は、信号SW32, SG32, SR34, SB34からなる映像信号S34に対して所定の信号処理を行い、その結果を映像信号S35として出力するものである。所定の信号処理としては、例えば、映像信号S34により表現される色域および色温度を、表示部10の色域および色温度に変換する、いわゆる色域変換などが挙げられる。

【0042】

パネルガンマ変換部36は、線形なガンマ特性を有する映像信号S35を、表示部10の特性に対応した非線形なガンマ特性を有する映像信号S36に変換（パネルガンマ変換）するものである。このパネルガンマ変換部36は、リニアガンマ変換部31と同様に、例えばルックアップテーブルを有しており、このルックアップテーブルを用いてこのようなガンマ変換を行うようになっている。

【0043】

図1において、タイミング生成部22は、外部から供給される同期信号Ssyncに基づいて、走査線駆動部23、電源線駆動部26、およびデータ線駆動部27に対してそれぞれ制御信号を供給し、これらがお互いに同期して動作するように制御する回路である。

【0044】

走査線駆動部23は、タイミング生成部22から供給された制御信号に従って、複数の走査線WSLに対して走査信号WSを順次印加することにより、サブ画素11を順次選択するものである。

【0045】

電源線駆動部26は、タイミング生成部22から供給された制御信号に従って、複数の電源線PLに対して電源信号DSを順次印加することにより、サブ画素11の発光動作および消光動作の制御を行うものである。電源信号DSは、電圧Vccpと電圧Viniとの間で遷移するものである。後述するように、電圧Viniは、サブ画素11を初期化するための電圧であり、電圧Vccpは、駆動トランジスタDRTに電流を流して発光素子19を発光させるための電圧である。

【0046】

データ線駆動部27は、映像信号処理部30から供給された映像信号Sdisp2およびタイミング生成部22から供給された制御信号に従って、各サブ画素11の発光輝度を指示する画素電圧Vsig、および後述するVth補正を行うための電圧Vofsを含む信号Sigを生成し、各データ線DTLに印加するものである。

【0047】

この構成により、駆動部20は、後述するように、サブ画素11に対して駆動トランジスタDRTの素子ばらつきが画質に与える影響を抑えるための補正（Vth補正およびμ（移動度）補正）を行い、サブ画素11に対して画素電圧Vsigの書き込みを行う。そして、その後に、サブ画素11の発光素子19が、書き込まれた画素電圧Vsigに応じた輝度で発光するようになっている。

【0048】

ここで、サブ画素11Gは、本開示における「第1の画素」の一具体例に対応し、サブ画素11Bは、本開示における「第2の画素」の一具体例に対応し、サブ画素11Rは、本開示における「第3の画素」の一具体例に対応する。サブ画素11Wは、本開示における「非基本色画素」の一具体例に対応する。セルCAを構成するサブ画素11G, 11W, 11Bは、本開示における「第1の画素セット」の一具体例に対応する。セルCBを構成するサブ画素11G, 11W, 11Rは、本開示における「第2の画素セット」の一具体例に対応する。セルCAは、本開示における「第1の画素セル」の一具体例に対応する。セルCBは、本開示における「第2の画素セル」の一具体例に対応する。データ線DTLは、本開示における「信号線」の一具体例に対応する。信号Sigは、本開示における「画素信号」の一具体例に対応する。駆動トランジスタDRTは、本開示における「トランジスタ」の一具体例に対応する。

10

20

30

40

50

## 【0049】

## [動作および作用]

続いて、本実施の形態の表示装置1の動作および作用について説明する。

## 【0050】

## (全体動作概要)

まず、図1を参照して、表示装置1の全体動作概要を説明する。映像信号処理部30は、外部から供給される映像信号S<sub>disp</sub>に対してRGBW変換やガンマ変換などを行い、映像信号S<sub>disp2</sub>を生成する。タイミング生成部22は、外部から供給される同期信号S<sub>sync</sub>に基づいて、走査線駆動部23、電源線駆動部26およびデータ線駆動部27に対してそれぞれ制御信号を供給し、これらがお互いに同期して動作するように制御する。走査線駆動部23は、タイミング生成部22から供給された制御信号に従って、複数の走査線WSLに対して走査信号WSを順次印加することにより、サブ画素11を順次選択する。電源線駆動部26は、タイミング生成部22から供給された制御信号に従って、複数の電源線PLに対して電源信号DSを順次印加することにより、サブ画素11の発光動作および消光動作の制御を行う。データ線駆動部27は、映像信号処理部30から供給された映像信号S<sub>disp2</sub>およびタイミング生成部22から供給された制御信号に従って、各サブ画素11の輝度に対応する画素電圧Vsig、およびV<sub>th</sub>補正を行うための電圧V<sub>ofs</sub>を含む信号Sigを生成し、各データ線DTLに印加する。表示部10は、駆動部20から供給された走査信号WS、電源信号DS、および信号Sigに基づいて表示を行う。

## 【0051】

## (詳細動作)

次に、表示装置1の詳細動作を説明する。

## 【0052】

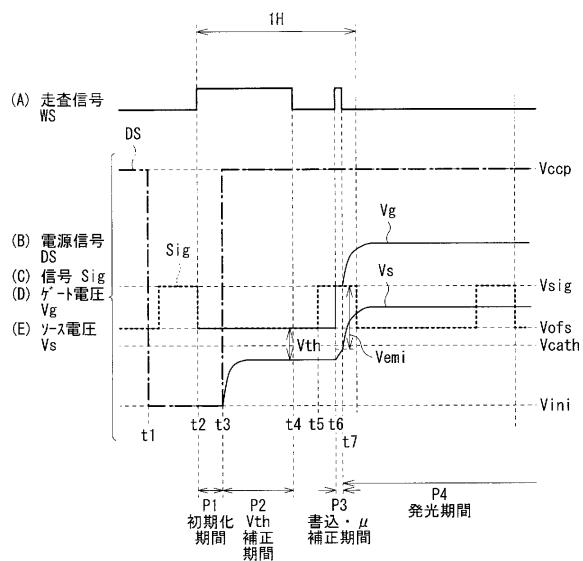

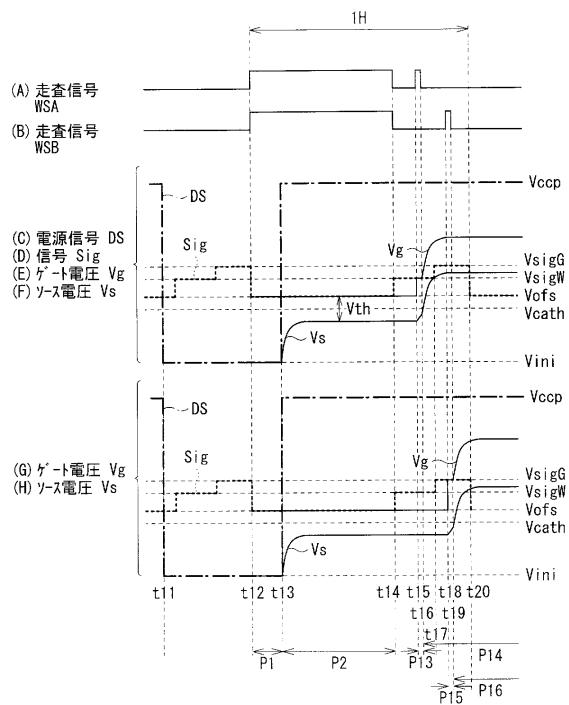

図10は、表示装置1における表示動作のタイミング図を表すものである。この図は、着目した1つのサブ画素11に対する表示駆動の動作例を表すものである。図10において、(A)は走査信号WSの波形を示し、(B)は電源信号DSの波形を示し、(C)は信号Sigの波形を示し、(D)は駆動トランジスタDRT<sub>r</sub>のゲート電圧V<sub>g</sub>の波形を示し、(E)は駆動トランジスタDRT<sub>r</sub>のソース電圧V<sub>s</sub>の波形を示す。

## 【0053】

駆動部20は、1水平期間(1H)内において、サブ画素11の初期化を行い(初期化期間P1)、駆動トランジスタDRT<sub>r</sub>の素子ばらつきが画質に与える影響を抑えるためのV<sub>th</sub>補正を行い(V<sub>th</sub>補正期間P2)、サブ画素11に対して画素電圧Vsigの書き込みを行うとともに、V<sub>th</sub>補正とは異なるμ(移動度)補正を行う(書き込み・μ補正期間P3)。そして、その後に、サブ画素11の発光素子19が、書き込まれた画素電圧Vsigに応じた輝度で発光する(発光期間P4)。以下に、その詳細を説明する。

## 【0054】

まず、電源線駆動部26は、初期化期間P1に先立つタイミングt1において、電源信号DSを電圧V<sub>ccp</sub>から電圧V<sub>ini</sub>に変化させる(図10(B))。これにより、駆動トランジスタDRT<sub>r</sub>がオン状態になり、駆動トランジスタDRT<sub>r</sub>のソース電圧V<sub>s</sub>が、電圧V<sub>ini</sub>に設定される(図10(E))。

## 【0055】

次に、駆動部20は、タイミングt2～t3の期間(初期化期間P1)において、サブ画素11を初期化する。具体的には、タイミングt2において、データ線駆動部27が、信号Sigを電圧V<sub>ofs</sub>に設定し(図10(C))、走査線駆動部23が、走査信号WSの電圧を低レベルから高レベルに変化させる(図10(A))。これにより、書き込みトランジスタWST<sub>r</sub>がオン状態になり、駆動トランジスタDRT<sub>r</sub>のゲート電圧V<sub>g</sub>が電圧V<sub>ofs</sub>に設定される(図10(D))。このようにして、駆動トランジスタDRT<sub>r</sub>のゲート・ソース間電圧V<sub>gs</sub>(=V<sub>ofs</sub>-V<sub>ini</sub>)は、駆動トランジスタDRT<sub>r</sub>の閾値電圧V<sub>th</sub>よりも大きい電圧に設定され、サブ画素11が初期化される。

## 【0056】

10

20

30

40

50

次に、駆動部 20 は、タイミング  $t_3 \sim t_4$  の期間 (V<sub>th</sub>補正期間 P2) において、V<sub>th</sub>補正を行う。具体的には、電源線駆動部 26 が、タイミング  $t_3$  において、電源信号 D<sub>S</sub> を電圧 V<sub>ini</sub> から電圧 V<sub>ccp</sub> に変化させる (図 10 (B))。これにより、駆動トランジスタ D<sub>RT</sub>r は飽和領域で動作するようになり、ドレインからソースに電流 I<sub>ds</sub> が流れ、ソース電圧 V<sub>s</sub> が上昇する (図 10 (E))。その際、この例では、ソース電圧 V<sub>s</sub> は発光素子 19 のカソードの電圧 V<sub>cath</sub> よりも低いため、発光素子 19 は逆バイアス状態を維持し、発光素子 19 には電流は流れない。このようにソース電圧 V<sub>s</sub> が上昇することにより、ゲート・ソース間電圧 V<sub>gs</sub> が低下するため、電流 I<sub>ds</sub> は低下する。この負帰還動作により、電流 I<sub>ds</sub> は “0” (ゼロ) に向かって収束していく。言い換えれば、駆動トランジスタ D<sub>RT</sub>r のゲート・ソース間電圧 V<sub>gs</sub> は、駆動トランジスタ D<sub>RT</sub>r の閾値電圧 V<sub>th</sub> と等しくなる (V<sub>gs</sub> = V<sub>th</sub>) ように収束していく。

10

#### 【0057】

次に、走査線駆動部 23 は、タイミング  $t_4$  において、走査信号 W<sub>S</sub> の電圧を高レベルから低レベルに変化させる (図 10 (A))。これにより、書込トランジスタ W<sub>ST</sub>r はオフ状態になる。そして、データ線駆動部 27 は、タイミング  $t_5$  において、信号 S<sub>ig</sub> を画素電圧 V<sub>sig</sub> に設定する (図 10 (C))。

#### 【0058】

次に、駆動部 20 は、タイミング  $t_6 \sim t_7$  の期間 (書込・μ補正期間 P3) において、サブ画素 11 に対して画素電圧 V<sub>sig</sub> の書き込みを行うとともに μ 補正を行う。具体的には、走査線駆動部 23 が、タイミング  $t_6$  において、走査信号 W<sub>S</sub> の電圧を低レベルから高レベルに変化させる (図 10 (A))。これにより、書込トランジスタ W<sub>ST</sub>r はオン状態になり、駆動トランジスタ D<sub>RT</sub>r のゲート電圧 V<sub>g</sub> が、電圧 V<sub>ofs</sub> から画素電圧 V<sub>sig</sub> に上昇する (図 10 (D))。このとき、駆動トランジスタ D<sub>RT</sub>r のゲート・ソース間電圧 V<sub>gs</sub> が閾値電圧 V<sub>th</sub> より大きくなり (V<sub>gs</sub> > V<sub>th</sub>)、ドレインからソースへ電流 I<sub>ds</sub> が流れるため、駆動トランジスタ D<sub>RT</sub>r のソース電圧 V<sub>s</sub> が上昇する (図 10 (E))。このような負帰還動作により、駆動トランジスタ D<sub>RT</sub>r の素子ばらつきの影響が抑えられ (μ 補正)、駆動トランジスタ D<sub>RT</sub>r のゲート・ソース間電圧 V<sub>gs</sub> は、画素電圧 V<sub>sig</sub> に応じた電圧 V<sub>emi</sub> に設定される。なお、このような μ 補正の方法については、例えば、特開 2006-215213 に記載がある。

20

#### 【0059】

次に、駆動部 20 は、タイミング  $t_7$  以降の期間 (発光期間 P4) において、サブ画素 11 を発光させる。具体的には、タイミング  $t_7$  において、走査線駆動部 23 は、走査信号 W<sub>S</sub> の電圧を高レベルから低レベルに変化させる (図 10 (A))。これにより、書込トランジスタ W<sub>ST</sub>r がオフ状態になり、駆動トランジスタ D<sub>RT</sub>r のゲートがフローティングとなるため、これ以後、容量素子 C<sub>s</sub> の端子間電圧、すなわち、駆動トランジスタ D<sub>RT</sub>r のゲート・ソース間電圧 V<sub>gs</sub> は維持される。そして、駆動トランジスタ D<sub>RT</sub>r に電流 I<sub>ds</sub> が流れるにつれ、駆動トランジスタ D<sub>RT</sub>r のソース電圧 V<sub>s</sub> が上昇し (図 10 (E))、これに伴って駆動トランジスタ D<sub>RT</sub>r のゲート電圧 V<sub>g</sub> も上昇する (図 10 (D))。そして、駆動トランジスタ D<sub>RT</sub>r のソース電圧 V<sub>s</sub> が、発光素子 19 の閾値電圧 V<sub>el</sub> と電圧 V<sub>cath</sub> の和 (V<sub>el</sub> + V<sub>cath</sub>) よりも大きくなると、発光素子 19 のアノード・カソード間に電流が流れ、発光素子 19 が発光する。すなわち、発光素子 19 の素子ばらつきに応じた分だけソース電圧 V<sub>s</sub> が上昇し、発光素子 19 が発光する。

40

#### 【0060】

その後、表示装置 1 では、所定の期間 (1 フレーム期間) が経過したのち、発光期間 P4 から書込期間 P1 に移行する。駆動部 20 は、この一連の動作を繰り返すように表示部 10 を駆動する。

#### 【0061】

(画質および消費電力について)

表示装置 1 は、消費電力を低減するために、いくつかの工夫がなされている。以下に、いくつかの比較例を挙げて、それらの技術について詳細に説明する。

50

## 【0062】

(比較例1)

表示装置1では、図2に示したように、4色のサブ画素のうち、赤色(R)のサブ画素を省いてセルCAを構成するとともに、青色(B)のサブ画素を省いてセルCBを構成したので、以下に説明する表示装置1Rと比べて、画質の低下を抑えつつ、消費電力を低減することができる。

## 【0063】

図11は、比較例1に係る表示装置1Rにおける表示部10Rの一構成例を表すものである。表示部10Rには、複数の画素Pixがマトリクス状に配置されている。各画素Pixは、赤色(R)、緑色(G)、青色(B)、白色(W)の4つのサブ画素12(12R, 12G, 12B, 12W)を有している。この例では、これらの4つのサブ画素12R, 12G, 12B, 12Wは、画素Pixにおいて2行2列で配置されている。具体的には、画素Pixにおいて、左上に赤色(R)のサブ画素12Rを配置し、右上に緑色(G)のサブ画素12Gを配置し、左下に白色(W)のサブ画素12Wを配置し、右下に青色(B)のサブ画素12Bを配置している。

## 【0064】

ここで、比較例1に係る画素Pix(図11)は、本実施の形態におけるセルCAまたはセルCB(図2)に対応するものである。具体的には、本実施の形態におけるセルCAは、比較例1に係る画素Pixから赤色のサブ画素12Rを省いたものに対応しており、本実施の形態におけるセルCBは、比較例1に係る画素Pixから青色のサブ画素12Bを省いたものに対応している。

## 【0065】

図12は、比較例1に係る表示部10Rの回路構成の一例を表すものである。表示部10Rでは、1つの画素Pixに属するサブ画素12Rとサブ画素12Gは、同じ走査線WS(例えばk番目の走査線WS(k))および同じ電源線PL(例えばk番目の電源線PL(k))に接続されている。また、その画素Pixに属するサブ画素12Wとサブ画素12Bは、同じ走査線WS(例えば(k+1)番目の走査線WS(k+1))および同じ電源線PL(例えば(k+1)番目の電源線PL(k+1))に接続されている。

## 【0066】

また、1つの画素Pixに属するサブ画素12Rとサブ画素12Wは、同じデータ線DTL(例えばj番目のデータ線DTL(j))に接続され、その画素Pixに属するサブ画素12Gとサブ画素12Bは、同じデータ線DTL(例えば(j+1)番目のデータ線DTL(j+1))に接続されている。

## 【0067】

比較例1に係る表示装置1Rでは、走査駆動を行う際、1つの画素Pixを構成する4つのサブ画素12のうちの、サブ画素12R, 12Gと、サブ画素12B, 12Wとを、異なる期間において駆動する必要がある。具体的には、例えば、1水平期間の前半においてサブ画素12R, 12Gを駆動し、1水平期間の後半においてサブ画素12B, 12Wを駆動する必要がある。よって、データ線駆動部27Rは、例えば1フレーム期間において、より多くのサブ画素12に、画素電圧Vsigを供給する必要がある。すなわち、データ線DTLを駆動する際の駆動周波数が高くなってしまう。これにより、消費電力が高くなるおそれがある。

## 【0068】

また、比較例1に係る表示装置1Rでは、1つの画素Pixにつき6本の配線(2本の走査線WS、2本の電源線PL、および2本のデータ線DTL)が必要となる。よって、表示装置1Rでは、これらの配線を駆動するための電力を要するため、消費電力が高くなるおそれがある。

## 【0069】

また、比較例1に係る表示装置1Rでは、1つの画素Pixが4つのサブ画素12を有するようにしたので、表示部10Rにおけるサブ画素12の数が多くなる。これにより、各

10

20

30

40

50

サブ画素 1 2 の面積が小さくなるため、開口率が低下してしまう。すなわち、例えば、アノード間隔などのデザインルールにより、アノードの大きさは制限され、またアノードの縁と開口部 W I N の縁との間の距離に関するデザインルールにより開口部 W I N の大きさも制限されるため、開口部 W I N を大きくすることができず、開口率が低下してしまう。このように開口率が低い場合には、開口率が高い場合に比べて、同じ発光輝度を実現するための発光層 2 3 0 の電流密度が高くなってしまい、画質が劣化するおそれがある。すなわち、発光層 2 3 0 を構成する有機 E L 層は、一般に、電流密度が高いほど経時劣化（いわゆる焼き付き）が生じやすいため、電流密度が高くなることにより、画質が低下するおそれがある。

## 【 0 0 7 0 】

10

また、比較例 1 に係る表示装置 1 R では、上述したように駆動周波数が高くなってしまうため、例えば、サブ画素 1 2 に画素電圧 V sig を書き込むための十分な時間が確保しにくくなり、画質が低下するおそれがある。

## 【 0 0 7 1 】

一方、本実施の形態に係る表示装置 1 では、図 2 , 3 に示したように、赤色のサブ画素 1 1 R を省いてセル C A を構成して、1 つのセル C A に属する 3 つのサブ画素 1 1 W , 1 1 G , 1 1 B が同じ走査線 W S L 等に接続されるようにするとともに、青色のサブ画素 1 1 B を省いてセル C B を構成し、1 つのセル C B に属する 3 つのサブ画素 1 1 W , 1 1 G , 1 1 R が同じ走査線 W S L 等に接続されるようにしている。これにより、1 水平期間において、セル C A に属する 3 つのサブ画素 1 1 W , 1 1 G , 1 1 B をまとめて駆動することができ、同様に、1 水平期間において、セル C B に属する 3 つのサブ画素 1 1 W , 1 1 G , 1 1 R をまとめて駆動することができる。よって、データ線駆動部 2 7 は、例えば、1 フレーム期間において、比較例 1 の場合の半分の数のサブ画素 1 1 に、画素電圧 V sig を供給すればよい。すなわち、表示装置 1 では、データ線 D T L を駆動する際の駆動周波数を低くすることができるため、消費電力を低減することができる。

20

## 【 0 0 7 2 】

また、本実施の形態に係る表示装置 1 では、セル C A , C B のそれぞれにつき 5 本の配線（1 本の走査線 W S 、1 本の電源線 P L 、および 3 本のデータ線 D T L ）が必要となる。すなわち、比較例 1 の場合（6 本）に比べて少ない配線で済む。よって、これらの配線に対する駆動電力が少なくて済むため、消費電力を低減することができる。

30

## 【 0 0 7 3 】

また、本実施の形態に係る表示装置 1 では、赤色のサブ画素 1 1 R を省いてセル C A を構成し、青色のサブ画素 1 1 B を省いてセル C B を構成することにより、画質の低下を抑えつつ、消費電力を低減することができる。すなわち、表示装置 1 では、上述したように、消費電力を低減するために、赤色のサブ画素 1 1 R や青色のサブ画素 1 1 B を少なくしているため、白色（W）のサブ画素 1 1 W や緑色（G）のサブ画素 1 1 G の解像度に比べて、赤色（R）のサブ画素 1 1 R や青色（B）のサブ画素 1 1 B の解像度が低下している。しかしながら、人間は、赤色（R）と青色（B）などのいわゆる色度成分の解像度が低下しても、画質の低下を感じないことが知られている。すなわち、色を輝度成分と色度成分に分けた場合、人間は、輝度成分の解像度を下げると画質が低下したように感じるが、色度成分の解像度を下げても、さほど画質の低下を感じない。サブ画素 1 1 が発光する 4 色（赤色、緑色、青色、白色）のうち、白色（W）と緑色（G）は輝度成分への寄与が多く、一方、赤色（R）と青色（B）は輝度成分への寄与が少ない。表示装置 1 では、このように、輝度成分への寄与が少ない赤色のサブ画素 1 1 R や青色のサブ画素 1 1 B を少なくしたので、画質の低下を抑えつつ、消費電力を低減することができる。

40

## 【 0 0 7 4 】

また、本実施の形態に係る表示装置 1 では、サブ画素 1 1 の数を減らしたので、各サブ画素 1 1 を大きくすることができ、サブ画素 1 1 R , 1 1 B の開口率を高くすることができる。これにより、発光層の経時劣化（いわゆる焼き付き）を抑えることができるため、画質を高めることができる。また、上述したように駆動周波数を低くすることができるた

50

め、例えば、サブ画素 1 1 に画素電圧  $V_{sig}$  を書き込むための十分な時間を確保することができる。これにより、画質が低下するおそれを低減することができる。

【 0 0 7 5 】

( 比較例 2 )

また、表示装置 1 では、図 2 に示したように、セル C A , C B が白色のサブ画素 1 1 W を有するようにしたので、以下に説明する比較例 2 に係る表示装置 1 S と比べて、消費電力を低減することができるとともに、画質を高めることができる。

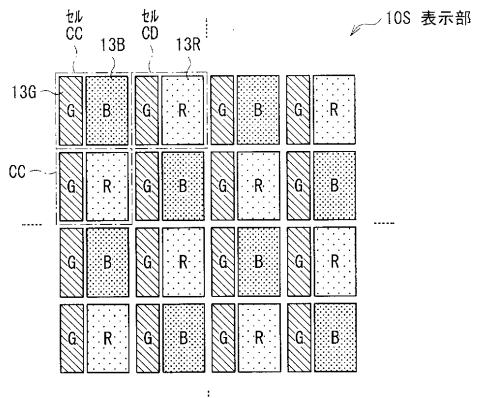

【 0 0 7 6 】

図 1 3 は、比較例 2 に係る表示装置 1 S の表示部 1 0 S におけるサブ画素 1 3 の配置の一例を表すものである。表示部 1 0 S は、赤色 ( R ) 、緑色 ( G ) 、および青色 ( B ) の 3 色のサブ画素 1 3 ( 1 3 R , 1 3 G , 1 3 B ) を有している。すなわち、表示部 1 0 S は、白色 ( W ) のサブ画素を有しないものである。表示部 1 0 S には、サブ画素 1 3 G , 1 3 B により構成されるセル C C と、サブ画素 1 3 G , 1 3 R により構成されるセル C D が並設されている。セル C C およびセル C D は、列方向 ( 垂直方向 ) に交互に配置されるとともに、行方向 ( 水平方向 ) に交互に配置されている。

【 0 0 7 7 】

比較例 2 に係る表示装置 1 S では、白色のサブ画素 1 1 W が設けられていないため、例えば白色を表示する場合には、3 つのサブ画素 1 3 R , 1 3 G , 1 3 B を発光させる必要がある。よって、表示装置 1 S では、消費電力が高くなるおそれがある。

【 0 0 7 8 】

一方、本実施の形態に係る表示装置 1 では、図 2 に示したように、赤色 ( R ) 、緑色 ( G ) 、青色 ( B ) の光を発する 3 つのサブ画素 1 1 R , 1 1 G , 1 1 B に加え、白色 ( W ) の光を発するサブ画素 1 1 W を設けている。これにより、例えば白色を表示する場合には、この 1 つのサブ画素 1 1 W のみを発光させればよいため、消費電力を低減することができる。

【 0 0 7 9 】

また、本実施の形態に係る表示装置 1 では、セル C A , C B が白色のサブ画素 1 1 W を有するようにしたので、比較例 2 に係る表示装置 1 S に比べて画質を高めることができ。すなわち、このサブ画素 1 1 W が発する白色光は、赤色成分、緑色成分、および青色成分を含んでいる。よって、セル C A では、赤色のサブ画素 1 1 R がないものの、白色のサブ画素 1 1 W が赤色成分の光を発する。また、セル C B では、青色のサブ画素 1 1 B がないものの、白色のサブ画素 1 1 W が青色成分の光を発する。よって、表示装置 1 では、比較例 2 に係る表示装置 1 S に比べて、赤色成分および青色成分の解像度を等価的に高めることができ、画質を高めることができる。

【 0 0 8 0 】

( 比較例 3 )

また、表示装置 1 では、図 7 に示したように、アノード 2 1 2 がデータ線 D T L と重ならないようにしたので、以下に説明する比較例 3 に係る表示装置 1 T と比べて、画質の低下を抑えることができる。

【 0 0 8 1 】

図 1 4 は、比較例 3 に係る表示装置 1 T のセル C A におけるアノード 2 1 2 の配置を表すものである。この例では、セル C A において、データ線 D T L 、回路領域 1 5 W 、データ線 D T L 、回路領域 1 5 G 、データ線 D T L 、および回路領域 1 5 B が、左から右へこの順に配置されている。そして、サブ画素 1 1 W のアノード 2 1 2 W は 2 本のデータ線 D T L と重なるように配置され、サブ画素 1 1 G のアノード 2 1 2 G は 2 本のデータ線 D T L と重なるように配置され、サブ画素 1 1 B のアノード 2 1 2 B は 1 本のデータ線 D T L と重なるように配置されている。

【 0 0 8 2 】

比較例 3 に係る表示装置 1 T では、アノード 2 1 2 W が 2 本のデータ線 D T L と重なっているため、これらのデータ線 D T L における信号  $S_{ig}$  が、カップリングによりアノード

10

20

30

40

50

212Wにノイズとして伝わってしまうおそれがある。同様に、アノード212Gが2本のデータ線DTLと重なっているため、これらのデータ線DTLにおける信号Sigが、カップリングによりアノード212Gにノイズとして伝わってしまうおそれがある。また、アノード212Bが1本のデータ線DTLと重なっているため、このデータ線DTLにおける信号Sigが、カップリングによりアノード212Bにノイズとして伝わってしまうおそれがある。特に、表示装置1Tでは、アノード212によって、重なるデータ線DTLの本数が異なるため、ノイズの影響が不均一となり、画質が低下するおそれがある。

#### 【0083】

一方、本実施の形態に係る表示装置1では、図7に示したように、アノード212をデータ線DTLと重ならないように配置したので、アノード212にノイズが伝わるおそれを低減することができ、画質を高めることができる。10

#### 【0084】

##### [効果]

以上のように本実施の形態では、赤色、緑色、青色、白色の4色のサブ画素を設けるとともに、白色や緑色のサブ画素と比べて、赤色や青色のサブ画素を少なくしたので、画質の低下を抑えつつ、消費電力を低減することができる。

#### 【0085】

また、本実施の形態では、サブ画素の数を減らすようにしたので、サブ画素の開口率を高めることができるために、発光層の経時劣化を抑えることができ、画質を高めることができます。20

#### 【0086】

また、本実施の形態では、アノードをデータ線と重ならないように配置したので、画質を高めることができます。

#### 【0087】

##### [変形例1-1]

上記実施の形態では、図2に示したように、3つのサブ画素11W, 11G, 11BによりセルCAを構成するとともに、3つのサブ画素11W, 11G, 11RによりセルCBを構成したが、これに限定されるものではない。

#### 【0088】

例えば、白色(W)のサブ画素11Wに代えて黄色(Y)のサブ画素11Yを用いてもよい。この場合は、3つのサブ画素11Y, 11G, 11BによりセルCAを構成するとともに、3つのサブ画素11Y, 11G, 11RによりセルCBを構成することができる。サブ画素11Yが発する黄色光は、赤色成分および緑色成分を含んでいるため、セルCAでは、赤色のサブ画素11Rがないものの、黄色のサブ画素11Yが赤色成分の光を発する。よって、本変形例に係る表示装置では、比較例2に係る表示装置1Sに比べて、赤色成分の解像度を等価的に高めることができ、画質を高めることができる。30

#### 【0089】

また、例えば、白色(W)のサブ画素11Wに代えてマゼンタ色(M)のサブ画素11Mを用いてもよい。この場合は、3つのサブ画素11M, 11G, 11BによりセルCAを構成するとともに、3つのサブ画素11M, 11G, 11RによりセルCBを構成することができる。サブ画素11Mが発するマゼンタ色光は、赤色成分および青色成分を含んでいるため、セルCAでは、赤色のサブ画素11Rがないものの、マゼンタ色のサブ画素11Mが赤色成分の光を発し、セルCBでは、青色のサブ画素11Bがないものの、マゼンタ色のサブ画素11Mが青色成分の光を発する。よって、本変形例に係る表示装置では、比較例2に係る表示装置1Sに比べて、赤色成分および青色成分の解像度を等価的に高めることができ、画質を高めることができます。40

#### 【0090】

また、例えば、白色(W)のサブ画素11Wに代えてシアン色(C)のサブ画素11Cを用いてもよい。この場合は、3つのサブ画素11C, 11G, 11BによりセルCAを構成するとともに、3つのサブ画素11C, 11G, 11RによりセルCBを構成するこ50

とができる。サブ画素 11C が発するシアン色光は、緑色成分および青色成分を含んでいるため、セル C B では、青色のサブ画素 11B がないものの、シアン色のサブ画素 11C が青色成分の光を発する。よって、本変形例に係る表示装置では、比較例 2 に係る表示装置 1S に比べて、青色成分の解像度を等価的に高めることができ、画質を高めることができ。

【0091】

[変形例 1 - 2 ]

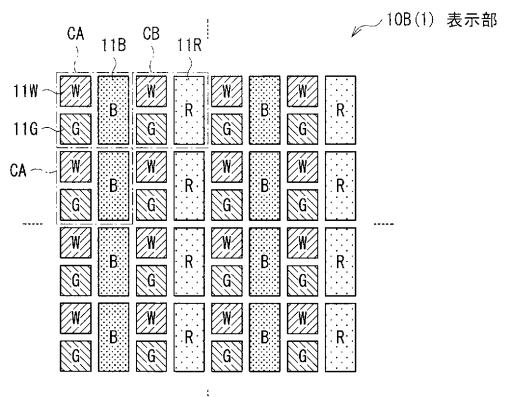

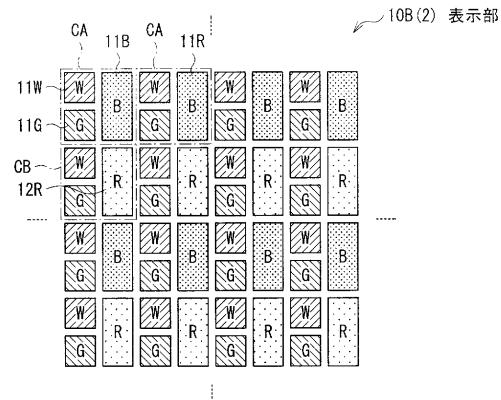

上記実施の形態では、図 2 に示したように、セル C A およびセル C B を、列方向（垂直方向）に交互に配置するとともに、行方向（水平方向）に交互に配置したが、これに限定されるものではない。これに代えて、例えば、図 15 に示す表示部 10B (1) のように、行方向（水平方向）にはセル C A およびセル C B を交互に配置し、列方向（垂直方向）には同じセルを繰り返し配置してもよい。また、例えば、図 16 に示す表示部 10B (2) のように、列方向（垂直方向）にはセル C A およびセル C B を交互に配置し、行方向（水平方向）には同じセルを繰り返し配置してもよい。

10

【0092】

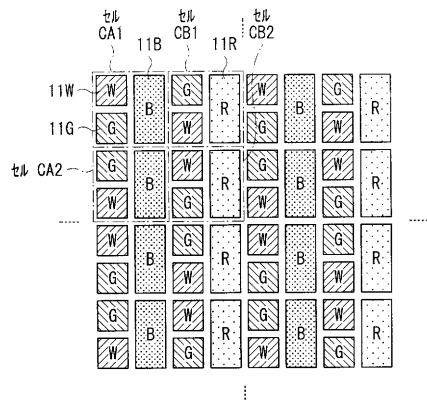

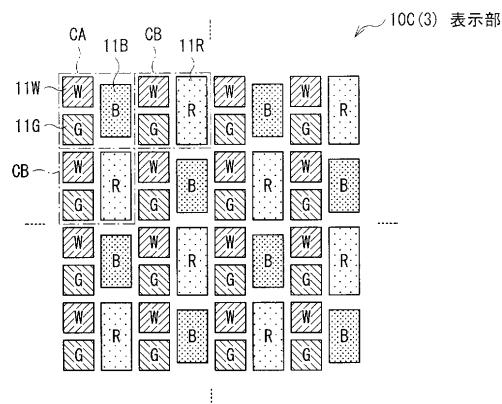

また、上記実施の形態では、全てのセル C A においてサブ画素 11W, 11G, 11B の配置を同じにするとともに、全てのセル C B においてサブ画素 11W, 11G, 11R の配置を同じにしたが、これに限定されるものではない。例えば、図 17 に示す表示部 10B (3) のように、隣り合うセル C A においてサブ画素 11W, 11G, 11B の配置が互いに異なるようにするとともに、隣り合うセル C B においてサブ画素 11W, 11G, 11R の配置が互いに異なるようにしてもよい。この表示部 10B (3) には、3 つのサブ画素 11W, 11G, 11B により構成されるセル C A (C A 1, C A 2) と、3 つのサブ画素 11W, 11G, 11R により構成されるセル C B (C B 1, C B 2) とが並設されている。この例では、セル C A 1 において、白色 (W) のサブ画素 11W が左上に配置され、緑色 (G) のサブ画素 11G が左下に配置され、青色 (B) のサブ画素 11B が右側に配置されている。そして、セル C A 2 において、緑色 (G) のサブ画素 11G が左上に配置され、白色 (W) のサブ画素 11W が左下に配置され、青色 (B) のサブ画素 11B が右側に配置されている。同様に、セル C B 1 において、緑色 (G) のサブ画素 11G が左上に配置され、白色 (W) のサブ画素 11W が左下に配置され、赤色 (R) のサブ画素 11R が右側に配置されている。そして、セル C B 2 において、白色 (W) のサブ画素 11W が左上に配置され、緑色 (G) のサブ画素 11G が左下に配置され、赤色 (R) のサブ画素 11R が右側に配置されている。

20

【0093】

[変形例 1 - 3 ]

上記実施の形態において、サブ画素 11R, 11G, 11B, 11W の開口部 W I N の開口面積 A R, A G, A B, A W は、次のような関係を有しているのが望ましい。

$$A W \quad A G < A R = A B \quad \dots \quad (1)$$

$$A W \quad A G < A R < A B \quad \dots \quad (2)$$

$$A W \quad A G < A B < A R \quad \dots \quad (3)$$

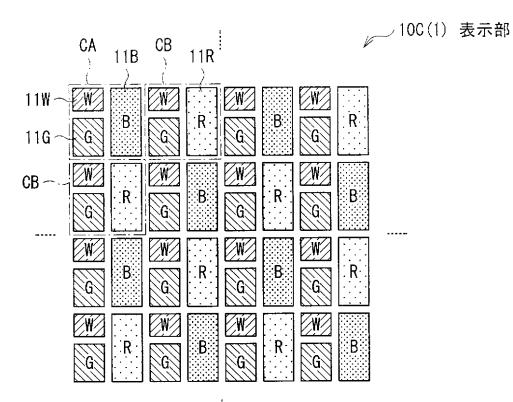

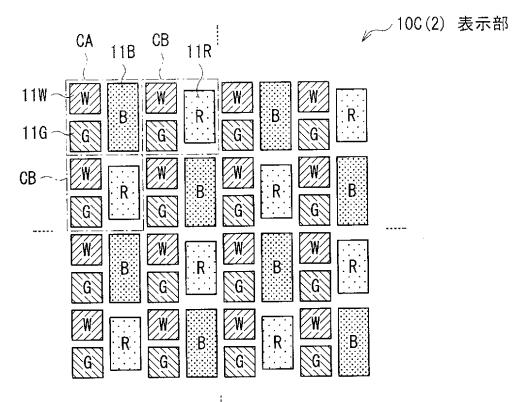

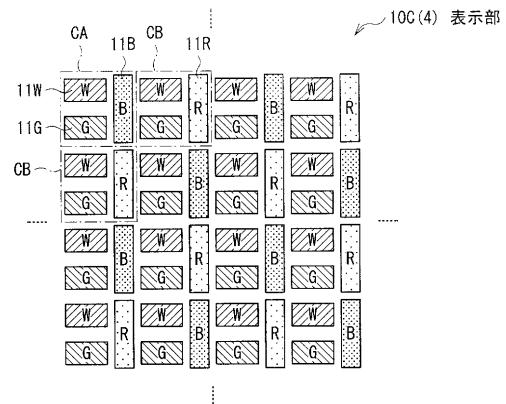

具体的には、例えば、図 18 に示す表示部 10C (1) のように、サブ画素 11W の開口面積 A W をサブ画素 11G の開口面積 A G よりも小さくしてもよいし、図 19 に示す表示部 10C (2) のように、サブ画素 11R の開口面積 A R をサブ画素 11B の開口面積 A B よりも小さくしてもよいし、例えば、図 20 に示す表示部 10C (3) のように、サブ画素 11B の開口面積 A B をサブ画素 11R の開口面積 A R よりも小さくしてもよい。また、例えば、図 21 に示す表示部 10C (4) のように、白色のサブ画素 11W の開口面積 A W、および緑色のサブ画素 11G の開口面積 A G を、これらの変形例の場合よりも大きくし、赤色のサブ画素 11R の開口面積 A R、および青色のサブ画素 11B の開口面積 A B を、これらの変形例の場合よりも小さくてもよい。ここで、サブ画素 11R の開口面積 A R と、サブ画素 11B の開口面積 A B との大小関係は、例えば、サブ画素 11R, 11B の発光効率などを考慮して決定することができる。

40

50

## 【0094】

この式(1)～式(3)において、白色のサブ画素11Wの開口面積AWが、緑色のサブ画素11Gの開口面積AG以下である(AW < AG)のは、図5に示したように、発光層230が白色の光を発し、この白色光が赤色、緑色、青色、白色のカラーフィルタ218を介して出力されるためである。すなわち、一般に、緑色(G)のカラーフィルタ218を通過した後の輝度は、白色(W)のカラーフィルタ218を通過した後の輝度以下になってしまないので、その輝度差を補うために、開口面積AWを開口面積AG以下にしている。

## 【0095】

また、式(1)～式(3)において、緑色のサブ画素11Gの開口面積AGが、赤色のサブ画素11Rの開口面積ARよりも小さく(AG < AR)、青色のサブ画素11Bの開口面積ABよりも小さい(AG < AB)。これは、発光層230が発する白色光において、一般に、緑色成分が赤色成分および青色成分よりも大きいことを考慮したためであり、その差を補うために、開口面積AGを開口面積AR, ABよりも小さくしている。

10

## 【0096】

## [変形例1-4]

上記実施の形態では、図7に示したように、コンタクト205を回路領域15W, 15G, 15Bの上端付近または下端付近に設けたが、これに限定されるものではなく、これに代えて、例えば、図22に示す表示部10Dのように、回路領域15W, 15G, 15Bの中央付近に設けてもよい。この場合には、回路領域15W, 15G, 15Bにおける書込トランジスタWSTR、駆動トランジスタDRT、および容量素子Csのレイアウトを同一にすることができ、設計効率が向上するとともに、サブ画素11間の特性ばらつきを抑えることができる。

20

## 【0097】

## [変形例1-5]

上記実施の形態では、図7に示したように、アノード212をデータ線DTLと重ならないように配置したが、これに限定されるものではなく、これに代えて、例えば図23に示す表示部10Eのように、各アノード212(212W, 212G, 212B)を1本のデータ線DTLと重なるように配置してもよい。この構成では、データ線DTLにおける信号Sigが、カップリングにより、アノード212W, 212G, 212Bにノイズとして伝わってしまうおそれがある。しかしながら、比較例3の場合と異なり、どのアノード212W, 212G, 212Bも、1本のデータ線DTLと重なるようにしたので、ノイズの影響がより均一になるため、画質の低下を抑えることができる。

30

## 【0098】

## [変形例1-6]

上記実施の形態では、図2に示したように、セルCA, CBにおいて、サブ画素11W, 11Gを列方向(垂直方向)に並設したが、これに限定されるものではない。これに代えて、例えば、図24～図26に示す表示部10F(1)～10F(3)のように、行方向(水平方向)に並設してもよい。この例では、セルCAにおいて、左から、サブ画素11B、サブ画素11G、サブ画素11Wをこの順で配置し、セルCBにおいて、左から、サブ画素11R、サブ画素11G、サブ画素11Wをこの順で配置している。表示部10F(1)(図24)では、セルCAおよびセルCBを、列方向に交互に配置するとともに、行方向に交互に配置している。表示部10F(2)(図25)では、行方向にはセルCAおよびセルCBを交互に配置し、列方向には同じセルを繰り返し配置している。表示部10F(3)(図26)では、列方向にはセルCAおよびセルCBを交互に配置し、行方向には同じセルを繰り返し配置している。

40

## 【0099】

表示部10F(1)～10F(3)においても、アノード212を、図27に示すように、データ線DTLと重ならないように配置することが望ましい。また、図28に示すように、各アノード212(212W, 212G, 212B)を、1本のデータ線DTLと

50

重なるように配置してもよい。

【0100】

[変形例1-7]

上記実施の形態では、トップエミッション型の発光素子19により表示部10を構成したが、これに限定されるものではなく、これに代えて、例えば、図29に示す表示部10Gのように、いわゆるボトムエミッション型の発光素子19Gにより構成してもよい。表示部10Gは、アノード232と、カソード236と、カラーフィルタ238とを有している。アノード232は、例えば、スズ酸化インジウムスズ(ITO; Indium Tin Oxide)により構成されている。すなわち、アノード232は、透明または半透明なものである。このアノード232は、例えば数十~数百nmの膜厚で形成されている。カソード236は、光を反射する性質を有するものであり、例えば、マグネシウム銀(MgAg)により構成することができる。このカソード236は、例えば数十nm~数百nm程度の膜厚で形成されている。カラーフィルタ238は、絶縁層204の上の、開口WINに対応する領域に形成されている。この構成により、黄色発光層214から射出した黄色の光と、青色発光層215から射出した青色の光は、混ざり合って白色光となり、支持基板である透明基板200の方向に進む。そして、この白色光は、赤色(R)、緑色(G)、青色(B)、白色(W)のカラーフィルタ238を介して表示面より出力される。

【0101】

[変形例1-8]

上記実施の形態では、図6A, 6Bに示したように、発光層230(黄色発光層214および青色発光層215)が合成光として白色の光を発し、この白色光が赤色、緑色、青色、白色のカラーフィルタ218を介して出力されるようにしたが、これに限定されるものではない。

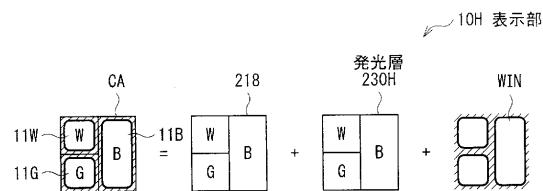

【0102】

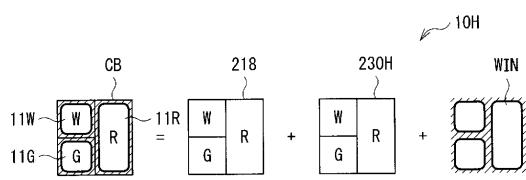

例えば、図30A, 30Bに示す表示部10Hのように、発光層230の代わりに、サブ画素11R, 11G, 11B, 11Wに対応する領域において赤色(R)、緑色(G)、青色(B)および白色(W)の光をそれぞれ発する発光層230Hを設けてよい。この場合、この発光層230Hから射出した各色の光が、赤色(R)、緑色(G)、青色(B)および白色(W)のカラーフィルタ218を介してそれぞれ出力される。ここで、カラーフィルタ218は、各色の色域を調整するために設けられている。なお、画質(色域)に対する要求がさほど高くないアプリケーションなどにおいては、このカラーフィルタ218を省いてよい。

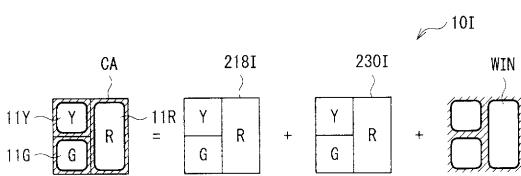

【0103】

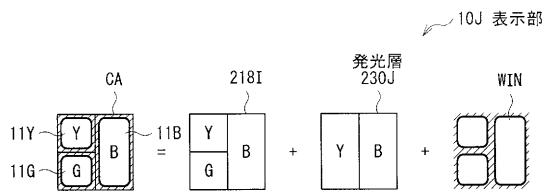

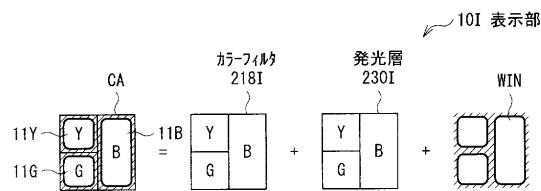

変形例1-1に係る表示部のように、白色(W)のサブ画素11Wの代わりに黄色(Y)のサブ画素11Yを設けた場合には、例えば、図31A, 31Bのように構成することができる。この表示部10Iは、発光層230Iと、カラーフィルタ218Iを有している。発光層230Iは、各サブ画素11R, 11G, 11B, 11Yに対応する領域において赤色(R)、緑色(G)、青色(B)および黄色(Y)の光をそれぞれ発するものである。カラーフィルタ218Iは、各サブ画素11R, 11G, 11B, 11Yに対応する領域において、赤色(R)、緑色(G)、青色(B)および黄色(Y)のカラーフィルタが配置されたものである。この表示部10Iでは、発光層230Iから射出した各色の光が、各色のカラーフィルタ218Iを介して出力される。この例においても、カラーフィルタ218Iを省くことができる。

【0104】

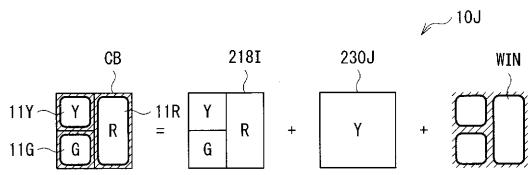

また、図32A, 32Bに示す表示部10Jのように、サブ画素11R, 11G, 11Yに対応する領域において黄色(Y)の光を発し、サブ画素11Bに対応する領域において青色(B)の光を発する発光層230Jを設けてよい。この場合、発光層230Jから射出した黄色(Y)の光は、赤色(R)、緑色(G)、黄色(Y)のカラーフィルタ218Iを通過することにより各色の成分に分離され出力される。また、発光層230Jから射出した青色(B)の光は、青色(B)のカラーフィルタ218Iを介して出力される

。この例では、青色（B）および黄色（Y）のカラーフィルタ218Iを省くことができる。

### 【0105】

#### [変形例1-9]

上記実施の形態では、図2,7などに示したように、サブ画素11の開口部WINの形状を長方形に近い形にしたが、これに限定されるものではなく、これに代えて、例えば、図33に示す表示部10Kのように、サブ画素14の開口部WINの形状を円形にしてもよい。表示部10Kは、赤色（R）、緑色（G）、青色（B）、および白色（W）のサブ画素14R,14G,14B,14Wを有している。表示部10Kには、3つのサブ画素14W,14G,14Bにより構成されるセルCA（CA1,CA2）と、3つのサブ画素14W,14G,14Rにより構成されるセルCB（CB1,CB2）とが並設されている。各セルCA1,CA2,CB1,CB2では、3つのサブ画素14が互いに隣り合うように配置されている。言い換えれば、これらの3つのサブ画素14は、それらの中心を結ぶ線が正3角形の各辺をなすように配置されている。具体的には、セルCA1において、白色（W）のサブ画素14Wが右上に配置され、緑色（G）のサブ画素14Gが下側に配置され、青色（B）のサブ画素14Bが左上に配置され、また、セルCA2において、白色（W）のサブ画素14Wが右下に配置され、緑色（G）のサブ画素14Gが上側に配置され、青色（B）のサブ画素14Bが左下に配置されている。また、セルCB1において、白色（W）のサブ画素14Wが右上に配置され、緑色（G）のサブ画素14Gが下側に配置され、赤色（R）のサブ画素14Rが左上に配置され、また、セルCB2において、白色（W）のサブ画素14Wが右下に配置され、緑色（G）のサブ画素14Gが上側に配置され、赤色（R）のサブ画素14Rは左下に配置されている。行方向（水平方向）には、セルCA1,CA2が交互に配置されるとともに、セルCB1,CB2が交互に配置される。また、列方向（垂直方向）には、セルCA1,CB1が交互に配置されるとともに、セルCA2,CB2が交互に配置される。このように、表示部10Kでは、サブ画素14がいわゆる最密充填配置になるように配置されている。このように、開口部WINを円形にしても、上記実施の形態と同様の効果を得ることができる。なお、この例では、開口部WINの形状を円形にしたが、これに限定されるものではなく、これに代えて、例えば橢円形にしてもよい。

### 【0106】

#### [変形例1-10]

上記実施の形態等において、開口部WINの形状、および絶縁層213,217の材料等を工夫することにより、発光層230から射出した光の外部への取り出し効率を高めるようにしてよい。以下に、本変形例について詳細に説明する。なお、この例では、サブ画素の開口部WINは円形として説明するが、これに限定されるものではなく、橢円形や、長方形に近い形などであってもよい。

### 【0107】

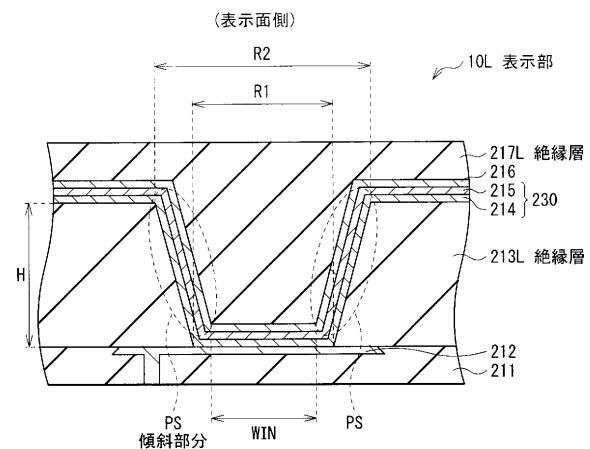

図34は、本変形例に係る表示部10Nの要部断面構造を示す。表示部10Lは、絶縁層213L,217Lを有している。絶縁層213L,217Lは、上記実施の形態における絶縁層213,217にそれぞれ対応するものである。図34に示したように、絶縁層213Lの端は傾斜（傾斜部分PS）している。表示部10Lでは、この傾斜部分PSにより、発光層230の開口部WINから発した光が反射されるため、光の外部への取り出し効率を高めることができるようになっている。

### 【0108】

この表示部10Lは、より詳細には、以下のように構成されている。すなわち、絶縁層217Lの屈折率をn1とし、絶縁層213Lの屈折率をn2としたとき、これらの屈折率n1,n2は、以下の式を満たすものである。

$$1.1 \quad n_1 \quad 1.8 \quad \cdots \quad (4)$$

$$n_1 - n_2 \quad 0.20 \quad \cdots \quad (5)$$

また、絶縁層213Lの高さをHとし、絶縁層213Lの開口部分の、アノード電極21

10

20

30

40

50

2側における直径をR1とし、絶縁層213Lの開口部分の、表示面側の直径をR2とすると、高さH、直径R1, R2は、以下の式を満たすように設定されている。

$$0.5 \quad R1 / R2 \quad 0.8 \quad \dots \quad (6)$$

$$0.5 \quad H / R1 \quad 2.0 \quad \dots \quad (7)$$

#### 【0109】

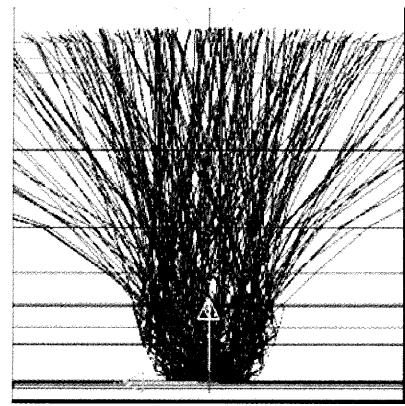

図35は、表示部10Lにおける、光線のシミュレーション結果の一例を表すものである。このように、表示部10Lでは、発光層230の開口部WINから発した光が傾斜部分PSにおいて反射され、表示部10Lの正面に向かって射出する。すなわち、例えば、傾斜部分PSにおいて反射しない場合には、その光は、表示部10L内で弱められ、またはブラックマトリクス219により遮断され、外部に射出されないおそれがある。表示部10Lでは、この傾斜部分PSにおいて光が反射するようにしたので、光の外部への取り出し効率を高めることができる。

#### 【0110】

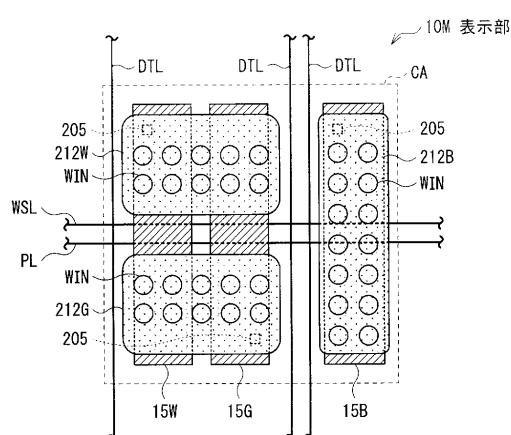

また、本変形例に係る表示部10Lでは、1つのサブ画素11に1つの開口部WINを設けたが、これに限定されるものではなく、これに代えて、図36, 37に示す表示部10Mのように、1つのサブ画素11に複数の開口部WINを設けてもよい。この場合には、各開口部WINの傾斜部分PSを有効に用いることにより、光の外部への取り出し効率を高めることができる。

#### 【0111】

##### [変形例1-11]

上記実施の形態では、図3に示したように、各セルCA, CB内の3つのサブ画素11を、互いに異なるデータ線DTLに接続したが、これに限定されるものではない。以下に、本変形例について詳細に説明する。

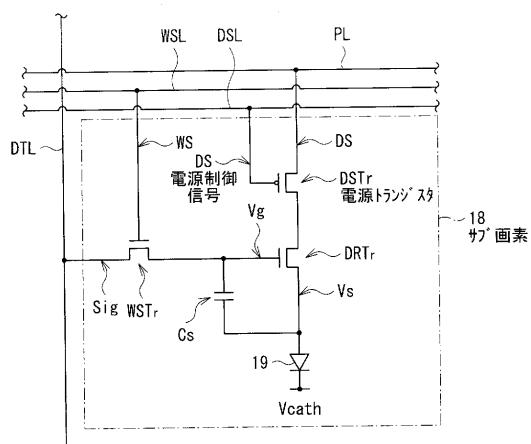

#### 【0112】

図38は、本変形例に係る表示部10Nの回路構成の一例を表すものである。表示部10Nは、行方向に延伸する複数の走査線WSAL, WSBLを有している。この例では、データ線DTLは、行方向（水平方向）において、2つのサブ画素11に一本の割合で設けられている。また、これらの2つのサブ画素11は、一方は走査線WSALに接続されるとともに、他方は走査線WSBLに接続されている。データ線DTLの一端は、データ線駆動部27Nに接続されている。また、走査線WSAL, WSBLの一端は、図示しない走査線駆動部23Nに接続され、電源線PLの一端は、図示しない電源線駆動部26Nに接続されている。走査線駆動部23Nは、走査線WSALに対して走査信号WSAを印加するとともに、走査線WSBLに対して走査信号WSBを印加する。データ線駆動部27Nは、これらの2つのサブ画素11の画素電圧Vsig、およびVth補正を行うための電圧Vofsを含む信号Sigを生成し、各データ線DTLに印加するものである。

#### 【0113】

本変形例に係る表示部10Nでは、各セルCA, CBにつき4.5本の配線（2本の走査線WS、1本の電源線PL、および1.5本のデータ線DTL）が必要となる。すなわち、上記実施の形態の場合（5本）に比べてさらに少ない配線で済む。よって、消費電力を低減することができる。

#### 【0114】

図39は、表示部10Nにおけるアノード212の配置を表すものである。セルCAには、3つの回路領域16W, 16G, 16Bが設けられ、セルCBには、3つの回路領域16W, 16G, 16Rが設けられている。この例では、セルCAにおいて、回路領域16Wは左上に配置され、回路領域16Gは左下に配置され、回路領域16Bは右上に配置されており、アノード212Wは左上に配置され、アノード212Gは左下に配置され、アノード212Bは右側に配置されている。また、セルCBにおいて、回路領域16Wは右下に配置され、回路領域16Gは右上に配置され、回路領域16Rは左下に配置されており、アノード212Wは右下に配置され、アノード212Gは右上に配置され、アノード212Rは左側に配置されている。

10

20

30

40

50

## 【0115】

このように、本変形例に係る表示部10Nでも、アノード212をデータ線D<sub>TL</sub>と重ならないように配置したので、アノード212にノイズが伝わるおそれを低減することができ、画質を高めることができる。

## 【0116】

次に、同じデータ線D<sub>TL</sub>に接続された、行方向（水平方向）に隣り合う2つのサブ画素11として、走査線W<sub>SAL</sub>に接続されたサブ画素11Wと、走査線W<sub>SB</sub>Lに接続されたサブ画素11Gを例に挙げ、これらのサブ画素11W, 11Gの表示動作について詳細に説明する。

## 【0117】

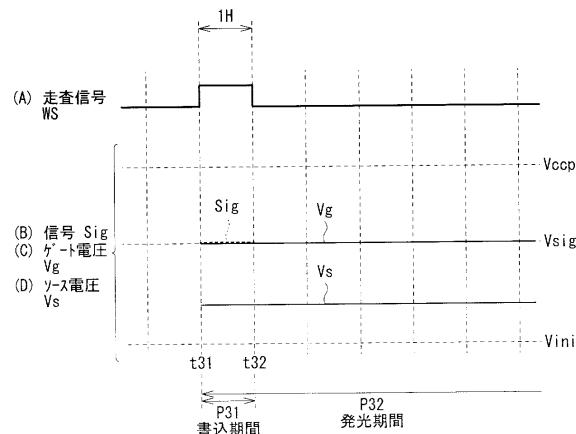

図40は、サブ画素11W, 11Gの動作のタイミング図を表すものであり、（A）は走査信号W<sub>SA</sub>の波形を示し、（B）は走査信号W<sub>SB</sub>の波形を示し、（C）は電源信号D<sub>S</sub>の波形を示し、（D）は信号Sigの波形を示し、（E）はサブ画素11Wにおける駆動トランジスタD<sub>RT</sub>rのゲート電圧V<sub>g</sub>の波形を示し、（F）はサブ画素11Wにおける駆動トランジスタD<sub>RT</sub>rのソース電圧V<sub>s</sub>の波形を示し、（G）はサブ画素11Gにおける駆動トランジスタD<sub>RT</sub>rのゲート電圧V<sub>g</sub>の波形を示し、（H）はサブ画素11Gにおける駆動トランジスタD<sub>RT</sub>rのソース電圧V<sub>s</sub>の波形を示す。図40（C）～（F）では、同じ電圧軸を用いて各波形を示し、同様に、図40（G）, (H)では、同じ電圧軸を用いて各波形を示している。なお、説明の便宜上、図40（G）, (H)と同じ電圧軸に、電源信号D<sub>S</sub>（図40（C））および信号Sig（図40（D））の波形と同じものを示している。

10

## 【0118】

本変形例に係る駆動部20Nは、上記実施の形態の場合と同様に、タイミングt<sub>12</sub>～t<sub>13</sub>の期間（初期化期間P<sub>1</sub>）において、サブ画素11W, 11Gを初期化し、タイミングt<sub>13</sub>～t<sub>14</sub>の期間（V<sub>th</sub>補正期間P<sub>2</sub>）において、V<sub>th</sub>補正を行う。

## 【0119】

次に、走査線駆動部23Nは、タイミングt<sub>14</sub>において、走査信号W<sub>SA</sub>, W<sub>SB</sub>の電圧を高レベルから低レベルにそれぞれ変化させる（図40（A）, (B)）。これにより、サブ画素11W, 11Gの書き込みトランジスタW<sub>ST</sub>rはそれぞれオフ状態になる。これと同時に、データ線駆動部27Nは、信号Sigを画素電圧V<sub>sigW</sub>に設定する（図40（D））。

30

## 【0120】

次に、駆動部20Nは、タイミングt<sub>15</sub>～t<sub>16</sub>の期間（書き込み・μ補正期間P<sub>13</sub>）において、サブ画素11Wに対して画素電圧V<sub>sigW</sub>の書き込みを行うとともにμ補正を行う。具体的には、走査線駆動部23Nが、タイミングt<sub>15</sub>において、走査信号W<sub>SA</sub>の電圧を低レベルから高レベルに変化させる（図40（A））。これにより、上記実施の形態の場合と同様に、サブ画素11Wに画素電圧V<sub>sigW</sub>が書き込まれるとともに、μ補正が行われる。

## 【0121】

次に、駆動部20Nは、タイミングt<sub>16</sub>以降の期間（発光期間P<sub>14</sub>）において、サブ画素11Wを発光させる。具体的には、タイミングt<sub>16</sub>において、走査線駆動部23Nは、走査信号W<sub>SA</sub>の電圧を高レベルから低レベルに変化させる（図40（A））。これにより、上記実施の形態の場合と同様に、サブ画素11Wの発光素子19が発光する。

40

## 【0122】

次に、データ線駆動部27Nは、タイミングt<sub>17</sub>において、信号Sigを画素電圧V<sub>sigG</sub>に設定する（図40（D））。

## 【0123】

次に、駆動部20Nは、タイミングt<sub>18</sub>～t<sub>19</sub>の期間（書き込み・μ補正期間P<sub>15</sub>）において、サブ画素11Gに対して画素電圧V<sub>sigG</sub>の書き込みを行うとともにμ補正を行う。具体的には、走査線駆動部23Nが、タイミングt<sub>18</sub>において、走査信号W<sub>SB</sub>の電

50

圧を低レベルから高レベルに変化させる(図40(B))。これにより、上記実施の形態の場合と同様に、サブ画素11Gに画素電圧Vsigtが書き込まれるとともに、μ補正が行われる。

#### 【0124】

次に、駆動部20Nは、タイミングt19以降の期間(発光期間P16)において、サブ画素11Gを発光させる。具体的には、タイミングt19において、走査線駆動部23Nは、走査信号WSBの電圧を高レベルから低レベルに変化させる(図40(B))。これにより、上記実施の形態の場合と同様に、サブ画素11Gの発光素子19が発光する。

#### 【0125】

##### [変形例1-12]

10

以上、第1の実施の形態およびその変形例について説明したが、これらのうちの2以上を組み合わせてもよい。

#### 【0126】

##### <2. 第2の実施の形態>

次に、第2の実施の形態に係る表示装置2について説明する。本実施の形態は、データ線DTLの波形が、上記第1の実施の形態に係る表示装置1の場合と異なるものである。上記第1の実施の形態に係る表示装置1と実質的に同一の構成部分には同一の符号を付し、適宜説明を省略する。

#### 【0127】

表示装置2は、図1に示したように、表示部40と、駆動部50とを備えている。表示部40には、図2,3に示したように、3つのサブ画素11W, 11G, 11Bにより構成されるセルCAと、3つのサブ画素11W, 11G, 11Rにより構成されるセルCBが並設されている。

20

#### 【0128】

図41は、セルCAにおけるアノード212の配置を表すものである。セルCAには、3つの回路領域15W, 15G, 15Bと、3つのアノード312W, 312G, 312Bが設けられている。この例では、セルCAにおいて、1本のデータ線DTL、回路領域15W、1本のデータ線DTL、回路領域15G、1本のデータ線DTL、および回路領域15Bが、左から右へこの順に配置されている。また、セルCAにおいて、アノード312Wは左上に配置され、アノード312Gは左下に配置され、アノード312Bは右側に配置されている。アノード312W, 312Gは、3本のデータ線DTLと重なるように配置され、アノード312Bは、データ線DTLと重ならないように配置されている。すなわち、上記第1の実施の形態に係る表示部10では、3つのアノード212W, 212G, 212Bを、データ線DTLと重ならないように配置したが、本実施の形態に係る表示部40では、3つのアノード312W, 312G, 312Bのうちの2つ(アノード312W, 312G)を、3本のデータ線DTLと重なるように配置している。

30

#### 【0129】

以上、セルCAについて説明したが、セルCBについても同様である。すなわち、セルCBには、3つの回路領域15W, 15G, 15Rと、3つのアノード312W, 312G, 312Rが設けられている。セルCBにおいて、1本のデータ線DTL、回路領域15W、1本のデータ線DTL、回路領域15G、1本のデータ線DTL、および回路領域15Rが、左から右へこの順に配置されている。また、セルCBにおいて、アノード312Wは左上に配置され、アノード312Gは左下に配置され、アノード312Rは右側に配置されている。アノード312W, 312Gは、3本のデータ線DTLと重なるように配置され、アノード312Rは、データ線DTLと重ならないように配置されている。

40

#### 【0130】

駆動部50は、データ線駆動部57を有している。データ線駆動部57は、映像信号処理部30から供給された映像信号Sdisp2およびタイミング生成部22から供給された制御信号に従って、各サブ画素11の発光輝度を指示する画素電圧Vsigtからなる信号Sigを生成し、各データ線DTLに印加するものである。

50

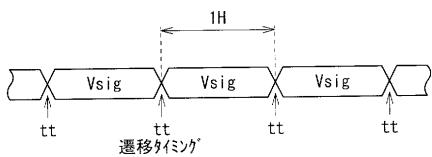

## 【0131】

図42は、データ線駆動部57が生成する信号Sigの一例を表すものである。信号Sigは、同じデータ線DTLに接続された複数のサブ画素11に供給する複数の画素電圧Vsigが連なるものである。この画素電圧Vsigは、1水平期間ごとに切り換えられるようになっている。すなわち、上記第1の実施の形態では、図10に示したように、画素電圧Vsigと電圧Vofsとを交互に配置して信号Sigを構成したが、本実施の形態では、電圧Vofsを含まずに信号Sigを構成している。

## 【0132】

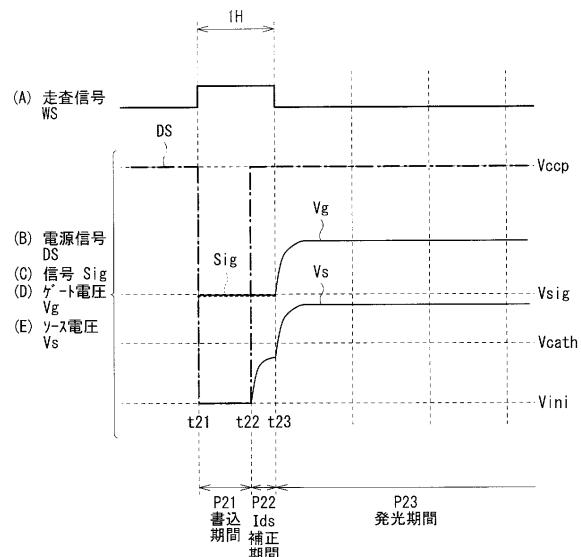

## (詳細動作について)

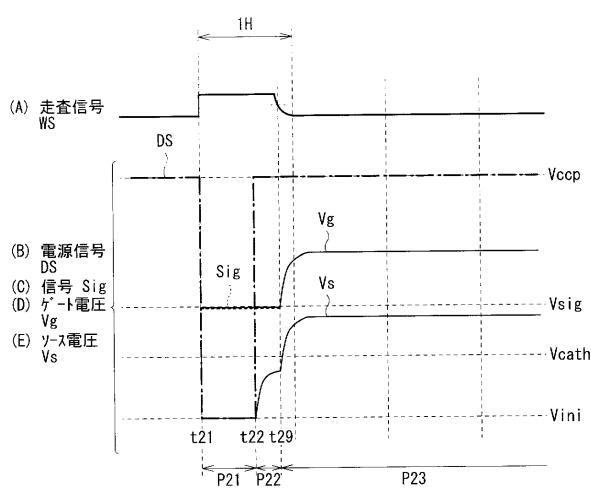

図43は、表示装置2における表示動作のタイミング図を表すものである。この図は、着目した1つのサブ画素11に対する表示駆動の動作例を表すものである。図43において、(A)は走査信号WSの波形を示し、(B)は電源信号DSの波形を示し、(C)は信号Sigの波形を示し、(D)は駆動トランジスタDRTのゲート電圧Vgの波形を示し、(E)は駆動トランジスタDRTのソース電圧Vsの波形を示す。図43(B)～(E)では、同じ電圧軸を用いて各波形を示している。

## 【0133】

駆動部50は、1水平期間(1H)内において、サブ画素11に対して画素電圧Vsigの書き込みを行うとともにサブ画素11の初期化を行い(書き期間P21)、駆動トランジスタDRTの素子ばらつきが画質に与える影響を抑えるためのIds補正を行う(Ids補正期間P22)。そして、その後に、サブ画素11の発光素子19が、書き込まれた画素電圧Vsigに応じた輝度で発光する(発光期間P23)。以下に、その詳細を説明する。

## 【0134】

まず、駆動部50は、タイミングt21～t22の期間(書き期間P21)において、サブ画素11に対して画素電圧Vsigの書き込みを行うとともに、サブ画素11の初期化を行う。具体的には、まず、タイミングt21において、データ線駆動部57が、信号Sigを画素電圧Vsigに設定し(図43(C))、走査線駆動部23が、走査信号WSの電圧を低レベルから高レベルに変化させる(図43(A))。これにより、書きトランジスタWSTがオン状態になり、駆動トランジスタDRTのゲート電圧Vgが画素電圧Vsigに設定される(図43(D))。また、これと同時に、電源線駆動部26が、電源信号DSを電圧Vccpから電圧Viniに変化させる(図43(B))。これにより、駆動トランジスタDRTがオン状態になり、駆動トランジスタDRTのソース電圧Vsが電圧Viniに設定される(図43(E))。これにより、駆動トランジスタDRTのゲート・ソース間電圧Vgs(=Vsig - Vini)は、駆動トランジスタDRTの閾値電圧Vthよりも大きい電圧に設定され、サブ画素11が初期化される。

## 【0135】

次に、駆動部50は、タイミングt22～t23の期間(Ids補正期間P22)において、サブ画素11に対してIds補正を行う。具体的には、タイミングt22において、電源線駆動部26が、電源信号DSを電圧Viniから電圧Vccpに変化させる(図43(B))。これにより、駆動トランジスタDRTは飽和領域で動作するようになり、ドレンからソースに電流Idsが流れ、ソース電圧Vsが上昇する(図43(E))。その際、この例では、ソース電圧Vsは発光素子19のカソードの電圧Vcathよりも低いため、発光素子19は逆バイアス状態を維持し、発光素子19には電流は流れない。このようにソース電圧Vsが上昇することにより、ゲート・ソース間電圧Vgsが低下するため、電流Idsは低下する。この負帰還動作により、ソース電圧Vsは、時間が経つにつれ、よりゆっくりと上昇するようになる。このIds補正を行う時間の長さ(タイミングt22～t23)は、後述するように、タイミングt23における電流Idsのばらつきを抑えるために定められている。

## 【0136】

次に、駆動部50は、タイミングt23以降の期間(発光期間P23)において、サブ画素11を発光させる。具体的には、タイミングt23において、走査線駆動部23は、

10

20

30

40

50

走査信号 W S の電圧を高レベルから低レベルに変化させる（図 4 3 ( A )）。これにより、書込トランジスタ W S T r がオフ状態になり、駆動トランジスタ D R T r のゲートがフローティングとなるため、これ以後、容量素子 C s の端子間電圧、すなわち、駆動トランジスタ D R T r のゲート・ソース間電圧 V gs は維持される。そして、駆動トランジスタ D R T r に電流 I ds が流れるにつれ、駆動トランジスタ D R T r のソース電圧 V s が上昇し（図 4 3 ( E )）、これに伴って駆動トランジスタ D R T r のゲート電圧 V g も上昇する（図 4 3 ( D )）。そして、駆動トランジスタ D R T r のソース電圧 V s が、発光素子 1 9 の閾値電圧 V el と電圧 V cath の和（V el + V cath）よりも大きくなると、発光素子 1 9 のアノード・カソード間に電流が流れ、発光素子 1 9 が発光する。すなわち、発光素子 1 9 の素子ばらつきに応じた分だけソース電圧 V s が上昇し、発光素子 1 9 が発光する。 10

#### 【 0 1 3 7 】

その後、表示装置 2 では、所定の期間（1 フレーム期間）が経過したのち、発光期間 P 2 3 から書込期間 P 2 1 に移行する。駆動部 5 0 は、この一連の動作を繰り返すように駆動する。 20

#### 【 0 1 3 8 】

##### （ I ds 補正について ）

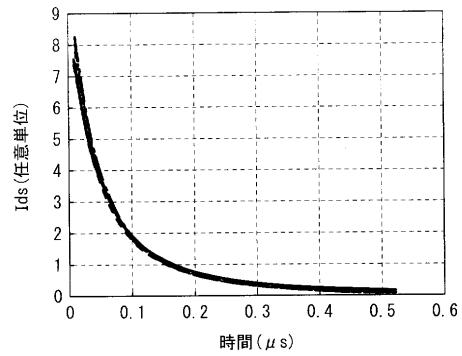

上述したように、 I ds 補正期間 P 2 2 では、駆動トランジスタ D R T r のドレインからソースに電流 I ds が流れ、ソース電圧 V s が上昇し、ゲート・ソース間電圧 V gs が徐々に低下する。これにより、駆動トランジスタ D R T r のドレインからソースに流れる電流 I ds も徐々に低下する。 20

#### 【 0 1 3 9 】

図 4 4 は、ある画素電圧 V sig を与えたときの電流 I ds の時間変化を表すものである。この図 4 4 は、互いに異なる複数のプロセス条件でトランジスタを製造した場合を想定したシミュレーション結果を示している。図 4 4 に示したように、電流 I ds は、時間が経過するとともに徐々に低下する。その際、電流 I ds の時間変化は、プロセス条件に依存して互いに異なったものとなる。具体的には、例えば、電流値 I ds が大きい場合（移動度  $\mu$  が高く閾値 V th が低い場合）にはより早く低下し、電流値 I ds が小さい場合（移動度  $\mu$  が低く閾値 V th が高い場合）にはより遅く低下する。 30

#### 【 0 1 4 0 】

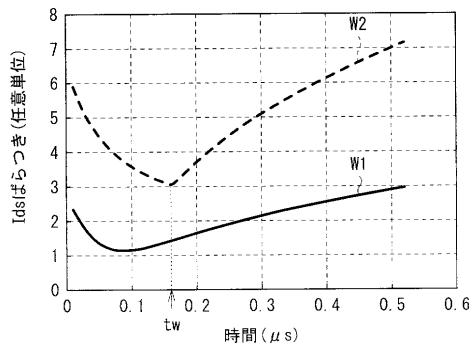

図 4 5 は、図 4 4 に示した電流 I ds のばらつきの時間依存性を表すものである。特性 W 1 は、標準偏差を平均値で割ったもの（ / ave. ）を示し、特性 W 2 は、ばらつき幅を平均値で割ったもの（ Range / ave. ）を示す。このように、電流 I ds のばらつきは、ある時間 t （例えば特性 W 2 では時間 t w ）において極小値をとる。つまり、 I ds 補正を時間 t w の長さで行うと、電流 I ds のばらつき幅を最も小さくすることができる。 30

#### 【 0 1 4 1 】

表示装置 2 では、このように、 I ds 補正期間 P 2 2 の長さ（図 4 3 におけるタイミング t 2 2 ~ t 2 3 ）を、電流 I ds のばらつきが小さくなる長さ（例えば時間 t w ）に設定している。これにより、タイミング t 2 3 における電流 I ds のばらつきを抑えることができるため、画質の低下を抑えることができる。 40

#### 【 0 1 4 2 】

##### （ 画質について ）

表示装置 2 では、図 4 1 に示したように、アノード 3 1 2 W , 3 1 2 G を、3 本のデータ線 D T L と重なるように配置し、アノード 3 1 2 R を、データ線 D T L と重ならないように配置している。これにより、以下に示すように、画質を高めることができる。 50

#### 【 0 1 4 3 】

すなわち、アノード 3 1 2 W , 3 1 2 G を 3 本のデータ線 D T L と重なるように配置することにより、アノード 3 1 2 W , 3 1 2 G の面積を広くすることができ、開口部 W I N を広くすることができる。このように開口部 W I N を広くした場合には、開口部 W I N が狭い場合に比べて、同じ発光輝度を実現するための、発光層 2 3 0 における電流密度を低くすることができる。よって、表示装置 2 では、発光層 2 3 0 の経時劣化（いわゆる焼き

付き)を抑えることができ、画質を高めることができる。

【0144】

その際、アノード312W, 312Gが3本のデータ線DTLと重なっているため、これらの3本のデータ線DTLにおける信号Sigが、カップリングにより、アノード312W, 312Gにノイズとして伝わってしまうおそれがある。しかしながら、アノード312W, 312Gに生ずるノイズは、3つの信号Sigからのノイズの和になるため、互いに打ち消し合うことにより、画質への影響を低減することができる。すなわち、図42に示したように、信号Sigは、上記第1の実施の形態の場合と異なり電圧Vofsを含まず、複数の画素電圧Vsigが連なるものであるため、1水平期間(1H)ごとの遷移タイミングttでは、電圧が上昇する方向の遷移(立ち上がり遷移)と、電圧が下降する方向の遷移(立ち下がり遷移)のいずれも生じる。よって、ある遷移タイミングttにおける3つの信号Sigに、立ち上がり遷移と立ち下がり遷移の両方が生ずる場合には、アノード312W, 312Gに生ずるノイズが互いに打ち消し合うため、ノイズを抑えることができ、画質を高めることができる。

【0145】

以上のように本実施の形態では、アノードを複数の信号線と重ねて配置するとともに、複数の画素電圧を連ねて信号Sigを構成したので、画質を高めることができる。その他の効果は、上記第1の実施の形態の場合と同様である。

【0146】

[変形例2-1]

上記実施の形態では、走査信号WSの立ち下がり部分の電圧が短時間で変化するものでしたが、これに限定されるものではなく、これに代えて、例えば、この立ち下がり部分の電圧が徐々に下がるようにしてもよい。以下に、本変形例について、詳細に説明する。

【0147】

図46は、本変形例に係る表示装置2Aにおける表示動作のタイミング図を表すものであり、(A)は走査信号WSの波形を示し、(B)は電源信号DSの波形を示し、(C)は信号Sigの波形を示し、(D)は駆動トランジスタDRTのゲート電圧Vgの波形を示し、(E)は駆動トランジスタDRTのソース電圧Vsの波形を示す。

【0148】

まず、本変形例に係る駆動部50Aは、タイミングt21~t22の期間(書込期間P21)において、上記第2の実施の形態の場合と同様に、サブ画素11に対して画素電圧Vsigの書き込みを行うとともに、サブ画素11を初期化する。

【0149】

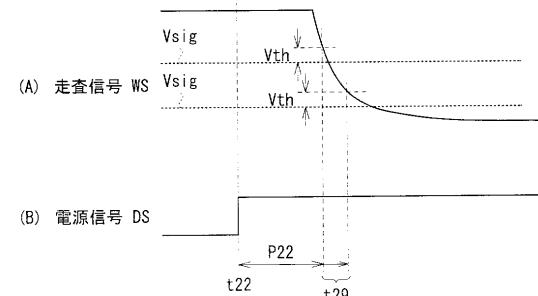

次に、駆動部50Aは、タイミングt22~t29の期間(I<sub>ds</sub>補正期間P22)において、上記第2の実施の形態に係る表示部40と同様に、サブ画素11に対してI<sub>ds</sub>補正を行う。その際、本変形例に係る走査線駆動部23Aは、波形の立ち下がり部分の電圧が徐々に下がる走査信号WSを生成する(図46(A))。これにより、画素電圧Vsigのレベルにより、I<sub>ds</sub>補正期間P22の時間の長さ(タイミングt22~t29)が異なるように動作する。

【0150】

図47は、I<sub>ds</sub>補正動作のタイミング図を表すものであり、(A)は走査信号WSの波形を示し、(B)は電源信号DSの波形を示す。書込トランジスタWSTRは、走査信号WSの電圧が、(画素電圧Vsig+閾値電圧Vth)よりも高い場合にはオン状態になり、(画素電圧Vsig+閾値電圧Vth)よりも低い場合にはオフ状態になる。走査信号WSは、立ち下がりの際、図47(A)に示したように、電圧が徐々に低下する。よって、この書込トランジスタWSTRがオン状態からオフ状態に変化するタイミングt29は、画素電圧Vsigのレベルに依存する。すなわち、I<sub>ds</sub>補正期間P22の時間の長さは、画素電圧Vsigのレベルに依存する。具体的には、I<sub>ds</sub>補正期間P22の時間は、画素電圧Vsigのレベルが高いほど短く、画素電圧Vsigのレベルが低いほど長くなる。

【0151】

10

20

30

40

50

そして、 $I_{ds}$ 補正が終了した後、駆動部 50 A は、タイミング  $t_{29}$  以降の期間（発光期間  $P_{23}$ ）において、上記第 2 の実施の形態の場合と同様に、サブ画素 11 を発光させる。

#### 【0152】

このように、表示装置 2 A では、走査信号  $WS$  の波形の立ち下がり部分の電圧が徐々に下がるようにしている。これにより、以下に示すように、画質を高めることができる。

#### 【0153】

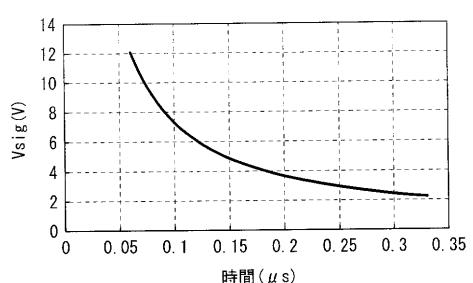

図 44, 45 に示したように、電流  $I_{ds}$  のばらつきは、ある時間  $t$ （例えば特性  $W2$  では時間  $t_w$ ）において極小値をとる。この電流  $I_{ds}$  のばらつきが極小値になる時間は、画素電圧  $V_{sig}$  に応じて変化する。

10

#### 【0154】

図 48 は、電流  $I_{ds}$  のばらつきが極小値になる時間と、画素電圧  $V_{sig}$  との関係を表すものである。このように、電流  $I_{ds}$  のばらつきが極小値になる時間は、画素電圧  $V_{sig}$  の電圧が高いほど短くなり、画素電圧  $V_{sig}$  の電圧が低いほど長くなる。すなわち、 $I_{ds}$  補正期間  $P_{22}$  の時間を、画素電圧  $V_{sig}$  の電圧が高いほど短くし、画素電圧  $V_{sig}$  の電圧が低いほど長くすれば、画素電圧  $V_{sig}$  によらず、タイミング  $t_{29}$  における電流  $I_{ds}$  のばらつきを抑えることができる。

#### 【0155】

表示装置 2 A では、このように画素電圧  $V_{sig}$  によって  $I_{ds}$  補正期間  $P_{22}$  の時間の長さを変化させるために、走査信号  $WS$  の立ち下がり部分の電圧を徐々に下げるようしている。具体的には、図 48 に示した特性を実現できるように、走査信号  $WS$  の立ち下がり部分の波形を生成している。これにより、画素電圧  $V_{sig}$  の電圧によらず、電流  $I_{ds}$  のばらつきを抑えることができ、画質の低下を抑えることができる。

20

#### 【0156】

なお、このような走査信号  $WS$  の波形を生成する方法については、例えば、特開 2008-9198 に記載がある。

#### 【0157】

##### [変形例 2-2]

上記実施の形態では、 $I_{ds}$  補正を行うようにしたが、これに限定されるものではなく、これに代えて、この  $I_{ds}$  補正を行わないようにしてもよい。以下に、本変形例について詳細に説明する。

30

#### 【0158】

図 49 は、本変形例に係る表示装置 2 B における表示動作のタイミング図を表すものであり、(A) は走査信号  $WS$  の波形を示し、(B) は信号  $Sig$  の波形を示し、(C) は駆動トランジスタ  $DRTr$  のゲート電圧  $V_g$  の波形を示し、(D) は駆動トランジスタ  $DRTr$  のソース電圧  $V_s$  の波形を示す。

#### 【0159】

本変形例に係る駆動部 50 B は、タイミング  $t_{31} \sim t_{32}$  の期間（書込期間  $P_{31}$ ）において、サブ画素 11 に対する画素電圧  $V_{sig}$  の書き込みを行う。具体的には、まず、データ線駆動部 57 が、タイミング  $t_{31}$  において、信号  $Sig$  を画素電圧  $V_{sig}$  に設定し（図 49 (B)）、走査線駆動部 23 が、走査信号  $WS$  の電圧を低レベルから高レベルに変化させる（図 49 (A)）。これにより、書込トランジスタ  $WSTr$  がオン状態になり、駆動トランジスタ  $DRTr$  のゲート電圧  $V_g$  が電圧  $V_{sig}$  に設定される（図 49 (C)）。そして、駆動トランジスタ  $DRTr$  の電流  $I_{ds}$  が発光素子 19 に流れて、ソース電圧  $V_s$  が定まる（図 49 (D)）。このようにして、発光素子 19 は、タイミング  $t_{31}$  以降の期間（発光期間  $P_{32}$ ）において発光する。

40

#### 【0160】

この場合でも、複数の画素電圧を連ねて信号  $Sig$  を構成することができるため、上記第 2 の実施の形態の場合と同様に、画質を高めることができる。

#### 【0161】

50

## [変形例 2 - 3]

上記実施の形態では、アノード 312W, 312G を 3 本のデータ線 DTL と重なるように配置したが、これに限定されるものではなく、これに代えて、例えば、上記第 1 の実施の形態の場合(図 7)と同様に、各アノード 212 をデータ線 DTL と重ならないように配置してもよいし、上記第 1 の実施の形態の変形例 1 - 5 の場合(図 23)と同様に、各アノード 212 を 1 本のデータ線 DTL と重なるように配置してもよい。

## 【0162】

## [変形例 2 - 4]

以上、第 2 の実施の形態およびその変形例について説明したが、これらのうちの 2 以上を組み合わせてもよい。また、これらに、上記第 1 の実施の形態の変形例のうちの 1 以上を組み合わせてもよい。

10

## 【0163】

## &lt;3. 適用例&gt;

次に、上記実施の形態および変形例で説明した表示装置の適用例について説明する。

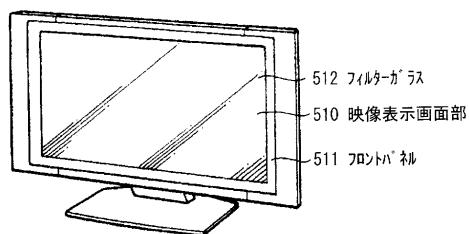

## 【0164】

図 50 は、上記実施の形態等の表示装置が適用されるテレビジョン装置の外観を表すものである。このテレビジョン装置は、例えば、フロントパネル 511 およびフィルターガラス 512 を含む映像表示画面部 510 を有している。このテレビジョン装置は、上記実施の形態等に係る表示装置により構成されている。

20

## 【0165】

上記実施の形態等の表示装置は、このようなテレビジョン装置の他、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置、携帯型ゲーム機、あるいはビデオカメラなどのあらゆる分野の電子機器に適用することが可能である。言い換えると、上記実施の形態等の表示装置は、映像を表示するあらゆる分野の電子機器に適用することが可能である。

## 【0166】

以上、いくつかの実施の形態および変形例、ならびに電子機器への適用例を挙げて本技術を説明したが、本技術はこれらの実施の形態等には限定されず、種々の変形が可能である。

## 【0167】

30

例えば、上記実施の形態等では、書込トランジスタ WSTR および駆動トランジスタ DRTR を NMOS で構成したが、これに限定されるものではなく、これに代えて、これらのトランジスタのうちの一方または双方を PMOS で構成してもよい。

## 【0168】

また、例えば、上記実施の形態等では、サブ画素をいわゆる「2Tr1C」の構成にしたが、これに限定されるものではなく、その他の素子を追加して構成してもよい。具体的には、例えば、図 51 に示すサブ画素 17 のように、発光素子 19 と並列接続された容量素子 Csub を設け、いわゆる「2Tr2C」の構成にしてもよい。また、例えば、図 52 に示すサブ画素 18 のように、駆動トランジスタ DRTR への電源信号 DS の供給を制御する電源トランジスタ DSTr を設け、いわゆる「3Tr1C」の構成にしてもよい。

40

## 【0169】

また、例えば、上記各実施の形態では、表示装置は、有機 EEL 表示素子を有するものとしたが、これに限定されるものではなく、電流駆動型の表示素子を有するものであれば、どのような表示装置であってもよい。

## 【0170】

なお、本技術は以下の構成とすることができる。

## 【0171】

(1) 第 1 の基本色光を発する第 1 の画素と、第 2 の基本色光を発する第 2 の画素と、基本色光以外の一の色光を発する非基本色画素との組み合わせから構成される第 1 の画素セットと、

50

前記第1の基本色光を発する第1の画素と、第3の基本色光を発する第3の画素と、前記一の色光を発する非基本色画素との組み合わせから構成される第2の画素セットとを備え、

前記第1の画素セットおよび前記第2の画素セットは、第1の方向および前記第1の方向と交差する第2の方向のいずれか一方または双方において、交互に配置されている表示装置。

**【0172】**

(2) 前記第1の方向に延伸する複数の信号線をさらに備え、

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は、それぞれ、画素電極を含む発光素子を有し、

10

前記第1の画素の画素電極は、前記複数の信号線のうちの、その第1の画素が属する画素セットの配置領域内に配置された所定数の信号線のいずれとも重なるように配置され、

前記非基本色画素の画素電極は、前記複数の信号線のうちの、その非基本色画素が属する画素セットの配置領域内に配置された所定数の信号線のいずれとも重なるように配置されている

前記(1)に記載の表示装置。

**【0173】**

(3) 前記第2の画素の画素電極および前記第3の画素の画素電極は、前記複数の信号線のいずれとも重ならないように配置されている

前記(2)に記載の表示装置。

20

**【0174】**

(4) 前記第1の方向に延伸する複数の信号線をさらに備え、

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は、それぞれ、前記複数の信号線のうちの1本と重なるように配置された画素電極を含む発光素子を有する

前記(1)に記載の表示装置。

**【0175】**

(5) 前記第1の方向に延伸する複数の信号線をさらに備え、

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は、それぞれ、前記複数の信号線のいずれとも重ならないように配置された画素電極を含む発光素子を有する

30

前記(1)に記載の表示装置。

**【0176】**

(6) 前記信号線に画素信号を印加する駆動部をさらに備え、

前記画素信号では、各画素の輝度を画定する輝度信号部分が時間軸上で連なっている

前記(2)から(5)のいずれかに記載の表示装置。

**【0177】**

(7) 前記信号線に画素信号を印加する駆動部をさらに備え、

前記画素信号は、直流信号部分と、各画素の輝度を画定する輝度信号部分とを含み、

前記輝度信号部分と前記直流信号部分とが時間軸上で交互に配置されている

40

前記(4)または(5)に記載の表示装置。

**【0178】**

(8) 前記第2の基本色光に対応する第1の輝度情報マップに対してフィルタ処理を行うとともに、前記第3の基本色光に対応する第2の輝度情報マップに対してフィルタ処理を行うフィルタ部と、

フィルタ処理された第1の輝度情報マップから、前記第1の画素セットに対応する位置の第1の輝度情報を抽出するとともに、フィルタ処理された第2の輝度情報マップから、前記第2の画素セットに対応する位置の第2の輝度情報を抽出する輝度情報抽出部とをさらに備え、

前記駆動部は、前記第1の輝度情報に基づいて前記第2の画素に対応する前記輝度信号

50

部分を生成するとともに、前記第2の輝度情報に基づいて前記第3の画素に対応する前記輝度信号部分を生成する

前記(6)または(7)に記載の表示装置。

【0179】

(9) 前記第1の方向に延伸する複数の信号線をさらに備え、

前記第1の画素セットが、第1の画素セル内に配置され、

前記第2の画素セットが、第2の画素セル内に配置され、

前記第1の画素セルにおいて、前記第1の画素および前記非基本色画素は、前記第1の方向に配列されるとともに、前記第2の画素と前記第2の方向において配列され、

前記第2の画素セルにおいて、前記第1の画素および前記非基本色画素は、前記第1の方向に配列されるとともに、前記第3の画素と前記第2の方向において配列されている

前記(1)から(8)のいずれかに記載の表示装置。

【0180】

(10) 前記第1の方向に延伸する複数の信号線をさらに備え、

前記第1の画素セットが、第1の画素セル内に配置され、

前記第2の画素セットが、第2の画素セル内に配置され、

前記第1の画素セルにおいて、前記第1の画素、前記第2の画素、および前記非基本色画素は、前記第2の方向に配列され、

前記第2の画素セルにおいて、前記第1の画素、前記第3の画素、および前記非基本色画素は、前記第2の方向に配列されている

前記(1)から(8)のいずれかに記載の表示装置。

【0181】

(11) 前記第1の方向に延伸する複数の信号線をさらに備え、

前記第1の画素セットが、第1の画素セル内に配置され、

前記第2の画素セットが、第2の画素セル内に配置され、

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素の開口部は円形または橢円形であり、

前記第1の画素セルにおいて、前記第1の画素、前記第2の画素、および前記非基本色画素は、互いに隣り合うように配置されるとともに、そのうちの2つは、前記第2の方向に配列され、

前記第2の画素セルにおいて、前記第1の画素、前記第3の画素、および前記非基本色画素は、互いに隣り合うように配置されるとともに、そのうちの2つは、前記第2の方向に配列されている

前記(1)から(8)のいずれかに記載の表示装置。

【0182】

(12) 前記第1の画素セットは、複数の第1の画素セル内に、互いに異なる配置パターンとなるように配置され、

前記第2の画素セットは、複数の第2の画素セル内に、互いに異なる配置パターンとなるように配置されている

前記(9)から(11)のいずれかに記載の表示装置。

【0183】

(13) 前記第2の画素における開口領域、および前記第3の画素における開口領域は、前記第1の画素における開口領域、および前記非基本色画素における開口領域のいずれよりも大きい

前記(1)から(12)のいずれかに記載の表示装置。

【0184】

(14) 前記第1の画素における開口領域は、前記非基本色画素の開口領域以上の大きさである

前記(13)に記載の表示装置。

【0185】

10

20

30

40

50

(15) 前記第1の基本色光は緑色光であり、

前記第2の基本色光は青色光であり、

前記第3の基本色光は赤色光である

前記(1)から(14)のいずれかに記載の表示装置。

## 【0186】

(16) 前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は

、それぞれ、

容量素子と、

ドレインと、前記容量素子の一端に接続されたゲートと、前記容量素子の他端に接続さ

れたソースとを含むトランジスタと

を有する

前記(1)から(15)のいずれかに記載の表示装置。

## 【0187】

(17) 表示装置と

前記表示装置に対して動作制御を行う制御部と

を備え、

前記表示装置は、

第1の基本色光を発する第1の画素と、第2の基本色光を発する第2の画素と、基本色

光以外の一の色光を発する非基本色画素との組み合わせから構成される第1の画素セット

と、

前記第1の基本色光を発する第1の画素と、第3の基本色光を発する第3の画素と、前

記一の色光を発する非基本色画素との組み合わせから構成される第2の画素セットと

を備え、

前記第1の画素セットおよび前記第2の画素セットは、第1の方向および前記第1の方

向と交差する第2の方向のいずれか一方または双方において、交互に配置されている

電子機器。

## 【符号の説明】

## 【0188】

1, 2...表示装置、10, 10B~10M, 40...表示部、11, 11R, 11G, 1

1B, 11W, 14R, 14G, 14B, 14W, 17, 18...サブ画素、15, 15R

, 15G, 15B, 15W, 16, 16R, 16G, 16B, 16W...回路領域、19...

発光素子、20, 50...駆動部、22...タイミング生成部、23...走査線駆動部、26...

電源線駆動部、27, 27N, 57...データ線駆動部、30...映像信号処理部、31...リ

ニアガンマ変換部、32...RGBW変換部、33R, 33B...フィルタ処理部、34R,

34B...輝度情報抽出部、35...信号処理部、36...パネルガンマ変換部、201...ゲー

ト、202...絶縁層、203...ポリシリコン、204...絶縁層、205...コントクト/配

線、211...絶縁層、212, 212R, 212G, 212B, 212W, 232, 31

2, 312R, 312G, 312B, 312W...アノード、213, 213L, 221...

絶縁層、214...黄色発光層、215...青色発光層、216, 236...カソード、217

, 217L...絶縁層、218, 218I, 238...カラーフィルタ、219...ブラックマ

トリクス、220...透明基板、230, 230H, 230I, 230J...発光層、CA,

CA1, CA2, CB, CB1, CB2...セル、Cs, Csub...容量素子、DRT...駆

動トランジスタ、DS...電源信号、DSTR...電源トランジスタ、DTL...データ線、H

...高さ、MAPR, MAPB...マップ、PL...電源線、P1...初期化期間、P2...Vth補

正期間、P3, P13, P15...書込・μ補正期間、P4, P14, P16...発光期間、

P21...書込期間、P22...Ids補正期間、P23...発光期間、P31...書込期間、P3

2...発光期間、R1, R2...直径、Sdisp, Sdisp2...映像信号、Sig...信号、Sync...

同期信号、S31, S34, S35...映像信号、SR32, SG32, SB32, SW3

2, SR33, SB33, SR34, SB34...信号、Vcath, Vccp, Vini, Vofs...

電圧、Vsig...画素電圧、WIN...開口部、WS, WSA, WSB...走査信号、WSL,

10

20

40

50

W S A L , W S B L ...走査線、 W S T r ...書き込トランジスタ。

【図1】

【 図 2 】

【図3】

【図4】

【図5】

【図6 A】

【図6 B】

【図7】

【図 8】

【図 9 A】

【図 9 B】

【図 10】

【図 11】

### 【図12】

【図13】

### 【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30A】

【図31B】

【図30B】

【図32A】

【図31A】

【図32B】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図 4 3】

【図 4 4】

【図 4 5】

【図 4 6】

【図 4 7】

【図 4 8】

【図 4 9】

【図 5 1】

【図 5 0】

【図 5 2】

## フロントページの続き

| (51)Int.Cl.   |              | F I              |               |              |

|---------------|--------------|------------------|---------------|--------------|

| <i>H 05 B</i> | <i>33/12</i> | <i>(2006.01)</i> | <i>G 09 G</i> | <i>3/20</i>  |

| <i>H 01 L</i> | <i>51/50</i> | <i>(2006.01)</i> | <i>G 09 G</i> | <i>3/20</i>  |

|               |              |                  | <i>G 09 G</i> | <i>3/20</i>  |

|               |              |                  | <i>G 09 G</i> | <i>3/20</i>  |

|               |              |                  | <i>G 09 G</i> | <i>3/20</i>  |

|               |              |                  | <i>G 09 G</i> | <i>3/20</i>  |

|               |              |                  | <i>G 09 G</i> | <i>3/20</i>  |

|               |              |                  | <i>G 09 G</i> | <i>3/20</i>  |

|               |              |                  | <i>G 09 G</i> | <i>3/20</i>  |

|               |              |                  | <i>G 09 G</i> | <i>3/20</i>  |

|               |              |                  | <i>G 09 G</i> | <i>3/20</i>  |

|               |              |                  | <i>G 09 G</i> | <i>3/20</i>  |

|               |              |                  | <i>G 09 G</i> | <i>3/20</i>  |

|               |              |                  | <i>G 09 G</i> | <i>3/20</i>  |

|               |              |                  | <i>G 09 F</i> | <i>9/30</i>  |

|               |              |                  | <i>H 05 B</i> | <i>33/12</i> |

|               |              |                  | <i>H 05 B</i> | <i>33/14</i> |

(56)参考文献 特開2008-096549 (JP, A)

特表2008-502004 (JP, A)

特開2009-069251 (JP, A)

特開2009-282190 (JP, A)

國際公開第2006/115165 (WO, A1)

特表2007-532949 (JP, A)

特表2008-539555 (JP, A)

特開2002-287664 (JP, A)

特開2001-313172 (JP, A)

特開2006-106659 (JP, A)

特開2005-106993 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

|               |                  |   |                  |

|---------------|------------------|---|------------------|

| <i>G 09 F</i> | <i>9 / 3 0</i>   | - | <i>9 / 4 6</i>   |

| <i>H 01 L</i> | <i>2 7 / 3 2</i> |   |                  |

| <i>G 09 G</i> | <i>3 / 1 2</i>   | - | <i>3 / 1 4</i>   |

|               | <i>3 / 3 0</i>   | - | <i>3 / 3 2</i>   |

| <i>G 09 G</i> | <i>3 / 0 0</i>   | - | <i>3 / 0 8</i>   |

|               | <i>3 / 1 2</i>   |   |                  |

|               | <i>3 / 1 6</i>   |   |                  |

|               | <i>3 / 1 9</i>   | - | <i>3 / 2 6</i>   |

|               | <i>3 / 3 0</i>   |   |                  |

|               | <i>3 / 3 4</i>   |   |                  |

|               | <i>3 / 3 8</i>   |   |                  |

| <i>H 01 L</i> | <i>5 1 / 5 0</i> |   |                  |

| <i>H 05 B</i> | <i>3 3 / 0 0</i> | - | <i>3 3 / 2 8</i> |