등록특허 10-2661125

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2024년04월29일

(11) 등록번호 10-2661125

(24) 등록일자 2024년04월23일

- (51) 국제특허분류(Int. Cl.)

*H02J 50/20* (2016.01) *G06F 1/04* (2006.01)

*G06F 1/26* (2006.01) *G06F 1/324* (2019.01)

*H02M 3/335* (2006.01) *H02M 3/337* (2006.01)

*H03L 7/099* (2006.01)

- (52) CPC특허분류

*H02J 50/20* (2016.02)

*G06F 1/04* (2013.01)

- (21) 출원번호 10-2020-7003772

- (22) 출원일자(국제) 2018년08월10일

심사청구일자 2021년08월10일

- (85) 번역문제출일자 2020년02월07일

- (65) 공개번호 10-2020-0035964

- (43) 공개일자 2020년04월06일

- (86) 국제출원번호 PCT/US2018/046307

- (87) 국제공개번호 WO 2019/033024

국제공개일자 2019년02월14일

(30) 우선권주장

15/674,360 2017년08월10일 미국(US)

## (56) 선행기술조사문현

US20170040988 A1\*

US20170126069 A1\*

US05657211 A

US20140191815 A1

\*는 심사관에 의하여 인용된 문현

전체 청구항 수 : 총 16 항

심사관 : 박형준

## (54) 발명의 명칭 미세 타이밍 해상도를 갖는 무선 전력 송신

**(57) 요약**

미세 타이밍 해상도를 갖는 무선 전력 전송을 위한 시스템들(100) 및 방법들에서, 전기 전력 송신기(101)는 트랜지스터(Q1); 및 풀-클록 주기보다 큰 해상도로 선택된 시간에서 펄스의 상승 에지를 생성하기 위해 트랜지스터(Q1)의 게이트를 제어하는 상승 에지 제어 회로(103)를 포함할 수 있다.

**대 표 도**

(52) CPC특허분류

*G06F 1/266* (2013.01)

*G06F 1/324* (2019.01)

*H02M 3/33515* (2013.01)

*H02M 3/33576* (2013.01)

*H02M 3/3376* (2013.01)

*H03L 7/099* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

전기 전력 송신기로서,

트랜지스터; 및

상승 에지 제어 회로를 포함하고, 상기 상승 에지 제어 회로는,

전압 제어 발진기(voltage controlled oscillator)(VCO) - 상기 VCO는 전력 캐리어 주파수 입력,  $m$ 개의 스테이지 출력들 및 클록 신호 출력을 포함함 -;

상승 에지 멀티플렉서 - 상기 상승 에지 멀티플렉서는,

상기  $m$ 개의 스테이지 출력들에 커플링된  $m$ 개의 서브-부분 입력들;

선택 입력; 및

상승 에지 멀티플렉서 출력을 포함함 -;

상승 에지 분배기 회로 - 상기 상승 에지 분배기 회로는,

상기 클록 신호 출력에 커플링된 입력; 및

$n$ 개의 상승 에지 부분 출력들을 포함함 -;

카운터 선택 회로 - 상기 카운터 선택 회로는,

상기  $n$ 개의 상승 에지 부분 출력들에 커플링된 입력들;

선택 입력; 및

출력을 포함함 -; 및

상승 에지 로직 회로 - 상기 상승 에지 로직 회로는,

상기 상승 에지 멀티플렉서 출력에 커플링된 제1 입력;

상기 카운터 선택 회로의 상기 출력에 커플링된 제2 입력; 및

상기 트랜지스터의 게이트에 커플링된 상승 에지 제어 출력을 포함함 -

를 포함하고,

상기 전기 전력 송신기는 전력 캐리어 주파수를 통해 무선으로 전력을 방출하도록 구성되는 인덕터를 추가로 포함하는, 전기 전력 송신기.

#### 청구항 2

삭제

#### 청구항 3

삭제

#### 청구항 4

제1항에 있어서, 상기 상승 에지 분배기 회로는 클록 신호를  $n$ 개의 부분들로 분할하도록 구성되는, 전기 전력 송신기.

#### 청구항 5

제4항에 있어서, 상기 상승 에지 멀티플렉서는 상기  $n$ 개의 부분들 각각을 복수의  $m$ 개의 서브-부분으로 세분화하도록 구성되는, 전기 전력 송신기.

#### 청구항 6

제5항에 있어서,  $m$ 은 상기 VCO의 클록 위상들의 수인 전기 전력 송신기.

#### 청구항 7

제6항에 있어서, 상기 상승 에지 제어 회로는 모든 가능한  $m$ 개의 값보다 적은 수의 값들에만 타이밍 지연을 적용하도록 구성되는 지연 회로를 추가로 포함하는 전기 전력 송신기.

#### 청구항 8

삭제

#### 청구항 9

제1항에 있어서, 상기 트랜지스터의 게이트는, 펄스의 하강 에지를 생성하기 위해 상기 전력 캐리어 주파수를 채택하는 하강 에지 제어 회로를 통해 추가로 제어되고, 상기 하강 에지 제어 회로는,

상기  $m$ 개의 스테이지 출력들에 커플링된  $m$ 개의 서브-부분 입력들, 선택 입력 및 하강 에지 멀티플렉서 출력을 갖는 하강 에지 멀티플렉서;

상기 클록 신호 출력에 커플링된 입력을 갖고,  $n$ 개의 하강 에지 부분 출력들을 갖는 하강 에지 분배기 회로; 및

상기 하강 에지 멀티플렉서 출력 및 상기  $n$ 개의 하강 에지 부분 출력들에 커플링된 입력들을 갖고, 상기 트랜지스터의 게이트에 커플링된 하강 에지 제어 출력을 갖는 하강 에지 로직 회로

를 포함하는, 전기 전력 송신기.

#### 청구항 10

제9항에 있어서, 상기 상승 에지 제어 회로에 커플링된 설정 입력 및 상기 하강 에지 제어 회로에 커플링된 재 설정 입력을 갖는 플립-플롭을 추가로 포함하고, 상기 플립-플롭의 출력은 상기 펄스를 생성하는 데 사용되고, 상기 펄스는 상기 트랜지스터의 게이트를 구동하는 데 사용 가능한 펄스-폭 변조(pulse-width modulated)(PWM) 펄스인 전기 전력 송신기.

#### 청구항 11

제1항에 있어서,

수신기를 추가로 포함하고, 상기 수신기는,

무선 전력을 수신하도록 구성되는 인덕터; 및

상기 인덕터에 커플링된 제2 트랜지스터 - 상기 제2 트랜지스터의 게이트는 제2 상승 에지 제어 회로 및 제2 하강 에지 제어 회로를 사용하여 제어되고, 상기 제2 상승 에지 제어 회로 및 상기 제2 하강 에지 제어 회로는 전력 캐리어 주파수를 사용하여 펄스를 발생시키도록 구성됨 -

를 포함하는, 전기 전력 송신기.

#### 청구항 12

제11항에 있어서, 상기 트랜지스터는 H-브리지 회로의 일부이고, 상기 제2 트랜지스터는 정류기 브리지의 일부인 전기 전력 송신기.

#### 청구항 13

컴퓨팅 디바이스로서,

프로세서; 및

상기 프로세서에 전력을 제공하도록 구성되는 무선 전력 수신기 - 상기 무선 전력 수신기는 트랜지스터에 커플링된 인덕터를 포함하고, 상기 트랜지스터의 게이트는 상승 에지 제어 회로를 통해 부분적으로 제어됨 - 를 포함하고, 상기 상승 에지 제어 회로는,

전압 제어 발진기(voltage controlled oscillator)(VCO) - 상기 VCO는 전력 캐리어 주파수 입력,  $m$ 개의 스테이지 출력들 및 클록 신호 출력을 포함함 -;

상승 에지 멀티플렉서 - 상기 상승 에지 멀티플렉서는,

상기  $m$ 개의 스테이지 출력들에 커플링된  $m$ 개의 서브-부분 입력들;

선택 입력; 및

상승 에지 멀티플렉서 출력을 포함함 -;

상승 에지 분배기 회로 - 상기 상승 에지 분배기 회로는,

상기 클록 신호 출력에 커플링된 입력; 및

$n$ 개의 상승 에지 부분 출력들을 포함함 -;

카운터 선택 회로 - 상기 카운터 선택 회로는,

상기  $n$ 개의 상승 에지 부분 출력들에 커플링된 입력들;

선택 입력; 및

출력을 포함함 -; 및

상승 에지 로직 회로 - 상기 상승 에지 로직 회로는,

상기 상승 에지 멀티플렉서 출력에 커플링된 제1 입력;

상기 카운터 선택 회로의 상기 출력에 커플링된 제2 입력; 및

상기 트랜지스터의 게이트에 커플링된 상승 에지 제어 출력을 포함함 -

를 포함하는, 컴퓨팅 디바이스.

#### 청구항 14

제13항에 있어서, 상기 무선 전력 수신기는 배터리를 충전함으로써 상기 프로세서에 전력을 제공하도록 구성되는 컴퓨팅 디바이스.

#### 청구항 15

제13항에 있어서, 상기 트랜지스터는 정류기 회로의 일부인 컴퓨팅 디바이스.

#### 청구항 16

삭제

#### 청구항 17

제13항에 있어서,

상기 상승 에지 분배기 회로는 클록 신호를  $n$ 개의 부분들로 분할하도록 구성되고;

상기 상승 에지 멀티플렉서는 상기  $n$ 개의 부분들 각각을 복수의  $m$ 개의 서브-부분으로 세분화하도록 구성되고,  $m$ 은 상기 VCO의 클록 위상들의 수인, 컴퓨팅 디바이스.

#### 청구항 18

제13항에 있어서, 상기 트랜지스터의 게이트는, 펄스의 하강 에지를 생성하기 위해 전력 캐리어 주파수를 채택하도록 구성되는 하강 에지 제어 회로를 통해 부분적으로 추가로 제어되고, 상기 무선 전력 수신기는 상기 상승 에지 제어 회로에 커플링된 설정 입력 및 상기 하강 에지 제어 회로에 커플링된 채설정 입력을 갖는 플립-플롭

을 추가로 포함하고, 상기 플립-플롭의 출력은 상기 펄스를 생성하는 데 사용 가능하고, 상기 하강 에지 제어 회로는,

상기  $m$ 개의 스테이지 출력들에 커플링된  $m$ 개의 서브-부분 입력들, 선택 입력 및 하강 에지 멀티플렉서 출력을 갖는 하강 에지 멀티플렉서;

상기 클록 신호 출력에 커플링된 입력을 갖고,  $n$ 개의 하강 에지 부분 출력들을 갖는 하강 에지 분배기 회로; 및

상기 하강 에지 멀티플렉서 출력 및 상기  $n$ 개의 하강 에지 부분 출력들에 커플링된 입력들을 갖고, 상기 트랜지스터의 게이트에 커플링된 하강 에지 제어 출력을 갖는 하강 에지 로직 회로

를 포함하는, 컴퓨팅 디바이스.

## 청구항 19

방법으로서,

전력 캐리어 주파수에 걸쳐 인덕터를 통해 무선으로 전기 전력을 수신하는 단계 - 상기 인덕터는 트랜지스터들의 세트를 갖는 정류기에 커플링됨 -;

위상-고정 루프(PLL) 회로의 전압 제어 발진기(VCO)에 의해 생성된 전압 제어 발진기(VCO) 출력의  $n \times m$ 개의 서브디비전 중 선택된 하나 이상의 것을 사용하여 펄스-폭 변조(PWM) 신호를 발생시키는 단계 - 상기 VCO는, 상기 전력 캐리어 주파수를 갖는 기준 클록을 수신하고  $m$ 개의 선택 가능한 위상들을 생성하도록 구성되고, 상기  $m$ 개의 선택 가능한 위상들은 제어 워드의 제1 부분에 기초하여 선택됨 -;

분배기에 의해, 상기 VCO 출력에 기초하여  $n$ 개의 선택 가능한 빈들을 생성하는 단계 - 상기  $n$ 개의 선택 가능한 빈들은 상기 제어 워드의 제2 부분에 기초하여 선택됨 - ; 및

상기 PWM 신호로 상기 트랜지스터들의 세트의 각각을 제어하는 단계

를 포함하는 방법.

## 청구항 20

제19항에 있어서, 상기 전력을 배터리 또는 컴퓨팅 디바이스에 제공하는 단계를 추가로 포함하는 방법.

## 발명의 설명

### 기술 분야

[0001] 이것은 일반적으로 무선 전력 송신에 관한 것으로, 보다 구체적으로는, 미세 타이밍 해상도(fractional timing resolution)를 갖는 무선 전력 송신에 관한 것이다.

### 배경 기술

[0002] 무선 전력 송신 시스템은 라디오-주파수(radio-frequency)(RF) 송신기 및 RF 수신기를 갖는다. RF 송신기는 전기 전력 소스(예를 들어, 주 전력선)에 커플링되고, 이것은 인덕터, 코일, 안테나, 금속판 또는 다른 커플링 디바이스를 사용하여 전류를 전동 전자기장으로 변환한다. RF 수신기의 다른 커플링 디바이스는 방사된 전자기장의 일부를 포착하고(서로 근접한 2개의 코일이 전기 변압기를 형성함), RF 수신기는 수신된 전자기장을 다시 전류로 변환한다.

[0003] 많은 구현들에서, RF 송신기는 충전 패드 또는 스테이션 내에 배치될 수 있고, RF 수신기는 (데스크탑, 랩톱, 태블릿, 스마트폰 등과 같은) 컴퓨팅 디바이스 또는 배터리에 커플링될 수 있다. 그 후, RF 송신기와 RF 수신기 간에 전송되는 에너지가 컴퓨팅 디바이스를 동작시키고/시키거나 배터리를 충전하는 데 사용될 수 있다. 따라서, 전송 효율(송신된 에너지량에 대한 수신된 에너지량)은 무선 전력 전송 설계에서 중요한 파라미터이다.

[0004] RF 송신기 및 RF 수신기 모두의 코일들은 다수의 스위치들 또는 트랜지스터들을 사용하여 제어되며, 전력 전송 효율을 증가시키려면 종종 해당 트랜지스터들의 정밀한 제어를 필요로 한다. 그러나, 이러한 제어를 제공하기 위해 통상적으로 필요한 고주파수 클록들은 비용 및 복잡성을 현저히 증가시킬 것이다.

## 발명의 내용

- [0005] 미세 타이밍 해상도를 갖는 무선 전력 전송을 위한 시스템들 및 방법들의 설명된 예들에서, 전기 전력 송신기가 트랜지스터; 및 풀-클록 주기보다 큰 해상도로 선택된 시간에서 펄스의 상승 에지를 생성하기 위해 트랜지스터의 게이트를 제어하도록 구성되는 상승 에지 제어 회로를 포함할 수 있다.

- [0006] 전기 전력 송신기는 또한 전력 캐리어 주파수를 통해 무선 전력을 방출하도록 구성되는 인덕터를 포함할 수 있고, 여기서 풀-클록 주기는 전력 캐리어 주파수의 역수이다. 전기 전력 송신기는 또한 전압 제어 발진기 (voltage controlled oscillator)(VCO)를 갖는 위상-고정 루프(phased-locked loop)(PLL) 회로를 포함할 수 있고, 여기서 VCO는 전력 캐리어 주파수보다  $n$ 배 큰 주파수를 갖는 클록 신호를 생성하도록 구성된다.

- [0007] 일부 경우들에서, 상승 에지 제어 회로는, VCO에 커플링되고 클록 신호를  $n$ 개의 부분으로 분할하도록 구성되는 분배기 회로를 포함할 수 있다. 상승 에지 제어 회로는 또한, VCO에 커플링되고  $n$ 개의 부분 각각을 복수의  $m$ 개의 서브-부분으로 세분화하도록 구성되는 멀티플렉서를 포함할 수 있다. 예를 들어,  $m$ 은 VCO의 클록 위상들의 수일 수 있다. 상승 에지 제어 회로는 모든 가능한  $m$ 개의 값보다 적은 수의 값들에만 타이밍 지연을 적용하도록 구성되는 지연 회로를 추가로 포함할 수 있다. 해상도는 전력 캐리어 주파수의 역수를  $n$ 곱하기  $m$ 의 곱으로 나눈 값과 동일할 수 있다.

- [0008] 일부 구현들에서, 트랜지스터의 게이트는, 해상도로 선택된 후속 시간에서 펄스의 하강 에지를 생성하기 위해 전력 캐리어 주파수를 채택하는 하강 에지 제어 회로를 통해 제어될 수 있다. 무선 전력 송신기는 상승 에지 제어 회로에 커플링된 설정 입력 및 하강 에지 제어 회로에 커플링된 재설정 입력을 갖는 플립-플롭을 추가로 포함하여, 플립-플롭의 출력이 펄스를 생성하는 데 사용되게 할 수 있고, 여기서 펄스는 트랜지스터의 게이트를 구동하는 데 사용 가능한 펄스-폭 변조(pulse-width modulated)(PWM) 펄스이다.

- [0009] 전기 전력 송신기는 또한 무선 전력을 수신하도록 구성되는 다른 인덕터; 및 다른 인덕터에 커플링된 다른 트랜지스터를 포함하는 수신기를 포함할 수 있고, 여기서 다른 트랜지스터의 다른 게이트는 다른 상승 에지 제어 회로 및 다른 하강 에지 제어 회로를 사용하여 제어되고, 다른 상승 에지 제어 회로 및 다른 하강 에지 제어 회로는 전력 캐리어 주파수를 사용하여 해상도를 갖는 다른 펄스를 발생시키도록 구성된다. 트랜지스터는 H-브리지 회로의 일부일 수 있고, 다른 트랜지스터는 정류기 브리지의 일부일 수 있다.

- [0010] 다른 실시예에서, 컴퓨팅 디바이스가 프로세서; 및 프로세서에 전력을 제공하도록 구성되는 무선 전력 수신기를 포함할 수 있고, 여기서 무선 전력 수신기는 트랜지스터에 커플링된 인덕터를 포함하고, 트랜지스터의 게이트는 전력 캐리어 주파수의 역수보다 큰 해상도로 선택된 시간에서 펄스의 상승 에지를 생성하기 위해 전력 캐리어 주파수를 채택하도록 구성되는 상승 에지 제어 회로를 통해 부분적으로 제어된다.

- [0011] 무선 전력 수신기는 배터리를 충전함으로써 프로세서에 전력을 제공하도록 구성될 수 있다. 트랜지스터는 정류기 회로의 일부일 수 있다. 그리고, 무선 전력 수신기는 PLL 회로의 VCO를 추가로 포함할 수 있으며, 여기서 VCO는 전력 캐리어 주파수를 수신하고 전력 캐리어 주파수의  $n$ 배의 주파수를 갖는 클록 신호를 생성하도록 구성된다.

- [0012] 상승 에지 제어 회로는, VCO에 커플링되고 클록 신호를  $n$ 개의 부분으로 분할하도록 구성되는 분배기; 및 VCO에 커플링되고  $n$ 개의 부분 각각을 복수의  $m$ 개의 서브-부분으로 세분화하도록 구성되는 멀티플렉서를 포함할 수 있고, 여기서  $m$ 은 VCO의 클록 위상들의 수이고, 해상도는 전력 캐리어 주파수의 역수를  $n$ 곱하기  $m$ 의 곱으로 나눈 값과 동일하다. 트랜지스터의 게이트는, 해상도로 선택된 후속 시간에서 펄스의 하강 에지를 생성하기 위해 전력 캐리어 주파수를 채택하도록 구성되는 하강 에지 제어 회로를 통해 부분적으로 추가로 제어되고, 여기서 무선 전력 수신기는 상승 에지 제어 회로에 커플링된 설정 입력 및 하강 에지 제어 회로에 커플링된 재설정 입력을 갖는 플립-플롭을 추가로 포함하고, 플립-플롭의 출력은 펄스를 생성하는 데 사용 가능하다.

- [0013] 또 다른 실시예에서, 방법은 전력 캐리어 주파수에 걸쳐 인덕터를 통해 무선으로 전기 전력을 수신하는 단계 - 인덕터는 트랜지스터들의 세트를 갖는 정류기에 커플링됨 -; PLL 회로의 VCO에 의해 생성된 VCO 출력의  $n \times m$ 개의 서브디비전 중 선택된 하나 이상의 것을 사용하여 PWM 신호를 발생시키는 단계 - VCO는 전력 캐리어 주파수를 갖는 기준 클록을 수신하고 전력 캐리어 주파수의  $n$ 배의 주파수 및  $m$ 개의 선택 가능한 위상을 갖는 출력을 생성하도록 구성됨 -; 및 PWM 신호로 트랜지스터들의 세트 각각을 제어하는 단계를 포함할 수 있다. 방법은 또한 전력을 배터리 또는 컴퓨팅 디바이스에 제공하는 단계를 포함할 수 있다.

## 도면의 간단한 설명

[0014]

도 1은 일부 실시예들에 따른 무선 전력 송신 시스템의 예의 블록도이다.

도 2는 일부 실시예들에 따른 미세 주기 타이밍 해상도를 갖는 위상-고정 루프(PLL)-기반 펄스-폭 변조(PWM) 발생기의 예의 블록도이다.

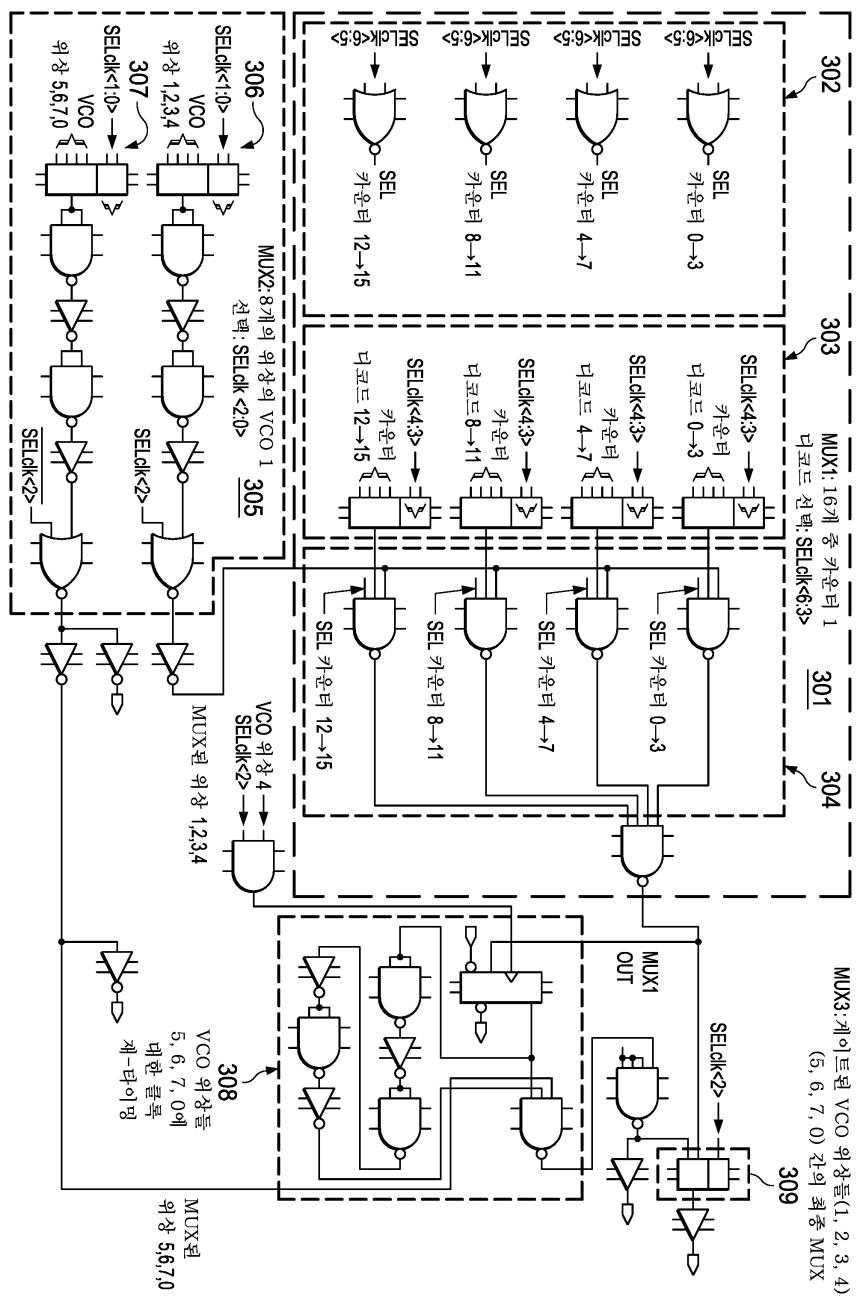

도 3은 일부 실시예들에 따른 미세 주기 타이밍 해상도를 갖는 PLL-기반 PWM 발생기의 예시적인 구현의 회로도이다.

도 4는 일부 실시예들에 따른 미세 주기 타이밍 해상도를 갖는 PLL-기반 PWM 발생기의 동작을 예시하는 차트이다.

## 발명을 실시하기 위한 구체적인 내용

[0015]

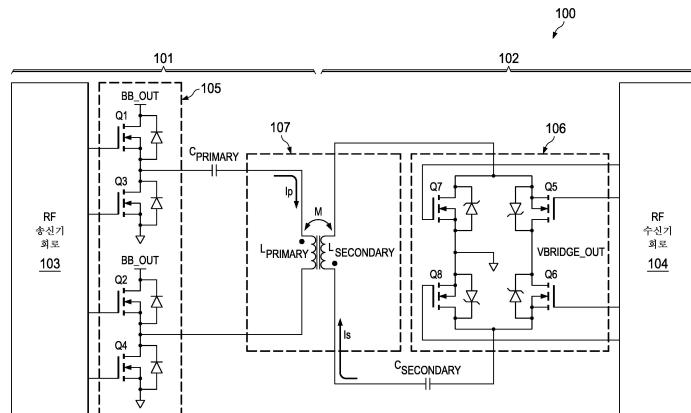

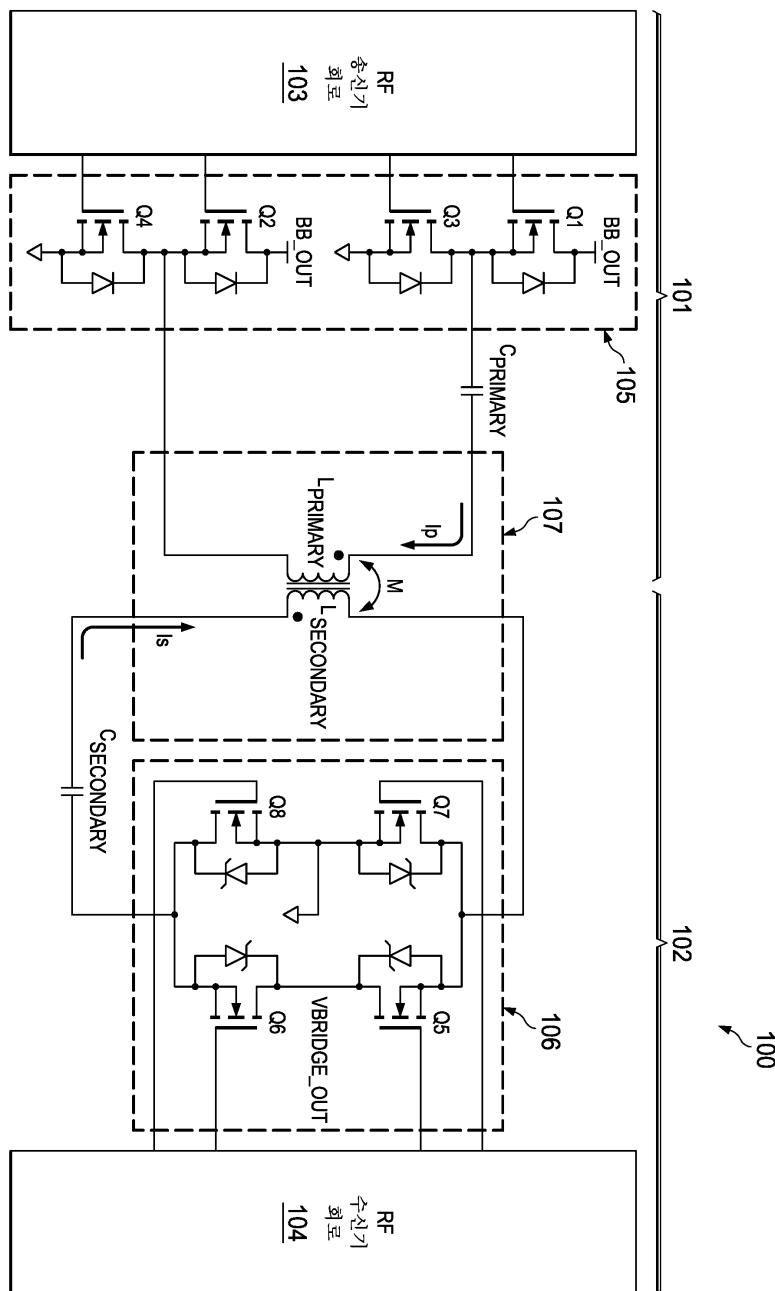

도 1은 일부 실시예들에 따른 예시적인 무선 전력 송신 시스템(100)의 블록도이다. 도시된 바와 같이, 무선 전력 송신 시스템(100)은 라디오 주파수(RF) 송신기(101) 및 RF 수신기(102)를 포함한다.

[0016]

RF 송신기(101)는 RF 송신기 회로(103) 및 복수의 트랜지스터들 또는 스위치들(Q1-Q4)을 갖는 H-브리지(105)를 포함한다. 본 명세서에서 사용된 바와 같이, "H-브리지"라는 용어는 전압이 부하를 가로질러 어느 방향으로든 인가되게 할 수 있는 전자 회로를 지칭한다. 다양한 실시예들에서, 트랜지스터들(Q1-Q4)은 각각 소스 단자와 드레인 단자들 사이에 다이오드를 가질 수 있다. 예를 들어, Q1-Q4는 전력 금속-산화물-반도체 전계-효과 트랜지스터(metal-oxide-semiconductor field-effect transistor)(MOSFET)들 등으로서 구현될 수 있다.

[0017]

RF 송신기(101)는 또한 H-브리지(105)에 커플링된 1차 평활 캐패시턴스( $C_{primary}$ ) 및 1차 인덕터, 코일 또는 안테나( $L_{primary}$ )를 포함한다.  $L_{primary}$ 가 2차 인덕터, 코일 또는 안테나( $L_{secondary}$ )에 전자기적으로 커플링될 때, 그것은 전기 변압기(107)를 형성한다.

[0018]

RF 수신기(102)는 정류기 브리지(106)에 커플링된  $L_{secondary}$  및 2차 평활 캐패시턴스( $C_{secondary}$ )를 포함한다. 정류기 브리지(106)는 RF 수신기 회로(104)에 커플링된 복수의 트랜지스터들 또는 스위치들(Q4-Q8)(예를 들어, 전력 MOSFET들)을 포함한다. Q5와 Q8 사이의 노드는 출력 전압 레일( $V_{bridge\_out}$ )을 제공한다. 그리고,  $V_{bridge\_out}$ 은 컴퓨팅 디바이스의 배터리 또는 프로세서와 같은 전기 부하에 전력을 공급하기 위해 벽-부스트 컨버터, 전압 레귤레이터 등(도시 생략)에 제공된다.

[0019]

전기 변압기(107)는 1차 전류( $I_p$ )가 전자기장( $M$ )으로 변환될 수 있게 하고, 이는 그 후  $L_{primary}$ 에 의해 전력 캐리어 주파수를 갖는 전력 캐리어 신호로서 방출된다. 차례로,  $L_{secondary}$ 는 전자기 에너지의 일부를 수신하고, 이를 2차 전류( $I_s$ )로 변환한다.

[0020]

RF 송신기(101)와 RF 수신기(102) 사이의 전력 전송 효율은 송신된 에너지와 수신된 에너지 사이의 비에 의해 주어지며, 이는 전류  $I_s$ 와  $I_p$  사이의 비에 비례한다. 또한, 이 효율은  $I_p$  및  $I_s$ 를 발생시키기 위해 트랜지스터들(Q1-Q8)이 텐온(도전성) 및 텐오프(누설 효과들을 위한 비-도전성 저장)될 수 있는 속도 및 정밀도에 크게 의존한다.

[0021]

광범위하게, 트랜지스터들(Q1-Q8)은 그들 개개의 트랜지스터들의 게이트 단자들에 펄스 신호들을 인가하는 RF 송신기 회로(103) 및 RF 수신기 회로(104)에 의해 제어된다. 다양한 실시예들에서, RF 송신기 회로(103) 및 RF 수신기 회로(104)는 클록 신호의 미세 분할(fractional division)에 기초하여 선택된 타이밍 해상도 또는 입도(granularity)를 갖는 펄스-폭 변조(PWM) 펄스들을 생성할 수 있다. 예를 들어, 이러한 클록 신호는 동일한 주파수를 가질 수 있고, 이를 통해 전력이 무선으로 방사된다(전력 캐리어 주파수).

[0022]

예를 들어, 전력 캐리어 주파수가 6.78MHz와 같이 수 메가헤르츠를 초과하는 경우, 게이트 드라이버 펄스들(온/오프)에 대한 해상도 또는 입도는 1.1ns 범위에 있어야 한다. 이러한 요구 사항을 감안하면, 이러한 펄스들을 발생시키기 위한 시간 기준으로서 일반적으로 870MHz의 시스템 클록이 필요할 것이다. 그러나, 이러한 높은 클록 주파수에서 동작하려면 최종 솔루션의 구현 비용 및 복잡성이 현저히 증가할 것이다. 주된 비용의 추가 사항은 이러한 시스템을 구현하는 데 필요한 프로세스 및 기술이 동시에 고전압 및 고속 동작을 모두 지원해야 한다는 사실이다. 이것은 대개 허용 가능한 비용으로는 달성하기가 쉽지 않다. 또한, 결과적인 높은 전력 소비

는 종래의 구현들을 경쟁력 없게 만드는 또 다른 요인이다.

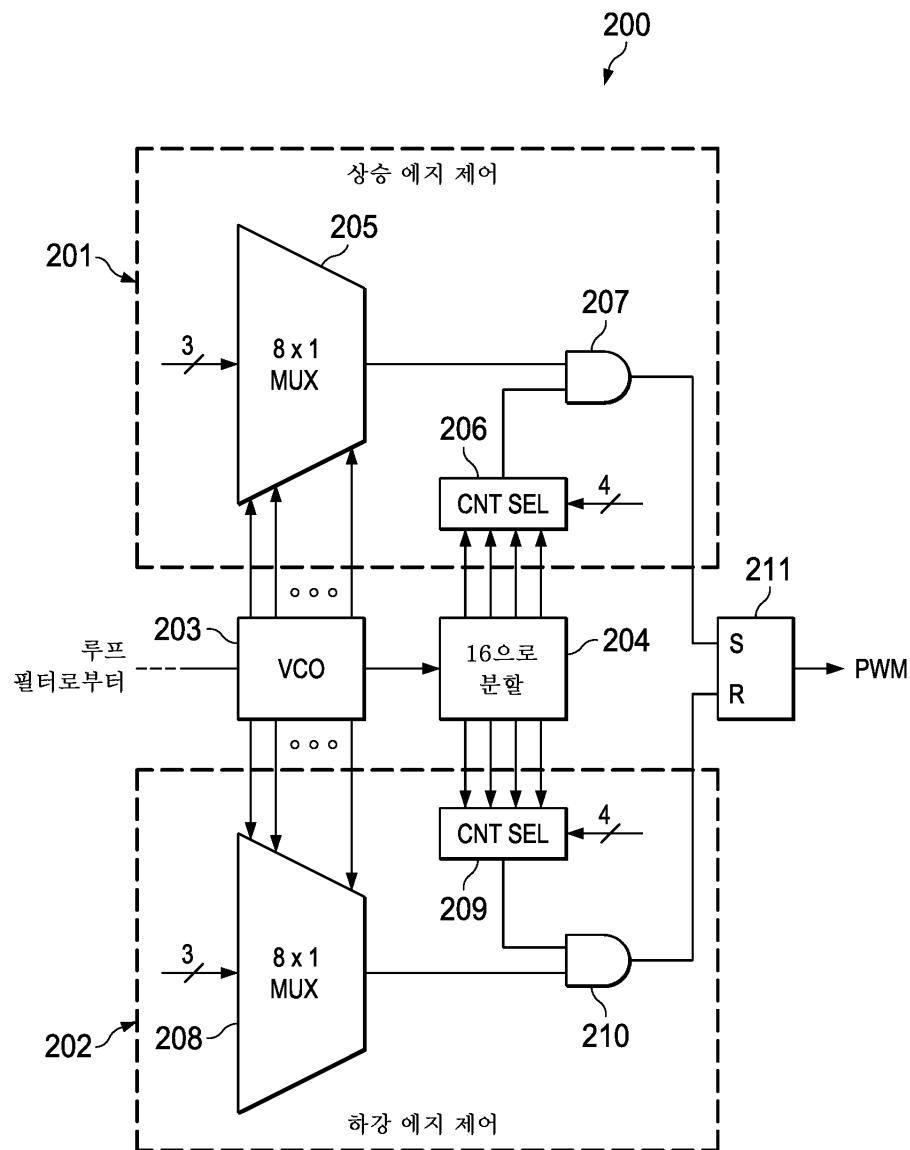

[0023] 따라서, 다양한 실시예들에서는, 도 2에 도시된 바와 같이, 클록 신호의 미세 분할이 하나 이상의 게이트 제어 회로에 커플링된 위상-고정 루프(PPL) 회로에 의해 달성될 수 있다. 특히, 도 2는 미세 주기 타이밍 해상도를 갖는 PLL-기반 PWM 펄스 발생기(200)의 블록도이다. 다양한 실시예들에서, 발생기(200)의 하나 이상의 인스턴스는 RF 송신기 회로(103) 및/또는 RF 수신기 회로(104)에 배치될 수 있다.

[0024] 도시된 바와 같이, 전압 제어 발진기(VCO)(203)는 PLL 필터(도시 생략)로부터 전력 캐리어 주파수(예를 들어, 6.78MHz로 실행)에 고정된 신호를 수신한다. 이에 응답하여, VCO(203)는 전력 캐리어 주파수보다  $n$ 배 큰 주파수를 갖는 클록을 생성한다(예를 들어,  $n=16$ 인 경우, VCO(203)의 출력 클록 주파수는 108.48MHz이다). 일부 구현들에서, VCO(203)는  $m$ -스테이지 완전 차동 링 발진기(예를 들어, 108.48MHz에서 실행되는 8-스테이지 발진기)일 수 있다.

[0025] VCO(203)의 출력은 분배기 회로(204)에 제공된다(이 경우, 클록 주기를 16개의 부분 또는 "빈"으로 분할한다). 상승 에지 제어 회로(201)는, VCO(203)의  $m$ 개의 위상 중 하나를 수신하고 (예를 들어, 제어 워드의 3-비트 LSB 부분에 기초하여) 하나의  $m$ 의 값을 선택하도록 구성되는 제1 멀티플렉서(205)를 포함한다. 카운터 선택 회로(209)는 (예를 들어, 제어 워드의 4-비트 MSB 부분에 기초하여) 분배기(204)로부터의  $n$ 개의 빈 중 하나를 선택한다. 멀티플렉서(205) 및 카운터 선택 회로(209)로부터의 출력들은 로직 게이트(207)에 의해 결합되어, 전력 캐리어 주파수의 주기를  $n \times m$ 의 꼽으로 나눈 값과 동일한 시간 해상도 또는 입도를 갖는 (및/또는 이산 시간 중분들로) PWM 펄스의 상승 시간을 선택한다.

[0026] 특히, 주파수가 6.78MHz인 경우, 전력 캐리어 신호의 주기는 ~147ns이지만,  $n = 16$ 이고  $m = 8$ 일 때, 선택된 상승 시간에 대한 타이밍 해상도는 1.15ns 정도이다.

[0027] 여전히 도 2를 참조하면, 하강 에지 제어 회로(202)는, 멀티플렉서(208)가 멀티플렉서(205)와 동일한 디바이스의 다른 인스턴스일 수 있고 카운터 선택 회로(209)는 카운터 선택 회로(206)와 동일한 디바이스의 다른 인스턴스일 수 있다는 점에서, 상승 에지 제어 회로(201)와 유사하다.

[0028] 로직 게이트(207)의 출력은 플립-플롭(211)의 설정 입력에 커플링되고, 로직 게이트(210)의 출력은 플립-플롭(211)의 재설정 입력에 커플링된다. 따라서, 플립-플롭(211)의 출력에서의 결과적인 PWM 펄스는 전술한 증가된 타이밍 입도 또는 해상도로 선택된 상승 및 하강 에지를 갖고 생성된다.

[0029] PLL-기반 PWM 펄스 발생기(200)는 (VCO(203)로부터의) 108.48MHz 시스템 클록 속도에서만 실행되면서 서브-나노초 PWM 펄스 충실도를 가질 수 있다. 미세 타이밍 해상도는 8-스테이지 링 발진기 내에서 중간 스테이지들을 탭핑함으로써 달성될 수 있다. 올-디지털 게이트-펄스 인코더는 링 발진기 클록 위상들을 PLL 피드백 분배기로부터 나오는 상태 정보와 결합하여, 충실도가 높고 매우 유연한 PWM 펄스 발생기를 생성한다.

[0030] 결과는 펄스 폭 및 위치 모두에 대해 1.15ns 해상도를 갖는 PWM 발생 방식이다. 따라서, (송신기 및 동기식 수신기/정류기 모두 상에서의) NexFet 디바이스들(Q1-Q8)의 게이트들을 구동하는 PWM 펄스들은 1/6.78MHz(~147ns) 기준 클록 사이클 내에서는 어디서든 시작하고 어디서든 중단될 수 있다.

[0031] 송신기 측에서, VCO(203)는 6.78MHz에서 실행되는 외부 기준 클록에 고정된 PLL 주파수 합성기의 일부이다. 수신기 측은 6.78MHz 수신 캐리어 신호가 PLL 기준으로서 기능하는 것을 제외하고는 동일한 회로를 모두 사용할 수 있다.

[0032] 일부 구현들에서, 회로는 임의의 시작 시간에서(예를 들어, 항상  $t = 150\text{ns}$ 에서) PWM 펄스의 상승 에지를 생성할 수 있고, 하강 에지는  $t = 150\text{ns} + 1.15\text{ns}$  내지  $t = 150\text{ns} + 1.15\text{ns} \times 124 = 292\text{ns}$ 의 임의의 이산 시간에서 선택될 수 있다. 펄스 각각의 펄스 폭은 하강 에지를 제어하는 디코더의 선택이 1 내지 124(7비트 해상도) 사이에서 변화함에 따라 제어될 수 있다.

[0033] 예를 들어, 8-스테이지 VCO 링 발진기로부터의 8개의 클록 위상은 16 피드백 분배기(16으로 분할) 텁과 결합되어, 송신기(1차) 및 수신기(2차) 측 모두에서 4개의 게이트/FET 드라이버 모두에 PWM 제어 펄스들을 발생시킬 수 있다. 따라서, 147ns(1/6.78MHz) 기준 클록 사이클은 128개의 슬롯으로 분할되며, 각각의 슬롯은 1.15ns의 폭을 갖는다. 마지막으로, 상승 에지 제어 출력은 SR FF를 설정하는 반면(PWM 펄스를 시작), 하강 에지 제어 출력은 SR FF를 재설정한다(PWM 펄스를 종료).

[0034] 프로세스 노드 선택의 속도 제한들에 따라, 125-128의 PWM 폭이 회로(200)로 커버 가능하지 않을 수 있지만, 이

것은 본 출원에 필요하지 않다. 그러나, 다른 실시예들에서는, 전체 PWM 폭 범위가 커버될 수 있다.

[0035] 도 3은 일부 실시예들에 따른 미세 주기 타이밍 해상도를 갖는 PLL-기반 PWM 발생기(200)의 구현 예(300)의 회로도이다. 여기서, 멀티플렉서 회로(301)(MUX1))는 카운터 선택기들(206 및/또는 209)을 구현할 수 있고, 멀티플렉서 회로(305)는 멀티플렉서들(206 및/또는 208)을 구현할 수 있다. 구현 예(300)는 또한 멀티플렉서(209)를 통해 멀티플렉서 회로(301)의 출력과 결합되기 전에 멀티플렉서(305)를 통해 선택된 위상들의 서브세트에서 동작하고 궁극적인 PWM 펄스의 상승 또는 하강 에지에 대한 특정 시간을 선택하기 위해 구성되는 타이밍 회로(308)를 포함한다.

[0036] 멀티플렉서 회로(301)는 7-비트 제어 워드 중 2-비트 부분(예를 들어, 비트 5 및 6)을 사용하여 분배기(204)의 동작으로부터 획득되는 16개의 빈(빈 0 내지 15로 지정됨)의 제1 서브세트를 선택하도록 구성되는 제1 세트의 로직 게이트들(302)을 포함한다. 여기서, 빈들의 서브세트들 각각은 4개의 굽은 서브디비전: SEL 카운터들 = 0  $\rightarrow$  3, 4  $\rightarrow$  7, 8  $\rightarrow$  11, 또는 12  $\rightarrow$  15를 갖는다.

[0037] 멀티플렉서 회로(301)는 또한 빈들의 서브세트 각각 내에서 7-비트 제어 워드 중 다른 2-비트 부분(예를 들어, 비트 3 및 4)을 사용하여 해당 빈들 중 특정 하나를 선택하도록 구성되는 제2 세트의 로직 게이트들(303) 또는 멀티플렉서들을 포함한다. 여기서, COUNTER 디코드 입력들은 다시 상이한 그룹들: COUNTER 디코드 = 0  $\rightarrow$  3, 4  $\rightarrow$  7, 8  $\rightarrow$  11 또는 12  $\rightarrow$  15로 분산되며, 각각의 COUNTER 디코드 입력은 빈들의 해당 서브세트 내에서 개개의 빈을 선택한다(더 세밀하거나 더 정밀한 선택). 마지막으로, 로직 게이트들(302 및 303)의 출력은 로직 게이트들(304)에 의해 결합되어, 선택된 m의 값을 출력함으로써 16개의 빈 중 특정 하나를 선택한다.

[0038] 멀티플렉서 회로(305)는 멀티플렉서(306) 및 멀티플렉서(307)를 포함한다. 멀티플렉서(306)는 VCO(203)의 위상 1, 2, 3 또는 4 중 하나를 선택하도록 동작 가능하고, 멀티플렉서(307)는 위상 5, 6, 7 또는 0 중 하나를 선택하도록 동작 가능하다. 멀티플렉서(306 또는 307) 중 어느 것이 위상을 선택할 때, n의 값이 설정되고, 멀티플렉서(309)는 증가된 해상도로 선택된 시간(예를 들어, 1.15ns)에서 상승 또는 하강 에지를 발생시킨다. 일부 경우들에서, 타이밍 회로(308)는 누설 효과들 등을 피하기 위해 멀티플렉서(307)의 출력에서 특정 위상 선택들의 타이밍을 조정하는 데 사용될 수 있다.

[0039] 따라서, 멀티플렉서 회로(301)는 16개의 CNTR 피드백 분배기 위상 중 어느 것이 사용될지를 선택한다. 모든 CNTR 위상들은 VCO의 동일한 텁, 즉, VCO PHASE 0에서 나온다. 또한, 멀티플렉서 회로(301)는 VCO 위상 1, 2, 3, 4를 게이트하며, CNTR이 위상 0에서 상태를 변경하는 것을 고려하면, 어떤 COUNTER 상태가 선택되든 간에, 이 지점이 직접 AND될 수 있다. 한편, 멀티플렉서 회로(305)는 2개의 출력을 갖는데, 제1 출력은 MUX된 위상 1, 2, 3, 4이며, 이는 직접 AND된다. 제2 출력은 MUX된 위상 5, 6, 7, 0이며, 이는 COUNTER 선택 상태(VCO 위상 0에 의해 클록됨)가 MUX된 위상 5, 6, 7, 0과 AND될 때 원치 않는 이중 에지를 생성하지 않기 위해 클록 재-타이밍 회로(308)를 통해 다른 루트를 취한다.

[0040] 일부 경우들에서, 클록 재-타이밍 회로(308)는 VCO 위상 4를 사용하여 출력을 리샘플링하고, 후속 VCO 위상 5, 6, 7, 0에 대해 출력을 재-타이밍 할 수 있다. 다시 말하자면, 이는, VCO 위상 5, 6, 7, 0이 선택되고 재-타이밍된 CNTR 상태와 함께 - 클록 재-타이밍 회로(308) 내에서 - AND될 때, 이중 클록이 발생하지 않도록 보장한다. 마지막으로, 멀티플렉서(309)는 (SELclk<2>에 기초하여) VCO 위상 뱅크(1, 2, 3, 4 또는 5, 6, 7, 0)가 최종 출력으로 가는 것을 선택한다.

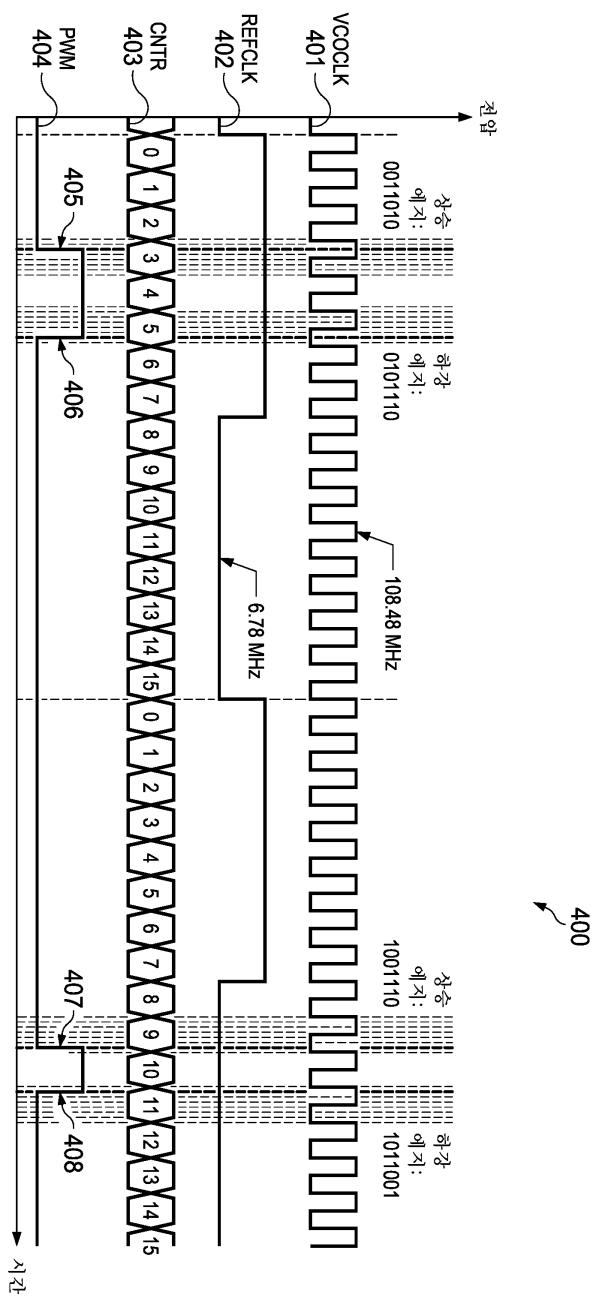

[0041] 도 4는 일부 실시예들에 따른 미세 주기 타이밍 해상도를 갖는 PLL-기반 PWM 발생기(200)의 동작을 예시하는 차트(400)를 도시한다. VCOCLK 신호(401)는 VCO(203)에 의해 출력된 클록 신호이며, 이는 REFCLK 신호(402)로 도시된 전력 캐리어 주파수의 16배의 주파수를 갖는다(예를 들어, 각각 108.48 및 6.78MHz). 카운터 선택기(들)(403)의 출력은 게이트 곡선(403)으로 도시된 빈 0-16이다.

[0042] 적어도 하나의 예에서, 제어 워드는 2개의 그룹으로 분할된 7-비트 워드이며, 이는 4개의 상위 비트 또는 MSB; 및 3개의 하위 비트 또는 LSB이다. 제1 그룹은 n(빈 번호 0  $\rightarrow$  15)에 대해 선택된 값을 인코딩하고, 제2 부분은 m(위상 0  $\rightarrow$  7)에 대해 선택된 값을 인코딩한다. 더욱이, 제1 그룹은 2개의 부분으로 추가로 세분화되는데, 제1의 2-비트 부분은 빈들의 서브세트를 나타내고, 제2의 2-비트 부분은 서브세트 내의 개개의 빈을 나타낸다.

[0043] 이 예에서, 제1 펄스는 이진 형태의 제어 워드 0011010에 의해 주어진 상승 에지(405)를 갖는다. 왼쪽에서 오른쪽으로 순차적으로, 4개의 MSB에서, "00"은 4개의 빈들의 서브세트 중 하나(예를 들어, 빈들 0-4 중 하나, 이 경우에는, 빈 0)를 나타내고, "01"은 해당 서브세트 내의 제3 빈(이 경우에는, 빈 3)의 위치를 정확히 나타낸다. 또한, 3개의 LSB에서, "010"은 빈-내 서브디비전을 나타낸다(m=2).

- [0044] 그 후, 펠스는 제어 워드 0101110에 의해 선택된 하강 에지(406)를 가지며, 이는 빈 5( $n=5$ )의 제6 빈-내 서브디비전( $m=6$ )에 정확하게 배치된다. 따라서, 본 명세서에 설명된 시스템들 및 방법들에 의해 제공된 입도를 사용하여, 상승 에지(405)가 정확하게 원하는 상승 시간에 배치될 수 있다.

- [0045] 나중 시간에, 서브시퀀스 펠스는 각각 제어 워드 1001110 및 1011001에 의해 선택된 상승 에지(407) 및 하강 에지(408)를 갖는다. 본 명세서에 설명된 시스템들 및 방법들을 사용하여, 상승 에지(405)는 빈 9( $n=9$ )의 제6 빈-내 서브디비전( $m=6$ )에 배치되고, 하강 에지(408)는 빈 11( $n=11$ )의 제1 빈-내 서브디비전( $m=1$ )에 배치된다.

- [0046] 본 명세서에 설명된 시스템들 및 방법들과 대조적으로, 전술한 문제들에 대한 종래의 솔루션들은 두 가지 범주 중 하나에 속한다. 첫째, 동기식 PWM 발생을 갖는 PLL/DLL 타입의 구현에 불가피하게 의존하는 디지털 PWM 발생기들이 존재한다. 이러한 구현들은 (~1.15ns 타이밍 해상도의 경우, 870MHz와 같이) 필요한 PWM 해상도에 비례하는 레이트로 실행되는 시스템 클록을 필요로 한다. 또한, 이러한 구현들은 높은 구현 비용, 높은 전력 소비 및 증가된 복잡성으로 인해 어려움을 겪는다.

- [0047] 둘째, 카운터, 디지털-아날로그 변환기(digital-to-analog converter)(DAC) 및 비교기 방식들에 의존하여 PWM 펠스들을 발생시키는 아날로그 구현들이 존재한다. 그러나, 이들 아날로그 기술들은 불량한 컴포넌트 매칭, 온도에 따른 드리프트, 프로세스에 따른 변동, 더 높은 전력, 잠재적 불안정성 및/또는 감소된 확장 가능성과 같이 아날로그 회로들과 통상적으로 연관된 제한들로 인해 어려움을 겪는다.

- [0048] 또한, (VCO가 1/1.15ns = 870Mhz에서 실행되는 경우와 같은) 풀-클록-기반 설계들과 비교하여, 본 명세서에 설명된 시스템들 및 방법들은 더 저렴하고/하거나 더 오래된 기술들이 외부 NexFet 디바이스들을 구동하는 데 필요한 고전압 능력을 채택할 수 있게 하는 것과 같은 다수의 특징들을 제공할 수 있다. 이러한 시스템들 및 방법들은 또한, 최대 동작 주파수가 풀-클록-기반 설계의 1/8에 불과하다는 점을 감안할 때, 훨씬 적은 전력을 사용한다(RMS 전력은 동작 주파수에 비례한다).

- [0049] 종래의 아날로그 PWM 발생 방식들과 비교하여, 제안된 PWM 발생기는 백그라운드 캘리브레이션 또는 트리밍(trimming)에 대한 필요 없이 우수한 성능을 제공한다. 올-디지털 구현은 부품 간 매칭을 개선시키고, 광범위한 동작 온도 범위들에 걸쳐 일관되고 반복 가능한 성능을 제공한다. 이들 시스템들 및 방법들은 유연하며, 임의의 바람직한 PWM 및/또는 기준 주파수로 확장 가능하다.

- [0050] 설명된 실시예들에서 수정들이 가능하며, 청구 범위 내에서 다른 실시예들이 가능하다.

도면

도면1

도면2

도면3

도면4