(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4722795号

(P4722795)

(45) 発行日 平成23年7月13日(2011.7.13)

(24) 登録日 平成23年4月15日(2011.4.15)

(51) Int.CI.

H01L 25/00 (2006.01)

F 1

H01L 25/00

B

請求項の数 11 (全 21 頁)

(21) 出願番号 特願2006-235727 (P2006-235727)

(22) 出願日 平成18年8月31日 (2006.8.31)

(65) 公開番号 特開2008-60342 (P2008-60342A)

(43) 公開日 平成20年3月13日 (2008.3.13)

審査請求日 平成20年11月25日 (2008.11.25)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(73) 特許権者 000204284

太陽誘電株式会社

東京都台東区上野6丁目16番20号

(74) 代理人 100086380

弁理士 吉田 稔

(74) 代理人 100103078

弁理士 田中 達也

(72) 発明者 ミイ シヤオユウ

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

最終頁に続く

(54) 【発明の名称】配線基板および電子部品モジュール

## (57) 【特許請求の範囲】

## 【請求項 1】

セラミック基板の表面上に直接形成された少なくとも1つのコイルインダクタを含む受動素子と、

前記受動素子と重複する領域に搭載されるデバイスチップと接続される第1のパッド部と、

前記第1のパッド部と電気的に接続され、前記セラミック基板の裏面に設けられた外部接続用の第2のパッド部とを有し、

前記コイルインダクタは隣り合うコイル導線が空隙を介して離隔していることを特徴とする配線基板。

10

## 【請求項 2】

前記受動素子は、平坦化処理されたセラミック上に直接形成されることを特徴とする請求項1に記載の配線基板。

## 【請求項 3】

前記セラミック基板は、少なくとも一つの内部配線層を有する多層セラミック基板であることを特徴とする請求項1または2に記載の配線基板。

## 【請求項 4】

前記第1のパッド部が前記受動素子の上位に位置することを特徴とする請求項1から3のいずれか一つに記載の配線基板。

## 【請求項 5】

20

セラミック基板の表面上に直接形成された少なくとも1つのコイルインダクタを含む受動素子と、

前記受動素子と重複する領域に搭載されるデバイスチップと接続される第1のパッド部と、

前記第1のパッド部と電気的に接続され、前記セラミック基板の裏面に設けられた外部接続用の第2のパッド部とを有し、

前記コイルインダクタは、空隙を介して互いに離隔する多段のスパイラルコイルであることを特徴とする配線基板。

**【請求項6】**

前記コイルインダクタは、それぞれの段のコイルで電流の方向が同一旋回方向であることを特徴とする請求項5に記載の配線基板。 10

**【請求項7】**

前記セラミック基板の表面上に直接形成された第1の電極と、前記第1の電極上に形成された誘電体層と、前記誘電体層上に形成された第2の電極とにより構成されるキャパシタを前記受動素子に含むことを特徴とする請求項1から6のいずれか一つに記載の配線基板。

**【請求項8】**

更に立体配線を備え、当該立体配線は、前記セラミック基板に接して延びる第1配線部と、前記セラミック基板から離隔して当該セラミック基板に沿って延び前記受動素子と接続する第2配線部と、前記セラミック基板の厚み方向に延び前記第1および第2の配線部を接続する第3配線部と、を含む請求項5から7のいずれか一つに記載の配線基板。 20

**【請求項9】**

請求項5または6に記載の多段のスパイラルコイルと請求項7に記載のキャパシタの両方が形成された配線基板が請求項8に記載の立体配線を備え、前記スパイラルコイルに接続された前記第2配線部と前記キャパシタに接続された前記第2配線部とが同じ高さであることを特徴とする配線基板。

**【請求項10】**

前記受動素子が直接形成されたセラミック基板の表面が、当該表面の表面粗さより小さい絶縁膜で覆われ、当該絶縁膜を介して前記受動素子が形成されていることを特徴とする請求項1から9のいずれか一つに記載の配線基板。 30

**【請求項11】**

セラミック基板の表面上に直接形成された少なくとも1つのコイルインダクタを含む受動素子と、

前記受動素子と重複する領域に搭載されるデバイスチップと接続される第1のパッド部と、

前記第1のパッド部と電気的に接続され、前記セラミック基板の裏面に設けられた外部接続用の第2のパッド部とを有する配線基板において、

前記第1のパッド部に前記デバイスチップが搭載されており、

前記受動素子と前記デバイスチップとが同一空間に封止されることを特徴とする電子部品モジュール。 40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、例えば複数のデバイスチップおよび複数の受動部品を構成要素として含む、いわゆる電子部品モジュール、そのための配線基板、並びに、電子部品モジュール製造方法に関する。

**【背景技術】**

**【0002】**

情報社会を支える大型コンピュータ、パーソナルコンピュータ、および移動通信端末などの情報処理装置においては、処理速度の高速化、並びに、装置の小型化、多機能化、お 50

より小消費電力化などが進められている。このような性能向上は、主に、装置に組み込まれる多数の半導体デバイスの高集積化や高性能化（高速化、高機能化等）により図られるところ、半導体デバイスの高集積化や高性能化を図るための手段として、マルチチップモジュール（MCM）技術が知られている。MCM技術については、例えば下記の特許文献1, 2に記載されている。

【0003】

【特許文献1】特開平10-294421号公報

【特許文献2】特開2000-36657号公報

【0004】

MCMは、一般に、モジュール全体のベース基板たる配線基板と、ベアチップの状態で当該配線基板に実装された複数のデバイスチップと、複数の受動部品（キャパシタ、インダクタ、抵抗等）とを有する。また、MCMとしては、MCM-L（MCM-Laminated）、MCM-C（MCM-Ceramic）、およびMCM-D（MCM-Deposited）が知られている。これら3種類は、ベース基板たる配線基板の構成の違いに基づいて分類されたものである。

【0005】

MCM-Lは、樹脂材料のラミネート成形により得られた樹脂基板を用いて作製された配線基板を、モジュール全体のベース基板として有する。この配線基板は、樹脂基板の表面や内部に配線が作り込まれた構造を有し、このような配線基板に対してデバイスチップがベアチップの状態で実装される。受動部品は、一般に、表面実装部品として個別に製造されたうえで配線基板に実装される。受動部品は、配線基板内に設けられる場合もある。

【0006】

MCM-Lにおいて、表面実装部品として個別に製造された受動部品が配線基板に実装される構成を採用すると、当該モジュールについて充分に小型化することができない場合がある。表面実装型の受動部品は、所定の基板上ないし基板内に個別に作り込まれてチップ化されたものであるために比較的大きいからである。

【0007】

また、MCM-Lにおいて、受動部品が配線基板内に設けられる構成を採用すると、当該モジュールについて充分な性能が得られない場合がある。配線基板内の受動素子や配線の間、および、配線基板内の各キャパシタの一対の電極間には、配線基板を構成する樹脂材料（誘電体材料）が介在するところ、配線基板内のキャパシタにとっては、大きな静電容量を得るために当該樹脂材料の誘電率は大きい方が好ましいが、配線基板内における他の受動素子（特にインダクタ）と配線にとっては、受動素子や配線の間に生じ得る寄生容量を抑制するために当該樹脂材料の誘電率は小さい方が好ましい。このように、高性能化を図るうえで、矛盾する二つの特性が配線基板構成樹脂材料に要求される。加えて、配線基板内のインダクタにおいては、寄生容量の発生はQ値の低下を招く。したがって、受動部品が配線基板内に設けられた構成を有するMCM-Lについては、充分な性能が得られない場合があるのである。

【0008】

MCM-Cは、セラミック基板を用いて製造された配線基板を、モジュール全体のベース基板として有する。MCM-C用の配線基板としては、単層のセラミック基板上に厚膜配線が形成されたものや、表面に配線パターンが印刷された複数のセラミック基板が同時焼成により一体化されたものがあり、このような配線基板に対してデバイスチップがベアチップの状態で実装される。受動部品は、一般に、表面実装部品として個別に製造されたうえで配線基板に実装される。受動部品は、配線基板内に作り込まれる場合もある。

【0009】

MCM-Cにおいて、表面実装部品として個別に製造された受動部品が配線基板に実装される構成を採用すると、当該モジュールについて充分に小型化することができない場合がある。表面実装型の受動部品は、上述のように、所定の基板上ないし基板内に個別に作り込まれてチップ化されたものであり、比較的大きいからである。

【0010】

10

20

30

40

50

また、MCM-Cにおいて、受動部品が配線基板内に作り込まれる構成を採用すると、当該モジュールについて充分な性能が得られない場合がある。配線基板内の受動素子や配線の間、および、配線基板内の各キャパシタの一対の電極間には、配線基板を構成するセラミック材料（誘電体材料）が介在するところ、配線基板内のキャパシタにとっては、大きな静電容量を得るために当該セラミック材料の誘電率は大きい方が好ましいが、配線基板内における他の受動素子（特にインダクタ）と配線にとっては、受動素子や配線の間に生じ得る寄生容量を抑制するために当該セラミック材料の誘電率は小さい方が好ましい。このように、高性能化を図るうえで、矛盾する二つの特性が配線基板構成セラミック材料に要求される。加えて、配線基板内のインダクタにおいては、寄生容量の発生はQ値の低下を招く。したがって、受動部品が配線基板内に作り込まれた構成を有するMCM-Cについては、充分な性能が得られない場合があるのである。10

#### 【0011】

MCM-Dは、セラミックや、シリコン、ガラスなどよりなる基材の上に薄膜積層技術により形成された多層配線構造を有する配線基板を、モジュール全体のベース基板として有する。多層配線構造は、一般に、複数の薄膜配線層、配線層間ごとの絶縁層、および配線層間を接続するピアを有する。このような多層配線構造を有する配線基板に対してデバイスチップがペアチップの状態で実装される。受動部品は、表面実装部品として個別に製造されたうえで配線基板に実装されるか、或は、多層配線構造内に作り込まれる。

#### 【0012】

MCM-Dにおいて、表面実装部品として個別に製造された受動部品が配線基板に実装される構成を採用すると、上述のように表面実装部品が比較的大きいため、当該モジュールについて充分に小型化することができない場合がある。20

#### 【0013】

また、MCM-Dにおいて、受動部品が多層配線構造内に作り込まれる構成を採用すると、当該モジュールについて充分な性能が得られない場合がある。多層配線構造内の受動素子や配線の間、および、多層配線構造内の各キャパシタの一対の電極間には、絶縁層を構成する絶縁材料（誘電体材料）が介在するところ、多層配線構造内のキャパシタにとっては、大きな静電容量を得るために当該絶縁材料の誘電率は大きい方が好ましいが、多層配線構造内における他の受動素子（特にインダクタ）と配線にとっては、受動素子や配線の間に生じ得る寄生容量を抑制するために当該絶縁材料の誘電率は小さい方が好ましい。このように、高性能化を図るうえで、矛盾する二つの特性が多層配線構造内の絶縁材料に要求される。加えて、配線基板内のインダクタにおいては、寄生容量の発生はQ値の低下を招く。したがって、受動部品が多層配線構造内に作り込まれた構成を有するMCM-Dについては、充分な性能が得られない場合があるのである。30

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0014】

本発明は、以上のような事情の下で考え出されたものであり、小型化および高性能化に適したMCMないし電子部品モジュール、およびその製造方法を提供することを、目的とする。40

#### 【0015】

本発明の第1の側面によると電子部品モジュールが提供される。この電子部品モジュールは、配線基板と、配線基板上にて形成された複数の受動素子を含む受動素子群と、配線基板に実装された少なくとも一つのデバイスチップとを備える。配線基板上にて形成された複数の受動素子とは、表面実装部品として個別に製造されたうえで各々が配線基板に対して搭載された複数の受動素子ではなく、例えばマイクロマシニング技術を用いて、配線基板上に各受動素子の各部が順次形成されることにより、基板表面に直接的に形成された複数の受動素子である。また、本電子部品モジュールは、目的とする機能に応じて、インダクタや、キャパシタ、抵抗を受動素子として含んで設計される。

#### 【0016】

50

20

30

40

50

本電子部品モジュールの各受動素子は、配線基板上にて形成されたものあり、比較的大きな表面実装部品の形態で配線基板に対して搭載されたものではない。そのため、本電子部品モジュールは、各受動素子を基板表面の小領域内に設けるのに適し、従って、これら受動素子を含んで所定の受動回路を構成することのできる受動素子群を、基板表面の小領域内に設けるのに適する。このような電子部品モジュールは、モジュール自体の小型化に適する。

#### 【0017】

本電子部品モジュールの各受動素子は、樹脂材料やセラミック材料など誘電体材料内に埋め込まれたものではない。受動素子と受動素子の間や受動素子と配線（例えば配線基板表面に設けられている配線）の間には誘電体材料は介在しない。そのため、本電子部品モジュールでは、受動素子と受動素子の間や受動素子と配線の間に生じ得る寄生容量を抑制することができる。このような寄生容量の抑制は、各受動素子の高性能化の観点から好ましく、複数の受動素子がインダクタを含む場合には、当該インダクタのQ値向上の観点から特に好ましい。このように、本電子部品モジュールは高性能化に適する。また、本電子部品モジュールでは、複数の受動部品がキャパシタを含む場合、キャパシタにおける一対の電極間に設けるべき誘電体層について、誘電率の高い材料を自由度高く選択することが可能である。このような点においても、本電子部品モジュールは高性能化に適する。

10

#### 【0018】

このように、本発明の第1の側面に係る電子部品モジュールは、小型化に適するとともに、高性能化に適するのである。このような電子部品モジュールは、情報処理装置など電子装置全体の小型化および高性能化に資する。

20

#### 【0019】

本電子部品モジュールにおける複数の受動素子がインダクタを含む場合、当該インダクタは、好ましくは、配線基板上にて形成された多段コイルインダクタである。好ましくは、当該多段コイルインダクタは、多段配置された複数のコイルを有し、且つ、隣り合うコイル導線が空隙を介して離隔している。より好ましくは、多段コイルインダクタは、空隙を介して互いに離隔する複数のスパイラルコイルを有する。このような多段コイルインダクタは、インダクタについて大きなインダクタンスを得るうえで好適であり、且つ、インダクタについて高いQ値を得るうえで好適である。

30

#### 【0020】

好ましくは、本電子部品モジュールは更に立体配線を備え、当該立体配線は、配線基板に接して延びる第1配線部と、配線基板から離隔して当該配線基板に沿って延びる第2配線部と、配線基板の厚み方向に延びる第3配線部とを含む。これら3種類の配線部（第1～第3配線部）の適宜の組み合せにより、受動素子と受動素子の間や、受動素子とデバイスチップの間を、自由度高く接続することが可能である。すなわち、本電子部品モジュールでは、配線基板上の各コンポーネント（受動素子、デバイスチップ）間の配線設計における自由度が高いのである。配線基板上の配線設計の自由度が高いことは、各コンポーネント間の配線長の最短化を実現するうえで好適であり、配線どうしの交差および配線と受動素子の交差を回避するうえで好適である。各コンポーネント間の配線長の最短化は、配線の高周波抵抗を抑制するのに好ましく、また、配線どうしの交差および配線とコイル導線の交差の回避は、当該交差構造に起因して電磁場相互誘導により配線やインダクタに誘導電流が生じてしまうのを抑制するのに、資する。これら、高周波抵抗の抑制および誘導電流の抑制は、各コンポーネント間を接続するための配線における損失を抑制するのに適している。そして、配線損失の抑制は、本電子部品モジュール全体において高いQ値を実現して高性能化を達成するのに好適である。

40

#### 【0021】

好ましい実施の形態においては、デバイスチップは受動素子群の上位に位置する。本電子部品モジュールにおいては、配線基板上の所定領域内に複数の受動素子を受動素子群として高密度に配置することが可能であるところ、そのような受動素子群の上位にデバイスチップを配置することにより、配線基板上における受動素子群形成領域とデバイスチップ

50

形成領域とを重複させることができる。したがって、デバイスチップが受動素子群の上位に位置する構成は、電子部品モジュールの小型化に資する。

【0022】

他の好ましい実施の形態においては、配線基板は凹部を有し、デバイスチップは当該凹部に位置する。他の好ましい実施の形態においては、デバイスチップは配線基板の内部に位置する。これらの構成も、電子部品モジュールの小型化に資する。

【0023】

好ましくは、少なくとも一つのデバイスチップは高周波フィルタを含む。高周波フィルタは、好ましくは、SAWフィルタ、FBARフィルタ、およびマイクロ機械振動型フィルタからなる群より選択される單一または複数のフィルタにより構成される。また、好ましくは、少なくとも一つのデバイスチップは半導体デバイスを含む。半導体デバイスは、信号を増幅するための増幅器を有してもよい。

【0024】

好ましくは、配線基板は、少なくとも一つの内部配線層を有する多層配線基板である。このような構成は、デバイスチップおよび受動素子を配線基板上において高密度に配置するうえで好ましい。好ましい実施の形態では、多層配線基板は、積層された複数のセラミック層を含む多層セラミック配線基板である。他の好ましい実施の形態では、多層配線基板は、積層された複数の樹脂層を含む。多層配線基板たる配線基板は、好ましくは、内部配線層に接続するビアを有する。このビアは、例えば内部配線層間を電気的に接続する。

【0025】

配線基板は、当該配線基板を貫通するビアを有してもよい。この場合、配線基板については、内部配線層を有しない構成を採用してもよい。

【0026】

本電子部品モジュールは、更に封止用キャップを備えてもよい。本電子部品モジュールは、必要に応じて、配線基板上のデバイスチップおよび受動素子群などを封止するための封止用キャップを備える。

【0027】

本発明の第2の側面によると、配線基板と、配線基板上に設けられた複数の受動素子を含む受動素子群と、配線基板に実装された少なくとも一つのデバイスチップと、を備える電子部品モジュールを製造するための方法が提供される。この方法は、複数の電子部品モジュール形成区画を有する配線基板ウエハを作製する工程と、電子部品モジュール形成区画の各々において配線基板ウエハ上にて複数の受動素子を形成する工程と、電子部品モジュール形成区画の各々において配線基板ウエハにデバイスチップを搭載する工程と、配線基板ウエハを分割する工程とを含む。

【0028】

本方法によると、本発明の第1の側面に係る電子部品モジュールを適切に製造することができる。また、従来のシリコンウエハなどに代えて配線基板ウエハが用いられる本方法は、本発明の第1の側面に係る電子部品モジュールを大量生産するのに適する。

【0029】

好ましくは、電子部品モジュール形成区画の各々において配線基板ウエハに封止キャップを搭載する工程を更に含む。このようにウエハレベルで封止工程を行うことは、電子部品モジュールの製造効率向上の観点から好ましい。

【発明を実施するための最良の形態】

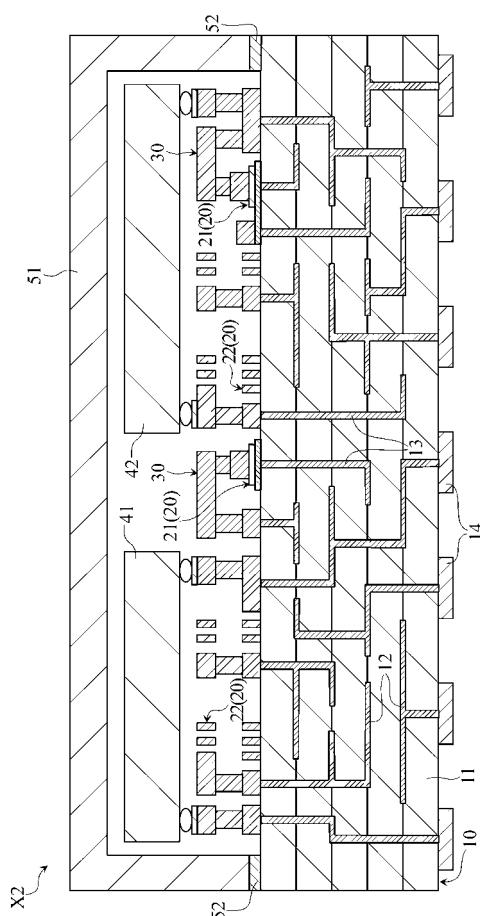

【0030】

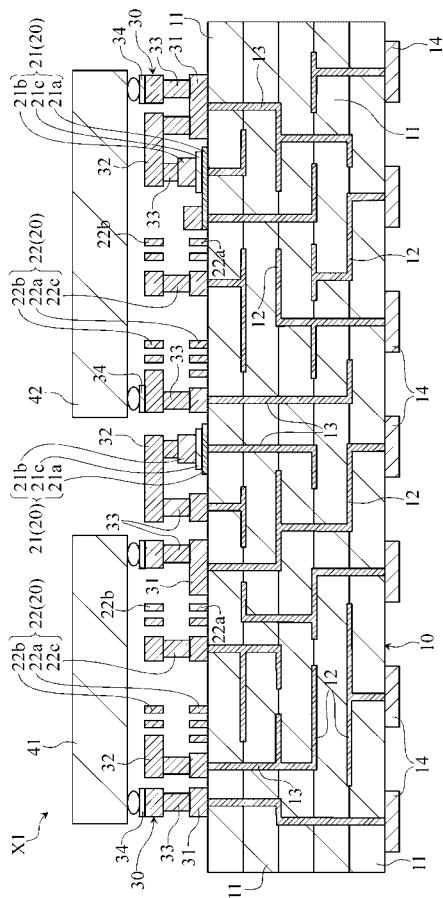

図1は、本発明の第1の実施形態に係る電子部品モジュールX1の断面図である。電子部品モジュールX1は、配線基板10と、受動素子群20と、立体配線30と、デバイスチップ41, 42とを備える。

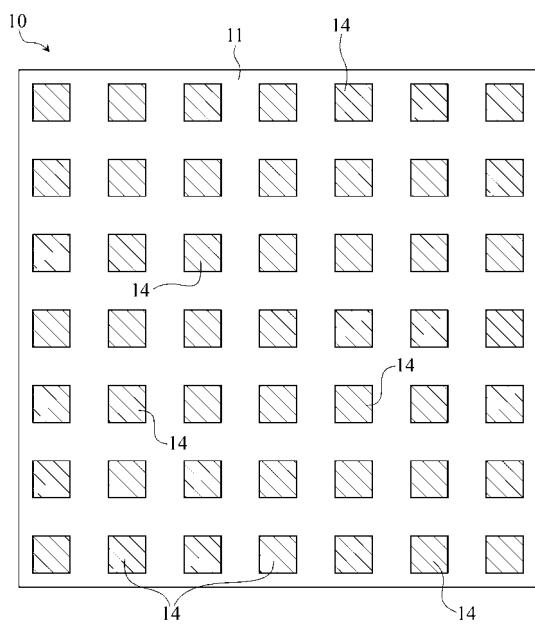

【0031】

配線基板10は、いわゆる多層セラミック配線基板であり、絶縁層11と、配線パターン12と、ビア13と、外部接続用のパッド部14とを有する。各絶縁層11は、例えば

10

20

30

40

50

$\text{Al}_2\text{O}_3$ よりなるセラミック層である。各配線パターン12は、例えばCu、Ag、W、またはMoよりなり、所定のパターン形状を有して絶縁層11間に埋設されている。各ビア13は、例えばCu、Ag、W、またはMoよりなり、絶縁層11を貫通して配線パターン12に接続する。一部のビア13は、配線パターン12間を接続する。各パッド部14は、例えばCuよりなり、配線基板10における一方の面上に設けられている。各パッド部14は、Ni母体およびその表面を被覆するAu膜により構成されてもよい。複数のパッド部14は、配線基板10における、受動素子群20が設けられている側とは反対の側にて、例えば図2に示すようにアレイ状に配されている。本発明における配線基板としては、このような多層セラミック配線基板たる配線基板10に代えて多層プリント配線板を採用してもよい。多層プリント配線板を採用する場合、絶縁層は、ガラスクロスやカーボンファイバなどの基材とこれを包みする樹脂材料とからなり、このような絶縁層間に配線パターンが埋設される。

#### 【0032】

受動素子群20は、配線基板10上にて形成された複数のキャパシタ21および複数のインダクタ22を含む。各キャパシタ21は、図1に示すように、第1電極21aと、第2電極21bと、これらの間の誘電体層21cとからなる積層構造を有する。第1電極21aは、配線基板10上に設けられ、第2電極21bは、配線基板10から離隔して配線基板10に沿って設けられている。第1電極21aは、例えば、所定の多層構造を有し、当該多層構造の各層には、Cu、Au、Ag、およびAlから選択される金属が含まれる。第1電極21aの厚さは例えば0.2~3μmである。第2電極21bは、例えばCu、Au、Ag、またはAlよりなる。第2電極21bの厚さは例えば0.2~15μmである。誘電体層21cは、例えば酸化シリコン、窒化シリコン、酸化アルミニウム、酸化タンタル、または酸化チタンよりなる。誘電体層21cの厚さは例えば0.1~1μmである。

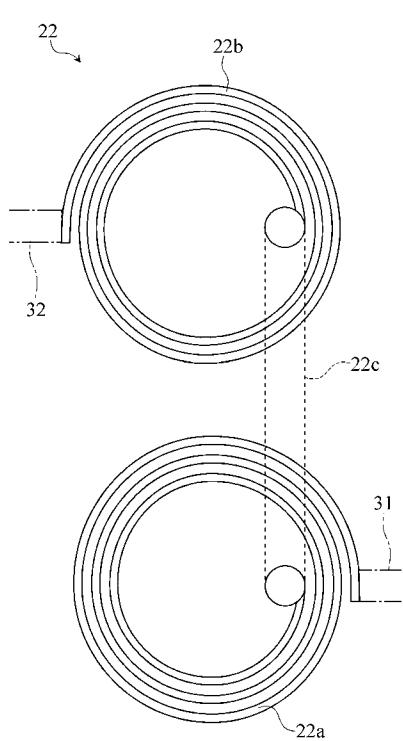

#### 【0033】

各インダクタ22は、多段コイルインダクタであり、各々、二段に配されたスパイラルコイル22a, 22bと、これらを直列に接続する連絡部22cとからなる。スパイラルコイル22aは、配線基板10表面にパターン形成されたものであり、スパイラルコイル22bは、配線基板10から離隔している。図3は、多段コイルインダクタたるインダクタ22の分解平面図である。インダクタ22の各々において、スパイラルコイル22a, 22bは、各々を流れる電流の方向が同一旋回方向となるような巻形状を有する。また、インダクタ22の各々においては、隣り合うコイル導線は空隙を介して離隔している。スパイラルコイル22a, 22bの厚さは好ましくは3μm以上であり、スパイラルコイル22a, 22b間の離隔距離は例えば1~100μmである。このようなインダクタ22は、例えばCu、Au、Ag、またはAlよりなる。

#### 【0034】

受動素子群20は、配線基板10上にて形成された受動素子として、これらキャパシタ21およびインダクタ22に加え、所定の高抵抗材料からなる抵抗を含んでもよい。

#### 【0035】

立体配線30は、配線基板10上の各コンポーネント(キャパシタ21, インダクタ22, デバイスチップ41, 42)間および各コンポーネントと配線基板10の間を電気的に接続するための配線であり、配線基板10に接して延びる部位を有する第1配線部31と、配線基板10から離隔して配線基板10に沿って延びる第2配線部32と、配線基板10の厚さ方向に延びる第3配線部33と、パッド部34とからなる。立体配線30は、例えばCu、Au、Ag、またはAlよりなる。また、第1配線部31および第2配線部32の厚さは好ましくは3μm以上である。

#### 【0036】

デバイスチップ41, 42の各々は、ペアチップの状態で配線基板10に実装されたものであり、そのバンプ電極と立体配線30のパッド部34とが接合されている。本実施形態では、デバイスチップ41, 42は受動素子群20の上位に位置する。すなわち、配線

10

20

30

40

50

基板 10 上における受動素子群 20 の形成領域と、デバイスチップ 41, 42 の各々の形成領域とは、重複している。また、デバイスチップ 41, 42 は、電子部品モジュール X 1 の設計に応じた所定の機能を有する。例えば、デバイスチップ 41, 42 は高周波フィルタである。当該高周波フィルタは、例えば、SAW フィルタ、FBAR フィルタ、およびマイクロ機械振動型フィルタからなる群より選択される单一または複数のフィルタにより構成される。デバイスチップ 41, 42 は半導体デバイスであってもよい。当該半導体デバイスは、例えば、信号を増幅するための増幅器を有する。

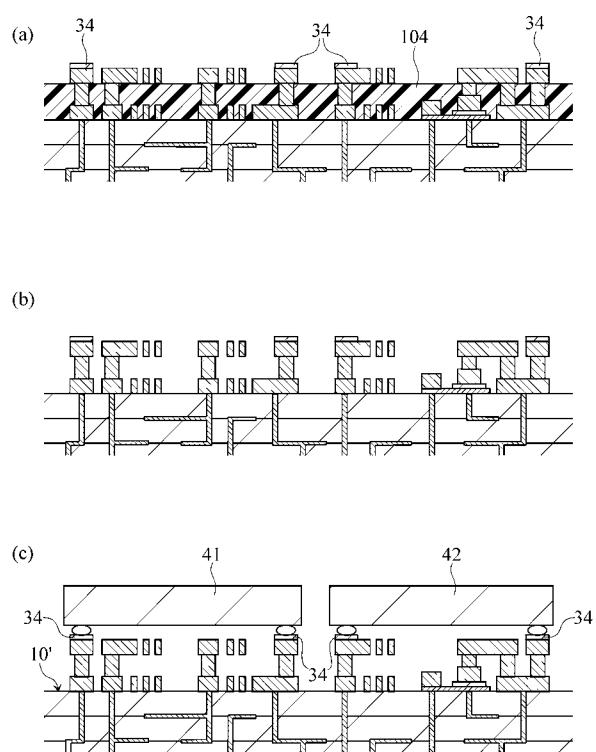

#### 【 0 0 3 7 】

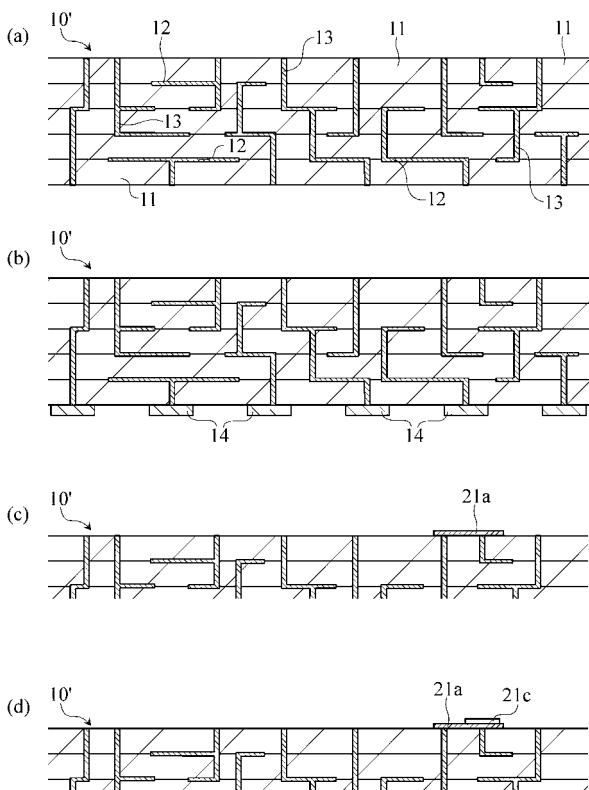

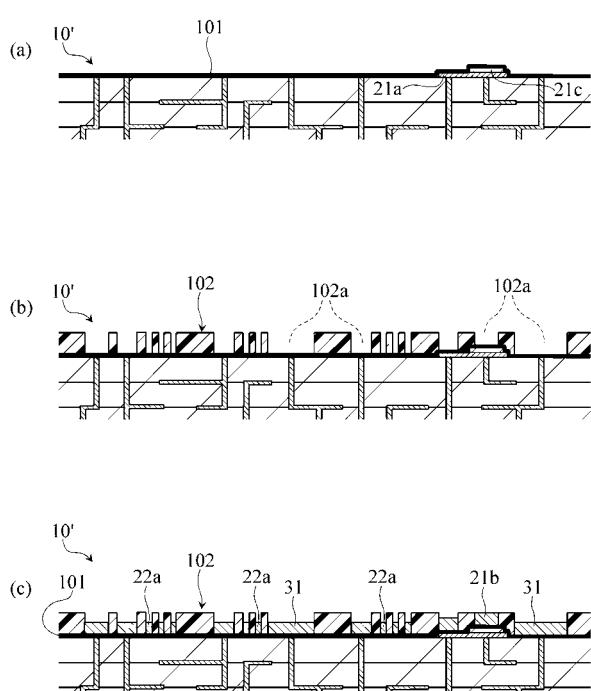

図 4 から図 9 は、電子部品モジュール X 1 の製造方法の一例を表す。図 4 から図 9 においては、電子部品モジュール X 1 の製造過程を断面の変化で表す。当該断面は、加工が施されるウエハにおける单一の電子部品モジュール形成区画に含まれる複数の所定箇所の断面を、モデル化して連続断面としたものである。

#### 【 0 0 3 8 】

電子部品モジュール X 1 の製造においては、まず、図 4 (a) に示すような配線基板ウエハ 10' を作製する。配線基板ウエハ 10' は、絶縁層 11、配線パターン 12、およびビア 13 を含む多層配線構造を有するウエハであり、複数の電子部品モジュール形成区画を有する。また、電子部品モジュール X 1 は、例えば、一辺が 1 ~ 10 mm の矩形形状を有し、500 ~ 1000  $\mu$ m の厚さを有する。配線基板ウエハ 10' において上述の受動素子群 20 が形成される側の表面粗さ Rz は 0.2  $\mu$ m 以下である。

#### 【 0 0 3 9 】

配線基板ウエハ 10' の作製においては、まず、グリーンシートたる複数のセラミック基板の各々において、ビア用の開口部を形成した後、当該ビア用開口部に導電ペーストを充填するとともに、セラミック基板表面に導電ペーストで配線パターンを印刷する。このような工程を経て用意された所定枚数のセラミック基板を積層し、当該積層体を加熱下にて厚み方向にプレスする。その後、所定の加熱処理により、当該積層体を一体焼成し、プリ配線基板ウエハ 10'' を得る（一体焼成を経ることにより、配線パターン 12 およびビア 13 が形成される）。

#### 【 0 0 4 0 】

配線基板ウエハ 10' の作製においては、次に、プリ配線基板ウエハ 10'' の両面を研磨処理する。研磨処理の手法は、例えば、所定の研磨剤（薬液）を使用して行う機械的研磨を採用することができる。この研磨処理により、プリ配線基板ウエハ 10'' の反り及びうねりを低減する。本研磨処理では、反りについては好ましくは 40  $\mu$ m 以下まで低減し、うねりについては充分になくなるまで低減する。

#### 【 0 0 4 1 】

配線基板ウエハ 10' の作製においては、次に、プリ配線基板ウエハ 10'' において上述の受動素子群 20 が形成される側の面を平滑化処理する。上述のようにして得られたプリ配線基板ウエハ 10'' の表面には凹凸（構成セラミック粒子のサイズや研磨剤による研磨作用に起因して生ずると考えられる）が存在するところ、セラミック材質の選定および研磨方法を最適化しても、プリ配線基板ウエハ 10'' 表面の表面粗さ Rz は 5  $\mu$ m を大きくは下回らない。このような凹凸を有する表面には、上述の受動素子群 20 に含まれる小サイズの各受動素子を適切に形成することはできない。例えば、表面粗さ Rz 5  $\mu$ m 程度の凹凸を有する表面にキャパシタ 21 を形成することを想定すると、上述のように相当程度に薄い第 1 電極 21a および誘電体層 21c について、当該凹凸表面においては適切な平坦性を確保しつつ形成することができず、従って、誘電体層 21c について均等な厚さを実現することができず、その結果、キャパシタ 21 について充分な耐圧特性を確保することが阻まれる。このような問題が生ずるのを回避するため、配線基板ウエハ 10' の作製においては、上述の研磨処理の後に所定の平滑化処理が必要なのである。

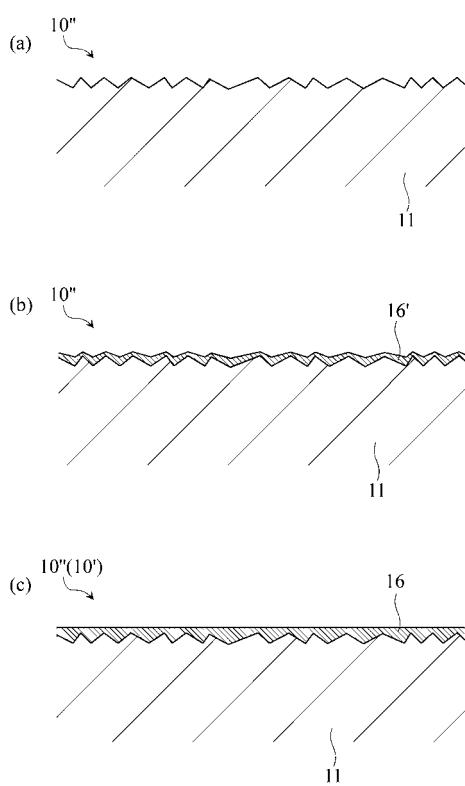

#### 【 0 0 4 2 】

図 10 は平滑化処理を表す。図 10 では、平滑化処理が施されるプリ配線基板ウエハ 10'' の表面付近の部分拡大断面を示す。本平滑化処理では、上述の研磨処理を経たプリ

10

20

30

40

50

配線基板ウエハ 10' ないし表面の絶縁層 11 における図 10 (a) に示すような凹凸表面に、まず、図 10 (b) に示すように、薄い絶縁膜 16' を形成する。絶縁膜 16' の形成においては、プリ配線基板ウエハ 10' の表面に絶縁コーティング液を薄く塗布して焼成する。絶縁コーティング液としては、例えば SOG (Spin-on-Glass) を用いることができる。塗布される絶縁コーティング液の厚さは例えば 1  $\mu\text{m}$  以下である。このようして薄い絶縁膜 16' を形成することにより、プリ配線基板ウエハ 10' の表面における凹凸の程度を低減することができる。この後、このような絶縁膜形成工程を所定回数繰り返し、図 10 (c) に示すように、プリ配線基板ウエハ 10' のセラミック素地表面の凸部を、絶縁膜 16' を重ねて形成された絶縁膜 16 に埋没させる (図 10 以外の図面では絶縁膜 16 を表さない)。図 10 に示すこの方法により、プリ配線基板ウエハ 10' において受動素子群 20 が形成される側の面全体の表面粗さ  $R_z$  を 0.02  $\mu\text{m}$  以下に低減することができる。上述の研磨処理の後にこのような平滑化処理を行うことにより、配線基板ウエハ 10' を得ることができる。

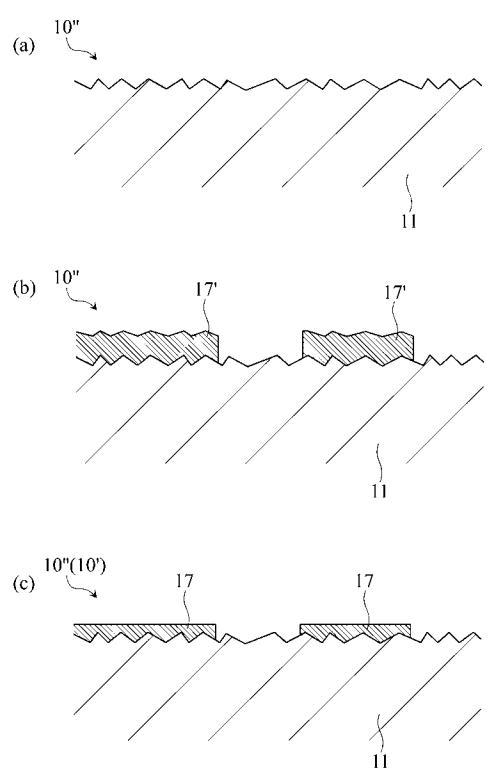

#### 【0043】

図 11 は他の平滑化処理を表す。図 11 では、平坦化が施されるプリ配線基板ウエハ 10' の表面付近の部分拡大断面を示す。本平坦化処理では、上述の研磨処理を経たプリ配線基板ウエハ 10' ないし表面の絶縁層 11 における図 11 (a) に示すような凹凸表面に、まず、図 11 (b) に示すように厚い金属膜 17' を形成する。金属膜 17' は、上述の受動素子群 20 に含まれる各受動素子を形成すべき箇所にて、例えば無電解めっき法や電気めっき法により形成される。金属膜 17' の厚さは例えば 20  $\mu\text{m}$  である。このようにして、プリ配線基板ウエハ 10' のセラミック素地表面の凸部を金属膜 17' に埋没させる。次に、金属膜 17' に研磨処理を施して、図 11 (c) に示すように、表面が平坦化された金属膜 17 を形成する (図 11 以外の図面では金属膜 17 を表さない)。研磨処理の手法は、例えば、所定の研磨剤 (薬液) を使用して行う機械的研磨を採用することができる。図 11 に示すこの方法によると、プリ配線基板ウエハ 10' の表面において各受動素子を形成すべき箇所の表面粗さ  $R_z$  を 0.02  $\mu\text{m}$  以下に低減して配線基板ウエハ 10' を得ることができる。

#### 【0044】

電子部品モジュール X 1 の製造においては、次に、上述のようにして作製した配線基板ウエハ 10' の片面に、図 4 (b) に示すようにパッド部 14 を形成する。例えば、スパッタリング法により所定の金属材料を配線基板ウエハ 10' 上に成膜した後、所定のウェットエッティングまたはドライエッティングにより当該金属膜をパターニングすることによって、パッド部 14 を形成することができる。或は、パッド部 14 の形成においては、無電解めっき法や電気めっき法を採用してもよい。

#### 【0045】

次に、図 4 (c) に示すように、キャパシタ 21 の第 1 電極 21a を配線基板ウエハ 10' 上に形成する。例えば、スパッタリング法により所定の金属材料を配線基板ウエハ 10' 上に成膜した後、所定のウェットエッティングまたはドライエッティングにより当該金属膜をパターニングすることによって、第 1 電極 21a を形成することができる。

#### 【0046】

次に、図 4 (d) に示すように、キャパシタ 21 の誘電体層 21c を第 1 電極 21a 上に形成する。例えば、スパッタリング法により所定の誘電体材料を少なくとも第 1 電極 21a 上に成膜した後、所定のウェットエッティングまたはドライエッティングにより当該誘電体膜をパターニングすることによって、誘電体層 21c を形成することができる。

#### 【0047】

次に、図 5 (a) に示すように、第 1 電極 21a および誘電体層 21c を覆うように、電気めっき用のシード層 101 (太線で表す) を配線基板ウエハ 10' 上に形成する。シード層 101 は、例えば、Ti 膜およびその上の Au 膜からなる積層構造、Cr 膜およびその上の Au 膜からなる積層構造、Ti 膜およびその上の Cu 膜からなる積層構造、または、Cr 膜およびその上の Cu 膜からなる積層構造を有する。シード層 101 の形成手法

としては、例えば蒸着法やスパッタリング法を採用することができる。

【0048】

次に、図5(b)に示すように、1段目肉厚導体部形成用のレジストパターン102を形成する。1段目肉厚導体部には、キャパシタ21の第2電極21b、インダクタ22のスパイラルコイル22a、および立体配線30の第1配線部31が含まれる。レジストパターン102は、1段目肉厚導体部のパターン形状に対応する開口部102aを有する。レジストパターン102の形成においては、まず、配線基板ウエハ10'上に、液状のフォトレジストをスピンドルコーティングにより成膜する。次に、露光処理およびその後の現象処理を経て、当該フォトレジスト膜をパターニングする。フォトレジストとしては、例えば、AZP4210(AZエレクトロニクスマテリアルズ製)やAZ1500(AZエレクトロニクスマテリアルズ製)を使用することができる。後出のレジストパターンについても、このようなフォトレジストの成膜ならびにその後の露光処理および現象処理を経て、形成することができる。10

【0049】

次に、図5(c)に示すように、電気めっき法により、レジストパターン102の開口部102aにて、1段目肉厚導体部(第2電極21b、スパイラルコイル22a、および第1配線部31を含む)を形成する。当該電気めっき時には、シード層101が通電される。

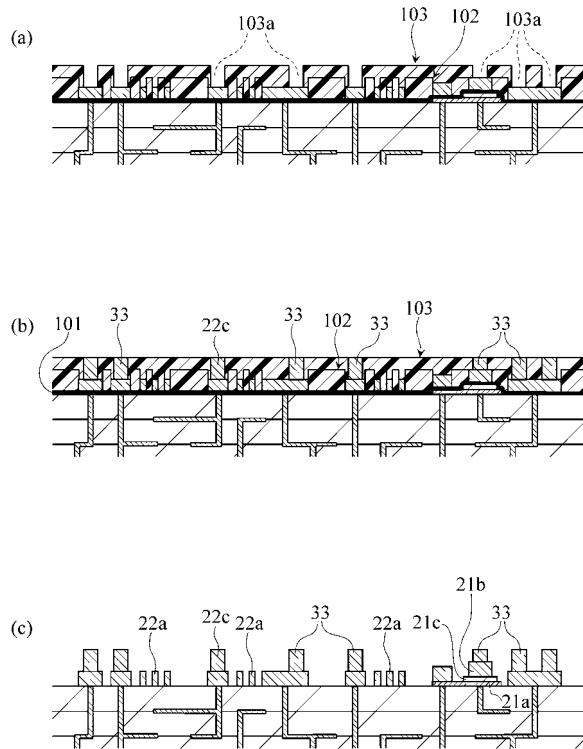

【0050】

次に、図6(a)に示すように、レジストパターン102の上位に、2段目肉厚導体部形成用のレジストパターン103を形成する。2段目肉厚導体部には、インダクタ22の連絡部22cおよび立体配線30の第3配線部33が含まれる。レジストパターン103は、2段目肉厚導体部のパターン形状に対応する開口部103aを有する。20

【0051】

次に、図6(b)に示すように、電気めっき法により、レジストパターン103の開口部103aにて、2段目肉厚導体部(連絡部22cおよび第3配線部33を含む)を形成する。当該電気めっき時には、シード層101が通電される。

【0052】

次に、図6(c)に示すように、例えば剥離液を作用させることによりレジストパターン102, 103を除去し、そして、当該除去の後にシード層101において露出している箇所を除去する(シード層101において露出していない箇所は、図6(c)以降の工程図では省略する)。剥離液としては、例えばAZリムーバ700(AZエレクトロニクスマテリアルズ製)を使用することができる。後出のレジストパターンの除去手法については、レジストパターン102, 103の当該除去手法と同様である。30

【0053】

次に、図7(a)に示すようにレジストパターン104を形成する。レジストパターン104は、2段目肉厚導体部の上位に3段目肉厚導体部を形成するための犠牲層として機能するものである。3段目肉厚導体部には、インダクタ22のスパイラルコイル22bおよび立体配線30の第2配線部32が含まれる。

【0054】

次に、図7(b)に示すように、レジストパターン104の表面、および、2段目肉厚導体部において露出する表面にわたり、シード層105(太線で表す)を形成する。シード層105の構成および形成手法は、上述のシード層101の構成および形成手法と同様である。40

【0055】

次に、図7(c)に示すように、3段目肉厚導体部形成用のレジストパターン106を形成する。レジストパターン106は、3段目肉厚導体部(スパイラルコイル22bおよび第2配線部32を含む)のパターン形状に対応する開口部106aを有する。

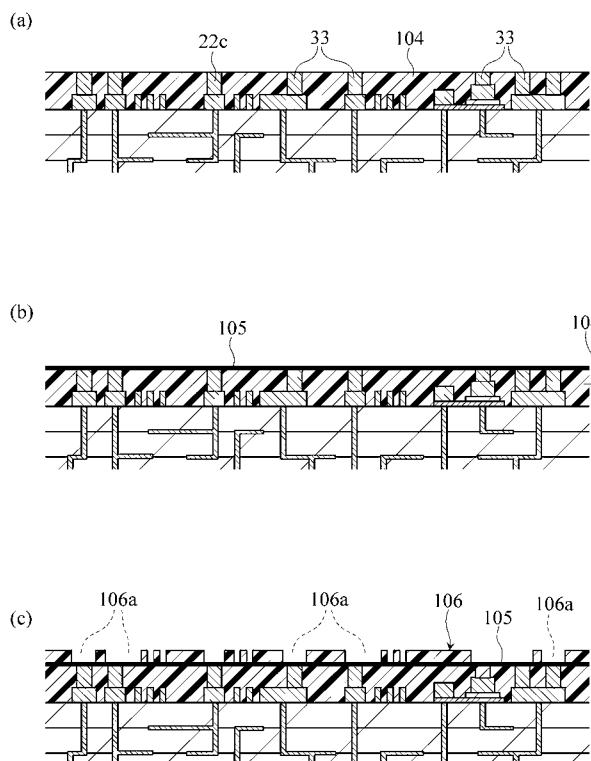

【0056】

次に、図8(a)に示すように、電気めっき法により、レジストパターン106の開口

50

部 106a にて、3段目肉厚導体部（スパイラルコイル 22b および第2配線部 32 を含む）を形成する。当該電気めっき時には、シード層 105 が通電される。

【0057】

次に、図 8 (b) に示すようにレジストパターン 107 を形成する。レジストパターン 017 は、立体配線 30 のパッド部 34 を形成するための開口部 107a を有する。

【0058】

次に、図 8 (c) に示すように、電気めっき法により、レジストパターン 107 の開口部 107a 内にパッド部 34 を形成する。当該電気めっき時には、シード層 105 が通電される。

【0059】

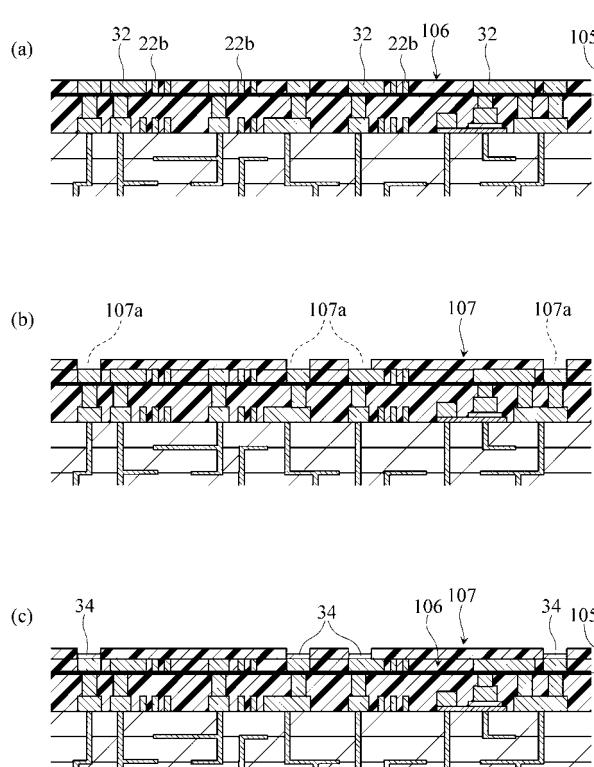

次に、図 9 (a) に示すように、レジストパターン 106, 107 を除去し、そして、当該除去の後にシード層 105 において露出している箇所を除去する（シード層 105 において露出していない箇所については、図 9 (a) 以降の工程図で省略する）。この後、図 9 (b) に示すように、レジストパターン 104 を除去する。

【0060】

次に、図 9 (c) に示すように、デバイスチップ 41, 42 の実装工程を行う。本工程では、デバイスチップごとに、そのバンプ電極とパッド部 34 とを位置合わせした後、当該バンプ電極とパッド部 34 とを接合する。デバイスチップ 41, 42 のバンプ電極が例えば Au スタッドバンプにより構成される場合、当該接合には、超音波を利用したボンディングを採用する。デバイスチップ 41, 42 のバンプ電極が例えばハンダバンプにより構成される場合、当該接合の際には、所定の加熱処理を経る。

【0061】

次に、ダイシング工程を実行し、配線基板ウエハ 10' を分割して複数の電子部品モジュール X1 を得る。以上のようにして、複数の電子部品モジュール X1 を一括して製造することができる。

【0062】

電子部品モジュール X1 における受動素子たるキャパシタ 21 およびインダクタ 22 は、配線基板 10 上にて形成されたものであり、比較的大きな表面実装部品の形態で配線基板 10 に対して搭載されたものではない。そのため、電子部品モジュール X1 は、各受動素子を基板表面の小領域内に設けるのに適し、従って、これら受動素子を含んで所定の受動回路を構成することのできる受動素子群 20 を、基板表面の小領域内に設けるのに適する。このような電子部品モジュール X1 は、モジュール自体の小型化に適する。

【0063】

電子部品モジュール X1 における受動素子たるキャパシタ 21 およびインダクタ 22 ならびに立体配線 30 は、樹脂材料やセラミック材料など誘電体材料内に埋め込まれたものではない。受動素子と受動素子の間や受動素子と立体配線 30 の間には誘電体材料は介在しない。そのため、電子部品モジュール X1 では、受動素子と受動素子の間や受動素子と立体配線 30 の間に生じ得る寄生容量を抑制することができる。このような寄生容量の抑制は、各受動素子の高性能化の観点から好ましく、特にインダクタ 22 の Q 値向上の観点から好ましい。加えて、電子部品モジュール X1 では、キャパシタ 21 における誘電体層 21c について、誘電率の高い材料を自由度高く選択することが可能である。したがって、電子部品モジュール X1 は高性能化に適する。

【0064】

このように、電子部品モジュール X1 は、小型化に適するとともに、高性能化に適するのである。このような電子部品モジュール X1 は、これが組み込まれる情報処理装置など電子装置全体の小型化および高性能化に資する。

【0065】

加えて、電子部品モジュール X1 は、受動素子群 20 が設けられている側とは反対の側に外部接続用のパッド部 14 を有する配線基板 10 を、モジュール全体のベース基板として備えるため、別の配線基板（例えば多層配線基板）を仲介せずに、当該モジュールを組

10

20

30

40

50

み込むべきシステム全体を支持するためのシステム基板ないしマザーボードに実装することができる。このような電子部品モジュールX1は、システムの小型化に資する。

【0066】

図12は、本発明の第2の実施形態に係る電子部品モジュールX2の断面図である。電子部品モジュールX2は、封止用キャップ51を更に備える点において、電子部品モジュールX1と異なる。封止用キャップ51は、例えば金属材料やセラミック材料よりも、封止用キャップ51により、配線基板10上の受動素子群20、立体配線30、およびデバイスチップ41, 42が気密封止されている。

【0067】

電子部品モジュールX2は、図9(c)を参照して上述したデバイスチップ実装工程の後であってダイシング工程の前に配線基板ウエハ10'に封止用キャップ51を搭載する工程(封止工程)を行う以外は、電子部品モジュールX1と同様の方法により製造することができる。封止工程では、封止材52を介して封止用キャップ51を配線基板ウエハ10'(配線基板10)に接合する。封止材52は、例えば、ハンダ、フリットガラス、または樹脂材料よりもなる。このようにウエハレベルで封止工程を行うことは、電子部品モジュールX2の製造効率の観点から好ましい。

【0068】

このような電子部品モジュールX2においては、電子部品モジュールX1に関して上述したのと同様の技術的利点を享受することができる。加えて、電子部品モジュールX2においては、上述のように、封止用キャップ51により、配線基板10上の受動素子群20、立体配線30、およびデバイスチップ41, 42が気密封止される。

【0069】

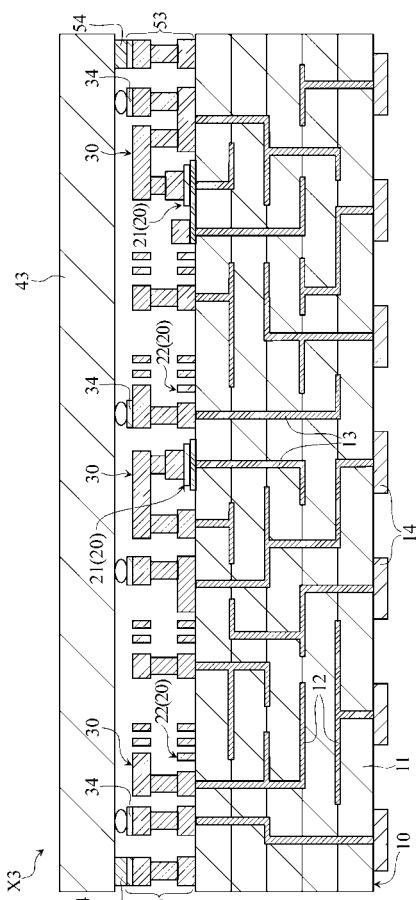

図13は、本発明の第3の実施形態に係る電子部品モジュールX3の断面図である。電子部品モジュールX3は、デバイスチップ41, 42に代えてデバイスチップ43を備え、且つ、周壁部53を更に備える点において、電子部品モジュールX1と異なる。デバイスチップ43は、複数のデバイスチップ(例えばデバイスチップ41, 42)がワンチップ化されたものであり、配線基板10上の受動素子群20および立体配線30の全体を覆うように設けられている。周壁部53は、配線基板10上において受動素子群20の周囲を包囲するように形成されたものである。デバイスチップ43は、立体配線30に加えて周壁部53を介して、配線基板10に固定されている。周壁部53は例えば金属材料よりもなる。このようなデバイスチップ43および周壁部53により、配線基板10上の受動素子群20および立体配線30が気密封止されている。実質的に、デバイスチップ43が封止用キャップとしての機能をも担う。

【0070】

電子部品モジュールX3は、周壁部53を形成し、且つ、実装工程においてデバイスチップ41, 42に代えてデバイスチップ43を実装する以外は、電子部品モジュールX1と同様の方法により製造することができる。周壁部53は、立体配線30の形成過程と併行して配線基板ウエハ10'上に形成することができる。実装工程では、デバイスチップ43のバンプ電極とパッド部34とを接合するとともに、封止材54を介してデバイスチップ43を周壁部53に接合する。封止材54は、例えば、ハンダ、フリットガラス、または樹脂材料よりもなる。実装工程と封止工程とが同時に実行されることとなる。また、このようにウエハレベルで封止工程を行うことは、電子部品モジュールX3の製造効率の観点から好ましい。

【0071】

このような電子部品モジュールX3においては、電子部品モジュールX1に関して上述したのと同様の技術的利点を享受することができる。加えて、電子部品モジュールX3においては、上述のように、実質的にデバイスチップ43が封止用キャップとしての機能も担い、このようなデバイスチップ43および周壁部53により、配線基板10上の受動素子群20および立体配線30が気密封止されている。

【0072】

10

20

30

40

50

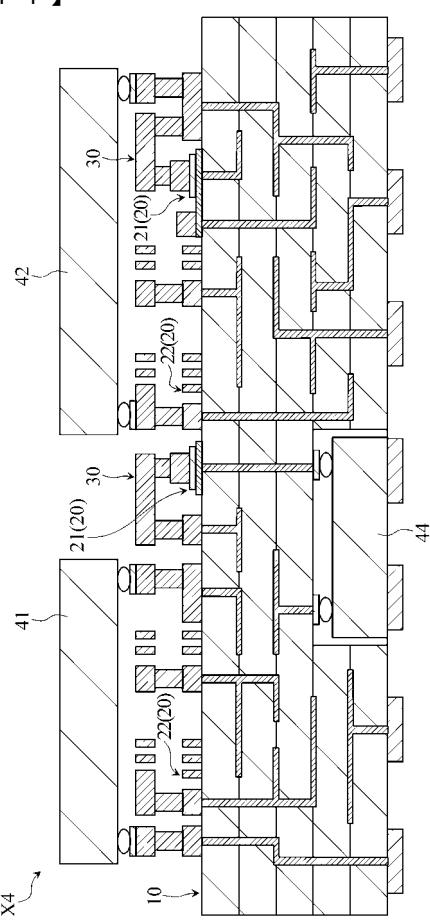

図14は、本発明の第4の実施形態に係る電子部品モジュールX4の断面図である。電子部品モジュールX4は、配線基板10に設けられた所定の凹部内に搭載されたデバイスチップ44を更に備える点において、電子部品モジュールX1と異なる。本発明の電子部品モジュールは、デバイスチップの実装態様について、このような構成を有してもよい。

【0073】

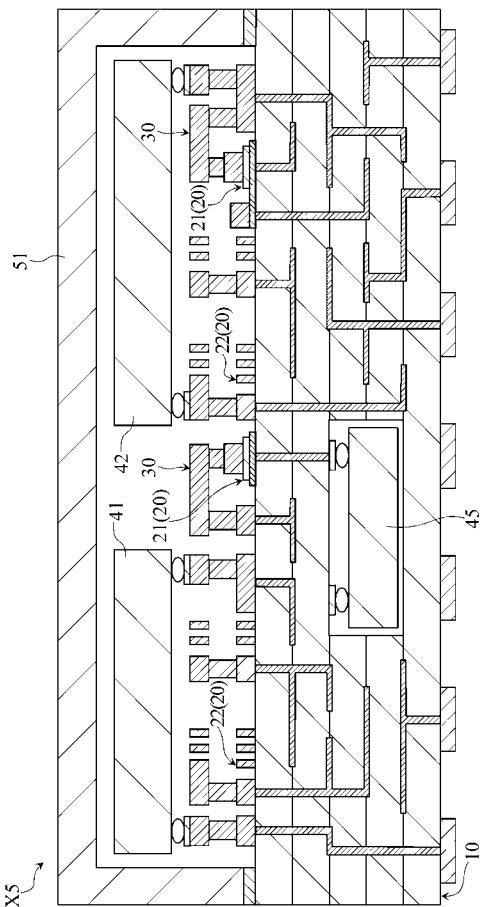

図15は、本発明の第5の実施形態に係る電子部品モジュールX5の断面図である。電子部品モジュールX5は、配線基板10に内蔵されたデバイスチップ45を更に備える点において、電子部品モジュールX2と異なる。本発明の電子部品モジュールは、デバイスチップの実装態様について、このような構成を有してもよい。

【0074】

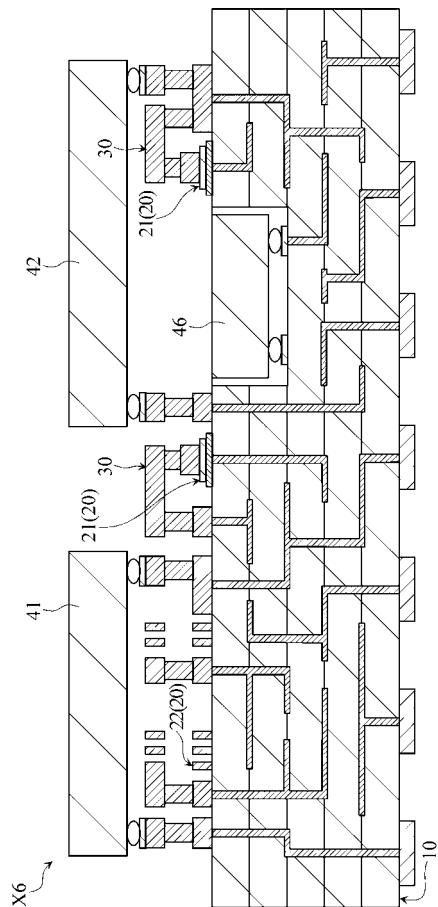

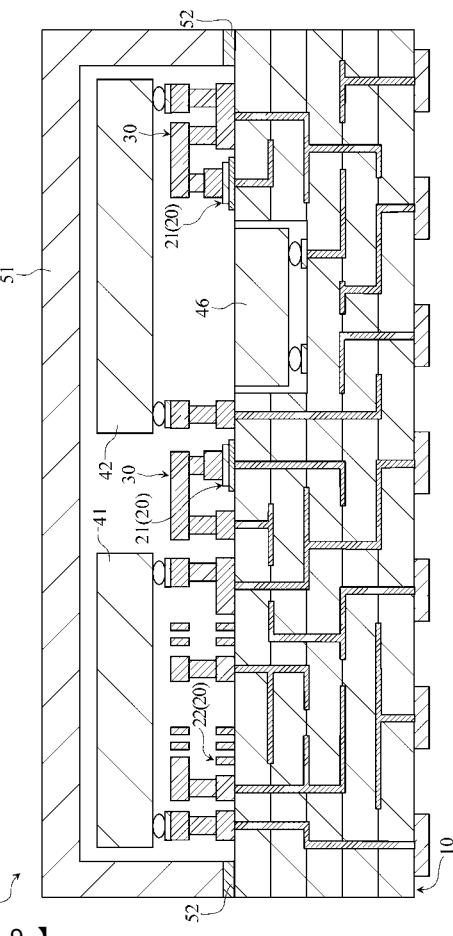

図16は、本発明の第6の実施形態に係る電子部品モジュールX6の断面図である。電子部品モジュールX6は、配線基板10と、受動素子群20と、立体配線30と、デバイスチップ41, 42, 46とを備える。電子部品モジュールX6は、配線基板10に設けられた所定の凹部内に搭載されたデバイスチップ46を更に備える点以外は、電子部品モジュールX1と略同様の構成を有する。

【0075】

図17は、本発明の第7の実施形態に係る電子部品モジュールX7の断面図である。電子部品モジュールX7は、封止用キャップ51を更に備える点において、電子部品モジュールX6と異なる。封止用キャップ51の構成材料、および、配線基板10に対する封止用キャップ51の接合態様は、電子部品モジュールX2の封止用キャップ51と同様である。

【0076】

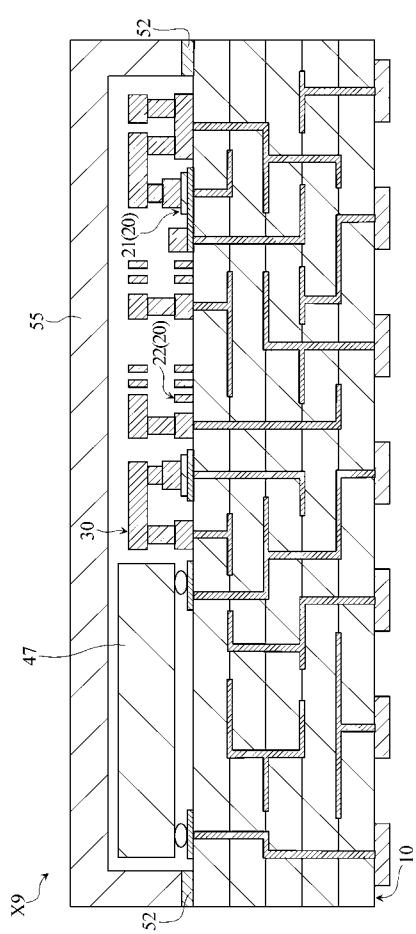

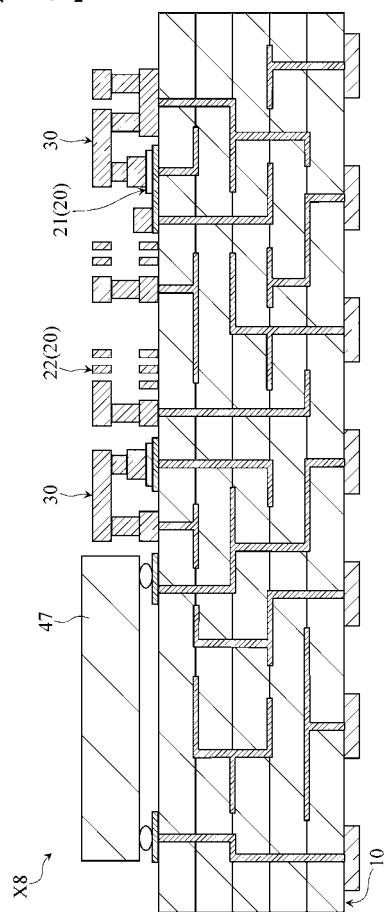

図18は、本発明の第8の実施形態に係る電子部品モジュールX8の断面図である。電子部品モジュールX8は、配線基板10と、受動素子群20と、立体配線30と、デバイスチップ47とを備える。デバイスチップ47は、立体配線30を介さずに直接的に配線基板10に搭載されている。本発明の電子部品モジュールは、デバイスチップの実装態様について、このような構成を有してもよい。

【0077】

図19は、本発明の第9の実施形態に係る電子部品モジュールX9の断面図である。電子部品モジュールX9は、封止用キャップ55を更に備える点において、電子部品モジュールX8と異なる。封止用キャップ55の構成材料、および、配線基板10に対する封止用キャップ55の接合態様は、電子部品モジュールX2の封止用キャップ51と同様である。

【0078】

以上のまとめとして、本発明の構成およびそのバリエーションを以下に付記として列挙する。

【0079】

(付記1) 配線基板と、

前記配線基板上にて形成された複数の受動素子を含む受動素子群と、

前記配線基板に実装された少なくとも一つのデバイスチップと、を備える電子部品モジュール。

(付記2) 前記複数の受動素子は、前記配線基板上にて形成された多段コイルインダクタを含み、当該多段コイルインダクタは、多段配置された複数のコイルを有し、且つ、隣り合うコイル導線が空隙を介して離隔している、付記1に記載の電子部品モジュール。

(付記3) 前記多段コイルインダクタは、空隙を介して互いに離隔する複数のスパイラルコイルを有する、付記2に記載の電子部品モジュール。

(付記4) 前記複数の受動素子は、前記配線基板上にて形成されたキャパシタおよび/または抵抗を含む、付記1から3のいずれか一つに記載の電子部品モジュール。

(付記5) 更に立体配線を備え、当該立体配線は、前記配線基板に接して延びる第1配線部と、前記配線基板から離隔して当該配線基板に沿って延びる第2配線部と、前記配線基

10

20

30

40

50

板の厚さ方向に延びる第3配線部とを含む、付記1から4のいずれか一つに記載の電子部品モジュール。

(付記6) 前記デバイスチップは、前記受動素子群の上位に位置する、付記1から5のいずれか一つに記載の電子部品モジュール。

(付記7) 前記配線基板は凹部を有し、前記デバイスチップは当該凹部に位置する、付記1から5のいずれか一つに記載の電子部品モジュール。

(付記8) 前記デバイスチップは前記配線基板の内部に位置する、付記1から5のいずれか一つに記載の電子部品モジュール。

(付記9) 前記少なくとも一つのデバイスチップは高周波フィルタを含む、付記1から8のいずれか一つに記載の電子部品モジュール。 10

(付記10) 前記高周波フィルタは、SAWフィルタ、F B A R フィルタ、およびマイクロ機械振動型フィルタからなる群より選択される单一または複数のフィルタにより構成される、付記9に記載の電子部品モジュール。

(付記11) 前記少なくとも一つのデバイスチップは半導体デバイスを含む、付記1から10のいずれか一つに記載の電子部品モジュール。

(付記12) 前記半導体デバイスは、信号を増幅するための増幅器を有する、付記11に記載の電子部品モジュール。

(付記13) 前記配線基板は、少なくとも一つの内部配線層を有する多層配線基板である、付記1から12のいずれか一つに記載の電子部品モジュール。

(付記14) 前記多層配線基板は、積層された複数のセラミック層を含む多層セラミック配線基板である、付記13に記載の電子部品モジュール。 20

(付記15) 前記多層配線基板は、積層された複数の樹脂層を含む、付記13に記載の電子部品モジュール。

(付記16) 前記配線基板は、内部配線層に接続するビアを有する、付記13から15のいずれか一つに記載の電子部品モジュール。

(付記17) 前記配線基板は、当該配線基板を貫通するビアを有する、付記1から16のいずれか一つに記載の電子部品モジュール。

(付記18) 更に封止用キャップを備える、付記1から17のいずれか一つに記載の電子部品モジュール。

(付記19) 配線基板と、前記配線基板上に設けられた複数の受動素子を含む受動素子群と、前記配線基板に実装された少なくとも一つのデバイスチップと、を備える電子部品モジュールを製造するための方法であって、 30

複数の電子部品モジュール形成区画を有する配線基板ウエハを作製する工程と、

前記電子部品モジュール形成区画の各々において前記配線基板ウエハ上にて複数の受動素子を形成する工程と、

前記電子部品モジュール形成区画の各々において前記配線基板ウエハにデバイスチップを搭載する工程と、

前記配線基板ウエハを分割する工程と、を含む電子部品モジュール製造方法。

(付記20) 前記電子部品モジュール形成区画の各々において前記配線基板ウエハに封止キャップを搭載する工程を更に含む、付記19に記載の電子部品モジュール。 40

【図面の簡単な説明】

【0080】

【図1】本発明の第1の実施形態に係る電子部品モジュールの断面図である。

【図2】配線基板の平面図である。

【図3】多段コイルインダクタの分解平面図である。

【図4】第1の実施形態に係る電子部品モジュールの製造方法における一部の工程を表す。

【図5】図4の後に続く工程を表す。

【図6】図5の後に続く工程を表す。

【図7】図6の後に続く工程を表す。 50

【図8】図7の後に続く工程を表す。

【図9】図8の後に続く工程を表す。

【図10】平滑化処理を表す。

【図11】他の平滑化処理を表す。

【図12】本発明の第2の実施形態に係る電子部品モジュールの断面図である。

【図13】本発明の第3の実施形態に係る電子部品モジュールの断面図である。

【図14】本発明の第4の実施形態に係る電子部品モジュールの断面図である。

【図15】本発明の第5の実施形態に係る電子部品モジュールの断面図である。

【図16】本発明の第6の実施形態に係る電子部品モジュールの断面図である。

【図17】本発明の第7の実施形態に係る電子部品モジュールの断面図である。

【図18】本発明の第8の実施形態に係る電子部品モジュールの断面図である。

【図19】本発明の第9の実施形態に係る電子部品モジュールの断面図である。

【符号の説明】

【0081】

X 1 ~ X 9 電子部品モジュール

1 0 配線基板

1 0 ' 配線基板ウエハ

1 0 ' ' プリ配線基板ウエハ

1 1 絶縁層

1 2 配線パターン

1 3 ビア

1 4 パッド部

2 0 受動素子群

2 1 キャパシタ

2 1 a 第1電極

2 1 b 第2電極

2 1 c 誘電体層

2 2 インダクタ

2 2 a , 2 2 b スパイラルコイル

3 0 立体配線

3 1 第1配線部

3 2 第2配線部

3 3 第3配線部

3 4 パッド部

4 1 , 4 2 , 4 3 , 4 4 , 4 5 , 4 6 , 4 7 デバイスチップ

5 1 , 5 5 封止用キャップ

5 2 , 5 4 封止材

5 3 周壁部

10

20

30

【図1】

第1の実施形態の電子部品モジュール

【図3】

多段コイルインダクタの分解平面図

【図2】

配線基板の平面図

【図4】

電子部品モジュール製造方法における一部の工程

【図5】

図4の後に続く工程

【図6】

図5の後に続く工程

【図7】

図6の後に続く工程

【図8】

図7の後に続く工程

【図9】

図8の後に続く工程

【図10】

平滑化処理

【図11】

他の平滑化処理

【図12】

第2の実施形態の電子部品モジュール

【図13】

【図15】

第5の実施形態の電子部品モジュール

【図14】

【図16】

第6の実施形態の電子部品モジュール

第3の実施形態の電子部品モジュール

【図17】

第7の実施形態の電子部品モジュール

【図19】

第9の実施形態の電子部品モジュール

【図18】

第8の実施形態の電子部品モジュール

---

フロントページの続き

(72)発明者 松本 剛

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 上田 知史

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 高橋 岳雄

神奈川県横浜市港北区新横浜二丁目3番地12 富士通メディアデバイス株式会社内

審査官 宮本 靖史

(56)参考文献 特開平09-326451 (JP, A)

特開2005-302873 (JP, A)

特開2001-223301 (JP, A)

特開2002-252324 (JP, A)

特開平11-274416 (JP, A)

特開平08-274575 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/00