(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4993249号

(P4993249)

(45) 発行日 平成24年8月8日(2012.8.8)

(24) 登録日 平成24年5月18日(2012.5.18)

(51) Int.Cl.

G06F 9/48 (2006.01)

F 1

G06F 9/46 315Z

請求項の数 3 (全 30 頁)

(21) 出願番号 特願2005-305195 (P2005-305195)

(22) 出願日 平成17年10月20日 (2005.10.20)

(65) 公開番号 特開2006-134318 (P2006-134318A)

(43) 公開日 平成18年5月25日 (2006.5.25)

審査請求日 平成20年10月16日 (2008.10.16)

(31) 優先権主張番号 10/970,570

(32) 優先日 平成16年10月21日 (2004.10.21)

(33) 優先権主張国 米国(US)

(73) 特許権者 390041542

ゼネラル・エレクトリック・カンパニイ

アメリカ合衆国、ニューヨーク州、スケネ

クタディ、リバーロード、1番

(74) 代理人 100137545

弁理士 荒川 智志

(74) 代理人 100105588

弁理士 小倉 博

(74) 代理人 100129779

弁理士 黒川 俊久

(72) 発明者 グレゴリー・スコット・ドロバ

アメリカ合衆国、カリフォルニア州、サン

ノゼ、ナンバー1307、アルマデン・

ロード、1776番

最終頁に続く

(54) 【発明の名称】計測システムおよび制御システム向けのイベントベースのオペレーティングシステム、方法、および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ノンプリエンプティブなオペレーティングシステムを備えたコントローラ(12)をプロセッサにより操作する方法であって、前記方法は、

前記プロセッサにより、クロック間で、センサー(42)、スイッチ(56)、実行中のプログラムの命令、あるいはその組み合わせからの、複数のイベントのうちの1つのイベントが、非アクティブなイベント(302)、アクティブなイベント(308)、保留中のイベント(306)、実行中のイベント(310)、または、待機中のイベント(304)であることを示すとともに、非アクティブなイベント(302)、アクティブなイベント(308)、保留中のイベント(306)、実行中のイベント(310)、および、待機中のイベント(304)を含む前記イベントの1つまたは複数を開始する1つまたは複数の信号を受信する工程と、

前記プロセッサにより、前記1つまたは複数の信号を受信する工程の直後のクロックまたはその後に、前記受信した信号に従ってイベントのエントリを更新し、クロック時に前記オペレーティングシステムのシャドウセマフォを更新して、前記シャドウセマフォを用いて開始期限を過ぎたイベントの優先順位を付け直す工程であって、前記エントリには、前記保留中のイベントの残り時間、前記アクティブなイベントの開始期限経過時間、各イベントの優先順位、前記複数のイベント中のイベントが非アクティブ、待機、保留、アクティブ、実行中のいずれであるかの表示を含む、工程と、

前記プロセッサにより、前記保留中のイベント(306)が開始期限が到来したかどうか

かを判断し、前記開始期限が到来したイベントを保留中のイベント(306)からアクティブなイベント(308)に変更する工程と、

前記プロセッサにより、最も優先順位の高い、前記保留からアクティブに変更されたイベントを実行中のプログラムに通知する工程と、

を含み、

開始期限を過ぎたイベントの優先順位を付け直す工程は、前記プロセッサにより、前記実行中のプログラムにまだ通知していない開始期限を過ぎたアクティブなイベント(308)の前記優先順位を上げる工程を含む、

方法。

**【請求項2】**

10

ノンプリエンプティブなオペレーティングシステムを備え、プロセッサにより実行可能な命令が記録されたコンピュータ可読記録媒体であって、前記命令は、プロセッサにより

クロック間で、センサー(42)、スイッチ(56)、実行中のプログラムの命令、あるいはその組み合わせからの、複数のイベントのうちの1つのイベントが、非アクティブなイベント(302)、アクティブなイベント(308)、保留中のイベント(306)、実行中のイベント(310)、または、待機中のイベント(304)であることを示すとともに、非アクティブなイベント(302)、アクティブなイベント(308)、保留中のイベント(306)、実行中のイベント(310)、および、待機中のイベント(304)を含む前記イベントの1つまたは複数を開始する1つまたは複数の信号を受信し、

20

前記1つまたは複数の信号の受信の直後のクロックまたはその後に、前記受信した信号に従ってイベントのエントリを更新し、クロック時に前記オペレーティングシステムのシャドウセマフォを更新して、前記シャドウセマフォを用いて開始期限を過ぎたイベントの優先順位を付け直し、この際、前記エントリは、前記保留中のイベントの残り時間、前記アクティブなイベントの開始期限経過時間、各イベントの優先順位、前記複数のイベント中のイベントが非アクティブ、待機、保留、アクティブ、実行中のいずれであるかの表示を含み、

前記保留中のイベント(306)が開始期限が到来したかどうかを判断し、前記開始期限が到来したイベントを保留中のイベント(306)からアクティブなイベント(308)に変更し、

30

最も優先順位の高い、前記保留からアクティブに変更されたイベントを実行中のプログラムに通知する

命令であり、この際、

開始期限を過ぎたイベントの優先順位の付け直しは、前記プロセッサにより、前記実行中のプログラムにまだ通知していない開始期限を過ぎたアクティブなイベント(308)の前記優先順位を上げることを含む、

コンピュータ可読記録媒体。

**【請求項3】**

40

プロセッサと、ノンプリエンプティブなオペレーティングシステムと前記プロセッサにより実行可能な命令が記録されたメモリとを備えたコントローラであって、前記コントローラは、

クロック間で、センサー(42)、スイッチ(56)、実行中のプログラムの命令、あるいはその組み合わせからの、複数のイベントのうちの1つのイベントが、非アクティブなイベント(302)、アクティブなイベント(308)、保留中のイベント(306)、実行中のイベント(310)、または、待機中のイベント(304)であることを示すとともに、非アクティブなイベント(302)、アクティブなイベント(308)、保留中のイベント(306)、実行中のイベント(310)、および、待機中のイベント(304)を含む前記イベントの1つまたは複数を開始する1つまたは複数の信号を受信し、

前記1つまたは複数の信号の受信の直後のクロックまたはその後に、前記受信した信号に従ってイベントのエントリを更新し、クロック時に前記オペレーティングシステムのシ

50

ヤドウセマフォを更新して、前記シャドウセマフォを用いて開始期限を過ぎたイベントの優先順位を付け直し、この際、前記エントリは、前記保留中のイベントの残り時間、前記アクティブなイベントの開始期限経過時間、各イベントの優先順位、前記複数のイベント中のイベントが非アクティブ、待機、保留、アクティブ、実行中のいずれであるかの表示を含み、

前記保留中のイベント（306）が開始期限が到来したかどうかを判断し、前記開始期限が到来したイベントを保留中のイベント（306）からアクティブなイベント（308）に変更し、

最も優先順位の高い、前記保留からアクティブに変更されたイベントを実行中のプログラムに通知し、

この際、

開始期限を過ぎたイベントの優先順位の付け直しは、前記プロセッサにより、前記実行中のプログラムにまだ通知していない開始期限を過ぎたアクティブなイベント（308）の前記優先順位を上げることを含む、

コントローラ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般的にはコンピュータオペレーティングシステムに関し、より具体的には計測システムおよび制御システムにおいて高度なタイミング機能提供するためのコンピュータオペレーティングシステムに関する。 20

【背景技術】

【0002】

原子力発電所向けのホウ酸水注入系（SLC：Standby Liquid Control）の論理プロセッサは、複数のさまざまなイベントに迅速に反応する必要があり、結果として発電所内の複数のさまざまなシステムのパラメータを監視する必要がある。こうしたパラメータには、頻繁かつ／または定期的に変化するものがある一方で、特定の設備で発生してはならないきわめてまれなイベントに応答した場合にのみ変化するものもある。論理プロセッサのイベントおよびその状態変化のコンテキストを検出し、間接費の導入を一定程度に抑えるために、マイクロプロセッサ用のオペレーティングシステム（OS：Operating System）を採用することができる。いくつかの構成において、SLCには多くの同期タイマー（たとえば、8個の同期タイマー）が必要であり、1つのマイクロコントローラでは対応できない場合がある。 30

【特許文献1】米国特許6,775,728号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

タスク指向のOSには、少なくともいくつかの周知の核計測分析および制御（NUMA C：Nuclear Measurement Analysis and Control）機器が使用されている。このOSでは、すべてのタスクをラウンドロビン方式で実行する必要がある。この種のOSを適用すると、間接費がかかり、特定の機能が必要ないのに実行される。しかし、各タイマーのカウンタとしてグローバルなスタティック変数を作成することで、複数のタイミングイベントを監視できる。このような変数は、システムクロックを使用してセットし、カウンタの値を増減できる。この限られた数のタイマーを使用して複数のタイミングイベントを監視する方法は、非常に単純であるが、記述するコードの量を増大し、コードのメンテナンスコストを増大する傾向がある。さらに、グローバル変数を使用することでインターフェイスの設計が複雑になり、さまざまなモジュールの操作の相互依存性が必要以上に高くなる。 40

【課題を解決するための手段】

【0004】

したがって、本発明のいくつかの構成では、複数のタイマーを備えるコントローラを操作し、これを使用してタイマーの数より多い複数のイベントを制御する方法を提供する。本方法には、クロックチック (clock ticks) 間で、1つまたは複数の時間指定 (time) イベントを開始するセンサー、スイッチ、実行中のプログラム、あるいはその組み合わせからの1つまたは複数の信号を受信する工程が含まれる。本方法には、1つまたは複数の信号を受信した直後のクロックチックの後に、受信した信号 (1つまたは複数) に従ってイベント制御ブロック内のエントリを更新する工程がさらに含まれる。エントリには、保留イベントの残り時間、アクティブイベントの期限経過時間、および各イベントの優先順位が含まれる。本方法には、保留イベント (1つまたは複数) がタイムアウトしたかどうかを判断する工程と、タイムアウトしたイベントがある場合にそれを開始する工程と、開始した最も優先順位の高いイベントについて通知する信号を実行中のプログラムに送信する工程がさらに含まれる。10

#### 【0005】

本発明の別のいくつかの態様において、プロセッサに対してさまざまな機能の実行を指示するように構成された命令を含むノンプリエンプティブ (non-preemptive) なオペレーティングシステムが記録された機械可読媒体またはメモリが提供される。このような機能には、クロックチック間で、1つまたは複数の時間指定イベントを開始するセンサー、スイッチ、実行中のプログラム、あるいはその組み合わせからの1つまたは複数の信号を受信する機能が含まれる。こうした機能には、1つまたは複数の信号を受信した直後のクロックチックまたはその後に、受信した信号 (1つまたは複数) に従ってイベント制御ブロック内のエントリを更新する機能がさらに含まれる。ただし、エントリには保留イベントの残り時間、アクティブイベントの期限経過時間、および各イベントの優先順位が含まれる。本機能には、保留イベント (1つまたは複数) がタイムアウトしたかどうかを判断する機能と、タイムアウトしたイベントがある場合にそれを開始する機能と、開始した最も優先順位の高いイベントについて通知する信号を実行中のプログラムに送信する機能がさらに含まれる。20

#### 【0006】

本発明のさらに別の態様において、本発明は複数のタイマーを備えるプロセッサと、プロセッサに対する命令を格納するメモリとを備えるコントローラを提供する。本コントローラには、クロックチック間で、1つまたは複数の時間指定イベントを開始するセンサー、スイッチ、実行中のプログラム、あるいはその組み合わせからの1つまたは複数の信号を受信するように構成されている。本コントローラは、1つまたは複数の信号を受信した直後のクロックチックまたはその後に、受信した信号 (1つまたは複数) に従ってイベント制御ブロック内のエントリを更新するようにさらに構成されている。こうしたエントリには、保留イベントの残り時間、アクティブイベントの期限経過時間、および各イベントの優先順位が含まれる。本コントローラは、保留イベント (1つまたは複数) がタイムアウトしたかどうかを判断し、タイムアウトしたイベントがある場合にそれを開始し、開始した最も優先順位の高いイベントについて通知する信号を実行中のプログラムに送信するようにさらに構成されている。30

#### 【0007】

したがって、本発明の構成は、1つまたは複数の物理的なタイマーを備えるコントローラを使用して、工業プラント内のイベントのように複雑なイベントのタイミングを提供するのが有利であることが認識されよう。ただし、物理的なタイマーの数は時間指定イベントの数より少ない。

#### 【発明を実施するための最良の形態】

#### 【0008】

本発明の構成は、時間指定イベント (原子力発電所を含む工業プラント内で発生するものなど) の高度な制御を可能にする。本発明のいくつかの構成による技術的な効果には、使用可能なハードウェアタイマーの数より多い複数のイベントのタイミングを制御することと、時間指定イベントが特定の時間内に確実に発生することがある。50

いくつかの構成では、工業プロセスにおける安全制御として使用するのに適したマイクロコントローラーアーキテクチャが提供される。このアーキテクチャは多くの工業プロセスに適しているが、特に原子力に関する機器および制御システムには最適である。たとえば、このマイクロコントローラーアーキテクチャは核計測分析および制御（NUMAC）モジュール、高圧炉心注水系（HPCF：High Pressure Core Floop der）制御モジュール、出力論理ユニット（OLU：Output Logic Unit）モジュール、ホウ酸注入系（SLC）モジュールでの使用に適している。こうしたモジュールは、本発明の構成を採用する一連のマイクロコントローラベースのシャーシである。さまざまな構成において、このような機器はモジュール形式をとっており、さらにリレー、ファイバ／光通信リンク、入力コンタクトカード（input contact cards）、またはマイクロコントローラ、ファームウェア、カスタムロジック（CPLD）、EPROM、NVRAM、RAM、およびさまざまなICを含む論理ボード（マザーボード）に直接または間接的に挿入できるその他の入力／出力（I/O）カードを追加することで拡張できる。本発明のいくつかの構成では、同類のモジュールを交換できるように、取り外し可能なすべてのモジュールを標準化している。いくつかの構成において、外部接続やインターフェイスはメンテナンスしやすいように機器のパネル背面に配置される。本発明のさまざまな構成から得られる技術的な効果には、特に担当者が監視を行うことによるアナログの安全システムの自動化、容易に拡張できる操作、コンポーネントの標準化による利便性がある。

## 【0009】

本発明のマイクロプロセッサーアーキテクチャを利用した機器は、幅48.26cm（19インチ）の業務用のラックに収納できるように設計でき、標準の高さを13.335cm（5.25インチ）にできる。本発明のいくつかの構成では、冗長電源（2つの電源）を使用して、マイクロプロセッサーアーキテクチャを利用した機器のフェイルセーフで堅牢な電気的なニーズを満たしている。いくつかの構成では、マイクロコントローラファームウェアにおいて特定のアプリケーションのセルフテストと監視の方法が提供される。いくつかの構成では、マイクロコントローラサブシステムロジックは、CPLDサブシステムに含まれるロジックから独立して動作し、一方のサブシステムに破局的な（catastrophic）障害が発生した場合に他方が機能するように、マイクロコントローラとCPLDとのインターフェイスが提供される。本発明の構成を複数の機器で利用すると、一貫したユーザーインターフェイスとフィードバック（「ルックアンドフィール」）が得られる。各機器は、たとえばキーロックスイッチを使用してフロントパネルを固定することもできる。本発明のいくつかの構成では、押しボタン、LED、および／または英数字ディスプレイも提供される。新しい機器は、顧客に固有の要件や技術的な要件を満たすように拡張できる。たとえば、特定の通信プロトコル（MIL-STD-1553、RS-232など）、特定の電圧と電流（12VDC、24VDC、120VACなど）を処理するように設計されたリレー、さまざまな波長（850nm、1300nmなど）の光データを送信および受信するように設計された光ファイバカードに適応できるデバイスは、本発明のさまざまな構成で利用できる。

## 【0010】

本発明のいくつかの構成において、機器はたとえば48.26cm（19インチ）の標準的な機器ラックにラックマウント方式で取り付けることができる。たとえば、本発明のいくつかの構成において、機器のシャーシは、幅48.26cm（19インチ）、高さ13.335cm（5.25インチ）、奥行き30.48cm～35.56cm（12～14インチ）である。各機器のシャーシには、機器の該当するアプリケーションに応じて、前面パネルディスプレイ、デュアル冗長電源、論理カード、I/Oカードを収納できる。同類のモジュールは電気的にも機械的にも機器間で交換可能であり、交換しても補正は必要ない。

## 【0011】

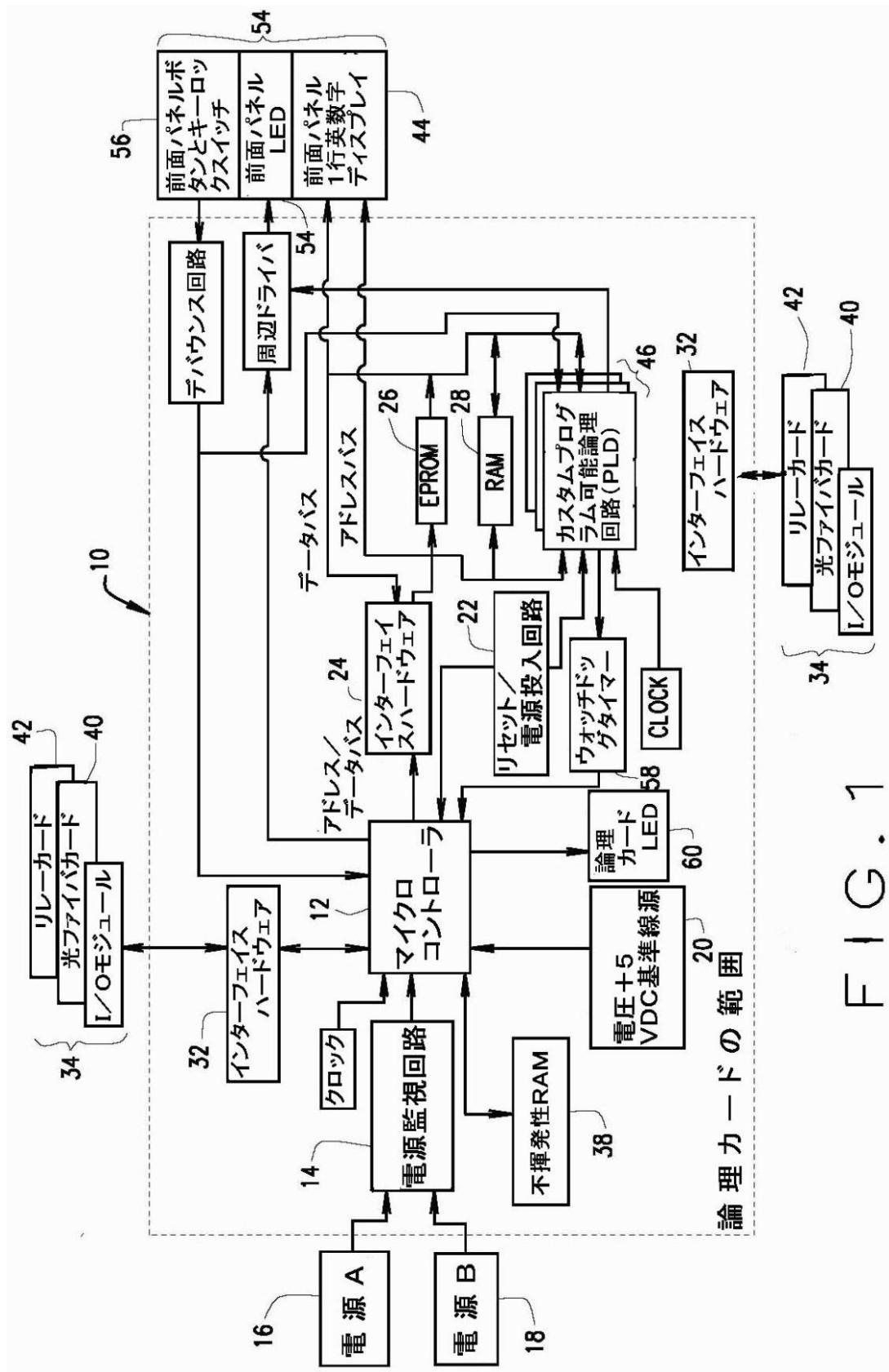

本発明のいくつかの構成において、図1を参照すると、論理カード10は機器のロジッ

10

20

30

40

50

クと制御、外部システム（論理カード10を含む機器の外部のシステム）へのステータス通信、およびオペレータ用のディスプレイおよびキーボード制御を提供している。論理カード10のいくつかの構成には、以下のコンポーネントが含まれる。

#### 【0012】

##### マイクロコントローラ

マイクロコントローラ12を使用すると、高速の計算と迅速な入力／出力操作を処理できる。適切なマイクロコントローラの例には、87C196KDマイクロコントローラ、すなわちIntel Corporation, Santa Clara, CAから入手可能な16ビットCHMOSプロセッサがある。本発明の構成に利用できるこのマイクロコントローラの機能には、20MHzのクロック、1KBレジスタRAM、前二重シリアルポート、5つの8ビットI/Oポート、4個の内蔵16ビットタイマー、および入力MUXを伴う10ビットA/Dコンバータが含まれる。

#### 【0013】

論理カードの機能上の操作は、マイクロコントローラ12で監視する。マイクロコントローラ12は、監視に利用できる非同期のシリアルステータスマッセージを送信し、キーボードとディスプレイの制御を可能にし、デジタルI/Oラインを監視する。こうした機能に加えて、マイクロコントローラは電源と外部のセンサー電圧を監視し、メモリの整合性を確認することで、起動およびオンラインのセルフテストを実行する。送信された通信メッセージは、ループバックしてセルフテストで確認できる。

#### 【0014】

##### マイクロコントローラスーパーバイザ

マイクロプロセッサスーパーバイザロジックには、冗長電源16および18から供給される論理カード10およびI/Oモジュール34の+5VDC電力を監視し、電圧が+4.50～4.60VDCの場合にマイクロコントローラ12をリセットする電源監視回路14が含まれる。このリセットにより、CPLDコントローラロジック46も初期状態に戻る。マイクロプロセッサスーパーバイザロジックの要素として、電圧+5VDCという基準線源(reference source)20とリセット／電源投入回路22も提供される。

#### 【0015】

マイクロコントローラ12の他に1つまたは複数の結合プログラム可能論理回路(CPLD: Complex Programmable Logic Device)46が提供され、制御と復号を実行し、かつ／または機能ロジックを提供する。

#### 【0016】

##### 制御および復号ハードウェア

本発明のいくつかの構成において、制御および復号ハードウェアは、次の1つまたは複数を提供するように構成された結合プログラム可能論理回路(CPLD)46を含むまたはそれから基本的に構成される。

1. EPROM 26やRAM 28、およびメモリをマップするすべてのI/O機能のアドレス復号

2. さまざまな論理ステータスレジスタのアドレス復号

3. 周辺装置に低速でアクセスすることによるマイクロコントローラ12の待ち状態のジェネレータ制御(たとえば、読み出しまたは書き込みアクセスのいくつかの構成では、前面パネルLEDディスプレイ30には3つの待ち状態が必要である)。

#### 【0017】

##### 機能ロジックインターフェイスハードウェア

本発明のいくつかの構成において、機能ロジックインターフェイスハードウェアは、次の少なくとも1つを提供するように構成された結合プログラム可能論理回路(CPLD)を含むまたはそれから基本的に構成される。

1. さまざまな分周器(frequency dividers)

2. トリップステータスとI/Oを監視し、トリップコマンドとその他の制御コマン

10

20

30

40

50

ドを生成できる機能ロジック

- 3 . さまざまな通信プロトコルのサポートロジック

- 4 . 外部インターフェイスカード34とその他のグルーロジック(g l u e l o g i c)のサポート

**【0018】**

論理カード10の構成は複数のCPLD 46(たとえば、いくつかの構成では1枚のカードに最大3個)に対応しており、CPLDは容易に修理、交換、再構成できるようソケットが付いている。したがって、制御および復号ハードウェアと機能ロジックインターフェイスハードウェアは、唯一のCPLD内の配置、2つの別々のCPLD上の配置、あるいは2つ以上のCPLDにまたがった配置などが可能である。本発明では、一方で制御および復号ハードウェアと機能ロジックインターフェイスハードウェア、他方で個々のCPLDが1対1に対応する必要はない。

**【0019】**

入力保護とアナログ参照

制御カード上の入力ライン、+5VDC、+5VDC前面パネル、+5VDC光ファイバ、+5VDCリレーカードA & B、+24VDC、+48VDCは、温度限流器(thermal current limiting devices)(図1で個別には図示せず)を自動的にリセットすることで保護される。電流が限界に達して限流器が加熱されると、過電流の状態がなくなるまで回路が開く。入力ラインは、セルフテスト中に電源監視回路14を使用してマイクロコントローラ12で監視される。このテストの各測定の結果を組み合わせて、前面パネルに表示された電源障害LED(LED 30に含まれる)を制御する。いくつかの構成において、電源電圧は論理カード10を備える機器の背面パネルのテストポイントで測定できる。

マイクロコントローラ12のA/Dコンバータで必要な+5VDC参考20は、+24VDC入力から生成され、不足電圧/過電圧検出回路によって監視される。

**【0020】**

E PROMおよびRAMメモリ

いくつかの構成では、不揮発性プログラムストレージとしてE PROM 26が提供される。この目的で、32KB E PROMを提供してもよい。いくつかの構成では、コントローラ12用の高速読み出し/書き込みメモリとしてスタティックRAM 28、たとえば8KBスタティックRAMが提供される。

**【0021】**

不揮発性RAM

いくつかの構成では、電力が供給されなくなっても失われてはならないアプリケーションパラメータを記憶するために、不揮発性RAM 38(2K×8ビット強誘電性RAMなど)が提供される。こうしたパラメータはカード10を利用するアプリケーションに依存するが、不揮発性RAM 38に格納できるアプリケーションパラメータの部分的なリストには、セルフテストのエラーコードと回数、較正パラメータなどを含めてよい。いくつかの構成において、RAM 38は電力消費が低く、耐久性がきわめて高いシリアルデバイスである。

**【0022】**

光ファイバインターフェイスカード

光ファイバインターフェイスカード40は、光信号と電気信号との変換を行う。本発明のいくつかの構成において、各カードは6つの物理チャネルを備えている。こうしたチャネルは、カード10のアプリケーションに基づいて、送信、受信、あるいは双方向通信に利用できる。たとえば、各チャネルは最大感度(peak sensitivity)の波長が850nmの光ファイバ信号で動作するが、いくつかの構成では別の波長(たとえば1300nm)を使用している。いくつかの構成において、光送信機と光受信機は標準のSTタイプの光コネクタに接続する。

**【0023】**

10

20

30

40

50

リレー I/O カード

多くのアプリケーションでは、1つまたは複数のリレー I/O カード 42 が提供される。I/O カード 42 には、たとえば機械的なラッチリレー (latching relay)、ノンラッチリレー、コンタクトクロージャ (contact closure) 感知回路、またはそれらの任意の組み合わせを含めてもよい。各 I/O カード 42 は、論理カード 10 と制御の対象となる他のデバイスとのインターフェイス バッファとして構成される（論理カード 10 の視点からは「外部の世界」として映る）。シャーシに入る高電圧信号は、標準の TTL レベルに変換される。標準の TTL レベルの信号は、多くのインスタンスでこうしたカードに送信され、外部システムで使用するはるかに高い電圧に切り替えられる。

10

## 【0024】

光ファイバインターフェイスカード 40 とリレー I/O カード 42 は、外部システム（たとえば、限定はされないが、バルブ、ポンプ、その他の機器）を制御かつ／または感知でき、監視できる。一方では、外部のシステムと論理カード 10 上のコンポーネントとの電気的絶縁を提供する。このように、論理カード 10 は外部システムまたは安全機器と外部システムとの通信ラインの電気的障害が原因となって発生する問題に左右されにくい。いくつかの構成では、インターフェイスハードウェア 32 が提供され、マイクロコントローラ 12 および／または CPLD 46 と機器内にある任意のインターフェイスカード 34 とをインターフェイスする。

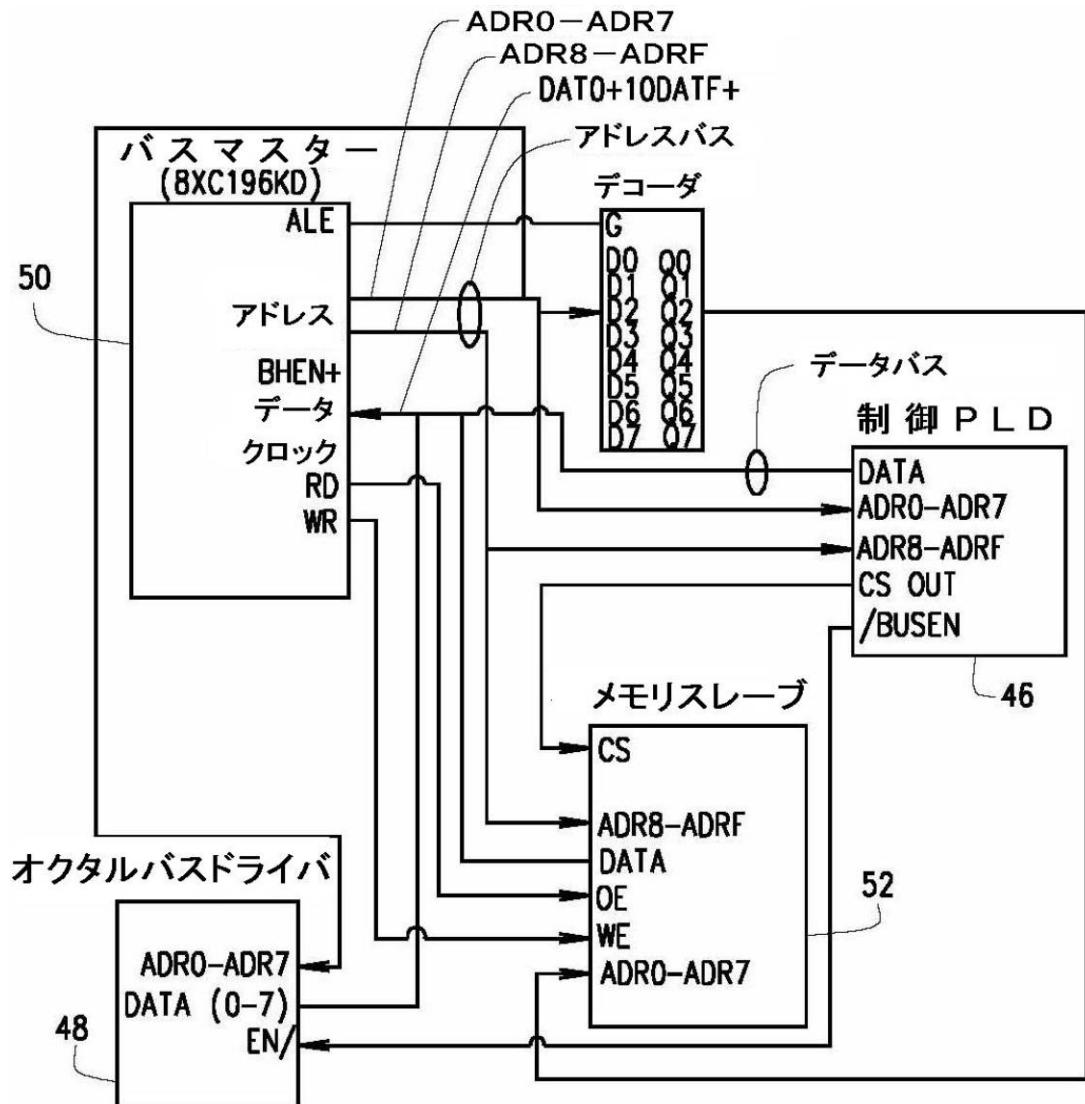

## 【0025】

20

外部ロジックを使用するか CPLD を使用するかに関わらず、本発明のいくつかの構成では、最大 4 枚の I/O カード 34、前面パネルディスプレイ 30、および／または 44、EPROM 26、RAM 28、および 1～3 個の CPLD 46 へのインターフェイスを提供するバスを採用している。適切なバス構成の一部を図 2 に示す。この構成には、特に、アドレスバス (ADR BUS) とデータバス (DATA BUS) が含まれており、本明細書では集合的にアドレス / データバス (ADDR / DATA BUS) と呼ぶこともある。バス構造によって信号を搬送することで、コンポーネントの相互の対話、メモリおよび I/O データ転送、直接メモリアクセス、その他の機能を実行できる。バス構造は、マスター デバイス 50 がバスとスレーブ デバイス（たとえばスレーブ デバイス 52）を制御する「マスタースレーブ」構成の変形であり、アドレスを復号すると同時に、マスター デバイスが発行するコマンドに従って動作する。

30

## 【0026】

いくつかの構成では、8XC196KD デバイス (Intel Corporation, Santa Clara, CA から入手できる) がバスマスター 50 として動作する。バスマスターは、アドレスラッチャイネーブル (ALE: Address Latch Enable) 信号を外部ラッチに送信し、アドレス / データバスからのアドレスを多重分離する。この信号は外部メモリ（たとえば RAM 28 や EPROM 26）で使用され、下位の 8 つのアドレス信号を復号する。その他の周辺装置は、CPLD 46 と 1 つまたは複数のオクタルバスドライバ 48 の組み合わせによって処理され、制御される。CPLD 46 は、上位の 8 つのアドレスラインを復号し、適切なオクタルバス BUS ドライバ 48 に対して ENABLE 信号を発行することで、下位の 8 つのアドレスラインを使用して周辺装置を処理できる。バスを介して転送された信号は、実行する機能に基づいて複数のクラスにグループ分けできる。こうしたクラスには、制御信号、アドレスおよび抑制信号、データ信号がある。

40

## 【0027】

監視機能

本発明のいくつかの構成は、セルフテストステータスおよび報告の機能を提供し、高度な監視機能をサポートする。いくつかの構成において、電源電圧は論理カード 10 を備える機器の背面パネルで測定できる。たとえば、マイクロコントローラ 12 で動作するソフトウェアまたはファームウェアによって、バス状態の過不足の電圧をテストし、報告する

50

。いくつかの構成において、監視の対象となる各電源の電圧は、パネル背面からDVMで直接測定できる。

#### 【0028】

本発明のさまざまな構成において、マイクロコントローラ12とCPLD46は2つの別々のサブシステムとして並列に実行される。安全関連のロジックやグルーロジックをCPLDに適切に分割することで、いずれか1つのサブシステムに発生した破局的な障害が他のいずれかのサブシステムに必ずしも影響を及ぼさない。たとえば、マイクロコントローラ12で使用するアドレス/データラッチのセット、マルチプレクサ、デマルチプレクサ、割り込みコントローラ(*interrupt controllers*)は第1のCPLD46内でプログラミングしてもよい。別のCPLD46(または一連のCPLD)は、論理カード10を含む機器の機能を実装するようにプログラミングしてもよい。<sup>10</sup>。マイクロコントローラ12で使用する数百個のレジスタやアドレスデコーダ(*address decoders*)を追加してもよい(CPLD46の物理的な限界まで)。論理カード10を含む機器の動作を定義するCPLD46は、今後のプラントのアプリケーションに合わせて調整できる。たとえば、I/Oライン、タイマー、波形発生器(*waveform generators*)、さまざまなステートマシンを追加してもよい。マイクロコントローラ12のグルーロジック(CPLD46内または他の場所)により、マイクロコントローラロジックサブシステム12とCPLDロジックサブシステム46とのバッファリングが可能になる。このような構成では、バッファリングCPLD46が正常に動作している限り、マイクロコントローラ12内のロジックの破局的な障害は機器の論理カード10の性能には影響を及ぼさない。こうした分割によって、機器の論理カード10は動作でき、安全上の分類の異なる他の機器にインターフェイスできる。たとえば、CPLD46はその動作が人命を左右する安全に関連する機能を実行できる。EPROM26および/またはRAM28内にマイクロコントローラ12に対して人命を危険にさらす安全以外の機能を実行するように命令するソフトウェアまたはファームウェアを配置できる。あるいは、CPLD46は安全関連以外の機能を実行してもよい。<sup>20</sup> EPROM26および/またはRAM28と組み合わせて安全関連の機能を実行してもよい。CPLD46とマイクロコントローラ12は、選択された機能を協調的に実行するように構成してもよい。前面パネルインディケータ30および/または44は論理カード10で制御されており、論理カード10で監視かつ/または制御する外部システムに関する情報(たとえば、バルブやポンプの状態、または機器への入力を提供する外部センサー)をユーザーに提供する。<sup>30</sup>

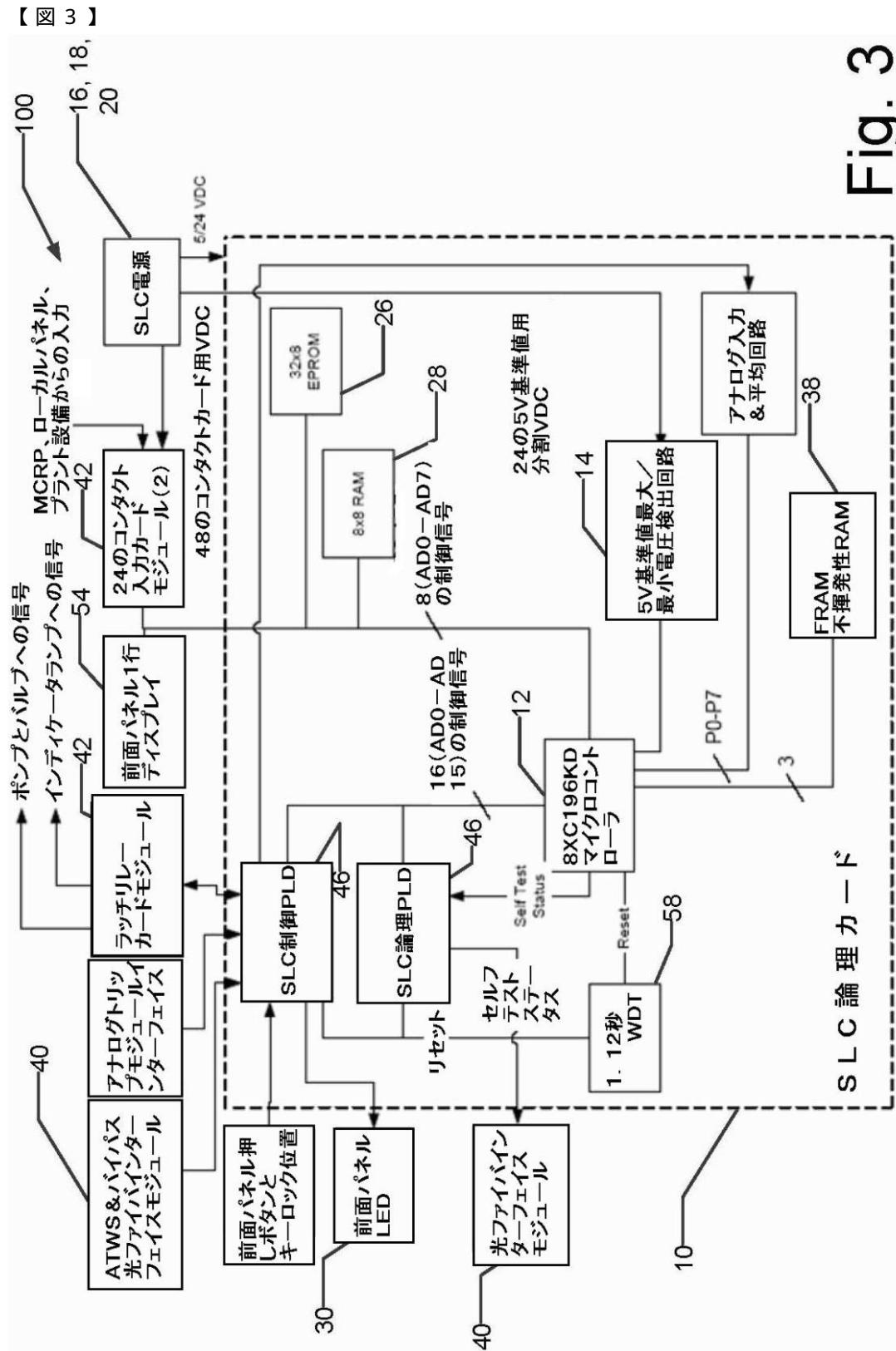

#### 【0029】

前述のように、論理カード10はさまざまなタイプの機器(たとえば、OLU、SLC、HPCF)で利用できるが、特に原子力発電所内にある複数の安全システムに適している。たとえば、原子炉容器(*reactor vessel*)を備える原子力発電所内のホウ酸注入系(SLC)の1つの構成では、4つのスクラム失敗イベント(ATWS:*T ransient Without Scram*)論理ユニットの少なくとも2つによって、またはオペレータが起動したキースイッチによってコマンドが発行された場合に、原子炉容器にホウ素溶液が注入される。注入のプロセスは、ロッドの動作を制御しなくても原子炉を全出力から臨界前(*sub-critical*)の状態にするのに十分である。いくつかの構成において、SLCシステムは2つの冗長SLC論理ユニットコントローラを備えており、安全区分1と2に配置する。図3を参照すると、SLC論理プロセッサ100として構成された論理カード10をSLCシステムで使用し、自動または手動で起動する。起動すると、SLC論理プロセッサ100は必要なバルブとポンプを自動的に制御し、原子炉を全出力から臨界前の状態にする。SLC論理プロセッサ100はハードウェアベースとソフトウェアベースのロジック(マイクロコントローラ12とCPLD46)を協調的に使用して、SLC論理プロセッサ100のステータスを監視かつ報告し、監視機能を自動化するための制御機能とソフトウェアを実現する。SLC論理プロセッサ100内の論理カード10はモジュール方式で設計されており、機器の障害に関する通知を<sup>40</sup>

オペレータに自動送信するように構成できる。いくつかの構成では、セルフテストソフトウェアおよびハードウェアの機能が提供され、モジュールレベルで障害を特定できる。したがって、モジュールを交換することで SLC 論理プロセッサ 100 のさまざまな構成を迅速に修復できる（たとえば 30 分以内）。

#### 【0030】

SLC 論理プロセッサ 100 は NUMAC ファミリのメンバーであり、論理カード 100 ( CPLD 46 を含む)、マイクロコントローラ 12、ソフトウェア / フームウェアプログラミングを含んでいる。いくつかの実施形態は、SLC 注入の中央制御室パネル (Main Control Room Panel) から送信される手動の起動 / 停止信号を処理して「深層防護 (Defense in Depth)」を実現し、このシステムの多様性の要件を満足するように構成されている。いくつかの構成では、さらに前面パネル (図 4 を参照) に機器のセルフテストとステータス診断が表示され、Reactor Trip and Isolation Function (RTIF) Communications Interface Module (CIM) に送信される。いくつかの構成において、安全に関連する機能は、ハードワイヤード (hardwired) (CPLD 46) と SLC 論理プロセッサ 100 内のソフトウェアロジックで協調的に実行される。ソフトウェアはこうした機能をセルフテスト診断で監視し、光ファイバモジュール 40 を経由してステータスマッセージを CIM に送信する。また、ソフトウェアはシャーシの前面パネル 54 の LED 30 と英数字ディスプレイ 44 を制御し、前面パネルの押しボタンとキーロックスイッチ 56 に直ちに反応する。いくつかの構成において、ハードワイヤード / SLC 論理プロセッサのソフトウェアによる協調的な機能には、中央制御室パネル (MCRP) 上の 24 のコンタクト入力モジュール (Contact Input Module) 42 を介して MCRP から信号を受信する機能、ソリッドステートリレーを介してインディケータライトを制御する機能、さらにラッチリレー制御モジュール (Latching Relay Control Module) 42 を介してポンプとバルブを制御する機能が含まれる。10

#### 【0031】

コンタクト入力モジュール 42 (たとえば、いくつかの構成では 24 のコンタクト入力モジュール) は MCRP にインターフェイスし、オペレータはさまざまなスイッチや押しボタンを使用して SLC 論理プロセッサ 100 を制御できる。また、コンタクト入力モジュール 42 はポンプ、バルブ、スイッチギアからステータス信号を受信する。30

#### 【0032】

本発明のいくつかの構成において、光ファイバモジュール 40 には少なくとも 1 つの送信機が含まれる。光ファイバモジュール 40 は、SLC 論理プロセッサ 100 と Reactor Trip and Isolation Function (RTIF) Communication Interface Module (CIM) との通信リンクを提供する。

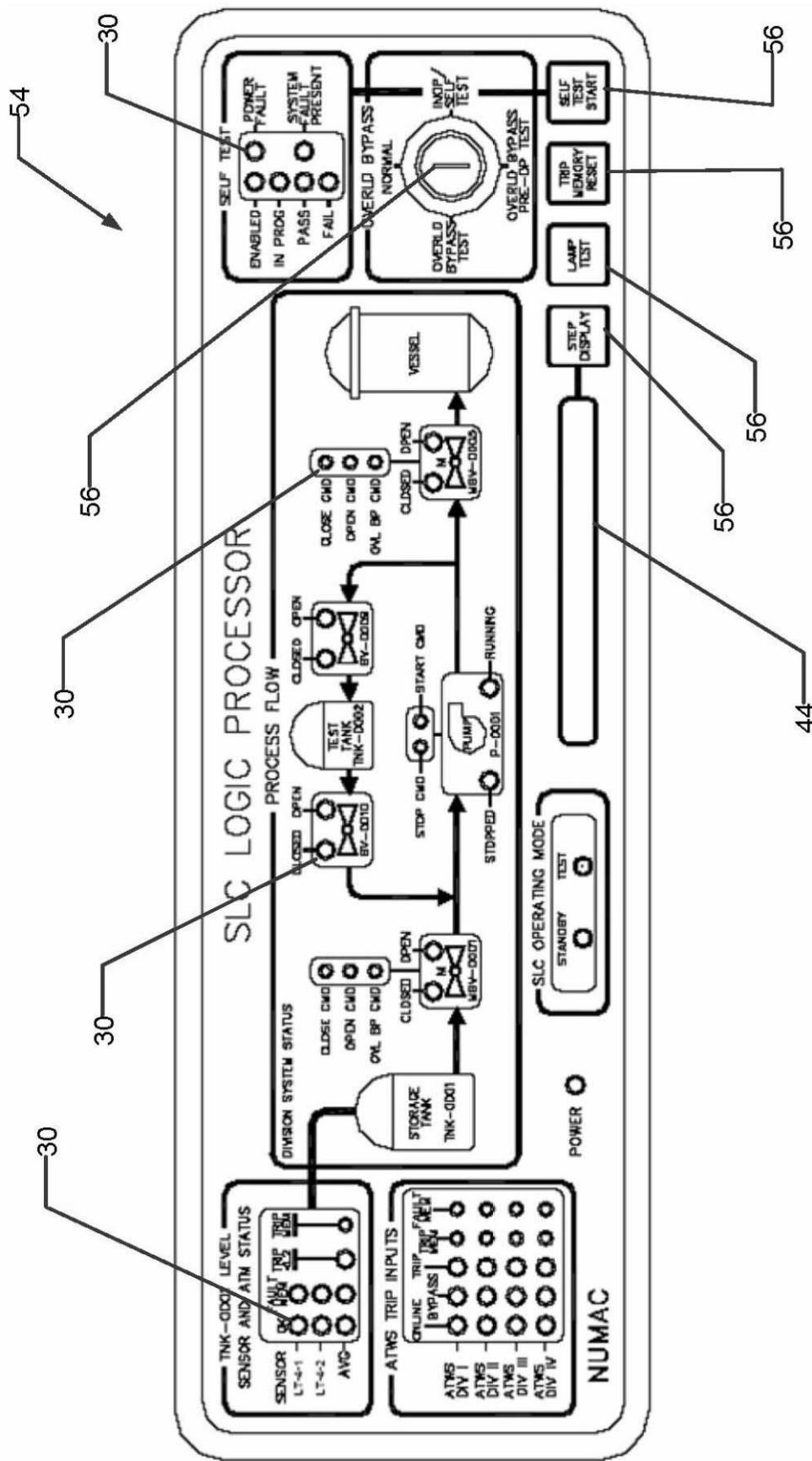

#### 【0033】

いくつかの構成において、図 4 を参照すると、SLC 前面パネル 54 アセンブリはオペレータと SLC 論理プロセッサとのローカルインターフェイスを提供する。SLC 前面パネルアセンブリには、オペレータがセルフテストを開始し、SLC 論理プロセッサとホウ素注入系のステータスを監視するための押しボタンとキーロックスイッチ 56 が含まれる。前面パネルの LED 30 とディスプレイ 44 は、ATWS 信号、バイパス信号、アナログトリップモジュール (ATM: Analog Trip Module) 信号、中央制御室パネル (MCRP) 信号、リレー、セルフテストの結果、および SLC 論理プロセッサの動作モードを示している。40

#### 【0034】

本発明のいくつかの構成において、2 つのラッチリレー モジュール 42 はそれぞれ 12 個の機械的ラッチリレーと 2 つのソリッドステートリレー (solid-state relays) を備えている。ラッチリレー コンタクト (latching relay) 50

`contacts`)を使用してポンプの起動と停止、およびバルブの開閉機能を制御する。ソリッドステートリレーを使用して、MCRP上に配置されたインディケータライトを操作する。

#### 【0035】

SLC論理プロセッサカード10は、SLC論理プロセッサのロジックによる処理、監視、通信の各機能を提供する。このモジュールには、マイクロコントローラ12、メモリ38、26、28、CPLD46、およびインターフェイスロジックが含まれる。このモジュールは、入力モジュール34からのMCRP信号のステータスを表す信号を受信し、ホウ素タンクレベル信号を受信する。さらに、ノンラッチ(Non-Latching)リレー モジュール42上のリレーを制御し、光ファイバモジュール40のインターフェイスしてRTIF CIMにメッセージを送信する。マイクロコントローラスーパーバイザは、電源16および/または18からの入力電圧が範囲外の場合にリセット信号を生成する電源監視回路14の形で提供される。いくつかの構成において、監視回路14はさらにCPLD46ロジックをリセットして初期状態に戻す。ウォッチドッグタイマー58は、あらかじめ指定した時間(たとえば1.12秒)内にマイクロコントローラがストップ信号を送信できなかった場合にタイムアウトする。いくつかの構成において、ウォッチドッグタイマー58はマスク不可能な割り込み(NMI:non-maskable interrupt)に電気的に接続するので、ウォッチドッグタイマー58がタイムアウトすると、マイクロコントローラ12へのNMIが生成され、ウォームリブートが行われる。ただし、ウォッチドッグタイマーによってCPLD46はリセットされない。

10

#### 【0036】

いくつかの構成において、CPLD46は複雑な560個のマクロセル(macro-cell)のプログラム可能な論理デバイス(PLD:Programmable Logic Devices)を備えており、a) EEPROM26およびRAM28メモリデバイスとメモリにマップされたすべてのI/O機能のアドレス復号、b) 低速の周辺装置にアクセスするためのマイクロコントローラ12の待ち状態(いくつかの構成において、前面パネルLEDディスプレイ30と24枚のコンタクト入力カードには、読み出しアクセスと書き込みアクセスのための2つの待ち状態が必要である)、c) マイクロコントローラ12が入力信号のステータス、出力制御、PLD改訂、リレーのステータスにアクセスするためのアドレス指定可能なポートとレジスタ、d) リードライバコンポーネントにインターフェイスする5つの出力ポート、e) 前面パネルディスプレイカードにインターフェイスする1つの出力ポート、f) 12MHz~1MHzのクロックジェネレータ、g) SLC論理プロセッサの1) ATMトリップステータスとコンタクト入力スイッチステータスの監視、2) コンタクト入力の処理、3) ポンプとバルブの制御コマンド生成のすべての機能ロジックを提供するように構成されている。

20

#### 【0037】

電流が限界に達して温度限流器が加熱されると、限流器が自動的にリセットされ、過電流の状態がなくなるまで回路が開くことで、SLC論理モジュールの入力ラインが保護される。

30

#### 【0038】

いくつかの構成において、32KB EEPROM26はソフトウェアを格納する不揮発性ストレージを提供する。いくつかの構成において、すべてのソフトウェアはファームウェアとして不揮発性メモリに格納されるので、ソフトウェアの変更はEEPROMの交換によって実行される。いくつかの構成において、8KBのスタティックRAM28はマイクロコントローラ12から要求される高速の読み出し/書き込みメモリを提供する。いくつかの構成で提供される不揮発性の2Kx8強誘電性RAM38は、電力が供給されなくなっても失われてはならないアプリケーションパラメータの記憶場所を提供する。このRAMは電力消費が低く、耐久性がきわめて高いシリアルデバイスである。マイクロコントローラのポート1を介した4線のシリアルインターフェイスによって、メモリデバイス内の任意のバイトにアクセスできる。NVRAM38に格納する変数の例には

40

50

、 1 ) コールドブートカウンタ、 2 ) ウォームブートカウンタ、 3 ) ウオッヂドッグカウンタ、 4 ) 電源電圧の測定値と設定値、 5 ) エラーコード、 6 ) セルフテストステータスがあるが、これらに限定はされない。

#### 【 0 0 3 9 】

L E D 6 0 は、論理カード 1 0 自体の上に配置され、テストおよび / または障害を示している。また、必要に応じて電圧とタイミングを観測するさまざまなテストポイントと監視ポイントが提供される。

#### 【 0 0 4 0 】

S L C 論理プロセッサ 1 0 0 は、シャーシ背面にあるコネクタを介して光ファイバ出力などのさまざまな電気信号にインターフェイスする論理カード 1 0 を備えている。電気的入力には、中央制御室パネルやさまざまなポンプ、流量計、圧力トランスデューサ ( t r a n s d u c e r s ) 上のコンタクトクロージャ ( c o n t a c t c l o s u r e s ) が含まれる。シャーシの前面パネルにも、複数の電気的コンタクト入力が配置されている。こうした入力には、押しボタンやキーロックスイッチ 5 6 が含まれる。

#### 【 0 0 4 1 】

##### イベントベースオペレーティングシステム ( E B O S )

いくつかの構成において、原子力発電所向けのホウ酸注入系 ( S L C ) は I n t e l Corporation , S a n t a C l a r a , C A から入手できる I N T E L ( 登録商標 ) 8 7 C 1 9 6 K D マイクロコントローラ 1 2 を使用している。論理プロセッサカード 1 0 は、さらに 8 K B のランダムアクセスメモリ ( R A M : R a n d o m A c c e s s M e m o r y ) 2 8 、 3 2 K B の外付けの電気的にプログラム可能な読み出し専用メモリ ( E P R O M : E l e c t r i c a l l y P r o g r a m m a b l e R e a d O n l y M e m o r y ) 2 6 、および 2 K B の不揮発性メモリ N V R A M 3 8 が含まれる。「 K D 」バージョンのマイクロコントローラ 1 2 には、さらに 1 0 2 4 バイトの内蔵 R A M と 3 2 K B の 1 度のみ書き込み可能な読み出し専用メモリ ( R O M : R e a d O n l y M e m o r y ) が含まれる。ただし、これらは本発明のいくつかの構成では使用されない。本発明のいくつかの構成において、ノンプリエンプティブなイベントベースのオペレーティングシステム ( E B O S ) が提供される。これは、特にこうしたハードウェアアーキテクチャおよび原子力発電所内の S L C システムに適している。ただし、本発明の E B O S 構成は、 S L C システムにも原子力発電所での利用にも限定はされず、特定のタイプのマイクロコントローラ、マイクロプロセッサ、コンピュータ、論理カードのいずれにも限定はされない。

#### 【 0 0 4 2 】

マイクロコントローラ 1 2 は、高速の計算と迅速な入力 / 出力 ( I / O ) 操作を行う 1 6 ビットの C H M O S デバイスである。

#### 【 0 0 4 3 】

8 7 C 1 9 6 K D マイクロコントローラ 1 2 は、さまざまな方法で構成できる 2 つの別々の内蔵タイマーを提供する。本発明のいくつかの構成では、多くのタイマー ( たとえば 8 個以上の同期タイマー ) を提供する。多くのハードウェア ( たとえば外付けのタイマー ) を提供しないように、本発明のいくつかの構成では、限られた数のハードウェアタイマー ( たとえばマイクロソフトコントローラ 1 2 の 2 つのタイマー ) を使用して多くのタイマーがあるように見せかける E B O S を提供する。このように、本発明のいくつかの構成では、 E B O S と適切なアプリケーションソフトウェアを提供し、時間指定イベントより少ない数のタイマーで複数の時間指定イベントを検出し、追跡する。中央のタイミング ( t i m i n g ) 機能が提供され、本明細書では個別の「 チック 」を提供するシステムクロックと呼ぶ。本発明のいくつかの構成では、唯一のタイマーを使用して中央のタイミング機能を提供し、すべてのタイミング機能が唯一のポイントから制御され、監視され、更新されるので、決定性 ( d e t e r m i n i s m ) のレベルが向上する。

#### 【 0 0 4 4 】

本発明のいくつかの構成では、スケジューラとシステムクロックの両方を提供し、タイ

10

20

30

40

50

ミングイベントを管理する。スケジューラを使用することでイベントベースのオペレーティングシステム（E B O S）の抽象化とカプセル化が進み、結果として実装に必要なコードの量が減少するとともに、モジュール性が向上し、ソフトウェアメンテナンスコストが削減される。いくつかの構成では、さらにコンテキストスイッチャ（context switcher）が提供される。実行ループにおいて、コンテキストスイッチャはたとえば1つまたは複数のC A S E文またはI F、E L S E文の組み合わせを含むソフトウェアモジュールを備えていてもよい。（C A S E文とI F、E L S E文の組み合わせは、CおよびC++プログラミング言語のコードである。他の言語の相当する文も使用できることは、コンピュータプログラミング技術者には言うまでもない。本明細書と添付の特許請求の範囲に記載するこのCまたはC++に固有の表現は、本発明と請求項をCまたはC++プログラミング言語を使用する構成またはこれを含む構成に限定するものと理解してはならない。）コンテキストスイッチャは実行機能のプリエンプション（preempt）を行い、プリエンプションを行った機能を正確に復元するために必要なオーバーヘッドを提供する。しかし、本発明のいくつかの構成では、こうしたプリエンプションが提供されず、それに伴う複雑性は回避される。代わりに、コンテキストスイッチャは抽象化とカプセル化を使用したブランチアクティビティ（branching activity）を呼び出す。

#### 【0045】

いくつかの構成ではセマフォが提供され、これを使用してアトミックな（atomic）操作を保護する。たとえば、いくつかの構成において唯一のセマフォ構造が提供され、E B O Sでイベントが発生したがイベントの厳密な特性がわからない場合に、残っているアプリケーションソフトウェアについて通知する。このように、機能をモジュール化でき、S L Cの安全性と堅牢性を維持できる。

#### 【0046】

E B O Sイベントは、スケジューラの外付けハードウェア割り込みの結果として、または入力レジスタがポーリングするときに発生する。いくつかの構成において、スケジューラは割り込みを生成するハードウェアタイマーでも定義される。本発明のいくつかの構成で使用する8 X C 1 9 6 K Dマイクロコントローラは、ハードウェアイベント割り込みを処理するように構成されているが、本発明の多くの構成では割り込みの使用を制限または限定している。8 X C 1 9 6 K Dマイクロコントローラは、周辺装置ステータスタイマー（P S T：Peripheral Status Timers）、パルス幅変調（P W M：Pulse Width Modulators）、高速I / O（H S I O：High Speed I / O）を含む18種類の割り込みを提供する。ただし、本発明のいくつかの構成では、使用する割り込みを制限している。たとえば、割り込みをタイマー割り込み（システムクロックとスケジューラで使用する）、押しボタンイベントをキャプチャする外部割り込み、送信（T X）割り込み（マイクロコントローラのT Xポートにデータを送信する）、マスク不可能な割り込み（N M I、ウォッチドッグタイマーで使用する）に制限してもよい。

表Iは割り込みと、8 X C 1 9 6 K Dマイクロコントローラが提供する優先順位のリストである。本発明のいくつかの構成ではこのすべてを利用できる。

#### 【0047】

表I

【表1】

【表1】

| 優先順位 | 割り込み名                      | 割り込みアプリケーションステータス          |

|------|----------------------------|----------------------------|

| 0    | タイマーオーバーフロー割り込み            | 無効                         |

| 1    | A/D変換完了割り込み                | 無効                         |

| 2    | H S I データ利用可能割り込み          | 無効                         |

| 3    | H S O 割り込み                 | 無効                         |

| 4    | H S I . 0 ピン割り込み           | 無効                         |

| 5    | タイマー割り込み                   | 無効                         |

| 6    | シリアルポート割り込み                | 無効                         |

| 7    | 外部割り込み                     | 有効（診断モードで押しボタンのみ）          |

| 8    | 送信割り込み                     | 有効                         |

| 9    | 受信割り込み                     | 標準モードで無効、I N O P セルフテストで有効 |

| 10   | H S I f i f o 4 割り込み       | 無効                         |

| 11   | タイマー2キャプチャ割り込み             | 無効                         |

| 12   | タイマー2オーバーフロー割り込み           | 有効（システムクロック）               |

| 13   | 外部割り込み1                    | 無効                         |

| 14   | H S I f i f o f u l 1 割り込み | 無効                         |

| 15   | N M I                      | 有効（無効化できない）                |

| N/A  | ソフトウェアトラップ                 | エラー処理の場合は有効                |

| N/A  | 実装されていないO p C o d e        | エラー処理の場合は有効                |

## 【0048】

割り込みを使用することで決定性が向上し、マイクロコントローラのハードウェア割り込みの優先順位スキーマに従ってE B O Sイベントに優先順位が割り当てられる。8 X C 30

196 K D 上の割り込みは、優先順位に従って処理される。番号が大きい割り込みほど処理の優先順位が高い。S L C のいくつかの構成では、N M I 、ソフトウェアタイマーのオーバーフロー、T X データ、最後に外付けハードウェア割り込みの順に処理される。ソフトウェアトラップと実装されないO p C o d e 割り込みには優先順位を割り当てていない。いくつかの構成では、一般的なタイマー割り込みの代わりにタイマー2オーバーフロー割り込みを使用することで、システムクロックとその機能の優先順位を上げ、システムクロックが押しボタン、データ送信、入力イベントのポーリングより優先されることを保証している。このような構成では、N M I （ウォッチドッグで使用する）はタイマー2オーバーフロー割り込みより優先される唯一のイベントである。

## 【0049】

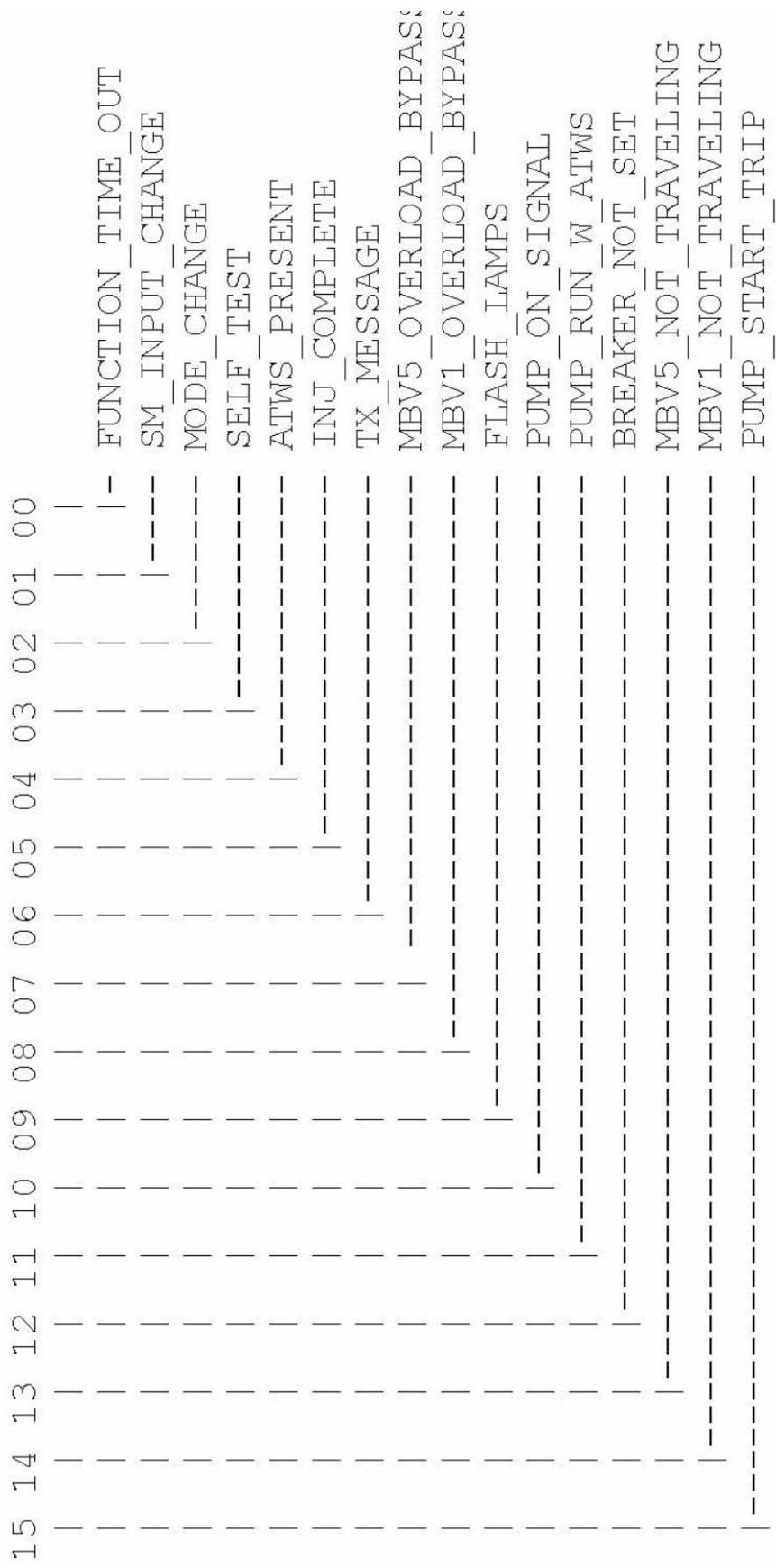

本発明のいくつかの構成において、E B O S で処理できる各イベントに優先順位が割り当てられるので、いったんスケジュールされたイベントがアクティブになると、優先順位の最も高いイベントがスケジューラで処理される。S L C アプリケーションの1つの構成で使用するためにローカライズされたイベントを、優先順位に従って表IIにリストアップする。イベントには、安全機能と応答時間に従って優先順位が割り当てられる。この特定の構成では、ダブルワード（D W O R D ）セマフォを使用しているので、D W O R D の32ビット中の31ビットがさまざまなイベントと優先順位に対応する割り込みとは異なり、低い優先順位の数値を割り当てられたイベントが最初に実行される。こうしたイベントは特定のS L C アプリケーション構成に関連するが、他の多くのイベントドリブン型システムで発生するイベントについても同様の優先順位のリストを作成できる。したがって 50

、本発明の構成が SLC アプリケーションでの使用のみに限定されないことは言うまでもない。

【0050】

表 II

【0051】

【表 2 - 1】

【表 2 - 1】

| 優先順位 | イベント名                    | イベントの説明                                                                  |    |

|------|--------------------------|--------------------------------------------------------------------------|----|

| 1.   | FUNCTION_TIM<br>E_OUT    | 機能にかかる時間が長すぎる。                                                           | 10 |

| 2.   | SM_INPUT_CHA<br>NGE      | ステートマシンの入力が変更された。                                                        |    |

| 3.   | MODE_CHANGE              | 機器のモードが変更された。                                                            |    |

| 4.   | SELF_TEST                | セルフテストのステータスが変更された。                                                      |    |

| 5.   | ATWS_PRESENT             | 有効な ATWS 緩和 (Mitigation) イベントパルスを 0.5 秒間生成し、次のパルスまでのすべての入力を無視する。         |    |

| 6.   | FLASH_LAMPS              | 0.5 秒が経過し、ランプが点滅すると、ランプの状態がオンの場合にオフになり、オフの場合はオンになる。                      | 20 |

| 7.   | INJ_COMPLETE             | 注入完了信号を実際の信号の期限が切れてから 2.5 秒間保持する。                                        |    |

| 8.   | TX_MESSAGE               | 最後のメッセージ送信から 0.5 秒が経過した。                                                 |    |

| 9.   | MBV5_OVERLOA<br>D_BYPASS | MBV5 過負荷バイパス (Overload Bypass) 信号がバイパス信号のない状態で 2.5 秒間要求された。              |    |

| 10.  | MBV1_OVERLOA<br>D_BYPASS | MBV1 過負荷バイパス信号がバイパス信号のない状態で 2.5 秒間要求された。                                 | 30 |

| 11.  | PUMP_START_T<br>RIP      | ポンプ起動信号が 2.5 秒間要求された。                                                    |    |

| 12.  | PUMP_ON_SIGN<br>AL       | ポンプ停止信号を受信してからポンプが 2.5 秒間動作している（停止しようとしたが実際には動作している）。                    |    |

| 13.  | PUMP_RUN_W_A<br>TWS      | ATW 自動起動 (Initiate Auto Start) 信号とポンプ稼働 (Pump Running) 信号が 2.5 秒間存在している。 |    |

| 14.  | BREAKER_NOT_<br>SET      | ブレーカーが設定されない状態で蓄積エネルギー (stored energy) 信号が 2.5 秒間存在している。                 | 40 |

| 15.  | MBV5_2_5_SEC<br>_EVENT   | 2.5 秒の遅延の間にバルブが動作（開くまたは閉じる）を開始するか、あるいは動作を開始しない場合に信号が設定され、保持される。          |    |

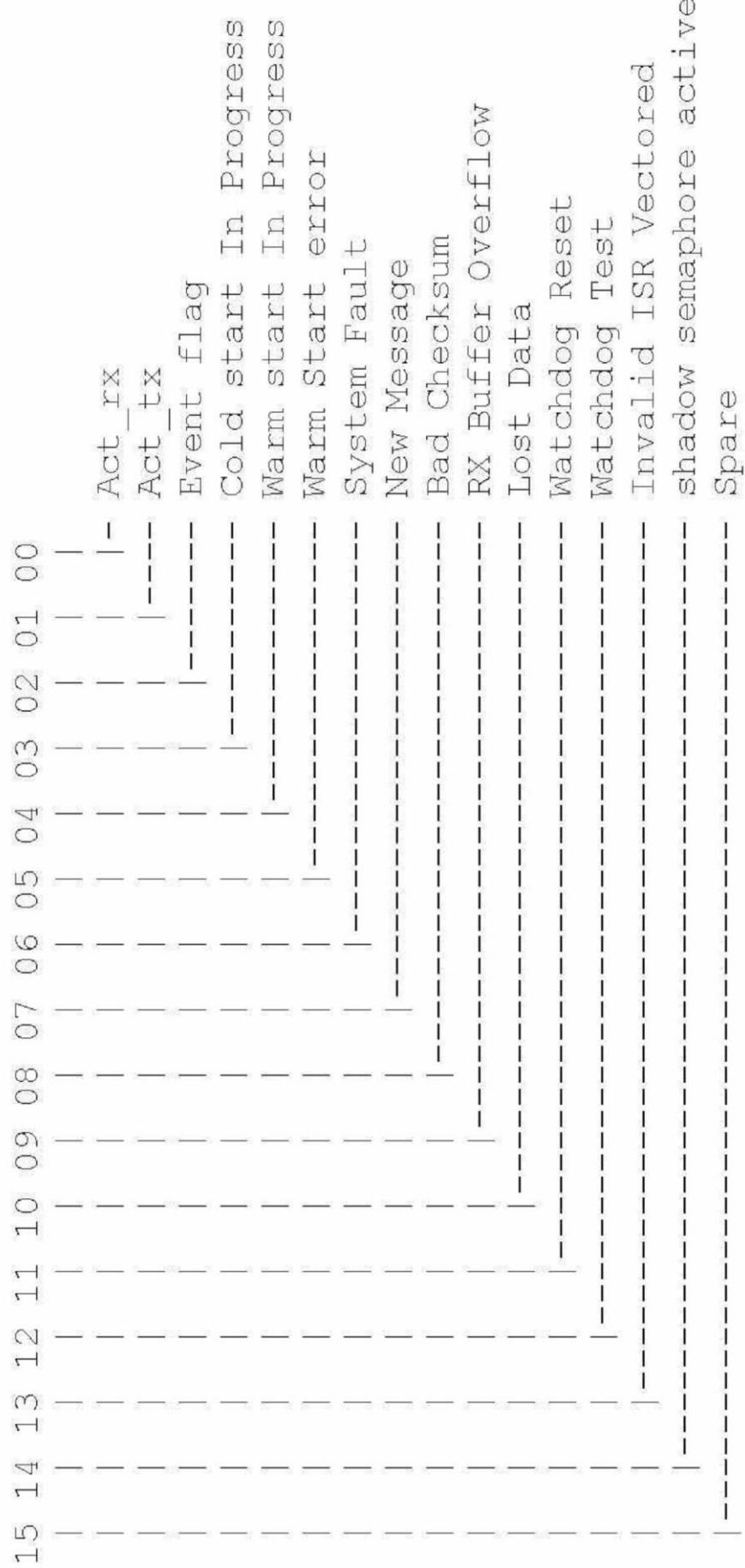

【0052】

【表2-2】

【表2-2】

|           |                           |                                                                                |    |

|-----------|---------------------------|--------------------------------------------------------------------------------|----|

| 16.       | MBV5_VLV_STR<br>OK_EVENT  | 31. 5秒の遅延の間にバルブが開閉を終了するか、あるいは動終了しない場合に信号が設定され、保持される。                           |    |

| 17.       | MBV1_2_5_SEC<br>_EVENT    | 2. 5秒の遅延の間にバルブが動作（開くまたは閉じる）を開始するか、あるいは動作を開始しない場合に信号が設定され、保持される。                | 10 |

| 18.       | MBV1_VLV_STR<br>OKE_EVENT | 101. 5秒の遅延の間にバルブが開閉を終了するか、あるいは動終了しない場合に信号が設定され、保持される。                          |    |

| 19.       | LAMP_TEST_EVENT           | ランプテストイベントの継続をスケジュールし、ランプテスト機能がCPUを独占できないようにする。                                |    |

| 20.       | HEX_DUMP                  | 5秒の遅延の間にオペレータが適切なキーシーケンスを入力し、機器はHEXダンプモードに入る。                                  |    |

| 21.       | MEMORY_RESET<br>_EVENT    | メモリリセットイベントをスケジュールする（押しボタンを押すのと同様に）                                            | 20 |

| 22.       | FIVE_SEC_EVENT            | セルフテスト全体の表示や1行のディスプレイを更新する場合など、5秒以上かかるイベントの場合に、完了時期をスケジュールして通知し、合間に他のタスクを実行する。 |    |

| 23.       | STEP_DISPLAY<br>_EVENT    | ステップディスプレイイベントをスケジュールする（押しボタンを押すのと同様に）                                         |    |

| 24.       | WDT_TEST                  | ウォッチドッグタイマーをテストするのに1. 12秒が経過した。                                                |    |

| 25.       | START_SELF_T<br>EST       | セルフテスト開始イベントをスケジュールする（押しボタンを押すのと同様に）                                           | 30 |

| 26.       | UPDATE_NVRAM<br>_EVENT    | NVRAM内の情報を更新するための1分のイベント                                                       |    |

| 27.       | INVALID_EVEN<br>T         | 常に一覧の最後のイベント。                                                                  |    |

| 28-<br>31 | N/A                       | このSLCアプリケーション構成の例では使用しない。                                                      |    |

【0053】

実行ループは、イベントをビットマップする唯一のセマフォを追跡する。イベントを処理するには、機能を実行する必要がある。本明細書で説明する例示的な構成では、スケジューラのイベントハンドラがLSBからMSBの順にイベントを1度に1つずつ処理する(DWORDセマフォで指定する)。0のイベントが最も優先順位が高い。本発明のいくつかの構成では、複数のイベントのどれを実行するかを決定するときにレイテンシー( latency )を考慮する。より具体的には、特定のスケジュールされたイベントが他のスケジュールされたイベントより短い時間で実行を終了でき、2つのイベントはそれ以外の優先順位が等しい場合に、時間が短い方が優先される。両方のイベントの絶対的なタイマーレイテンシーが同じでも、イベント全体のレイテンシーはイベントのレイテンシーにそのイベントに関連するすべてのイベントを実行する時間を加えたものである。1つのイベントが別のイベントの後にスケジュールされた場合は、2つのレイテンシーが発生し、

レイテンシーのパーセンテージは直ちに実行するようにスケジュールされたイベントの倍になる。ただし、2つのレイテンシーが発生する長期のイベントは、1つのレイテンシーが発生する短期のイベントより実行時間に対するレイテンシーのパーセンテージとしては低くなる可能性がある。したがって、本発明のいくつかの構成では、短期のイベントは優先順位の同じ長期のイベントより前にスケジュールされる。

#### 【0054】

さらに、本発明のいくつかの構成では、安全に関連しない機能には最も低い優先順位が割り当てられる。たとえば、ランプテストイベントは1クロックチックの最長時間、最悪の場合、50ミリ秒のチックで実行できるので、クロックチックの直後にランプテストボタンを押した場合はランプテストが100ミリ秒にわたって実行されている可能性がある。オペレータがランプテストボタンを押した状態で1チックを過ぎると、ランプテストが再スケジュールされる。SLCに優先順位の高いイベントが続けざまに発生すると、ランプテスト機能（またはその他の優先順位の低い安全に関連しない機能）は特定の期間は実行できない。ただし、本発明のいくつかの構成では、すべての機能を6ミリ秒以内に実行できるように構成されているので、こうした状況が発生する可能性は低い。10

#### 【0055】

いくつかの構成では、グローバルフラグセマフォを使用して一部の機能またはイベントの実行を許可または拒否できる。すべてのイベントが実行される可能性があること、そして優先順位の高いイベントはCPU 12を独占しないことを保証するために、イベントがACTIVEになるクロックチックごとに、「Time Active」ECBエントリが増分される。いくつかの構成では、26のイベントが同時にスケジュールされた場合に、1チックの間にどのイベントにも実行されるチャンスが与えられる。このような構成では、1つのイベントが実行されずに26チックを経過すると、シャドウセマフォマスク(shadow semaphore mask)によってこのイベントに優先順位が割り当てられ、次にこのイベントが実行される。20

#### 【0056】

本発明のいくつかの構成では、指定されたセマフォ、システムロック、スケジュールアップデータ(schedule updater)を使用した決定性が保証される。スケジューラとセマフォを組み合わせて使用することで、予想以上に時間のかかるイベントを監視する。スケジューラでセマフォを使用すると、システム障害、ブリエンプション、後続のシステムのウォームスタートが発生する。これらはすべてオペレータの注意を促す異常な状態を発生し、望ましい決定性の結果をもたらす。30

#### 【0057】

さまざまなイベントハンドラ、押しボタン、タイミング、ステートマシンが連携することで、実行中のステートマシンに1つの処理状態から別の処理状態へのコンテキストの切り替えが発生する。コンテキストの切り替えが発生するまで、ステートマシンは実行ループによってセルフテストモードで無限にループする。3つのイベントハンドラを使用して、動作中にマシンに発生するさまざまなタイプのイベントを処理する。

#### 【0058】

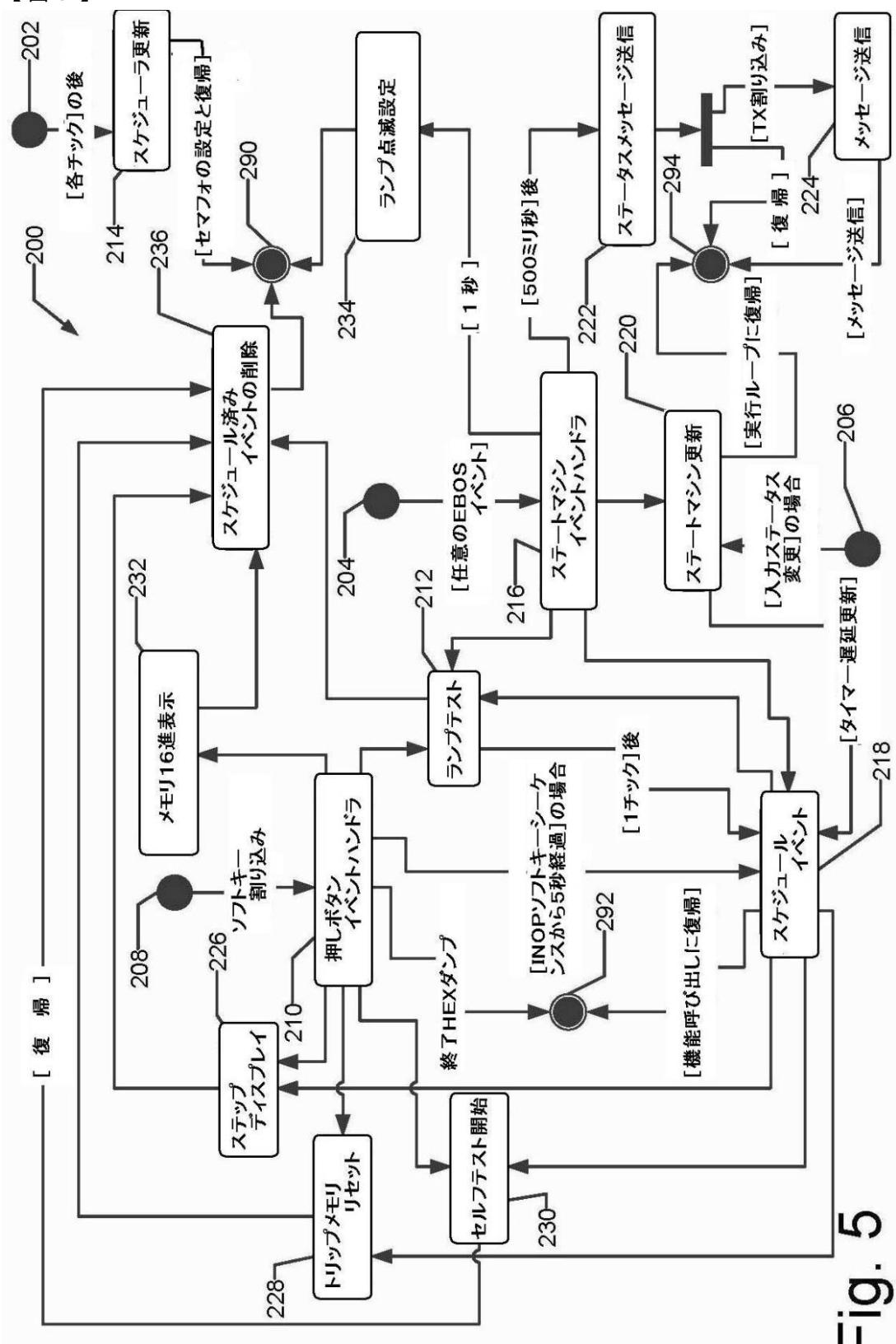

より具体的には、図5を参照すると、本発明のいくつかの構成では、流れ図200によって222で表現される実行ループを提供する。このループの技術的な効果は、たとえば工場の運転中に発生するイベントのタイミング調整とスケジューリングである。ポイント202、204、206、208は、イベントハンドラ起動の原因となるイベントとしてラベル付けされた開始ポイントを表す。終了ポイントは290、292、294で示されている。押しボタンイベントは、押しボタンイベントハンドラ210でほとんど排他的に処理される。このハンドラは、いくつかの構成において押しボタンを押すことで発生する外部イベントによってのみ起動するランプテスト機能212は、CPUを独占できないので、50ミリ秒または1クロック「チック」のランプテスト機能212は保留になり、他のイベントが処理される。したがって、ランプテスト機能212のスケジュール自体が再実行され、次にタイマー／スケジューライベントハンドラ218がこのスケジュールを処理する。4050

理する。システムクロックは、スケジュール更新ハンドラ 214 を使用して、50ミリ秒間隔でスケジューリングイベントが発生していないかをチェックする。ユーザーがモードを変更した場合、または入力ステータスの変更が検出された場合は、ステートマシンイベントハンドラ 216 が起動する。診断モードでは押しボタンイベントが直ちに処理され、完了するとコンテキストはスイッチによって中断されていた機能に戻る。タイマーイベントとステートマシンイベントが発生すると、一般にステートマシンが変更される。この場合は、ステートマシン更新ハンドラ 220 が呼び出され、完了するとコンテキストは実行ループの 294 に戻る。222 で、CIMへのステータス送信イベントがスケジュールされる。TXイベントが発生すると、送信バッファにデータが入り、224 で別の送信機能が生成されてメッセージが送信される。メッセージの送信が完了すると、コンテキストは実行ループの最後の状態である 294 に直ちに返される。本発明のさまざまな構成において、その他のイベントハンドラ（ステップディスプレイハンドラ 226、トリップメモリリセットハンドラ 228、セルフテスト開始ハンドラ 230、メモリ 16 進表示（`memory hex display`）ハンドラ 232、ランプ点滅設定（`set flashboard lamp`）ハンドラ 234 など）が提供される。一部のイベントは、スケジュールイベント削除ハンドラ 236 で処理された後にスケジュールから削除される。10

#### 【0059】

任意のイベントをスケジュールできるが、通常はタイミングイベントのみがスケジュールされる。「`Value failed to move`（バルブが動かない）」などのアラームは、最初の信号から少し時間が経過してからキャプチャされる。イベントがスケジュールされると、タイマーが起動する。ステートマシンが変化した場合（たとえばバルブ移動信号がアサートされた場合）は、変化が発生したときにイベントがスケジュールから削除される。それ以外の場合は、イベントが発生し、ステートマシンの更新とそれに関連する後続のアラームが発生する。20

#### 【0060】

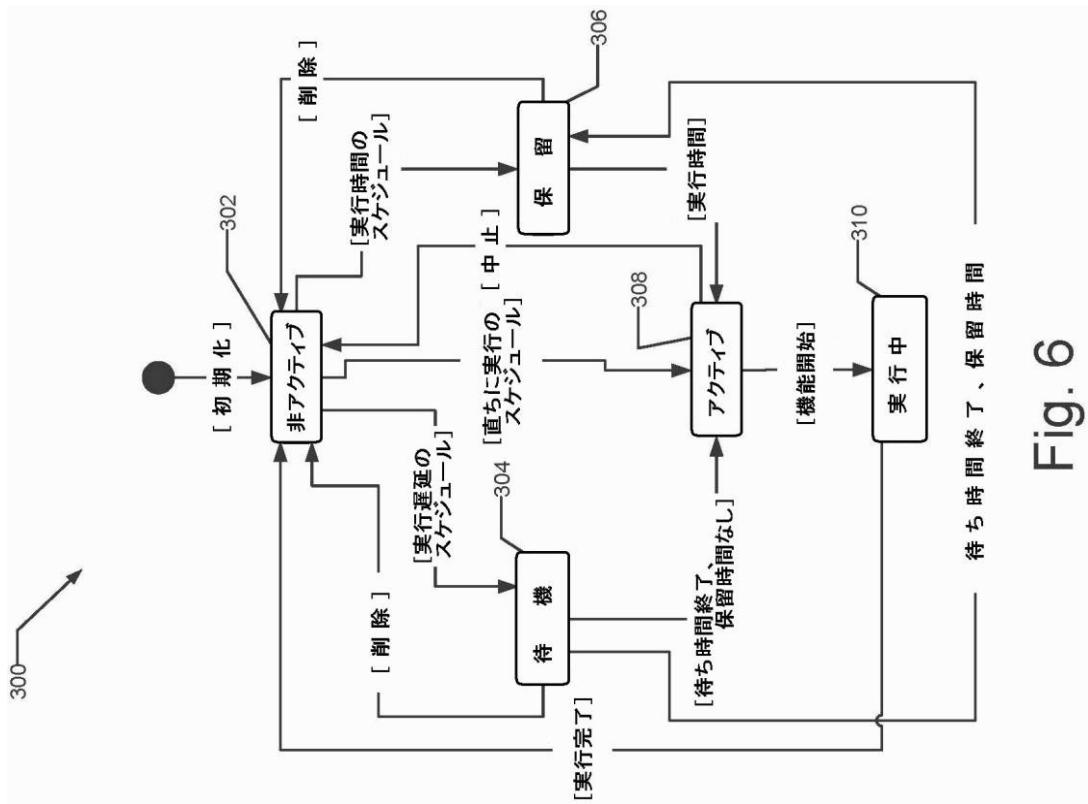

いくつかの構成では、図 6 の状態図 300 を参照すると、イベントの状態は 5 つの状態、すなわち非アクティブ 302、待機 304、保留 306、アクティブ 308、実行 310 のいずれかである。イベントがスケジュールされた場合に、実行時間は希望のタイミング要件を満たすためのクロックチック数の計算値として設定される。チックを刻むたびに、実行時間が減少する。実行時間がゼロになると、以下で説明するスケジューラの状態に関する動作で指定するように状態が変化する。レイテンシー、アクティブな時間、実行された時間もスケジュールアップデータによってクロックサイクルごとに増加または減少する。30

#### 【0061】

EBOSスケジューラは、スケジューライベント制御ブロック（ECB：Event Control Block）データ構造を使用する。イベントごとに、ECBへのエントリがある。たとえば、いくつかの構成において、ECB は以下の構造をとるが、これに限定はされない。

```

typedef struct scheduler_ecb

{

EVENT_STATE event_state;

WORD wait_time;

WORD execution_time;

BYTE time_executed;

WORD time_active;

} ECB;

```

#### 【0062】

スケジュールされた各イベントは、状態図 300 に示す状態に対応する非アクティブ、アクティブ、保留、実行、待機のいずれかの状態が可能である。クロックサイクルまたはクロックチックごとに、次に示す特定のイベントの状態に基づいて、ECB が走査され、50

## 更新される

- ・非アクティブなイベントは、スケジューラで特に注目する必要のないイベントである。

- ・アクティブなイベントは、実行される順番を待っているアクティブなイベントである。アクティブライトが実行されないチックごとに、time\_active\_Ecbエントリが増分される。

- ・保留中のイベントは、実行できるまで特定の時間を必要とするイベントであり、スケジュールアップデータはクロックチックごとにECB内の「time\_to\_execute」ワードから1を減算する。「time\_to\_execute」がゼロになると、状態はアクティブに変化する。

- ・実行中のイベントの状態は、一部のアプリケーションでは機能開始時に設定され、機能終了時に解除される。他のアプリケーションでは、実行中の状態を使用してプログラムアプリケーションにタイマーの特定の実装（たとえばパルスタイマーか遅延タイマーか）に関する信号を送る。機能の開始と終了を制御する場合は、イベントを1度に1つずつ実行する必要があり、イベント実行中のサイクルごとに、ECB「execution\_time」が増分される。execution\_timeはイベントが実行を許可される時間（ハードコードされた値）と比較できる。時間指定イベントのタイプを通知する場合は、状態の変化を使用してアプリケーションまたは実行ループステートマシンおよび論理バスの変化を通知できる。10

- ・待機中のイベントは、実行されたが再び実行されるまでに特定のレイテンシーが必要である。この値は、イベントの実行が完了したときに設定され、「time\_to\_execute」と同様にチックごとにカウントダウンされる。イベントがスケジュールされ、レイテンシーが保留の時間を超えると、両方がカウントダウンされ、保留の時間がゼロになると、直ちに状態がアクティブになる。それ以外の場合は保留中になり、残り時間がカウントダウンされる。0xFFFFFhの値は減少しないので、この値が変わらない限り、イベントは永久に待機する。20

## 【0063】

本発明のいくつかの構成において、システムクロックは約50ミリ秒ごとに1チックを刻む。チックごとに、スケジュールされたイベントがないか、イベント制御ブロック（ECB）がチェックされる。イベントがある場合は、現在の機能を完了できるか、「タイムアウト」とタグ付けされるかに関わらず、プリエンプションが行われる。通常は、機能を完了でき、制御は実行ループに戻る。実行ループは、スケジューリングセマフォを受け取り、機能を呼び出してステートマシンを更新する。30

## 【0064】

本発明のいくつかの構成において、外部のウォッチドッグタイマーは1.12秒後にタイムアウトし、正常な状態では1.00秒以内にリセットされる。ウォッチドッグは、システムクロックISRからリセットされる。これで、ウォッチドッグタスクも実行される。システムクロックISRは50ミリ秒ごとに起動するので、50ミリ秒以内にはリセットできない。標準モードのセルフテスト機能は、実行ループによって実行され、さまざまな機能を備えている。一般に、標準モードの各機能は50ミリ秒以内に実行されるので、コンテキストスイッチャがより優先順位の高い機能に変わる前に、唯一のチックが終了する。本発明のいくつかの構成では、他の多くの機能が6ミリ秒以内に実行される。40

## 【0065】

### 6.1 データストアとデータ構造

## 【0066】

EBOSSは、セマフォを使用してイベントがスケジュールされたかどうかを検知するとともに、グローバルに知られている必要のある特定の機能について通知する。セマフォは、2つのグループ、すなわちスケジュールされたイベントとシステムフラグに分類される。イベントセマフォは、スケジュールされたイベントが現在アクティブであり、実行を待機していることを示す。システムフラグセマフォは、特定のアトミックな機能の実行を許50

可するかどうかを制御する。こうしたセマフォは、特定のアプリケーションで使用するようにカスタマイズできる。SLCアプリケーションのいくつかの構成については、こうしたセマフォの仕様が図7、図8及び図9に示されている。

#### 【0067】

イベントベースのマイクロOSを使用すると、ほんのわずかなCPUオーバーヘッドで、堅牢な機能を提供し、複数のタイミングイベントを同時に追跡できる。

#### 【0068】

特許請求の範囲で使用する「コントローラ」という用語は、特に指定のない限り、その範囲内には、オペレーティングシステムが動作することができるマイクロコントローラ、マイクロプロセッサ、CPU、コンピュータ、または他の同様のデバイスを含むものとすることが認識されよう。コントローラは、オペレーティングシステムを使用して、センサー、タイマー、および/またはスイッチを使用するプログラムを実行し、時間および/または制御イベントを検出できることを目的としている。コントローラには、マイクロコントローラ、およびメモリに使用するエレクトロニクスを含めてよいがこれに限定はされない。外部信号インターフェイスをコントローラに統合してもよいが、それに限定はされない。

10

#### 【0069】

また、特許請求の範囲で使用する「プロセッサ」という用語には、特に指定のない限り、マイクロコントローラ、マイクロプロセッサ、あるいはCPUを含めてもよいことが理解されよう。また、EPOSは不揮発性メモリとしても揮発性メモリとしても提供できる（前述のSLCモジュール、プロセッサ、マイクロコントローラ、CPUなどで提供されるものなど）。いくつかの構成において、EPOSは磁気、光学、または他のタイプの媒体として提供できる。こうした構成では、磁気、光学、または他のタイプの読み取り装置が提供される。たとえば、EPOSは不揮発性または揮発性のメモリ内の命令としても、CD-ROM、DVD、CD-RW、DVD-RW、DVD+RW、フロッピー（登録商標）ディスク、ハードディスク、あるいは紙テープとしても提供できる。さらに、プロセッサへの命令は複数の異なるメモリユニットおよび/または媒体にわたって任意にまたは意図的に分割できるので、メモリおよび/または媒体の組み合わせを使用してもよい。したがって、特に指定のない限り、何かすることを「プロセッサに対して指示するように構成された命令を含むノンプリエンプティブなオペレーティングシステムが記録された機械可読媒体またはメモリには、これらの命令が記録された複数の機械可読媒体またはメモリ（すべて同じタイプである必要はない）が含まれるものと理解されたい。

20

#### 【0070】

本発明のさまざまな実施形態について説明してきたが、本発明の精神と範囲を逸脱しない限りの変更が可能なことは、当業者には言うまでもない。なお、特許請求の範囲に記載された符号は、理解容易のためであってなんら発明の技術的範囲を実施例に限縮するものではない。

30

#### 【図面の簡単な説明】

#### 【0071】

【図1】本発明による論理カードのさまざまな構成を示すブロック図である。

40

【図2】図1に示す論理カードに適したバス構成の1つを示す概略図である。

【図3】図1に示す論理カード構成を備える安全制御機器（この場合は、ホウ酸注入系[SLC]の論理プロセッサ）を示すブロック図である。

【図4】図3に示す機器構成の前面パネルを示す実体図である。

【図5】本発明のいくつかの構成による実行ループ構成を示す流れ図である。

【図6】図5に示す実行ループを実行する間に本発明のいくつかの構成で発生する可能性のあるイベントの状態を示す状態図である。

【図7】本発明のいくつかの構成で使用するイベントセマフォを示す図である。

【図8】本発明のいくつかの構成で使用するイベントセマフォを示す図である。

【図9】本発明のいくつかの構成で使用するフラグセマフォを示す図である。

50

【図1】

【図2】

FIG. 2

Fig. 3

S L C 論 理 力 一 ド

【図4】

Fig. 4

[図 5]

Fig. 5

【図6】

Fig. 6

【図7】

**Fig. 7.**

EventSemaphore (DWORD) (LSB)

८

EventSemaphore (DWORD) (MSB)

【図9】

**Fig. 9**

FlagSemaphore (WORD)

---

フロントページの続き

審査官 井上 宏一

(56)参考文献 特開2000-259429(JP,A)

特開2000-148513(JP,A)

特開平02-156336(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 9 / 46 - 9 / 54